# ARM Cortex-R Series (Armv7-R) Programmer's Guide

Version 1.0

Non-Confidential

Copyright  $\ensuremath{\mathbb{Q}}$  2014 Arm Limited (or its affiliates). All rights reserved.

**Issue 01** den0042\_0100\_01\_en

### ARM Cortex-R Series (Armv7-R) Programmer's Guide

Copyright © 2014 Arm Limited (or its affiliates). All rights reserved.

### Release information

### **Document history**

| Issue   | Date         | Confidentiality  | Change        |

|---------|--------------|------------------|---------------|

| 0100-01 | 3 April 2014 | Non-Confidential | First release |

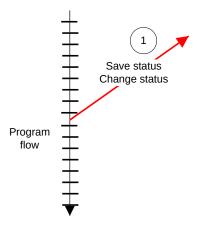

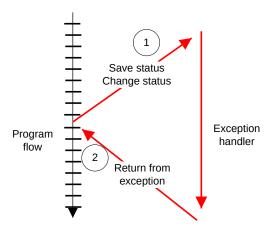

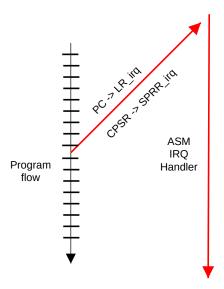

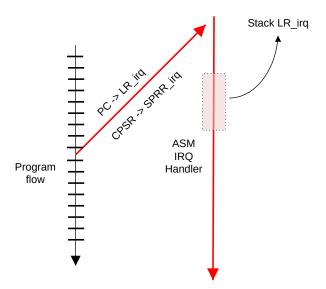

### **Proprietary Notice**

This document is protected by copyright and other related rights and the use or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm Limited ("Arm"). No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether the subject matter of this document infringes any third party patents.

The content of this document is informational only. Any solutions presented herein are subject to changing conditions, information, scope, and data. This document was produced using reasonable efforts based on information available as of the date of issue of this document. The scope of information in this document may exceed that which Arm is required to provide, and such additional information is merely intended to further assist the recipient and does not represent Arm's view of the scope of its obligations. You acknowledge and agree that you possess the necessary expertise in system security and functional safety and that you shall be solely responsible for compliance with all legal, regulatory, safety and security related requirements concerning your products, notwithstanding any information or support that may be provided by Arm herein. In addition, you are responsible for any applications which are used in conjunction with any Arm technology described in this document, and to minimize risks, adequate design and operating safeguards should be provided for by you.

This document may include technical inaccuracies or typographical errors. THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm

makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, any patents, copyrights, trade secrets, trademarks, or other rights.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Reference by Arm to any third party's products or services within this document is not an express or implied approval or endorsement of the use thereof.

This document consists solely of commercial items. You shall be responsible for ensuring that any permitted use, duplication, or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of this document shall prevail.

The validity, construction and performance of this notice shall be governed by English Law.

The Arm corporate logo and words marked with ® or ™ are registered trademarks or trademarks of Arm Limited (or its affiliates) in the US and/or elsewhere. Please follow Arm's trademark usage guidelines at https://www.arm.com/company/policies/trademarks. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

PRE-1121-V1.0

### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

### **Product Status**

The information in this document is Final, that is for a developed product.

### **Feedback**

Arm welcomes feedback on this product and its documentation. To provide feedback on the product, create a ticket on https://support.developer.arm.com

To provide feedback on the document, fill the following survey: https://developer.arm.com/documentation-feedback-survey.

### Inclusive language commitment

Arm values inclusive communities. Arm recognizes that we and our industry have used language that can be offensive. Arm strives to lead the industry and create change.

This document includes language that can be offensive. We will replace this language in a future issue of this document.

To report offensive language in this document, email terms@arm.com.

# **Contents**

| 1. Introduction                               | 13 |

|-----------------------------------------------|----|

| 1.1 Conventions                               | 13 |

| 1.2 Useful resources                          | 14 |

| 1.3 Other information                         | 14 |

| 2. Introduction to Cortex-R                   | 16 |

| 2.1 Determinism                               | 18 |

| 3. ARM Architecture and Processors            | 19 |

| 3.1 Processor properties                      | 20 |

| 3.2 Cortex-R series processors                | 22 |

| 3.3 The Cortex-R4 processor                   | 22 |

| 3.4 The Cortex-R5 processor                   | 23 |

| 3.5 The Cortex-R7 processor                   | 24 |

| 3.6 Development platforms                     | 26 |

| 3.7 Operating systems for Cortex-R processors | 26 |

| 4. ARM Processor modes and Registers          | 27 |

| 4.1 Registers                                 | 28 |

| 4.1.1 Program Status Registers                | 30 |

| 4.1.2 Coprocessor 15                          | 32 |

| 4.1.3 System Control Register (SCTLR)         | 34 |

| 5. Introduction to Assembly Language          | 38 |

| 5.1 Comparison with other assembly languages  | 38 |

| 5.2 The ARM instruction sets                  | 39 |

| 5.2.1 Thumb-2                                 | 40 |

| 5.3 Introduction to the GNU Assembler         | 41 |

| 5.3.1 Invoking the GNU Assembler              | 41 |

| 5.3.2 GNU Assembler syntax                    | 41 |

| 5.3.3 Sections                                | 42 |

| 5.3.4 Assembler directives                    | 42 |

| 5.3.5 Expressions                             | 44 |

| 5.3.6 GNU tools naming conventions        | 44 |

|-------------------------------------------|----|

| 5.4 ARM tools assembly language           | 45 |

| 5.4.1 ARM assembler syntax                |    |

| 5.4.2 Labels                              | 45 |

| 5.4.3 Directives                          | 46 |

| 5.5 Interworking                          | 47 |

| 5.6 Identifying assembly code             | 48 |

| 6. Unified Assembly Language Instructions | 49 |

| 6.1 Instruction set basics                | 49 |

| 6.1.1 Constant and immediate values       | 49 |

| 6.1.2 Conditional execution               | 51 |

| 6.1.3 Status flags and condition codes    | 53 |

| 6.2 Data processing operations            | 53 |

| 6.2.1 Operand 2 and the barrel shifter    | 55 |

| 6.2.2 Multiplication operations           | 56 |

| 6.2.3 Additional multiplies               | 56 |

| 6.2.4 Hardware divide operations          | 56 |

| 6.3 Memory instructions                   | 57 |

| 6.3.1 Addressing modes                    | 57 |

| 6.3.2 Multiple transfers                  | 58 |

| 6.4 Branches                              | 59 |

| 6.4.1 Direct and indirect branches        | 60 |

| 6.5 Branch prediction                     | 60 |

| 6.5.1 Static branch prediction            | 61 |

| 6.5.2 Dynamic branch prediction           |    |

| 6.5.3 Return stack prediction             | 61 |

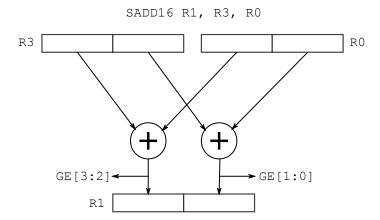

| 6.6 Integer SIMD instructions             | 63 |

| 6.6.1 Integer register SIMD instructions  | 63 |

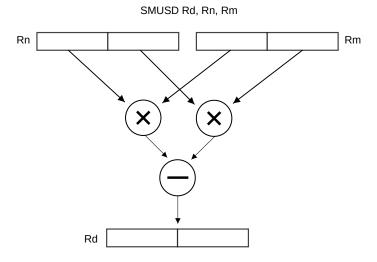

| 6.6.2 Integer register SIMD multiplies    | 64 |

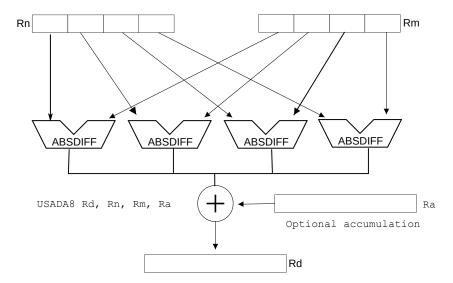

| 6.6.3 Sum of absolute differences         | 65 |

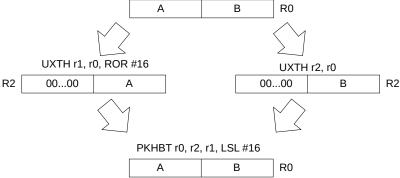

| 6.6.4 Data packing and unpacking          | 66 |

| 6.6.5 Byte selection                      | 66 |

| 6.7 Saturating arithmetic                 | 67 |

| 6.7.1 Saturated math instructions         | 67 |

| 6.8 Miscellaneous instructions            | 67 |

| 6.8.1 Coprocessor instructions                      | 67 |

|-----------------------------------------------------|----|

| 6.8.2 SVC                                           | 68 |

| 6.8.3 PSR modification                              | 68 |

| 6.8.4 Bit manipulation                              | 69 |

| 6.8.5 Cache preload                                 | 69 |

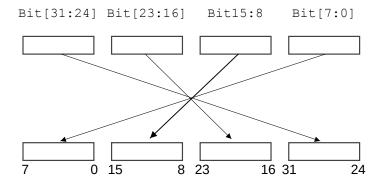

| 6.8.6 Byte reversal                                 | 69 |

| 6.8.7 Other instructions                            | 70 |

| 7. Floating-Point                                   | 71 |

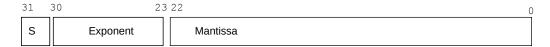

| 7.1 Floating-point basics and the IEEE-754 standard | 71 |

| 7.1.1 Rounding algorithms                           | 73 |

| 7.1.2 ARM VFP                                       | 74 |

| 7.1.3 Instructions                                  | 76 |

| 7.1.4 VFP support in GCC                            | 76 |

| 7.1.5 Enabling VFP                                  | 77 |

| 7.1.6 VFP in the Cortex-R processors                | 77 |

| 7.2 VFP support in the ARM Compiler                 | 78 |

| 7.3 Floating-point optimization                     | 78 |

| 8. Caches                                           | 80 |

| 8.1 Cache drawbacks                                 | 81 |

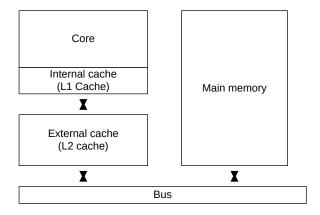

| 8.2 Memory hierarchy                                | 82 |

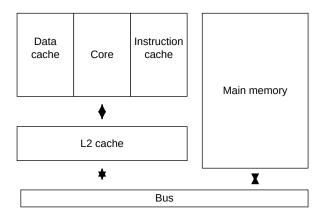

| 8.3 Cache architecture                              | 83 |

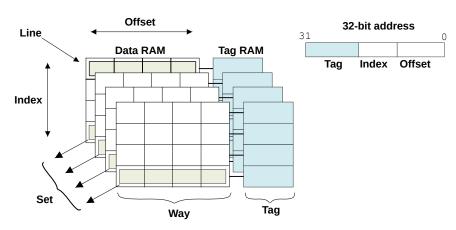

| 8.3.1 Cache terminology                             | 83 |

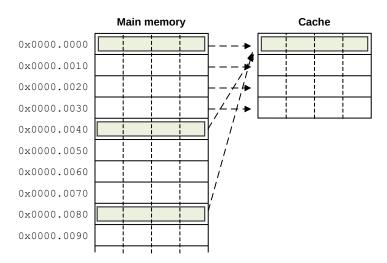

| 8.3.2 Direct mapped caches                          | 84 |

| 8.3.3 Set associative caches                        | 86 |

| 8.3.4 A real-life example                           | 87 |

| 8.3.5 Cache controller                              | 87 |

| 8.4 Cache policies                                  | 88 |

| 8.4.1 Allocation policy                             | 88 |

| 8.4.2 Replacement policy                            |    |

| 8.4.3 Write policy                                  |    |

| 8.4.4 Choosing the best write policy                |    |

| 8.5 Write and Fetch buffers                         |    |

| 8.6 Cache performance and hit rate                  |    |

| 8.7 Invalidating and cleaning cache memory          | 91 |

| 8.8 Point of coherency and unification              | 93 |

| 8.8.1 Example code for cache maintenance operations          | 95  |

|--------------------------------------------------------------|-----|

| 8.9 Level 2 cache controller                                 | 96  |

| 8.9.1 Level 2 cache maintenance                              | 96  |

| 9. Tightly Coupled Memory                                    | 97  |

| 9.1 Location of the TCM in the memory map                    | 99  |

| 9.2 Performance of TCM compared to cache                     | 100 |

| 9.3 Loading values into TCMs                                 | 101 |

| 9.4 TCM Properties in the Cortex-R4 and Cortex-R5 processors | 102 |

| 9.5 TCM properties in the Cortex-R7 processor                | 102 |

| 9.6 Quality of Service                                       | 103 |

| 9.6.1 Access to peripherals                                  | 104 |

| 10. The Memory Protection Unit                               | 105 |

| 10.1 Memory subsystem                                        | 106 |

| 10.2 Implementing a Protected Memory System with Regions     | 106 |

| 10.2.1 Sub-Regions                                           | 110 |

| 10.2.2 MPU memory region programming registers               | 111 |

| 10.2.3 MPU control registers in CP15                         | 112 |

| 10.3 Memory attributes                                       | 113 |

| 10.3.1 Memory Access Permissions                             | 113 |

| 10.3.2 Memory types                                          | 114 |

| 10.3.3 Execute Never                                         | 116 |

| 10.4 Attributes and cache maintenance                        | 116 |

| 10.5 Managing the MPU in context switches                    | 117 |

| 10.5.1 Permission modification in context switching          | 117 |

| 10.6 Cache maintenance recommendations                       | 118 |

| 11. Memory Ordering                                          | 120 |

| 11.1 ARM memory ordering model                               | 121 |

| 11.1.1 Strongly-ordered and Device memory                    | 122 |

| 11.1.2 Normal memory                                         | 122 |

| 11.2 Memory barriers                                         | 124 |

| 11.2.1 Memory barrier use example                            | 126 |

| 11.2.2 Avoiding deadlocks with a barrier                     | 127 |

| 11.2.3 WFE and WFI Interaction with barriers                 | 127 |

| 11.3 Cache coherency implications                            | 128 |

| 11.3.1 Issues with copying code           | 128 |

|-------------------------------------------|-----|

| 11.3.2 Compiler re-ordering optimizations | 128 |

|                                           |     |

| 12. Exceptions and Interrupts             |     |

| 12.1 Types of exception                   |     |

| 12.2 Exception priorities                 |     |

| 12.2.1 Exception mode summary             |     |

| 12.2.2 The Vector table                   |     |

| 12.2.3 FIQ and IRQ                        | 134 |

| 12.2.4 The return instruction             | 135 |

| 12.3 Exception handling                   |     |

| 12.3.1 Exit from an exception handler     |     |

| 12.4 Other exception handlers             | 138 |

| 12.4.1 Abort handler                      | 138 |

| 12.4.2 Undefined instruction handling     | 138 |

| 12.4.3 SVC exception handling             | 139 |

| 12.5 External interrupt requests          |     |

| 12.5.1 Assigning interrupts               | 140 |

| 12.5.2 Simplistic interrupt handling      | 141 |

| 12.5.3 Nested interrupt handling          | 143 |

| 12.6 Low latency interrupts               | 145 |

| 12.7 The Generic Interrupt Controller     | 146 |

| 12.7.1 Configuration                      | 147 |

| 12.7.2 Initialization                     | 148 |

| 12.7.3 Interrupt handling                 | 148 |

|                                           |     |

| 13. Fault Detection and Control Features  |     |

| 13.1 Types of errors                      |     |

| 13.2 Error detection methods              | 151 |

| 13.2.1 Parity                             |     |

| 13.2.2 Error Checking and Correction      | 152 |

| 13.2.3 ECC and parity initialization      | 153 |

| 13.2.4 Redundant logic                    | 153 |

| 13.3 Error signalling                     | 153 |

| 13.3.1 No signal                          |     |

| 13.3.2 Abort                              |     |

| 13.3.3 Interrupt                          | 154 |

| 13.4 Recovering from hard errors                                                   | 154 |

|------------------------------------------------------------------------------------|-----|

| 13.5 Power and performance                                                         | 155 |

| 13.6 Fault detection and control features in the Cortex-R4 processor               | 155 |

| 13.6.1 ECC for the Cache RAM in the Cortex-R4 processor                            | 157 |

| 13.6.2 Parity for the TCM in the Cortex-R4 processor                               | 158 |

| 13.6.3 ECC for the TCMs in the Cortex-R4 processor                                 | 159 |

| 13.6.4 Hard error banks in the Cortex-R4 processor                                 | 160 |

| 13.6.5 Bus protection on the Cortex-R4 processor                                   | 161 |

| 13.6.6 Redundant core in the Cortex-R4 processor                                   | 161 |

| 13.6.7 Test of the fault detection and control features on the Cortex-R4 processor | 162 |

| 13.7 Fault detection and control features in the Cortex-R5 processor               | 163 |

| 13.7.1 Parity in Cache RAM in the Cortex-R5 processor                              | 163 |

| 13.7.2 ECC for the Cache RAM in the Cortex-R5 processor                            | 164 |

| 13.7.3 ECC for the TCMs in the Cortex-R5 processor                                 | 166 |

| 13.7.4 Hard error banks in the Cortex-R5 processor                                 | 167 |

| 13.7.5 Bus protection on the Cortex-R5 processor                                   | 168 |

| 13.7.6 Redundant core in the Cortex-R5 processor                                   | 168 |

| 13.7.7 Test of the fault detection and control features on the Cortex-R5 processor | 169 |

| 13.8 Fault detection and control features in the Cortex-R7 processor               | 170 |

| 13.8.1 ECC for Cache RAMs in the Cortex-R7 processor                               | 170 |

| 13.8.2 ECC for the TCMs on the Cortex-R7 processor                                 | 172 |

| 13.8.3 BTAC and PRED RAM in the Cortex-R7 processor                                | 173 |

| 13.8.4 Hard error banks on the Cortex-R7 processor                                 | 173 |

| 13.8.5 Bus protection on the Cortex-R7 processor                                   | 174 |

| 13.8.6 Redundant core in the Cortex-R processors                                   | 175 |

| 13.8.7 Test of the fault detection and control features on the Cortex-R7 processor | 175 |

| 14. Profiling                                                                      | 177 |

| 14.1 Profiler output                                                               | 177 |

| 14.2 Performance Monitor Unit                                                      | 178 |

| 15. Coding for Cortex-R Processors                                                 | 180 |

| 15.1 Compiler optimizations                                                        | 180 |

| 15.1.1 Idiom recognition                                                           | 180 |

| 15.1.2 Function inlining                                                           | 181 |

| 15.1.3 Eliminating common sub-expressions                                          | 182 |

| 15.1.4 Loop unrolling                                                              | 182 |

| 15.1.5 GCC optimization options           | 183 |

|-------------------------------------------|-----|

| 15.1.6 armcc optimization options         | 185 |

| 15.2 Endianness                           | 186 |

| 15.3 ARM memory system optimizations      | 189 |

| 15.3.1 Use of cache                       | 189 |

| 15.3.2 Loop tiling                        | 190 |

| 15.3.3 Loop interchange                   | 191 |

| 15.3.4 Structure alignment                | 191 |

| 15.3.5 Associativity effects              | 192 |

| 15.3.6 Optimizing instruction cache usage | 192 |

| 15.3.7 Prefetching a memory block access  | 193 |

| 15.3.8 Branch predictability              | 194 |

| 15.4 Source code modifications            | 194 |

| 15.4.1 Loop termination                   | 195 |

| 15.4.2 Loop fusion                        | 195 |

| 15.4.3 Reducing stack and heap usage      | 196 |

| 15.4.4 Variable selection                 | 196 |

| 15.4.5 Pointer aliasing                   | 197 |

| 15.4.6 Division                           | 198 |

| 15.4.7 Extern data                        | 198 |

| 15.4.8 Inline or embedded assembler       | 198 |

| 15.4.9 Complex addressing modes           | 198 |

| 15.4.10 Unaligned access                  | 199 |

| 15.4.11 Linker optimizations              | 199 |

| 15.4.12 Floating point operations         | 199 |

| 16. Boot Code                             | 200 |

| 16.1 Booting a bare-metal system          | 200 |

| 17. Power Management                      | 204 |

| 17.1 Idle management                      | 204 |

| 17.1.1 Power and clocking                 | 205 |

| 17.1.2 Standby                            | 205 |

| 17.1.3 Retention                          | 206 |

| 17.1.4 Power down                         | 206 |

| 17.1.5 Dormant mode                       | 206 |

| 17.2 Assembly language power instructions | 207 |

| 18. Debug                                                 | 208 |

|-----------------------------------------------------------|-----|

| 18.1 ARM debug hardware                                   | 208 |

| 18.1.1 Single stepping                                    | 209 |

| 18.1.2 Debug events                                       | 209 |

| 18.1.3 Semihosting debug                                  | 210 |

| 18.2 ARM trace hardware                                   | 210 |

| 18.2.1 CoreSight                                          | 211 |

| 18.3 Debug monitor                                        | 213 |

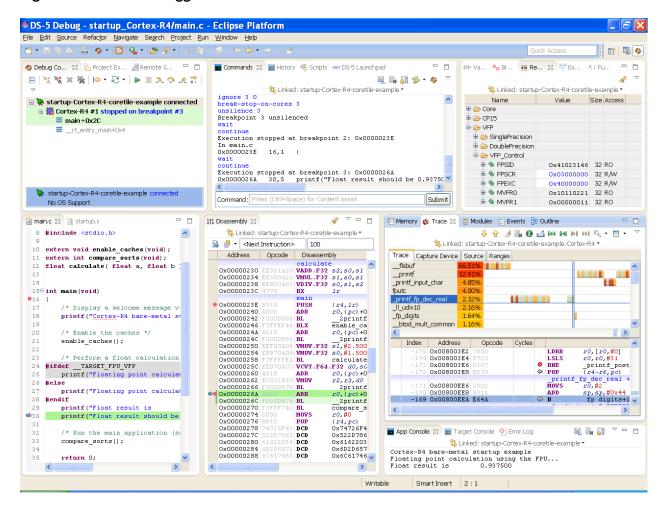

| 18.4 ARM DS-5                                             | 213 |

| 18.4.1 DS-5 debug and trace                               | 215 |

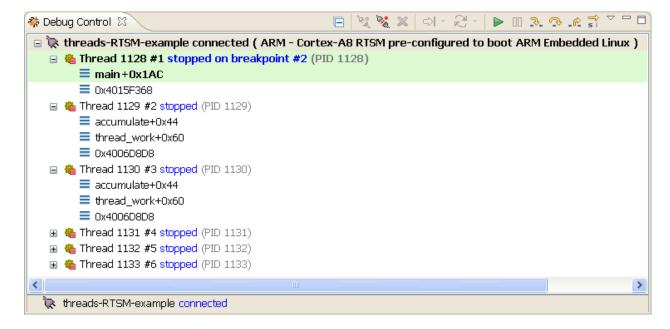

| 18.4.2 Debugging a multi-threaded applications using DS-5 | 215 |

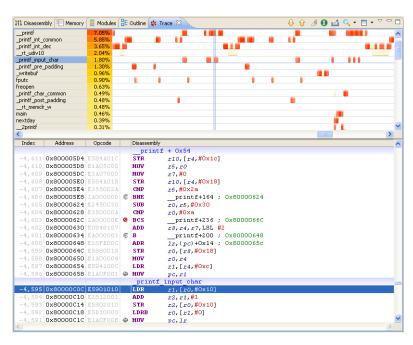

| 18.4.3 Trace support in DS-5                              | 216 |

### 1. Introduction

### 1.1 Conventions

The following subsections describe conventions used in Arm documents.

### Glossary

The Arm Glossary is a list of terms used in Arm documentation, together with definitions for those terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

See the Arm Glossary for more information: developer.arm.com/glossary.

### Typographic conventions

Arm documentation uses typographical conventions to convey specific meaning.

| Convention                 | Use                                                                                                                                                                    |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| italic                     | Citations.                                                                                                                                                             |

| bold                       | Interface elements, such as menu names.                                                                                                                                |

|                            | Terms in descriptive lists, where appropriate.                                                                                                                         |

| monospace                  | Text that you can enter at the keyboard, such as commands, file and program names, and source code.                                                                    |

| monospace <u>underline</u> | A permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.                                        |

| <and></and>                | Encloses replaceable terms for assembler syntax where they appear in code or code fragments.  For example:                                                             |

|                            | MRC p15, 0, <rd>, <crn>, <opcode_2></opcode_2></crn></rd>                                                                                                              |

| SMALL CAPITALS             | Terms that have specific technical meanings as defined in the Arm® Glossary. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE. |

We recommend the following. If you do not follow these recommendations your system might not work.

Your system requires the following. If you do not follow these requirements your system will not work.

You are at risk of causing permanent damage to your system or your equipment, or harming yourself.

This information is important and needs your attention.

A useful tip that might make it easier, better or faster to perform a task.

A reminder of something important that relates to the information you are reading.

### 1.2 Useful resources

This document contains information that is specific to this product. See the following resources for other useful information.

Arm documents are available on developer.arm.com/documentation.

Confidential documents are only available to licensees, when logged in. Each document link in the tables below provides direct access to the online version of the document.

### 1.3 Other information

See the Arm website for other relevant information.

- Arm® Developer.

- Arm® Documentation.

- Technical Support.

- Arm® Glossary.

### 2. Introduction to Cortex-R

An embedded system can be defined as a piece of computer hardware running software designed to perform a specific task. This contrasts with what is generally considered a computer system, that is, one that runs a wide range of general purpose software running multiple tasks.

Embedded systems are commonly found in consumer, industrial, automotive, medical, commercial and military applications, with a controlling SoC designed for a single purpose ranging from digital watches to traffic lights, and larger, more complex systems. Aircraft contain advanced avionics such as inertial guidance systems and GPS receivers, both systems with considerable safety requirements. Automotive safety systems include Anti-lock Braking System (ABS), Electronic Stability Control (ESC/ESP), Traction Control (TCS) and automatic four-wheel drive.

In dealing with security, the embedded systems can also be self-sufficient and be able to deal with a failure of electrical and communication systems. Complexity can vary from single core devices, to multiple units, peripherals and networks.

There are many constraints on embedded systems that can make programming them more of a challenge than writing an application for a general-purpose PC.

### **Memory Footprint**

In many systems, to minimize cost and power, memory size is limited. This forces you to consider the size of the program and how to reduce memory usage while it runs.

#### **Power**

In many embedded systems the power source is a battery. Programmers and hardware designers must take great care to minimize the total energy usage of the system.

#### Real-time behavior

A feature of certain systems is that there are time constraints to respond to external events. This might be a hard requirement or soft requirement. An example hard requirement is a car braking system because it must respond within a certain time consistently. An example soft requirement is an audio processing system because it must complete within a certain time. The ARM Real-time (R) profile defines an architecture aimed at systems that require deterministic timing and low interrupt latency.

A system is said to be real-time if the total correctness of an operation depends not only on its logical correctness, but also on the time in which it is performed. Real-time systems, and their deadlines, are classified by the consequence of missing a deadline:

#### Hard

Missing a deadline is a total system failure.

#### Firm

Infrequent deadline misses are tolerable, but can degrade the systems quality of service. The usefulness of a result is zero after its deadline.

#### Soft

The usefulness of a result degrades after its deadline, thereby degrading the system's Quality of Service.

The goal of a hard real-time system is to ensure that all deadlines are met, but for soft real-time systems the goal can be meeting a certain subset of deadlines to optimize an application-specific criteria. The particular subset of deadlines depends on the application, but some typical examples might include minimizing the lateness of tasks and maximizing the number of high priority tasks meeting their deadlines.

Hard real-time systems are used when it is vital that an event be reacted to within a strict deadline. Such guarantees are required of systems for which not reacting in a certain interval of time would cause great loss in some manner, especially damaging the surroundings physically or threatening human lives, although the strict definition is that missing the deadline constitutes failure of the system. For example, a car engine control systemis a hard real-time system because any delayed signal might cause engine failure or damage to the engine. Other examples include medical systems such as heart pacemakers and industrial process controllers. Hard real-time systems are typically found interacting at a low level with physical hardware, in embedded systems.

Cortex-R series cores are intended for use in deeply-embedded, real-time systems. providing high-performance computing solutions where reliability, high availability, fault tolerance, maintainability and real-time responses are required. This requires optimizing the core for performance while enabling time-critical code to execute in a timely manner. Cortex-R series processors include features to improve the determinism of the core for critical code.

For embedded applications requiring high performance combined with high reliability, Cortex-R series cores also provide several useful features, including both soft and hard error management, redundant dual-core systems using two cores in lock-step and Error Correcting Codes (ECC) on all external buses.

- The ARM Cortex-R4 processor is a mid-range real-time processor for use in deeply embedded systems.

- The ARM Cortex-R4F processor is a Cortex-R4 processor with a floating-point unit (FPU).

- The ARM Cortex-R5 processor is a high-performance real-time processor for use in embedded systems.

- The ARM Cortex-R5F processor is a Cortex-R5 processor with a floating-point unit (FPU).

- The ARM Cortex-R7 MPCore processor is a high performance real-time multi-core processor for use in a vast range of deeply embedded applications.

The Cortex-R series processors differ from both the Cortex-M and Cortex-A series processors. Cortex-R series processors typically offer much higher performance and can run at higher clock speeds than the Cortex-M series, while the Cortex-A series is intended for user-facing applications with complex software operating systems employing virtual memory management.

ARM Partners have developed families of devices using the Cortex-R4 processor with varying feature sets and levels of performance for products ranging from 3G USB modem sticks to automotive microcontrollers such as the TMS570 devices available from Texas Instruments. Infineon also has a Cortex-R4 processor-based medical device platform, MD8710. In all cases these devices are enabled by the specific capabilities of the Cortex-R4 processor, namely high computing performance, configurable features such as soft error handling, and the ability to respond deterministically to hard real-time events in an embedded system

Hard disk drives also continue to be one of the most demanding applications for embedded processors and the Cortex-R series has been adopted by many of the major manufacturers. For HDD and SSD mass storage systems the Cortex-R series processors provide a balance between processor performance, reliability and real-time response, along with ease of development and CoreSight debug to support current and future system chip architectures. Cortex-R series processors are also being widely adopted for Solid State Drives where performance and real time responses both to the host interface and the NAND devices is key to the system performance.

Mobile handsets are introducing high data rate wireless broadband to deliver feature-rich, audio, video and Internet services to users. Advanced multi-core SoCs use Cortex-R series processors for these tasks, complementing Cortex-A series processors for user applications. Low cost and power consumption continue to be key success criteria for mobile handset products. The real-time features of Cortex-R series processors are particularly suited to advanced mobile baseband applications and include support for high frequency interrupts along with fast and deterministic control of data transmission between cellular base-stations and mobile devices.

### 2.1 Determinism

Deeply-embedded, real-time systems require optimizing the processor for performance while enabling time-critical code to execute in a timely manner. Cortex-R processors include features to improve the predictability (determinism) of the processor for critical code. The memory subsystems of Cortex-R processors use Tightly Coupled Memory (TCM) located close to the processor core, meaning the core can have immediate access to memory rather than having to wait for external memory. This is described in Tightly Coupled Memory.

The Cortex-R5 and Cortex-R7 processors include ports specifically to provide access to time-critical peripherals. Having the dedicated ports means that accesses to these peripherals do not contend with lower priority memory accesses in the rest of the memory subsystem. This is described in Access to peripherals.

The Cortex-R processors also contain a number of features that provide deterministic timing and low interrupt latency for hard real-time applications. These features are collectively referred to as Low Latency Interrupt features. This is described in Low latency interrupts.

The Cortex-R7 processor has an out-of-order pipeline, in contrast to the in-order pipeline of the Cortex-R4 and Cortex-R5 processors. This means that the Cortex-R7 processor is more optimized towards performance than the Cortex-R4 and Cortex-R5 processors. The Cortex-R7 processor also includes features to help prioritize more critical code. These features are called Quality of Service (QoS) features and are described in Quality of Service.

### 3. ARM Architecture and Processors

Periodically, new versions of the architecture are announced by ARM. These add new features or make changes to existing behaviors. Such changes are almost always backwards compatible, meaning that user code that ran on older versions of the architecture will continue to run correctly on new versions. Of course, code written to take advantage of new features will not run on older processors that lack these features.

In all versions of the architecture, some system features and behaviors are implementation-defined. For example, the architecture does not define cache sizes or cycle timings for individual instructions. These are determined by the individual processor and SoC.

The ARMv7 architecture also has the concept of profiles. These are variants of the architecture describing processors targeting different markets and uses.

#### The profiles are:

#### Α

The Application profile defines an architecture aimed at high performance processors and supports a virtual memory system using a Memory Management Unit (MMU). It is capable of running fully featured operating systems. It has support for the ARM and Thumb instruction sets.

### R

The Real-time profile defines an architecture aimed at systems that require deterministic timing and low interrupt latency. These systems use a Memory Protection Unit (MPU) to protect the memory regions. These systems do not support a virtual memory system and MMU.

### Μ

The Microcontroller profile defines an architecture aimed at low cost systems, where low-latency interrupt processing is vital. It uses a different exception handling model to the other profiles and supports only a variant of the Thumb instruction set.

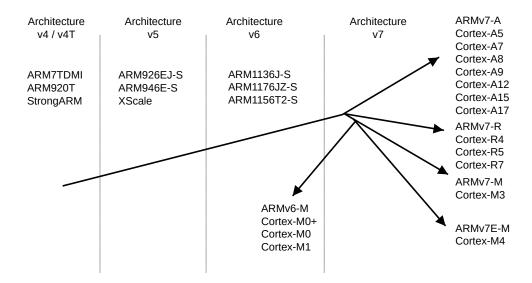

Figure 3-1: Architecture history on page 20 shows the development of the architecture over time, illustrating additions to the architecture at each new version. Almost all architecture changes are backwards compatible, meaning software written for the ARMv4T architecture can be used on ARMv7 processors.

Figure 3-1: Architecture history

| 4Т                                                                          | 5                                                                                                                             | 6                                                                                                                                                                                     | 7                                                                                                                                                                                            |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Halfword and signed halfword/byte support System mode Thumb instruction set | Improved ARM/Thumb Interworking  CLZ  Saturated arithmetic  DSP multiply-accumulate Instructions  Extensions: Jazelle (v5TEJ) | SIMD instructions  Multi-processing  TrustZone  v6 memory architecture  Unaligned data support  Extensions:  Thumb-2 (v6T2)  TrustZone (v6Z)  Multiprocessor (v6K)  Thumb only (v6-M) | Thumb-2 technology  NEON  Profiles:  v7-A (Applications)  NEON  LPAE  Virtualization  v7-R (Real-time)  Hardware divide  v7-M (Microcontroller)  Hardware divide  Thumb only  Floating-point |

### 3.1 Processor properties

For many years, ARM adopted a sequential numbering system for processors with ARM9 following ARM8, which came after ARM7. Various numbers and letters were appended to the base family to denote different variants. For example, the ARM7TDMI processor has T for Thumb, D for Debug, M for a fast multiplier and I for EmbeddedICE.

For the ARMv7 architecture, ARM adopted the brand name Cortex for its processors, with a supplementary letter indicating which of the three profiles, A, R, or M, the processor supports. Figure 3-2: Architecture and processors on page 21 shows how different versions of the architecture correspond to different processor implementations. The figure is not comprehensive and does not include all architecture versions or processor implementations.

Figure 3-2: Architecture and processors

This section briefly looks at some ARM processors and identifies which processor implements which architecture version. Cortex-R series processors takes a slightly more detailed look at some of the individual processors that implement architecture version ARMv7-R. The terminology in this chapter might be unfamiliar to the first-time user of ARM processors.

Table 3-1: Cortex processors and architecture versions on page 21 lists the architecture version implemented by the Cortex family of processors.

Table 3-1: Cortex processors and architecture versions

| v7-R (Real-time) | v7-A (Application)    | v6-M/v7-M (Microcontroller) |  |

|------------------|-----------------------|-----------------------------|--|

| Cortex-R4        | Cortex-A5 (Single/MP) | Cortex-M0+ (ARMv6-M)        |  |

| Cortex-R5        | Cortex-A7 (MP)        | Cortex-M0 (ARMv6-M)         |  |

| Cortex-R7        | Cortex-A8 (Single)    | Cortex-M1 (ARMv6-M)         |  |

|                  | Cortex-A9 (Single/MP) | Cortex-M3 (ARMv7-M)         |  |

|                  | Cortex-A12 (MP)       | Cortex-M4(F) (ARMv7E-M)     |  |

|                  | Cortex-A15 (MP)       |                             |  |

|                  | Cortex-A17 (MP)       |                             |  |

Table 3-2: Properties of Cortex-R series processors on page 21 compares the properties of Cortex-R series processors.

Table 3-2: Properties of Cortex-R series processors

| Property            | Cortex-R4        | Cortex-R5            | Cortex-R7      |

|---------------------|------------------|----------------------|----------------|

| Release date        | May 2006         | August 2010          | March 2012     |

| Typical clock speed | 600 MHz on 40 nm | 600 MHz on 40 nm     | 1 GHz on 28 nm |

| Execution order     | In-order         | In-order             | Out-of-order   |

| Cores               | 1                | 1 to 2 (in AMP mode) | 1 to 2         |

| Property                        | Cortex-R4                       | Cortex-R5                        | Cortex-R7                                        |

|---------------------------------|---------------------------------|----------------------------------|--------------------------------------------------|

| Peak integer throughput         | 2.45 DMIPS/MHz                  | 2.45 DMIPS/MHz                   | 2.50 DMIPS/MHz                                   |

| VFP architecture                | VFPv3                           | VFPv3                            | VFPv3                                            |

| Half precision extension        | No                              | No                               | Yes                                              |

| Hardware integer divide         | Yes                             | Yes                              | Yes                                              |

| Fused Multiply<br>Accumulate    | No                              | No                               | No                                               |

| Pipeline stages                 | 8                               | 8                                | 11                                               |

| Instruction decode per cycle    | Partial dual issue              | Partial dual issue               | 2 (Superscalar)                                  |

| Return stack entries            | 4                               | 4                                | 8                                                |

| Floating Point Unit             | Optional                        | Optional                         | Optional                                         |

| AMBA interface                  | 64-bit AXI 3                    | 64-bit AXI 3                     | 64-bit AXI 3                                     |

| Generic Interrupt<br>Controller | Not included                    | Not included                     | Included                                         |

| Branch predictor entries        | 256                             | 256                              | Configurable                                     |

| Indirect predictor              | No BTAC                         | No BTAC                          | 256, 512, 1024, 2048, or 4096 BTAC entries       |

| Trace                           | Optional ETM Separate macrocell | Optional ETM, Separate macrocell | Optional ETM                                     |

| Cache                           | I-Cache and D-Cache             | I-Cache and D-Cache              | I-Cache and D-Cache                              |

| Pipeline                        | 8 stage dual issue              | 8 stage dual issue               | 11 stage superscalar with Out-of-order execution |

### 3.2 Cortex-R series processors

This section takes a closer look at each of the processors that implement the ARMv7-R architecture. It gives only a general description in each case. For more specific information on each processor, see Table 3-2: Properties of Cortex-R series processors on page 21.

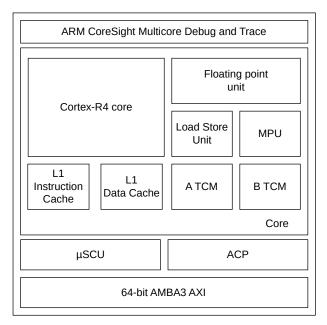

### 3.3 The Cortex-R4 processor

The ARM Cortex-R4 processor is designed for use in embedded, real-time systems. It implements the ARMv7-R architecture, and includes Thumb-2 technology for optimum code density and processing throughput, but can also use ARM instructions. It is for use in high-volume, deeply embedded System-on-Chip applications, for example, hard disk drive controllers, wireless baseband processors, consumer products and electronic control units for automotive systems.

Figure 3-3: Cortex-R4 core block diagram

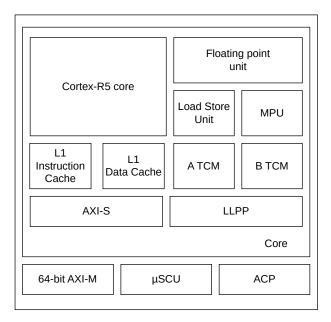

### 3.4 The Cortex-R5 processor

The Cortex-R5 processor is designed for use in embedded, real-time systems. It implements the ARMv7-R architecture, and includes Thumb-2 technology for optimum code density and processing throughput, but can also use ARM instructions. The pipeline has a single Arithmetic Logic Unit, but implements limited dual-issuing of instructions for efficient utilization of other resources such as the register file. A hardware Accelerator Coherency Port (ACP) is available to reduce the requirement for slow software cache maintenance operations when sharing memory with other masters.

Figure 3-4: Cortex-R5 core block diagram

### 3.5 The Cortex-R7 processor

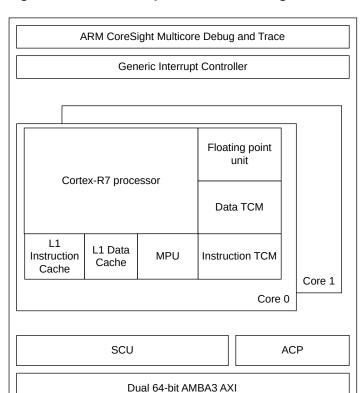

The ARM Cortex-R7 MPCore processor is a highly configurable processor for use in embedded real-time systems. It consists of one or two Cortex-R7 cores in a single cluster. It implements the ARMv7-R architecture, and includes Thumb-2 technology for optimum code density and processing throughput.

The Cortex-R7 processor provides higher levels of performance to the Cortex-R series of processors through the introduction of out-of-order instruction execution and dynamic register renaming, combined with improved branch prediction, superscalar execution capability and faster hardware support for divide, DSP and floating point functions.

Figure 3-5: Cortex-R7 processor block diagram

The Cortex-R7 processor has the following features:

- Flexible Multi-Processor Core (MPCore) configurations.

- Lock-step configuration with redundant core.

- Symmetric Multi-Processing (SMP).

- Asymmetric Multi-Processing (AMP).

- Integrated Generic Interrupt Controller (GIC), Snoop Control Unit (SCU), and timers.

- Quality of Service (QoS) features.

- Full coherency support for SMP.

- Hardware accelerated data cache operation with Tag RAM copies in SCU.

- Twin core and I/O coherency.

- Dedicated Low Latency Peripheral and Memory Ports for hard real-time work.

- Flexible and configurable Floating Point Unit (FPU).

- CoreSight SoC Debug and Trace.

- Optional Embedded Trace Macrocell ETMv4.

### 3.6 Development platforms

There are off-the-shelf ARM processor based platforms that are suitable for students and hobbyists:

#### MCBTMS570

The MCBTMS570 Development Kit is an Cortex-R4 based board set that can be used use to generate and test application programs for the Texas Instruments TMS570x microcontroller. The MCBTMS570 Board contains all the hardware components required in a single-chip TMS570x system.

The TMS570LS series is a high performance automotive grade microcontroller family that has been certified for use in IEC 61508 SIL3 safety systems and integrates the Cortex-R4F processor running at 1.6DMIPS/MHz, and has configurations that can run up to 160 MHz providing more than 250 DMIPS. The TMS570LS series also provides different Flash (1MB or 2MB) and data SRAM (128KB or 160KB) options with single bit error correction and double bit error detection.

The TMS570LS series is an ideal solution for high performance real time control applications with safety critical requirements.

#### Hercules

The Hercules safety microcontroller platform consists of two Cortex R4-based microcontroller families: TMS570 and RM4x. Designed specifically for IEC 61508 and ISO 26262 safety critical applications, the Hercules platform provides advanced integrated safety features while delivering scalable performance, connectivity, and memory options.

### 3.7 Operating systems for Cortex-R processors

Code running on Cortex-R processors might be running as bare-metal applications without an operating system, or use a Real-Time Operating System (RTOS). Real-time operating systems include:

- Integrity from Green Hills

- Nucleus from Mentor Graphics

- Extended T-Kernel from eSOL.

Many other operating systems are available. Cortex-R processors can also run suitably modified versions of Linux, configured to run without the use of a full MMU.

# 4. ARM Processor modes and Registers

The ARMv7-R architecture is a modal architecture. There are six privileged modes and a non-privileged user mode. Privilege, in this case, is the ability to perform certain tasks that cannot be done from User (unprivileged) mode. In User mode, there are limitations on operations that affect overall system configuration. For example, only privileged modes can change the operating mode. Modes are associated with exception events, described in Exceptions and Interrupts.

Table 4-1: ARM processor modes

| Mode             | Function                                                                                      | Privilege    |

|------------------|-----------------------------------------------------------------------------------------------|--------------|

| User (USR)       | Mode in which most programs and applications run                                              | Unprivileged |

| FIQ              | Entered on an FIQ interrupt exception                                                         | Privileged   |

| IRQ              | Entered on an IRQ interrupt exception                                                         | Privileged   |

| Supervisor (SVC) | Entered on reset or when a Supervisor Call instruction (SVC) is executed                      | Privileged   |

| Abort (ABT)      | Entered on a memory access exception                                                          | Privileged   |

| Undef (UND)      | Entered when an undefined instruction is executed                                             | Privileged   |

| System (SYS)     | Runs tasks that require a privileged processor mode, shares the register view with User mode. | Privileged   |

The introduction of the TrustZone Security Extensions in the ARMv6Z architecture created two security states (Secure and Non-secure) that are independent of Privilege and processor mode. The ARMv7-A architecture Virtualization Extensions also add a hypervisor mode (Hyp) in addition to the existing privileged modes. While the ARMv7-R architecture profile does not implement either the Security Extensions or Virtualization Extensions, their existence in the ARMv7 architecture has led to the redefinition of privileged (unprivileged or privileged) modes of operation in terms of Privilege levels.

Every memory access has an access privilege, that is either unprivileged or privileged.

The ARMv7-R architecture profile defines the following privilege levels:

#### PLO

The privilege level of application software, that executes in User mode. Therefore, software executed in User mode is described as unprivileged software. This software cannot access some features of the system. In particular, it cannot change many of the configuration settings.

Software executing at PLO makes only unprivileged memory accesses.

#### PL1

Software execution in all modes other than User mode is at PL1. Normally, operating system software executes at PL1.

The PL1 modes refers to all the modes other than User mode.

We can therefore redefine the processor modes in terms of privilege levels.

Table 4-2: ARM processor modes and privilege levels

| Mode             | Function                                                                                      | Privilege level |

|------------------|-----------------------------------------------------------------------------------------------|-----------------|

| User (USR)       | Mode in which most programs and applications run                                              | PLO             |

| FIQ              | Entered on an FIQ interrupt exception                                                         | PL1             |

| IRQ              | Entered on an IRQ interrupt exception                                                         | PL1             |

| Supervisor (SVC) | Entered on reset or when a Supervisor Call instruction (SVC) is executed                      | PL1             |

| Abort (ABT)      | Entered on a memory access exception                                                          | PL1             |

| Undef (UND)      | Entered when an undefined instruction is executed                                             | PL1             |

| System (SYS)     | Runs tasks that require a privileged processor mode, shares the register view with User mode. | PL1             |

The current processor mode and execution state is contained in the Current Program Status Register (CPSR). Changing processor state and modes can be either explicit by privileged software, or as a result of taking exceptions.

### 4.1 Registers

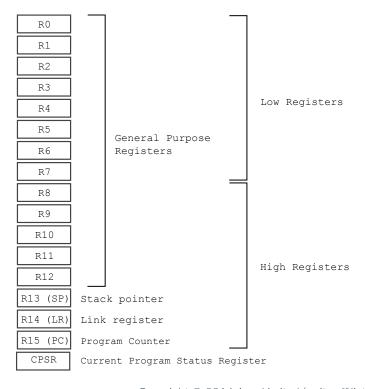

The ARMv7-R architecture provides sixteen 32-bit general purpose registers (R0-R15) for software use. Fifteen of them (R0-R14) can be used for general purpose data storage, while R15 is the program counter whose value is altered as the core executes instructions. An explicit write to R15 by software will alter program flow. Software can also access the CPSR and, in privileged modes a saved copy of the CPSR from the previously executed mode, called the Saved Program Status Register (SPSR).

Figure 4-1: Programmer visible registers for user code

Although software can access the registers, depending on the mode the software is executing in and the register being accessed, a register might correspond to a different physical storage location. This is called banking, the shaded registers in Figure 4-2: The ARMv7-R register set on page 29 are banked. They use physically distinct storage and are usually accessible only when a process is executing in that particular mode.

Figure 4-2: The ARMv7-R register set

| R0        | R0       | R0       | R0       | RO       | R0       | R0       |

|-----------|----------|----------|----------|----------|----------|----------|

| R1        | R1       | R1       | R1       | R1       | R1       | R1       |

| R2        | R2       | R2       | R2       | R2       | R2       | R2       |

| R3        | R3       | R3       | R3       | R3       | R3       | R3       |

| R4        | R4       | R4       | R4       | R4       | R4       | R4       |

| R5        | R5       | R5       | R5       | R5       | R5       | R5       |

| R6        | R6       | R6       | R6       | R6       | R6       | R6       |

| R7        | R7       | R7       | R7       | R7       | R7       | R7       |

| R8        | R8       | R8_fiq   | R8       | R8       | R8       | R8       |

| R9        | R9       | R9_fiq   | R9       | R9       | R9       | R9       |

| R10       | R10      | R10_fiq  | R10      | R10      | R10      | R10      |

| R11       | R11      | R11_fiq  | R11      | R11      | R11      | R11      |

| R12       | R12      | R12_fiq  | R12      | R12      | R12      | R12      |

| R13 (sp)  | R13 (sp) | SP_fiq   | SP_irq   | SP_abt   | SP_svc   | SP_und   |

| R14 (lr)  | R14 (lr) | LR_fiq   | LR_irq   | LR_abt   | LR_svc   | LR_und   |

| R15 (pc)  | R15 (pc) | R15 (pc) | R15 (pc) | R15 (pc) | R15 (pc) | R15 (pc) |

|           |          |          |          |          |          |          |

| (A/C) PSR | CPSR     | CPSR     | CPSR     | CPSR     | CPSR     | CPSR     |

|           |          | SPSR_fiq | SPSR_irq | SPSR_abt | SPSR_svc | SPSR_und |

| User      | Sys      | FIQ      | IRQ      | ABT      | SVC      | UND      |

| Banked    |          |          |          |          |          |          |

In all modes, 'Low Registers' and R15 share the same physical storage location. Figure 4-2: The ARMv7-R register set on page 29 shows that some 'High Registers' are banked for certain modes. For example, R8 to R12 are banked for FIQ mode, that is, accesses to them go to a different physical storage location. For all modes other than User and System modes, R13, R14 and the SPSRs are banked.

The stack pointer, R13, can be used as a general-purpose register only in ARM code but not in Thumb code.

In the case of banked registers, software does not normally specify the instance of the banked register. The instance of the banked register is implied by the mode from which the access is made. For example, a program executing in User mode that specifies R13 accesses R13\_usr. A program executing in SVC mode that specifies R13 accesses R13 svc.

R14 (the Link Register) holds the return address from a subroutine entered when you use the branch with link (BL) instruction. It can be used as a general purpose register when it is not supporting returns from subroutines. R14\_svc, R14\_irq, R14\_fiq, R14\_abt and R14\_und are used similarly to hold the return address when interrupts and exceptions arise, or when Branch and Link instructions are executed within interrupt or exception routines.

R15 is the program counter and holds the current program address (actually, it always points eight bytes ahead of the current instruction in ARM state and four bytes ahead of the current instruction in Thumb state, a legacy of the three stage pipeline of the original ARM1 processor). In ARM state, bits[1:0] of R15 always read as zero. In Thumb state, bit[0] of R15 always reads as zero.

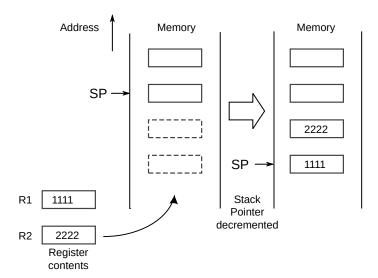

The reset values of RO-R14 are unpredictable. SP, the stack pointer, must be initialized, for each mode, by boot code before making use of the stack. The AAPCS or AEABI specifies how software should use the general purpose registers to interoperate between different toolchains or programming languages.

### 4.1.1 Program Status Registers

At any given moment, you have access to 16 registers (RO-R15) and the Current Program Status Register (CPSR). In User mode, a restricted form of the CPSR called the Application Program Status Register (APSR) is accessed instead.

The Current Program Status Register (CPSR) is used to store:

- The APSR flags.

- The current processor mode.

- Interrupt disable flags.

- The current processor state, that is, ARM, Thumb, ThumbEE, or Jazelle.

- The endianness.

- Execution state bits for the IT block.

The Program Status Registers (PSRs) form an additional set of banked registers. Each exception mode has its own Saved Program Status Register (SPSR) where a copy of the pre-exception CPSR is stored automatically when an exception occurs. These are not accessible from User mode.

Application programmers must use the APSR to access the parts of the CPSR that can be changed in unprivileged mode. The APSR must be used only to access the N, Z, C, V, Q, and GE[3:0] bits. These bits are not normally accessed directly, but instead set by condition code setting instructions and tested by instructions that are executed conditionally.

For example CMP RO, R1 compares the values of RO and R1 and sets the zero flag (Z) if RO and R1 are equal.

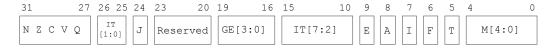

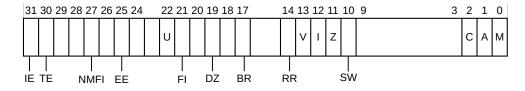

The CPSR contains condition code flags, the current mode bits, and other information as Figure 4-3: CPSR bits on page 31 shows.

### Figure 4-3: CPSR bits

The individual bits represent the following:

Ν

Negative result from ALU.

Ζ

Zero result from ALU.

C

ALU operation Carry out.

V

ALU operation oVerflowed.

Q

Cumulative saturation (also described as sticky bit).

J

Indicates whether the processor is in Jazelle state.

### GE[3:0]

Used by SIMD instructions.

### IT[7:0], bits [15:10, 26:25]

If-Then conditional execution of Thumb instruction groups.

Ε

Controls endianness for load and store operations.

Α

Value of 1 disables asynchronous aborts.

ı

Value of 1 disables IRQ.

F

Value of 1 disables FIQ.

Т

Indicates whether the processor is in Thumb state.

#### M[4:0]

Specifies the processor mode (see Table 4-2: ARM processor modes and privilege levels on page 28).

The processor can change between modes using instructions that directly write to the CPSR mode bits. More commonly, the processor changes mode automatically as a result of exception events. In User mode, you cannot manipulate bits [4:0] that control the processor mode or the A, I and F bits that govern the exceptions to be enabled or disabled.

### 4.1.2 Coprocessor 15

CP15, the System Control coprocessor, is (despite the name coprocessor) an integral part of the processor and provides control of many features. It can contain up to 16 primary registers, each of size 32 bits. However access to CP15 is privilege controlled and not all registers are available in User (unprivileged) mode.

The CP15 register access instructions specify the required primary register, with the other fields in the instruction used to define the access more precisely and increase the number of physical 32-bit registers in CP15. The 16 primary registers in CP15 are named c0 to c15, but are often referred to by a series of letters.

For example, the CP15 System Control Register is named CP15.SCTLR. Table 3.3 summarizes the function of some of the more relevant registers used in Cortex-R series processors. We will consider some of these in more detail when we look at the operation of the cache and MPU.

Table 4-3: CP15 Register summary

| Register                                          | Description                                                                                                                         |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Main ID Register<br>(MIDR)                        | Gives identification information for the processor, including implementer code and device ID.                                       |

| Multiprocessor<br>Affinity Register<br>(MPIDR)    | Provides a way to uniquely identify individual processors within a multi-processor system.                                          |

| CP15 c1 System<br>Control registers               |                                                                                                                                     |

| System Control<br>Register (SCTLR)                | The main processor control register, see System Control Register (SCTLR).                                                           |

| Auxiliary Control<br>Register (ACTLR)             | Implementation defined. Implementation specific additional control and configuration options.                                       |

| Coprocessor<br>Access Control<br>Register (CPACR) | Controls access to all coprocessors except CP14 and CP15.                                                                           |

| CP15 c5 and c6,<br>memory system<br>registers     |                                                                                                                                     |

| Data Fault Status<br>Register (DFSR)              | Gives status information about the last data fault (see Exceptions and Interrupts).                                                 |

| Instruction Fault<br>Status Register<br>(IFSR)    | Gives status information about the last instruction fault (see Exceptions and Interrupts).                                          |

| Data Fault Address<br>Register (DFAR)             | Gives the address of the access that caused the most recent precise data abort (see Exceptions and Interrupts).                     |

| Instruction Fault<br>Address Register<br>(IFAR)   | Gives the address of the access that caused the most recent precise prefetch abort (see Exceptions and Interrupts).                 |

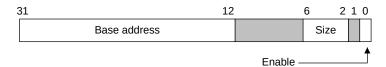

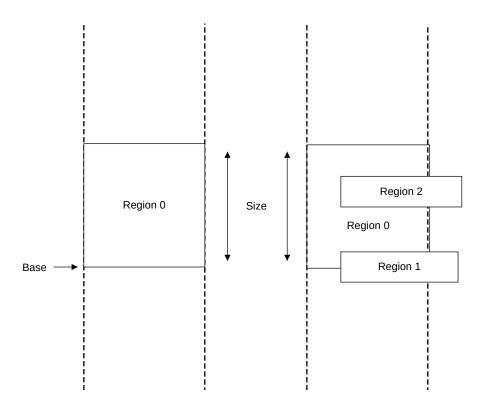

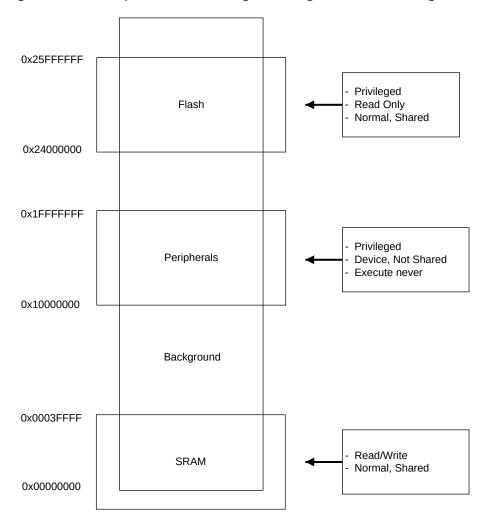

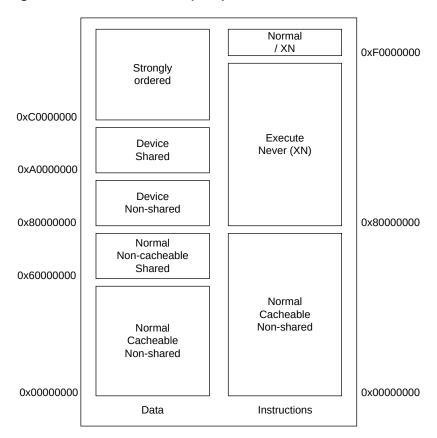

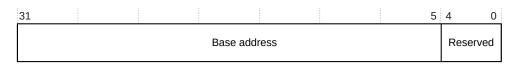

| MPU Region Base<br>Address Register               | Describes the base address of the region specified by the Memory Region Number Register. (See c6, MPU Region Base Address Register) |

| Register                                                  | <b>Description</b>                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

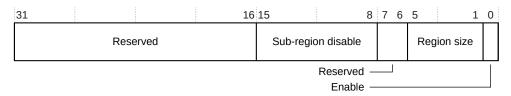

| MPU Region<br>Size and Enable<br>Register                 | Specifies the size of the region specified by the Memory Region Number Register.Identifies the address ranges that are used for a particular region.Enables or disables the region, and its sub-regions, specified by the Memory Region Number Register. (See c6, MPU Region Size and Enable Register) |

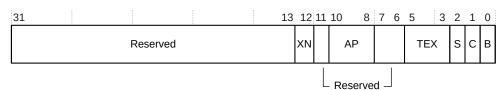

| MPU Region<br>Access Control<br>Register                  | Holds the region attributes and access permissions for the region specified by the Memory Region Number Register. (See c6, MPU Region Access Control Register)                                                                                                                                         |

| MPU Region<br>Number Register                             | Multiple registers with one register for each memory region implemented. The value contained determines which of the multiple registers is accessed.                                                                                                                                                   |

| CP15 c7, cache<br>maintenance and<br>other functions      |                                                                                                                                                                                                                                                                                                        |

| Cache and<br>branch predictor<br>maintenance<br>functions | See Caches.                                                                                                                                                                                                                                                                                            |

| Data and instruction barrier operations                   | See Memory Ordering.                                                                                                                                                                                                                                                                                   |

| CP15 c9,<br>performance<br>monitors                       |                                                                                                                                                                                                                                                                                                        |

| CP15 c13, process,<br>context and thread<br>ID registers  |                                                                                                                                                                                                                                                                                                        |

| Context ID<br>Register<br>(CONTEXTIDR)                    | Holds a process identification value for the running process. It is available in Privileged mode only.                                                                                                                                                                                                 |

| Software thread ID registers                              | Provide locations to store the IDs of software threads and processes of the operating system.                                                                                                                                                                                                          |

| CP15 c15,<br>implementation<br>defined registers          |                                                                                                                                                                                                                                                                                                        |

| Configuration Base<br>Address Register<br>(CBAR)          | Provides a base address for the GIC and Local timer type peripherals.                                                                                                                                                                                                                                  |

All system architecture functions are controlled by reading or writing a general purpose processor register (Rt) from or to a set of registers (CRn) located within Coprocessor 15. The Op1, Op2, and CRm fields of the instruction can also be used to select registers or operations. The format is as follows:

```

MRC p15, Op1, Rt, CRn, CRm, Op2 ; read a CP15 register into an ARM register

MCR p15, Op1, Rt, CRn, CRm, Op2 ; write a CP15 register from an ARM register

```

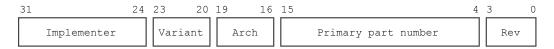

We will not go through each of the various CP15 registers in detail, as this would duplicate reference information that can readily be obtained from the ARM Architecture Reference Manual or product documentation. We will look at two examples, the read-only Main ID Register (MIDR), the format of which is shown in Figure 4-4: Main ID Register format on page 34 and the System Control Register (SCTLR).

### Figure 4-4: Main ID Register format

In a privileged mode, we can read this register, using the instruction:

The result, placed in register Rt, tells software the processor it is running on. For a Cortex-R series processor conforming to the ARMv7-R architecture the results will be as follows:

Bits [31:24] - implementer, is 0x41 for an ARM designed processor.

Bits [23:20] - variant, shows the revision number of the processor.

Bits [19:16] - architecture, is 0xF for ARM architecture v7.

Bits [15:4] - part number (for example 0xC15 for the Cortex-R5 processor).

Bits [3:0] - revision, shows the patch revision number of the processor.

### 4.1.3 System Control Register (SCTLR)

The System Control Register (SCTLR) can be accessed using CP15. It:

- Controls standard memory.

- Controls system facilities.

- Provides status information for functions implemented in the core.

The SCTLR is only accessible from PL1 (privileged mode).

Figure 4-5: Simplified view of the System Control Register

The individual bits represent the following:

ΙE

Instruction Endianness (not on Cortex-R7 processor). This controls the endianness of instructions issued to the processor:

• Value O for little-endian.

• Value 1 for Big-endian.

#### TE

Thumb exception enable. This controls whether exceptions are taken in ARM or Thumb state:

- Value 0 for ARM state

- Value 1 for Thumb state.

#### **NMFI**

Non-maskable FIQ (NMFI) support.

#### EE

Exception endianness. This defines the value of the CPSR.E bit on entry to an exception:

- Value 0 for Little-endian

- Value 1 for Big-endian.

U

Not on Cortex-R7 processor. Indicates use of the alignment model.

FI

Fast interrupts configuration enable.

- Value 0 to enable all performance features.

- Value 1 to enable low interrupt latency. Disables some features.

#### DΖ

Divide by zero fault bit.

- Value 0. Divide by zero returns zero, and no exception is taken.

- Value 1. Divide by zero cause as Undefined Instruction exception.

#### BR

Background region bit. See Implementing a Protected Memory System with Regions.

- Value 0. Any access to an address that is not mapped to an MPU region generates a Background fault memory abort.

- Value 1. The default memory map is used as a background region.

#### RR

Not on Cortex-R7 processor. Round Robin bit for cache implementation policy.

- Value 0. Normal replacement strategy, for example, random replacement.

- Value 1. Predictable strategy, for example, round-robin replacement.

V

This bit selects the base address of the exception vector table.

- Value 0 for low exception vectors, base address 0x00000000.

- Value 1 for high exception vectors, base address 0xFFFF0000.

Τ

Instruction cache enable bit.

- Value 0 to disable instruction caches.

- Value 1 to enable instruction caches.

Z

Branch prediction enable bit.

- Value 0 to disable branch prediction.

- Value 1 to enable branch prediction.

#### SW

SWP/SWPB enable bit.

- Value 0 to disable branch prediction.

- Value 1 to enable branch prediction.

ARM recommends that an ARMv7-R implementation does not include support for these instructions. When use of this bit is supported, at reset, this bit disables swp and swpb. This means that operating systems have to choose to use swp and swpb.

C

Cache enable bit.

- Value 0 to disable data and unified caches.

- Value 1 to enable data and unified caches.

Α

Alignment check enable bit.

- Value 0 to disable alignment fault checking.

- Value 1 to enable alignment fault checking.

М

Enable the MPU. See Implementing a Protected Memory System with Regions.

- Value 0 disables MPU.

- Value 1 enables MPU.

Part of the boot code sequence will typically set the Z bit in the CP15:SCTLR, System Control Register, that enables branch prediction. A code sequence to do this is shown below:

```

MRC p15, 0, r0, c1, c0, 0 ; Read System Control Register configuration data ORR r0, r0, \#(1 << 2) ; Set C bit ORR r0, r0, \#(1 << 12) ; Set I bit ORR r0, r0, \#(1 << 11) ; Set Z bit MCR p15, 0, r0, c1, c0, 0 ; Write System Control Register configuration data

```

A similar form of this code can be found in the example in Boot Code.

Data endianness is controlled by the CPSR.E and SCTLR.EE bits. The CPSR.E bit can be changed using the SETEND instruction. It also provides instructions for converting the format of data held in registers. These include the REV and REV16 instructions.

# 5. Introduction to Assembly Language

Assembly language is a low-level programming language. There is in general a one-to-one relationship between assembly language instructions (mnemonics) and the actual binary opcode executed by the processor.

Many programmers writing at the application level have little need to code in assembly language. However, knowledge of assembly code can be useful in cases where highly optimized code is required, when writing compilers, or where low level use of features not directly available in C is required. It might be required for portions of boot code, device drivers or when performing OS development. Finally, it can be useful to be able to read assembly code when debugging C, and particularly, to understand the mapping between assembly instructions and C statements.

Programmers seeking a more detailed description of ARM assembly language can also refer to the ARM Compiler Toolchain Assembler Reference or the ARM Architecture Reference Manual.

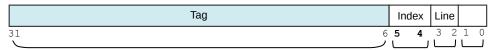

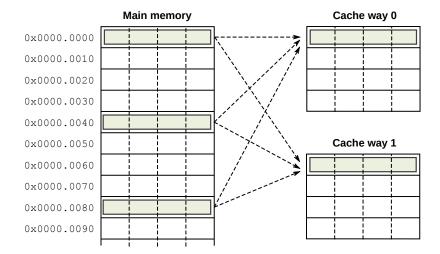

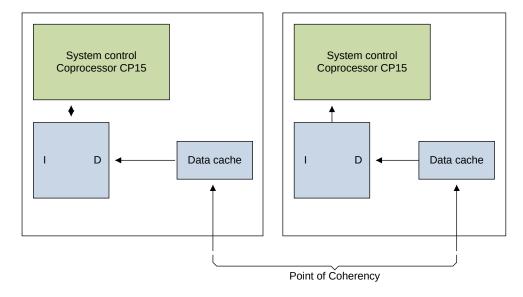

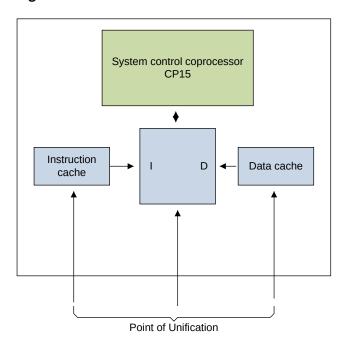

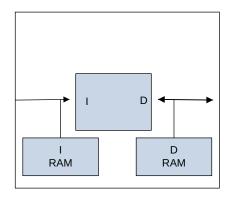

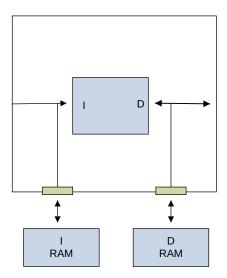

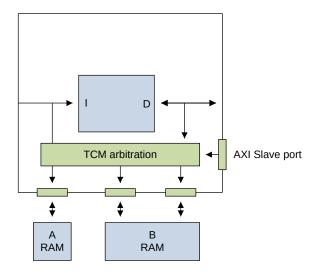

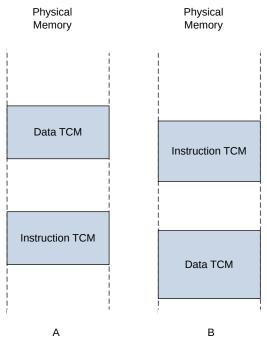

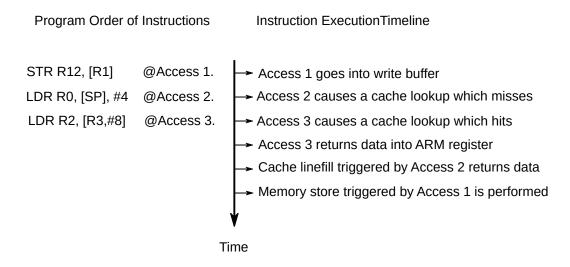

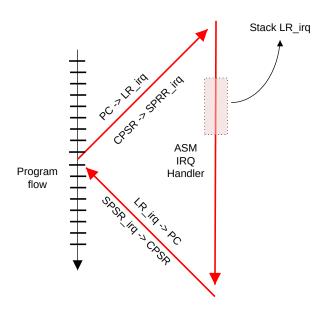

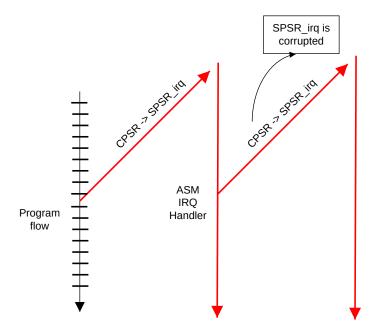

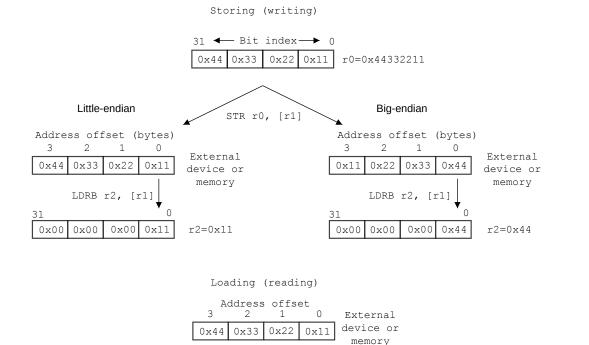

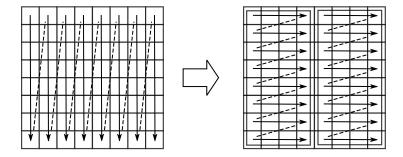

## 5.1 Comparison with other assembly languages