# **SMC Calling Convention**

Document number DEN0028

Document quality BET0

Document version 1.6 G

Document confidentiality Non-confidential

Copyright © 2013-2025 Arm Limited or its affiliates. All rights reserved.

### **Notice**

This document is a Beta version of a specification undergoing review by Arm partners. It is provided to give advanced information only.

# **SMC Calling Convention**

### **Release information**

| Date        | Version    | Changes                                                                                                            |

|-------------|------------|--------------------------------------------------------------------------------------------------------------------|

| 2025/Jan/28 | 1.6 G BET0 | Add SoC name to SMCCC_ARCH_SOC_ID                                                                                  |

|             |            | <ul> <li>Add SMCCC_ARCH_WORKAROUND_4</li> </ul>                                                                    |

|             |            | <ul> <li>Allocated FIDs for the RHI in the Standard Hypervisor range</li> </ul>                                    |

|             |            | Update CCA FID reservation                                                                                         |

|             |            | <ul> <li>Clarify that SMC32/HVC32 and SMC64/HVC64 function definitions can only differ</li> </ul>                  |

|             |            | in the range of the integer arg/returns.                                                                           |

| 2024/Apr/01 | 1.5 F      | <ul> <li>Add Vendor Specific EL3 Monitor Service range.</li> </ul>                                                 |

|             |            | <ul> <li>Clarify that SMC/HVC callers from any Security state are supported.</li> </ul>                            |

|             |            | <ul> <li>Clarify that the RMM restricts the services exposed to Realms.</li> </ul>                                 |

|             |            | <ul> <li>Rename "Secure Monitor" as "EL3 Monitor".</li> </ul>                                                      |

|             |            | <ul> <li>Minor text clarifications.</li> </ul>                                                                     |

|             |            | <ul> <li>Clarify that the term hypervisor refers to Non-secure EL2 Software.</li> </ul>                            |

|             |            | <ul> <li>Add the SMCCC_ARCH_FEATURE_AVAILABILITY interface.</li> </ul>                                             |

| 2022/May/01 | E          | <ul> <li>Add SME state management guidelines.</li> </ul>                                                           |

|             |            | • Update Standard Secure Service call list.                                                                        |

|             |            | <ul> <li>Add Standard Hypervisor Service call list.</li> </ul>                                                     |

|             |            | <ul> <li>Add SMCCC_ARCH_WORKAROUND_3 definition.</li> </ul>                                                        |

| 2024/7 /04  |            | Add SMCCC deployment model description.                                                                            |

| 2021/Jan/01 | D          | • Add SVE absence of live state hint bit (FID[16]).                                                                |

| 2020/Aug/01 | C          | <ul> <li>Minor text clarifications.</li> <li>Merge information contained in DEN 0070 (see @ARMDEN0070).</li> </ul> |

|             | _          | Add guidelines for SVE register context management and SoC ID Arm architecture                                     |

|             |            | call.                                                                                                              |

|             |            | <ul> <li>Allow R4—R7 (SMC32/HVC32) to be used as result registers.</li> </ul>                                      |

|             |            | • Allow X8—X17 to be used as parameter registers in SMC64/HVC64.                                                   |

|             |            | • Allow X4—X17 to be used as result registers in SMC64/HVC64.                                                      |

| 2016/Nov/01 | В          | • HVC calling convention.                                                                                          |

|             |            | SMC calling convention clarifications and updates.                                                                 |

| 2013/Jun/01 | A          | • First release                                                                                                    |

### **Arm Non-Confidential Document License ("License")**

This License is a legal agreement between you and Arm Limited ("Arm") for the use of Arm's intellectual property (including, without limitation, any copyright) embodied in the document accompanying this License ("Document"). Arm licenses its intellectual property in the Document to you on condition that you agree to the terms of this License. By using or copying the Document you indicate that you agree to be bound by the terms of this License.

"Subsidiary" means any company the majority of whose voting shares is now or hereafter owner or controlled, directly or indirectly, by you. A company shall be a Subsidiary only for the period during which such control exists.

This Document is **NON-CONFIDENTIAL** and any use by you and your Subsidiaries ("Licensee") is subject to the terms of this License between you and Arm.

Subject to the terms and conditions of this License, Arm hereby grants to Licensee under the intellectual property in the Document owned or controlled by Arm, a non-exclusive, non-transferable, non-sub-licensable, royalty-free, worldwide License to:

- (i) use and copy the Document for the purpose of designing and having designed products that comply with the Document;

- (ii) manufacture and have manufactured products which have been created under the License granted in (i) above; and

- (iii) sell, supply and distribute products which have been created under the License granted in (i) above.

# Licensee hereby agrees that the Licenses granted above shall not extend to any portion or function of a product that is not itself compliant with part of the Document.

Except as expressly licensed above, Licensee acquires no right, title or interest in any Arm technology or any intellectual property embodied therein.

The content of this document is informational only. Any solutions presented herein are subject to changing conditions, information, scope, and data. This document was produced using reasonable efforts based on information available as of the date of issue of this document. The scope of information in this document may exceed that which Arm is required to provide, and such additional information is merely intended to further assist the recipient and does not represent Arm's view of the scope of its obligations. You acknowledge and agree that you possess the necessary expertise in system security and functional safety and that you shall be solely responsible for compliance with all legal, regulatory, safety and security related requirements concerning your products, notwithstanding any information or support that may be provided by Arm herein. In addition, you are responsible for any applications which are used in conjunction with any Arm technology described in this document, and to minimize risks, adequate design and operating safeguards should be provided for by you.

Reference by Arm to any third party's products or services within this document is not an express or implied approval or endorsement of the use thereof.

THE DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. Arm may make changes to the Document at any time and without notice. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

NOTWITHSTANDING ANYTHING TO THE CONTRARY CONTAINED IN THIS LICENSE, TO THE FULLEST EXTENT PERMITTED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, IN CONTRACT, TORT OR OTHERWISE, IN CONNECTION WITH THE SUBJECT MATTER OF THIS LICENSE (INCLUDING WITHOUT LIMITATION) (I) LICENSEE'S USE OF THE DOCUMENT; AND (II) THE IMPLEMENTATION OF THE DOCUMENT IN ANY PRODUCT CREATED BY LICENSEE UNDER THIS LICENSE). THE EXISTENCE OF MORE THAN ONE CLAIM OR SUIT WILL NOT ENLARGE OR EXTEND THE LIMIT. LICENSEE RELEASES ARM FROM ALL OBLIGATIONS, LIABILITY, CLAIMS OR DEMANDS IN EXCESS OF THIS LIMITATION.

This License shall remain in force until terminated by Licensee or by Arm. Without prejudice to any of its other rights, if Licensee is in breach of any of the terms and conditions of this License then Arm may terminate this License immediately upon giving written notice to Licensee. Licensee may terminate this License at any time. Upon termination of this License by Licensee or by Arm, Licensee shall stop using the Document and destroy all copies of the Document in its possession. Upon termination of this License, all terms shall survive except for the License grants.

Any breach of this License by a Subsidiary shall entitle Arm to terminate this License as if you were the party in breach. Any termination of this License shall be effective in respect of all Subsidiaries. Any rights granted to any Subsidiary hereunder shall automatically terminate upon such Subsidiary ceasing to be a Subsidiary.

The Document consists solely of commercial items. Licensee shall be responsible for ensuring that any use, duplication or disclosure of the Document complies fully with any relevant export laws and regulations to assure that the Document or any portion thereof is not exported, directly or indirectly, in violation of such export laws.

This License may be translated into other languages for convenience, and Licensee agrees that if there is any conflict between the English version of this License and any translation, the terms of the English version of this License shall prevail.

The Arm corporate logo and words marked with ® or TM are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. No license, express, implied or otherwise, is granted to Licensee under this License, to use the Arm trade marks in connection with the Document or any products based thereon. Visit Arm's website at http://www.arm.com/company/policies/trademarks for more information about Arm's trademarks.

The validity, construction and performance of this License shall be governed by English Law.

Copyright © 2013-2025 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

Arm document reference: PRE-21585

version 5.0, March 2024

### **Contents**

# **SMC Calling Convention**

|           | <b>U</b>                                                                                   | ii |

|-----------|--------------------------------------------------------------------------------------------|----|

|           |                                                                                            | ii |

|           | Arm Non-Confidential Document License ("License") ii                                       |    |

|           | Conventions                                                                                |    |

|           | Typographical conventions                                                                  |    |

|           | Numbers                                                                                    |    |

|           | Pseudocode descriptions                                                                    |    |

|           | References                                                                                 |    |

|           | Feedback                                                                                   |    |

|           | Feedback on this book                                                                      |    |

|           | Inclusive terminology commitment                                                           |    |

| Chapter 1 | Introduction 12                                                                            | 2  |

| Chapter 2 | SMC and HVC calling conventions                                                            | 3  |

| •         | 2.1 Secure Monitor Calls                                                                   | 3  |

|           | <b>2.2</b> Hypervisor Calls                                                                | 3  |

|           | 2.3 Fast Calls and Yielding Calls                                                          | 3  |

|           | 2.4 32-bit and 64-bit conventions                                                          |    |

|           | 2.5 Function Identifiers                                                                   |    |

|           | <b>2.5.1</b> Fast Calls                                                                    |    |

|           | 2.5.2 Yielding Calls                                                                       |    |

|           | <b>2.5.3</b> Conduits                                                                      |    |

|           | <b>2.6</b> SMC32/HVC32 argument passing                                                    |    |

|           | <b>2.7</b> SMC64/HVC64 argument passing                                                    |    |

|           | 2.8 Equivalence of SMC32/HVC32 and SMC64/HVC64 function definitions 16                     |    |

|           | 2.9 SME, SVE, SIMD and floating-point registers                                            |    |

|           | 2.10 SMC and HVC immediate value                                                           |    |

|           | 2.11         Client ID (optional)         17           2.11.1         SMC calls         17 |    |

|           |                                                                                            |    |

|           | <b>2.11.2</b> HVC calls                                                                    |    |

|           | 2.13 Session ID (optional)                                                                 |    |

|           |                                                                                            | ر  |

| Chapter 3 | AArch64 SMC and HVC calling conventions                                                    |    |

|           | 3.1 Register use in AArch64 SMC and HVC calls                                              | 9  |

| Chapter 4 | AARCH32 SMC AND HVC CALLING CONVENTION 27                                                  |    |

|           | 4.1 Register use in AArch32 SMC and HVC calls                                              | 1  |

| Chapter 5 | SMC and HVC results                                                                        |    |

|           | <b>5.1</b> Error codes                                                                     |    |

|           | 5.2 Unknown Function Identifier                                                            |    |

|           | 5.3 Unique Identification format                                                           |    |

|           | 5.4 Revision information format                                                            | 3  |

| Chapter 6 | Function Identifier Ranges 24                                                              |    |

|           | <b>6.1</b> Allocation of values                                                            | 2  |

#### Contents

|           | 6.2 |                | eral service queries                      |    |

|-----------|-----|----------------|-------------------------------------------|----|

|           | 6.3 |                | emented Standard Secure Service Calls     |    |

|           | 6.4 | Impl           | emented Standard Hypervisor Service Calls | 27 |

| Chapter 7 | Arm | Archite        | ecture Calls                              | 28 |

| •         | 7.1 |                | ırn codes                                 | 28 |

|           | 7.2 |                | CCC VERSION                               | 28 |

|           |     | 7.2.1          | Usage                                     | 28 |

|           |     | 7.2.2          | Discovery                                 | 28 |

|           |     | 7.2.3          | Caller responsibilities                   | 29 |

|           |     | 7.2.4          | Implementation responsibilities           | 29 |

|           | 7.3 |                | CCC_ARCH_FEATURES                         | 29 |

|           | 7.3 | 7.3.1          |                                           | 29 |

|           |     | 7.3.1<br>7.3.2 | Usage                                     | 29 |

|           |     | 7.3.2<br>7.3.3 | Discovery                                 | 29 |

|           |     |                | Parameters                                |    |

|           |     | 7.3.4          | Return                                    | 29 |

|           |     | 7.3.5          | Caller responsibilities                   | 30 |

|           |     | 7.3.6          | Implementation responsibilities           | 30 |

|           | 7.4 |                | CCC_ARCH_SOC_ID                           | 30 |

|           |     | 7.4.1          | Usage                                     | 31 |

|           |     | 7.4.2          | Discovery                                 | 31 |

|           |     | 7.4.3          | Parameters                                | 31 |

|           |     | 7.4.4          | Return                                    | 32 |

|           |     | 7.4.5          | Caller responsibilities                   | 32 |

|           |     | 7.4.6          | Implementation responsibilities           | 32 |

|           | 7.5 | SMC            | CCC_ARCH_WORKAROUND_1                     | 32 |

|           |     | 7.5.1          | Usage                                     | 32 |

|           |     | 7.5.2          | Discovery                                 | 32 |

|           |     | 7.5.3          | Caller responsibilities                   | 33 |

|           |     | 7.5.4          | Implementation responsibilities           | 33 |

|           | 7.6 | SMC            | CCC ARCH WORKAROUND 2                     | 33 |

|           |     | 7.6.1          | Usage                                     | 34 |

|           |     | 7.6.2          | Discovery                                 | 34 |

|           |     | 7.6.3          | Caller responsibilities                   | 34 |

|           |     | 7.6.4          | Implementation responsibilities           | 34 |

|           | 7.7 |                | CCC ARCH WORKAROUND 3                     | 35 |

|           |     | 7.7.1          | Usage                                     | 35 |

|           |     | 7.7.2          | Discovery                                 | 35 |

|           |     | 7.7.3          | Caller responsibilities                   | 35 |

|           |     | 7.7.4          | Implementation responsibilities           | 35 |

|           | 7.8 |                | CCC_ARCH_FEATURE_AVAILABILITY             | 36 |

|           | 7.0 | 7.8.1          | Usage                                     | 37 |

|           |     | 7.8.2          | Discovery                                 | 37 |

|           |     | 7.8.3          | •                                         | 37 |

|           |     |                | Caller responsibilities                   |    |

|           | 7.0 | 7.8.4          | Implementation responsibilities           | 39 |

|           | 7.9 |                | CCC_ARCH_WORKAROUND_4                     | 39 |

|           |     | 7.9.1          | Usage                                     | 39 |

|           |     | 7.9.2          | Discovery                                 | 39 |

|           |     | 7.9.3          | Caller responsibilities                   | 39 |

|           |     | 7.9.4          | Implementation responsibilities           | 39 |

| Conventions |                                                                           |             |

|-------------|---------------------------------------------------------------------------|-------------|

| Appendix A  | Example implementation of Yielding Service calls                          | 41          |

| Appendix B  | Discovery of Arm Architecture Service functions                           | 42          |

| Appendix C  | SME, SVE, SIMD and FP live state preservation by the SMCCC implementation | ı <b>43</b> |

| Chapter 1   | SVE state                                                                 | 43          |

| Chapter 2   | SME state 2.1 Streaming SVE processor state                               | <b>43</b>   |

| Chapter 3   | Register list to be preserved                                             | 44          |

| Appendix D  | SMCCC deployment model                                                    | 46          |

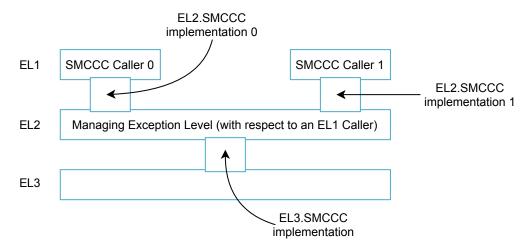

| Chapter 1   | SMCCC implementations and security states                                 | 46          |

| Appendix E  | Feature Discovery bitmask                                                 | 47          |

| Appendix F  | Changelog                                                                 | 51          |

| Conventio   | ns                                                                        |             |

| Typographic | al conventions                                                            |             |

| Th          | e typographical conventions are:                                          |             |

| ita         | lic                                                                       |             |

|             | Introduces special terminology, and denotes citations.                    |             |

#### bold

Denotes signal names, and is used for terms in descriptive lists, where appropriate.

monospace

Used for assembler syntax descriptions, pseudocode, and source code examples.

Also used in the main text for instruction mnemonics and for references to other items appearing in assembler syntax descriptions, pseudocode, and source code examples.

#### SMALL CAPITALS

Used for some common terms such as IMPLEMENTATION DEFINED.

Used for a few terms that have specific technical meanings, and are included in the Glossary.

#### Red text

Indicates an open issue.

#### Blue text

Indicates a link. This can be

- A cross-reference to another location within the document

- A URL, for example http://developer.arm.com

#### **Numbers**

Numbers are normally written in decimal. Binary numbers are preceded by 0b, and hexadecimal numbers by 0x. In both cases, the prefix and the associated value are written in a monospace font, for example 0xFFFF0000. To improve readability, long numbers can be written with an underscore separator between every four characters, for example <code>0xFFFF\_0000\_0000\_0000</code>. Ignore any underscores when interpreting the value of a number.

#### **Pseudocode descriptions**

This book uses a form of pseudocode to provide precise descriptions of the specified functionality. This pseudocode is written in a monospace font. The pseudocode language is described in the Arm Architecture Reference Manual.

### **Assembler syntax descriptions**

This book contains numerous syntax descriptions for assembler instructions and for components of assembler instructions. These are shown in a monospace font.

#### References

This section lists publications by Arm and by third parties.

See Arm Developer (http://developer.arm.com) for access to Arm documentation.

- ARM DEN 0070 Firmware interfaces for mitigating cache speculation vulnerabilities. Arm.

- [2] ARM DDI 0487 Arm<sup>®</sup> Architecture Reference Manual, Armv8, for Armv8-A architecture profile. Arm.

- ARM DDI 0406 Arm® Architecture Reference Manual Armv7-A and Armv7-R edition. Arm. [3]

- [4] ARM DEN 0091 SVE impact on Secure firmware. Arm.

- [5] ARM IHI 0055 Procedure Call Standard for the Arm 64-bit Architecture. Arm.

- [6] RFC 4122 - A Universally Unique IDentifier (UUID) URN Namespace. See http://tools.ietf.org/html/rfc4

- [7] ARM DEN 0022 Power State Coordination Interface. Arm.

- [8] Arm Security Update. See https://developer.arm.com/support/security-update

- [9] Cache Speculation Side-channels. See https://developer.arm.com/support/arm-security-updates/speculative -processor-vulnerability

- ARM DEN 0054 Software Delegated Exception Interface (SDEI). Arm. [10]

- [11] ARM DEN 0044 Arm® Base Boot Requirements. Arm.

- ARM DEN 0137 Realm Management Monitor specification. Arm.

#### **Feedback**

Arm welcomes feedback on its documentation.

#### Feedback on this book

If you have any comments or suggestions for additions and improvements create a ticket at https://support.develo per.arm.com. As part of the ticket include:

#### Contents

Inclusive terminology commitment

- The title (SMC Calling Convention).

- The number (DEN0028 1.6 G).

- The page numbers to which your comments apply.

- The rule identifiers to which your comments apply, if applicable.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

#### Note

Arm tests PDFs only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the appearance or behavior of any document when viewed with any other PDF reader.

### Inclusive terminology commitment

Arm values inclusive communities.

Arm recognizes that we and our industry have used terms that can be offensive. Arm strives to lead the industry and create change.

We believe that this document contains no offensive terms. If you find offensive terms in this document, please contact terms@arm.com.

### Terms and abbreviations

- **AArch32 state** The Arm 32-bit Execution state that uses 32-bit general purpose registers, and a 32-bit Program Counter (PC), Stack Pointer (SP), and Link Register (LR). AArch32 Execution state provides a choice of two instruction sets, A32 and T32, previously called the Arm and Thumb instruction sets.

- **AArch64 state** The Arm 64-bit Execution state that uses 64-bit general purpose registers, and a 64-bit program counter (PC), stack pointer (SP), and exception link registers (ELR). AArch64 Execution state provides a single instruction set, A64.

- **ACPI** The Advanced Configuration and Power Interface specification. This defines a standard for device configuration and power management by an OS.

- **CPU** A hardware implementation of the Arm Architecture.

- **EL1 Software** The software running at EL1 in a particular Security state. If the Security state implements EL2 [2], then there may be multiple EL1 Software instances managed by the EL2 Software in that Security state. Otherwise, the EL1 Software is managed by the EL3 Monitor.

- **EL2 Software** The software running at EL2 in a particular Security state. There is an EL2 Software instance for every implemented Security state that has an EL2 Exception level. The EL2 Software, in any Security state, is managed by the EL3 Monitor.

- **EL3 Monitor** The EL3 Monitor is software that executes at the EL3 Exception level. The EL3 Monitor receives and handles Secure Monitor exceptions, and provides transitions between distinct security states.

- **Execution context** The PE that is state associated with a thread of execution, including register state, exception level and security state. Usually an execution context is managed by another execution context at a higher exception level or an exception level in the Secure state. For example, firmware manages one or more system software execution contexts. However, the managing and managed execution contexts may reside at the same exception level and security state. For example, a runtime environment manages one or more interpreted applications.

- **Firmware** Software that provides platform specific services. Firmware typically operates at an exception level higher than the operating system or Hypervisor which makes use of the firmware services.

- **Function Identifier** A 32-bit integer that identifies which function is being invoked by an SMC or HVC call. Passed in R0 or W0 into every SMC or HVC call.

- HVC Hypervisor Call, an Arm assembler instruction that causes an exception that is taken synchronously into EL2.

- **Hypervisor** The hypervisor runs at the EL2 Exception level, in the Non-secure Security state, and supports the execution of multiple operating systems.

- **Non-secure state** The Arm Execution state that restricts access to only the Non-secure system resources, for example memory, peripherals, and System registers.

- **OEM** Original Equipment Manufacturer. In this document, the final device manufacturer.

- **OS** Application operating system, for example Linux or Windows. This also includes a virtualized OS running under a hypervisor.

**PE** Processing element. The abstract machine that is defined in the Arm architecture, see [2]

Rx Register; A32 native 32-bit register, A64 architectural register

**Secure state** The Arm Execution state that enables access to the Secure and Non-secure systems resources, for example memory, peripherals, and System registers.

**SiP** Silicon Partner. In this document, the silicon manufacturer.

**SMC** Secure Monitor Call. An Arm assembler instruction that causes an exception that is taken synchronously into EL3.

**SMCCC** SMC Calling Convention, this document.

**SMCCC Implementation** The firmware at a managing EL that handles the SMC or HVC calls, made from a SMCCC Caller, in a manner that is compliant with this document. A SMCCC implementation complies with a particular version of the SMCCC.

**Managing EL** The firmware in the more privileged EL that is immediate to the SMCCC Caller. Note that in the case of a type 2 Hypervisor, both the Hypervisor and its guest may be in the same EL. In that case, the term Managing EL, of these guests, refers to the type 2 Hypervisor.

**SMCCC Caller** The entity that invokes a SMC or HVC call.

SMC32/HVC32 32-bit SMC and HVC calling convention

SMC64/HVC64 64-bit SMC and HVC calling convention

SoC System on Chip

Wx A64 32-bit register view

Xx A64 64-bit register view

**Trusted OS** The Secure operating system that is running in the Secure EL1 Exception level. Trusted OS supports the execution of Trusted applications in Secure EL0.

**Unknown Function Identifier** A reserved return code defined by SMCCC that indicates that the function is not implemented. The Unknown Function Identifier is declared as NOT\_SUPPORTED in the interface specification and takes the value -1.

### 1 Introduction

This document defines a common calling mechanism to be used with the Secure Monitor Call (SMC) and Hypervisor Call (HVC) instructions in both the Armv7, Armv8, and Armv9 architectures.

The SMC instruction is used to generate a synchronous exception that is handled by the EL3 Monitor, or trapped and handled by EL2 Software. Arguments and return values are passed in registers. After being handled by the EL3 Monitor, calls that result from the instructions can be passed to a target software component that may reside in a Security state [2] distinct from the caller.

The HVC instruction is used to generate a synchronous exception that is handled by the EL2 Software.

Arguments and return values are passed in registers. EL2 Software can also trap SMC calls that are made by EL1 Software, which allows the calls to be emulated, passed through, or denied as appropriate.

#### Note

The HVC instruction is defined in [2], it can be issued by a caller in any Security state and is handled by the EL2 Software running in the same Security state as the caller. Throughout this document the term hypervisor refers to the Non-Secure EL2 Software.

This specification aims to ease integration and reduce fragmentation between software layers running at different Exception levels and Security states, for example operating systems, hypervisors, Trusted OSs, EL3 Monitors, and system firmware in general.

The calling mechanism defined in this document applies to callers in all Arm A-profile Security states [2] managed by EL3 (i.e. Non-secure, Secure, Realm).

#### Note

This document is defined for the Armv8-A and Armv9-A Exception levels, EL0 to EL3 [2]. The relationship between these Exception levels and the 32-bit Armv7 Exception levels is described in [2].

## 2 SMC and HVC calling conventions

#### 2.1 Secure Monitor Calls

In the Arm architecture, control is synchronously transferred between a caller in one Security state [2] and a callee, in a potentially distinct Security state, through Secure Monitor Call (SMC) exceptions [3][2]. SMC exceptions are generated by the SMC instruction [3][2], and are handled by the EL3 Monitor, or trapped and handled by EL2 Software. The operation of the callee is determined by the parameters that are passed in through registers.

### 2.2 Hypervisor Calls

Hypervisor Calls (HVCs) that are made by EL1 Software, in any Security state, result in a synchronous transfer of control to EL2 Software, and are regarded as HVC exceptions. The operation of the callee is determined by the parameters that are passed in through registers.

### 2.3 Fast Calls and Yielding Calls

Two types of calls are defined:

- Fast Calls execute atomic operations. The call appears to be atomic from the perspective of the calling PE, and returns when the requested operation has completed

- Yielding Calls start operations that can be pre-empted by a Non-secure interrupt. The call can return before the requested operation has completed. Appendix A provides an example of handling Yielding Calls.

#### 2.4 32-bit and 64-bit conventions

For the SMC and HVC, two calling conventions instructions are defined:

- SMC32/HVC32: A 32-bit interface that can be used by either a 32-bit or a 64-bit client code, and passes up to seven 32-bit arguments. Because only SMC32 and HVC32 calls are used for the identification of Function Identifier ranges, the 32-bit calling convention is mandatory for all compliant systems, whether they are 32-bit or 64-bit systems. For more information, see Section 6.2.

- SMC64/HVC64: A 64-bit interface that can be used only by 64-bit client code, and passes up to seventeen 64-bit arguments. SMC64/HVC64 calls are expected to be the 64-bit equivalent to the 32-bit call, where applicable.

#### 2.5 Function Identifiers

The **Function Identifier** is passed on W0 on every SMC and HVC call. Its 32-bit integer value indicates which function is being requested by the caller. It is always passed as the first argument to every SMC or HVC call in R0 or W0. The bit W0[31] determines if the call is Fast (W0[31]==1) or Yielding (W0[31]==0).

#### 2.5.1 Fast Calls

In the Fast Call case (W0[31]==1), the bits W0[30:0] determine:

- The service to be invoked

- The function to be invoked

- The calling convention (32-bit or 64-bit) that is in use

#### 2.5. Function Identifiers

Several bits within the 32-bit value have defined meanings valid for Fast Calls, as shown in Table 2-1.

Table 2-1: Bit usage within the SMC and HVC Function Identifier for Fast Call

| Bit<br>Numbers | Bit Mask   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                |                                          |  |

|----------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------|--|

| 31             | 0x80000000 | Always set to 1 for Fast Calls.                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                |                                          |  |

| 30             | 0x40000000 | If set to 0, the SMC32/HVC32 calling convention is used. If set to 1, the SMC64/HVC64 calling convention is used.                                                                                                                                                                                                                                                                                                                                        |                                                |                                          |  |

|                |            | Service Ca Owning Entity Number                                                                                                                                                                                                                                                                                                                                                                                                                          | ll ranges. For more information, see  Bit Mask | Section 6.  Description                  |  |

|                |            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x00000000                                     | Arm Architecture Calls                   |  |

|                |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0x01000000                                     | CPU Service Calls                        |  |

|                |            | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x02000000                                     | SiP Service Calls                        |  |

| 29:24          | 0x3F000000 | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x03000000                                     | OEM Service Calls                        |  |

|                |            | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x04000000                                     | Standard Secure Service Calls            |  |

|                |            | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x05000000                                     | Standard Hypervisor Service Calls        |  |

|                |            | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x06000000                                     | Vendor Specific Hypervisor Service Calls |  |

|                |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0x07000000                                     | Vendor Specific EL3 Monitor Calls        |  |

|                |            | 8-47                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0x08000000 - 0x2F000000                        | Reserved for future use                  |  |

|                |            | 48-49                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0x30000000 - 0x31000000                        | Trusted Application Calls                |  |

|                |            | 50-63                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0x32000000 - 0x3F000000                        | Trusted OS Calls                         |  |

| 23:17          | 0x00FE0000 | Must be zero (MBZ), for all Fast Calls, when bit[31] == 1. All other values are reserved for future use.  Note: Some Armv7 legacy Trusted OS Fast Call implementations have all bits set to 1.                                                                                                                                                                                                                                                           |                                                |                                          |  |

| 16             | 0x00010000 | From SMCCCv1.3: Hint bit denoting the absence of SVE specific live state. If set to 1, the caller asserts that the registers P0-P15, FFR and the bits with index greater than 127 in the Z0-Z31 registers do not contain any live state. This bit is not part of the function identification. The SMCCC implementation must disregard this bit and consider it to be 0 for the purpose of function identification.  Before SMCCCv1.3: Must be zero (MBZ) |                                                |                                          |  |

| 15:0           | 0x0000FFFF | Function n                                                                                                                                                                                                                                                                                                                                                                                                                                               | umber within the range call type that          | is defined by bits[29:24]                |  |

#### 2.6. SMC32/HVC32 argument passing

#### 2.5.2 Yielding Calls

In the Yielding Call case (W0[31]==0), Trusted OS Yielding Calls are placed in the 0x02000000-0x1FFFFFFF range. For more details on the Yielding Call Function ranges<sup>1</sup>, see Table 6-2.

#### 2.5.3 Conduits

The mechanism or instruction that is used to perform a call is referred to as the conduit. The conduit can be either an SMC or an HVC.

Table 2-2 describes which conduits are available, and how they depend on the Exception levels that are implemented.

Table 2-2: Dependence of conduits on implemented Exception levels

| EL3 Implemented | EL2 Implemented | Conduits | Notes                      |

|-----------------|-----------------|----------|----------------------------|

| Yes             | Yes             | SMC, HVC |                            |

| Yes             | No              | SMC      |                            |

| No              | Yes             | HVC      | Only permitted on Armv8-A. |

| No              | No              | N/A      | No conduit required        |

### 2.6 SMC32/HVC32 argument passing

When the SMC32/HVC32 convention is used, an SMC or HVC instruction takes a Function Identifier and up to seven 32-bit register values as arguments, and returns the status and up to seven 32-bit register values. When an SMC32/HVC32 call is made from AArch32:

- A Function Identifier is passed in register R0.

- Arguments are passed in registers R1-R7.

- Results are returned in R0-R7.

- The registers R4-R7 must be preserved unless they contain results, as specified in the function definition.

- Registers R8-R14 are saved by the function that is called, and must be preserved over the SMC or HVC call.

When an SMC32/HVC32 call is made from AArch64:

- A Function Identifier is passed in register W0.

- Arguments are passed in registers W1-W7.

- Results are returned in W0-W7.

- Registers W4-W7 must be preserved unless they contain results, as specified in the function definition.

- Registers X8-X30 and stack pointers SP\_EL0 and SP\_ELx are saved by the function that is called, and must be preserved over the SMC or HVC call.

#### Note

Unused result and scratch registers can leak information after an SMC or HVC call. An implementation can mitigate this risk by either preserving the register state over the call, or returning a constant value, such as zero, in each register.

#### Note

<sup>&</sup>lt;sup>1</sup>Arm recognizes that some TOS vendors use calls with FID in the 0x2000\_0000—0x7FFF\_FFFF range, calls in this range should not be blocked by FW unless strictly needed.

#### 2.7. SMC64/HVC64 argument passing

SMC32/HVC32 calls from AArch32 and AArch64 use the same physical registers for arguments and results, since register names W0-W7 in AArch64 map to register names R0-R7 in AArch32.

### 2.7 SMC64/HVC64 argument passing

When the SMC64/HVC64 convention is used, the SMC or HVC instruction takes a Function Identifier, up to seventeen 64-bit arguments in registers, and returns the status and up to seventeen 64-bit values in registers. When an SMC64/HVC64 call is made from AArch64:

- A Function Identifier is passed in register W0.

- Arguments are passed in registers X1-X17.

- Results are returned in X0-X17.

- Registers X4-X17 must be preserved unless they contain results, as specified in the function definition.

- Registers X18-X30 and stack pointers SP\_EL0 and SP\_ELx are saved by the function that is called, and must be preserved over the SMC or HVC call.

#### Note

The SMCCCv1.0 interface defines the return state of the X4—X17 registers to be unpredictable. If the SMCCC version is 1.0, a caller must accommodate an unpredictable return on X4—X17.

This calling convention cannot be used by code executing in AArch32 state.

Any SMC64/HVC64 call from AArch32 state receives the "Unknown Function Identifier" result, see Section 5.2.

#### Note

Unused result and scratch registers can leak information after an SMC or HVC call. An implementation can mitigate against this risk by either preserving the register state over the call, or returning a constant value, such as zero, in each register.

## 2.8 Equivalence of SMC32/HVC32 and SMC64/HVC64 function definitions

W0[30] in the **Function Identifier** specifies whether a call is SMC32/HVC32 or SMC64/HVC64 (see Table **2-1**). In the case where 2 **Function Identifiers** only differ in W0[30], Arm strongly recommends that the SMC32/HVC32 and SMC64/HVC64 definitions of the function are semantically equivalent."

These two definitions should:

- use the same set of registers for arguments and return values.

- have the same bit definitions for each argument and return value.

For example, a 32-bit bit-field argument located in W1[31:0] for the SMC32/HVC32 function definition, should also be a 32-bit bit-field in X1[31:0] for the SMC64/HVC64 function definition, and bits X1[63:32] should be 0.

The two definitions may differ in trivial ways, for example:

- a 32-bit integer argument/return in the SMC32/HVC32 definition may become a sign-extended 64-bit integer argument/return in the SMC64/HVC64 function definition.

- a 32-bit address argument/return in the SMC32/HVC32 definition may become a 64-bit address argument/return in the SMC64/HVC64 function definition.

### 2.9 SME, SVE, SIMD and floating-point registers

SME, SVE, SIMD, and floating-point registers must not be used to pass arguments to or receive results from any SMC or HVC call that complies with this specification.

If the calling context does not have live state in any SVE registers (P0-P15, FFR and the bits with index greater than 127 in Z0-Z31), the caller can set the FID[16] bit, see Table 2-1.

The SMCCC implementation must ensure that the live state, belonging to the calling context, on all SME (ZA array) [2], SVE (Z0-Z31, P0-P15, FFR) [2], Advanced SIMD and floating-point registers (V0-V31, FPCR, FPSR), is preserved over all SMC and HVC calls.

The live state to be preserved, by the SMCCC implementation, depends on the architectural implemented features (FEAT\_SVE, FEAT\_SWE2, FEAT\_SME, FEAT\_SME\_FA64) and caller provided input (PSTATE.SM, PSTATE.ZA, FID[16]). A detailed list of registers to be preserved is provided in Appendix C .

If SME is implemented and the calling context does not have live state in any SME registers (ZA[0]-ZA[31]), the caller should set PSTATE.ZA to 0 before invoking an SMC or HVC call.

Additionally, if FID[16] is 1, the SMCCC implementation must either preserve, or set to zero, the P0-P15 and FFR registers, and the bits with index greater than 127 in the Z0-Z31 registers if these are architecturally accessible from the context of the caller.

The SMCCC implementation is responsible for ensuring that information is not disclosed between execution contexts through SME, SVE, SIMD, and floating-point registers.

Arm recommends that the SMCCC implementation adopts a design pattern, for SVE state preservation, from the set of patterns that are described in [4].

### 2.10 SMC and HVC immediate value

The SMC and HVC instructions encode an immediate value, as defined by the Arm architecture [3][2]. The size of this immediate value, and mechanisms to access the value, differ between the Arm instruction sets. Also, it is time-consuming for 32-bit EL3 Monitor code to access this immediate value.

Therefore:

- For all compliant calls, an SMC or HVC immediate value of zero must be used.

- Nonzero immediate values in SMC instructions are reserved.

- Nonzero immediate values in HVC instructions are designated for use by hypervisor vendors.

## 2.11 Client ID (optional)

Provisions have been made for Secure software to track and index client IDs.

#### 2.11.1 SMC calls

If an implementation includes a hypervisor or similar supervisory software that executes at EL2, it might be necessary to identify the client operating system from which the SMC call originated.

- A 16-bit client ID parameter is optionally defined for SMC calls.

- In AArch32, the client ID is passed in the R7 register. For more information, see Table 4-1.

- In AArch64, the client ID is passed in the W7 register. For more information, see Table 3-1.

- The client ID of 0x0000 is designated for SMC calls from the hypervisor itself.

The client ID is expected to be created within the hypervisor and used to register, reference, and de-register client operating systems to a Trusted OS. It is not expected to correspond to the VMIDs used by the MMU.

If a client ID is implemented, all SMC calls that are generated by software executing at EL1 must be trapped by the hypervisor. Identification information must be inserted into R7 or W7 register before forwarding any SMC call

# 2. SMC and HVC calling conventions 2.12. Secure OS ID (optional)

on to the EL3 Monitor.

If no hypervisor is implemented, the Guest OS is not required to set the client ID value.

#### 2.11.2 HVC calls

The Client ID is ignored by the HVC calling convention.

### 2.12 Secure OS ID (optional)

In the presence of multiple Secure operating systems at S-EL1, the caller must specify the Secure OS for which the call is intended:

- An optional 16-bit Secure OS ID parameter can be defined for SMC calls.

- In AArch32, the Secure OS ID is passed in the R7 register. For more information, see Table 4-1.

- In AArch64 state, the Secure OS ID is passed in the W7 register. For more information, see Table 3-1.

### 2.13 Session ID (optional)

To support multiple sessions within a Trusted OS or hypervisor, it might be necessary to identify multiple instances of the same SMC or HVC call:

- An optional 32-bit Session ID can be defined for SMC and HVC calls.

- In AArch32, the Session ID is passed in the R6 register, see Table 4-1.

- In AArch64, the Session ID is passed in the W6 register, see Table 3-1.

The Session ID is expected to be provided by the Trusted OS or hypervisor, and is used by its clients in subsequent calls.

## 3 AArch64 SMC and HVC calling conventions

This specification defines common calling mechanisms for use with the SMC and HVC instructions from the AArch64 state. These calling mechanisms are referred to as SMC32/HVC32 and SMC64/HVC64. For Arm AArch64:

- All Trusted OS and EL3 Monitor implementations must conform to this specification.

- All hypervisors must implement the Standard Secure and Hypervisor Service calls.

### 3.1 Register use in AArch64 SMC and HVC calls

For the AArch64 calling conventions, usage of the architectural registers is defined in Table 3-1.

The working size of the register is identified by its name:

- Xn: All 64-bits are used.

- Wn: The least significant 32-bits are used, and the most significant 32-bits are zero. Implementations must ignore the most significant bits.

For more information, see [5]

<sup>&</sup>lt;sup>2</sup>An SMC call or HVC call can return results in this register. Otherwise the call must preserve the value in the register. Refer to the documentation for the defined behavior of each SMC or HVC call. **Note:** on SMCCCv1.0 compliant implementations these are scratch registers.

#### 3. AArch64 SMC and HVC calling conventions

### 3.1. Register use in AArch64 SMC and HVC calls

Table 3-1: Register Usage in AArch64 SMC32, HVC32, SMC64, and HVC64 calls

| Register Name |             | Role during SMC or HVC call                                                                                        |                                                      |                                 |

|---------------|-------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------|

| SMC32/HVC32   | SMC64/HVC64 | Calling values                                                                                                     | Modified                                             | Return state                    |

| SP_ELx        |             | ELx stack pointer                                                                                                  |                                                      |                                 |

| SP_EL0        |             | EL0 stack pointer                                                                                                  |                                                      |                                 |

| X30           |             | The Link Register                                                                                                  | No                                                   | Register values are preserved   |

| X29           |             | The Frame Pointer                                                                                                  |                                                      | register various are preserved. |

| X19X28        |             | Registers that are saved by the called function                                                                    |                                                      |                                 |

| X18           |             | The Platform Register                                                                                              |                                                      |                                 |

| X17           |             | Parameter register. The second intra-procedure-call scratch register.                                              |                                                      |                                 |

| X16           |             | Parameter register. The first intra-procedure-call scratch register.                                               |                                                      | Registers values are            |

| X9X15         |             | Parameter registers. Temporary registers.                                                                          | Dependent <sup>2</sup> preserved or contain results. |                                 |

| X8            |             | Parameter register. Indirect result location register.                                                             |                                                      |                                 |

| W7 X7 (or W7) |             | Parameter register. Optional Client ID in bits[15:0] (ignored for HVC calls). Optional Secure OS ID in bits[31:16] |                                                      |                                 |

| W6 X6 (or W6) |             | Parameter register. Optional Session ID register                                                                   |                                                      |                                 |

| W4W5 X4X5     |             | Parameter registers.                                                                                               | Parameter registers.                                 |                                 |

| W1W3          | X1X3        | Parameter registers.                                                                                               | Yes                                                  | SMC and HVC result              |

| W0 W0         |             | Function Identifier.                                                                                               | 103                                                  | registers.                      |

## 4 AARCH32 SMC AND HVC CALLING CONVENTION

This specification defines a common calling mechanism for use with the SMC and HVC instructions from the AArch32 state, which are referred to as SMC32/HVC32.

#### Note

Arm recognizes that some vendors already use a proprietary calling convention and are not able to meet all the following requirements.

### 4.1 Register use in AArch32 SMC and HVC calls

Table 4-1: Register usage in AArch32 SMC and HVC Calls

| Register Name | Name Role during SMC or HVC call                                                                                   |                                  |                                                        |  |

|---------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------------------|--|

| SMC32/HVC32   | Calling values                                                                                                     | Modified                         | Return state                                           |  |

| R15           | The Program Counter                                                                                                | Yes                              | Next instruction                                       |  |

| R14           | The Link Register                                                                                                  |                                  |                                                        |  |

| R13           | The stack pointer                                                                                                  | -                                |                                                        |  |

| R12           | The Intra-Procedure-call scratch register.                                                                         |                                  | Unchanged, registers are saved or restored.            |  |

| R11           | Variable-register 8                                                                                                | No                               |                                                        |  |

| R10           | Variable-register 7                                                                                                |                                  |                                                        |  |

| R9            | Platform Register                                                                                                  |                                  |                                                        |  |

| R8            | Variable-register 5                                                                                                |                                  |                                                        |  |

| R7            | Parameter register 7 Optional Client ID in bits[15:0] (ignored for HVC calls) Optional Secure OS ID in bits[31:16] | Dependent <sup>3</sup>           | Register values are preserved or contain call results. |  |

| R6            | Parameter register 6 Optional Session ID                                                                           |                                  | contain can results.                                   |  |

| R5            | Parameter register 5                                                                                               |                                  |                                                        |  |

| R4            | Parameter register 4                                                                                               |                                  |                                                        |  |

| R3            | Parameter register 3                                                                                               |                                  |                                                        |  |

| R2            | Parameter register 2                                                                                               | Yes                              | CMC and HWC manks are it to                            |  |

| R1            | Parameter register 1                                                                                               | Yes SMC and HVC results registed |                                                        |  |

| R0            | Function Identifier                                                                                                |                                  |                                                        |  |

<sup>&</sup>lt;sup>3</sup>An SMC call or HVC call can return results in this register. Otherwise the call must preserve the value in the register. Refer to the documentation for the defined behavior of each SMC or HVC call.

### 5 SMC and HVC results

#### 5.1 Error codes

Errors codes that are returned in R0, W0 and X0 are signed integers of the appropriate size:

- In AArch32:

- When using the SMC32/HVC32 calling convention, error codes, which are returned in R0, are 32-bit signed integers.

- In AArch64:

- When using the SMC64/HVC64 calling convention, error codes, which are returned in X0, are 64-bit signed integers.

- When using the SMC32/HVC32 calling convention, error codes, which are returned in W0, are 32-bit signed integers. X0[63:32] is UNDEFINED.

### 5.2 Unknown Function Identifier

The Unknown SMC Function Identifier is a sign-extended value of (-1) that is returned in the R0, W0 or X0 registers. An implementation must return this error code when it receives:

- An SMC or HVC call with an unknown Function Identifier

- An SMC or HVC call for a removed Function Identifier

- An SMC64/HVC64 call from AArch32 state

#### Note

The Unknown Function Identifier must not be used to discover the presence of an SMC or HVC function, or that lack of a function. Function Identifiers must be determined from the UID and Revision information. For the Arm Architecture Call range, Function Identifiers can be determined using  $SMCCC\_ARCH\_FEATURES$  as described in Section 7.3 and Appendix B .

## 5.3 Unique Identification format

This value identifies the implementer of a subrange (see Section 6.2) of the API, and therefore what controls the actions of SMCs in that subrange.

The Unique Identification UID is a UUID as defined by RFC 4122 [6]. These UUIDs must be generated by any method that is defined by RFC 4122 [6], and are 16-byte strings.

UIDs are returned as a single 128-bit value using the SMC32 calling convention. This value is mapped to argument registers as shown in Table 5-1.

UIDs with the least significant 32 bits set to 0xFFFFFFF must not be used, because they are indistinguishable from Unknown Function Identifiers.

#### 5.4. Revision information format

Table 5-1: UUID register mapping

| Register |         | Value                                         |  |

|----------|---------|-----------------------------------------------|--|

| AArch32  | AArch64 | value                                         |  |

| R0       | W0      | Bytes 03 with byte 0 in the low-order bits    |  |

| R1       | W1      | Bytes 47 with byte 4 in the low-order bits    |  |

| R2       | W2      | Bytes 811 with byte 8 in the low-order bits   |  |

| R3       | W3      | Bytes 1215 with byte 12 in the low-order bits |  |

There can be many implementers of standard APIs. The API compatibility is determined by revision numbers.

#### 5.4 Revision information format

The revision information for a subrange (see Section 6.2) is defined by a 32-bit major version and a 32-bit minor version.

Different major version values indicate a possible incompatibility between SMC and HVC APIs for the affected SMC and HVC range.

For two revisions, A and B, where the major version values are identical, and the minor version value of revision B is greater than the minor version value of revision A, every SMC and HVC instruction in the affected range that works in revision A must also work in revision B, with a compatible effect.

When returned by a call, the major version is returned in R0 or W0 and the minor version is returned in R1 or W1. Such an SMC or HVC instruction must use the SMC32 or HVC32 calling conventions.

The rules for interface updates are:

- A Function Identifier, when issued, must never be reused.

- Subsequent SMC or HVC calls must take a new unused Function Identifier.

- Calls to Function Identifiers that have been removed must return the Unknown Function Identifier value.

- Incompatible argument changes cannot be made to an existing SMC or HVC call. A new call is required.

- Major revision numbers must be incremented when:

- Any SMC or HVC call is removed.

- Minor revision numbers must be incremented when:

- Any SMC or HVC call is added.

- Backwards compatible changes are made to existing function arguments.

# **Function Identifier Ranges**

Arm defines the SMC and HVC Fast Call services that are listed in Table 6-1.

Table 6-1: SMC and HVC Services

| Service                                   | Owning<br>Entity<br>Number | Comment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arm<br>Architecture<br>Service            | 0                          | Provides interfaces to generic services for the Arm Architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CPU Service                               | 1                          | Provides interfaces to CPU implementation-specific services for this platform, for example access to errata workarounds.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SiP Service                               | 2                          | Provides interfaces to SoC implementation-specific services on this platform, for example Secure platform initialization, configuration, and some power control services.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OEM Service                               | 3                          | Provides interfaces to OEM-specific services on this platform.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Standard Secure<br>Service                | 4                          | Standard Service Calls for the management of the overall system. By standardizing such calls, the job of implementing operating systems on Arm is made easier. Section <b>6.3</b> lists Secure Services that are already defined.                                                                                                                                                                                                                                                                                                                                                              |

| Standard<br>Hypervisor<br>Service         | 5                          | Standardized Hypervisor Service Calls allow for common hypervisor discovery mechanism from any Guest OS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |