### **Armv8-M Security Extension**

Version 1.0

### **User Guide**

Non-Confidential

All rights reserved.

Copyright © 2025 Arm Limited (or its affiliates).

**Issue 01** 107655\_100\_01\_en

### Armv8-M Security Extension

#### User Guide

Copyright © 2025 Arm Limited (or its affiliates). All rights reserved.

#### **Release information**

#### Document history

| Issue   | Date            | Confidentiality  | Change        |

|---------|-----------------|------------------|---------------|

| 0100-01 | 22 January 2025 | Non-Confidential | First release |

### **Proprietary Notice**

This document is protected by copyright and other related rights and the use or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm Limited ("Arm"). No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether the subject matter of this document infringes any third party patents.

The content of this document is informational only. Any solutions presented herein are subject to changing conditions, information, scope, and data. This document was produced using reasonable efforts based on information available as of the date of issue of this document. The scope of information in this document may exceed that which Arm is required to provide, and such additional information is merely intended to further assist the recipient and does not represent Arm's view of the scope of its obligations. You acknowledge and agree that you possess the necessary expertise in system security and functional safety and that you shall be solely responsible for compliance with all legal, regulatory, safety and security related requirements concerning your products, notwithstanding any information or support that may be provided by Arm herein. In addition, you are responsible for any applications which are used in conjunction with any Arm technology described in this document, and to minimize risks, adequate design and operating safeguards should be provided for by you.

This document may include technical inaccuracies or typographical errors. THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, any patents, copyrights, trade secrets, trademarks, or other rights.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Reference by Arm to any third party's products or services within this document is not an express or implied approval or endorsement of the use thereof.

This document consists solely of commercial items. You shall be responsible for ensuring that any permitted use, duplication, or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of this document shall prevail.

The validity, construction and performance of this notice shall be governed by English Law.

The Arm corporate logo and words marked with ® or <sup>™</sup> are registered trademarks or trademarks of Arm Limited (or its affiliates) in the US and/or elsewhere. Please follow Arm's trademark usage guidelines at https://www.arm.com/company/policies/trademarks. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

PRE-1121-V1.0

### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

### **Product Status**

The information in this document is Final, that is for a developed product.

### Feedback

Arm welcomes feedback on this product and its documentation. To provide feedback on the product, create a ticket on https://support.developer.arm.com

To provide feedback on the document, fill the following survey: https://developer.arm.com/ documentation-feedback-survey.

### Inclusive language commitment

Arm values inclusive communities. Arm recognizes that we and our industry have used language that can be offensive. Arm strives to lead the industry and create change.

We believe that this document contains no offensive language. To report offensive language in this document, email terms@arm.com.

# Contents

| 1. Introducing Armv8-M Security Extension                                      | 9  |

|--------------------------------------------------------------------------------|----|

| 1.1 Security concept                                                           | 9  |

| 1.2 Privilege levels and security states                                       |    |

| 1.3 Real world examples                                                        | 12 |

| 1.3.1 Bluetooth device                                                         | 12 |

| 1.3.2 Firmware IP protection                                                   | 13 |

| 2. Registers                                                                   | 15 |

| 2.1 General-purpose registers                                                  | 15 |

| 2.2 Stack pointers                                                             | 16 |

| 2.3 Stack limit registers                                                      | 17 |

| 2.4 Special-purpose registers                                                  | 18 |

| 2.5 System control registers                                                   | 19 |

| 3. Memory configuration                                                        | 20 |

| 3.1 Memory security attributes                                                 | 20 |

| 3.2 SAUs                                                                       |    |

| 3.2.1 SAU                                                                      | 21 |

| 3.2.2 IDAU                                                                     | 21 |

| 3.2.3 Address lookup                                                           | 22 |

| 3.2.4 Configuring SAU using CMSIS                                              | 23 |

| 3.3 Memory configuration with the MPU in Secure state                          | 24 |

| 4. Function calls                                                              | 26 |

| 4.1 Transition between security states                                         | 26 |

| 4.2 Implementing function calls across the Security boundary for C development | 27 |

| 4.2.1 Non-Secure software calling a Secure API                                 |    |

| 4.2.2 Secure software calling a Non-Secure function                            |    |

| 4.3 The assembly instructions for Security states transition by function call  |    |

| 4.3.1 Function call from Non-Secure to Secure state                            |    |

| 4.3.2 Function return from Secure state                                        |    |

| 4.3.3 Function call from Secure to Non-Secure state                            |    |

| 4.3.4 Function return from Non-Secure state                                    | 34 |

| 4.4 Software considerations in function calls across security boundary |    |

|------------------------------------------------------------------------|----|

| 4.4.1 Pointer passing across Security boundary                         |    |

| 4.4.2 Non-pointer parameter passing                                    |    |

| 4.4.3 CMSE intrinsic functions                                         |    |

| 4.4.4 TT instruction                                                   |    |

| 4.5 Floating-point context consistency and FPCXT payload               |    |

| 5. Armv8-M exception model with Security Extension                     | 43 |

| 5.1 Prerequisites                                                      |    |

| 5.2 Target states of exceptions                                        |    |

| 5.3 Exception prioritization                                           |    |

| 5.4 Stack frames                                                       |    |

| 5.4.1 State context                                                    |    |

| 5.4.2 Additional state context                                         |    |

| 5.5 EXC_RETURN                                                         |    |

| 5.5.1 Scenario 1                                                       | 51 |

| 5.5.2 Scenario 2                                                       |    |

| 5.5.3 Scenario 3                                                       | 53 |

| 5.6 SecureFault                                                        | 53 |

| 5.7 External interrupts configuration and management                   |    |

| 5.8 SVC and PendSV                                                     |    |

| 5.9 SysTick timer                                                      |    |

| 5.10 MemManage faults                                                  |    |

| 5.10.1 Caution for Secure code developers                              |    |

| 6. Developing software with Security Extension                         | 60 |

| 6.1 Memory map partitioning                                            | 61 |

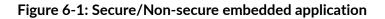

| 6.2 Add CMSIS startup and initialization code                          | 61 |

| 6.3 Write the linker script or scatter file                            |    |

| 6.4 Develop Secure software using Armv8-M Security Extensions          | 63 |

| 6.5 Build the Secure image                                             | 65 |

| 6.6 Build a Non-secure image that can call Secure APIs                 |    |

| 6.7 Launch Non-secure images from Secure side                          |    |

| 6.8 Preload and run the images on your device                          | 68 |

| 6.9 Build a Secure image using a previously generated import library   |    |

| 7. Booting and initializations                                         | 70 |

| 7.1 Vector table, VTOR and reset behavior                              | 70 |

|------------------------------------------------------------------------|----|

| 7.2 FPU related Security settings for a device with FPU implemented    | 71 |

| 7.3 Stack pointer limit setup and stack sealing                        | 71 |

| 8. RTOS and Secure software design considerations                      |    |

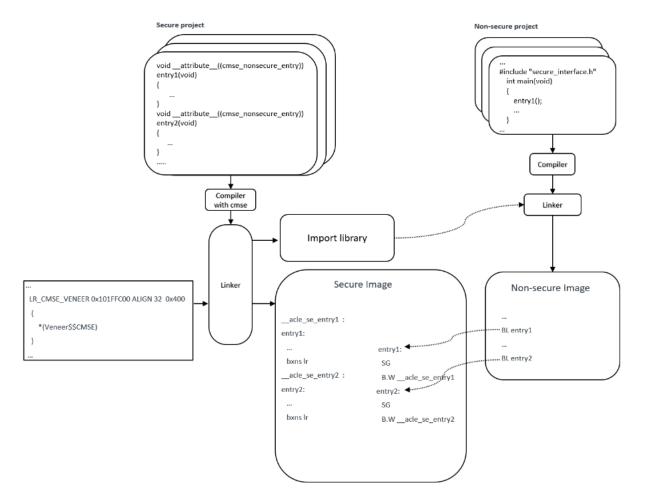

| 8.1 RTOS configurations                                                |    |

| 8.1.1 Possible OS configurations                                       |    |

| 8.1.2 Extension of CMSIS-RTOS for Non-secure RTOS                      |    |

| 8.2 Context-switching operations                                       | 77 |

| 8.2.1 RTOS design requirements                                         | 77 |

| 8.2.2 RTOS in the Non-secure state                                     |    |

| 8.2.3 RTOS in the Secure state                                         |    |

| 8.2.4 Supporting multiple Secure software libraries                    | 79 |

| 8.3 Secure software development design considerations                  | 80 |

| 8.3.1 Prevent Secure thread mode reentrancy                            |    |

| 8.3.2 Security and privilege combination                               | 80 |

| 8.3.3 AIRCR.BFHFNMINS considerations                                   |    |

| 8.3.4 EXC_RETURN.DCRS and EXC_RETURN.FType                             |    |

| 8.3.5 Interrupt deprivileging                                          |    |

| 8.3.6 Non-reentrant exceptions                                         |    |

| 8.3.7 Secure floating-point contexts                                   |    |

| 9. Armv8-M Security Extension use case examples                        | 83 |

| 9.1 Generic information                                                |    |

| 9.1.1 Tool versions                                                    |    |

| 9.1.2 What does the program image contain?                             |    |

| 9.1.3 Stack sealing                                                    |    |

| 9.1.4 System memory map                                                |    |

| 9.1.5 SAU regions configuration in Secure project                      |    |

| 9.1.6 Import library                                                   |    |

| 9.2 hello-world-in-security-states                                     |    |

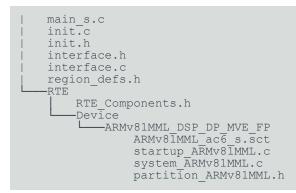

| 9.2.1 Secure project structure                                         |    |

| 9.2.2 Non-secure project structure                                     |    |

| 9.2.3 Output in Target Console                                         |    |

| 9.3 security-func-call-params-passing                                  | 94 |

| 9.3.1 Secure project structure                                         |    |

| 9.3.2 Non-secure project structure                                     |    |

| Copyright © 2025 Arm Limited (or its affiliates). All rights reserved. |    |

| 9.3.3 Output in Target Console              |     |

|---------------------------------------------|-----|

| 9.4 basic-Non-secure-only-program           | 99  |

| 9.4.1 Secure project structure              | 100 |

| 9.4.2 Settings for minimal secure boot code | 101 |

| 9.4.3 Launch Non-secure image               | 102 |

| 9.4.4 Non-secure project structure          | 102 |

| 9.4.5 Output in target console              | 103 |

| 9.5 exception-across-security-state         | 103 |

| 9.5.1 Secure project structure              | 104 |

| 9.5.2 Non-secure project structure          | 106 |

| 9.5.3 Output in Target Console              |     |

## 1. Introducing Armv8-M Security Extension

The Security Extension provides a foundation for improved system security in a wide range of embedded applications. This guide is for programmers intending to use the Security Extension in their systems.

This guide describes:

- Basic concepts that are used by the technology

- Toolchain requirements to create Secure software

- Concepts and best practices that developers must understand.

Developers must still perform their own security analysis in the context of their own threat model.

The Security Extension has also been known as TrustZone technology. This guide uses the name Security Extension.

### **1.1 Security concept**

At a high level, the concepts of the Security Extension are similar to those in Armv8-A architecture. In both architectures, the processor has Secure and Non-secure states:

- Non-secure software can access Non-secure resources only

- Secure software can access both Non-secure and Secure resources

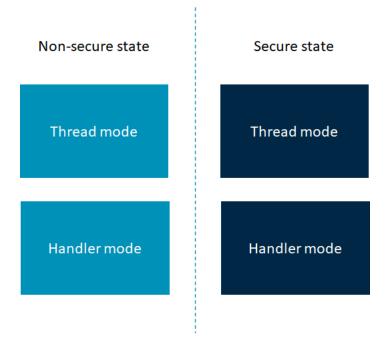

When the Security Extension is included in a processor, the existing Thread and Handler modes are duplicated to create Secure and Non-secure versions.

The Security Extension is designed for small energy-efficient systems. Code, assets, and data that belong to the more trusted software must be protected from access by or interference from the lesser trusted software. The trust model is asymmetrical and allows the more trusted software to access all code and data.

The Security Extension key functionalities are:

- The Security Extension supports multiple Secure function entry points. These can be directly called from the Non-secure state, without the overhead of calling into the operating system.

- The division of Secure and Non-secure worlds is memory map-based.

- Non-secure interrupts can still be serviced when executing a Secure function. Transitions between security states take place automatically during exception handling.

- There are dedicated resources, such as SysTick timers and fault handlers, for each security state.

- Protected exception priorities ensure that critical Secure operations cannot be blocked by Nonsecure code.

- Separate debug authentication ensures that the Non-secure state can be debugged even if the Secure state is locked down.

- Security attributes are added to the bus so that protection can be applied to the whole system, not just the CPU.

The Security Extension enables the system and the software to be partitioned into Secure and Non-secure states. This enables software with two different levels of trust to co-exist in the same system, running on the same processor. This reduces the attack surface by enabling security critical software in the Secure state to be protected even if there is a security vulnerability in the Non-secure software.

One of the use cases for Security Extension technology is implementing a PSA Certified Root of Trust. The PSA Certified scheme is a common industry framework and methodology for built-in security, enabling silicon manufacturers, system software providers, and OEMs. This ensures the security of connected products using a proven security architecture and corresponding open-source implementations. For more information see PSA Certified.

Trusted Firmware-M (TF-M) leverages Security Extension technology to provide a Trusted Execution Environment (TEE). It is the reference implementation of platform security architecture aligning with PSA Certified guidelines. See TF-M for more details.

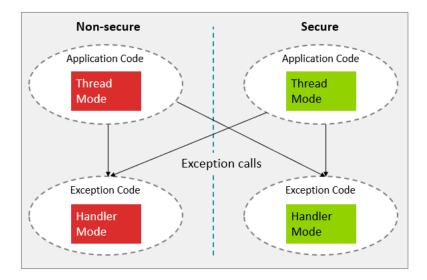

### **1.2 Privilege levels and security states**

The Armv8-M architecture uses modes to partition software between privilege levels.

- Handler mode is always privileged and is used for all exception and interrupt handlers.

- Thread mode is used for all other code and can be privileged or unprivileged.

Privilege affects the ability to access memory, the control register, and some instructions.

When the Security Extension is present two Security states are added:

- Secure software can access both Secure and Non-secure memories and resources

- Non-secure software can only access Non-secure memories and resources.

These security states are orthogonal to the existing Thread and Handler modes. This enables both a Thread and Handler mode in both Secure and Non-secure states.

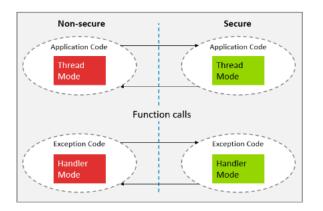

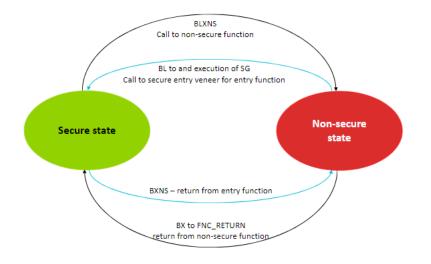

The following figure shows Secure and Non-Secure processor states.

#### Figure 1-1: Processor states

This split enables you to allocate code to one of the four mode or state combinations depending on the level of trust and privilege that are necessary:

- Secure thread mode executes the initial boot code.

- You can configure each interrupt to run in either the Secure or Non-secure state.

- Application threads can run in a single security state, or transition between security states while running. The processor can switch between security states at a function call boundary or by taking an exception that targets a different security state.

- Code must be allocated to either the Secure or Non-secure states, but not both, because the security of the memory indicates which security state the code must execute in.

- In Armv8.0-M privileged access is unified across the security states. For example, an attacker might control Non-secure privileged code and Secure unprivileged code. This means that the attacker has both privileged and Secure access, and therefore can access the Secure privileged state. Enhancements in the Armv8.1-M architecture increase the level of protection and make privileged access independent in both security states.

If the Security Extension is implemented, the system starts up in Secure state. If the Security Extension is not implemented, the system is always in Non-secure state.

The Secure software and Non-secure software are built as separate images. To understand how to build and link these images, see Booting and initializations.

### 1.3 Real world examples

Microcontrollers have a diverse set of use cases, ranging from simple bare metal systems to complex RTOS based environments. This section describes a few real-world use case examples that can be mapped with the Armv8-M Security Extensions.

This guide does not describe all the steps that you must take to implement the mapping or ensure the security of the system. Information is here for clarity.

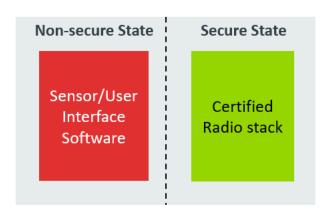

### 1.3.1 Bluetooth device

The Armv8-M Security Extensions enables a better foundation for system-level security. The simplest use case is where the thread modes in both the security states are privileged and only a single thread or firmware library needs protection.

One example of this is a radio communication system where:

- The certified radio stack, such as a Bluetooth stack, runs in Secure state

- The sensor software runs in Non-secure state

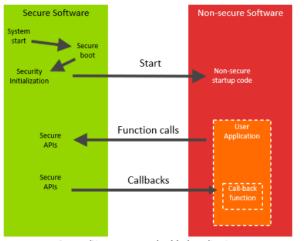

The following figure shows this kind of system.

#### Figure 1-2: IoT smart sensor

In this use case, the Security Extensions prevent:

- The application code from interfering with the operation of the certified radio stack

- Cloning and reverse engineering of the stack

If there are any bugs in the sensor software running in Non-secure state, they do not affect the radio stack because it is running in a Secure state. The low complexity of this use case and the

ability to directly call across the security boundary makes it easy to retrofit protection to an existing software stack.

In this example, a simple monolithic sensor code and a monolithic radio stack are used within a single thread. In this case, using a single stack pointer (MSP) in each security state, you can set:

- All the sensor software to run in Non-secure Privileged thread mode

- The certified radio stack to run in Secure Privileged thread mode

You can also use this setup to end system software of a safety critical systems like automotives or medical devices.

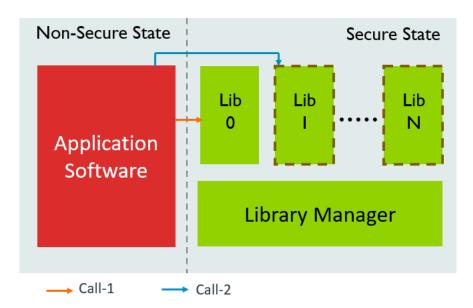

### 1.3.2 Firmware IP protection

In some systems, software libraries from several mutually distrustful vendors are run on a single processor. For example, an OEM might buy a microcontroller with multiple add-on libraries such as USB stacks, motor control code, and graphics libraries, from mutually distrustful 3rd party suppliers.

The following figure shows an example setup.

Figure 1-3: Firmware IP protection

In this system, a library manager running in the Secure privileged states uses the Secure MPU to make all except one of the Secure libraries inaccessible. If a function call is made to the active library that is currently accessible, then no fault is generated. The call has a very low calling overhead. See call 1 in the figure above. When a function call is made to an inactive library, an

MPU fault is generated. See call 2 to lib 1 in the figure above). This fault causes the library manager to swap the MPU configuration and Secure stack pointer to make the inactive library active.

This functionality has several advantages:

- Function calls are made directly to the destination library, which makes the software easier to write.

- The overhead of changing the MPU configuration only happens when a call is made to an inactive library. Subsequent calls to the same library do not cause a fault and have minimal overheads.

- Direct calls between Secure libraries are supported without a loss of protection.

# 2. Registers

Seeing data in registers and accessing control registers is crucial for the security of the system. The behavior of registers based on the current security states can include:

- Common access: The register or field is accessible from both security states.

- Secure access only: The register or field can only be accessed from the Secure state.

- Banked registers or fields: Both a Secure and Non-secure version of the register or field are implemented and can hold different values.

Armv8-M architecture banking behaves as follows:

- Sometimes only one of a banked pair of registers or fields is used at a time.

- The bank to select is sometimes based on the state the processor is in at the moment, for example stack pointers.

- The bank to select is sometimes based on the state of another control bit. For example, the bank of FPCCR.LSPACT bit to use is based on the FPCCR.S bit.

- The bank to select is based on another condition, such as whether Secure debug is allowed.

- Sometimes, both the Secure and Non-secure banks of a register or field apply at the same time. You then get the combined behavior of both sides, for example priority boosting registers like BASEPRI.

For more information, see the architectural register description in Armv8-M Architecture Reference Manual that specifies the banking options used.

### 2.1 General-purpose registers

Armv8-M uses 16 General-Purpose Registers (GPRs), R0 - R15, for normal execution. Most instructions use these registers. Some registers have special uses:

- R13 accesses the current stack pointer.

- R14 is a link register to hold the return address of function calls.

- R15 represents the current program counter.

The following figure shows the GPRs.

#### Figure 2-1: GPRs

| r0         |

|------------|

| r1         |

| r2         |

| r3         |

| r4         |

| r5         |

| r6         |

| <b>r</b> 7 |

| r8         |

| r9         |

| r10        |

| r11        |

| r12        |

| r13 (SP)   |

| r14 (LR)   |

| r15 (PC)   |

|            |

All of these registers, except R13 the stack pointer, are unbanked and always accessible to software. This means that a value, left in a register after a change in state, is visible to the other security state. Sometimes this is useful. For example, it allows data to be passed as part of a function call. It is crucial that Secure data is not made visible to non-trusted code in a unexpected way. For exceptions that change Security state, the registers are protected automatically by the hardware. For function calls, software must protect the registers. See Memory configuration.

### 2.2 Stack pointers

The Armv8-M architecture contains two stack pointers:

- The Main Stack Pointer (MSP): Software running in Thread mode can use the MSP. It is always used by Handler mode.

- The Process Stack Pointer (PSP): Thread mode software can use the PSP. The SPSel bit in the CONTROL register configures the Stack Pointer register to be used by Thread mode.

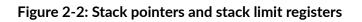

If the Armv8-M Security Extension is implemented, both the MSP and PSP are banked between security states. This provides four stack pointers: MSP\_NS, PSP\_NS, MSP\_,S and PSP\_S. The bank of the stack pointer is selected based on the current security state. The CONTROL.SPSel bit is also banked. This enables different stack configurations in Secure and Non-secure Thread modes.

The following figure shows the stack pointers and the stack limit registers.

For stacks and stack limit register configurations:

- All Secure stack pointers must point to memory that is marked as Secure and so it is not accessible for Non-secure code.

- All the stacks, both Secure and Non-secure, must be placed in a memory with an eXecute Never (XN) attribute.

- If both privilege levels are used, then the Thread mode must always use the PSP stack.

- The top of all Secure stacks must be sealed with a value of 0xFEF5EDA5. This concept is called stack sealing. See Armv8-M Architecture-Stack sealing and why it is needed in TrustZone for Armv8-M.

- Each stack pointer has an associated limit register which detects and prevents stack overflows. See Stack limit registers.

### 2.3 Stack limit registers

The stack limit registers in Armv8-M architecture can minimize stack overflow errors which are common in software. With stack limit registers, the privileged software can define the stack sizes for MSP and PSP in each security state as the [Stack Pointers and Stack Limit Registers] figure shows. If the value of the stack pointer goes below the stack limit registers, then it raises a synchronous stack limit violation (STKOF) UsageFault.

Armv8-M Architecture Reference Manual describes every instruction operation that operates with stack limit checks. Legal instructions that write to the stack pointer are subject to stack pointer limit checking, except where SP is the destination register for load instruction.

Table 2-1 shows how the stack limit registers can be accessed through CMSIS-CORE functions.

| Function                                          | Description                                  |

|---------------------------------------------------|----------------------------------------------|

| uint32_tget_PSPLIM (void)                         | Get PSP limit in the current security state. |

| voidset_PSPLIM (uint32_t ProcStackPtrLimit)       | Set PSP in the current security state.       |

| uint32_tget_MSPLIM (void)                         | Get MSP limit in the current security state  |

| set_MSPLIM (uint32_t MainStackPtrLimit)           | Set MSP limit in the current security state. |

| voidset_MSPLIM(void)                              | Set MSP limit in the current security state  |

| uint32_tTZ_get_PSPLIM_NS (void)                   | Get PSP limit (Non-secure)                   |

| voidTZ_set_PSPLIM_NS (uint32_t ProcStackPtrLimit) | Set PSP (Non-secure)                         |

| uint32_tTZ_get_MSPLIM_NS (void)                   | Get MSP limit (Non-secure)                   |

| voidTZ_set_MSPLIM_NS (uint32_t MainStackPtrLimit) | Set MSP limit (Non-secure)                   |

In Cortex-M processors that implement Armv8-M-Baseline, the stack limit registers are not implemented. If you use CMSIS-CORE functions shown in Table 2-1 in Cortex-M processors, reads return zero and writes are ignored.

### 2.4 Special-purpose registers

PRIMASK, FAULTMASK, and BASEPRI registers are Special-Purpose Registers (SPRs) used for exception masking. See Armv8-M Programmers Model User Guide. When Security Extension is implemented, these mask registers are banked between the security states. Both the Secure and Non-secure versions are applied at the same time, regardless of the current security state of the processor. These and other SPRs are accessible in privileged state only. To access these registers, use special move instructions such as MRS, MSR, VMSR, VMSR, and CPS. In addition to accessing the register associated with the current security state, the Secure state can also access the Non-secure version of the registers:

| MRS RO, PRIMASK    | // Copy PRIMASK value to R0                                                                                                       |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| MRS RO, PRIMASK_NS | <pre>// in current security state // Copy Non-secure PRIMASK value to R0. Only // allowed when executed in the Secure state</pre> |

CMSIS-CORE also provides functions access to exception masking registers as Table 2-2 shows.

| Function                               | Usage                        |

|----------------------------------------|------------------------------|

| voidset_PRIMASK (uint32_t priMask)     | Sets the PRIMASK register    |

| uint32_tget_PRIMASK (void)             | Reads the PRIMASK register   |

| voidset_FAULTMASK (uint32_t faultMask) | Sets the FAULTMASK register  |

| uint32_tget_FAULTMASK (void)           | Reads the FAULTMASK register |

| voidset_BASEPRI(uint32_t basePri)      | Sets the BASEPRI register    |

| uint32_tget_BASEPRI(void)              | Reads the BASEPRI register   |

Copyright @ 2025 Arm Limited (or its affiliates). All rights reserved. Non-Confidential

| Function                                     | Usage                                              |

|----------------------------------------------|----------------------------------------------------|

| voidset_BASEPRI_MAX (uint32_t basePri)       | Sets the BASEPRI register using BASEPRI_MAX symbol |

| voidTZ_set_PRIMASK_NS (uint32_t priMask)     | Sets the PRIMASK_NS register                       |

| uint32_tTZ_get_PRIMASK_NS (void)             | Reads the PRIMASK_NS register                      |

| voidTZ_set_FAULTMASK_NS (uint32_t faultMask) | Sets the FAULTMASK_NS register                     |

| uint32_tTZ_get_FAULTMASK_NS (void)           | Reads the FAULTMASK_NS register                    |

| voidTZ_set_BASEPRI_NS (uint32_t basePri)     | Sets the BASEPRI_NS register                       |

| voidTZ_get_BASEPRI_NS (void)                 | Reads the BASEPRI_NS register                      |

For more information, see Armv8-M Architecture Reference Manual

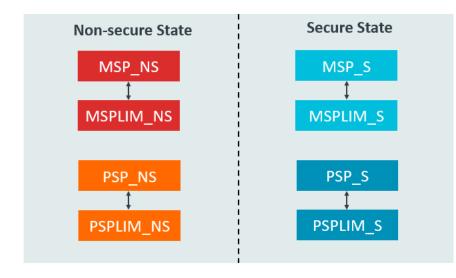

### 2.5 System control registers

The System Control Space (SCS) provides registers for control, configuration, and status reporting of the processor. The SCS is in the Private Peripheral Bus (PPB) space and contains:

- The NVIC

- The MPU

- The System Control Block (SCB)

- Various peripherals

The SCS is at address 0xE000E000, which Secure and Non-secure software can access. The SCS accesses the bank of the registers associated with the current security state. Secure software can access the Non-secure version of SCS registers at alias address 0xE002E000.

The following figure shows the SCS in Security state.

#### Figure 2-3: SCS in Security State

# 3. Memory configuration

This chapter describes:

- Memory security attributes and Security Attribute Units (SAU)

- How to partition memory into Secure, Non-secure, and Secure, Non-secure Callable (NSC) regions using SAU

- Memory Protection Unit (MPU) interactions with the security state

### 3.1 Memory security attributes

When the Security Extension is implemented, the address space is partitioned into Secure and Non-secure memory regions. The Secure memory space is further divided into two types:

- Non-secure (NS): Non-secure memory regions are accessible by both Non-secure and Secure software. When executing software in Non-secure memories, the processor is in Non-secure state.

- Secure: Secure regions are used for memory and peripherals that are only accessible by Secure software. When executing software in Secure memories, the processor is in Secure state. If a data access is made from Non-secure state to an address marked as Secure, then the processor takes a SecureFault.

- Non-secure Callable (NSC): NSC region is a special Secure memory region, which is the only type that an Armv8-M processor permits to hold entry points for Secure APIs. These entry points enable software to transition from Non-secure state to Secure state. The combination of a Secure NSC region and the SG instruction provides a mechanism to prevent Non-secure software jumping into arbitrary Secure code and potentially bypassing security checks in entry points.

If the Non-secure software does branch into Secure executable memory region where either the first instruction is not an SG instruction or the address does not have a Secure NSC attribute, then then the processor takes a SecureFault. Non-secure software cannot read or write to a Secure NSC memory, but can branch into it if the branch target is a SG instruction.

Exempted memory regions can be accessed by both Secure and Non-secure software. These regions are generally used by processor and debug registers.

### 3.2 SAUs

The Security attribution of a memory region is controlled by a combination of two attribution units:

• Security Attribution Unit (SAU): The SAU is programmable in Secure state and is controlled by CPU registers in a similar way to the MPU.

• Implementation Defined Attribution Unit (IDAU): The IDAU is external to the processor and depends on chip designer implementation.

Both the SAU and IDAU are optional. The memory Security attribution is determined by the unit which has the strictest Security attribution specified.

The device designer divides the memory spaces into Secure and Non-secure areas. Designers can use an IDAU to define a fixed memory map, and use a SAU to override the security attributes for some parts of the memory.

### 3.2.1 SAU

The SAU contains programmable registers within System Control Space (SCS). The SAU is programmable by Secure privileged software. The number of SAU regions depends on the implementation of the Armv8-M processor. It is common for processors to include 0, 4, or 8 SAU regions. Each region is defined using the base address register and the limit address register. These registers have a minimum granularity of 32 bytes.

The following table lists the SAU registers used for programming the regions.

| Address    | Register | Description                       | CMSIS-Core Symbol |

|------------|----------|-----------------------------------|-------------------|

| 0xE000EDD0 | SAU_CTRL | SAU Control register              | SAU->CTRL         |

| 0xE000EDD4 | SAU_TYPE | SAU Type register                 | SAU->TYPE         |

| 0xE000EDD8 | SAU_RNR  | SAU Region Number register        | SAU->RNR          |

| 0xE000EDDC | SAU_RBAR | SAU Region Base Address register  | SAU->RBAR         |

| 0xE000EDE0 | SAU_RLAR | SAU Region Limit Address register | SAU->RLAR         |

### 3.2.2 IDAU

Chip vendors design the IDAU. Usually, the IDAU:

- Provides address lookups

- Generates Security attributes of the address being accessed

- Defines the memory regions as Secure, Non-secure, Non-secure Callable, or exempt from Security checking

For more details on a particular IDAU, read the materials provided by the relevant chip vendor. However, IDAUs often follow the guidelines in the TrustZone Technology Microcontroller System Hardware Design Concepts User Guide.

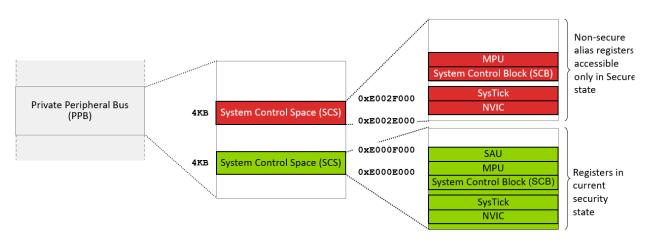

### 3.2.3 Address lookup

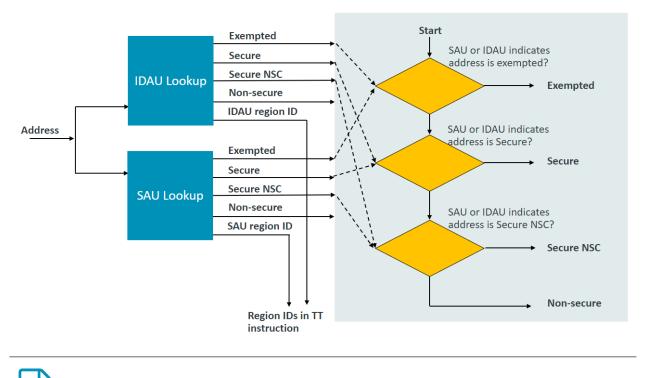

The following figure shows the SAU address lookup function.

#### Figure 3-1: SAU address lookup

When both SAU and IDAU are implemented in a system, then the address lookup occurs from both as the following figure shows.

#### Figure 3-2: Combined SAU and IDAU Address lookup

The addresses for registers inside the CPU defined as exempt by the SAU are not programmable

### 3.2.4 Configuring SAU using CMSIS

Note

To program the SAU, Secure privileged software performs the following steps:

- 1. Read the SAU\_TYPE register to find the number of available regions for the Armv8-M processor you are working with.

- 2. Use the SAU\_RNR register to select a region for configuration. For example, in a system that allows 8 SAU regions, the software can write a 0x3 to SAU\_RNR to select region three.

- 3. Configure the selected SAU region:

- a. Write the region base address into the SAU\_RBAR

- b. Write the region limit address into the SAU\_RLAR. Bits [4:0] of the limit address are defined as 0x1F.

The SAU\_RLAR register also contains two additional fields, the NSC bit and the ENABLE bit:

• The NSC bit determines whether a region is Non-secure or Secure NSC.

- The ENABLE bit determines whether the region is currently enabled or disabled. Repeat steps 2 and 3 for the remaining SAU regions to be programmed.

- 4. Add DSB to ensure that the register accesses are finished.

- 5. Enable SAU by using the SAU\_CTRL.ENABLE bit.

CMSIS-Core pack provides the partition\_<device>.h file which contains the TZ\_SAU\_Setup() function and related settings. SAU registers are set up in the TZ\_SAU\_Setup() function.

Example SAU region settings in the partition\_<device>.h file are as follows:

```

// Initialize SAU Region 0 Setup SAU Region 0 memory attributes

#define SAU_INIT_REGION0 1

#define SAU_INIT_START0 0x101FFC00 // Start address

#define SAU_INIT_END0 0x101FFFFF // End address

#define SAU_INIT_NSC0 1 //Region is 0: Non-secure 1:Secure, Non-

secure Callable

// Initialize SAU Region 1 Setup SAU Region 1 memory attributes

#define SAU_INIT_REGION1 1

#define SAU_INIT_START1 0x0000000

#define SAU_INIT_END1 0x001FFFFF

#define SAU_INIT_NSC1 0

```

The TZ\_SAU\_Setup() function in partition\_<device>.h uses these settings to configure SAU regions one by one. The combination of the IDAU and programmed SAU attributes must match the system memory map and the linker script, so that secret data is marked as Secure. For example, this ensures that a Secure peripheral is not accessible to the Non-secure state. In software programming, we recommend that you allocate a single software object, such as the stack, within one single SAU/IDAU region. This ensures that the TT instruction can be used to quickly check ranges of addresses.

### 3.3 Memory configuration with the MPU in Secure state

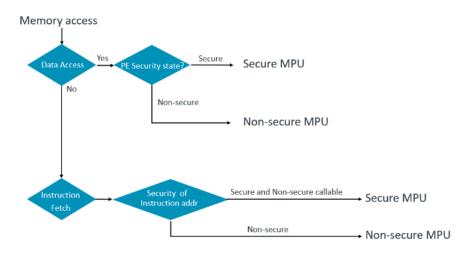

The processor contains a Secure MPU and a Non-secure MPU. The MPUs set memory attributes like cacheability, and provide several privileged and unprivileged permissions. See Armv8-M Memory Model and Memory Protection User Guide.

The following figure shows the address MPU lookup flow when both the MPU and SAU or IDAU are implemented in a system.

#### Figure 3-3: MPU in Security state

In software programming, we recommend that you allocate a single software object, such as the stack, within a single MPU region. This ensures that the TT instruction can be used to quickly check ranges of addresses.

## 4. Function calls

This chapter describes the following functionality:

- Security state transitions

- Function calls across the Security boundary

- Parameters passing

- Pointer passing

- TT instruction and CMSE intrinsic functions

- Floating point context consistency and FPCXT payload

### 4.1 Transition between security states

The Armv8-M Security Extension supports Security state transition by function call, as the following figure shows.

#### Figure 4-1: State transitions across security states

Function calls can cross the security boundary in both directions. That is, both Secure to Non-Secure calls and Non-Secure to Secure calls are supported. Although cross security boundary calls are supported in both thread and handler mode, they do not change the mode the CPU is in. For example, a function call in Secure Handler mode which targets the Non-Secure state, stays in Handler mode.

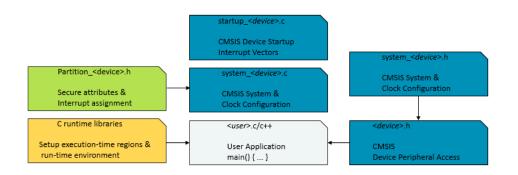

# 4.2 Implementing function calls across the Security boundary for C development

The Cortex-M Security Extension (CMSE) helps you to implement function calls across the Security boundary. CMSE is a toolchain extension which:

- Provides support for Secure software that is written in the C language

- Provides mechanisms to build and link the Secure and Non-Secure part of the software independently

- Generates Security Extension-related instructions such as SG, BXNS, BXNS

- Generates an import library that allows the Non-Secure image to be linked against the functions provided by the Secure image

The Non-Secure software build process does not need the CMSE toolchain support. The <arm\_cmse.h> header must be included by the Secure software before using CMSE support. For information about CMSE, see CMSE.

The following section describes how to implement function calls across the Security boundary with the CMSE for C level development.

### 4.2.1 Non-Secure software calling a Secure API

To enable a Secure function to be called from the Non-Secure state follow these steps:

Include the arm\_cmse.h file and add the CMSE function attribute \_\_attribute\_\_(cmse\_nonsecure\_entry)) in a Secure function definition. The function can then be called from the Non-Secure state.

The cmse\_nonsecure\_entry attribute causes the compiler to:

- Automatically generate a veneer with the SG entry point gateway

- Clear the registers of any secret data before returning

- Cause the return operation to be performed with a BXNS instruction

A simple Secure function is as follows:

```

#include <arm_cmse.h>

#include "secure_interface.h"

int __attribute__((cmse_nonsecure_entry)) entry1(int x)

{

...

}

```

2. Secure APIs are prototyped as normal in an interface header in a Secure project. For example:

```

Secure_interface.h:

int entry1(int x);

```

3. Group the entry point veneers into a section to define as Non-Secure callable (NSC). The following scatter file section shows how to define a NSC region and place the veneer section:

```

LR_CMSE_VENEER 0x10100000 ALIGN 32 0x400

{

-(Veneer$$CMSE)

}

```

See Secure entry veneers.

- 4. Set up SAU regions so that veneer regions are marked as NSC. For more details on configuring SAU regions, see Configuring SAU using CMSIS.

- 5. Compile by using the command-line build option -mcmse. Add the linker command-line option to generate import library.

- 6. During the Non-Secure project build process, the linker must resolve the symbols and addresses of the Secure APIs entry point. The CMSE toolchain provides build options, such as --import-cmse-lib-out in armclang to generate the import library for a Non-Secure project.

- 7. In the Non-Secure project, perform the following steps without any CMSE support:

- a. Add and include the header file that declares the Secure functions that are callable from the Non-Secure state. In this example this is the secure\_interface.h file.

- b. Link with the Secure import library generated in step above.

- c. Call the Secure APIs as a normal library function

A simple example code is as follows:

```

#include "secure_interface.h"

int main(void)

{

int x = 100;

entry1(x);

...

}

```

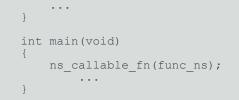

### 4.2.2 Secure software calling a Non-Secure function

- Using the BXNS instruction for the function call

- Saving and clearing the registers that might contain secret data. To save time the floating point registers might be handled lazily.

- Restoring the registers after the Non-Secure function returns

Whether a function pointer with the cmse\_nonsecure\_call attributes actually causes a Secure to Non-Secure transition, or stays within the Secure state is determined an runtime by checking the

LSB of the pointer. This allows the same function in C to be used for both Secure and Non-Secure function pointers, causing a security state transition only when necessary.

During the Secure software development, the address location of the Non-Secure function is unknown. Function pointers are passed from Non-Secure software to Secure software via Secure APIs, when the Secure software receives the Non-Secure function pointer, Secure software can call the Non-Secure function when needed later.

The following is an example of a Secure software calling a Non-Secure function:

- 2. Define a Secure function that takes a pointer to the Non-Secure function to call. Use the cmse nsfptr create() intrinsic to mark the pointer as coming from the Non-Secure state.

- 3. The Non-Secure function will be called later in a Secure project.

Example code is as follows:

```

typedef int __attribute__((cmse_nonsecure_call)) nsfunc(int);

nsfunc -ns_callback = 0;

int __attribute__((cmse_nonsecure_entry)) ns_callable_fn(nsfunc- callback)

{

ns_callback = (nsfunc -)cmse_nsfptr_create(callback);

...

}

void Secure_fn(void)

{

int indata = 0;

...

ns_callback(indata);

...

}

```

-cmse\_nsfptr\_create()-#

This intrinsic function returns the value of the callback function pointer, with its LSB cleared. You can find more details about this in section CMSE intrinsic functions. In this example the Non-Secure function pointer is called from a different function, then cmse\_nsfptr\_create() should be called in the function where the Non-Secure pointer is passed into the Secure state, and not the one where it is called.

The security\_func\_call\_params\_passing example in [Use case examples] shows you how to implement function call with function pointer as argument and call the Non-Secure function in Secure state.

4. The Non-Secure software implements Non-Secure functions as usual, and passes this function pointer to Secure side when Non-Secure software calls the Secure API. A simple example is as follows:

```

#include "secure_interface.h"

int func_ns (int x)

{

```

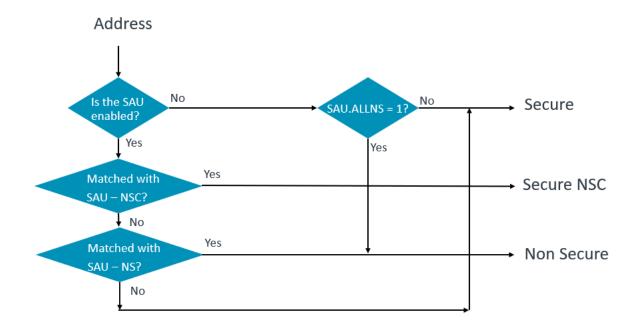

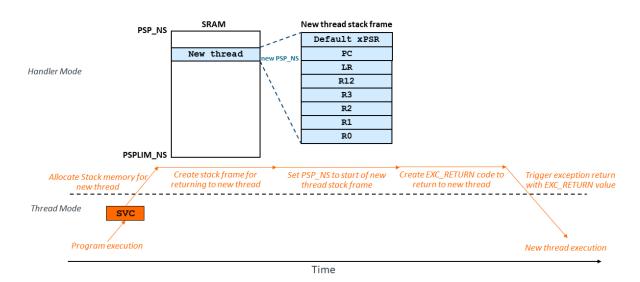

# 4.3 The assembly instructions for Security states transition by function call

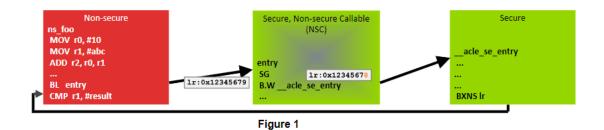

The following figure shows the assembly instructions for Security states transition by function call.

Figure 4-2: Security switch with Function call

- sc: Secure gateway. Used for switching from Non-Secure to Secure state as the first instruction of Secure entry veneer.

- BXNS <Rn>: Branch with exchange to Non-Secure state if Rn[0] = 0. Used by Secure software to return from a Security entry point function.

- BXNS <Rn>: Branch with link and exchange to Non-Secure state if Rn[0] = 0. Used by Secure software to call Non-Secure functions.

- FNC\_RETURN: When a BXNS instruction causes a transition to the Non-Secure state, it places a reserved address called FNC\_RETURN in the link register. The Non-Secure function triggers the return to the Secure state by branching to this address, for example, with BX LR.

### 4.3.1 Function call from Non-Secure to Secure state

Function calls from Non-Secure to Secure state can be initiated by a Non-Secure software function branching to a Secure gateway.

Figure 4-3 shows how a Non-Secure program calls a Secure API.

Figure 4-3: Non-Secure call Secure

The process is as follows:

- 1. Non-Secure code calls a Secure API. The Secure address location through which the Non-Secure code branches into the Secure API is called Secure entry veneer. The Secure entry veneer must be in the Non-Secure Callable (NSC) memory region with the first instruction sg.

- 2. If sg is executed in the Non-Secure state, as the figure above shows:

- Bit 0 of the return address in LR is set to 0.

- Bit 0 of the return address can therefore be trusted to indicate which Security state the Secure function must return to when it is complete.

- 3. After sg instruction is executed from the NSC memory, the processor state switches to Secure.

sg is treated as a No Operation (NOP) if it is fetched from Non-Secure memory.

If a Non-Secure program tries to branch or call a Secure program address without using a valid entry gateway, a SecureFault event is generated. On Cortex-M processors built with Armv8-M Baseline architecture, such as Cortex-M23, SecureFault is permanently disabled, so a Secure HardFault is generated instead.

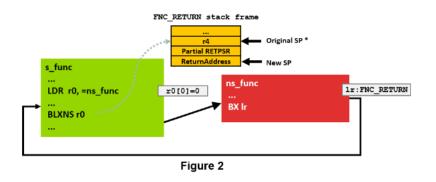

### 4.3.1.1 Secure entry veneers

Secure entry veneers consist of an sg instruction followed by a B.W instruction that targets the entry function in Secure memory.

An example veneer code is as follows:

```

entry1

0x10100000: e97fe97f .... SG ;

0x10100004: f702bae0 .... B.W __acle_se_entry1;

```

The Secure APIs are prefixed with \_\_acle\_se to indicate that the symbols point to the body of Secure entry functions:

Secure entry veneers allow Non-Secure code to call Secure APIs via sg instructions. The following figure shows the relationships between Non-Secure code, veneer code, and Secure code.

#### Figure 4-4: Secure entry veneers

| Secure region                                                    |

|------------------------------------------------------------------|

| Secure code                                                      |

|                                                                  |

| <br>acle_se_entry1:<br>entry1:<br>/*Function Body*/<br>BXNS lr   |

| <br>acle_se_entry2:<br>entry2:                                   |

| <br>/*other functions*/                                          |

| Secure, Non-secure callable (NSC) region<br>Secure entry veneers |

| <br>entry1:<br>SG                                                |

| B.Wacle_se_entry1                                                |

| entry2:<br>SG<br>B.Wacle_se_entry2                               |

| Secure data                                                      |

| Non-secure region<br>NS code                                     |

| ••••<br>bl entry1                                                |

| ••••<br>NS data                                                  |

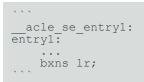

### 4.3.2 Function return from Secure state

As the above figure shows, after Secure API completes, it uses a BXNS instruction to return back to the Security state it was called from, as shown by bit 0 of the return address. Before executing the BXNS instruction, all sensitive data must be cleared from the caller saved registers. For example, if the floating point registers are not used, these are RO-R3, R12, LR, and APSR.

### 4.3.3 Function call from Secure to Non-Secure state

A function call from Secure to Non-Secure state can be initiated by Secure software using the BXNS instruction that has the Least Significant Bit (LSB) of the target address set to 0.

The following figure shows how a Secure program calls a Non-Secure function.

#### Figure 4-5: Secure call Non-Secure

Steps for a Secure program to call a Non-Secure function are as follows:

- 1. Before executing the BXNS instruction to switch to Non-Secure state, Secure software must save and clear all callee and caller saved registers except the following registers:

- Link Register (LR)

- Registers that hold arguments for the Non-Secure function

- Registers that do not hold secret information

- 2. The function call is performed using a BXNS instruction. If bit 0 of the function pointer is 0 the instruction transitions to the Non-Secure state. If a transition to the Non-Secure state is NOT requested, then all the operations below are skipped. Instead, a normal branch is performed.

- 3. The function return address is pushed into the FNR\_RETURN stack frame on the Secure stack to hide it from Non-Secure code. This prevents Non-Secure code from modifying the Secure return address. The processor also pushes what is known architecturally as the Partial RETPSR into the Secure stack.

- 4. If the processor is in Secure Handler mode, IPSR is set to 1. Non-Secure code has no knowledge of which exception was run previously.

- 5. The processor stores the value called FNC\_RETURN into the LR.

### 4.3.4 Function return from Non-Secure state

As the above figure shows, after the Non-Secure function finishes execution, it returns to caller function. The return operation, for example, BX LR, loads the FNC\_RETURN value into the Program Counter (PC). 1. Integrity checks are performed. For example, one check is that the current mode of the processor matches the mode indicated by the RESPSR value saved in the FNC\_RETURN stack frame. Any failed integrity check on function return generates Fault. 2. If integrity checks are successful, the real ReturnAddress is unstacking from the FNC\_RETURN stack frame on the Secure stack. 3. The processor switches back to Secure state.

# 4.4 Software considerations in function calls across security boundary

This section describes key software considerations during function calls across security boundary.

### 4.4.1 Pointer passing across Security boundary

Pointer passing in function calls across the Security boundary is supported. Several Security issues can occur from passing pointers across Security state boundaries, including: 1. The Non-Secure state might be able to pre-empt Secure code and modify the data referenced by a pointer passed to a Secure function. This might break assumptions a programmer makes about the data not changing, for example between validating it and using it. 2. The Non-Secure state can pass a pointer to Secure memory to a Secure function. If the Secure code uses this pointer without validating it, it might be tricked into performing an operation on behalf or Non-Secure code that the Non-Secure code does not have permission to do directly. This is more commonly known as the confused deputy attack.

This can happen when either:

The Non-Secure software tries to trick the Secure code into accessing Secure data

The unprivileged Non-Secure software tries to trick the Secure code into accessing privileged Non-Secure data

The Armv8-M Security Extension defines II instructions and CMSE-compliant compiler toolchain support CMSE intrinsics. [Use Case Examples] describes how to use these intrinsics to check pointer arguments in Secure software.

#### 4.4.1.1 Data Pointer validation

Secure APIs perform operations on behalf of Non-Secure software, such as cryptographic data processing. Non-Secure software passes data pointers to the Secure software to indicate where the data sources are and where to put the processing results. When a Secure API gets the data pointer from Non-Secure side, it must check that Non-Secure software can read or write this memory before accessing it.

Non-Secure memory can be changed asynchronously during the execution of a Secure API. When a Secure API is executed, the processor is interrupted to service Non-Secure interrupts. The Non-Secure data that the pointer points to can be accessed and modified by the Non-Secure interrupt handler. The following code shows the problem:

```

int array[N];

void __attribute__((cmse_nonsecure_entry)) SecureFunc1(int -p)

{

// No checks performed on Non-Secure pointer before it is dereferenced.

if (-p >= 0 && -p < N)</pre>

```

```

/- Non-Secure memory (-p) may be changed at this point so that

-p is outside the range of the array. For example,

by a Non-Secure interrupt handler.

array[-p] = 0;

}

}

void attribute ((cmse nonsecure entry)) copy(int -src, int -dest, int len)

for ( int i = 0; i < len; i++)

/- if Non-Secure code passed Secure addresses to either src or dest

then this code would allow the Non-Secure state to bypass the memory

protection

by getting the Secure code to copy secret data into Non-Secure

memory,

or by overwriting Secure memory

-/

dest[i] = src[i];

}

```

The following code shows a safe example:

```

int array[N];

void __attribute__((cmse_nonsecure_entry)) SecureFunc1(int -p)

int index = 0;

volatile int -psafe = NULL;

/- The cmse check pointed object() intrinsic checks that p points to

Non-Secure memory and Non-Secure MPU indicates that it is readable in

the current mode.

- /

psafe = cmse check pointed object(p, CMSE NONSECURE|CMSE MPU READ);

if ( psafe != NULL)

{

/- without the volatile keywork to declare psafe, the compiler may

choose

not to copy the value to index variable,

and could still access Non-Secure memory multiple times.

-/

index = -psafe; // copy the value from Non-Secure to Secure memory

/- even if the data pointed to by psafe changes,

then all references to index here get the same value

because we have a local copy

- /

if (index \geq 0 && index < N )

array[index] = 0;

}

}

. . .

}

void attribute ((cmse nonsecure entry)) copy(int -src, int -dest, int len)

int -srcsafe = NULL;

int -destsafe = NULL;

srcsafe = cmse check address range(src, len, CMSE NONSECURE |

CMSE MPU READ );

destsafe = cmse_check_address_range(dest, len, CMSE_NONSECURE |

CMSE MPU READWRITE );

if ((srcsafe != NULL) && (destsafe != NULL))

```

```

for ( int i = 0; i < len; i++ )

{

destsafe[i] = srcsafe[i];

}

...

}

</pre>

```

You must also consider other usage scenarios for data pointer validation across the security boundary:

- When passing a data pointer from the Non-Secure side, permission checks on the objects pointed to by the pointer can be performed. These checks use the address range checking intrinsic, cmse\_check\_address\_range() and cmse\_check\_pointed\_object().

- When dealing with complex software objects like linked lists, software developers must use the address range checking intrinsic to verify each linked list object individually.

- If the return values from Non-Secure to Secure functions involve complex software objects, the Secure function must use the address range checking intrinsic to verify the permissions.

#### 4.4.1.2 Function pointer checking

For function pointer checking:

- No special checking is needed when a function pointer which remains within the Secure state, and always points to a Secure function. Call the function normally.

- When a function pointer passes to a Secure entry point that is always called from the Non-Secure state, software developers must use the cmse\_nsftptr\_create() function to clear the LSB of the Non-Secure function pointer.

- A function pointer can pass to a Secure entry point which can be called by both the Secure state and the Non-Secure state. We recommend that you use cmse\_nonsecure\_caller() to check whether the Secure entry point function has been called from the Non-Secure state or Secure state. Only use the cmse\_nsftptr\_create() function when the Secure entry point is called by the Non-Secure state.

#### 4.4.2 Non-pointer parameter passing

Non-pointer parameter passing in function calls across the Security boundary is supported for Secure APIs or Non-Secure functions calls that have more arguments than can fit in registers. You can pass a pointer to a struct containing all the arguments. The security\_func\_call\_params\_passing example in Armv8-M Security Extension use case examples describes how to use a struct to pass more arguments during a function call.

### 4.4.3 CMSE intrinsic functions

CMSE provides intrinsics to check the memory attributes within C/C++ code:

cmse\_address\_info\_t cmse\_TT(void -p)

The intrinsic cmse\_TT returns the memory attributes for a single address in memory:

void -cmse\_check\_address\_range(void -p, size\_t size, int flags)

The cmse\_check\_address\_range intrinsic checks that the specified address range meets the access permissions outlined by the flags. It returns NULL on a failed check and -p on a successful check.

void -cmse\_check\_pointed\_object(void -p, int flags)

The cmse\_check\_pointed\_object intrinsic checks that the specified object meets the access permissions outlined by the flags. Returns NULL on a failed check and -p on a successful check.

When using these intrinsic functions, the access permission condition needs to be specified by using the flags parameter. The flag values are defined in CMSE using C macros.

| Macro              | Description                                                                                                                                                                                                               |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMSE_MPU_UNPRIV    | Forces the check to be done using unprivileged permission. Without this flag, the current mode and CONTROL.nPRIV flag for the security state corresponding to the MPU selected are used to determine the privilege level. |

| CMSE_MPU_READWRITE | Checks if the readwrite_ok field is set in the permission of an address                                                                                                                                                   |

| CMSE_MPU_READ      | Checks if the read_ok field is set in the permission of an address                                                                                                                                                        |

| CMSE_AU_NONSECURE  | Checks if the Secure field is unset in the permission of an address                                                                                                                                                       |

| CMSE_MPU_NONSECURE | Checks the permission of an address using the Non_secure MPU                                                                                                                                                              |

| CMSE_NONSECURE     | The combined semantics of CMSE_AU_NONSECURE and CMSE_MPU_NONSECURE                                                                                                                                                        |

The address range checking intrinsics work assuming that the configurations of the SAU, IDAU, and MPU are constrained as follows:

- An object or an address range to be checked is allocated in a single region.

- A stack is allocated in a single region.

- A region does not overlap other regions.

The address range checking intrinsics use TT instruction to return an SAU, IDAU, and MPU region number. When the region numbers of the start and end of the address range match, the complete range is in one SAU, IDAU, and MPU region. See TT instruction for information on TT instruction checks across the region boundary.

CMSE also provides Non-Secure function pointer intrinsic functions listed as follows:

• cmse\_nsfptr\_create(p): Makes a function pointer as Non-Secure so it can only be used to call back to the Non-Secure state.

- cmse\_is\_nsfptr(p): Checks whether a given function pointer value should be interpreted as a Non-Secure function address.

- cmse\_nonsecure\_caller(): Returns non-zero if the Secure function is called from the Non-Secure state and zero otherwise.

For details about these functions, see TT instruction intrinsics.

#### 4.4.4 TT instruction

The Armv8-M architecture defines the Test Target (TT) instruction. The TT instruction is used to query the Security state and access permission of a memory location.

| TT instruction<br>variant                              | Description                                                                                                                                                                                                                                                       |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TT (Test Target)                                       | Queries the Security state and access permissions of a memory location                                                                                                                                                                                            |

| TTT (Test Target<br>Unprivileged)                      | Queries the Security state and access permissions of a memory location for unprivileged access to that location                                                                                                                                                   |

| TTA (Test Target<br>Alternate domain)                  | Query the Security state and the Non-Secure MPU setting to get access permissions of a memory location for a Non-Secure access to that location. Only valid when executing in Secure state. <b>UNDEFINED</b> if they are used from Non-Secure state.              |

| TTAT (Test Target<br>Alternate domain<br>Unprivileged) | Query the Security state and the Non-Secure MPU setting to get access permissions of a memory location for a Non-Secure unprivileged access to that location. Only valid when executing in Secure state. <b>UNDEFINED</b> if they are used from Non-Secure state. |

TTA and TTAT instructions are only valid when executing in Secure state, the instructions are **UNDEFINED** if they are used from Non-Secure state.

TT\_RESP payload provides the response information from a TT, TTA, TTT, or TTAT instruction. *Armv8-M Architecture Reference Manual* defines the TT\_RESP bitfields.

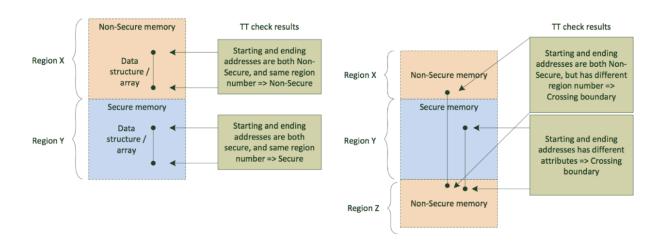

For each memory region defined by the SAU, IDAU, and MPU, there is an associated region number that is generated by the SAU, IDAU, or MPU. Software uses this region number to determine if a contiguous range of memory shares common security attributes. The TT instruction returns the attributes and region numbers for an address value. For data array or data structure, software can quickly determine that the memory range is located in the same SAU, IDAU, and MPU region by:

- Uing a TT instruction on the start and end addresses of the memory range

- Identifying that both reside in the same region number

The following figure shows TT instruction checks across the region boundary.

#### Figure 4-6: TT instruction checks across the region boundary

Software needs to check that memory addresses configured in SAU, IDAU, and MPU regions are not overlapping with each other because this affects the range checking mechanism implemented by TT instruction.

Using this mechanism, Secure code can determine if the memory referenced by a pointer from Non-Secure software has the appropriate security attribute. This prevents Non-Secure software from using Secure software to read out or corrupt Secure or privileged information it does not have access to.

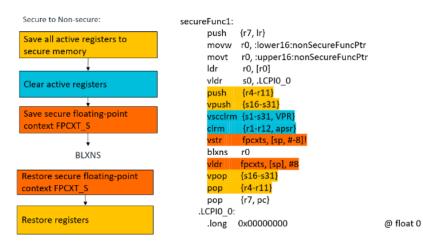

## 4.5 Floating-point context consistency and FPCXT payload

The floating-point context, stored in FPSCR, is not banked between the security states. In Armv8.1-M, the floating-point context payload, FPCXT\_S and FPCXT\_NS, is added to enable floating-point context to be saved/restored during function calls with Security state switch.

Both FPCXT\_NS and FPCXT\_S can only be accessible in the Secure state. For more details on FPCXT bitfield, See *Armv8.1-M Architecture Reference Manual*.

FPCXT\_S enables saving and restoring the floating-point context around a call to a Non-Secure function from the Secure state. It also initializes the floating-point context ready for the Non-Secure code. FPCXT\_S only needs to be used if the Secure state has used floating point instructions. FPCXT\_S saves and restores the context if this has not been performed by other instructions, for example, if VLSTM or VLLDM are not used because floating-point arguments are passed to the Non-Secure function.

FPCXT\_NS enables saving and restoring the floating-point context and the start/end of a Secure entry point function. This only needs to be done if the Secure entry point function or the other functions it calls might use floating point instructions.

The following example code shows a Secure function secureFunc1() which calls nonSecureFuncPtr. nonSecureFuncPtr is a pointer to a Non-Secure function with a floating-point parameter.

```

#include <arm_cmse.h>

void __attribute__((cmse_nonsecure_call)) (-nonSecureFuncPtr)(float a);

void SecureFunc1()

{

nonSecureFuncPtr(0.0);

}

```

Build the example code with the -march=armv8.1-m.main -mfpu=fpv5-sp-d16 -mfloat-abi=hard - mcmse build options.

When -secureFunc1- calls -nonSecureFuncPtr-, it causes Security state switch. The following figure shows the actions needed before switching from Secure to Non-Secure state, and the generated assembly code.

#### Figure 4-7: Secure to Non-Secure save flow

The following example code shows a Secure entry point function secureAPI() which calls a sub function secureFunc2(), which can use floating point.

```

#include <arm_cmse.h>

extern void SecureFunc2(void);

void __attribute__((cmse_nonsecure_entry)) SecureAPI()

{

SecureFunc2();

}

```

FPCXT\_NS is saved before other operations in Secure side and restores FPCXT\_NS before returning back to the Non-Secure state. VSCCLRM zeros the specified floating-point registers if there is an active floating-point context, as the following generated assembly code shows.

\_acle\_se\_secureAPI: SecureAPI:

| vstr    | fpcxtns,  | [sp,   | #-8]! |

|---------|-----------|--------|-------|

| push    | {r7, lr}  |        |       |

| bl      | SecureFur | nc2    |       |

| рор     | {r7, lr}  |        |       |

| vscclrm | {s0-s15,  | vpr}   |       |

| vldr    | fpcxtns,  | [sp],  | #8    |

| clrm    | {r0-r3, 1 | :12, a | psr}  |

| bxns    | lr        |        | -     |

SoftFP ABI use with Security extension <code>-mfloat-abi=softfp</code> uses floating point instructions. However, there is no requirement to save and restore the callee floating-point registers, S16-S31. Therefore, these registers can leak secret values when transitioning from Secure to Non-Secure. This applies to both function returns to Non-Secure, and when a secure exception is returning to Non-Secure background code. We recommend that you do not use the SoftFP ABI with the Security Extensions.

## 5. Armv8-M exception model with Security Extension

This guide describes exception handling functionality when Security Extension is implemented in a system. See Armv8-M Exception Model User Guide for details on how exceptions and interrupts are handled in the Armv8-M architecture when Security Extension is not implemented in a system.

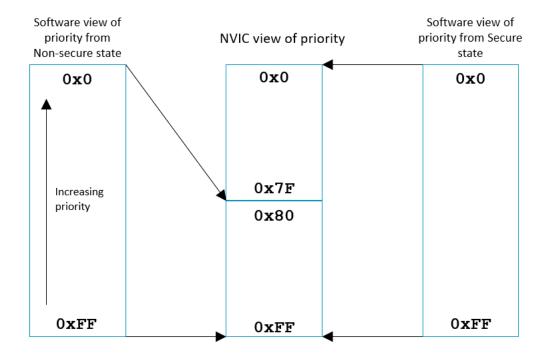

The Security Extensions modify the exception model so that exceptions can be taken directly to the required security state, without compromising the security of the system. Some exceptions are banked between the security states, for example, MemManage Fault. This enables each state to operate independently. Other exceptions have a single instance that can be configured to target either security state, for example, external interrupts. The exception model also allows the priority of critical Secure exceptions to be protected so they cannot be blocked by Non-secure exceptions. The subsequent section explains about the details of the exception model along with security extension.

## 5.1 Prerequisites

We recommend that you fully understand the concepts that the Armv8-M Exception Model User Guide describes.

## 5.2 Target states of exceptions

The following table summarizes the configurability and default target states for interrupts and exceptions available in an Armv8-M processor.

| Exception number | Exception<br>type  | Туре         | Default target state | Notes                                                                                                                                                                                                        |

|------------------|--------------------|--------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | Reset              | Secure only  | Secure               | -                                                                                                                                                                                                            |

| 2                | NMI                | Configurable | Secure               | Configurable by AIRCR.BFHFMNINS bit. However,<br>AIRCR.BFHFNMINS bit should be set to 1 only when<br>Secure state is unused and calling Secure functions or<br>Secure exceptions should be strictly blocked. |

| 3                | HardFault          | Configurable | Secure               | Configurable by AIRCR.BFHFMNINS bit. However,<br>AIRCR.BFHFNMINS bit should be set to 1 only when<br>Secure state is unused and calling Secure functions or<br>Secure exceptions should be strictly blocked  |

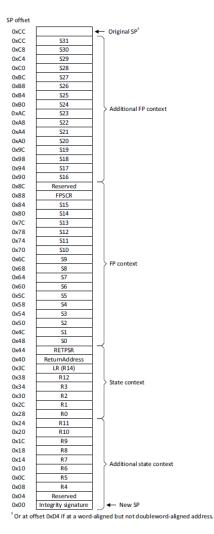

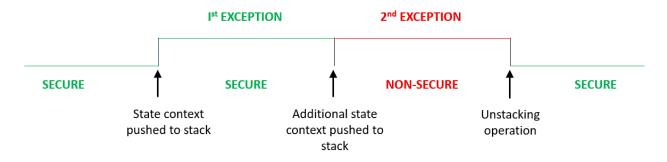

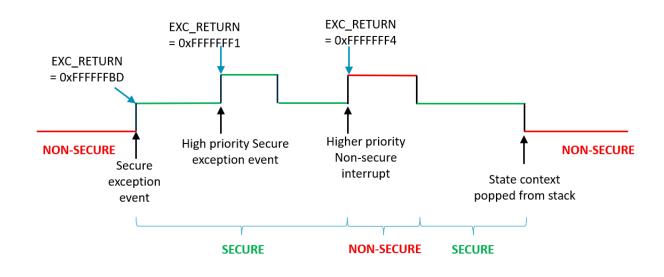

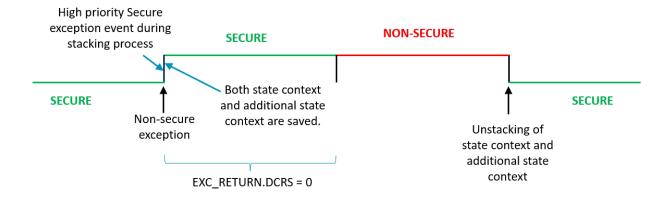

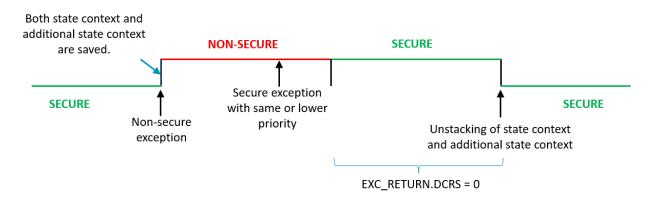

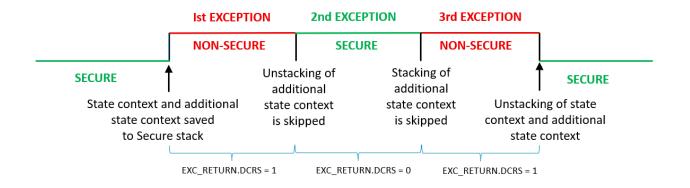

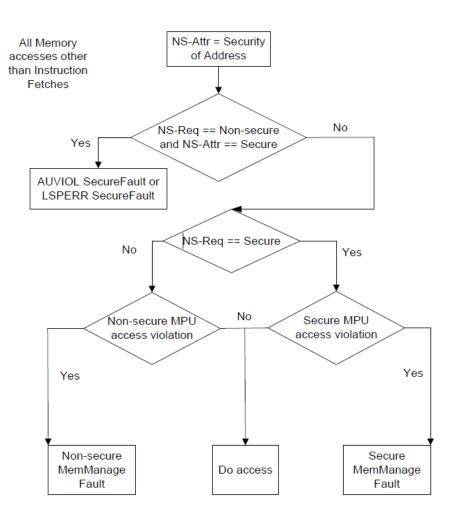

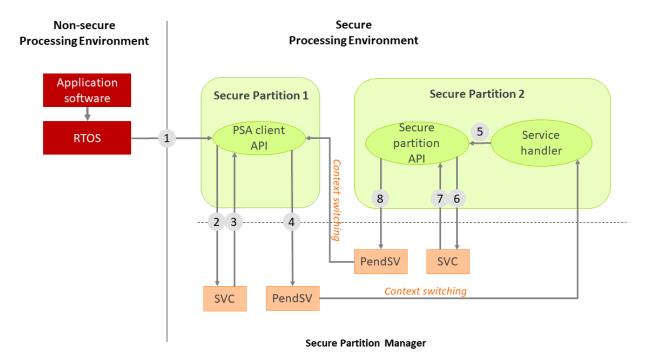

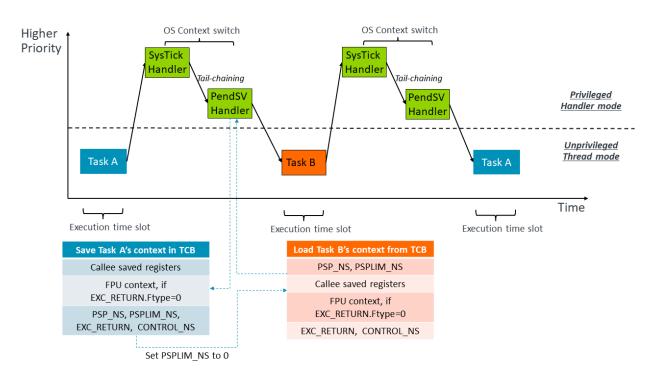

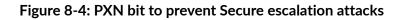

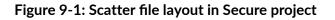

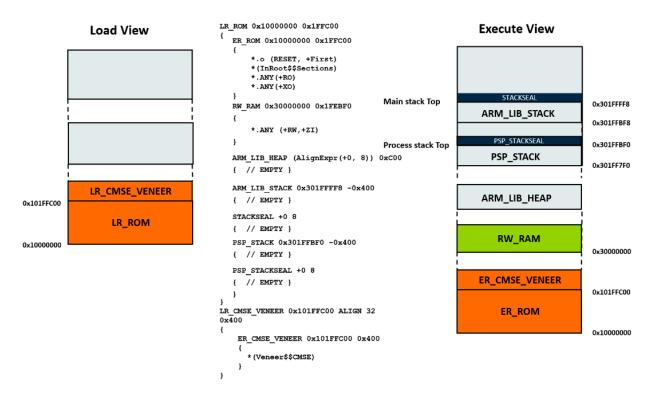

| 4                | MemManage<br>Fault | Banked       | N/a                  | -                                                                                                                                                                                                            |