# **DRTM Architecture for Arm**

Document number: ARM DEN 0113

Release Quality: EAC

Document Version: 1.1

Confidentiality: Non-Confidential

Date of Issue: October 8, 2024

Copyright  $\hbox{@ }$  2022-2024 Arm Limited or its affiliates. All rights reserved.

# Contents

| Abou | ut this o | document   | t                                       | vii  |

|------|-----------|------------|-----------------------------------------|------|

|      | Relea     | se Inform  | nation                                  | vii  |

|      | Arm I     | Non-Conf   | idential Document License ("License")   | ix   |

|      | Refer     | ences      |                                         | хi   |

|      | Term      | s and abb  | previations                             | xii  |

|      | Conv      | entions    |                                         | xiii |

|      |           | Typogr     | raphical conventions                    | xiii |

|      |           | Numbe      | ers                                     | xiii |

|      | Feedl     | oack       |                                         | xiv  |

|      | Inclus    | sive langu | uage commitment                         | xiv  |

| 1    |           | Overvi     | ew of this document                     | 15   |

| 2    |           | DRTM       | architecture overview                   | 16   |

|      | 2.1       | DRTM       | background                              | 16   |

|      | 2.2       | DRTM       | overview                                | 17   |

|      | 2.3       | DRTM       | terms                                   | 18   |

|      |           | 2.3.1      | DCE preamble                            | 18   |

|      |           | 2.3.2      | D-CRTM and DCE                          | 18   |

|      |           | 2.3.3      | DLME                                    | 18   |

|      |           | 2.3.4      | Devices and non-host platforms          | 19   |

|      | 2.4       | DRTM       | on Arm                                  | 19   |

|      |           | 2.4.1      | Overview of DRTM on Arm                 | 19   |

|      |           | 2.4.2      | DRTM SMC functions                      | 20   |

|      | 2.5       | DRTM       | implementations                         | 21   |

|      |           | 2.5.1      | Firmware-backed implementation overview | 21   |

|      |           | 2.5.2      | Hardware-backed implementation overview | 22   |

|      | 2.6       | Differe    | ences from the TCG DRTM specification   | 23   |

|      | 2.7       | DRTM       | and the TPM                             | 23   |

|   |     | 2.7.1  | Firmware-based measurements                           | 24 |

|---|-----|--------|-------------------------------------------------------|----|

|   |     | 2.7.2  | TPM-based measurements                                | 24 |

|   |     | 2.7.3  | TPM PCR usage                                         | 24 |

|   | 2.8 | Memo   | ory protection                                        | 25 |

|   | 2.9 | Securi | ity considerations                                    | 25 |

|   |     | 2.9.1  | Security goals                                        | 25 |

|   |     | 2.9.2  | Security non-goals                                    | 25 |

|   |     | 2.9.3  | Stakeholders                                          | 26 |

|   |     | 2.9.4  | Threats and mitigations                               | 26 |

|   |     | 2.9.5  | Security considerations for stakeholders              | 28 |

| 3 |     | Interf | ace functions and data structures                     | 30 |

|   | 3.1 | Introd | duction to interface functions and data structures    | 30 |

|   | 3.2 | DRTM   | I_VERSION                                             | 31 |

|   |     | 3.2.1  | DRTM_VERSION usage                                    | 31 |

|   |     | 3.2.2  | DRTM_VERSION implementation responsibilities          | 31 |

|   | 3.3 | DRTM   | 1_FEATURES                                            | 32 |

|   |     | 3.3.1  | DRTM_FEATURES usage                                   | 35 |

|   | 3.4 | DRTM   | I_DYNAMIC_LAUNCH                                      | 36 |

|   |     | 3.4.1  | DRTM_DYNAMIC_LAUNCH usage                             | 36 |

|   |     | 3.4.2  | DRTM_DYNAMIC_LAUNCH caller responsibilities           | 37 |

|   |     | 3.4.3  | DRTM_DYNAMIC_LAUNCH implementation responsibilities   | 37 |

|   | 3.5 | DRTM   | I_UNPROTECT_MEMORY                                    | 38 |

|   |     | 3.5.1  | DRTM_UNPROTECT_MEMORY usage                           | 38 |

|   |     | 3.5.2  | DRTM_UNPROTECT_MEMORY implementation responsibilities | 38 |

|   | 3.6 | DRTM   | I_CLOSE_LOCALITY                                      | 39 |

|   |     | 3.6.1  | DRTM_CLOSE_LOCALITY usage                             | 39 |

|   |     | 3.6.2  | DRTM_CLOSE_LOCALITY caller responsibilities           | 39 |

|   |     | 3.6.3  | DRTM_CLOSE_LOCALITY implementation responsibilities   | 40 |

|   | 3.7 |        | 1_GET_ERROR                                           | 41 |

|   |     | 3.7.1  | DRTM_GET_ERROR usage                                  | 41 |

|   |     | 3.7.2  | DRTM_GET_ERROR caller responsibilities                | 41 |

|   |     | 3.7.3  | DRTM GET FRROR implementation responsibilities        | 41 |

|   | 3.8  | 3.8 DRTM_SET_ERROR                                          |    |

|---|------|-------------------------------------------------------------|----|

|   |      | 3.8.1 DRTM_SET_ERROR usage                                  | 42 |

|   |      | 3.8.2 DRTM_SET_ERROR caller responsibilities                | 42 |

|   |      | 3.8.3 DRTM_SET_ERROR implementation responsibilities        | 42 |

|   | 3.9  | DRTM_SET_TCB_HASH                                           | 43 |

|   |      | 3.9.1 DRTM_SET_TCB_HASH usage                               | 43 |

|   |      | 3.9.2 DRTM_SET_TCB_HASH caller responsibilities             | 44 |

|   |      | 3.9.3 DRTM_SET_TCB_HASH implementation responsibilities     | 44 |

|   | 3.10 | DRTM_LOCK_TCB_HASHES                                        | 45 |

|   |      | 3.10.1 DRTM_LOCK_TCB_HASHES usage                           | 45 |

|   |      | 3.10.2 DRTM_LOCK_TCB_HASHES caller responsibilities         | 45 |

|   |      | 3.10.3 DRTM_LOCK_TCB_HASHES implementation responsibilities | 45 |

|   | 3.11 | DRTM error encoding                                         | 46 |

|   | 3.12 | DRTM_PARAMETERS                                             | 47 |

|   | 3.13 | MEMORY_REGION_DESCRIPTOR_TABLE                              | 49 |

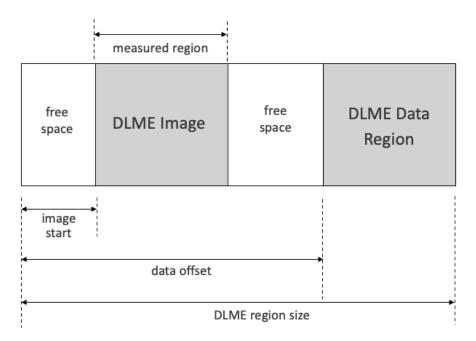

|   | 3.14 | DLME region                                                 | 50 |

|   | 3.15 | TCB_HASH_TABLE                                              | 54 |

|   | 3.16 | DRTM event log                                              | 55 |

|   |      | 3.16.1 DRTM event log requirements                          | 56 |

|   |      | 3.16.2 Event types                                          | 56 |

|   | 3.17 | Return codes                                                | 59 |

| 4 |      | Requirements for DRTM phases                                | 60 |

|   | 4.1  | Non-secure firmware and TCB-critical data                   | 60 |

|   | 4.2  | DCE preamble                                                | 61 |

|   | 4.3  | Dynamic launch event                                        | 62 |

|   | 4.4  | Firmware-backed D-CRTM requirements                         | 63 |

|   | 4.5  | DCE requirements                                            | 66 |

|   |      | 4.5.1 DLME image authentication                             | 71 |

|   | 4.6  | DLME                                                        | 72 |

|   |      | 4.6.1 DLME initial state                                    | 72 |

|   |      |                                                             |    |

|   |      | 4.6.2 DLME operation                | 72 |

|---|------|-------------------------------------|----|

|   | 4.7  | Error handling and remediation      | 74 |

|   | 4.8  | TPM measurements                    | 75 |

|   |      | 4.8.1 TPM measurement requirements  | 75 |

|   |      | 4.8.2 PCR schemas                   | 75 |

|   |      | 4.8.3 Default PCR schema            | 76 |

|   |      | 4.8.4 DLME Authorities PCR schema   | 77 |

| 5 |      | System requirements                 | 79 |

|   | 5.1  | Processing elements                 | 79 |

|   | 5.2  | Multiple sockets                    | 79 |

|   | 5.3  | SMMU and DMA capable devices        | 79 |

|   | 5.4  | Non-host platforms                  | 79 |

|   |      | 5.4.1 GIC                           | 80 |

|   |      | 5.4.2 Hardware trace                | 80 |

|   | 5.5  | Security lifecycle                  | 80 |

|   | 5.6  | ТРМ                                 | 81 |

|   |      | 5.6.1 TPM requirements              | 81 |

|   |      | 5.6.2 Closing localities            | 82 |

|   | 5.7  | ACPI                                | 82 |

|   | 5.8  | DMA protection                      | 83 |

|   | 5.9  | Platform                            | 83 |

|   | 5.10 | Firmware                            | 84 |

|   | 5.11 | Dynamic launch errors               | 84 |

|   | 5.12 | SMCCC and PSCI requirements         | 85 |

|   | 5.13 | Secure services                     | 85 |

| 6 |      | Hardware-backed implementation      | 86 |

|   | 6.1  | Hardware-backed overview            | 86 |

|   | 6.2  | Hardware-backed D-CRTM requirements | 87 |

| 6.3 | Hardv | vare-backed DCE requirements           | 89 |

|-----|-------|----------------------------------------|----|

| 6.4 | Hardv | vare-backed system requirements        | 90 |

|     | 6.4.1 | TPM                                    | 90 |

|     | 6.4.2 | Coprocessor                            | 91 |

|     | 6.4.3 | DMA protection                         | 92 |

| 6.5 | Hardv | vare-backed DRTM function requirements | 92 |

|     | 6.5.1 | DRTM DYNAMIC LAUNCH                    | 92 |

# **About this document**

## **Release Information**

The change history table lists the changes that have been made to this document.

| Date            | Issue | Confidentiality  | Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------|-------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| May 30, 2023    | 1.0   | Non-confidential | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| May 7, 2024     | 1.0B  | Non-confidential | <ul> <li>Minor release</li> <li>Fixed error in memory region descriptor caching attribute list</li> <li>Clarified usage of the Region type field in memory region descriptors</li> <li>Clarification update to DLME data diagram</li> <li>Minor editorial edits</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| October 8, 2024 | 1.1   |                  | <ul> <li>Minor version release</li> <li>Further defined optional image authentication:</li> <li>Defined the requirements of the implementation</li> <li>Advertisement in DRTM_FEATURES</li> <li>New error code</li> <li>New bit in DRTM_PARAMETERS, bump revision of this data structure to 2</li> <li>Additional measurements and event types</li> <li>New DLME Authorities PCR schema</li> <li>Added new ARM_NO_ACTION event type</li> <li>DRTM_DYNAMIC_LAUNCH: clarified behavior on success</li> <li>DRTM_DYNAMIC_LAUNCH: explicitly which error codes to return for different error cases</li> <li>Clarified that errors during D-CRTM phase 1 must return errors to the caller</li> <li>DRTM_UNPROTECT_MEMORY: added return code for success, clarified behavior if there are back-to-back calls</li> <li>DRTM_SET_TCB_HASH: clarified implementation behavior for OUT_OF_RESOURCES</li> <li>Clarified that errors in the DRTM_PARAMETERS must be returned to the caller</li> <li>Clarified that functions may return other return codes in addition to those explicitly defined in the function argument table.</li> </ul> |

- Clarified the tight coupling of a Normal world DCE to the Secure DRTM implementation

- For DCE public key measurement clarified which key is to be measured

- For all measurements, explicitly define which event type to use

- Updated system requirement for TPM

- Hardware backed DRTM: updated cases where DRTM returns errors to the caller to align with D-CRTM phase 1 in firmware-backed

- Editorial edits

### **DRTM Architecture for Arm**

Copyright ©2022-2024 Arm Limited or its affiliates. All rights reserved. The copyright statement reflects the fact that some draft issues of this document have been released, to a limited circulation.

### Arm Non-Confidential Document License ("License")

This License is a legal agreement between you and Arm Limited ("Arm") for the use of Arm's intellectual property (including, without limitation, any copyright) embodied in the document accompanying this License ("Document"). Arm licenses its intellectual property in the Document to you on condition that you agree to the terms of this License. By using or copying the Document you indicate that you agree to be bound by the terms of this License.

"Subsidiary" means any company the majority of whose voting shares is now or hereafter owned or controlled, directly or indirectly, by you. A company shall be a Subsidiary only for the period during which such control exists.

This Document is **NON-CONFIDENTIAL** and any use by you and your Subsidiaries ("Licensee") is subject to the terms of this License between you and Arm.

Subject to the terms and conditions of this License, Arm hereby grants to Licensee under the intellectual property in the Document owned or controlled by Arm, a non-exclusive, non-transferable, non-sub-licensable, royalty-free, worldwide License to:

- (i) use and copy the Document for the purpose of designing and having designed products that comply with the Document;

- (ii) manufacture and have manufactured products which have been created under the License granted in (i) above; and

- (iii) sell, supply and distribute products which have been created under the License granted in (i) above.

Licensee hereby agrees that the Licenses granted above shall not extend to any portion or function of a product that is not itself compliant with part of the Document.

Except as expressly licensed above, Licensee acquires no right, title or interest in any Arm technology or any intellectual property embodied therein.

The content of this document is informational only. Any solutions presented herein are subject to changing conditions, information, scope, and data. This document was produced using reasonable efforts based on information available as of the date of issue of this document. The scope of information in this document may exceed that which Arm is required to provide, and such additional information is merely intended to further assist the recipient and does not represent Arm's view of the scope of its obligations. You acknowledge and agree that you possess the necessary expertise in system security and functional safety and that you shall be solely responsible for compliance with all legal, regulatory, safety and security related requirements concerning your products, notwithstanding any information or support that may be provided by Arm herein. In addition, you are responsible for any applications which are used in conjunction with any Arm technology described in this document, and to minimize risks, adequate design and operating safeguards should be provided for by you.

Reference by Arm to any third party's products or services within this document is not an express or implied approval or endorsement of the use thereof.

THE DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. Arm may make changes to the Document at any time and without notice. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

NOTWITHSTANDING ANYTHING TO THE CONTRARY CONTAINED IN THIS LICENSE, TO THE FULLEST EXTENT PERMITTED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, IN CONTRACT, TORT OR OTHERWISE, IN CONNECTION WITH THE SUBJECT MATTER OF THIS LICENSE (INCLUDING WITHOUT LIMITATION) (I) LICENSEE'S USE OF THE DOCUMENT; AND (II) THE IMPLEMENTATION OF THE DOCUMENT IN ANY PRODUCT CREATED BY LICENSEE UNDER THIS LICENSE). THE EXISTENCE OF MORE THAN ONE CLAIM OR SUIT WILL NOT ENLARGE OR EXTEND THE LIMIT. LICENSEE RELEASES ARM FROM ALL OBLIGATIONS, LIABILITY, CLAIMS OR DEMANDS IN EXCESS OF THIS LIMITATION.

This License shall remain in force until terminated by Licensee or by Arm. Without prejudice to any of its other rights, if Licensee is in breach of any of the terms and conditions of this License then Arm may terminate this License immediately upon giving written notice to Licensee. Licensee may terminate this License at any time. Upon termination of this Licensee by Licensee or by Arm, Licensee shall stop using the Document and destroy all copies of the Document in its possession. Upon termination of this License, all terms shall survive except for the License grants.

Any breach of this License by a Subsidiary shall entitle Arm to terminate this License as if you were the party in breach. Any termination of this License shall be effective in respect of all Subsidiaries. Any rights granted to any Subsidiary hereunder shall automatically terminate upon such Subsidiary ceasing to be a Subsidiary.

The Document consists solely of commercial items. Licensee shall be responsible for ensuring that any use, duplication or disclosure of the Document complies fully with any relevant export laws and regulations to assure that the Document or any portion thereof is not exported, directly or indirectly, in violation of such export laws.

This License may be translated into other languages for convenience, and Licensee agrees that if there is any conflict between the English version of this License and any translation, the terms of the English version of this License shall prevail.

The Arm corporate logo and words marked with ® or ™ are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. No License, express, implied or otherwise, is granted to Licensee under this License, to use the Arm trade marks in connection with the Document or any products based thereon. Visit Arm's website at <a href="https://www.arm.com/company/policies/trademarks">https://www.arm.com/company/policies/trademarks</a> for more information about Arm's trademarks.

The validity, construction and performance of this License shall be governed by English Law.

Copyright © 2024 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England. 110 Fulbourn Road, Cambridge, England CB1 9NJ.

Arm document reference: PRE-21585 version 5.0, March 2024

# **References**

This document refers to the following documents.

| Ref  | <b>Document Number</b> | Title                                                                                                          |

|------|------------------------|----------------------------------------------------------------------------------------------------------------|

| [1]  | Arm DDI 0487           | Arm® Architecture Reference Manual for A-profile architecture                                                  |

| [2]  | Arm DEN 0022D          | Power State Coordination Interface                                                                             |

| [3]  | Arm DEN 0028D          | SMC Calling Conventions                                                                                        |

| [4]  |                        | TCG D-RTM Architecture, Version 1.0.0, June 17, 2013                                                           |

| [5]  | Arm DEN 0072           | Platform Security Boot Guide                                                                                   |

| [6]  |                        | TCG PC Client Platform Firmware Profile Specification, Family "2.0", Level 00, Revision 1.06, December 4, 2023 |

| [7]  | Arm DEN 0094A          | Arm® Base System Architecture 1.0                                                                              |

| [8]  |                        | Trusted Platform Module Library Specification, Family "2.0", Level 00, Revision 01.59 – November 2019          |

| [9]  |                        | TCG PC Client Platform TPM Profile Specification for TPM 2.0, Version 1.05, September 4, 2020                  |

| [10] | Arm DEN 0044A          | Arm® Base Boot Requirements 1.0                                                                                |

| [11] |                        | TCG Glossary, Version 1.1, Revision 1.00, May 11, 2017                                                         |

| [12] |                        | TCG Algorithm Registry, Family "2.0", Level 00, Revision 01.32 June 25, 2020                                   |

| [13] |                        | Advanced Configuration and Power Interface (ACPI) Specification, Version 6.4, January 2021.                    |

| [14] | Arm IHI 0069G          | Arm Generic Interrupt Controller Architecture Specification, GIC architecture version 3 and version 4          |

## **Terms and abbreviations**

This document uses the following terms and abbreviations.

| Term                                                                                                                                                                   | Meaning                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Application PE                                                                                                                                                         | The term application PE refers to a PE used by the operating system or hypervisor to execute user applications or kernel threads.                                                                                                                        |

| Boot PE                                                                                                                                                                | The boot PE is the PE designated by hardware to boot the system following reset.                                                                                                                                                                         |

|                                                                                                                                                                        | In this architecture it is the boot PE that initiates and performs the dynamic launch and executes the phases of DRTM. All other PEs besides the boot PE are "off" during DRTM.                                                                          |

| CRTM                                                                                                                                                                   | Core Root of Trust for Measurement                                                                                                                                                                                                                       |

| DCE                                                                                                                                                                    | DRTM Configuration Environment                                                                                                                                                                                                                           |

| D-CRTM                                                                                                                                                                 | Dynamic Core Root of Trust for Measurement                                                                                                                                                                                                               |

| Device                                                                                                                                                                 | A peripheral or controller that can be excluded from the TCB of the system through DMA protection hardware such as an SMMU.                                                                                                                              |

| DLME                                                                                                                                                                   | Dynamically Launched Measured Environment                                                                                                                                                                                                                |

| DRTM                                                                                                                                                                   | Dynamic Root of Trust for Measurement                                                                                                                                                                                                                    |

| Locality                                                                                                                                                               | Locality is a mechanism in a TPM that supports a privilege hierarchy for clients of the TPM. The platform in a system enforces access to the TPM so that clients can only access localities they have the privilege to access.                           |

| Non-Host Platform                                                                                                                                                      | A peripheral or controller in a system that has no DMA-protections and cannot be restricted from reading or writing the DCE or DLME.                                                                                                                     |

| Non-application PE                                                                                                                                                     | A Non-application PE is a PE that is not an application PE.                                                                                                                                                                                              |

| Normal world                                                                                                                                                           | The Non-secure privilege levels (Non-secure ELO, EL1, and EL2) and resources, for example memory, registers, and devices, that are not part of the Secure world.                                                                                         |

| Normal world DCE                                                                                                                                                       | A DCE component that executes at a Non-secure privilege level.                                                                                                                                                                                           |

| PCR                                                                                                                                                                    | Platform Configuration Register. A protected location within a TPM containing a digest of integrity measurements.                                                                                                                                        |

| PE Processing element. This is the term used for a CPU core in the Arm v8-A architecture. In this specification, unless otherwise stated, the term PE rapplication PE. |                                                                                                                                                                                                                                                          |

| RTM Root of trust for measurement. The Root of Trust that makes the initial integration measurement in a measured boot flow.                                           |                                                                                                                                                                                                                                                          |

| Secure world                                                                                                                                                           | The environment that is provided by the Secure privilege levels in the Arm v8-A architecture, S-EL0, S-EL1, S-EL2, EL3, and the resources, for example memory, registers, and devices, that are accessible exclusively from the Secure privilege levels. |

DEN 0113

| SRTM | Static root of trust for measurement. From the TCG glossary [11]: An RTM where the initial integrity measurement occurs at platform reset. The SRTM is static because the PCRs associated with it cannot be re-initialized without a platform reset. |  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ТСВ  | Trusted computing base                                                                                                                                                                                                                               |  |

| TPM  | Trusted Platform Module. A security module that is defined by TCG.                                                                                                                                                                                   |  |

| TCG  | Trusted Computing Group                                                                                                                                                                                                                              |  |

| UEFI | Unified Extensible Firmware                                                                                                                                                                                                                          |  |

### **Conventions**

### **Typographical conventions**

The typographical conventions are:

italic

Introduces special terminology, and denotes citations.

#### bold

Denotes signal names, and is used for terms in descriptive lists, where appropriate.

monospace

Used for assembler syntax descriptions, pseudocode, and source code examples.

Also used in the main text for instruction mnemonics and for references to other items appearing in assembler syntax descriptions, pseudocode, and source code examples.

#### SMALL CAPITALS

Used for some common terms such as IMPLEMENTATION DEFINED.

Also used for a few terms that have specific technical meanings, and are included in the Glossary.

#### Red text

Indicates an open issue.

#### Blue text

Indicates a link, which can be:

- A cross-reference to another location within the document.

- A URL, for example http://infocenter.arm.com.

#### **Numbers**

Numbers are normally written in decimal. Binary numbers are preceded by 0b, and hexadecimal numbers by 0x. In both cases, the prefix and the associated value are written in a monospace font, for example 0xFFFFF0000. To improve readability, long numbers can be written with an underscore separator between every four characters, for example 0xFFFFF 0000 0000 0000. Ignore any underscores when interpreting the value of a number.

### **Feedback**

Arm welcomes feedback on this product and its documentation. To provide feedback on the product, create a ticket on https://support.developer.arm.com.

To provide feedback on the document, fill the following survey: https://developer.arm.com/documentation-feedback-survey.

### **Inclusive language commitment**

Arm values inclusive communities. Arm recognizes that we and our industry have used language that can be offensive. Arm strives to lead the industry and create change.

This document includes language that can be offensive. We will replace this language in a future issue of this document.

To report offensive language in this document, email terms@arm.com.

# 1 Overview of this document

This specification defines an architecture for Dynamic Root of Trust for Measurement (DRTM) for processors based on the Arm A-profile architecture. This specification is based on concepts from the TCG D-RTM Architecture [4], but functions as a self-contained, standalone document. It uses the principles and terminology of the TCG architecture but contains significant differences as well.

The specification is structured as follows:

- Section 2, DRTM architecture overview, describes DRTM in general and an introduction to how this architecture maps DRTM to Arm-based systems. This section includes a description of differences with the TCG-defined architecture. This section also covers the security scope of DRTM on Arm and identifies threats that are in and out of scope.

- Section 3, Interface functions and data structures, describes the Secure world ABIs needed to implement DRTM on Arm.

- Section 4, Requirements for DRTM phases, describes the normative requirements that each phase of the DRTM process must comply with.

- Section 5, System requirements, describes the system-level assumptions and requirements that must be in place for a system to support the DRTM on Arm architecture.

- Section 6, Hardware-backed implementation, describes requirements specific to a hardware-backed implementation of DRTM.

In this specification, tables with requirement IDs describe the normative requirements. These requirements are distinct from the supporting informative text. The informative text provides more context to help clarify the rationale for each requirement.

# 2 DRTM architecture overview

### 2.1 DRTM background

The Trusted Computing Base (TCB) of a system consists of all hardware, firmware, and software components that are relied on to enforce the security of the system. A compromise in any TCB component affects the security posture of the entire system.

The integrity of the software TCB for a system is typically established during boot. The boot process begins in an immutable bootloader component, for example a boot ROM that loads the first mutable firmware image. Before transferring control to the loaded image a cryptographic digest of the image is computed. This digest is known as a *measurement*. That measurement might be:

- Immediately verified using a digital signature

- Securely stored in a Trusted Platform Module (TPM) for later use in security policies

The process is repeated for each loaded image in the boot chain. Critical data can be measured as well. This process forms a chain of trust that is anchored in the immutable bootloader. The chain of trust continues through all code that is executed up to the runtime environment such as a hypervisor or OS kernel.

Measured boot is a boot chain where the measurements taken during the boot process are stored securely in a root of trust for storage such as a TPM. The code in the boot ROM that begins the chain of trust is called the Core Root of Trust for Measurement (CRTM). When the CRTM executes on a processor, it is referred to as the Root of Trust for Measurement (RTM).

In measured boot flow typical boot stages include:

- Processor execution beginning with the CRTM

- Loading and executing other bootloader stages

- Executing UEFI firmware

- Executing an OS loader

- Launching the OS kernel or hypervisor

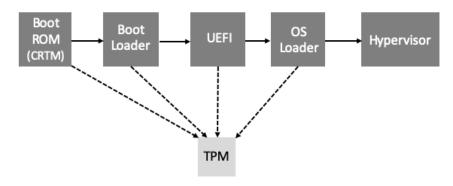

The measurements of each stage are recorded in Platform Configuration Registers (PCRs) of a TPM. These PCRs (0-15) are referred to as *static* PCRs because they cannot be re-initialized without a platform reset. The RTM in this boot flow is called the Static Root of Trust for Measurement (SRTM). See example in Figure 1.

Figure 1: Example SRTM boot flow

In an SRTM boot flow every component loaded up to and including the OS kernel is measured in the static PCRs and becomes part of the system's TCB. The PCRs allow a system to attest to what software is running on the system and enables security policies such as allowing access to sealed secrets in the TPM only when the PCRs reflect that the TCB has integrity.

#### 2.2 DRTM overview

Establishing an attestable TCB becomes difficult when the number of components in the boot chain grows or when firmware is dynamically extensible, for example by loading drivers from add-in peripherals. The larger and more complex the TCB, the greater the attack surface and the risk of untrusted code executing which can compromise security.

For example, UEFI is an extensible boot loader, where multiple EFI programs might run during the Boot Services phase. The EFI programs can include drivers, device option ROMs, and a bootloader. If compromised, these programs might be able to further compromise the target OS by tampering with the OS's code or data.

Dynamic Root of Trust for Measurement (DRTM) begins a new chain of trust by measuring and executing a protected payload. The newly started chain of trust results in a smaller TCB. DRTM is implemented by a trusted agent that ensures the following:

- All cores are placed in a known state

- The target payload is protected against modification

- A single core measures and begins running the payload

- Execution is confined to the payload

- The payload is provided with data that can be used to validate key properties of the system

When the system has been running, the same mechanism can be used again to return execution to a new measured payload without a system reset.

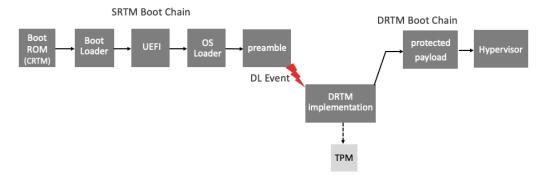

The event that initiates DRTM is referred to as the *Dynamic Launch Event* or DL Event.

A TPM device holds the measurements made during the dynamic launch, and these measurements are used by the launched payload to enforce a system-specific security policy. The TPM architecture defines a set of PCRs that are considered dynamic. Unlike the static PCRs used in the SRTM boot flow, the dynamic PCRs can be reset by a DL Event. This feature allows DRTM to be initiated multiple times without a system reset.

Figure 2 shows the SRTM boot chain ending with the DL Event which launches the DRTM boot chain.

Figure 2: SRTM and DRTM boot chain illustration

**DEN 0113**

A key goal of DRTM is that the new TCB established by the DRTM boot chain does not have a trust dependency on the SRTM trust chain or anything else which executed before the DL Event. A dynamic launch can be initiated any number of times on a running system.

#### 2.3 DRTM terms

### 2.3.1 DCE preamble

The preamble block shown in Figure 2 is referred to as the *DRTM Configuration Environment (DCE) Preamble*. The DCE Preamble prepares the platform for DRTM by:

- Doing any needed configuration

- Loading the target payload image

- Preparing input parameters needed by DRTM

- Invoking the DL Event to start the dynamic launch

The DCE Preamble is closely coupled with the launched payload. It is typically supplied by the OS-provider or might conform to a standardized boot protocol.

#### 2.3.2 D-CRTM and DCE

A DRTM implementation is composed of two logical components:

- The Dynamic Core Root of Trust for Measurement (D-CRTM)

- The DRTM Configuration Environment (DCE).

The D-CRTM and DCE are supplied by the silicon provider or OEM.

The D-CRTM is the trust anchor, or root of trust, for the DRTM boot sequence and is where the dynamic launch starts. The D-CRTM must be implemented in a trusted agent in the system. The D-CRTM initializes the TPM for DRTM and prepares the environment for the next stage of DRTM, the DCE. The D-CRTM:

- Measures the DCE

- Verifies its signature

- Transfers control to it

The DCE executes on an application core. The DCE:

- Verifies the state of the system

- Measures security-critical attributes of the system

- Prepares the memory region for the target payload

- Measures the payload

- Transfers control to the payload

#### 2.3.3 DLME

The protected payload is referred to as the *Dynamically Launched Measured Environment*, or DLME. The DLME begins execution in a safe state, with a single thread of execution, DMA protections, and interrupts disabled. The DCE provides data to the DLME that it can use to verify the configuration of the system. The trustworthy

measurements made by the dynamic launch can be used to implement a system-specific security policy. The policy decides whether the system is in the expected state.

The DLME can be an operating system-specific component supplied by the same vendor that provided the DCE Preamble, or it can conform to a standardized boot protocol.

#### 2.3.4 Devices and non-host platforms

The TCG DRTM architecture differentiates between two types of devices or controllers in a system that are capable of DMA. A *peripheral* is a device or controller that can be excluded from the TCB of the system through DMA protection hardware such as an IOMMU. A device or controller in a system that has no DMA-protections and cannot be restricted from reading or writing the DCE or DLME is referred to as a *non-host platform*. A non-host platform is trusted and is part of the system's TCB.

In this specification *device* refers to peripherals as defined in the preceding paragraph. The term non-host platform has the same usage as in the TCG specification.

#### 2.4 DRTM on Arm

#### 2.4.1 Overview of DRTM on Arm

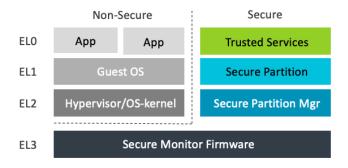

Armv8-A processors have two security states: Secure and Non-Secure. Figure 3 shows the two security states.

Figure 3: Exception levels and security states example

As section 2.2 describes, the objective of DRTM is to begin a new chain of trust and instantiate a smaller TCB that excludes untrusted and arbitrarily extensible components. DRTM does this by measuring and launching a protected payload.

The scope of DRTM on Arm is the Non-secure side of the processor. The launch and execution of the protected payload occurs at the highest Non-secure privilege level. The Secure privilege levels are not affected by DRTM.

A typical boot scenario for DRTM is for a Normal world OS loader to initiate a dynamic launch after loading OS images.

A DRTM implementation on Arm provides the following security guarantee:

- A trustworthy measurement is made of the DLME image and security relevant state into the TPM.

- The DLME image is launched in a safe state:

- o Single thread of execution on the boot PE. All other PEs are off

- Asynchronous Non-secure interrupts and exceptions are disabled

- The DLME region is protected against DMA

- Data needed by DLME to establish the new TCB is provided. The data includes:

- A trustworthy map of the system's memory

- An event log with the measurements made during the dynamic launch

- Trustworthy ACPI tables or hashes of ACPI tables, which can be used by the DLME to validate the ones provided by Non-secure firmware

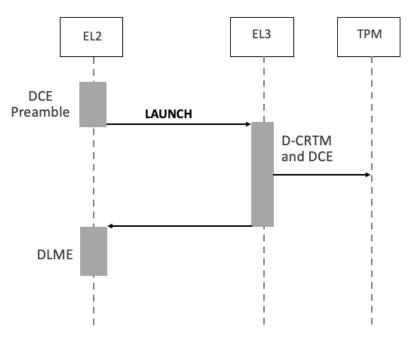

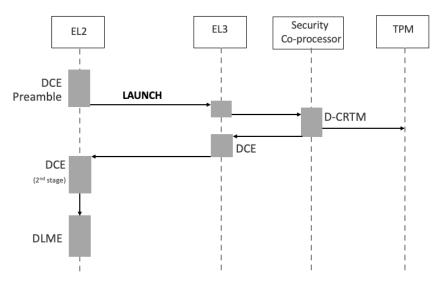

The architecture defines a new SMC function to initiate the dynamic launch. Figure 4 shows one example of how DRTM components interact in an implementation of DRTM. Section 2.5 describes possible implementation approaches.

Figure 4: Example dynamic launch flow on Arm

#### 2.4.2 DRTM SMC functions

This architecture defines a set of SMC functions which provide the interfaces needed by the Normal world DRTM client to perform initialization and initiate a DRTM dynamic launch.

Table 1 shows a summary of the DRTM SMC functions.

Table 1: DRTM functions

| Function              | Description                                                                                                                     |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------|

| DRTM_VERSION          | Returns the version of the DRTM implementation. See section 3.2.                                                                |

| DRTM_FEATURES         | Allows a client to query the DRTM implementation to determine the supported DRTM capabilities of the platform. See section 3.3. |

| DRTM_DYNAMIC_LAUNCH   | Initiates a dynamic launch. See section 3.4.                                                                                    |

| DRTM_UNPROTECT_MEMORY | Removes the memory protection put in place by the dynamic launch. See section 3.5.                                              |

| DRTM_CLOSE_LOCALITY   | Closes a locality in the TPM. See section 3.6.                                                                                  |

| DRTM_GET_ERROR        | Returns an error code from the previous dynamic launch. See section 3.7.                                                        |

| DRTM_SET_ERROR       | Sets a DRTM error code indicating that a dynamic launch has failed. See section 3.8.                                 |

|----------------------|----------------------------------------------------------------------------------------------------------------------|

| DRTM_SET_TCB_HASH    | Used by firmware to record hashes of components of the TCB of the system before the dynamic launch. See section 3.9. |

| DRTM_LOCK_TCB_HASHES | Used by firmware to prevent further hashes from being recorded. See section 3.10.                                    |

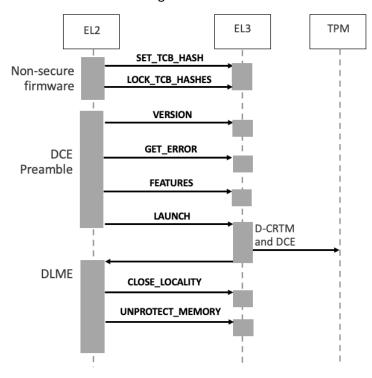

Figure 5 shows an example of how the functions might be used.

Figure 5: Example of SMC function usage

### 2.5 DRTM implementations

As section 2.3.2 describes, the D-CRTM must be in a trusted agent in the system. This specification describes two approaches to implementation of the D-CRTM: firmware-backed and hardware-backed.

#### 2.5.1 Firmware-backed implementation overview

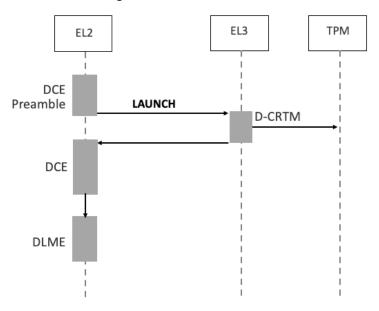

In a firmware-backed implementation the D-CRTM is implemented in secure firmware. How other DRTM components in a firmware implementation map to Arm v8 privilege levels is implementation-dependent and is not specified by this architecture. The architecture permits flexibility where the D-CRTM and DCE are implemented. Options include:

- A firmware implementation where the D-CRTM and the DCE are implemented together at EL3 as shown in Figure 4.

- A firmware implementation where the DCE is located completely in Non-secure firmware as shown in Figure 6.

• An implementation where an initial stage of the DCE is in Secure firmware and a second stage DCE is in Non-secure firmware as shown in Figure 7.

Figure 6: Firmware-backed implementation dynamic launch

### 2.5.2 Hardware-backed implementation overview

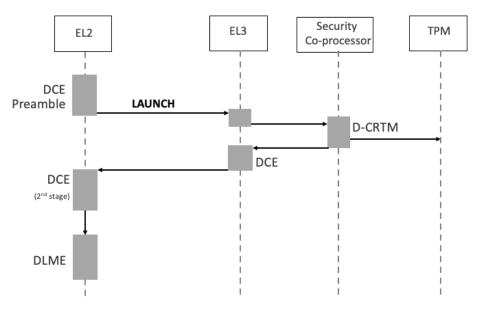

In a hardware-backed implementation, the D-CRTM is in a coprocessor separate from the PE that initiated the dynamic launch. A hardware-backed implementation provides a root of trust with a smaller footprint and a higher level of assurance than a firmware-backed implementation. Section 6 describes requirements for a hardware-backed implementation.

Figure 7 shows how DRTM components might map to PE privilege levels and the security coprocessor in a hardware-backed implementation.

Figure 7: Hardware-backed implementation dynamic launch

**DEN 0113**

### 2.6 Differences from the TCG DRTM specification

As the overview in section 1 describes, this specification is based on concepts from the TCG D-RTM Architecture [4]. The following are differences between the DRTM on Arm architecture compared to the TCG architecture:

- This architecture uses a different convention for PCR usage, and the terminology of PCR.Authorities,

PCR.Details, and PCR.DLME.Authority defined by the TCG architecture is not used.

- This architecture supports the concept of closing localities, which is not defined by TCG.

- The concept of Sensitive Resources defined in the TCG architecture is not used, as the Arm v8-A Secure exception levels protect these kinds of resources.

- Except for the TPM event log, data structures defined by the TCG architecture are not used:

- DRTM Resources Table and Resource Description structure. The DLME data (see section 3.12) provides equivalent functionality.

- DRTM PUBLIC KEY

- DLME\_DESCRIPTOR. This structure is replaced by the DRTM parameters. See section 3.12.

- DLME\_ARGUMENTS. This structure is replaced by the DLME data. See section 3.14.

- o DLME\_TRANSLATION\_LIST structure.

- This architecture does not define DLME Exit.

#### 2.7 DRTM and the TPM

This architecture defines requirements for measurements that must be made by the DRTM implementation into a TPM during the dynamic launch. The TPM implementation must comply with the appropriate TCG specifications. See details in section 5.6. The TPM must support the dynamic localities designed for use with DRTM.

A platform must have hardware protections in place so that access to the dynamic localities of the TPM can be restricted to components with access rights to those localities. It must not be possible for software at Non-secure privilege levels to access locality 4. For a firmware-backed implementation of DRTM, a typical approach for managing the TPM is to use a Secure world TPM service where the service mediates access to the dynamic localities.

For a hardware-backed implementation, there is a requirement that platforms provide hardware enforcement of access to locality 4. This ensures that no component in the system can access locality 4 except the D-CRTM in the security coprocessor.

For a firmware-backed implementation of DRTM, you can use a firmware TPM that runs as a Secure service.

This architecture includes the concept of *closing* a dynamic locality. The dynamic localities are used in sequence by phases of DRTM: The D-CRTM uses locality 4, the DCE uses locality 3, and the DLME uses locality 2. When a given phase of DRTM is completed, access to the associated locality is closed. After a locality is closed, commands sent to the TPM through the closed locality results in an error until the next system reset or DL Event.

Section 5.6 describes the system-level requirements for a TPM implementation.

This architecture supports two approaches to the measurements made during the dynamic launch:

1) Firmware-based measurements

#### 2) TPM-based measurements

Sections 2.7.1 to 2.7.3 provide further details.

#### 2.7.1 Firmware-based measurements

The default approach is for the D-CRTM and DCE to implement a software-based digest algorithm for computing measurements. A measurement is computed and then extended into the TPM using the command TPM2\_PCR\_Extend.

The firmware-based measurement approach must be supported by a DRTM implementation.

A DRTM client can discover the firmware-based digest algorithm used through the DRTM\_FEATURES function. See section 3.3.

#### 2.7.2 TPM-based measurements

A DRTM implementation can optionally support TPM-based measurements. With TPM-based measurements, the D-CRTM and DCE make measurements using the TPM command TPM2\_PCR\_Event. TPM2\_PCR\_Event sends the data to be measured to the TPM and the digest computation is performed by the TPM. TPM2\_PCR\_Event extends the measurements for all digest algorithms supported by the TPM.

A DRTM client can discover whether TPM-based measurements are supported using the DRTM\_FEATURES function. See section 3.3.

A DRTM client can request TPM-based measurements through the DRTM\_PARAMETERS data structure passed to DRTM\_DYNAMIC\_LAUNCH. See section 3.12.

With the TPM-based measurements, the TPM makes the measurements with all supported hash algorithms. Measurements made with all algorithms provides an advantage because the DRTM client has maximum flexibility in choosing which digest algorithm to base a security policy on. The only limitation is the algorithms supported by the TPM.

A disadvantage of the TPM-based approach is that it can be slower than the firmware-based approach. A discrete TPM chip does not have as much processing power as an Arm v8-A PE, and the TPM must compute digests for all algorithms that it supports.

#### 2.7.3 TPM PCR usage

This architecture can support flexibility in which TPM PCRs are used for measurements made by the D-CRTM and DCE through PCR usage schemas. The available PCR usage schemas are advertised through the DRTM\_FEATURES function. See section 3.3.

When a client invokes DRTM\_DYNAMIC\_LAUNCH, the client requests a supported schema through a field in the DRTM\_PARAMETERS. See section 3.12.

Table 2 shows a summary of the default schema. Section 4.8.2 describes the schema details.

Table 2: Default PCR usage schema

| PCR | Usage                                                                                                    |  |

|-----|----------------------------------------------------------------------------------------------------------|--|

| 17  | Measurements of DCE components, platform state, and any Secure firmware components reloaded during DRTM. |  |

| 18  | Measurement of the public key that signed any DCE components.  Measurement of the DLME.                  |  |

### 2.8 Memory protection

A key security requirement of this architecture is that the DLME is protected from DMA by devices during the dynamic launch. The DLME might need to measure and validate supplemental images, and these images must also be protected from DMA. The DLME and supplemental images all reside in Non-secure memory.

The DCE preamble must set up hardware-based DMA memory protections using the DRTM\_PARAMETERS. See section 3.12. The architecture allows for multiple types of memory protections, and the types supported by an implementation can be discovered using the function DRTM\_FEATURES. See section 3.3. The architecture currently supports the following protection types:

- Complete DMA protection is hardware-based enforcement at the SMMU that blocks all DMA from Non-secure devices.

- Region-based DMA protection is a platform-specific mechanism that provides hardware-based enforcement of DMA accesses for a number of protected memory regions. Region-based DMA protection enables a system to support active DMA during the dynamic launch process to memory that is outside the protected regions.

The DRTM implementation of DRTM\_DYNAMIC\_LAUNCH puts the requested memory protections in place before transitioning to the DLME. After the DLME has made any needed measurements or completed other steps to verify the state of the system, the DLME removes the memory protections using the DRTM\_UNPROTECT\_MEMORY function.

### 2.9 Security considerations

As section 2.2 describes, DRTM instantiates a smaller TCB in the Non-secure security state that excludes untrusted and arbitrarily extensible components by measuring and launching a protected payload, the DLME.

This section describes the assets that a DRTM implementation protects along with threats to those assets and corresponding mitigations. The responsibilities of key stakeholders are also identified.

The assets in scope are the DLME, the TPM, and components that comprise the DRTM implementation.

#### 2.9.1 Security goals

The key security goal of DRTM is ensuring the integrity of the DLME and its execution environment by:

- Providing reliable measurements of the DLME and key system properties in a TPM device

- Providing a protected environment for the DLME to begin execution in and defend itself

The measurements are then used by the DLME or OS to enforce a security policy.

### 2.9.2 Security non-goals

There is no security goal related to confidentiality in the DRTM architecture, as DRTM does not protect or use secrets. However, DRTM depends on a TCG-compliant TPM implementation that does have confidentiality requirements. If the TPM implementation can be compromised, any DRTM-based security policy can also be compromised.

There is no security goal related to availability in the DRTM architecture. It is assumed that the adversary is in control of the component that initiates the dynamic launch and the target payload. If their goal is denial of service, the adversary can skip initiating the dynamic launch.

The following are not security goals of this architecture:

• Attacks against the availability of a system

- Defense against compromises in components within the same security boundary as the D-CRTM. In firmware-backed DRTM this includes Secure world firmware components and services, Secure devices that can be DMA-capable, and Non-host platforms. In hardware-backed DRTM this includes the security coprocessor.

- Physical attacks against the TPM, including physical man-in-the-middle attacks

- Glitches of the SoC power supply or clocks during DRTM to bypass verification checks

- Laboratory attacks in which devices are unpackaged and probed

#### 2.9.3 Stakeholders

The following are stakeholders who each have roles in implementing the architecture:

- Silicon providers: provides silicon and potentially firmware components

- OEM or ODM: designs and manufactures the system and integrates firmware

- OSV: operating system or hypervisor provider

- End user: for example a cloud service provider that integrates components from OEM and OSV and defines a DRTM-based security policy for booting an OS

### 2.9.4 Threats and mitigations

Table 3 and Table 4 describe the threats in scope for this architecture, including mitigations addressed by the architecture.

Table 3: Threats in scope

| Threat                                                                                                                                                                                                                                              | Mitigation                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Adversary compromises Non-secure firmware, which enables them to tamper at boot time with Normal world DCE, DLME, or the DLME's supplemental images.                                                                                                | The DCE measures the DLME and Normal world DCE into the TPM, allowing detection of tampering.                                                                                            |

| Adversary compromises Non-secure firmware, which enables them to tamper with security critical ACPI tables.                                                                                                                                         | DRTM provides trustworthy ACPI tables or trustworthy hashes of ACPI tables in the data passed to the DLME.                                                                               |

| Adversary compromises Non-secure firmware and modifies the UEFI system memory map and reports an attacker controlled memory-mapped I/O region to be "normal memory". This allows the attacker to spoof responses to any access made to this region. | The DCE provides a trustworthy memory map to the DLME, allowing it to detect any discrepancies in the firmware provided map.                                                             |

| Adversary compromises a Non-secure device and during the dynamic launch uses DMA to tamper with the Normal world DCE, DLME, or the DLME's supplemental images.                                                                                      | There is a system requirement that all DMA-capable devices must be behind an SMMU.  The DRTM implementation verifies that DMA protections for Normal world DRTM components are in place. |

| Adversary uses a secondary PE to tamper with Normal world DCE, DLME, or the DLME's supplemental images.                                                                                                                                             | The DRTM implementation enforces that all PEs except the boot PE are off.                                                                                                                |

| Adversary gains access to locality 4 in the TPM allowing them to reset dynamic PCRs and control the PCR values. This enables them to potentially unseal secrets in the TPM or attest that the system has integrity.   | The system must support hardware or Secure firmware-based enforcement to mediate and control access to the dynamic localities (localities 1-4) of the TPM.                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Adversary triggers a Non-secure exception, causing an adversary-controlled ISR to run during a dynamic launch. This allows tampering with the Normal world DCE, DLME, or the DLME's supplemental images from the ISR. | The DRTM implementation must ensure that DRTM operation cannot be preempted by Non-secure asynchronous exceptions. Examples include interrupts, SError exceptions, and SDEI events.                                                                                                                                                                                                                                                                                                        |

| Adversary tampers with the DRTM parameters before DL Event.                                                                                                                                                           | The DCE verifies the DRTM parameters before use to ensure basic validity. Parameters tampered with might still be valid values, and in this case TPM measurements made during a dynamic launch enables detection of the tampering. For example, if the address or size of the DLME image was tampered with, the measurement made of the DLME enables detection of the tampering.  The DLME entry point in the DRTM parameters has a separate measurement in the TPM, allowing detection of |

|                                                                                                                                                                                                                       | tampering.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| On an SoC with a GIC ITS, adversary abuses GIC configuration to trigger an LPI interrupt during a dynamic launch. This causes the GIC to write data into the DLME region, bypassing SMMU controls.                    | The DRTM implementation must disable all ITSs and ensure LPIs are disabled during the dynamic launch.                                                                                                                                                                                                                                                                                                                                                                                      |

Table 4 shows the threats in scope for hardware-backed implementations, but out of scope for firmware-backed implementations:

Table 4: Threats in scope for hardware-backed implementations

| Threat                                                                                                                                  | Mitigation                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Adversary tampers with Secure or Non-secure DRTM components before they are executed.                                                   | The D-CRTM in the security coprocessor verifies the signature of the initial DCE image and measures it into the TPM, allowing detection of tampering. |

|                                                                                                                                         | All code executed from the D-CRTM until reaching the DLME must be verified using digital signatures.                                                  |

| Adversary tampers with Secure world firmware images.                                                                                    | Secure world firmware is reloaded, verified, and measured into the TPM, allowing detection of tampering.                                              |

| Adversary compromises Secure world firmware and spoofs a dynamic launch by resetting dynamic PCRs and replaying measurements into PCRs. | Hardware protections prevent locality 4 from being accessed by any component except the D-CRTM in the security coprocessor.                           |

| Adversary compromises a Secure device and during the dynamic launch uses DMA to tamper with DRTM components.          | The DRTM implementation puts DMA protections in place so that DCE components and the DLME region cannot be tampered with during the dynamic launch. |

|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| An attacker triggers a Secure device interrupt during the dynamic launch and the ISR tampers with the dynamic launch. | <ul> <li>The DRTM implementation either:</li> <li>Masks Secure asynchronous interrupts</li> <li>Aborts DRTM if an interrupt occurs</li> </ul>       |

| An attacker uses a JTAG probe to tamper with DRTM components during the dynamic launch.                               | The D-CRTM detects and measures if external debug can be enabled without a reset.                                                                   |

### 2.9.5 Security considerations for stakeholders

This section identifies security considerations that must be evaluated by the stakeholders who implement the DRTM architecture and the underlying platform. These responsibilities include ensuring that the underlying system meets the requirements defined in this specification and following best practices for threats not directly addressed by DRTM.

This architecture does not dictate a specific split of responsibility among the stakeholders that implement the DRTM architecture.

| Security Consideration                                                                                                                                                                                                                                                                                                                                                                                                                                     | Stakeholder                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| This architecture depends on a set of system requirements being met which provide the foundation for DRTM. These requirements are specified in section 5.                                                                                                                                                                                                                                                                                                  | Silicon Provider,<br>OEM/ODM |

| The security of components that comprise the system's TCB such as Non-host platforms or Secure services must be evaluated. Is there an attack surface that allows an adversary at a Non-secure or Secure privilege level to cause the component to perform a memory access that can compromise DRTM?                                                                                                                                                       | Silicon Provider,<br>OEM/ODM |

| For hardware-backed DRTM, Secure components that comprise the system's TCB must be verified during the dynamic launch. Also, any security-critical state in the system's TCB that is preserved across the dynamic launch must be verified. Threat modeling is required to determine what state is security-critical.                                                                                                                                       | Silicon Provider,<br>OEM/ODM |

| This architecture requires a TCG-compliant TPM. A firmware TPM is an allowed implementation. It is beyond the scope of this specification to define the security properties for a firmware TPM implementation or for a hardware enclave-based implementation. The TPM implementation is a critical component of the system's TCB and system level threat modeling is needed to evaluate possible threats against a firmware or hardware enclave-based TPM. | Silicon Provider,<br>OEM/ODM |

| There are general threats against the DRTM SMC call interface that are not specific to the DRTM architecture that must be considered by the implementer of DRTM firmware. These include:                                                                                                                                                                                                                                                                   | Silicon Provider,<br>OEM/ODM |

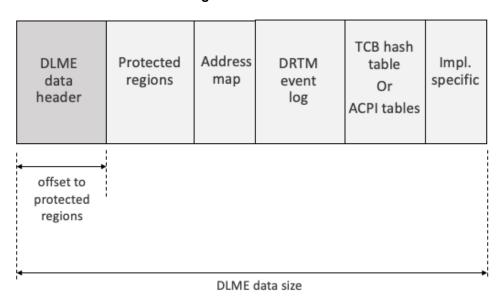

| <ul> <li>Buffer overflows of privileged buffers</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                 |                              |