## Arm<sup>®</sup> Neoverse<sup>™</sup> V2 Core

## **Telemetry Specification**

Non-Confidential

**Issue 02** 109528\_0200\_02\_en

Copyright  $\ensuremath{\mathbb{C}}$  2024 Arm Limited (or its affiliates). All rights reserved.

### Arm<sup>®</sup> Neoverse<sup>™</sup> V2 Core Telemetry Specification

This document is Non-Confidential.

Copyright © 2024 Arm Limited (or its affiliates). All rights reserved.

This document is protected by copyright and other intellectual property rights. Arm only permits use of this document if you have reviewed and accepted Arm's Proprietary Notice found at the end of this document.

This document (109528\_0200\_02\_en) was issued on 2024-09-23. There might be a later issue at https://developer.arm.com/documentation/109528

See also: Proprietary notice | Product and document information | Useful resources

#### Start reading

If you prefer, you can skip to the start of the content.

#### Intended audience

This specification is useful for engineers to collect and analyze Arm® Neoverse<sup>™</sup> V2 Core telemetry data to gain insights about a system's performance. Architects and system designers can also use it for resource characterization and platform tuning.

#### Inclusive language commitment

Arm values inclusive communities. Arm recognizes that we and our industry have used language that can be offensive. Arm strives to lead the industry and create change.

This document includes language that can be offensive. We will replace this language in a future issue of this document.

To report offensive language in this document, email terms@arm.com.

#### Feedback

Arm welcomes feedback on this product and its documentation. To provide feedback on the product, create a ticket on https://support.developer.arm.com.

To provide feedback on the document, fill the following survey: https://developer.arm.com/ documentation-feedback-survey.

# Contents

| 1. Overview of the Neoverse V2 core Telemetry methodology                                  | 5  |

|--------------------------------------------------------------------------------------------|----|

| 1.1 Documentation and resources                                                            | 6  |

|                                                                                            |    |

| 2. Telemetry features of Neoverse V2 core                                                  | 7  |

| 3. CPU performance analysis methodology                                                    |    |

| 3.1 Topdown methodology for the Neoverse V2 core                                           |    |

| 3.2 Stage 1: Topdown analysis                                                              | 12 |

| 3.3 Stage 2: Microarchitecture exploration                                                 |    |

| 4. Neoverse V2 Telemetry cheat-sheets and lookup tables                                    |    |

| 4.1 Metrics cheat sheet for Neoverse V2                                                    |    |

| 4.2 PMU events cheat sheet for Neoverse V2                                                 | 19 |

| 4.3 Metrics lookup table for Neoverse V2                                                   | 21 |

| 4.4 PMU events lookup table for Neoverse V2                                                |    |

| 5. Metrics by metric group in Neoverse V2                                                  |    |

| 5.1 Topdown_L1 metrics for Neoverse V2                                                     |    |

| 5.2 Cycle_Accounting metrics for Neoverse V2                                               |    |

| 5.3 General metrics for Neoverse V2                                                        |    |

| 5.4 MPKI metrics for Neoverse V2                                                           |    |

| 5.5 Miss_Ratio metrics for Neoverse V2                                                     |    |

| 5.6 Branch_Effectiveness metrics for Neoverse V2                                           | 47 |

| 5.7 ITLB_Effectiveness metrics for Neoverse V2                                             |    |

| 5.8 DTLB_Effectiveness metrics for Neoverse V2                                             | 52 |

| 5.9 L1I_Cache_Effectiveness metrics for Neoverse V2                                        | 55 |

| 5.10 L1D_Cache_Effectiveness metrics for Neoverse V2                                       |    |

| 5.11 L2_Cache_Effectiveness metrics for Neoverse V2                                        |    |

| 5.12 LL_Cache_Effectiveness metrics for Neoverse V2                                        | 60 |

| 5.13 Operation_Mix metrics for Neoverse V2                                                 |    |

| 6. PMU events by functional group in Neoverse V2                                           | 66 |

| 6.1 Bus (BUS) events for Neoverse V2                                                       | 67 |

| 6.2 Chain (CHAIN) events for Neoverse V2                                                   | 68 |

| Copyright © 2024 Arm Limited (or its affiliates). All rights reserved.<br>Non-Confidential |    |

| 6.3 Exception (EXCEPTION) events for Neoverse V2            |     |

|-------------------------------------------------------------|-----|

| 6.4 L1D_Cache (L1D CACHE) events for Neoverse V2            | 73  |

| 6.5 L1I_Cache (L1I CACHE) events for Neoverse V2            | 78  |

| 6.6 L2_Cache (L2 CACHE) events for Neoverse V2              |     |

| 6.7 L3_Cache (L3 CACHE) events for Neoverse V2              |     |

| 6.8 LL_Cache (LL CACHE) events for Neoverse V2              | 85  |

| 6.9 Memory (MEMORY) events for Neoverse V2                  |     |

| 6.10 Retired (RETIRED) events for Neoverse V2               |     |

| 6.11 SPE (SPE) events for Neoverse V2                       |     |

| 6.12 Spec_Operation (SPEC OPERATION) events for Neoverse V2 | 96  |

| 6.13 FP_Operation (FP OPERATION) events for Neoverse V2     |     |

| 6.14 Stall (STALL) events for Neoverse V2                   |     |

| 6.15 General (GENERAL) events for Neoverse V2               |     |

| 6.16 TLB (TLB) events for Neoverse V2                       |     |

| 6.17 SVE (SVE) events for Neoverse V2                       |     |

| 6.18 TRACE (TRACE) events for Neoverse V2                   |     |

| 7. Supplemental performance debug PMU events                | 123 |

| Proprietary notice                                          | 124 |

| Product and document information                            |     |

| Product status                                              |     |

| Revision history                                            |     |

| Conventions                                                 |     |

| Useful resources                                            |     |

# 1. Overview of the Neoverse V2 core Telemetry methodology

The Arm<sup>®</sup> Neoverse V2 Core Telemetry Specification describes the Topdown methodology, derived metrics, and Performance Monitoring Unit (PMU) events supported by the Arm Neoverse V2 core, also known as the processor.

This specification is applicable to all releases of the product.

This specification implements the framework provided by the Arm<sup>®</sup> CPU Telemetry Solution Topdown Methodology Specification, which is referred to as the Architecture Specification. The reader is expected to read this document in conjunction with the Architecture Specification.

#### Arm Telemetry framework

This specification outlines the telemetry features implemented for the Arm Neoverse V2 core and follows the Arm Telemetry framework for CPUs defined in the Architecture Specification.

The following list provides a brief description of the Telemetry framework:

#### **Events**

Hardware performance monitoring events implemented by the core that contain raw data read from the registers or memory buffers.

#### Metrics

Derived mathematical relationships between events that provide insight into the system behavior. They are developed to abstract hardware details of the events from consumers of the telemetry data.

#### Metric groups

Group of metrics that can be analyzed together to investigate a bottleneck scenario or a specific resource in a given system.

#### Methodology

Actionable guidance, such as Arm Topdown methodology, to explain how to consume the different metrics and events for a specific usage model. Decision tree with a group of metrics that can be analyzed hierarchically to investigate a bottleneck scenario or a specific resource in a given system.

#### Tool support for profiling and monitoring

This specification is also available in a machine-readable format (JSON) to be consumed by profiling and monitoring tools. The JSON schema implements the Arm Telemetry framework from the Architecture Specification.

The JSON for the core is published in the open source Arm<sup>®</sup> Telemetry Solution GitLab repository.

## **1.1 Documentation and resources**

Arm products include a set of documents.

The documentation and resources for the Neoverse V2 core consist of:

- Arm<sup>®</sup> Telemetry on Arm Developer

- Arm<sup>®</sup> Telemetry Solution GitLab repository

- Arm<sup>®</sup> Neoverse<sup>™</sup> V2 Core Technical Reference Manual

## 2. Telemetry features of Neoverse V2 core

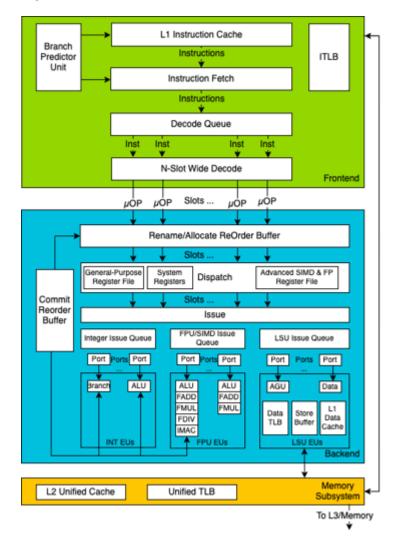

The Neoverse V2 core is a super pipelined superscalar processor that has an in-order frontend and out-of-order backend.

The following figure shows the microarchitecture details of the Neoverse V2 core.

The frontend of the core pipeline is comprised of the instruction fetch and decode units. The frontend also includes a branch predictor unit that predicts branch target addresses and fetches instructions ahead of the pipeline. This unit helps to hide latencies caused by control flow bubbles in the pipeline. The fetch unit can fetch multiple instructions for each cycle whose bandwidth is specific to a microarchitecture design, which gets stored in a decode queue. The decode queue sends multiple instructions per cycle for decoding, whose bandwidth is determined by the number of decode slots available. The decode unit decomposes the Arm architecture instructions into micro-operations, also known as micro-ops or ( $\mu$ ops). The decode unit decodes more than one

micro-operation for each cycle, which are then fed to the rename unit for organization for outof-order execution in the backend of the core. The bandwidth is determined by the number of renamed slots available in the microarchitecture. From a microarchitecture standpoint, the rename unit is considered the boundary between the frontend and backend of the core.

The backend of the core has a scheduler that orchestrates the operations to be executed when the issue queue associated with the operation can accept the operation. The issue queue sends operations for execution when the execution unit is free and the source operands are ready. Once the execution is complete, the results are sent to the commit Reorder Buffer (ROB) from where the instructions are retired when the speculated execution is confirmed. The backend of the core executes the operations out-of-order and stores results with the help of the reorder buffer. The dispatch unit tracks dependencies between operations and determines the operand availability for the execution of operations. Register renaming is occurs at this stage to mitigate data dependency hazards.

In the dispatch unit, issue queues are employed for:

- Queuing the micro-operations (µops) to assigned ports

- Managing dependencies between operations

- Tracking operand availability for execution

Each execution port supports different categories of operations. After the execution of operations, the ROB is updated with execution results. Completed operations are retired architecturally in the right program order. Operations are flushed when the predicted program flow changes due to mispredictions or exceptions.

The Memory subsystem of the core handles the execution of load and store operations which rely heavily on the memory hierarchy levels. The Neoverse V2 core has dedicated cache levels, L1 and L2 for each core, where the L2 cache is shared between the L1 data cache and the L1 instruction cache. The Load Store Unit controls the data flow between the caches and to memory. The core has multiple load/store units, which can handle both read and write operations. L1 and L2 caches are set-associative. The size of the cache is configurable for each implementation and determines the number of sets in each way. The private L2 cache of the core connects to the rest of the system through an AMBA® 5 CHI interface.

#### Neoverse V2 core system configurations

All systems with the Arm<sup>®</sup> Neoverse<sup>™</sup> Coherent Mesh Network support a shared system-level cache. Understanding the cache hierarchy and configuration of the system being analyzed is crucial in deriving insights from the cache effectiveness Performance Monitoring Unit (PMU) events.

It is always best to check with the Silicon Provider for details on the system configuration for the underlying system, including the cache sizes.

#### PMU capabilities of Neoverse V2

The Neoverse V2 core implements version 3.5 of the Performance Monitors Extension, FEAT\_PMUv3p5, and Arm v8.4 debug architecture, FEAT\_Debugv8p4.

For more information, see Arm<sup>®</sup> Architecture Reference Manual for A-profile architecture.

The Neoverse V2 PMU has six configurable counter registers and one dedicated function counter to count CPU cycles.

# 3. CPU performance analysis methodology

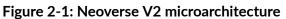

The Arm Topdown methodology for performance analysis and microarchitecture exploration is conducted in two stages.

#### Stage 1

The first stage is to perform Topdown analysis. It uses hierarchical pipeline stall-related metrics to detect and identify the performance bottleneck in the CPU. For more information, see Stage 1: Topdown analysis.

#### Stage 2

The second stage is to conduct microarchitecture exploration to further analyze bottlenecked CPU resources. It uses a set of CPU resource effectiveness metrics. For more information, see Stage 2: Microarchitecture Exploration.

For more information, see Arm<sup>®</sup> CPU Telemetry Solution Topdown Methodology Specification.

## 3.1 Topdown methodology for the Neoverse V2 core

Topdown analysis helps with hotspot detection and is the first stage completed in the Topdown methodology. Microarchitecture exploration is the second stage completed in the Topdown methodology and conducts a micro-architectural analysis of the bottlenecking CPU resource.

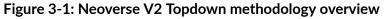

The following figure shows the Topdown methodology for the Neoverse V2 core covering both the Stage 1 metrics and the Stage 2 metric groups that can be used during your analysis.

Copyright © 2024 Arm Limited (or its affiliates). All rights reserved. Non-Confidential

Arm recommends collecting all the metrics that are in Stage 1 and Stage 2 for workload characterization. For further analysis, Arm recommends a set of set of microarchitecture exploration metric groups against some of the hotspots detected in Stage 1. All the Stage 2 metrics can be used to derive further insights into the overall microarchitecture behavior during the execution of the application under investigation and can be used independently to Stage 1.

## 3.2 Stage 1: Topdown analysis

The Neoverse V2 core supports the four key metrics for Topdown analysis level 1 that are slotbased, which is a measurement of the efficiency of pipeline slots.

The four metrics in the first level as part of the Topdown Level 1 metric group is defined by the Arm<sup>®</sup> CPU Telemetry Solution Topdown Methodology Specification, as follows:

#### frontend\_bound

This metric is the percentage of total slots that were stalled due to resource constraints in the frontend unit of the processor.

#### backend\_bound

This metric is the percentage of total slots that were stalled due to resource constraints in the backend unit of the processor.

#### bad\_speculation

This metric is the percentage of total slots that executed operations but did not retire due to a pipeline flush caused by mis-speculation. It indicates the cycles that were used but were inefficient executing the wrong instructions. It also includes cycles spent recovering from the pipeline flush, which requires an instruction pipeline refill from the correct instruction location.

#### retiring

This metric is the percentage of total slots that retired operations. This indicates the cycles that were used and efficient.

For more information on the Topdown Level 1 metric group and its corresponding metrics, see Topdown\_L1.

## 3.3 Stage 2: Microarchitecture exploration

When the execution pipeline bottleneck region is identified from Stage 1, the next step is to investigate the CPU resources for further analysis.

As described in the Architecture Specification:

• A relatively high frontend\_bound metric shows that execution cycles are wasted due to pipeline stalls in the in-order frontend division of the processor. There are many reasons why frontend stalls can occur, such as inefficiency in the branch prediction unit, fetch latency due to instruction cache misses, and translation delays caused by Instruction TLB walks.

- A relatively high backend\_bound metric shows that execution cycles are wasted due to pipeline stalls in the backend of the processor. There are many reasons why backend stalls can occur, such as inefficiency in execution units, data cache misses, and translation delays caused by data TLB walks.

- A relatively high bad\_speculation metric shows the pipeline stalls caused by flushes or machine clears that break the pipeline needing a control flow change. Branch mispredictions are one of the major causes for these stalls, as well as exceptions.

The Neoverse V2 core supports the following microarchitecture exploration metric groups that can be used for Stage 2 analysis. These metric groups support further analysis of the bottlenecking CPU resources following the Stage 1 analysis hotspot.

As a common step in Stage 2, the two metric groups MPKI and Miss rate are recommended for a quick behavioral analysis of the CPU components that could be the most probable bottlenecks.

#### MPKI – Misses Per Kilo Instructions

Misses Per Kilo Instructions is a set of metrics that can be derived to normalize the misses in CPU components, such as branches, caches, and TLBs against the total instructions executed. This is an industry-standard metric that also helps with comparison across different implementations of the Arm architecture, as instructions retired should count the same on all AArch64-based microarchitectures.

MPKI lists all the Misses Per Kilo Instructions metrics that can be derived for the Neoverse V2 core and their formulae.

#### **Miss Ratio**

The Miss Ratio metric group provides a set of metrics that calculate the ratio of the misses in the CPU components, such as branches, caches and TLBs against the total accesses in those components. These metrics provide insights on the efficiency of each CPU component in the pipeline and help to root cause issues.

Miss\_Ratio lists all the Miss Ratio metrics that can be derived for the Neoverse V2 core and their formulae.

#### **Operation Mix**

The Neoverse V2 microarchitecture has a variety of execution units that process different types of operations.

The execution units that are shown in Figure 2-1: Neoverse V2 microarchitecture on page 7 process the following types of operations:

- Branch

- Single-cycle integers

- Multicycle integers

- Load/store unit with address generation

- Advanced floating-point/SIMD operations

• SVE

The PMU events listed in Spec\_Operation count the operations that are issued to these execution units.

Operation\_Mix lists all the Speculative Operation Mix metrics that can be derived for the Neoverse V2 core and their formulae.

The following implementation criteria apply for this metric group:

• The sve\_all\_percentage operation includes SVE load and store operations. These operations are also counted in the load\_percentage and store\_percentage metrics. Therefore, this duplicate counting should be taken into account when these metrics are considered together.

These metrics use events that count speculatively issued operations at the issue stage, which provide an estimate of the execution unit utilization, but not the retired instruction mix of the program. To derive the utilization of each operation type, the percentage of each type of operation is calculated as a fraction of the total operations issued, which is counted by the event INST\_SPEC.

The Neoverse V2 core does not support retired events for counting the architectural instruction mix. The core supports events to further break down the branch operations into immediate, indirect, and return branches, counted by events BR\_IMMED\_SPEC, BR\_INDIRECT\_SPEC, and BR\_RETURN\_SPEC respectively. BR\_RETURN\_SPEC is a subset of BR\_INDIRECT\_SPEC, as returns are also counted as indirect branches. The sum of the BR\_IMMED\_SPEC and BR\_INDIRECT\_SPEC branch operation events can compute the total branches executed.

#### **Branch Effectiveness and Branch Mix**

Branch mispredictions are costly in a deeply pipelined CPU, causing pipeline flushes and wasted cycles. As a general rule, workloads typically contain, on average, one branch in every six instructions.

Though modern CPUs have optimized branch prediction units, there are many use cases such as ray tracing and decision tree algorithms that are branch heavy and hard to predict. In some of these applications, there can be hundreds of unique branch paths to take and the target may be input data dependent.

Branch prediction performance can be evaluated using two PMU events, BR\_MIS\_PRED\_RETIRED and BR\_RETIRED. BR\_MIS\_PRED\_RETIRED provides an account of the total branches that were executed but mispredicted. This means that the direction of the code path was wrong and the following operations in the path were wasted, causing a pipeline flush. BR\_RETIRED counts the total branches architecturally executed by the CPU.

There are two performance metrics that can be derived for a high-level evaluation of the branch execution performance regarding the overall program execution:

#### branch\_mpki metrics

Provides total branch mispredictions per kilo instructions

#### branch\_misprediction\_ratio metrics

Provides an indication of the ratio of branches that were mispredicted to overall branches

Branch\_Effectiveness lists all the Branch Effectiveness metrics that can be derived for the Neoverse V2 core and their formulae.

Branch prediction units work differently depending on the branch type. The following list describes the three main sub-units that work for different branch types:

- Branch History Table (BHT) stores the history of conditional branches, taken or not.

- Branch Target Buffer (BTB) stores the target address for indirect branches.

- Return Address Stack (RAS) stores the function return branches.

The Neoverse V2 core supports the following three events that respectively categorizes the immediate, indirect, and return branches executed:

- BR\_IMMED\_SPEC

- BR\_RETURN\_SPEC

- BR\_INDIRECT\_SPEC

Getting a breakdown of the branch type helps to investigate each of these sub-units within the branch prediction unit.

#### **TLB/MMU Effectiveness**

Arm recommends checking the virtual memory system performance which affects the instruction fetch performance in the frontend and memory access performance on the data side.

The processor needs to translate a virtual address to physical address for any instruction/data memory access before it accesses the respective cache. A program's view of memory is virtual address, but the processor works with the physical address when accessing cache or memory.

Virtual to physical mappings are defined in the page translation tables which reside in system memory. Accessing these tables requires one or more memory accesses that take many cycles to complete, which is referred to as a translation table walk. However, to make these translations faster, *Translation Lookaside Buffers* (TLBs) cache translation table walks, greatly reducing the number of accesses to system memory.

Neoverse V2 implements a two-level TLB hierarchy. The first level contains separate, dedicated TLBs for the instruction and data (load/store) address translations. Total accesses to these TLBs are counted by L11\_TLB and L1D\_TLB respectively. The second level contains a unified L2 TLB that is shared by both instruction-side and data-side accesses. There are corresponding REFILL counters for these TLB levels. Some performance metrics that can be derived for a high-level evaluation of the TLB execution performance are the I<n>\_tlb\_mpki and I<n>\_tlb\_miss\_rate metrics, where <n> stands for each level of TLB instruction and data side.

Accesses that cause a translation table walk due to misses in the instruction side and data side TLBs are counted by the events ITLB\_WALK and DTLB\_WALK, respectively. To evaluate the TLB effectiveness and cost of latency caused by translation table walks specifically, dtlb\_mpki, dtlb\_walk\_ratio, itlb\_mpki, and itlb\_walk\_ratio are the key metrics that can be derived. itlb\_mpki and dtlb\_mpki provide the rate of TLB Walks per kilo instructions for instruction and data accesses respectively. These derived metrics help to evaluate and correlate the TLB efficiency with respect to the total instructions.

dtlb\_walk\_ratio provides the ratio of DTLB Walks to the overall TLB lookups made by the program. This is the same as DTLB\_WALK/MEM\_ACCESS as every MEM\_ACCESS causes a L1D\_TLB access. itlb\_walk\_ratio provides a percentage of ITLB walks to the overall TLB lookups initiated from the instruction side.

ITLB\_Effectiveness and DTLB\_Effectiveness list all the TLB Effectiveness metrics that can be derived for Neoverse V2 and their formulae.

#### **Cache Effectiveness**

The Neoverse V2 implements a multi-level cache hierarchy.

The first level (L1) includes a dedicated cache for instructions and a separate dedicated cache for data accesses. The second level (L2) is a unified L2 cache that is shared between code and data. Further down the hierarchy, the system could have an optional shared *System Level Cache* (SLC) in the interconnect. Arm recommends checking the cache configurations with the platform provider.

The Neoverse V2 core supports hierarchical PMU events for all the cache hierarchy levels. For each level of caches, there are total access counts and refill counts. AArch64 does not support cache MISS counters, but only REFILLs. A cache miss could lead to multiple cache line refills if the access is on a cache line boundary or multiple cache misses could be satisfied by a single REFILL.

Some performance metrics that can be derived for a high-level evaluation of the cache execution behavior are the  $l<n>_cache_mpki$  and  $l<n>_cache_miss_ratio metrics, where <n> stands for each level of instruction and data caches.$

L1I\_Cache\_Effectiveness, L1D\_Cache\_Effectiveness, and L2\_Cache\_Effectiveness list all the L1 and L2 Cache Effectiveness metrics that can be derived for Neoverse V2 and their formulae.

#### Core Memory Traffic

The MEM\_ACCESS event counts the total number of memory operations that were issued by the *Load Store Unit* (LSU) of the core. As these operations are looked up in the L1D\_CACHE first, both the events L1D\_CACHE and MEM\_ACCESS count at the same rate.

Neoverse V2 also supports two additional events, MEM\_ACCESS\_RD and MEM\_ACCESS\_WR that can provide the read and write traffic breakdown respectively. Note that these events are not the same as LD\_SPEC and ST\_SPEC as they count memory operations speculatively issued but not necessarily executed.

#### Last Level Cache Counter Usage

On systems that support a shared SLC in the interconnect, LL\_CACHE\_RD counts the total accesses to the SLC. In a system that has the SLC configured to count LL\_CACHE\_RD events, LL\_CACHE\_RD counts total SLC accesses made by the core, and LL\_CACHE\_MISS\_RD counts accesses missed at the SLC.

The last level cache read miss metrics II\_cache\_read\_mpki and II\_cache\_miss\_ratio can be derived to study the last level read behavior. Another useful metric to measure is the SLC hit percentage for the read traffic is the SLC Read Hit Ratio denoted as II\_cache\_read\_hit\_ratio. Last level cache events do not have a write variant in Neoverse V2, since SLC is only used as an eviction cache for the core. In addition, all the writes complete early at the interconnect when the transaction is acknowledged but not necessarily completed.

LL\_Cache\_Effectiveness lists all the Last Level Cache Effectiveness metrics that can be derived for Neoverse V2 and their formulae.

#### Remote Cache Access

For systems with multiple sockets or SoCs, Neoverse V2 supports the REMOTE\_ACCESS event, which counts the memory transactions that were completed by a subordinate source from another chip.

# 4. Neoverse V2 Telemetry cheat-sheets and lookup tables

The cheat-sheets and lookup tables enable you to find and access metrics and events in different ways.

#### Cheat-sheets

Both metrics and events are listed by metric groups.

#### Lookup tables

Metrics are listed alphabetically, with the related events, and metric groups. Events are listed by code number, with the related metrics, metric groups, and functional groups.

## 4.1 Metrics cheat sheet for Neoverse V2

Metrics are listed in their respective metric groups. Some metrics are used in more than one metric group.

Neoverse V2 specification provides the following types of metrics:

• Total implemented Common metrics: 36

| Topdown Level 1 (4) | Cycle Accounting (2)    | General (1) |  |

|---------------------|-------------------------|-------------|--|

| backend_bound       | backend_stalled_cycles  | • ipc       |  |

| bad_speculation     | frontend_stalled_cycles |             |  |

| frontend_bound      |                         |             |  |

| retiring            |                         |             |  |

| Misses Per Kilo Instructions (10)  | Miss Ratio (10)          | Branch Effectiveness (2)         |

|------------------------------------|--------------------------|----------------------------------|

| • branch_mpki                      | branch_misprediction_ra  | tio • branch_misprediction_ratio |

| dtlb_mpki                          | dtlb_walk_ratio          | branch_mpki                      |

| itlb_mpki                          | • itlb_walk_ratio        |                                  |

| <ul> <li>I1d_cache_mpki</li> </ul> | • I1d_cache_miss_ratio   |                                  |

| l1d_tlb_mpki                       | • l1d_tlb_miss_ratio     |                                  |

| l1i_cache_mpki                     | • l1i_cache_miss_ratio   |                                  |

| l1i_tlb_mpki                       | • l1i_tlb_miss_ratio     |                                  |

| l2_cache_mpki                      | I2_cache_miss_ratio      |                                  |

| l2_tlb_mpki                        | • I2_tlb_miss_ratio      |                                  |

| Il_cache_read_mpki                 | Il_cache_read_miss_ratio |                                  |

| Instruction TLB Effectiveness (6)      | Data TLB Effectiveness (6) | L1 Instruction Cache Effectiveness (2) |

|----------------------------------------|----------------------------|----------------------------------------|

| • itlb_mpki                            | • dtlb_mpki                | I1i_cache_miss_ratio                   |

| • itlb_walk_ratio                      | dtlb_walk_ratio            | I1i_cache_mpki                         |

| <ul> <li>I1i_tlb_miss_ratio</li> </ul> | I1d_tlb_miss_ratio         |                                        |

| • l1i_tlb_mpki                         | • l1d_tlb_mpki             |                                        |

| <ul> <li>I2_tlb_miss_ratio</li> </ul>  | I2_tlb_miss_ratio          |                                        |

| • l2_tlb_mpki                          | • I2_tlb_mpki              |                                        |

| L1 Data Cache Effectiveness (2) | L2 Unified Cache Effectiveness (2) | Last Level Cache Effectiveness (3) |

|---------------------------------|------------------------------------|------------------------------------|

| I1d_cache_miss_ratio            | I2_cache_miss_ratio                | Il_cache_read_hit_ratio            |

| I1d_cache_mpki                  | I2_cache_mpki                      | Il_cache_read_miss_ratio           |

|                                 |                                    | Il_cache_read_mpki                 |

#### Speculative Operation Mix (8)

- branch\_percentage

- crypto\_percentage

- integer\_dp\_percentage

- load\_percentage

- scalar\_fp\_percentage

- simd\_percentage

- store\_percentage

- sve\_all\_percentage

## 4.2 PMU events cheat sheet for Neoverse V2

Events are listed in their respective metric groups. Some events are not used in the Methodology, therefore are not shown in the cheat sheet.

Neoverse V2 specification provides the following types of PMU events:

- Total implemented Common events: 155

- Total Implemented Product ImpDef events: 0

- PMU Only events : 0

- ETE Only events : 0

| Topdown Level 1 (7) | Cycle Accounting (3) | General (2)  |

|---------------------|----------------------|--------------|

| BR_MIS_PRED         | CPU_CYCLES           | CPU_CYCLES   |

| CPU_CYCLES          | STALL_BACKEND        | INST_RETIRED |

| OP_RETIRED          | STALL_FRONTEND       |              |

| OP_SPEC             |                      |              |

| STALL_SLOT          |                      |              |

| STALL_SLOT_BACKEND  |                      |              |

| STALL_SLOT_FRONTEND |                      |              |

| Misses Per Kilo Instructions (11) | Miss Ratio (18)     | Branch Effectiveness (3) |

|-----------------------------------|---------------------|--------------------------|

| BR_MIS_PRED_RETIRED               | BR_MIS_PRED_RETIRED | BR_MIS_PRED_RETIRED      |

| • DTLB_WALK                       | BR_RETIRED          | BR_RETIRED               |

| INST_RETIRED                      | • DTLB_WALK         | INST_RETIRED             |

| • ITLB_WALK                       | • ITLB_WALK         |                          |

| L1D_CACHE_REFILL                  | • L1D_CACHE         |                          |

| L1D_TLB_REFILL                    | L1D_CACHE_REFILL    |                          |

| L1I_CACHE_REFILL                  | • L1D_TLB           |                          |

| L1I_TLB_REFILL                    | L1D_TLB_REFILL      |                          |

| L2D_CACHE_REFILL                  | • L1I_CACHE         |                          |

| L2D_TLB_REFILL                    | L1I_CACHE_REFILL    |                          |

| LL_CACHE_MISS_RD                  | • L1I_TLB           |                          |

|                                   | L1I_TLB_REFILL      |                          |

|                                   | • L2D_CACHE         |                          |

|                                   | L2D_CACHE_REFILL    |                          |

|                                   | • L2D_TLB           |                          |

|                                   | L2D_TLB_REFILL      |                          |

|                                   | LL_CACHE_MISS_RD    |                          |

|                                   | LL_CACHE_RD         |                          |

| Instruction TLB Effectiveness (6) | Data TLB Effectiveness (6)         | L1 Instruction Cache Effectiveness (3) |

|-----------------------------------|------------------------------------|----------------------------------------|

| INST_RETIRED                      | DTLB_WALK                          | INST_RETIRED                           |

| • ITLB_WALK                       | INST_RETIRED                       | L1I_CACHE                              |

| L1I_TLB                           | • L1D_TLB                          | L1I_CACHE_REFILL                       |

| L1I_TLB_REFILL                    | L1D_TLB_REFILL                     |                                        |

| L2D_TLB                           | • L2D_TLB                          |                                        |

| L2D_TLB_REFILL                    | L2D_TLB_REFILL                     |                                        |

|                                   |                                    |                                        |

| L1 Data Cache Effectiveness (3)   | L2 Unified Cache Effectiveness (3) | Last Level Cache Effectiveness (3)     |

| INST_RETIRED                      | INST_RETIRED                       | INST_RETIRED                           |

| INST_RETIR | (ED      | • | INST_RETIRED     | • | INST_RETIRED     |

|------------|----------|---|------------------|---|------------------|

| • L1D_CACH | E        | • | L2D_CACHE        | • | LL_CACHE_MISS_RD |

| • L1D_CACH | E_REFILL | • | L2D_CACHE_REFILL | • | LL_CACHE_RD      |

#### Speculative Operation Mix (10)

- ASE\_SPEC

- BR\_IMMED\_SPEC

- BR\_INDIRECT\_SPEC

- CRYPTO\_SPEC

- DP\_SPEC

- INST\_SPEC

- LD\_SPEC

- ST\_SPEC

- SVE\_INST\_SPEC

- VFP\_SPEC

## 4.3 Metrics lookup table for Neoverse V2

All metrics are listed alphabetically, with the related events, and metric groups. Some metrics are used in more than one metric group, in that case they are listed multiple times so that you can jump to the most relevant metric group for your requirements.

| Metric Name                                   | Formula from Events                                                                                           | Metric Groups        |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------|

| backend_bound                                 | 100 * (STALL_SLOT_BACKEND /<br>(CPU_CYCLES * 8) - BR_MIS_PRED * 3 /<br>CPU_CYCLES)                            | Topdown_L1           |

| backend_stalled_cycles                        | STALL_BACKEND / CPU_CYCLES * 100                                                                              | Cycle_Accounting     |

| bad_speculation                               | 100 * ((1 - OP_RETIRED / OP_SPEC) *<br>(1 - STALL_SLOT / (CPU_CYCLES * 8)) +<br>BR_MIS_PRED * 4 / CPU_CYCLES) | Topdown_L1           |

| branch_misprediction_ratio in                 | BR_MIS_PRED_RETIRED / BR_RETIRED                                                                              | Branch_Effectiveness |

| Branch_Effectiveness                          |                                                                                                               | • Miss_Ratio         |

| • branch_misprediction_ratio in<br>Miss_Ratio |                                                                                                               |                      |

| branch_mpki in Branch_Effectiveness           | BR_MIS_PRED_RETIRED / INST_RETIRED *                                                                          | Branch_Effectiveness |

| branch_mpki in MPKI                           | 1000                                                                                                          | • MPKI               |

| branch_percentage                             | (BR_IMMED_SPEC + BR_INDIRECT_SPEC) /<br>INST_SPEC * 100                                                       | Operation_Mix        |

| crypto_percentage                             | CRYPTO_SPEC / INST_SPEC * 100                                                                                 | Operation_Mix        |

| dtlb_mpki in DTLB_Effectiveness               | DTLB_WALK / INST_RETIRED * 1000                                                                               | DTLB_Effectiveness   |

| • dtlb_mpki in MPKI                           |                                                                                                               | • MPKI               |

| dtlb_walk_ratio in DTLB_Effectiveness         | DTLB_WALK / L1D_TLB                                                                                           | DTLB_Effectiveness   |

| dtlb_walk_ratio in Miss_Ratio                 |                                                                                                               | Miss_Ratio           |

Table 4-11: Metrics listed by name, with related events and metric groups

| Metric Name                                                                 | Formula from Events                                                             | Metric Groups                                      |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------|

| frontend_bound                                                              | 100 * (STALL_SLOT_FRONTEND /<br>(CPU_CYCLES * 8) - BR_MIS_PRED /<br>CPU_CYCLES) | Topdown_L1                                         |

| frontend_stalled_cycles                                                     | STALL_FRONTEND / CPU_CYCLES * 100                                               | Cycle_Accounting                                   |

| integer_dp_percentage                                                       | DP_SPEC / INST_SPEC * 100                                                       | Operation_Mix                                      |

| ірс                                                                         | INST_RETIRED / CPU_CYCLES                                                       | • General                                          |

| itlb_mpki in ITLB_Effectiveness                                             | ITLB_WALK / INST_RETIRED * 1000                                                 | ITLB_Effectiveness                                 |

| • itlb_mpki in MPKI                                                         |                                                                                 | • MPKI                                             |

| itlb_walk_ratio in ITLB_Effectiveness                                       | ITLB_WALK / L1I_TLB                                                             | ITLB_Effectiveness                                 |

|                                                                             |                                                                                 | Miss_Ratio                                         |

| itlb_walk_ratio in Miss_Ratio                                               |                                                                                 |                                                    |

| <ul> <li>I1d_cache_miss_ratio in<br/>L1D_Cache_Effectiveness</li> </ul>     | L1D_CACHE_REFILL / L1D_CACHE                                                    | L1D_Cache_Effectiveness                            |

|                                                                             |                                                                                 | Miss_Ratio                                         |

| I1d_cache_miss_ratio in Miss_Ratio                                          |                                                                                 |                                                    |

| <ul> <li>I1d_cache_mpki in<br/>L1D Cache Effectiveness</li> </ul>           | L1D_CACHE_REFILL / INST_RETIRED *<br>1000                                       | L1D_Cache_Effectiveness                            |

|                                                                             |                                                                                 | • MPKI                                             |

| I1d_cache_mpki in MPKI                                                      |                                                                                 |                                                    |

| <ul> <li>I1d_tlb_miss_ratio in<br/>DTLB_Effectiveness</li> </ul>            | L1D_TLB_REFILL / L1D_TLB                                                        | DTLB_Effectiveness                                 |

|                                                                             |                                                                                 | Miss_Ratio                                         |

| I1d_tlb_miss_ratio in Miss_Ratio                                            |                                                                                 |                                                    |

| I1d_tlb_mpki in DTLB_Effectiveness                                          | L1D_TLB_REFILL / INST_RETIRED * 1000                                            | DTLB_Effectiveness                                 |

| I1d_tlb_mpki in MPKI                                                        |                                                                                 | • MPKI                                             |

| I1i_cache_miss_ratio in                                                     | L1I_CACHE_REFILL / L1I_CACHE                                                    | L1I_Cache_Effectiveness                            |

| L1I_Cache_Effectiveness                                                     |                                                                                 | Miss_Ratio                                         |

| • I1i_cache_miss_ratio in Miss_Ratio                                        |                                                                                 |                                                    |

| I1i_cache_mpki in                                                           | L1I_CACHE_REFILL / INST_RETIRED *                                               | L1I_Cache_Effectiveness                            |

| L1I_Cache_Effectiveness                                                     | 1000                                                                            | • MPKI                                             |

| I1i_cache_mpki in MPKI                                                      |                                                                                 |                                                    |

| • I1i_tlb_miss_ratio in ITLB_Effectiveness                                  | L1I_TLB_REFILL / L1I_TLB                                                        | ITLB_Effectiveness                                 |

| • 11i tlb miss ratio in Miss Ratio                                          |                                                                                 | Miss_Ratio                                         |

| I1i_tlb_miss_ratio in Miss_Ratio     I1i_tlb_mpki in ITLB_Effectiveness     | L1I_TLB_REFILL / INST_RETIRED * 1000                                            | ITLB_Effectiveness                                 |

|                                                                             | LITTED_KEFILL7 INST_KETIKED 1000                                                | <ul><li>II LB_Effectiveness</li><li>MPKI</li></ul> |

| I1i_tlb_mpki in MPKI                                                        |                                                                                 | • PILIN                                            |

| I2_cache_miss_ratio in     I2_Cache_Effectiveness                           | L2D_CACHE_REFILL / L2D_CACHE                                                    | L2_Cache_Effectiveness                             |

| L2_Cache_Effectiveness                                                      |                                                                                 | Miss_Ratio                                         |

| I2_cache_miss_ratio in Miss_Ratio                                           |                                                                                 |                                                    |

| I2_cache_mpki in     I2_Cache_Effective==================================== | L2D_CACHE_REFILL / INST_RETIRED *                                               | L2_Cache_Effectiveness                             |

| L2_Cache_Effectiveness                                                      | 1000                                                                            | • MPKI                                             |

| I2_cache_mpki in MPKI                                                       |                                                                                 |                                                    |

| Metric Name                               | Formula from Events                                                   | Metric Groups          |

|-------------------------------------------|-----------------------------------------------------------------------|------------------------|

| • I2_tlb_miss_ratio in DTLB_Effectiveness | L2D_TLB_REFILL / L2D_TLB                                              | DTLB_Effectiveness     |

|                                           |                                                                       | ITLB_Effectiveness     |

| I2_tlb_miss_ratio in ITLB_Effectiveness   |                                                                       | Miss_Ratio             |

| I2_tlb_miss_ratio in Miss_Ratio           |                                                                       |                        |

| I2_tlb_mpki in DTLB_Effectiveness         | L2D_TLB_REFILL / INST_RETIRED * 1000                                  | DTLB_Effectiveness     |

| - 12 the maki in ITLR Effectiveness       |                                                                       | ITLB_Effectiveness     |

| I2_tlb_mpki in ITLB_Effectiveness         |                                                                       | • MPKI                 |

| I2_tlb_mpki in MPKI                       |                                                                       |                        |

| II_cache_read_hit_ratio                   | (LL_CACHE_RD - LL_CACHE_MISS_RD) /<br>LL_CACHE_RD                     | LL_Cache_Effectiveness |

| Il_cache_read_miss_ratio in               | LL_CACHE_MISS_RD / LL_CACHE_RD                                        | LL_Cache_Effectiveness |

| LL_Cache_Effectiveness                    |                                                                       | Miss_Ratio             |

| • II_cache_read_miss_ratio in Miss_Ratio  |                                                                       |                        |

| Il_cache_read_mpki in                     | LL_CACHE_MISS_RD / INST_RETIRED *                                     | LL_Cache_Effectiveness |

| LL_Cache_Effectiveness                    | 1000                                                                  | • MPKI                 |

| Il_cache_read_mpki in MPKI                |                                                                       |                        |

| load_percentage                           | LD_SPEC / INST_SPEC * 100                                             | Operation_Mix          |

| retiring                                  | 100 * (OP_RETIRED / OP_SPEC * (1 -<br>STALL_SLOT / (CPU_CYCLES * 8))) | Topdown_L1             |

| scalar_fp_percentage                      | VFP_SPEC / INST_SPEC * 100                                            | Operation_Mix          |

| simd_percentage                           | ASE_SPEC / INST_SPEC * 100                                            | Operation_Mix          |

| store_percentage                          | ST_SPEC / INST_SPEC * 100                                             | Operation_Mix          |

| sve_all_percentage                        | SVE_INST_SPEC / INST_SPEC * 100                                       | Operation_Mix          |

## 4.4 PMU events lookup table for Neoverse V2

All events are listed in event code order, with the related metrics, metric groups, and functional groups. Some events are not used in the Methodology, however, they are all listed for completeness.

Summary of Events:

- Total Possible Common events: 734

- Total implemented Common events: 155

- Common : Architectural-defined events: 91

- Common : Implementation-defined events: 64

- Total Implemented Product ImpDef events: 0

- PMU Only Events : 0

- ETE Only Events : 0

| Code, Mnemonic Metrics   |                                                                                                                                                                                                                | Metric Groups                                                                 | Functional Groups     Retired |  |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------|--|

| 0x0000, SW_INCR          | 00, SW_INCR -                                                                                                                                                                                                  |                                                                               |                               |  |

| 0x0001, L1I_CACHE_REFILL | <ul> <li>I1i_cache_mpki in<br/>L1I_Cache_Effectiveness</li> <li>I1i_cache_mpki in MPKI</li> <li>I1i_cache_miss_ratio in<br/>L1I_Cache_Effectiveness</li> <li>I1i_cache_miss_ratio in<br/>Miss_Ratio</li> </ul> | <ul> <li>L1I_Cache_Effectiveness</li> <li>MPKI</li> <li>Miss_Ratio</li> </ul> | • L1I_Cache                   |  |

| 0x0002, L1I_TLB_REFILL   | <ul> <li>I1i_tlb_mpki in<br/>ITLB_Effectiveness</li> <li>I1i_tlb_mpki in MPKI</li> <li>I1i_tlb_miss_ratio in<br/>ITLB_Effectiveness</li> <li>I1i_tlb_miss_ratio in<br/>Miss_Ratio</li> </ul>                   | <ul> <li>ITLB_Effectiveness</li> <li>MPKI</li> <li>Miss_Ratio</li> </ul>      | • TLB                         |  |

| 0x0003, L1D_CACHE_REFILL | <ul> <li>I1d_cache_mpki in<br/>L1D_Cache_Effectiveness</li> <li>I1d_cache_mpki in MPKI</li> <li>I1d_cache_miss_ratio in<br/>L1D_Cache_Effectiveness</li> <li>I1d_cache_miss_ratio in<br/>Miss_Ratio</li> </ul> | <ul> <li>L1D_Cache_Effectiveness</li> <li>MPKI</li> <li>Miss_Ratio</li> </ul> | • L1D_Cache                   |  |

| 0x0004, L1D_CACHE        | <ul> <li>I1d_cache_miss_ratio in<br/>L1D_Cache_Effectiveness</li> <li>I1d_cache_miss_ratio in<br/>Miss_Ratio</li> </ul>                                                                                        | <ul><li>L1D_Cache_Effectiveness</li><li>Miss_Ratio</li></ul>                  | L1D_Cache                     |  |

| 0x0005, L1D_TLB_REFILL   | <ul> <li>I1d_tlb_mpki in<br/>DTLB_Effectiveness</li> <li>I1d_tlb_mpki in MPKI</li> <li>I1d_tlb_miss_ratio in<br/>DTLB_Effectiveness</li> <li>I1d_tlb_miss_ratio in<br/>Miss_Ratio</li> </ul>                   | <ul> <li>DTLB_Effectiveness</li> <li>MPKI</li> <li>Miss_Ratio</li> </ul>      | • TLB                         |  |

#### Table 4-12: Events listed by Event Code, with related Metrics, Metric Groups, and Functional Groups

| Code, Mnemonic Metrics              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Metric Groups                                                                                                                                                                                                                                                                  | Functional Groups                   |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| Code, Mnemonic 0x0008, INST_RETIRED | Metrics         ipc         branch_mpki in<br>Branch_Effectiveness         branch_mpki in MPKI         itlb_mpki in<br>ITLB_Effectiveness         itlb_mpki in MPKI         I1i_tlb_mpki in<br>ITLB_Effectiveness         I1i_tlb_mpki in<br>DTLB_Effectiveness         I1i_tlb_mpki in<br>DTLB_Effectiveness         dtlb_mpki in<br>DTLB_Effectiveness         I1d_tlb_mpki in<br>DTLB_Effectiveness         I1d_tlb_mpki in<br>DTLB_Effectiveness         I2_tlb_mpki in<br>DTLB_Effectiveness         I2_tlb_mpki in<br>ITLB_Effectiveness         I2_tlb_mpki in<br>MPKI         I1i_cache_mpki in<br>L1I_Cache_Effectiveness         I1i_cache_mpki in<br>MPKI         I1i_cache_mpki in<br>MPKI         I1i_cache_mpki in<br>MPKI         I2_cache_Effectiveness         I1d_cache_mpki in<br>MPKI         I2_cache_Effectiveness         I2_cache_Effectiveness         I2_cache_mpki in<br>L2_Cache_Effectiveness | Metric Groups <ul> <li>Branch_Effectiveness</li> <li>DTLB_Effectiveness</li> <li>General</li> <li>ITLB_Effectiveness</li> <li>L1D_Cache_Effectiveness</li> <li>L2_Cache_Effectiveness</li> <li>L1_Cache_Effectiveness</li> <li>L1_Cache_Effectiveness</li> <li>MPKI</li> </ul> | Functional Groups         • Retired |

|                                     | <ul> <li>II_cache_read_mpki in<br/>LL_Cache_Effectiveness</li> <li>II_cache_read_mpki in MPKI</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                |                                     |

| 0x0009, EXC_TAKEN                   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                                              | Exception                           |

| 0x000a, EXC_RETURN                  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                                              | Exception                           |

| 0x000в, CID_WRITE_RETIRED           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                                              | Retired                             |

| 0x0010, BR_MIS_PRED                 | <ul><li>frontend_bound</li><li>backend_bound</li><li>bad_speculation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Topdown_L1                                                                                                                                                                                                                                                                     | Spec_Operation                      |

| <ul> <li>frontend_stalled_cycles</li> <li>backend_stalled_cycles</li> <li>frontend_bound</li> <li>backend_bound</li> <li>retiring</li> <li>bad_speculation</li> </ul> | <ul><li>Cycle_Accounting</li><li>General</li><li>Topdown_L1</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | General        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| <ul><li>frontend_bound</li><li>backend_bound</li><li>retiring</li></ul>                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

| <ul><li>backend_bound</li><li>retiring</li></ul>                                                                                                                      | Topdown_L1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

| retiring                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

| _                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

| bad speculation                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

| - bud_speculation                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

| • ipc                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

| -                                                                                                                                                                     | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Spec_Operation |

| -                                                                                                                                                                     | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Memory         |