# **AMBA-PV Extensions to TLM**

Version 2.0

# **User Guide**

Non-Confidential

Issue 14

Copyright  $\ @$  2014–2018, 2020–2024 Arm Limited (or  $\ 100962\_0200\_14\_en$  its affiliates).

#### AMBA-PV Extensions to TLM User Guide

This document is Non-Confidential.

Copyright © 2014-2018, 2020-2024 Arm Limited (or its affiliates). All rights reserved.

This document is protected by copyright and other intellectual property rights.

Arm only permits use of this document if you have reviewed and accepted Arm's Proprietary Notice found at the end of this document.

This document (100962\_0200\_14\_en) was issued on 2024-09-16. There might be a later issue at http://developer.arm.com/documentation/100962

The product version is 2.0.

See also: Proprietary Notice | Product and document information | Useful resources

#### **Start Reading**

If you prefer, you can skip to the start of the content.

#### Intended audience

This document is written for experienced hardware and software developers to aid the development of models that are compatible with TLM 2.0 and communicate over AMBA buses.

You must be familiar with:

- The basic concepts of C++ such as classes and inheritance

- SystemC and TLM standards

#### Inclusive language commitment

Arm values inclusive communities. Arm recognizes that we and our industry have used language that can be offensive. Arm strives to lead the industry and create change.

This document includes language that can be offensive. We will replace this language in a future issue of this document.

To report offensive language in this document, email terms@arm.com.

#### Feedback

Arm welcomes feedback on this product and its documentation. To provide feedback on the product, create a ticket on https://support.developer.arm.com.

To provide feedback on the document, fill the following survey: https://developer.arm.com/documentation-feedback-survey.

# **Contents**

| 1. Introduction to AMBA-PV Extensions to TLM 2.0                        | 6  |

|-------------------------------------------------------------------------|----|

| 1.1 AMBA-PV classes and interfaces                                      | 6  |

| 2. AMBA-PV extension class                                              | 8  |

| 2.1 Attributes and methods                                              | 10 |

| 2.1.1 Class definitions                                                 | 10 |

| 2.1.2 Constructors, copying, and addressing                             | 14 |

| 2.1.3 Default values and modifiability of attributes                    | 14 |

| 2.1.4 Burst length attribute                                            | 16 |

| 2.1.5 Burst size attribute                                              | 16 |

| 2.1.6 Burst type attribute                                              | 17 |

| 2.1.7 ID attribute                                                      | 17 |

| 2.1.8 Privileged attribute                                              | 18 |

| 2.1.9 Non-secure attribute                                              | 18 |

| 2.1.10 Exclusive attribute                                              | 18 |

| 2.1.11 Locked attribute                                                 | 19 |

| 2.1.12 Bufferable attribute                                             | 20 |

| 2.1.13 Modifiable/cacheable attribute                                   | 20 |

| 2.1.14 Read allocate attribute                                          | 20 |

| 2.1.15 Write allocate attribute                                         | 21 |

| 2.1.16 Read other allocate attribute                                    | 21 |

| 2.1.17 Write other allocate attribute                                   | 22 |

| 2.1.18 Quality of Service (QoS) attribute                               | 22 |

| 2.1.19 Region attribute                                                 | 22 |

| 2.1.20 Domain attribute                                                 | 23 |

| 2.1.21 Snoop attribute                                                  | 23 |

| 2.1.22 Bar attribute                                                    | 24 |

| 2.1.23 DVM messages                                                     | 24 |

| 2.1.24 Response attribute                                               | 27 |

| 2.1.25 ACE response attributes PassDirty and IsShared                   | 28 |

| 2.1.26 ACE snoop response attributes DataTransfer, Error, and WasUnique | 29 |

| 2.1.27 Response array attribute                                         | 30 |

| 2.1.28 Data organization                    | 31 |

|---------------------------------------------|----|

| 2.1.29 Direct memory interface              | 31 |

| 2.1.30 Debug transport interface            | 31 |

| 2.1.31 Physical address space attribute     | 32 |

| 2.1.32 Atomic attributes                    | 32 |

| 2.1.33 Untranslated transactions attributes | 32 |

| 2.2 AMBA signal mapping                     | 33 |

| 2.3 Mapping for AMBA buses                  | 34 |

| 2.4 Basic transactions                      | 36 |

| 2.4.1 Fixed burst example                   | 36 |

| 2.4.2 Incremental burst example             | 37 |

| 2.4.3 Wrapped burst example                 | 38 |

| 2.4.4 Unaligned burst example               | 39 |

| 3. AMBA-PV classes                          | 40 |

| 3.1 Class description                       | 40 |

| 3.1.1 AMBA-PV extension                     | 40 |

| 3.1.2 Core interfaces                       | 41 |

| 3.1.3 User layer                            | 43 |

| 3.1.4 Sockets                               | 44 |

| 3.1.5 ACE sockets                           | 44 |

| 3.1.6 Bridges                               | 45 |

| 3.1.7 Memory                                | 47 |

| 3.1.8 Exclusive monitor                     | 48 |

| 3.1.9 Bus decoder                           | 48 |

| 3.1.10 Protocol checker                     | 49 |

| 3.1.11 Signaling                            | 50 |

| 3.1.12 User and transport layers            | 52 |

| 3.1.13 Transaction memory management        | 55 |

| 3.2 Class summary                           | 55 |

| 3.2.1 List of classes and interfaces        | 55 |

| 3.2.2 Classes for virtual platforms         | 57 |

| 3.2.3 Classes for side-band signals         | 58 |

| 4. Example systems                          | 60 |

| 4.1 Configuring the examples                | 60 |

| 4.2 Bridge example                          | 60 |

| 4.2.1 Building and running the bridge example       | 61 |

|-----------------------------------------------------|----|

| 4.3 Debug example                                   | 62 |

| 4.3.1 Building and running the debug example        | 62 |

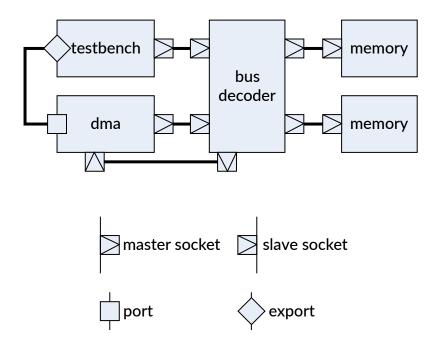

| 4.4 DMA example                                     | 64 |

| 4.4.1 Building and running the DMA example          | 64 |

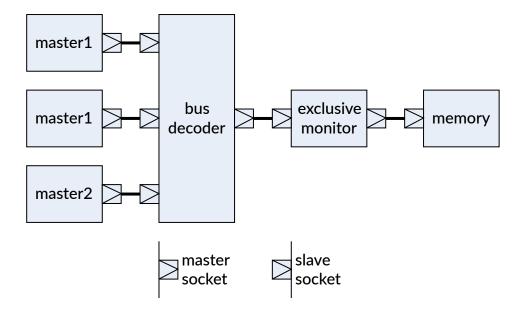

| 4.5 Exclusive example                               | 67 |

| 4.5.1 Building and running the exclusive example    | 67 |

| 4.6 Atomic example                                  | 68 |

| 5. Creating AMBA-PV compliant models                | 70 |

| 5.1 Creating an AMBA-PV master                      | 70 |

| 5.2 Creating an AMBA-PV slave                       | 70 |

| 5.3 Creating an AMBA-PV interconnect                | 71 |

| 5.4 Creating an AMBA-PV ACE master                  | 72 |

| 5.5 Creating an AMBA-PV ACE slave                   | 72 |

| 6. AMBA-PV protocol checker                         | 73 |

| 6.1 AMBA protocol check selection: check_protocol() | 73 |

| 6.2 Recommended checks: recommend_on()              | 74 |

| 6.3 Checks that the protocol checker performs       | 74 |

| 6.3.1 About the protocols                           | 74 |

| 6.3.2 Architecture checks                           | 75 |

| 6.3.3 Extension checks                              | 75 |

| 6.3.4 Address checks                                | 76 |

| 6.3.5 Data checks                                   | 77 |

| 6.3.6 Response checks                               | 77 |

| 6.3.7 Exclusive access checks                       | 78 |

| 6.3.8 Cacheability checks                           | 79 |

| 6.3.9 Atomic checks                                 | 80 |

| Proprietary Notice                                  | 81 |

| Product and document information                    | 83 |

| Product status                                      | 83 |

| Revision history                                    | 83 |

| Conventions                                         | 85 |

| Useful resources                                    | 87 |

# 1. Introduction to AMBA-PV Extensions to TLM 2.0

The AMBA-PV Extensions to TLM 2.0 (AMBA-PV) map AMBA® buses on top of TLM 2.0.

Its key features are:

- Dedicated to the *Programmer's View* (PV), it focuses on high-level, functionally accurate, transaction modeling. Low-level signals, for example, channel handshake, are not important at that level

- It is the standard for modeling AMBA® ACE, AXI, AHB, and APB buses with TLM 2.0.

- Targeted at Loosely Timed (LT) coding style of TLM 2.0, it includes blocking transport, Direct Memory Interface (DMI), and debug interfaces.

- Interoperable, it permits models using the mapped AMBA® buses to work in an Accelleracompliant SystemC environment.

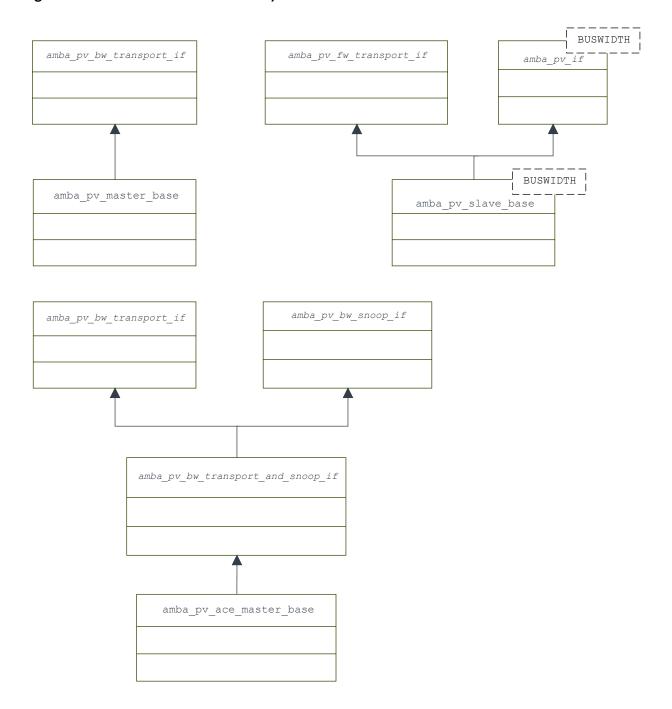

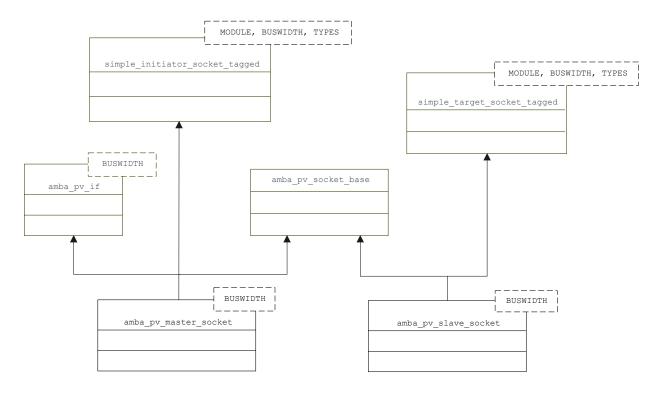

## 1.1 AMBA-PV classes and interfaces

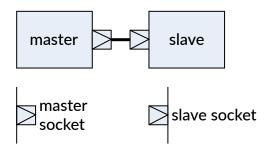

AMBA-PV classes and interfaces are layered on top of the TLM 2.0 library. AMBA-PV specializes TLM 2.0 classes and interfaces to handle AMBA® buses control information such as Secure, Non-secure, and privileged.

In addition, AMBA-PV provides a framework that minimizes the effort that is required to write TLM 2.0 models that communicate over the AMBA® buses.

AMBA® buses add the following specific features to the TLM 2.0 Generic Payload (GP):

- Addressing options support.

- Protection-unit support.

- Cache support.

- Atomic accesses support, including exclusive accesses and atomic transactions.

To use atomic transactions directly, use Fast Models version 11.27 or later.

- Quality of Service (QoS) support.

- Multiple region support.

- Coherency support.

- Barrier transactions.

- Distributed Virtual Memory (DVM) support.

The AMBA-PV extensions to the TLM 2.0 Base Protocol (BP) covers the following:

- Definition of AMBA-PV extension and trait classes.

- Specialization of TLM 2.0 sockets and interfaces.

- Use of TLM 2.0 b\_transport() blocking transport interface only.

In addition, AMBA-PV defines classes and interfaces for the modeling of side-band signals, for example, interrupts.

# 2. AMBA-PV extension class

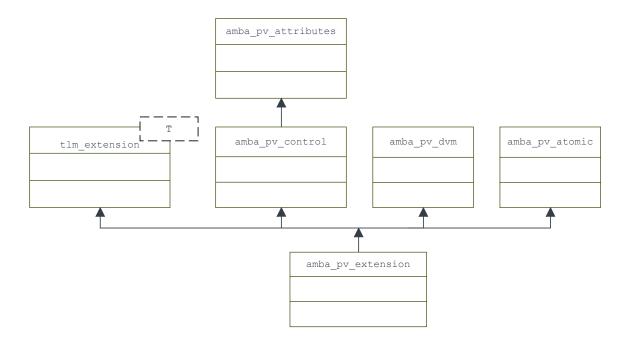

AMBA-PV defines an extension class amba\_pv\_extension, to the TLM 2.0 GP class tlm generic payload.

This extension class targets AMBA® buses modeling, using an LT coding style, and features attributes for the modeling of:

- Burst length, from 1 to 256 data transfers per burst.

- Burst transfer size of 8-1024 bits.

- Wrapping, incrementing, and non-incrementing burst types.

- Atomic accesses using exclusive accesses, locked accesses, or atomic transactions.

- Arm recommends that you use locked accesses only to support legacy devices, because of their impact on the interconnect performance and their unavailability in AXI4 and ACE.

- The AMBA-PV bus decoder model does not support locked accesses.

- To use atomic transactions directly, use Fast Models version 11.27 or later.

- System-level caching and buffering control.

- Secure and privileged accesses.

- Quality of Service (QoS) indication.

- Multiple regions.

- Cache coherency transactions (ACE-Lite).

- Bi-directional cache coherency transactions (ACE).

- Distributed Virtual Memory (DVM) transactions.

This extension class does not model any of the following:

- Separate address/control and data phases.

- Separate read and write data channels.

- Ability to issue multiple outstanding addresses.

- Out-of-order transaction completion.

- Optional extensions that cover signaling for low-power operation.

- Split transactions.

- Undefined-length bursts.

- User-defined signals.

Undefined-length bursts are specific to the AHB bus. They can be modeled as incrementing bursts of defined length, providing the master knows the total transfer length. AHB bus specifies a 1KB address boundary that bursts must not cross. This limits the length of an undefined-length burst.

It additionally supports unaligned burst start addresses and unaligned write data transfers using byte strobes.

AMBA-PV defines a new trait class amba pv protocol types that features:

- Support for most of the TLM 2.0 BP rules.

- Word length equals burst size.

- No part-words.

- Byte enables on write transactions only.

- Byte enable length is a multiple of the burst size.

- Simulated endianness equals host endianness.

This class is used for the TYPES template parameter with TLM 2.0 classes and interfaces.

When using amba\_pv\_protocol\_types with TLM 2.0 classes and interfaces, the following additional rules apply to the TLM 2.0 GP attributes:

- The data length attribute must be greater than or equal to the burst size times the burst length.

- The streaming width attribute must be equal to the burst size for a fixed burst.

- The byte enable pointer attribute must be NULL on read transactions.

- If nonzero, the byte enable length attribute shall be a multiple of the burst size on write transactions.

- If the address attribute is not aligned on the burst size, only the address of the first burst beat must be unaligned, the subsequent beats addresses being aligned.

This does not enforce any requirements on slaves for read transactions, and this must be represented with appropriate byte enables for write transactions.

You must use the AMBA-PV Extension class with AMBA-PV sockets, that is, sockets parameterized with the <code>amba\_pv\_protocol\_types</code> traits class. This follows the rules set out in the section Define a new protocol traits class containing a typedef for tlm\_generic\_payload of the IEEE Standard for Standard SystemC® Language Reference Manual, January 2012. The AMBA-PV Extension class is a mandatory extension for the modeling of AMBA® buses. For more information, see the section Non-ignorable and mandatory extensions in the same document.

## 2.1 Attributes and methods

The AMBA-PV extension classes contain a set of private attributes and a set of public access functions to get and set the values of these attributes. This section describes these attributes and functions.

#### 2.1.1 Class definitions

This section describes the class definitions.

The amba\_pv\_control base class includes attributes that relate to system-level caches, protection units, atomic accesses, QoS, multiple regions, cache coherency, barrier transactions, and DVM. The amba\_pv\_control class is used as an argument to the user layer interface methods.

```

namespace amba pv {

enum amba pv domain t {

AMBA_PV_NON_SHAREABLE = 0x0,

AMBA_PV_INNER_SHAREABLE = 0x1,

AMBA PV OUTER SHAREABLE = 0x2,

AMBA PV SYSTEM

};

std::string amba_pv_domain_string(amba_pv_domain_t);

enum amba pv bar t {

AMBA PV RESPECT BARRIER = 0x0,

AMBA PV MEMORY BARRIER = 0x1,

AMBA PV IGNORE BARRIER = 0x2,

AMBA PV SYNCHRONISATION BARRIER = 0x3

};

std::string amba_pv_bar_string(amba_pv_bar_t);

enum amba_pv_snoop_t {

AMBA PV READ NO SNOOP

AMBA PV READ ONCE

AMBA PV READ ONCE

AMBA PV READ CLEAN

= 0 \times 0,

= 0x2,

AMBA PV READ NOT SHARED DIRTY = 0x3,

AMBA PV READ SHARED = 0x1,

AMBA PV READ UNIQUE = 0x7,

AMBA_PV_CLEAN_UNIQUE

= 0xB,

AMBA PV CLEAN SHARED

AMBA PV CLEAN INVALID

= 0x9

AMBA_PV_MAKE_UNIQUE

= 0xC,

AMBA PV MAKE UNIQUE

AMBA PV MAKE INVALID

AMBA PV WRITE NO SNOOP

AMBA PV WRITE UNIQUE

AMBA PV WRITE LINE UNIQUE

AMBA PV WRITE BACK

AMBA PV WRITE CLEAN

= 0xD,

= 0x0,

= 0 \times 0

= 0x1,

= 0x3,

= 0x2,

AMBA PV EVICT

= 0x4,

AMBA PV BARRIER

AMBA PV DVM COMPLETE

= 0x0,

= 0xE,

AMBA PV DVM MESSAGE

= 0xF

};

std::string amba pv snoop read string(amba pv snoop t,amba pv domain t,amba pv bar t);

std::string amba pv snoop write string (amba pv snoop t, amba pv domain t, amba pv bar t);

enum amba_pv_physical_address_space_t {

AMBA_PV_SECURE_PAS = 0x0,

AMBA_PV_NON_SECURE_PAS = 0x1,

AMBA_PV_ROOT_PAS

AMBA_PV_REALM_PAS

= 0x2,

= 0 \times 3

};

class amba pv control {

```

```

public:

amba pv control();

void set_id(unsigned int);

unsigned int get_id() const;

void set privileged(bool = true);

bool is privileged() const;

void set_non_secure(bool = true);

bool is non_secure() const;

void set physical address space (amba pv physical address space t);

amba_pv_physical_address_space_t get_physical_address_space() const;

void set_instruction(bool = true);

bool is instruction() const;

void set exclusive(bool = true);

bool is exclusive() const;

void set_locked(bool = true);

bool is Tocked() const;

void set_bufferable(bool = true);

bool is bufferable() const;

void set cacheable(bool = true);

bool is cacheable() const;

void se\bar{t} read allocate (bool = true);

bool is read allocate() const;

void set write allocate(bool = true);

bool is write allocate() const;

void set modifiable(bool = true);

bool is modifiable() const;

void set_read_other_allocate(bool = true);

bool is read other allocate() const;

void set_write_other_allocate(bool = true);

bool is_write_other_allocate() const;

void set gathering (bool = true);

bool is gathering() const;

void set reordering(bool = true);

bool is_reordering() const;

void set_transient(bool = true);

bool is transient() const;

void set_translated_access(bool);

bool is translated access() const;

void set_mmu_flow_type(amba_pv_mmuflow_t mmu_flow_type);

amba_pv_mmuflow_t get_mmu_flow_type() const;

void set_qos(unsigned int);

unsigned int get_qos() const;

void set region (unsigned int);

unsigned int get_region() const;

void set snoop (amba pv snoop t);

amba pv snoop t get snoop() const;

void set_domain(amba_pv_domain_t);

amba_pv_domain_t get_domain() const;

void set_bar(amba_pv_bar_t);

amba pv bar t get bar() const;

void set_user(unsigned int);

unsigned int get_user() const;

};

enum amba_pv_resp_t {

AMBA PV OKAY =

= 0x0,

AMBA PV EXOKAY = 0 \times 1,

AMBA_PV_SLVERR

= 0x2,

AMBA PV DECERR

std::string amba pv resp string(amba pv resp t);

amba_pv_resp_t amba_pv_resp_from_tlm(tlm::tlm_response_status);

tlm::tlm_response_status amba_pv_resp_to_tlm(amba_pv_resp_t);

class amba_pv_response {

public:

amba pv response();

amba pv response (amba pv resp t);

void set resp(amba pv resp t);

amba_pv_resp_t get_resp() const;

bool is_okay() const;

void set okay();

bool is exokay() const;

```

```

void set exokay();

bool is slverr() const;

void set_slverr();

bool is decerr() const;

void set decerr();

bool is pass dirty() const;

void set_pass_dirty(bool=true);

bool is_shared() const;

void set shared(bool=true);

bool is_snoop_data_transfer() const;

void set snoop data transfer(bool=true);

bool is snoop error() const;

void set_snoop_error(bool=true);

bool is_snoop_was_unique() const;

void set_snoop_was_unique(bool=true);

void reset();

};

enum amba_pv_dvm_message_t {

AMBA PV TLB INVALIDATE

= 0x0,

AMBA PV BRANCH PREDICTOR INVALIDATE = 0x1,

AMBA PV PHYSICAL INSTRUCTION CACHE INVALIDATE = 0x2,

AMBA PV VIRTUAL INSTRUCTION CACHE INVALIDATE = 0x3,

AMBA_PV_SYNC

= 0x4,

AMBA PV HINT

};

std::string amba pv dvm message string(amba pv dvm message t);

enum amba_pv_dvm_os_t {

AMBA_PV_HYPERVISOR_OR_GUEST = 0x0,

AMBA PV GUEST

= 0x2,

AMBA_PV HYPERVISOR

= 0 \times 3

std::string amba_pv_dvm_os_string(amba_pv_dvm_os_t);

enum amba pv_dvm_security t {

AMBA PV_SECURE AND NON_SECURE = 0x0,

AMBA PV_SECURE ONLY = 0x2,

AMBA PV NON SECURE ONLY

};

std::string amba pv dvm security string(amba pv dvm security t);

class amba pv dvm {

public:

amba pv dvm();

void set dvm transaction(unsigned int);

unsigned int get dvm transaction() const;

void set_dvm_addītional_address(sc_dt::uint64);

bool is_dvm_additional_address_set() const;

sc dt:: uint 64 get dvm additional address() const;

void set dvm vmid(unsigned int);

bool is_dvm_vmid_set() const;

unsigned int get_dvm_vmid() const;

void set dvm asid(unsigned int);

bool is_dvm_asid_set() const;

unsigned int get_dvm_asid() const;

void set dvm virtual index(unsigned int);

bool is_dvm_virtual_index_set() const;

unsigned int get_dvm_virtual_index() const;

void set_dvm_completion(bool /* completion */ = true);

bool is dvm completion set() const;

void set_dvm_message_type(amba_pv_dvm_message_t);

amba_pv_dvm_message_t get_dvm_message_type() const;

void set_dvm_os(amba_pv_dvm_os_t);

amba_pv_dvm_os_t get_dvm_os() const;

void set_dvm_security(amba_pv_dvm_security_t);

amba pv dvm security t get dvm security() const;

void reset();

};

enum amba_pv_burst_t {

AMBA_PV_FIXED = 0,

AMBA_PV_INCR,

AMBA_PV_WRAP

std::string amba pv burst string(amba pv burst t);

```

```

class amba pv extension:

public tlm::tlm extension<amba_pv_extension>,

public amba_pv_control

public amba pv dvm {

public:

amba pv extension();

amba_pv_extension(size_t, const amba_pv_control *);

amba_pv_extension(size_t,

size t,

const amba_pv_control *,

amba_pv_burst_t);

virtual tlm::tlm_extension_base * clone() const;

virtual void copy_from(tlm::tlm_extension_base const &);

void set_length(unsigned int);

unsigned int get_length() const;

void set_size(unsigned int);

unsigned int get_size() const;

void set_burst(amba_pv_burst_t);

amba pv burst t get burst() const;

void set_resp(amba_pv_resp_t);

amba_pv_resp_t get_resp() const;

bool is_okay() const;

void set okay();

bool is exokay() const;

void set exokay();

bool is slverr() const;

void set_slverr();

bool is_decerr() const;

void set decerr();

bool is_pass_dirty() const;

void set pass dirty(bool);

bool is shared() const;

void set shared(bool);

bool is_snoop_data_transfer() const;

void set_snoop_data_transfer(bool=true);

bool is snoop error() const;

void set_snoop_error(bool=true);

bool is_snoop_was_unique() const;

void set_snoop_was_unique(bool=true);

void set_response_array_ptr(amba_pv_response*);

amba_pv_response* get_response_array_ptr();

void_set_response_array_complete(bool=true);

bool is response array complete();

void reset();

void reset (unsigned int,

const amba_pv_control *);

void reset (unsigned int,

unsigned int,

const amba pv control *,

amba pv burst t);

sc dt::uint64 amba pv address(const sc dt::uint64 &,

unsigned int,

unsigned int,

amba pv burst

unsigned int);

```

#### Related information

User layer on page 42

## 2.1.2 Constructors, copying, and addressing

The default constructors must set the AMBA-PV extension attributes to their default values.

The constructor amba\_pv\_extension(size\_t, const amba\_pv\_control \*) must set the burst size attribute value to the value passed as argument, and must set the attributes values of the amba\_pv\_control base class to the values of the attributes of the amba\_pv\_control object whose address is passed as argument, if not NULL.

The constructor amba\_pv\_extension(size\_t, size\_t, const amba\_pv\_control \*, amba\_pv\_burst\_t) must set the burst size attribute value to the value passed as argument, must set the burst length attribute value to the value passed as argument, must set the burst type attribute value to the value passed as argument, and must set the attribute values of the amba\_pv\_control base class to the values of the attributes of the amba\_pv\_control object whose address is passed as argument, if not NULL

The virtual method clone () must create a copy of the AMBA-PV extension object, including all its attributes.

The virtual method <code>copy\_from()</code> must modify the current AMBA-PV extension object by copying the attributes of another AMBA-PV extension object.

The global function amba\_pv\_address() must compute the address of a transfer or beat within a burst given the transaction address, burst length, burst size, burst type, and beat number.

## 2.1.3 Default values and modifiability of attributes

The master must set the value of every AMBA-PV extension attribute prior to passing the transaction object through an interface method call.

Table 2-1: Default values and modifiability of the AMBA-PV extension attributes

| Attribute    | Default value | Modifiable<br>by<br>interconnect | Modifiable<br>by slave | Notes                                                                                                                             |

|--------------|---------------|----------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Burst length | 1             | No                               | No                     | -                                                                                                                                 |

| Burst size   | 8             | No                               | No                     | -                                                                                                                                 |

| Burst type   | AMBA_PV_INCR  | No                               | No                     | -                                                                                                                                 |

| ID           | 0             | Yes                              | No                     | -                                                                                                                                 |

| Privileged   | false         | No                               | No                     | -                                                                                                                                 |

| Non-secure   | false         | No                               | No                     | -                                                                                                                                 |

| Instruction  | false         | No                               | No                     | -                                                                                                                                 |

| Exclusive    | false         | Yes                              | No                     | An example of Modifiable by interconnect is an exclusive monitor that flattens the exclusive access before passing it downstream. |

| Locked       | false         | No                               | No                     | -                                                                                                                                 |

| Bufferable   | false         | No                               | No                     | -                                                                                                                                 |

| Attribute                 | Default value               | Modifiable by interconnect | Modifiable<br>by slave | Notes                                                                                                                                        |

|---------------------------|-----------------------------|----------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Modifiable/<br>cacheable  | false                       | No                         | No                     | The modifiable attribute is identical to the cacheable attribute but has been renamed in AXI4 to better describe the required functionality. |

| Read allocate             | false                       | No                         | No                     | -                                                                                                                                            |

| Write allocate            | false                       | No                         | No                     | -                                                                                                                                            |

| Read other allocate       | false                       | No                         | No                     | -                                                                                                                                            |

| Write other allocate      | false                       | No                         | No                     | -                                                                                                                                            |

| QoS                       | 0                           | Yes                        | No                     | -                                                                                                                                            |

| Region                    | 0                           | No                         | No                     | -                                                                                                                                            |

| Domain                    | AMBA_<br>PV_NON_SHAREABLE   | No                         | No                     | -                                                                                                                                            |

| Snoop                     | AMBA_<br>PV_READ_NO_SNOOP   | No                         | No                     | AMBA_PV_WRITE_NO_SNOOP and AMBA_PV_READ_NO_SNOOP have the same encoding representation.                                                      |

| Bar                       | AMBA_PV_<br>RESPECT_BARRIER | No                         | No                     | -                                                                                                                                            |

| Response                  | AMBA_PV_OKAY                | Yes                        | Yes                    | -                                                                                                                                            |

| PassDirty                 | false                       | Yes                        | Yes                    | -                                                                                                                                            |

| IsShared                  | false                       | Yes                        | Yes                    | -                                                                                                                                            |

| DataTransfer              | false                       | Yes                        | Yes                    | Only a valid response to upstream snoops, typically from interconnect to master.                                                             |

| Error                     | false                       | Yes                        | Yes                    | Only a valid response to upstream snoops, typically from interconnect to master.                                                             |

| WasUnique                 | false                       | Yes                        | Yes                    | Only a valid response to upstream snoops, typically from interconnect to master.                                                             |

| ResponseArray             | null                        | No                         | No                     | -                                                                                                                                            |

| ResponseArray<br>complete | false                       | Yes                        | Yes                    | -                                                                                                                                            |

If an AMBA-PV extension object is re-used, the modifiability rules cease to apply at the end of the lifetime of the corresponding transaction instance. The rules re-apply if the AMBA-PV extension object is re-used for a new transaction.

After adding the AMBA-PV extension to a transaction object and passing that transaction object as an argument to an interface method call (b\_transport(), get\_direct\_mem\_ptr(), or transport\_dbg()), the master must not modify any of the AMBA-PV extension attributes during the lifetime of the transaction.

An interconnect can modify the ID attribute, but only before passing the corresponding transaction as an argument to an interface method call (b\_transport(), get\_direct\_mem\_ptr(), or transport\_dbg()) on the forward path. When the interconnect has passed a pointer to the AMBA-PV extension to a downstream model, it is not permitted to modify the ID of that extension object again during the entire lifetime of the corresponding transaction.

As a consequence of the above rule, the ID attribute is valid immediately on entering any of the method calls b\_transport(), get\_direct\_mem\_ptr(), or transport\_dbg(). Following the return from any of those calls, the ID attribute has the value set by the interconnect furthest downstream.

The interconnect and slave can modify the response attribute at any time between having first received the corresponding transaction object and the time at which they pass a response upstream by returning control from the <code>b\_transport()</code>, <code>get\_direct\_mem\_ptr()</code>, or <code>transport dbg()</code> methods.

The master can assume it is seeing the value of the AMBA-PV extension response attribute only after it has received a response for the corresponding transaction.

If the AMBA-PV extension is used for the direct memory or debug transport interfaces, the modifiability rules given here must apply to the appropriate attributes of the AMBA-PV extension, namely the ID, privileged, non-secure, and instruction attributes.

## 2.1.4 Burst length attribute

This attribute specifies the number of data transfers that occur within this burst.

It must have a value between 1 and 256 for defined-length burst. Additional restrictions apply depending on the value of the burst type attribute.

The method set\_length() must set this attribute to the value passed as argument. The method get length() must return the value of this attribute.

The default value of this attribute must be 1, for single transfer.

This attribute is specific to the AXI, ACE, and AHB buses. It is ignored for transactions modeling transfers on the APB bus.

The maximum burst length value for AXI3 and AHB buses is 16, and the maximum value for AXI4, AXI5, and ACE buses is 256.

#### Related information

Extension checks on page 75

#### 2.1.5 Burst size attribute

This attribute specifies the maximum number of data bytes to transfer in each beat, or data transfer, within a burst. It must have a value of 1, 2, 4, 8, 16, 32, 64, or 128.

The method set\_size() must set this attribute to the value passed as argument. The method get\_size() must return the value of this attribute.

The value of this attribute must be less than or equal to BUSWIDTH / 8, where BUSWIDTH is the template parameter of the socket classes from AMBA-PV (or classes derived from these) and expressed in bits.

The default value of this attribute must be 8, for 64-bit wide transfer.

This attribute is specific to the AXI, ACE, and AHB buses. It is ignored for transactions modeling transfers on the APB bus.

## 2.1.6 Burst type attribute

This attribute specifies the burst type.

The method set\_burst() must set this attribute to the value passed as an argument. The method get burst() must return the value of this attribute.

A transaction with a burst type attribute value of AMBA PV WRAP must have an aligned address.

AXI5 has an exception to this rule. According to the AMBA AXI Protocol Specification, an AtomicCompare transaction of type AMBA\_PV\_WRAP must have an address that aligns with half the total transaction size. Total transaction size = burst size\*burst length.

The default value of this attribute must be AMBA PV INCR, for incrementing burst.

This attribute is specific to the AXI, ACE, and AHB buses. It is ignored for transactions modeling transfers on the APB bus.

### 2.1.7 ID attribute

This attribute is mainly used for exclusive accesses.

The method set\_id() must set this attribute to the value passed as argument. The method get\_id() must return the value of this attribute.

This attribute must be set by the master originating the transaction. The interconnect must modify this attribute to ensure its uniqueness across all its masters before passing the transaction to the addressed slave.

The default value of this attribute must be 0.

This attribute is specific to the AXI, ACE, and AHB buses. It is ignored for transactions modeling transfers on the APB bus.

## 2.1.8 Privileged attribute

This attribute enables masters to indicate their processing mode. A privileged transaction typically has a greater level of access within the system.

The method set\_privileged() must set this attribute to the value passed as argument. The method is privileged() must return the value of this attribute.

The default value of this attribute must be false.

This attribute is specific to the AXI, ACE, and AHB buses. It is ignored for transactions modeling transfers on the APB bus.

#### 2.1.9 Non-secure attribute

This attribute enables differentiating between secure and non-secure transactions.

The method set\_non\_secure() must set this attribute to the value passed as argument. The method is non secure() must return the value of this attribute.

The default value of this attribute must be false.

This attribute is specific to the AXI and ACE buses. It is ignored for transactions modeling transfers on the AHB and APB buses.

#### 2.1.10 Exclusive attribute

This attribute selects exclusive access, and the response attribute indicates the success or failure of the exclusive access.

The method set\_exclusive() must set this attribute to the value passed as argument. The method is exclusive() must return the value of this attribute.

The AMBA-PV package provides an exclusive monitor model that supports exclusive access and that can be added before your slave. It removes the requirement for your slave to model additional logic to support exclusive access.

Arm recommends that masters do not use the direct memory interface for exclusive accesses.

The address of an exclusive access must be aligned to the total number of bytes in the transaction as determined by the value of the burst size attribute multiplied by the value of the burst length attribute.

The number of bytes to be transferred in an exclusive access must be a power of 2 and less than or equal to 128.

Arm recommends that every exclusive write has an earlier outstanding exclusive read with the same value for the ID attribute.

Arm recommends that the value of the address, burst size, and burst length attributes of an exclusive write with a given value for the ID attribute is the same as the value of the address, burst size, and burst length attributes of the preceding exclusive read with the same value for the ID attribute.

An amba PV Exokay value for the response attribute can only be given to an exclusive access.

Atomic transactions cannot be exclusive, according to the AMBA AXI Protocol Specification.

This attribute must not have the value true together with the locked attribute.

The default value of this attribute must be false.

This attribute is specific to the AXI and ACE buses. It is ignored for transactions modeling transfers on the AHB and APB buses.

#### Related information

Exclusive monitor on page 47 Response attribute on page 27

#### 2.1.11 Locked attribute

Locked transactions, those for which this attribute has the value true, require that the interconnect prevents any other transactions occurring while the locked sequence is in progress and can thus have an impact on the interconnect performance.

The method set\_locked() must set this attribute to the value passed as argument. The method is locked() must return the value of this attribute.

Arm recommends that locked accesses are only used to support legacy devices. Locked transactions are currently not supported by the AMBA-PV bus decoder.

This attribute must not have the value true together with the exclusive attribute.

The default value of this attribute must be false.

This attribute is specific to the AXI3 and AHB buses. It is ignored for transactions modeling transfers on the APB, AXI4, AXI5, and ACE buses.

#### 2.1.12 Bufferable attribute

This attribute specifies whether or not the associated transaction is bufferable.

The method set\_bufferable() must set this attribute to the value passed as argument. The method is bufferable() must return the value of this attribute.

A bufferable transaction can be delayed in reaching its final destination. This is usually only relevant to writes.

The default value of this attribute must be false.

This attribute is specific to the AXI and AHB buses. It is ignored for transactions modeling transfers on the APB bus.

#### 2.1.13 Modifiable/cacheable attribute

The modifiable attribute specifies whether the associated transaction is modifiable.

The methods set\_modifiable() and set\_cacheable() must set this attribute to the value passed as an argument. The methods is\_modifiable() and is\_cacheable() must return the value of this attribute.

For write transactions, a number of different writes can be merged together. For read transactions, a location can be pre-fetched or can be fetched only once for multiple reads. To determine if a transaction must be cached, use this attribute with the read allocate and write allocate attributes.

The default value of this attribute must be false.

This attribute is specific to the AXI and AHB buses. It is ignored for transactions modeling transfers on the APB bus.

The cacheable attribute used by the AXI3 and AHB buses has been renamed to this attribute for AXI4, AXI5, and ACE to better describe the required function of the attribute. The actual functionality is unchanged.

#### Related information

Read allocate attribute on page 20 Write allocate attribute on page 21

#### 2.1.14 Read allocate attribute

This attribute specifies whether or not this transaction must be allocated if it is a read and it misses in the cache.

The method set\_read\_allocate() must set this attribute to the value passed as argument. The method is read allocate() must return the value of this attribute.

The value of this attribute must not be set to true if the value of the modifiable attribute is set to false.

The default value of this attribute must be false.

This attribute is specific to the AXI and ACE buses. It is ignored for transactions modeling transfers on the AHB and APB buses.

#### 2.1.15 Write allocate attribute

This attribute specifies whether or not this transaction must be allocated if it is a write and it misses in the cache.

The method set\_write\_allocate() must set this attribute to the value passed as argument. The method is\_write\_allocate() must return the value of this attribute.

The value of this attribute must not be set to true if the value of the modifiable attribute is set to false.

The default value of this attribute must be false.

This attribute is specific to the AXI and ACE buses. It is ignored for transactions modeling transfers on the AHB and APB buses.

#### 2.1.16 Read other allocate attribute

This attribute indicates that the location could have been previously allocated in the cache because of a write transaction or because of the actions of another master.

The value of this attribute must not be set to true if the value of the modifiable attribute is set to false.

The method set\_read\_other\_allocate() sets this attribute to the value passed as argument. The method is read other allocate() returns the value of this attribute.

The default value of this attribute is false.

This attribute is specific to the AXI4, AXI5, and ACE buses. It is ignored for transactions modeling transfers on the AHB and APB buses.

To maintain compatibility with AXI3, this attribute may also be accessed using the write allocate attribute methods set write allocate().

#### 2.1.17 Write other allocate attribute

This attribute indicates that the location could have been previously allocated in the cache because of a read transaction or because of the actions of another master.

The method set\_write\_other\_allocate() sets this attribute to the value passed as argument. The method is write other allocate() returns the value of this attribute.

The value of this attribute must not be set to true if the value of the modifiable attribute is set to false.

The default value of this attribute is false.

This attribute is specific to the AXI4 and ACE buses. It is ignored for transactions modeling transfers on the AHB and APB buses.

To maintain compatibility with AXI3, this attribute may also be accessed using the read allocate attribute methods set read allocate() and is read allocate().

## 2.1.18 Quality of Service (QoS) attribute

This attribute supports Quality of Service (QoS) schemes.

The bus protocol does not specify the exact use of the QoS identifier but recommends that it is used as a priority indicator.

The method set\_qos() sets this attribute to the value passed as argument. The method get\_qos() returns the value of this attribute.

The default value of this attribute is 0, which indicates that the interface is not participating in any oos scheme.

This attribute is specific to the AXI4, AXI5, and ACE buses. It is ignored for transactions modeling transfers on the AXI3, AHB and APB buses.

For AXI4, AXI5, and ACE this indicator attribute value must be between 0 and 15 inclusive.

## 2.1.19 Region attribute

This attribute supports multiple region interfaces. It uniquely identifies a region.

The method set\_region() sets this attribute to the value passed as argument. The method get\_region() returns the value of this attribute.

The default value of this attribute is o.

This attribute is specific to the AXI4, AXI5, and ACE buses. It is ignored for transactions modeling transfers on the AXI3, AHB and APB buses.

For AXI4, AXI5, and ACE the value of this indicator attribute must be between 0 and 15 inclusive.

#### 2.1.20 Domain attribute

This attribute indicates the shareability domain for a transaction.

The method set\_domain() sets this attribute to the value passed as argument. The method get domain() returns the value of this attribute.

The default value of this attribute is AMBA PV NON SHAREABLE.

This attribute is specific to ACE buses. It is ignored for transactions modeling transfers on the AXI, AHB and APB buses.

The encoding of the value of this attribute exactly matches the encoding used on the ACE channels AWDOMAIN and ARDOMAIN.

## 2.1.21 Snoop attribute

This attribute specifies the transaction type for shareable transactions.

The method set\_snoop() sets this attribute to the value passed as argument. The method get snoop() returns the value of this attribute.

The default value of this attribute is encoded as 0 which for read transactions represents AMBA\_PV\_READ\_NO\_SNOOP and for write transactions AMBA\_PV\_WRITE\_NO\_SNOOP.

The meaning of a given snoop attribute value encoding is dependent on the domain and bar attribute values and whether the transaction is a read or a write.

This attribute is specific to ACE buses. It is ignored for transactions modeling transfers on the AXI, AHB, and APB buses.

The encoding of this attribute value exactly matches the encoding used on the ACE channels AWSNOOP and ARSNOOP.

For atomic transactions, AWSNOOP must be set to all zeros, according to the AMBA AXI Protocol Specification.

#### 2.1.22 Bar attribute

This attribute indicates barrier information for the transaction.

The method set\_bar() sets this attribute to the value passed as argument. The method get\_bar() returns the value of this attribute.

The default value of this attribute is AMBA PV RESPECT BARRIER.

This attribute is specific to ACE buses. It is ignored for transactions modeling transfers on the AXI, AHB and APB buses.

The encoding of this attribute value exactly matches the encoding used on the ACE channels AWBAR and ARBAR.

## 2.1.23 DVM messages

To provide a *Programmer's View* (PV) model of *Distributed Virtual Memory* (DVM) transactions, the AMBA-PV extension class contains a set of private attributes and a set of public access methods for DVM messages.

A given transaction only represents a DVM message if the snoop attribute is set to AMBA\_PV\_DVM\_MESSAGE.

DVM messages are specific to ACE and ACE-Lite buses. They are ignored for transactions modeling transfers on the AXI, AHB and APB buses.

#### 2.1.23.1 DVM default values

This section defines the DVM default values.

Table 2-2: DVM default values for the AMBA-PV extension attributes

| Attribute          | Default value                 | Default set status |

|--------------------|-------------------------------|--------------------|

| VMID               | 0                             | false              |

| ASID               | 0                             | false              |

| Virtual Index      | 0                             | false              |

| Completion         | false                         | -                  |

| Message type       | AMBA_PV_TLB_INVALIDATE        | -                  |

| Operating system   | AMBA_PV_HYPERVISOR_OR_GUEST   | -                  |

| Security           | AMBA_PV_SECURE_AND_NON_SECURE | -                  |

| Additional address | 0                             | false              |

| DVM transaction    | 0                             | -                  |

#### 2.1.23.2 DVM VMID attribute

This attribute defines the Virtual Machine Identifier for some DVM operations.

The method is\_dvm\_vmid\_set() returns true if this attribute has been set. If the VMID attribute has not been set then this attribute value should not be used.

The method get\_dvm\_vmid() returns the value of this attribute. The method set\_dvm\_vmid() sets the value of this attribute.

This attribute is not set by default. The default value of this attribute is o.

#### 2.1.23.3 DVM ASID attribute

This attribute defines the Address Space Identifier for some DVM operations.

The method is\_dvm\_asid\_set() returns true if this attribute has been set. If this attribute has not been set then this attribute value should not be used.

The method get\_dvm\_asid() returns the value of this attribute. The method set\_dvm\_asid() sets the value of this attribute.

This attribute is not set by default. The default value of this attribute is o.

#### 2.1.23.4 DVM Virtual Index attribute

You can use this attribute as part of the physical address by physical instruction cache invalidate DVM messages.

The method is\_dvm\_virtual\_index\_set() returns true if this attribute has been set. If this attribute has not been set then this attribute value should not be used.

The method get\_dvm\_virtual\_index() returns the value of this attribute. The method set dvm virtual index() sets the value of this attribute.

This attribute is not set by default. The default value of this attribute is o.

#### 2.1.23.5 DVM Completion attribute

This attribute identifies whether completion is required for DVM Sync messages.

The method is\_dvm\_completion\_set() returns true if this attribute has been set. The method set\_dvm\_completion() sets the value of this attribute.

By default this attribute has the value false.

#### 2.1.23.6 DVM Message type attribute

This attribute specifies the required DVM operation.

The method get\_dvm\_message\_type() returns the value of this attribute. The method set dvm message type() sets the value of this attribute.

By default this attribute has the value AMBA PV TLB INVALIDATE.

## 2.1.23.7 DVM Operating system attribute

This attribute specifies the operating system that the DVM operation applies to.

The method get\_dvm\_os() returns the value of this attribute. The method set\_dvm\_os() sets the value of this attribute.

By default this attribute has the value AMBA PV HYPERVISOR OR GUEST.

#### 2.1.23.8 DVM Security attribute

This attribute specifies how the DVM operation applies to the secure and non-secure worlds.

The method get\_dvm\_security() returns the value of this attribute. The method set\_dvm\_security() sets the value of this attribute.

By default this attribute has the value AMBA PV SECURE AND NON SECURE.

#### 2.1.23.9 DVM Additional address attribute

This attribute defines the additional address required by some DVM operations.

The method is\_dvm\_additional\_address\_set() returns true if this attribute has been set. If this attribute has not been set then this attribute value should not be used.

The method  $get_{dvm_additional_address()}$  returns the value of this attribute. The method  $set_{dvm_additional_address()}$  sets the value of this attribute.

This attribute is not set by default. The default value of this attribute is o.

#### 2.1.23.10 DVM transaction encoding

For ACE buses the DVM attributes are packed and encoded into the least significant 32 bits of the address channel.

The method get\_dvm\_transaction() returns the value of the VMID, ASID, Virtual Index, Completion, Message type, Operating system, and Security attributes as they would be packed and encoded on the address channel.

The method set\_dvm\_transaction() sets the value of the VMID, ASID, Virtual Index, Completion, Message type, Operating system, and Security attributes using a single 32-bit value encoded as the attributes would be packed and encoded on the address channel.

## 2.1.24 Response attribute

This section describes the response attribute.

The method set\_resp() must set the response attribute to the value passed as argument. The method get\_resp() must return the value of the response attribute.

The method is\_okay() must return true if and only if the value of the response attribute is AMBA\_PV\_OKAY. The method set\_okay() must set the value of the response attribute to AMBA\_PV\_OKAY.

The method is\_exokay() must return true if and only if the value of the response attribute is AMBA\_PV\_EXOKAY. The method set\_exokay() must set the value of the response attribute to AMBA\_PV\_EXOKAY.

The method is\_slverr() must return true if and only if the value of the response attribute is AMBA\_PV\_SLVERR. The method set\_slverr() must set the value of the response attribute to AMBA\_PV\_SLVERR.

The method is\_decerr() must return true if and only if the value of the response attribute is AMBA\_PV\_DECERR. The method set\_decerr() must set the value of the response attribute to AMBA\_PV\_DECERR.

The method is\_incomplete() must return true if and only if the value of the response attribute is AMBA\_PV\_INCOMPLETE. The method set\_incomplete() must set the value of the response attribute to AMBA\_PV\_INCOMPLETE.

#### Table 2-3: AMBA-PV responses

| Value          | Interpretation                                                                                                      |

|----------------|---------------------------------------------------------------------------------------------------------------------|

| AMBA_PV_OKAY   | A normal access success, or an exclusive access failure.                                                            |

| AMBA_PV_EXOKAY | Either the read or write portion of an exclusive access has been successful.                                        |

| AMBA_PV_SLVERR | The access has reached the slave successfully, but the slave returned an error condition to the originating master. |

| AMBA_PV_DECERR | There is no slave at the transaction address. This is typically generated by an interconnect component.             |

| Value              | Interpretation                                   |

|--------------------|--------------------------------------------------|

| AMBA_PV_INCOMPLETE | The slave did not attempt to perform the access. |

The response attribute must be set to AMBA\_PV\_OKAY by the master, and might be overwritten by the slave or the interconnect.

If the slave is able to execute the transaction, it must set the response attribute to AMBA\_PV\_OKAY. If not, the slave must set the response attribute to AMBA\_PV\_SLVERR.

If the interconnect is able to pass the transaction downstream to the addressed slave, it must not overwrite the response attribute. If not, the interconnect must set the response attribute to AMBA\_PV\_DECERR.

The default value of the response attribute must be AMBA PV OKAY.

The slave or interconnect is responsible for setting the response attribute before returning control from the b transport() method of the TLM 2.0 blocking transport interface.

Arm recommends that the master always checks the value of the response attribute after the completion of the transaction.

The global function <code>amba\_pv\_resp\_string()</code> must return the response value passed as argument as a text string.

The global function <code>amba\_pv\_resp\_from\_tlm()</code> must translate the TLM 2.0 response status value passed as argument into an AMBA-PV response value. The global function <code>amba\_pv\_resp\_to\_tlm()</code> must translate the AMBA-PV response value passed as argument into a TLM 2.0 response status value.

Table 2-4: Translation between AMBA-PV response and TLM 2.0 response status

| AMBA-PV response   | TLM 2.0 response status                                                                                          |

|--------------------|------------------------------------------------------------------------------------------------------------------|

| AMBA_PV_OKAY       | TLM_OK_RESPONSE                                                                                                  |

| AMBA_PV_EXOKAY     | TLM_OK_RESPONSE. The exclusive attribute of the associated transaction must have a value of true.                |

| AMBA_PV_SLVERR     | TLM_GENERIC_ERROR_RESPONSE, TLM_COMMAND_ERROR_RESPONSE, TLM_BURST_ERROR_RESPONSE, TLM_BYTE_ENABLE_ERROR_RESPONSE |

| AMBA_PV_DECERR     | TLM_ADDRESS_ERROR_RESPONSE                                                                                       |

| AMBA_PV_INCOMPLETE | TLM_INCOMPLETE_RESPONSE                                                                                          |

## 2.1.25 ACE response attributes PassDirty and IsShared

On ACE and ACE-Lite buses the additional response attributes PassDirty and IsShared are supported.

When true the PassDirty attribute indicates that before the snoop process, the cache line was held in a Dirty state and the responsibility for writing the cache line back to memory is being passed to the initiating master or interconnect.

The method is\_pass\_dirty() returns the value of the response PassDirty signal. The method set pass dirty() sets the value of the PassDirty attribute.

The default value of the PassDirty attribute is false.

When true the IsShared attribute indicates that the snooped cache retains a copy of the cache line after the snoop process has completed.

The method is\_shared() returns the value of the response IsShared attribute. The method set shared() sets the value of the IsShared attribute.

The default value of the IsShared attribute is false.

## 2.1.26 ACE snoop response attributes DataTransfer, Error, and WasUnique

On ACE buses additional snoop response attributes DataTransfer, Error and WasUnique are supported.

When true the DataTransfer attribute indicates that the snoop response includes a transfer of data.

The method is\_snoop\_data\_transfer() returns the value of the DataTransfer attribute. The method set snoop data transfer() sets the value of the DataTransfer attribute.

The default value of the DataTransfer attribute is false.

When true the Error attribute indicates that the snooped cache line is in error.

The method is\_snoop\_error() returns the value of the Error attribute. The method set snoop error() sets the value of the Error attribute.

The default value of the Error attribute is false.

When true the WasUnique attribute indicates that the snooped cache line was held in a Unique state before the snoop process.

The method is\_snoop\_was\_unique() returns the value of the snoop response WasUnique attribute. The method set\_snoop\_was\_unique() sets the value of the WasUnique attribute.

The default value of the WasUnique attribute is false.

## 2.1.27 Response array attribute

The response array provides an alternative path for slaves to return response status; with a separate response status for each beat of a burst transaction.

The method <code>get\_response\_array\_ptr()</code> returns a pointer to the response array or null if the master has not set an array response pointer. The method <code>set\_response\_array\_ptr()</code> sets a pointer to a response array.

The method set\_response\_array\_complete() is used by the slave to set the response array completion flag that when true indicates that the elements of the response array have been set with response data. The method is\_response\_array\_complete() returns the status of the response array completion flag.

If a response array is going to be made available it is the responsibility of the master to set the response array pointer. The size of the response array must be at least as large as the burst length attribute.

A slave can choose to use the response attribute to report response status with a single response for the entire transaction even if a response array has been made available. But a slave can also optionally check for a response array and if an array pointer is available set the response status in the response array instead of using the response attribute. The slave must not set elements of the response array beyond the value of the burst length attribute.

If a slave uses the response array it must set the response array completion flag to true.

The master reads response status from the response attribute unless it has both set an array response pointer and the slave has set the response array completion status to true.

## 2.1.27.1 Response array element attributes

These attributes have the same semantics and accessors as the equivalent response attributes.

Table 2-5: AMBA-PV response array element attributes

| Attribute    | Default value | Set methods                                                                 | Get methods                                                             |

|--------------|---------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------|

| Response     | AMBA_PV_OK    | <pre>set_resp(), set_okay(), set_exokay(), set_slverr(), set_decerr()</pre> | <pre>get_resp(), is_okay(), is_exokay(), is_slverr(), is_decerr()</pre> |

| PassDirty    | false         | set_pass_dirty()                                                            | is_pass_dirty()                                                         |

| IsShared     | false         | set_is_shared()                                                             | is_shared()                                                             |

| DataTransfer | false         | set_snoop_data_transfer()                                                   | is_snoop_data_transfer()                                                |

| Error        | false         | set_snoop_error()                                                           | is_snoop_error()                                                        |

| WasUnique    | false         | set_snoop_was_unique()                                                      | is_snoop_was_unique()                                                   |

#### Related information

Response attribute on page 27

ACE response attributes PassDirty and IsShared on page 28

ACE snoop response attributes DataTransfer, Error, and WasUnique on page 29

## 2.1.28 Data organization

In general, the organization of the AMBA-PV data array is in "bus order", independent of the organization of local storage within the master or the slave.

The contents of the data and byte enable arrays must be interpreted using the burst size attribute of the AMBA-PV extension. The size of a transferred word, or beat, within a transaction, is defined by the burst size attribute. The data array must not contain part-word, even when the transaction address is unaligned.

The word boundaries within the data and byte enable arrays must be address-aligned, that is, they must fall on addresses that are integer multiples of the burst size. The data length attribute must be greater than or equal to the burst size times the burst length.

The local address of a word or beat within the data array is given by the amba\_pv\_address() function:

```

\verb|amba_pv_address| (address, burst_length, burst_size, burst_type, N); \\

```

where N denotes the beat number as in 1-16.

## 2.1.29 Direct memory interface

For the AMBA-PV protocol, any of the AMBA-PV extension attributes can further indicate the address of the requested DMI access. The master must set them.

The slave can service DMI requests differently depending on the value of any AMBA-PV extension attributes. Arm recommends that the master sets all AMBA-PV extension attributes before requesting DMI access.

#### Related information

Default values and modifiability of attributes on page 14

## 2.1.30 Debug transport interface

For the AMBA-PV protocol, any of the AMBA-PV extension attributes can further indicate the address of the debug access. The master must set them.

The slave can service debug accesses differently depending on the value of any AMBA-PV extension attributes. Arm® recommends that the master sets all AMBA-PV extension attributes before performing debug accesses.

#### Related information

Default values and modifiability of attributes on page 14

## 2.1.31 Physical address space attribute

This attribute enables differentiating between secure, non-secure, root, or realm transactions.

The method set\_physical\_address\_space() sets this attribute to the value passed as the argument. The method get physical address space() returns the value of this attribute.

The default value is secure (AMBA PV SECURE PAS).

#### 2.1.32 Atomic attributes

The AWATOP atomic signals are modeled by class amba\_pv\_atomic, which amba\_pv\_extension inherits from.

amba pv atomic has three members that model AWATOP:

- amba\_pv\_atomic\_op\_t m\_atomic\_op

- amba\_pv\_atomic\_subop\_t m\_atomic\_subop

- amba\_pv\_atomic\_endianness\_t m\_atomic\_endianness

See the inline comments in amba pv atomic.h for detailed explanations.

As only a subset of enum values can form a valid signal, the amba\_pv\_atomic class has some helper functions to check if the member represents a valid signal. See the comments in the amba\_pv\_atomic op t type definition for details.

Atomic signals are supported for AXI5, ACE5-Lite, and ACE5-LiteDVM.

#### 2.1.33 Untranslated transactions attributes

AxMMUFLOW is the only signal to support untranslated transactions that is modeled. It is modeled as m\_mmu\_flow\_type.

The helper functions is\_translated\_access() and set\_translated\_access() rely on the value of m\_mmu\_flow\_type. A value of AxMMUATST indicates that the transaction has already undergone PCIe ATS translation. It is equivalent to AxMMUFLOW[0] when AxMMUFLOW[1] is deasserted, according to the AMBA AXI Protocol Specification.

## 2.2 AMBA signal mapping

This section describes the relationships between the AMBA® hardware signals and the private attributes of the AMBA-PV extension and the TLM 2.0 Generic Payload.

The tlm\_generic\_payload::m\_length attribute must be greater than or equal to amba\_pv\_addressing::m\_size multiplied by amba\_pv\_addressing::m\_length.

For fixed bursts, the tlm\_generic\_payload::m\_streaming\_width attribute holds the same information as the amba pv addressing::m size attribute.

#### Table 2-6: Address channels

| Signal    | Variable                                                                                                   | Description                   |

|-----------|------------------------------------------------------------------------------------------------------------|-------------------------------|

| AxID      | amba_pv_control::m_id                                                                                      | ID.                           |

| AxADDR    | tlm_generic_payload::m_address                                                                             | Address.                      |

| AxADDR    | amba_pv_extension::m_dvm_transaction                                                                       | DVM<br>message<br>attributes. |

| AxLEN     | amba_pv_extension::m_length                                                                                | Burst length.                 |

| AxSIZE    | amba_pv_extension::m_size                                                                                  | Burst size.                   |

| AxBURST   | amba_pv_extension::m_burst                                                                                 | Burst type.                   |

| AxLOCK    | amba_pv_control::m_exclusive amba_pv_control::m_locked                                                     | Lock type.                    |

| AxCACHE   | amba_pv_control::m_bufferable amba_pv_control::m_modifiable amba_pv_control::m_axcache_allocate_bit3       | Cache type.                   |

| AxPROT    | <pre>amba_pv_control::m_privileged amba_pv_control::m_non_secure amba_<br/>pv_control::m_instruction</pre> | Protection type.              |

| AxQOS     | amba_pv_control::m_qos                                                                                     | Quality of service type.      |

| Axregion  | amba_pv_control::m_region                                                                                  | Region type.                  |

| AxDOMAIN  | amba_pv_control::m_domain                                                                                  | Domain<br>type.               |

| AxSNOOP   | amba_pv_control::m_snoop                                                                                   | Snoop type.                   |

| AxBAR     | amba_pv_control::m_bar                                                                                     | Barrier type.                 |

| AxUSER    | amba_pv_control::m_user                                                                                    | User defined signals.         |

| AxMMUFLOW | amba_pv_control::m_mmu_flow_type                                                                           | MMU flow type.                |

## Table 2-7: Write data and response channels

| Signal   | Variable                                                                                 | Description    |

|----------|------------------------------------------------------------------------------------------|----------------|

| WID, BID | amba_pv_control::m_id                                                                    | ID             |

| WDATA    | tlm_generic_payload::m_data tlm_generic_payload::m_length                                | Write data     |

| 1        | <pre>tlm_generic_payload::m_byte_enable tlm_generic_payload::m_ byte_enable_length</pre> | Write strobes  |

| BRESP    | tlm_generic_payload::m_response_status amba_pv_extension::m_response                     | Write response |

| Signal | Variable                                                                                                         | Description               |

|--------|------------------------------------------------------------------------------------------------------------------|---------------------------|

|        | <pre>amba_pv_atomic::m_atomic_op, amba_pv_atomic::m_atomic_subop, amba_pv_<br/>atomic::m_atomic_endianness</pre> | Atomic transaction opcode |

#### Table 2-8: Read data channels

| Signal | Variable                                                             | Description    |

|--------|----------------------------------------------------------------------|----------------|

| RID    | amba_pv_extension::m_id                                              | ID.            |

| RDATA  | tlm_generic_payload::m_data tlm_generic_payload::m_length            | Read data.     |

| RRESP  | tlm_generic_payload::m_response_status amba_pv_extension::m_response | Read response. |

#### Table 2-9: Snoop data channels

| Signal | Variable                                                             | Description     |

|--------|----------------------------------------------------------------------|-----------------|

| CDDATA | tlm_generic_payload::m_data tlm_generic_payload::m_length            | Snoop data.     |

| CRRESP | tlm_generic_payload::m_response_status amba_pv_extension::m_response | Snoop response. |

#### Table 2-10: Unmapped signals

| Signal | Variable                    | Description                  |

|--------|-----------------------------|------------------------------|

| xVALID | Not applicable at PV level. | Address/data/response valid. |

| xREADY | Not applicable at PV level. | Address/data/response ready. |

| xLAST  | Not applicable at PV level. | Read/write last.             |

| xACK   | Not applicable at PV level. | Read/Write acknowledge.      |

# 2.3 Mapping for AMBA buses

This section describes the control signal mappings, response mappings, and response bit mappings for AMBA® buses.

The following table shows the control signal mappings for AXI, ACE, and AHB buses. The APB bus does not use these control signals.

Table 2-11: Signal mappings for amba\_pv\_control

| amba_pv_control                                                            | ACE, ACE-Lite | AXI4      | AXI3       | AHB      | AMBA5<br>AHB | CHI  |

|----------------------------------------------------------------------------|---------------|-----------|------------|----------|--------------|------|

| <pre>bool is_privileged() const; void set_privileged(bool = true);</pre>   | AxPROT[0]     | AxPROT[0] | AxPROT[0]  | HPROT[1] | HPROT[1]     | -    |

| <pre>bool is_instruction() const; void set_instruction(bool = true);</pre> | AxPROT[2]     | AxPROT[2] | AxPROT[2]  | HPROT[0] | HPROT[0]     | -    |

| <pre>bool is_non_secure() const; void set_non_secure(bool = true);</pre>   | AxPROT[1]     | AxPROT[1] | AxPROT[1]  | -        | -            | NS   |

| <pre>bool is_locked() const; void set_<br/>locked(bool = true);</pre>      | -             | -         | AxLOCK = 2 | HLOCK    | HLOCK        | -    |

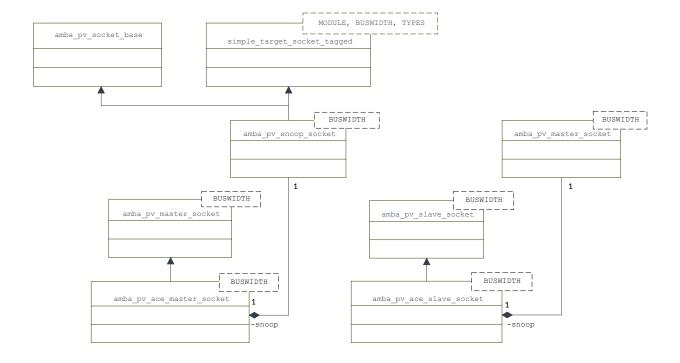

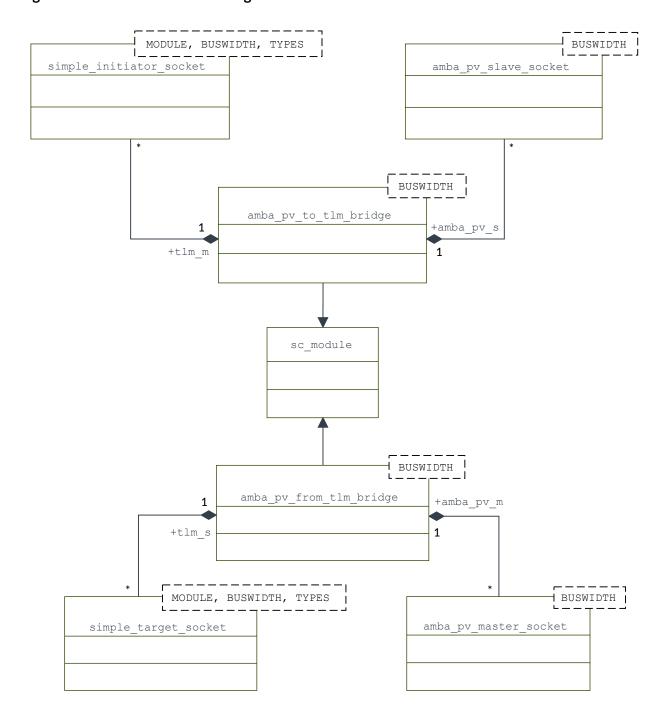

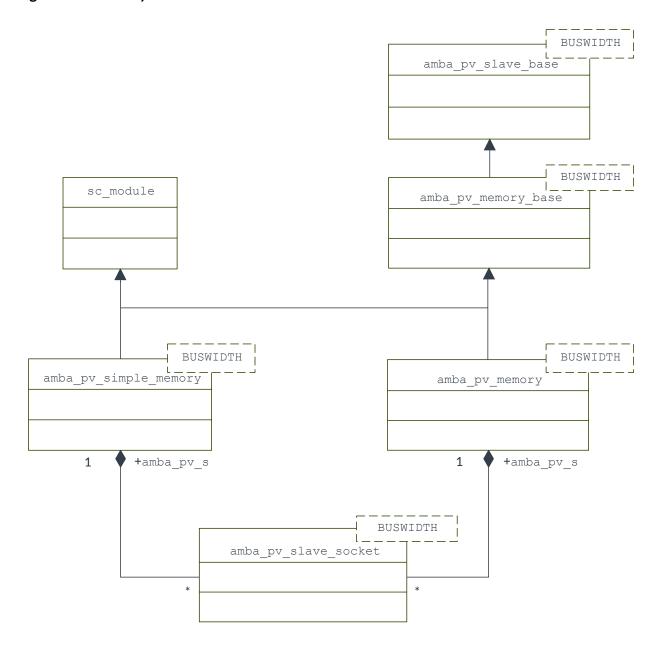

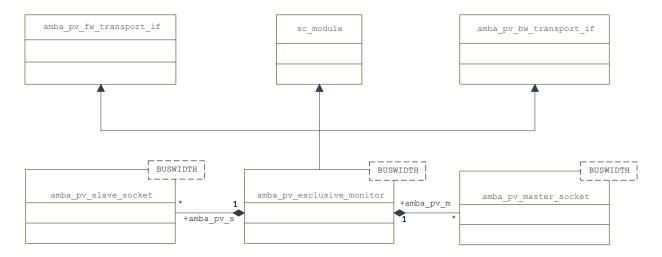

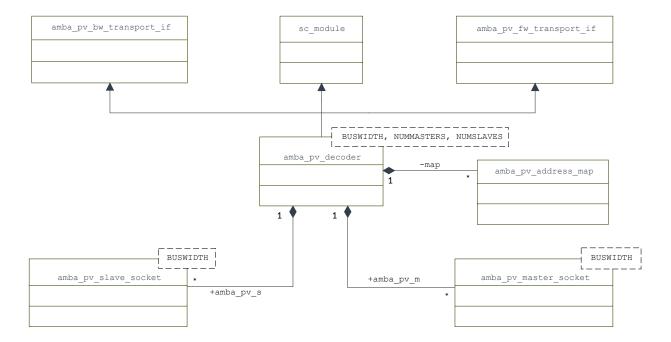

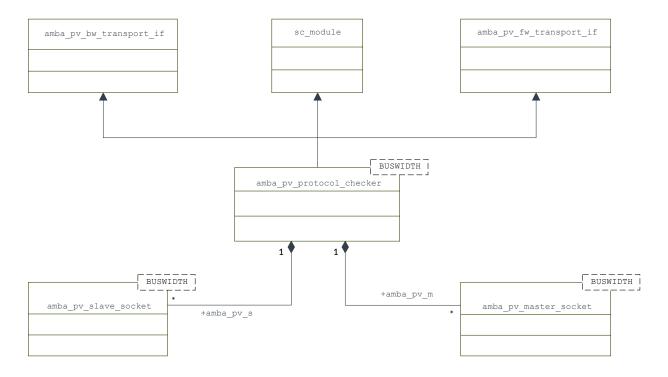

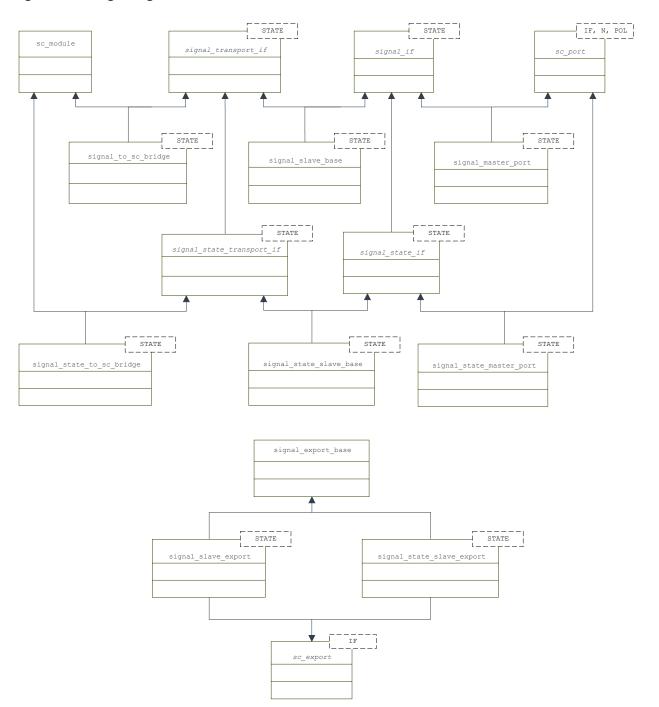

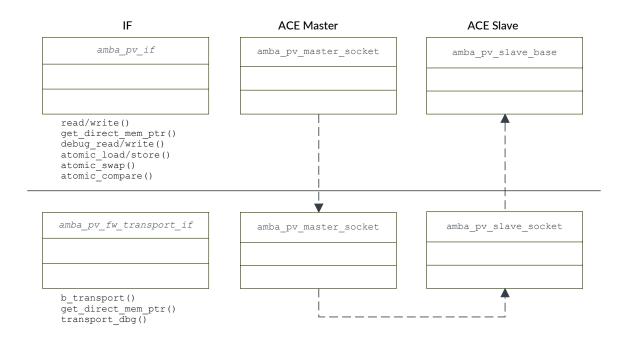

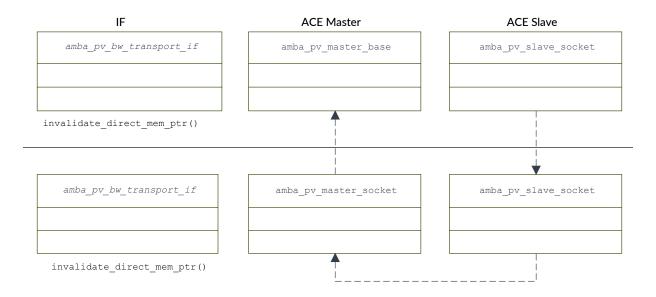

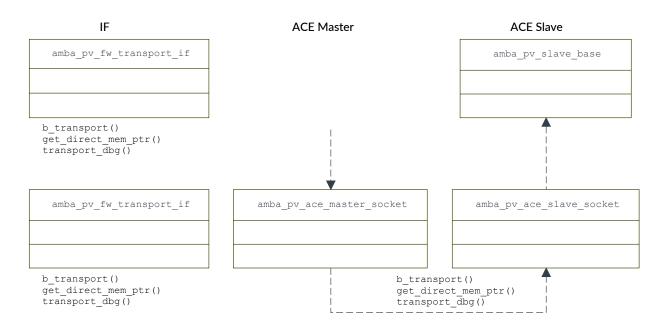

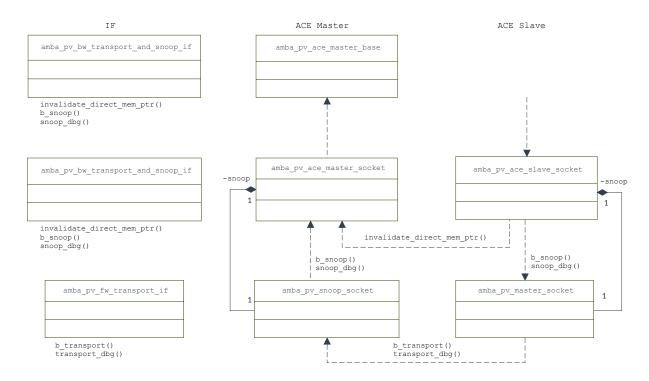

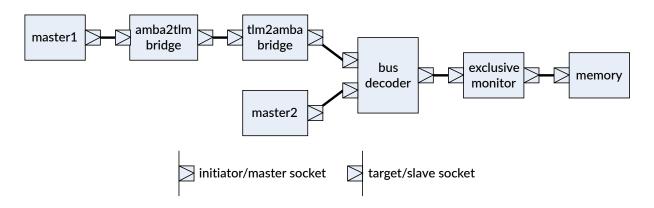

| <pre>bool is_exclusive() const; void set_exclusive(bool = true);</pre>     | AxLOCK        | AxLOCK    | AxLOCK = 1 | -        | -            | Excl |