# Message Handling Unit Architecture

version 3.0

Document number ARM-AES-0072

Document quality eac

Document version A.b

Document confidentiality Non-confidential

Copyright © 2023-2024 Arm Limited or its affiliates. All rights reserved.

# **Message Handling Unit Architecture**

## Release information

| Date        | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2024/Jul/11 | A.b     | <ul> <li>Corrected Secure access row in table in Rule KJHJD.</li> <li>Added missing reserved field in SSC_FCH_CFG0 register for bit [10].</li> <li>Removed duplicate rows in PFFCW register block table for the PFFCW<n>_PAY8/16/32/64 registers.</n></li> <li>Removed duplicate rows in PFCW and MFCW register block tables for the PFCW<n>_PAY32/64 and MFCW<n>_PAY32/64 registers.</n></n></li> </ul> |

| 2024/Mar/11 | A.a     | • Initial release of MHU v3.0 architecture.                                                                                                                                                                                                                                                                                                                                                              |

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or TM are registered trademarks or trademarks of Arm Limited (or its affiliates) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at http://www.arm.com/company/policies/trademarks.

Copyright © 2023-2024 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349 version 21.0

## **Contents**

# **Message Handling Unit Architecture**

|                | Message Handling Unit Architecture                     |  |

|----------------|--------------------------------------------------------|--|

|                | Release information                                    |  |

|                | Non-Confidential Proprietary Notice iii                |  |

| Preface        |                                                        |  |

|                | About this specification                               |  |

|                | Intended audience ix                                   |  |

|                | Conventions                                            |  |

|                | Typographical conventions                              |  |

|                | Numbers                                                |  |

|                | Pseudocode descriptions                                |  |

|                | Assembler syntax descriptions                          |  |

|                | Rules-based writing                                    |  |

|                | Content item rendering                                 |  |

|                | Content item classes                                   |  |

|                | Additional reading                                     |  |

|                | Feedback xiv                                           |  |

|                | Feedback on this book xiv                              |  |

|                |                                                        |  |

| D              | Handlin a Halt Analika atom Oceanian                   |  |

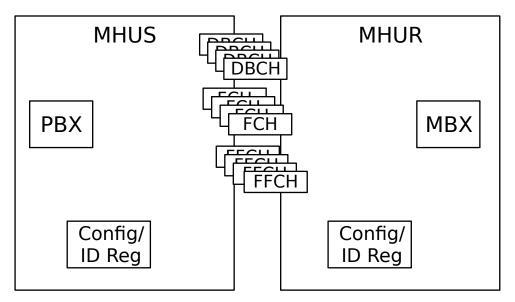

| Part A Message | Handling Unit Architecture Overview                    |  |

| Chapter A1     | Introduction to Message Handling Unit Architecture     |  |

| Onapior Ar     | A1.1 Interrupt Based Communication                     |  |

|                | A1.2 Usage                                             |  |

|                | A1.3 Architecture Structure                            |  |

|                |                                                        |  |

| Part B Message | Handling Unit v2 0                                     |  |

| rait b wessage | Handling Unit v3.0                                     |  |

| Chapter B1     | Message Handling Unit v3.0 Overview                    |  |

|                | B1.1 Structure                                         |  |

|                |                                                        |  |

| Chapter B2     | MHU Sender and Receiver                                |  |

| Chapter B3     | Postbox and Mailbox                                    |  |

| Chapter B4     | Power Control                                          |  |

| •              | B4.1 Overview                                          |  |

|                | B4.2 Auto Op                                           |  |

|                | B4.2.1 Auto Op(Min)                                    |  |

|                | B4.2.2 Auto Op(Full)                                   |  |

|                | B4.3 Entry to a Non-Operational State                  |  |

|                | B4.3.1 Controlled entry into Non-operational state     |  |

|                | B4.3.2 Uncontrolled entry into a Non-operational state |  |

| Chapter B5     | Data Endianness                                        |  |

| Chapter B6     | Doorbell Extension                                     |  |

| Onapier Du     | DOUBLE LAGISION                                        |  |

#### Contents

|             | B6.1       Doorbell Channel Window       37         B6.2       Events       38         B6.2.1       Channel Transfer event       39         B6.2.2       Channel Transfer Acknowledge event       39 | 9 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Chapter B7  | Fast Channel Extension                                                                                                                                                                               |   |

| •           | B7.1 Fast Channel Groups                                                                                                                                                                             | 2 |

|             | B7.2 Fast Channel Storage                                                                                                                                                                            |   |

|             | B7.3 Fast Channel Window                                                                                                                                                                             |   |

|             | B7.4 Fast Channel Control registers                                                                                                                                                                  |   |

|             | B7.5 Read-Acknowledge                                                                                                                                                                                |   |

|             | B7.6 Events                                                                                                                                                                                          |   |

| Chapter B8  | FIFO Extension                                                                                                                                                                                       |   |

| •           | B8.1 Data Flags                                                                                                                                                                                      | 1 |

|             | B8.1.1 Transfer Delineation Mode                                                                                                                                                                     |   |

|             | B8.1.2 Data Flag Storage                                                                                                                                                                             |   |

|             | B8.2 FIFO Behavior                                                                                                                                                                                   |   |

|             | B8.2.1 Reset                                                                                                                                                                                         |   |

|             | B8.2.2 Pushing data onto the FIFO                                                                                                                                                                    |   |

|             | B8.2.3 Reading data from the FIFO                                                                                                                                                                    |   |

|             | B8.2.4 Flag History Buffer                                                                                                                                                                           |   |

|             | • ,                                                                                                                                                                                                  |   |

|             |                                                                                                                                                                                                      |   |

|             | B8.2.6 Ordering of bytes when push, read or popping multiple bytes 60                                                                                                                                |   |

|             | B8.3 FIFO Flush                                                                                                                                                                                      |   |

|             | B8.4 FIFO Channel Window                                                                                                                                                                             |   |

|             | B8.4.1 Accesses to Payload and Flag registers                                                                                                                                                        |   |

|             | B8.4.2 FIFO Status                                                                                                                                                                                   |   |

|             | B8.4.3 Transfer Acknowledge Tracking                                                                                                                                                                 |   |

|             | B8.5 Events                                                                                                                                                                                          |   |

|             | B8.5.1 Channel Transfer event                                                                                                                                                                        |   |

|             | B8.5.2 FIFO Pop Ack event                                                                                                                                                                            |   |

|             | B8.5.3 Channel Transfer Acknowledge event                                                                                                                                                            | ) |

|             | B8.5.4 Sender FIFO Low and High Tide events                                                                                                                                                          | ) |

|             | B8.5.5 Receiver FIFO Low and High Tide events                                                                                                                                                        | I |

|             | B8.5.6 Sender FIFO flush event                                                                                                                                                                       | I |

|             | B8.5.7 Receiver FIFO flush event                                                                                                                                                                     | ١ |

| Chapter B9  | TrustZone and Realm Management Extension                                                                                                                                                             |   |

| Onapter D3  | B9.1 Overview                                                                                                                                                                                        | > |

|             | B9.2 Security Assignment Agent                                                                                                                                                                       |   |

|             |                                                                                                                                                                                                      |   |

|             |                                                                                                                                                                                                      |   |

|             | B9.4 RME                                                                                                                                                                                             | ) |

| Chapter B10 | Reliability, Availability and Serviceability Extensions                                                                                                                                              | _ |

|             | B10.1 Overview                                                                                                                                                                                       |   |

|             | B10.2 Reporting Requirements                                                                                                                                                                         |   |

|             | B10.3 Implications of error detection                                                                                                                                                                |   |

|             | B10.4 Error record requirements                                                                                                                                                                      |   |

|             | B10.5 RAS and Security                                                                                                                                                                               |   |

|             | B10.5.1 Error reporting                                                                                                                                                                              | 3 |

|             | B10.5.2 Error detection and reporting information                                                                                                                                                    | 1 |

|             | B10.5.3 Error Injection                                                                                                                                                                              | õ |

|             | B10.6 Interrupts                                                                                                                                                                                     | 3 |

|             | B10.7 Recommend implementation of RAS using Arm RAS extensions 87                                                                                                                                    | 7 |

|             |                                                                                                                                                                                                      |   |

| Chapter B11                  | Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

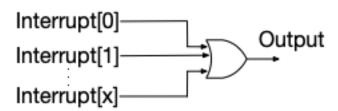

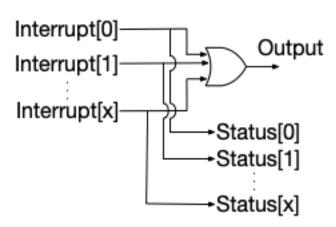

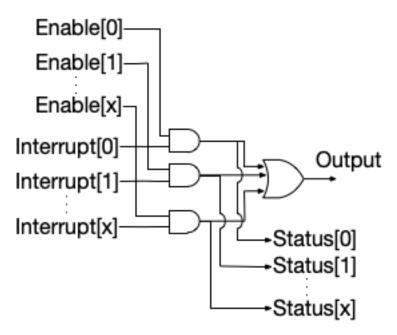

| •                            | B11.1 Interrupt Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

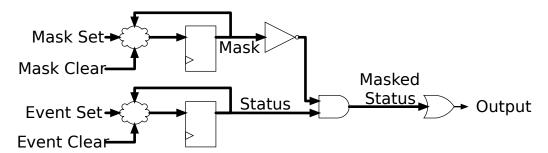

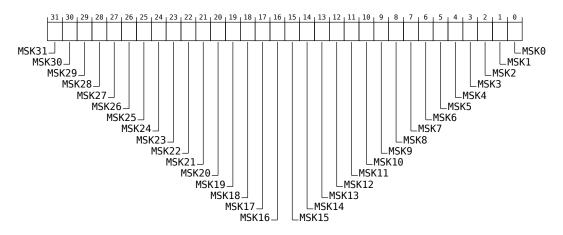

|                              | B11.1.1 Maskable interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

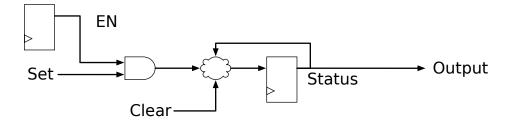

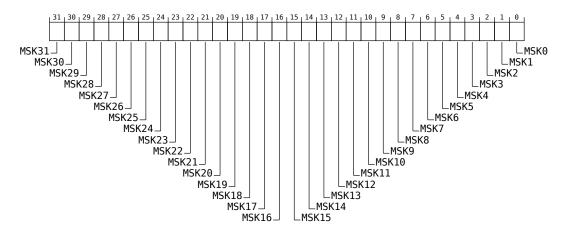

|                              | B11.1.2 Enable interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

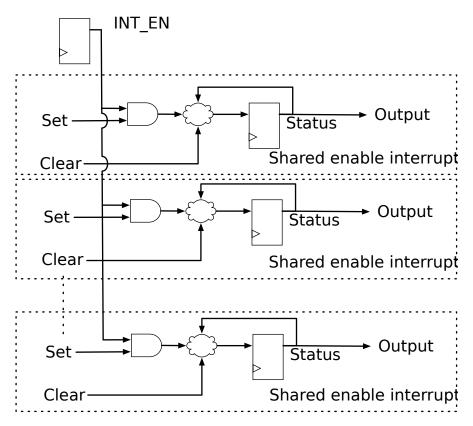

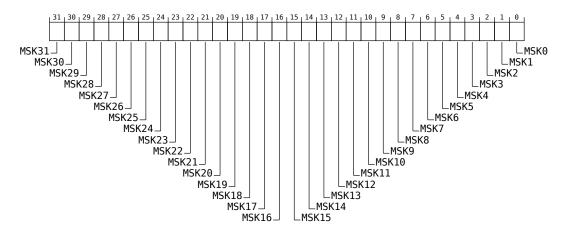

|                              | B11.1.3 Shared enable interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

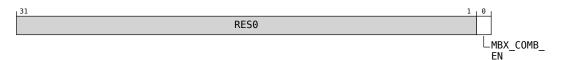

|                              | B11.1.4 Combined interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                              | B11.1.5 Combined status interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                              | B11.1.6 Combined enable interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                              | B11.2 MHU Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              | B11.2.1 Channel Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                              | B11.2.2 Channel Transfer Acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              | B11.2.3 Fast Channel Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                              | B11.2.4 Fast Channel Group Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                              | B11.2.5 Sender FIFO Low Tidemark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                              | B11.2.6 Sender FIFO High Tidemark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                              | B11.2.7 Sender FIFO Flush                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                              | B11.2.8 Receiver FIFO Low Tidemark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                              | B11.2.9 Receiver FIFO High Tidemark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                              | B11.2.10 Receiver FIFO Flush                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

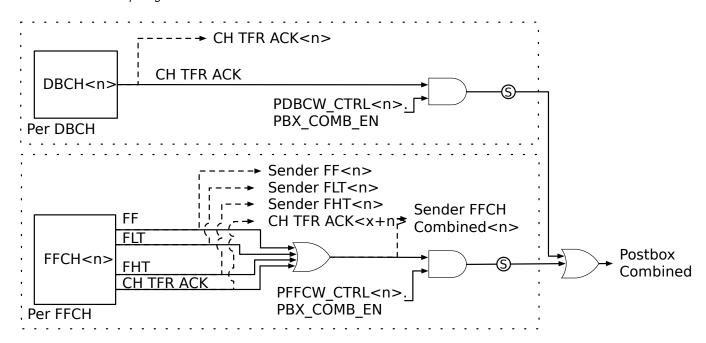

|                              | B11.2.11 Sender FFCH Combined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

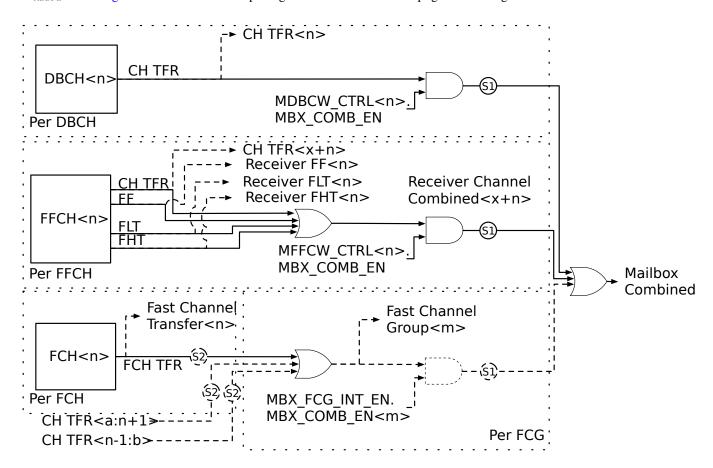

|                              | B11.2.12 Receiver FFCH Combined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                              | B11.2.13 Postbox Combined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                              | B11.2.14 Mailbox Combined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Part C Program               | imers Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Part C Program<br>Chapter C1 | Programmers Model Overview C1.1 Register Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| J                            | Programmers Model Overview C1.1 Register Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| J                            | Programmers Model Overview           C1.1 Register Access         103           C1.1.1 Generic Rules         103           C1.1.2 FCH Payload Accesses         104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| J                            | Programmers Model Overview           C1.1 Register Access         103           C1.1.1 Generic Rules         103           C1.1.2 FCH Payload Accesses         104           C1.1.3 FFCH Payload and Flag Accesses         104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| J                            | Programmers Model Overview           C1.1         Register Access         103           C1.1.1         Generic Rules         103           C1.1.2         FCH Payload Accesses         104           C1.1.3         FFCH Payload and Flag Accesses         104           C1.1.4         Unsupported Accesses         105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| J                            | Programmers Model Overview           C1.1         Register Access         103           C1.1.1         Generic Rules         103           C1.1.2         FCH Payload Accesses         104           C1.1.3         FFCH Payload and Flag Accesses         104           C1.1.4         Unsupported Accesses         105           C1.1.5         Illegal Accesses         106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| J                            | Programmers Model Overview           C1.1         Register Access         103           C1.1.1         Generic Rules         103           C1.1.2         FCH Payload Accesses         104           C1.1.3         FFCH Payload and Flag Accesses         104           C1.1.4         Unsupported Accesses         105           C1.1.5         Illegal Accesses         106           C1.2         Register Access Response         107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

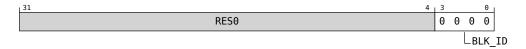

| J                            | Programmers Model Overview           C1.1         Register Access         103           C1.1.1         Generic Rules         103           C1.1.2         FCH Payload Accesses         104           C1.1.3         FFCH Payload and Flag Accesses         104           C1.1.4         Unsupported Accesses         105           C1.1.5         Illegal Accesses         106           C1.2         Register Access Response         107           C1.3         Reset Domains         110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| J                            | Programmers Model Overview           C1.1         Register Access         103           C1.1.1         Generic Rules         103           C1.1.2         FCH Payload Accesses         104           C1.1.3         FFCH Payload and Flag Accesses         104           C1.1.4         Unsupported Accesses         105           C1.1.5         Illegal Accesses         106           C1.2         Register Access Response         107           C1.3         Reset Domains         110           C1.4         Storage Resources         111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| J                            | Programmers Model Overview           C1.1         Register Access         103           C1.1.1         Generic Rules         103           C1.1.2         FCH Payload Accesses         104           C1.1.3         FFCH Payload and Flag Accesses         105           C1.1.4         Unsupported Accesses         105           C1.1.5         Illegal Accesses         106           C1.2         Register Access Response         107           C1.3         Reset Domains         110           C1.4         Storage Resources         111           C1.4.1         Storage resource location         111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| J                            | Programmers Model Overview           C1.1         Register Access         103           C1.1.1         Generic Rules         103           C1.1.2         FCH Payload Accesses         104           C1.1.3         FFCH Payload and Flag Accesses         105           C1.1.4         Unsupported Accesses         105           C1.1.5         Illegal Accesses         106           C1.2         Register Access Response         107           C1.3         Reset Domains         110           C1.4         Storage Resources         111           C1.4.1         Storage resource location         111           C1.4.2         Field Aliasing         111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| J                            | Programmers Model Overview           C1.1         Register Access         103           C1.1.1         Generic Rules         103           C1.1.2         FCH Payload Accesses         104           C1.1.3         FFCH Payload and Flag Accesses         105           C1.1.4         Unsupported Accesses         105           C1.1.5         Illegal Accesses         106           C1.2         Register Access Response         107           C1.3         Reset Domains         110           C1.4         Storage Resources         111           C1.4.1         Storage resource location         111           C1.4.2         Field Aliasing         111           C1.4.3         FIFO storage resources         111                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| J                            | Programmers Model Overview           C1.1         Register Access         103           C1.1.1         Generic Rules         103           C1.1.2         FCH Payload Accesses         104           C1.1.3         FFCH Payload and Flag Accesses         105           C1.1.4         Unsupported Accesses         105           C1.1.5         Illegal Accesses         106           C1.2         Register Access Response         107           C1.3         Reset Domains         110           C1.4         Storage Resources         111           C1.4.1         Storage resource location         111           C1.4.2         Field Aliasing         111           C1.4.3         FIFO storage resources         111           C1.5         Register Blocks         112                                                                                                                                                                                                                                                                                                                                                                                                       |

| J                            | Programmers Model Overview           C1.1         Register Access         103           C1.1.1         Generic Rules         103           C1.1.2         FCH Payload Accesses         104           C1.1.3         FFCH Payload and Flag Accesses         105           C1.1.4         Unsupported Accesses         105           C1.1.5         Illegal Accesses         106           C1.2         Register Access Response         107           C1.3         Reset Domains         110           C1.4         Storage Resources         111           C1.4.1         Storage resource location         111           C1.4.2         Field Aliasing         111           C1.4.3         FIFO storage resources         111           C1.5         Register Blocks         112           C1.5         Software Discovery         113                                                                                                                                                                                                                                                                                                                                                 |

| J                            | Programmers Model Overview         C1.1       Register Access       103         C1.1.1       Generic Rules       103         C1.1.2       FCH Payload Accesses       104         C1.1.3       FFCH Payload and Flag Accesses       105         C1.1.4       Unsupported Accesses       105         C1.1.5       Illegal Accesses       106         C1.2       Register Access Response       107         C1.3       Reset Domains       110         C1.4       Storage Resources       111         C1.4.1       Storage resource location       111         C1.4.2       Field Aliasing       111         C1.4.3       FIFO storage resources       111         C1.5       Register Blocks       112         C1.5       Register Blocks       112         C1.6       Software Discovery       113         C1.7       IMPLEMENTATION DEFINED registers       115                                                                                                                                                                                                                                                                                                                          |

| J                            | Programmers Model Overview           C1.1         Register Access         103           C1.1.1         Generic Rules         103           C1.1.2         FCH Payload Accesses         104           C1.1.3         FFCH Payload and Flag Accesses         105           C1.1.4         Unsupported Accesses         105           C1.1.5         Illegal Accesses         106           C1.2         Register Access Response         107           C1.3         Reset Domains         110           C1.4         Storage Resources         111           C1.4.1         Storage resource location         111           C1.4.2         Field Aliasing         111           C1.4.3         FIFO storage resources         111           C1.5         Register Blocks         112           C1.5         Software Discovery         113           C1.7         IMPLEMENTATION DEFINED registers         115           C1.7.1         Implementation Identification Registers         115                                                                                                                                                                                                |

| J                            | Programmers Model Overview           C1.1         Register Access         103           C1.1.1         Generic Rules         103           C1.1.2         FCH Payload Accesses         104           C1.1.3         FFCH Payload and Flag Accesses         105           C1.1.4         Unsupported Accesses         105           C1.1.5         Illegal Accesses         106           C1.2         Register Access Response         107           C1.3         Reset Domains         110           C1.4         Storage Resources         110           C1.4         Storage resource location         111           C1.4.1         Storage resource location         111           C1.4.2         Field Aliasing         111           C1.4.3         FIFO storage resources         111           C1.5         Register Blocks         112           C1.5         Register Blocks         112           C1.6         Software Discovery         113           C1.7.1         Implementation Identification Registers         115           C1.7.2         IMPLEMENTATION DEFINED Identification Registers         115                                                               |

| J                            | Programmers Model Overview           C1.1         Register Access         103           C1.1.1         Generic Rules         103           C1.1.2         FCH Payload Accesses         104           C1.1.3         FFCH Payload and Flag Accesses         105           C1.1.4         Unsupported Accesses         105           C1.1.5         Illegal Accesses         106           C1.2         Register Access Response         107           C1.3         Reset Domains         110           C1.4         Storage Resources         111           C1.4.1         Storage resource location         111           C1.4.2         Field Aliasing         111           C1.4.3         FIFO storage resources         111           C1.5         Register Blocks         112           C1.5         Software Discovery         113           C1.7         IMPLEMENTATION DEFINED registers         115           C1.7.1         Implementation Identification Registers         115                                                                                                                                                                                                |

| Chapter C1                   | Programmers Model Overview           C1.1         Register Access         103           C1.1.1         Generic Rules         103           C1.1.2         FCH Payload Accesses         104           C1.1.3         FFCH Payload and Flag Accesses         105           C1.1.4         Unsupported Accesses         105           C1.1.5         Illegal Accesses         106           C1.1.5         Illegal Accesses         106           C1.2         Register Access Response         107           C1.3         Reset Domains         116           C1.4         Storage Resources         117           C1.4         Storage resource location         111           C1.4.1         Storage resource location         111           C1.4.2         Field Aliasing         111           C1.4.3         FIFO storage resources         111           C1.5         Register Blocks         112           C1.5         Register Blocks         112           C1.6         Software Discovery         113           C1.7         IMPLEMENTATION DEFINED registers         115           C1.7.2         IMPLEMENTATION DEFINED Identification Registers         115           C1.7.3 |

| J                            | Programmers Model Overview           C1.1         Register Access         103           C1.1.1         Generic Rules         103           C1.1.2         FCH Payload Accesses         104           C1.1.3         FFCH Payload and Flag Accesses         105           C1.1.4         Unsupported Accesses         105           C1.1.5         Illegal Accesses         106           C1.2         Register Access Response         107           C1.2         Register Access Response         107           C1.3         Reset Domains         116           C1.4         Storage Resources         117           C1.4         Storage Resources         111           C1.4.1         Storage resource location         111           C1.4.2         Field Aliasing         111           C1.4.3         FIFO storage resources         111           C1.5         Register Blocks         112           C1.5         Register Blocks         112           C1.6         Software Discovery         113           C1.7         IMPLEMENTATION DEFINED registers         115           C1.7.1         Implementation Identification Registers         115           C1.7.2         < |

| Chapter C1                   | Programmers Model Overview         C1.1       Register Access       103         C1.1.1       Generic Rules       103         C1.1.2       FCH Payload Accesses       104         C1.1.3       FFCH Payload and Flag Accesses       105         C1.1.4       Unsupported Accesses       105         C1.1.5       Illegal Accesses       106         C1.2       Register Access Response       107         C1.3       Reset Domains       116         C1.4       Storage Resources       117         C1.4       Storage Resources       111         C1.4.1       Storage resource location       111         C1.4.2       Field Aliasing       111         C1.4.3       FIFO storage resources       111         C1.5       Register Blocks       112         C1.5       Register Blocks       112         C1.6       Software Discovery       113         C1.7       IMPLEMENTATION DEFINED registers       115         C1.7.1       Implementation Identification Registers       115         C1.7.2       IMPLEMENTATION DEFINED Page       115         Registers         C2.1       MHUS, MHU Sender       118                                                                         |

| Chapter C1                   | Programmers Model Overview         C1.1       Register Access       103         C1.1.1       Generic Rules       103         C1.1.2       FCH Payload Accesses       104         C1.1.3       FFCH Payload and Flag Accesses       105         C1.1.4       Unsupported Accesses       105         C1.1.5       Illegal Accesses       105         C1.2       Register Access Response       107         C1.3       Reset Domains       110         C1.4       Storage Resources       111         C1.4.1       Storage resource location       111         C1.4.2       Field Aliasing       111         C1.4.3       FIFO storage resources       111         C1.5       Register Blocks       112         C1.5       Register Blocks       112         C1.7       Implementation DeFINED registers       115         C1.7.1       Implementation Identification Registers       115         C1.7.2       IMPLEMENTATION DEFINED Page       115         Registers         C2.1       MHUS, MHU Sender       118         C2.1       PBX, Postbox       115                                                                                                                              |

| Chapter C1                   | Programmers Model Overview         C1.1       Register Access       103         C1.1.1       Generic Rules       103         C1.1.2       FCH Payload Accesses       104         C1.1.3       FFCH Payload and Flag Accesses       106         C1.1.4       Unsupported Accesses       105         C1.1.5       Illegal Accesses       106         C1.2       Register Access Response       107         C1.3       Reset Domains       110         C1.4       Storage Resources       111         C1.4.1       Storage resource location       111         C1.4.2       Field Aliasing       111         C1.4.3       FIFO storage resources       111         C1.5       Register Blocks       112         C1.5       Register Blocks       112         C1.6       Software Discovery       113         C1.7       IMPLEMENTATION DEFINED registers       115         C1.7.2       IMPLEMENTATION DEFINED Identification Registers       115         C1.7.3       IMPLEMENTATION DEFINED Page       115         Registers         C2.1       MHUS, MHU Sender       118         C2.1.1       PBX, Postbox       119                                                                    |

| Chapter C1                   | Programmers Model Overview         C1.1       Register Access       103         C1.1.1       Generic Rules       103         C1.1.2       FCH Payload Accesses       104         C1.1.3       FFCH Payload and Flag Accesses       105         C1.1.4       Unsupported Accesses       105         C1.1.5       Illegal Accesses       106         C1.2       Register Access Response       107         C1.3       Reset Domains       116         C1.4       Storage Resources       111         C1.4.1       Storage resource location       111         C1.4.2       Field Aliasing       111         C1.4.3       FIFO storage resources       111         C1.5       Register Blocks       112         C1.6       Software Discovery       113         C1.7       IMPLEMENTATION DEFINED registers       115         C1.7.1       Implementation Identification Registers       115         C1.7.2       IMPLEMENTATION DEFINED Page       115         C1.7.3       IMPLEMENTATION DEFINED Page       115         C1.7.3       IMPLEMENTATION DEFINED Page       115         C2.1       PBX, Postbox       119         C2.1                                                        |