# AMBA<sup>°</sup> LTI Protocol Specification

#### **AMBA LTI**

#### **Protocol Specification**

Copyright © 2020, 2021, 2023, 2024 Arm Limited or its affiliates. All rights reserved.

#### **Release Information**

The following changes have been made to this specification:

Change history

| Date              | Issue | Confidentiality  | Change                                                                                         |

|-------------------|-------|------------------|------------------------------------------------------------------------------------------------|

| 7 April 2020      | A     | Non-Confidential | First release                                                                                  |

| 21 July 2021      | A.b   | Non-Confidential | Terminology update                                                                             |

| 26 September 2023 | В     | Non-confidential | Release with support for Realm Management Extension (RME) and Memory Encryption Contexts (MEC) |

| 01 July 2024      | С     | Non-Confidential | Release with support for Device Permission Table (DPT) and coherent interfaces                 |

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the use or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm Limited ("Arm"). No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether the subject matter of this document infringes any third party patents.

The content of this document is informational only. Any solutions presented herein are subject to changing conditions, information, scope, and data. This document was produced using reasonable efforts based on information available as of the date of issue of this document. The scope of information in this document may exceed that which Arm is required to provide, and such additional information is merely intended to further assist the recipient and does not represent Arm's view of the scope of its obligations. You acknowledge and agree that you possess the necessary expertise in system security and functional safety and that you shall be solely responsible for compliance with all legal, regulatory, safety and security related requirements concerning your products, notwithstanding any information or support that may be provided by Arm herein. In addition, you are responsible for any applications which are used in conjunction with any Arm technology described in this document, and to minimize risks, adequate design and operating safeguards should be provided for by you.

This document may include technical inaccuracies or typographical errors. THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, any patents, copyrights, trade secrets, trademarks, or other rights.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Reference by Arm to any third party's products or services within this document is not an express or implied approval or endorsement of the use thereof.

This document consists solely of commercial items. You shall be responsible for ensuring that any permitted use, duplication, or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of this document shall prevail.

The validity, construction and performance of this notice shall be governed by English Law.

The Arm corporate logo and words marked with <sup>®</sup> or <sup>™</sup> are registered trademarks or trademarks of Arm Limited (or its affiliates) in the US and/or elsewhere. Please follow Arm's trademark usage guidelines at

http://www.arm.com/company/policies/trademarks. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners.

Copyright © 2016-2018, 2020-2024 Arm Limited or its affiliates. All rights reserved.

Arm Limited. Company 02557590 registered in England. 110 Fulbourn Road, Cambridge, England CB1 9NJ. PRE-21451 version 3

#### AMBA SPECIFICATION LICENCE

THIS END USER LICENCE AGREEMENT ("LICENCE") IS A LEGAL AGREEMENT BETWEEN YOU (EITHER A SINGLE INDIVIDUAL, OR SINGLE LEGAL ENTITY) AND ARM LIMITED ("ARM") FOR THE USE OF ARM'S INTELLECTUAL PROPERTY (INCLUDING, WITHOUT LIMITATION, ANY COPYRIGHT) IN THE RELEVANT AMBA SPECIFICATION ACCOMPANYING THIS LICENCE. ARM LICENSES THE RELEVANT AMBA SPECIFICATION TO YOU ON CONDITION THAT YOU ACCEPT ALL OF THE TERMS IN THIS LICENCE. BY CLICKING "I AGREE" OR OTHERWISE USING OR COPYING THE RELEVANT AMBA SPECIFICATION YOU INDICATE THAT YOU AGREE TO BE BOUND BY ALL THE TERMS OF THIS LICENCE.

"LICENSEE" means You and your Subsidiaries.

"Subsidiary" means, if You are a single entity, any company the majority of whose voting shares is now or hereafter owned or controlled, directly or indirectly, by You. A company shall be a Subsidiary only for the period during which such control exists.

- Subject to the provisions of Clauses 2, 3 and 4, Arm hereby grants to LICENSEE a perpetual, non-exclusive, non-transferable, royalty free, worldwide licence to:

- (i) use and copy the relevant AMBA Specification for the purpose of developing and having developed products that comply with the relevant AMBA Specification;

- (ii) manufacture and have manufactured products which either: (a) have been created by or for LICENSEE under the licence granted in Clause 1(i); or (b) incorporate a product(s) which has been created by a third party(s) under a licence granted by Arm in Clause 1(i) of such third party's AMBA Specification Licence; and

- (iii) offer to sell, supply or otherwise distribute products which have either been (a) created by or for LICENSEE under the licence granted in Clause 1(i); or (b) manufactured by or for LICENSEE under the licence granted in Clause 1(ii).

- 2. LICENSEE hereby agrees that the licence granted in Clause 1 is subject to the following restrictions:

- (i) where a product created under Clause 1(i) is an integrated circuit which includes a CPU then either: (a) such CPU shall only be manufactured under licence from Arm; or (b) such CPU is neither substantially compliant with nor marketed as being compliant with the Arm instruction sets licensed by Arm from time to time;

- (ii) the licences granted in Clause 1(iii) shall not extend to any portion or function of a product that is not itself compliant with part of the relevant AMBA Specification; and

- (iii) no right is granted to LICENSEE to sublicense the rights granted to LICENSEE under this Agreement.

- 3. Except as specifically licensed in accordance with Clause 1, LICENSEE acquires no right, title or interest in any Arm technology or any intellectual property embodied therein. In no event shall the licences granted in accordance with Clause 1 be construed as granting LICENSEE, expressly or by implication, estoppel or otherwise, a licence to use any Arm technology except the relevant AMBA Specification.

- 4. THE RELEVANT AMBA SPECIFICATION IS PROVIDED "AS IS" WITH NO REPRESENTATION OR WARRANTIES EXPRESS, IMPLIED OR STATUTORY, INCLUDING BUT NOT LIMITED TO ANY WARRANTY OF SATISFACTORY QUALITY, MERCHANTABILITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE, OR THAT ANY USE OR IMPLEMENTATION OF SUCH ARM TECHNOLOGY WILL NOT INFRINGE ANY THIRD PARTY PATENTS, COPYRIGHTS, TRADE SECRETS OR OTHER INTELLECTUAL PROPERTY RIGHTS.

- 5. NOTWITHSTANDING ANYTHING TO THE CONTRARY CONTAINED IN THIS AGREEMENT, TO THE FULLEST EXTENT PETMITTED BY LAW, THE MAXIMUM LIABILITY OF ARM IN AGGREGATE FOR ALL CLAIMS MADE AGAINST ARM, IN CONTRACT, TORT OR OTHERWISE, IN CONNECTION WITH THE SUBJECT MATTER OF THIS AGREEMENT (INCLUDING WITHOUT LIMITATION (I) LICENSEE'S USE OF THE ARM TECHNOLOGY; AND (II) THE IMPLEMENTATION OF THE ARM TECHNOLOGY IN ANY PRODUCT CREATED BY LICENSEE UNDER THIS AGREEMENT) SHALL NOT EXCEED THE FEES PAID (IF ANY) BY LICENSEE TO ARM UNDER THIS AGREEMENT. THE EXISTENCE OF MORE THAN ONE CLAIM OR SUIT WILL NOT ENLARGE OR EXTEND THE LIMIT. LICENSEE RELEASES ARM FROM ALL OBLIGATIONS, LIABILITY, CLAIMS OR DEMANDS IN EXCESS OF THIS LIMITATION.

- 6. No licence, express, implied or otherwise, is granted to LICENSEE, under the provisions of Clause 1, to use the Arm tradename, or AMBA trademark in connection with the relevant AMBA Specification or any products based thereon. Nothing in Clause 1 shall be construed as authority for LICENSEE to make any representations on behalf of Arm in respect of the relevant AMBA Specification.

- 7. This Licence shall remain in force until terminated by you or by Arm. Without prejudice to any of its other rights if LICENSEE is in breach of any of the terms and conditions of this Licence then Arm may terminate this Licence immediately upon giving written notice to You. You may terminate this Licence at any time. Upon expiry or termination

of this Licence by You or by Arm LICENSEE shall stop using the relevant AMBA Specification and destroy all copies of the relevant AMBA Specification in your possession together with all documentation and related materials. Upon expiry or termination of this Licence, the provisions of clauses 6 and 7 shall survive.

8. The validity, construction and performance of this Agreement shall be governed by English Law.

PRE-21451 version 3

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

### Contents

### **AMBA LTI Protocol Specification**

| About this specification Intended audience Using this specification Conventions Typographic conventions Timing diagrams Signals Numbers Additional reading Arm publications Other publications Feedback Inclusive terminology commitment  Chapter 1 Introduction  1.1 About the LTI protocol 1.2 Use cases 1.2.1 In-line integration 1.2.2 Lookaside integration 1.2.3 Cached integration 1.2.3 Cached integration 1.4.4 Supported translation flows 1.4.1 Stall flow 1.4.2 ATST flow 1.4.3 NoStall flow 1.4.4 PRI flow |           | Pref  | ace        |                                  |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|------------|----------------------------------|------|

| Intended audience Using this specification Conventions Typographic conventions Timing diagrams Signals Numbers Additional reading Arm publications Other publications Feedback Inclusive terminology commitment  Chapter 1 Introduction 1.1 About the LTI protocol 1.2 Use cases 1.2.1 In-line integration 1.2.2 Lookaside integration 1.2.3 Cached integration 1.3 Differences between DTI and LTI 1.4 Supported translation flows 1.4.1 Stall flow 1.4.2 ATST flow 1.4.3 NoStall flow                                 |           |       | About thi  | s specification                  | X    |

| Using this specification Conventions Typographic conventions Timing diagrams Signals Numbers Additional reading Arm publications Other publications Feedback Inclusive terminology commitment  Chapter 1  Introduction  1.1 About the LTI protocol 1.2 Use cases 1.2.1 In-line integration 1.2.2 Lookaside integration 1.2.3 Cached integration 1.3 Differences between DTI and LTI 1.4 Supported translation flows 1.4.1 Stall flow 1.4.2 ATST flow 1.4.3 NoStall flow 1.4.3 NoStall flow                              |           |       |            |                                  |      |

| Conventions Typographic conventions Timing diagrams Signals Numbers Additional reading Arm publications Other publications Feedback Inclusive terminology commitment  Chapter 1  Introduction  1.1 About the LTI protocol 1.2 Use cases 1.2.1 In-line integration 1.2.2 Lookaside integration 1.2.3 Cached integration 1.2.3 Cached integration 1.3 Differences between DTI and LTI 1.4 Supported translation flows 1.4.1 Stall flow 1.4.2 ATST flow 1.4.3 NoStall flow 1.4.3 NoStall flow                              |           |       |            |                                  |      |

| Typographic conventions Timing diagrams Signals Numbers Additional reading Arm publications Other publications Feedback Inclusive terminology commitment  Chapter 1 Introduction  1.1 About the LTI protocol 1.2 Use cases 1.2.1 In-line integration 1.2.2 Lookaside integration 1.2.3 Cached integration 1.2.3 Cached integration 1.3 Differences between DTI and LTI 1.4 Supported translation flows 1.4.1 Stall flow 1.4.2 ATST flow 1.4.3 NoStall flow                                                              |           |       |            |                                  |      |

| Timing diagrams Signals Numbers Additional reading Arm publications Other publications Feedback Inclusive terminology commitment  Chapter 1 Introduction  1.1 About the LTI protocol 1.2 Use cases 1.2.1 In-line integration 1.2.2 Lookaside integration 1.2.3 Cached integration 1.2.3 Cached integration 1.4 Supported translation flows 1.4.1 Stall flow 1.4.2 ATST flow 1.4.3 NoStall flow                                                                                                                          |           |       |            |                                  |      |

| Numbers Additional reading Arm publications Other publications Feedback Inclusive terminology commitment  Chapter 1 Introduction  1.1 About the LTI protocol 1.2 Use cases 1.2.1 In-line integration 1.2.2 Lookaside integration 1.2.3 Cached integration 1.2.3 Cached integration 1.4 Supported translation flows 1.4.1 Stall flow 1.4.2 ATST flow 1.4.3 NoStall flow                                                                                                                                                  |           |       |            | - · · - · ·                      |      |

| Additional reading Arm publications Other publications Feedback Inclusive terminology commitment  Chapter 1 Introduction  1.1 About the LTI protocol 1.2 Use cases 1.2.1 In-line integration 1.2.2 Lookaside integration 1.2.3 Cached integration 1.2.3 Cached integration 1.4 Supported translation flows 1.4.1 Stall flow 1.4.2 ATST flow 1.4.3 NoStall flow                                                                                                                                                          |           |       |            |                                  |      |

| Arm publications Other publications Feedback Inclusive terminology commitment  Chapter 1 Introduction  1.1 About the LTI protocol 1.2 Use cases 1.2.1 In-line integration 1.2.2 Lookaside integration 1.2.3 Cached integration 1.3 Differences between DTI and LTI 1.4 Supported translation flows 1.4.1 Stall flow 1.4.2 ATST flow 1.4.3 NoStall flow                                                                                                                                                                  |           |       |            | Numbers                          | xi   |

| Other publications Feedback Inclusive terminology commitment  Chapter 1 Introduction  1.1 About the LTI protocol 1.2 Use cases 1.2.1 In-line integration 1.2.2 Lookaside integration 1.2.3 Cached integration 1.2.3 Cached integration 1.4 Supported translation flows 1.4.1 Stall flow 1.4.2 ATST flow 1.4.3 NoStall flow                                                                                                                                                                                              |           |       | Additiona  | al reading                       | X    |

| Feedback Inclusive terminology commitment  Introduction  1.1 About the LTI protocol 1.2 Use cases 1.2.1 In-line integration 1.2.2 Lookaside integration 1.2.3 Cached integration 1.2.3 Cached integration 1.4 Supported translation flows 1.4.1 Stall flow 1.4.2 ATST flow 1.4.3 NoStall flow                                                                                                                                                                                                                           |           |       |            | Arm publications                 | X    |

| Feedback Inclusive terminology commitment  Introduction  1.1 About the LTI protocol 1.2 Use cases 1.2.1 In-line integration 1.2.2 Lookaside integration 1.2.3 Cached integration 1.2.3 Cached integration 1.4 Supported translation flows 1.4.1 Stall flow 1.4.2 ATST flow 1.4.3 NoStall flow                                                                                                                                                                                                                           |           |       |            | Other publications               | X    |

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |       |            |                                  |      |

| 1.1       About the LTI protocol         1.2       Use cases         1.2.1       In-line integration         1.2.2       Lookaside integration         1.2.3       Cached integration         1.3       Differences between DTI and LTI         1.4       Supported translation flows         1.4.1       Stall flow         1.4.2       ATST flow         1.4.3       NoStall flow                                                                                                                                     |           |       |            | Inclusive terminology commitment | XV   |

| 1.2       Use cases         1.2.1       In-line integration         1.2.2       Lookaside integration         1.2.3       Cached integration         1.3       Differences between DTI and LTI         1.4       Supported translation flows         1.4.1       Stall flow         1.4.2       ATST flow         1.4.3       NoStall flow                                                                                                                                                                              | Chapter 1 | Intro | duction    |                                  |      |

| 1.2       Use cases         1.2.1       In-line integration         1.2.2       Lookaside integration         1.2.3       Cached integration         1.3       Differences between DTI and LTI         1.4       Supported translation flows         1.4.1       Stall flow         1.4.2       ATST flow         1.4.3       NoStall flow                                                                                                                                                                              | -         | 1.1   | About the  | e LTI protocol                   | 1-18 |

| 1.2.2 Lookaside integration 1.2.3 Cached integration  1.3 Differences between DTI and LTI  1.4 Supported translation flows  1.4.1 Stall flow  1.4.2 ATST flow  1.4.3 NoStall flow                                                                                                                                                                                                                                                                                                                                       |           | 1.2   |            |                                  |      |

| 1.2.2 Lookaside integration 1.2.3 Cached integration  1.3 Differences between DTI and LTI  1.4 Supported translation flows  1.4.1 Stall flow  1.4.2 ATST flow  1.4.3 NoStall flow                                                                                                                                                                                                                                                                                                                                       |           |       | 1.2.1      | In-line integration              | 1-19 |

| 1.3 Differences between DTI and LTI  1.4 Supported translation flows  1.4.1 Stall flow  1.4.2 ATST flow  1.4.3 NoStall flow                                                                                                                                                                                                                                                                                                                                                                                             |           |       |            |                                  |      |

| 1.4 Supported translation flows  1.4.1 Stall flow  1.4.2 ATST flow  1.4.3 NoStall flow                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |       | 1.2.3      | Cached integration               | 1-20 |

| 1.4.1 Stall flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           | 1.3   | Difference | es between DTI and LTI           | 1-2  |

| 1.4.2 ATST flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           | 1.4   | Supporte   | ed translation flows             | 1-22 |

| 1.4.3 NoStall flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |       | 1.4.1      | Stall flow                       | 1-2: |

| 1.4.3 NoStall flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |       | 1.4.2      | ATST flow                        | 1-22 |

| 1.4.4 PRI flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |       | 1.4.3      | NoStall flow                     | 1-2  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |       | 1.4.4      | PRI flow                         | 1-23 |

| Chapter 2  | Channels |                                                         |       |  |  |

|------------|----------|---------------------------------------------------------|-------|--|--|

| •          | 2.1      | Transaction flow                                        | 2-26  |  |  |

|            | 2.2      | Virtual Channels                                        |       |  |  |

|            | 2.3      | Flow control                                            | 2-29  |  |  |

|            | 2.4      | Reserved encodings                                      | 2-30  |  |  |

|            | 2.5      | Signal validity                                         | 2-31  |  |  |

| Chapter 3  | Pron     | perties                                                 |       |  |  |

|            | 3.1      | LTI properties                                          | 3-34  |  |  |

| Chapter 4  | Regi     | uest channel                                            |       |  |  |

|            | 4.1      | Signals                                                 | 4-38  |  |  |

|            | 4.2      | Transaction types                                       |       |  |  |

|            | 4.3      | Transaction attributes                                  |       |  |  |

|            | 4.4      | Transaction scope                                       |       |  |  |

| Chapter 5  | Resi     | ponse channel                                           |       |  |  |

| •          | 5.1      | Signals                                                 | 5-48  |  |  |

|            | 5.2      | LRRESP details                                          |       |  |  |

|            |          | 5.2.1 Restrictions based on LATRANS                     | 5-54  |  |  |

|            |          | 5.2.2 Downgrade types                                   | 5-54  |  |  |

|            |          | 5.2.3 Restrictions based on LAFLOW                      |       |  |  |

|            |          | 5.2.4 Out of range address                              | 5-55  |  |  |

|            | 5.3      | Attribute restrictions for specific transaction types   | 5-56  |  |  |

| Chapter 6  | Com      | pletion channel                                         |       |  |  |

| •          | 6.1      | Signals                                                 | 6-58  |  |  |

|            | 6.2      | Completion channel characteristics                      |       |  |  |

|            |          | 6.2.1 Deadlock avoidance                                | 6-59  |  |  |

|            |          | 6.2.2 Use of LTI translations for multiple transactions | 6-59  |  |  |

| Chapter 7  | Inter    | rface management                                        |       |  |  |

| •          | 7.1      | Interface management overview                           | 7-62  |  |  |

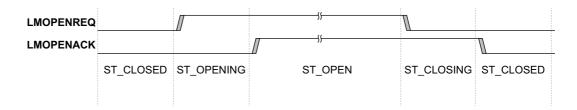

|            | 7.2      | Open and close handshake                                |       |  |  |

|            | 7.3      | Properties of interface states                          |       |  |  |

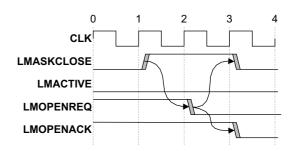

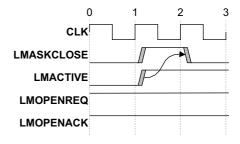

|            | 7.4      | Management Signals                                      |       |  |  |

|            |          | 7.4.1 LMASKCLOSE                                        |       |  |  |

|            |          | 7.4.2 LMACTIVE                                          | 7-65  |  |  |

| Chapter 8  | Cloc     | k and reset                                             |       |  |  |

| •          | 8.1      | Clock and reset                                         | 8-70  |  |  |

| Chapter 9  | Pipe     | elining                                                 |       |  |  |

| -          | 9.1      | Pipelining between Manager and Subordinate interfaces   | 9-72  |  |  |

| Chapter 10 | Inter    | roperability                                            |       |  |  |

| -          | 10.1     | LTI-A compatibility                                     | 10-74 |  |  |

|            | 10.2     | LTI_MMU and LTI_GPC properties                          |       |  |  |

|            | 10.3     | MPAM compatibility                                      |       |  |  |

|            | 10.4     | LAMECID and LAHWATTR signals compatibility              |       |  |  |

| Appendix A | Con      | siderations for AXI5                                    |       |  |  |

|            | A.1      | LATRANS mapping                                         | A-80  |  |  |

|            | A.2      | LAATTR mapping                                          |       |  |  |

|            | A.3      | LAIDENT mapping                                         |       |  |  |

|            | A.4      | LRATTR mapping                                          |       |  |  |

|            | A.5      | xRESP mapping                                           |       |  |  |

|            |          | ···                                                     |       |  |  |

|              | A.6  | Transactions that are legal in AXI5 and illegal in LTI |       |

|--------------|------|--------------------------------------------------------|-------|

|              | A.7  | Memory Tagging                                         | A-86  |

| Appendix B   | Con  | siderations for DTI                                    |       |

|              | B.1  | DTI_TBU_TRANS_REQ.PERM mapping                         | B-88  |

|              | B.2  | Special handling for specific LATRANS values           | B-89  |

|              |      | B.2.1 LATRANS = DCP                                    | B-89  |

|              |      | B.2.2 LATRANS = W-DCP                                  | B-89  |

|              |      | B.2.3 LATRANS = CMO                                    | B-89  |

|              |      | B.2.4 LATRANS = R-CMO                                  | B-89  |

|              |      | B.2.5 LATRANS = DCMO                                   | B-89  |

|              |      | B.2.6 LATRANS = R-DCMO                                 | B-89  |

|              |      | B.2.7 LATRANS = DHCMO                                  | B-89  |

|              | B.3  | Attribute mapping                                      | B-91  |

|              |      | B.3.1 LTI to Armv8 conversion                          | B-91  |

|              |      | B.3.2 Armv8 to LTI conversion                          |       |

|              | B.4  | DTI_TBU_TRANS_FAULT.FAULT_TYPE mapping                 | B-94  |

| Appendix C   | Con  | siderations for PCle                                   |       |

| Appointing C | C.1  | PCIe integration                                       | C-96  |

|              | 0.1  | · Ole magatien                                         |       |

| Appendix D   | Con  | siderations for coherent interfaces                    |       |

|              | D.1  | LTI properties                                         | D-100 |

|              | D.2  | LA mapping from CHI                                    | D-101 |

|              | D.3  | LATRANS mapping                                        | D-102 |

|              | D.4  | LAATTR mappings                                        | D-104 |

|              | D.5  | LRATTR mappings                                        | D-105 |

|              | D.6  | CHI completion response flit opcode mapping            | D-106 |

|              | D.7  | Transaction flow examples                              | D-107 |

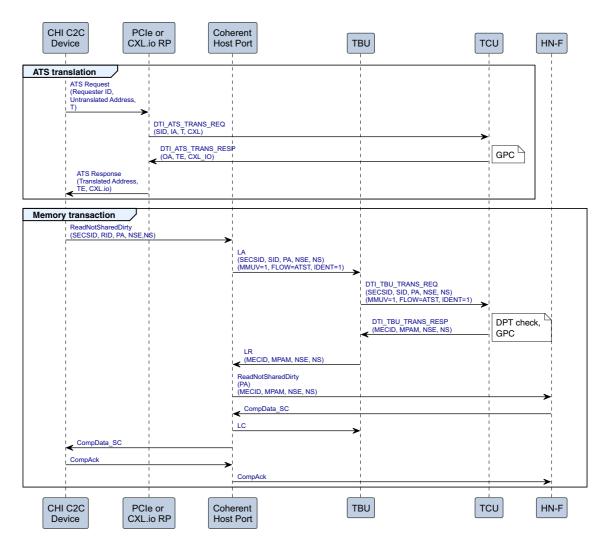

|              |      | D.7.1 Coherent read from CHI C2C device                | D-107 |

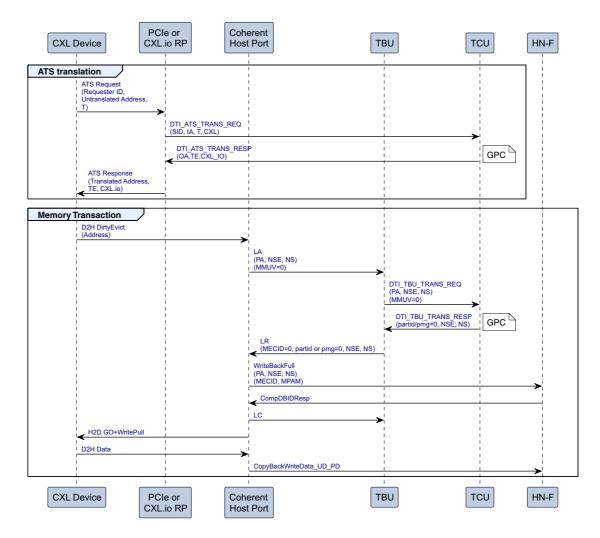

|              |      | D.7.2 Coherent write from CXL.cache device             | D-108 |

| Appendix E   | Sian | nal list                                               |       |

| 1- 1         | E.1  | Signal list                                            | E-112 |

|              |      | ·                                                      |       |

| Appendix F   | Revi | isions                                                 |       |

### **Preface**

This preface introduces the AMBA® LTI Protocol Specification. It contains the following sections:

- About this specification on page xii

- Additional reading on page xv

- Feedback on page xvi

#### About this specification

#### Intended audience

This specification is written for hardware engineers who wish to design components that implement *Local Translation Interface* (LTI).

#### Using this specification

#### **Chapter 1 Introduction**

Introduction to the AMBA LTI protocol specification.

#### Chapter 2 Channels

Describes LTI information flow.

#### Chapter 3 Properties

Describes the set of LTI properties that specify the supported behavior and interface signaling requirements.

#### Chapter 4 Request channel

Defines the LTI request (LA) channel.

#### Chapter 5 Response channel

Defines the LTI response (LR) channel.

#### Chapter 6 Completion channel

Defines the LTI completion (LC) channel.

#### Chapter 7 Interface management

Describes the LTI interface management function.

#### Chapter 8 Clock and reset

Describes a mapping strategy for clock and reset.

#### Chapter 9 Pipelining

Defines pipelining requirements for LTI.

#### Chapter 10 Interoperability

Describes how to connect LTI interfaces with different properties.

#### Appendix A Considerations for AXI5

Describes how to map LTI concepts onto AXI5.

#### Appendix B Considerations for DTI

Describes how to map LTI concepts onto DTI-TBU.

#### Appendix C Considerations for PCIe

Describes the integration of PCIe.

#### Appendix D Considerations for coherent interfaces

Describes how to map LTI concepts onto coherent interfaces.

#### Appendix E Signal list

Describes which signals are present on LTI-A and LTI-B interfaces.

#### Appendix F Revisions

Describes the technical changes between issues of this specification.

#### Conventions

The following sections describe conventions that this specification can use:

- Typographic conventions

- Timing diagrams

- Signals on page xiv

- Numbers on page xiv

#### **Typographic conventions**

The typographical conventions are:

italic Highlights important notes, introduces special terminology, and denotes internal

cross-references and citations.

bold Denotes signal names, and is used for terms in descriptive lists, where appropriate.

monospace Used for assembler syntax descriptions, pseudocode, and source code examples.

Also used in the main text for instruction mnemonics and for references to other items appearing in assembler syntax descriptions, pseudocode, and source code examples.

SMALL CAPITALS Used for a few terms that have specific technical meanings.

#### **Timing diagrams**

The components used in timing diagrams are explained in figure *Key to timing diagram conventions*. Variations have clear labels, when they occur. Do not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

| Clock                              |

|------------------------------------|

| HIGH to LOW                        |

| Transient V                        |

| HIGH/LOW to HIGH                   |

| Bus stable                         |

| Bus to high impedance              |

| Bus change                         |

| High impedance to stable bus -\(\) |

#### Key to timing diagram conventions

Timing diagrams sometimes show single-bit signals as HIGH and LOW at the same time and they look similar to the bus change shown in *Key to timing diagram conventions*. If a timing diagram shows a single-bit signal in this way then its value does not affect the accompanying description.

#### **Signals**

The signal conventions are:

**Signal level** The level of an asserted signal depends on whether the signal is active-HIGH or

active-LOW. Asserted means:

• HIGH for active-HIGH signals

• LOW for active-LOW signals.

**Lowercase n** At the start or end of a signal name denotes an active-LOW signal.

**Lowercase x** At the second letter of a signal name denotes a collective term for both Read and Write. For

example, AxCACHE refers to both the ARCACHE and AWCACHE signals.

#### **Numbers**

Numbers are normally written in decimal. Binary numbers are preceded by 0b, and hexadecimal numbers by 0x. Both are written in a monospace font.

#### **Additional reading**

This section lists relevant publications from Arm.

See Arm Developer https://developer.arm.com/documentation for access to Arm documentation.

#### **Arm publications**

- AMBA ® AXI Protocol Specification (ARM IHI 0022)

- AMBA ® DTI Protocol Specification (ARM IHI 0088)

- AMBA ® CHI Architecture Specification (ARM IHI 0050)

- AMBA ® CHI Chip-to-Chip (C2C) Architecture Specification (ARM IHI 0098)

- Arm® System Memory Management Unit Architecture Specification (ARM IHI 0070)

- Arm® Architecture Reference Manual for A-profile Architecture (ARM DDI 0487)

#### Other publications

- PCIe Express Base Specification, Revision 6, PCI-SIG

- Compute Expresss Link (CXL), CXL Consortium

#### **Feedback**

Arm welcomes feedback on its documentation.

If you have any comments or suggestions for additions and improvements, create a ticket at https://support.developer.arm.com. As part of the ticket, include:

- The title, AMBA LTI Protocol Specification.

- The number, ARM IHI0089C.

- The section name to which your comments refer.

- The page number(s) to which your comments apply.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

#### Inclusive terminology commitment

Arm values inclusive communities. Arm recognizes that we and our industry have terms that can be offensive. Arm strives to lead the industry and create change.

Previous issues of this document included language that can be offensive. We have replaced this language. To report offensive language in this document, email terms@arm.com.

## Chapter 1 **Introduction**

This chapter introduces the AMBA LTI protocol specification:

- About the LTI protocol on page 1-18

- Differences between DTI and LTI on page 1-21

- Supported translation flows on page 1-22

#### 1.1 About the LTI protocol

The AMBA LTI protocol specification aligns with the SMMU architecture and complements AMBA *Distributed Translation Interface* (DTI) to provide higher performance and more efficient translation services.

LTI is a point-to-point protocol and defines the communication between an IO Manager and a *Translation Buffer Unit* (TBU). LTI enables devices to directly request a translation for each transaction while leaving the TBU to manage the *Translation Lookaside Buffer* (TLB). This enables translations to be requested before ordering requirements are met and avoiding the need to pass transactions through the TBU. This provides improved performance and reduced silicon area.

This specification describes the LTI protocol and the components of an LTI-compliant implementation. The LTI protocol is used by implementations of the Arm *System MMUv3* (SMMUv3) Architecture Specification.

#### 1.2 Use cases

A system incorporating an LTI-based System Memory Management Unit (SMMU) might have the following components:

- A client device whose transactions require translation.

- A Bus Interface Unit (BIU), which fetches a translation for each transaction using LTI.

- A *TLB Unit* (TLBU) caches translations in a TLB. TLBU receives translation requests using LTI, and if the requested translation is not available in its TLB, it requests translations from a TCU using DTI.

- A Translation Control Unit (TCU), which calculates translations, reading translation tables when required.

Typically, the BIU and TLBU are packaged together as a TBU. Alternatively, the TBU might consist of just the TLBU.

A device can be integrated in one of the following ways:

- In-line integration

- Lookaside integration on page 1-20

- Cached integration on page 1-20

#### 1.2.1 In-line integration

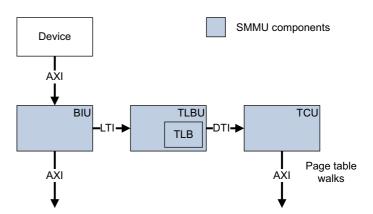

When in-line integration is implemented, every transaction passes through the SMMU, typically using AXI. The device is not aware of translation. Figure 1-1 shows the in-line integration option.

Figure 1-1 In-line SMMU Integration

#### 1.2.2 Lookaside integration

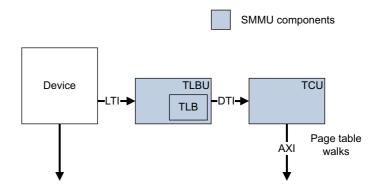

When lookaside integration is implemented, a translation request is made over LTI for each transaction, but the transaction data does not pass through the SMMU. Transaction completion is signaled to the TLBU using the LTI interface. This option is more complex than in-line integration, and enables the device to connect to the system using its native interface. Figure 1-2 shows the lookaside integration option.

Figure 1-2 Lookaside SMMU integration

#### 1.2.3 Cached integration

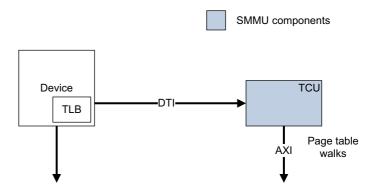

When cached integration is implemented, the device requests translations over DTI when required and caches them locally in an integrated TLB. The device must support invalidation messages. This option is the most complex, but gives the device control over how translations are cached, and can be the most efficient option for devices with specific caching requirements. Figure 1-3 shows the cached integration option.

Figure 1-3 Cached SMMU integration

#### 1.3 Differences between DTI and LTI

Table 1-1 shows the differences between the DTI and LTI protocols.

Table 1-1 LTI and DTI comparison

|                                            | LTI                                                                                                                                       | DTI                                                                                                                                                             |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Topology                                   | Designed for connecting to a single, local TLBU over a short distance.                                                                    | Designed for connecting multiple TBUs to a TCU over a longer distance.                                                                                          |

| Caching                                    | Translations must be used immediately and must not be not cached.                                                                         | Translations can be cached.                                                                                                                                     |

| Invalidation                               | No invalidation is required, because translations are not cached.                                                                         | The DTI Translation Buffer Unit (TBU) or PCIe <i>Root Port</i> (RP) must support invalidation messages to invalidate translations that are previously returned. |

| Transport                                  | AXI-like channel-based protocol gives dedicated signals for each data field to maximize throughput and avoid protocol conversion latency. | Message-based protocol can easily be passed over generic transports.                                                                                            |

| Mapping<br>translations to<br>transactions | Provides the translated transaction information directly, making it simple to use.                                                        | Requires the TBU or PCIe RP to follow rules on how to map configuration cache entries and TLB entries on to each transaction.                                   |

| Ordering                                   | Supports ordering of translations to match transaction ordering, or out of order operation.                                               | Supports fully out-of-order operation.                                                                                                                          |

#### 1.4 Supported translation flows

Several translation flows are supported by LTI.

#### 1.4.1 Stall flow

When the Stall flow is used, software can configure the SMMU to take one of the following actions when a translation fault occurs:

- Immediately terminate the transaction and optionally record an error record that informs software that the transaction was terminated.

- Stall the translation and inform software that the translation is stalled. Software can then terminate the

transaction, or update the translation tables and retry the translation. The LTI Manager is not aware of the

stall.

Stall flow enables software to manage translation faults and demand paging without the client device being aware. However, it has some limitations:

- The LTI Manager can see long translation times, potentially triggering timeouts.

- Due to the dependence of software activity, the Stall flow can cause deadlocks in some systems.

For example, Stall flow is not recommended for use with PCIe, because of dependencies between outgoing transactions to PCIe from a CPU, and incoming transactions from PCIe through the SMMU.

Stall flow is the most common flow for LTI Managers.

Enabling the Stall flow does not necessarily cause a stall when a translation fault occurs. Stalls only occur when enabled by software. Software does not normally enable stalling for PCIe endpoints.

#### 1.4.2 ATST flow

The Address Translation Service Translated (ATST) flow is a flow that is used by PCIe Root Ports only. The flow is:

- 1. A PCIe endpoint requests a translation over ATS, which is passed to the SMMU by the PCIe RP using the DTI-ATS protocol.

- The SMMU responds to the ATS request over DTI-ATS, which is passed back to the PCIe endpoint by the PCIe RP. If a translation fault occurs, then the response indicates the condition, and does not make any software-visible record.

- 3. The PCIe endpoint uses the ATS translation to translate the address of transaction, and then issues a transaction that is marked as ATS Translated.

An ATS Translated transaction uses the ATST flow. In all other respects, it is translated the same way as any other transaction. Normally this translation is fast because it is already translated by ATS, but some additional translation might still occur. For example, the SMMU can be configured to perform stage 1 translation when an ATS request is made, and perform stage 2 translation when the ATS Translated transaction is presented to the SMMU.

ATS translations are cached in the PCIe endpoint *Address Translation Cache* (ATC), for future use. These translations can be invalidated by ATS invalidation messages, which is conveyed over DTI-ATS.

If a translation fault occurs, the PCIe endpoint can issue a page request using the *Page Request Interface* (PRI), before retrying the ATS translation request if the PRI request is successful. PRI is an extension to ATS, and is also conveyed to the SMMU using DTI-ATS. The fault is not visible to LTI.

#### 1.4.3 NoStall flow

NoStall flow is used by a Manager that is not able to be stalled. If a translation fault occurs, the transaction is terminated, even if software has configured the device to be stalled when a translation fault occurs.

#### 1.4.4 PRI flow

The PRI flow is designed for use with a PCIe-enumerated endpoint. The device uses the LTI PRI flow to enable software to respond to translation faults without risking deadlock.

From a software point of view:

- The device is a PCIe endpoint.

- The device uses the ATS protocol to fetch translations.

- When a translation fault occurs, the device makes a page request using PRI.

The behavior of the LTI PRI flow is as follows:

- The SMMU ATS features are not required and not used, even though ATS is enabled in software.

Transactions are translated on-demand.

- If a translation fault occurs, no error is reported to software by the SMMU. Instead, a PRI fault response is returned to the LTI Manager.

- When the LTI Manager receives a PRI fault response, it uses a DTI-ATS connection to issue a page request. If the PRI response is successful, then the LTI Manager retries the transaction.

A device using this flow uses DTI-ATS for PRI requests only and does not make any ATS requests. In DTIv2, a device can implement a DTI-ATS connection that just performs PRI requests and does not receive ATS invalidation messages.

A device must be assigned page request credits by system software before it can issue PRI requests. These credits are not visible to the LTI or DTI protocols and are managed by PCIe software.

1 Introduction

1.4 Supported translation flows

## Chapter 2 Channels

This chapter describes LTI information flow:

- Transaction flow on page 2-26

- Virtual Channels on page 2-28

- Flow control on page 2-29

- Reserved encodings on page 2-30

- Signal validity on page 2-31

#### 2.1 Transaction flow

Table 2-1 shows the three LTI channels. For each channel, the TX is the component that sends a message on the channel and the RX is the component that receives the message.

Table 2-1 LTI interface channels

| Channel name Channel prefix |    | Channel TX  | Channel RX  |

|-----------------------------|----|-------------|-------------|

| LTI request                 | LA | Manager     | Subordinate |

| LTI response                | LR | Subordinate | Manager     |

| LTI completion              | LC | Manager     | Subordinate |

Additionally, interface management signals are included with the prefix LM.

In this specification, the term, Lx, is used to collectively refer to LA, LR, and LC.

A complete LTI transaction consists of a message on all three channels in sequence:

- 1. The Manager sends a request on the LA channel.

- 2. The Subordinate sends a response on the LR channel. Only after receiving the transaction can the translated transaction be issued downstream.

- 3. The Manager sends a completion on the LC channel, once the downstream transaction is complete.

There are no flows where any of these three stages can be skipped.

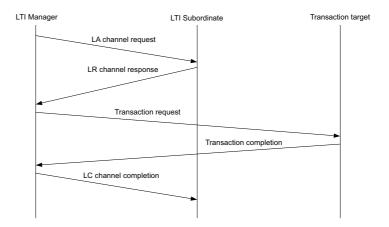

The relationship between LTI messages and the translated transaction are shown in Figure 2-1.

Figure 2-1 Relationship of messages

The LTI Subordinate does not correlate the completion messages to a specific LTI transaction, but instead counts the number of completions corresponding to each completion tag. The purpose of the Completion channel is to enable the LTI Subordinate to determine when all transactions with a completion tag have completed. This checking of the number of completions for a tag is part of the translation invalidation process. There are two completion tags to enable invalidation to take place without stopping the transaction flow.

An LTI response is permitted in the same cycle that the corresponding request is made. This response timing enables tightly coupled TLBs with low latency.

An LTI completion is not permitted in the same cycle that the corresponding response is returned. An LTI response can be followed by its completion in the following cycle or later.

All signals are driven by the channel TX, except LxCREDIT signals, which are driven by the channel RX.

An LTI transaction is considered to be outstanding from the cycle in which the LA request is used until the cycle in which the LC completion is issued.

#### 2.2 Virtual Channels

The LA and LR channels can be composed of multiple Virtual Channels. The LA and LR channels must support the same number of Virtual Channels.

The LC channel does not support multiple Virtual Channels. The LTI Subordinate must always be able to provide a credit on the LC channel without dependence on progress of other channels.

In an LTI transaction, messages on the LA and LR channels must use the same Virtual Channel (VC).

Because LC messages are not associated with a particular VC, it is necessary that any counter in the LTI Subordinate that is counting outstanding completions does not overflow. The LTI Subordinate must be able to track at least 65535 translation responses awaiting a completion. When this number is exceeded, the LTI Subordinate is permitted to introduce dependencies between Virtual Channels, by not returning a translation response until translation completions from previous translations are returned.

The intent of Virtual Channels is to enable one VC to progress when another is blocked, to avoid deadlock scenarios. Components implementing LTI must ensure that if progress is blocked on one VC it does not result in progress being blocked on a different VC.

In some cases, the forward progress properties of a single Virtual Channel is sufficient for an implementation.

Within a VC, LTI must make independent forward progress on all LTI transactions when:

- 1. The LA STALL flow is not used on any request.

- The LTI Manager is able to provide a credit to the LR channel without dependence on the progress of any other transaction.

- 3. The total number of translations that have sent an LTI request but haven't sent the LTI completion must not exceed the completion tracking limit of the LTI Subordinate.

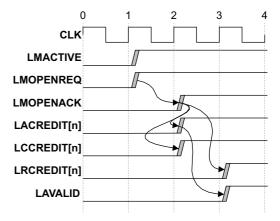

#### 2.3 Flow control

Flow control in the LTI protocol has the following rules:

- Each channel includes LxVALID and LxCREDIT signals. If more than one VC is supported, the LA and LR channels include LxVC signals.

- Each cycle that LxCREDIT[n] is asserted grants one credit on VC n to the channel TX.

- The channel TX consumes a credit on VC n each cycle that LxVALID is asserted with LxVC = n.

- LxVALID cannot be asserted with LxVC = n when the channel TX has zero credits for VC n.

- The maximum number of credits that the channel RX can grant the channel TX for each VC is 15.

In addition, there must not be combinatorial paths between LxCREDIT and other signals on a channel in either direction, such as LxVALID. This restriction has the following consequences:

- A credit cannot be used by LxVALID in the same cycle that it is granted by LxCREDIT when there are no

other credits granted.

- A credit cannot be returned on **LxCREDIT** in the same cycle that it is used by **LxVALID** when the maximum number of credits that are permitted to be granted is reached.

#### 2.4 Reserved encodings

Where encodings are given, unused encodings are Reserved.

$Use of a \ Reserved \ encoding \ in \ a \ field \ that \ is \ not \ ignored \ is \ a \ protocol \ error \ and \ can \ lead \ to \ UNPREDICTABLE \ behavior.$

#### 2.5 Signal validity

A signal can be defined as not valid within this specification. When a signal is not valid:

- The channel TX can drive it to any value.

- The channel RX must ignore its value.

## Chapter 3 **Properties**

This chapter describes the set of LTI properties that specifies the supported behavior and interface signaling requirements:

• *LTI properties* on page 3-34

#### 3.1 LTI properties

Table 3-1 describes the LTI properties.

All LTI properties have a minimum value of 0 and have no defined maximum value, unless otherwise specified.

**Table 3-1 LTI Properties**

| Name                                 | Туре    | Unit | Description                                                                                                                                            |  |

|--------------------------------------|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LTI_VC_COUNT                         | Integer | -    | Number of Virtual Channels. Minimum 1.                                                                                                                 |  |

| LTI_ID_WIDTH                         | Integer | bits | Width of translation request ID.                                                                                                                       |  |

| LTI_SID_WIDTH                        | Integer | bits | Width of StreamID. Maximum 32.  Higher-order bits of StreamID might be statically defined by the LTI Subordinate, for example using a tie-off.         |  |

| LTI_SSID_WIDTH                       | Integer | bits | Width of SubstreamID. Maximum 20.                                                                                                                      |  |

| LTI_OG_WIDTH                         | Integer | bits | Width of order group.                                                                                                                                  |  |

| LTI_TLBLOC_WIDTH                     | Integer | bits | Width of TLB location.                                                                                                                                 |  |

| LTI_LOOP_WIDTH                       | Integer | bits | Width of loopback signals.                                                                                                                             |  |

| LTI_LAUSER_WIDTH                     | Integer | bits | Width of translated address. LTI_LRADDR_WIDTH must be one of the following values:  • 32 • 36 • 40 • 42 • 44 • 48 • 52  Width of channel user signals. |  |

| LTI_LRUSER_WIDTH<br>LTI_LCUSER_WIDTH |         |      |                                                                                                                                                        |  |

| LTI_GPC                              | Boolean | -    | Set True to indicate that the SMMU is configured to perform Granule Protection Checks (GPC) as part of Realm Management Extension (RME).               |  |

**Table 3-1 LTI Properties (continued)**

| Name             | Туре        | Unit | Description                                                                                                                                                                                                                                                                                                                                                                     |  |

|------------------|-------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LTI_MMU          | Boolean     | -    | Set True to indicate that the SMMU is configured to perform Stage 1 and Stage 2 translations.                                                                                                                                                                                                                                                                                   |  |

| LTI_MECID_WIDTH  | Integer     | bits | Width of <i>Memory Encryption Context Identifier</i> (MECID).  LTI_MECID_WIDTH must be one of the following values:  • 0  • 16                                                                                                                                                                                                                                                  |  |

| LTI_MPAM_SUPPORT | Enumeration | -    | Used to indicate whether the interface supports MPAM. There are three values:  MPAM_9_1  This is the default value.  The interface is enabled for MPAM and includes LRMPAM.  The width of PARTID is 9 and PMG is  MPAM_12_1  The interface is enabled for MPAM and includes LRMPAM.  The width of PARTID is 12 and PMG is  False  MPAM is not supported and LRMPAM not present. |  |

|                  |             |      | See Table 10-3 on page 10-77 for more information on interoperability between an LTI Manager and Subordinate.                                                                                                                                                                                                                                                                   |  |

When the value of a property results in a signal being zero bits in width, that signal is omitted from the interface.

Table 3-2 shows how translations are affected by the combinations of properties LTI\_GPC and LTI\_MMU, and the signal LAMMUV.

Table 3-2 Legal combinations of properties LTI\_GPC and LTI\_MMU

| LTI_GPC | LTI_MMU | Interface usage                                                                              |

|---------|---------|----------------------------------------------------------------------------------------------|

| True    | True    | RME is supported.  When <b>LAMMUV</b> is HIGH, SMMU performs stage 1 and stage 2             |

|         |         | translations, as well as a GPC.                                                              |

|         |         | When LAMMUV is LOW, SMMU only performs a GPC.                                                |

| True    | False   | RME is supported.                                                                            |

|         |         | SMMU only performs a GPC.                                                                    |

|         |         | LAMMUV must be LOW.                                                                          |

| False   | True    | RME is not supported.                                                                        |

|         |         | When <b>LAMMUV</b> is HIGH, SMMU only performs stage 1 and stage 2 translations.             |

|         |         | When <b>LAMMUV</b> is LOW, SMMU does not perform stage 1 and stage 2 translations, or a GPC. |

LTI\_GPC and LTI\_MMU must not both be False.

3 Properties 3.1 LTI properties

# Chapter 4 Request channel

This chapter defines the LTI request (LA) channel:

- Signals on page 4-38

- *Transaction types* on page 4-43

- *Transaction attributes* on page 4-45

- *Transaction scope* on page 4-46

## 4.1 Signals

Table 4-1 describes the signals in the LA channel.

**Table 4-1 Request channel signals**

| Signal   | Category  | Width                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|-----------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LAVALID  | Transport | 1                        | Channel valid.  When this signal is LOW, other TX signals on the LA channel are not valid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| LAVC     | Transport | ceil(log2(LTI_VC_COUNT)) | VC number.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| LACREDIT | Transport | LTI_VC_COUNT             | Channel credit grant.  LACREDIT is an RX signal that flows in the other direction from other LA channel signals.  It is not affected by LAVALID.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| LAID     | Flow      | LTI_ID_WIDTH             | Translation request ID.  The ID must not match the ID of a previous request on the same VC that has not yet returned its LR channel response, unless LAOGV = 1 in both requests and the value of LAOG is the same for both requests.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| LAOGV    | Flow      |                          | Order group valid.  O No ordering required  The responses of all requests with this LAOG value must be returned in order.  There is no order requirement between requests on different Virtual Channels.  When LATRANS = UNSPEC, LAOGV must be LOW.  This signal is present even if LTI_OG_WIDTH = 0. In this case, there is a single order group, and LAOGV indicates whether each LTI request is ordered or unordered.  Note  If an LTI Manager uses LAFLOW = Stall for transactions issued downstream with order requirements, it is recommended for the LTI Manager to set LAOGV = 1 and use LTI order group instead of using unordered LTI requests. This prevents reordering the LTI responses and avoids deadlock. It is permitted to use unordered LTI requests for transactions issued downstream without order requirements. |

| LAOG     | Flow      | LTI_OG_WIDTH             | Order group. When <b>LAOGV</b> is LOW, this signal is not valid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Table 4-1 Request channel signals (continued)

| Signal   | Category | Width                    | Description                                 | 1                                                                                                                                                                                                                                                                                                                                                  |

|----------|----------|--------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LAFLOW   | Context  | 2                        | Indicates the                               | translation flow required.                                                                                                                                                                                                                                                                                                                         |

|          |          |                          | 0: Stall                                    | The SMMU stall fault flow can be used for this request, when it is enabled.                                                                                                                                                                                                                                                                        |

|          |          |                          | 1: ATST                                     | The transaction has already been translated by ATS.                                                                                                                                                                                                                                                                                                |

|          |          |                          | 2: NoStall                                  | If a translation fault occurs, then even if the SMMU has enabled stall faulting for this translation context, a fault response is returned without dependence on software activity.                                                                                                                                                                |

|          |          |                          | 3: PRI                                      | If a translation fault occurs, a fault response i returned indicating that a PRI request might resolve the fault. Architecturally, the request is treated as an ATS request, and translation faults do not result in an event record. This option is for use by PCIe enumerated endpoints. For more information, see <i>PRI flow</i> on page 1-23. |

|          |          |                          | response in r                               | is not Stall, then the Subordinate must return the easonable time, without dependence on softward ust not be Stall for PCIe Managers.                                                                                                                                                                                                              |

|          |          |                          | This signal is                              | s not valid when <b>LAMMUV</b> is LOW.                                                                                                                                                                                                                                                                                                             |

|          |          |                          | This signal is present only when LTI_MMU is |                                                                                                                                                                                                                                                                                                                                                    |

| LAMMUV   | Context  | 1                        | Indicates if S                              | MMU translation is required.                                                                                                                                                                                                                                                                                                                       |