# AMBA® DTI Protocol Specification

#### **AMBA DTI**

#### **Protocol Specification**

Copyright © 2016-2018, 2020-2024 Arm Limited or its affiliates. All rights reserved.

#### **Release Information**

The following changes have been made to this specification:

#### Change history

| Date              | Issue   | Confidentiality  | Change                                                                                                                                                                                                                                                                                                                                  |

|-------------------|---------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18 November 2016  | 0000-00 | Non-Confidential | Edition 0 (First release)                                                                                                                                                                                                                                                                                                               |

| 09 May 2017       | 0000-01 | Non-Confidential | Edition 1                                                                                                                                                                                                                                                                                                                               |

| 11 September 2017 | 0000-02 | Non-Confidential | Edition 2                                                                                                                                                                                                                                                                                                                               |

| 13 July 2018      | 0000-03 | Non-Confidential | Edition 3                                                                                                                                                                                                                                                                                                                               |

| 27 August 2020    | Е       | Non-Confidential | Addition of v2 protocols                                                                                                                                                                                                                                                                                                                |

| 16 June 2021      | E.b     | Non-Confidential | Technical corrections                                                                                                                                                                                                                                                                                                                   |

| 28 September 2023 | F       | Non-Confidential | DTI-TBU protocol: This issue is a standalone document for the DTI-TBUv3 protocol. Information on DTI-TBUv1 and DTI-TBUv2 is not included in this issue. For DTI-TBUv1 and DTI-TBUv2, see Arm Developer, https://developer.arm.com/documentation.  DTI-ATS protocol: This issue describes DTI-ATSv1, DTI-ATSv2, and DTI-ATSv3 protocols. |

| 28 June 2024      | G       | Non-Confidential | Support for DTI-TBUv4 and DTI-ATSv4, and other technical corrections.                                                                                                                                                                                                                                                                   |

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the use or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm Limited ("Arm"). No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether the subject matter of this document infringes any third party patents.

The content of this document is informational only. Any solutions presented herein are subject to changing conditions, information, scope, and data. This document was produced using reasonable efforts based on information available as of the date of issue of this document. The scope of information in this document may exceed that which Arm is required to provide, and such additional information is merely intended to further assist the recipient and does not represent Arm's view of the scope of its obligations. You acknowledge and agree that you possess the necessary expertise in system security and functional safety and that you shall be solely responsible for compliance with all legal, regulatory, safety and security related requirements concerning your products, notwithstanding any information or support that may be provided by Arm herein. In addition, you are responsible for any applications which are used in conjunction with any Arm technology described in this document, and to minimize risks, adequate design and operating safeguards should be provided for by you.

This document may include technical inaccuracies or typographical errors. THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, any patents, copyrights, trade secrets, trademarks, or other rights.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Reference by Arm to any third party's products or services within this document is not an express or implied approval or endorsement of the use thereof.

This document consists solely of commercial items. You shall be responsible for ensuring that any permitted use, duplication, or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of this document shall prevail.

The validity, construction and performance of this notice shall be governed by English Law.

The Arm corporate logo and words marked with ® or ™ are registered trademarks or trademarks of Arm Limited (or its affiliates) in the US and/or elsewhere. Please follow Arm's trademark usage guidelines at https://www.arm.com/company/policies/trademarks. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners.

Copyright © 2016-2018, 2020-2024 Arm Limited or its affiliates. All rights reserved.

Arm Limited. Company 02557590 registered in England. 110 Fulbourn Road, Cambridge, England CB1 9NJ. PRE-21451 version 3

#### AMBA SPECIFICATION LICENCE

THIS END USER LICENCE AGREEMENT ("LICENCE") IS A LEGAL AGREEMENT BETWEEN YOU (EITHER A SINGLE INDIVIDUAL, OR SINGLE LEGAL ENTITY) AND ARM LIMITED ("ARM") FOR THE USE OF ARM'S INTELLECTUAL PROPERTY (INCLUDING, WITHOUT LIMITATION, ANY COPYRIGHT) IN THE RELEVANT AMBA SPECIFICATION ACCOMPANYING THIS LICENCE. ARM LICENSES THE RELEVANT AMBA SPECIFICATION TO YOU ON CONDITION THAT YOU ACCEPT ALL OF THE TERMS IN THIS LICENCE. BY CLICKING "I AGREE" OR OTHERWISE USING OR COPYING THE RELEVANT AMBA SPECIFICATION YOU INDICATE THAT YOU AGREE TO BE BOUND BY ALL THE TERMS OF THIS LICENCE.

#### "LICENSEE" means You and your Subsidiaries.

"Subsidiary" means, if You are a single entity, any company the majority of whose voting shares is now or hereafter owned or controlled, directly or indirectly, by You. A company shall be a Subsidiary only for the period during which such control exists.

- Subject to the provisions of Clauses 2, 3 and 4, Arm hereby grants to LICENSEE a perpetual, non-exclusive, non-transferable, royalty free, worldwide licence to:

- (i) use and copy the relevant AMBA Specification for the purpose of developing and having developed products that comply with the relevant AMBA Specification;

- (ii) manufacture and have manufactured products which either: (a) have been created by or for LICENSEE under the licence granted in Clause 1(i); or (b) incorporate a product(s) which has been created by a third party(s) under a licence granted by Arm in Clause 1(i) of such third party's AMBA Specification Licence; and

- (iii) offer to sell, supply or otherwise distribute products which have either been (a) created by or for LICENSEE under the licence granted in Clause 1(i); or (b) manufactured by or for LICENSEE under the licence granted in Clause 1(ii).

- 2. LICENSEE hereby agrees that the licence granted in Clause 1 is subject to the following restrictions:

- (i) where a product created under Clause 1(i) is an integrated circuit which includes a CPU then either: (a) such CPU shall only be manufactured under licence from Arm; or (b) such CPU is neither substantially compliant with nor marketed as being compliant with the Arm instruction sets licensed by Arm from time to time;

- (ii) the licences granted in Clause 1(iii) shall not extend to any portion or function of a product that is not itself compliant with part of the relevant AMBA Specification; and

- (iii) no right is granted to LICENSEE to sublicense the rights granted to LICENSEE under this Agreement.

- 3. Except as specifically licensed in accordance with Clause 1, LICENSEE acquires no right, title or interest in any Arm technology or any intellectual property embodied therein. In no event shall the licences granted in accordance with Clause 1 be construed as granting LICENSEE, expressly or by implication, estoppel or otherwise, a licence to use any Arm technology except the relevant AMBA Specification.

- 4. THE RELEVANT AMBA SPECIFICATION IS PROVIDED "AS IS" WITH NO REPRESENTATION OR WARRANTIES EXPRESS, IMPLIED OR STATUTORY, INCLUDING BUT NOT LIMITED TO ANY WARRANTY OF SATISFACTORY QUALITY, MERCHANTABILITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE, OR THAT ANY USE OR IMPLEMENTATION OF SUCH ARM TECHNOLOGY WILL NOT INFRINGE ANY THIRD PARTY PATENTS, COPYRIGHTS, TRADE SECRETS OR OTHER INTELLECTUAL PROPERTY RIGHTS.

- 5. NOTWITHSTANDING ANYTHING TO THE CONTRARY CONTAINED IN THIS AGREEMENT, TO THE FULLEST EXTENT PETMITTED BY LAW, THE MAXIMUM LIABILITY OF ARM IN AGGREGATE FOR ALL CLAIMS MADE AGAINST ARM, IN CONTRACT, TORT OR OTHERWISE, IN CONNECTION WITH THE SUBJECT MATTER OF THIS AGREEMENT (INCLUDING WITHOUT LIMITATION (I) LICENSEE'S USE OF THE ARM TECHNOLOGY; AND (II) THE IMPLEMENTATION OF THE ARM TECHNOLOGY IN ANY PRODUCT CREATED BY LICENSEE UNDER THIS AGREEMENT) SHALL NOT EXCEED THE FEES PAID (IF ANY) BY LICENSEE TO ARM UNDER THIS AGREEMENT. THE EXISTENCE OF MORE THAN ONE CLAIM OR SUIT WILL NOT ENLARGE OR EXTEND THE LIMIT. LICENSEE RELEASES ARM FROM ALL OBLIGATIONS, LIABILITY, CLAIMS OR DEMANDS IN EXCESS OF THIS LIMITATION.

- 6. No licence, express, implied or otherwise, is granted to LICENSEE, under the provisions of Clause 1, to use the Arm tradename, or AMBA trademark in connection with the relevant AMBA Specification or any products based thereon. Nothing in Clause 1 shall be construed as authority for LICENSEE to make any representations on behalf of Arm in respect of the relevant AMBA Specification.

- 7. This Licence shall remain in force until terminated by you or by Arm. Without prejudice to any of its other rights if LICENSEE is in breach of any of the terms and conditions of this Licence then Arm may terminate this Licence immediately upon giving written notice to You. You may terminate this Licence at any time. Upon expiry or termination of this Licence by You or by Arm LICENSEE shall stop using the relevant AMBA Specification and destroy all copies of the relevant AMBA Specification in your possession together with all documentation and related materials. Upon expiry or termination of this Licence, the provisions of clauses 6 and 7 shall survive.

8. The validity, construction and performance of this Agreement shall be governed by English Law.

PRE-21451 version 3

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

### Contents

### **AMBA DTI Protocol Specification**

|           | Pret  | ace                                    |                  |

|-----------|-------|----------------------------------------|------------------|

|           |       | About this specification               | x                |

|           |       | Intended audience                      | x                |

|           |       | Using this specification               | x                |

|           |       | Conventions                            | x                |

|           |       | Typographic conventions                | x                |

|           |       | Signals                                | xi               |

|           |       | Numbers                                | xi               |

|           |       | Additional reading                     | xi               |

|           |       | Arm publications                       | xi               |

|           |       | Other publications                     | xi               |

|           |       | Feedback on this specification         | x                |

|           |       | Inclusive language commitment          | X                |

| Chapter 1 | Intro | oduction                               |                  |

|           | 1.1   | About DTI protocols                    | 1-1              |

|           |       | 1.1.1 Protocol interaction             | 1-18             |

|           |       | 1.1.2 Field references                 | 1-1!             |

|           | 1.2   | DTI protocol specification terminology | 1-20             |

| Chapter 2 | DTI   | Protocol Overview                      |                  |

| -         | 2.1   | DTI protocol messages                  | 2-2 <sup>/</sup> |

|           |       | 2.1.1 Message groups                   |                  |

|           |       | 2.1.2 Message listing                  |                  |

|           |       | 2.1.3 Flow control                     | 2-2 <sup>-</sup> |

|           |       | 2.1.4 Reserved fields                  |                  |

|           |       | 2.1.5 Reserved encodings               |                  |

|           |       | 2.1.6 IMPLEMENTATION DEFINED fields    |                  |

|           |       | 2.1.7 Ignored fields                   | 2-2 <sup>-</sup> |

|           |       |                                        |                  |

|           | 2.2  | Manag   | ging DTI connections                                | 2-28               |

|-----------|------|---------|-----------------------------------------------------|--------------------|

|           |      | 2.2.1   | Channel states                                      |                    |

|           |      | 2.2.2   | Handshaking                                         |                    |

|           |      | 2.2.3   | Initialization and disconnection                    |                    |

|           |      | 2.2.4   | Connecting multiple TBUs or PCIe RPs to a TCU       |                    |

|           |      | 2.2.4   | Connecting multiple 1003 of 1 Gle N/3 to a 100      | 2-30               |

| Chapter 3 | DTI- | TBU Me  | ssages                                              |                    |

|           | 3.1  | Conne   | ction and disconnection message group               | 3-32               |

|           |      | 3.1.1   | DTI_TBU_CONDIS_REQ                                  |                    |

|           |      | 3.1.2   | DTI_TBU_CONDIS_ACK                                  |                    |

|           | 3.2  | Transla | ation request message group                         |                    |

|           |      | 3.2.1   | DTI_TBU_TRANS_REQ                                   |                    |

|           |      | 3.2.2   | DTI_TBU_TRANS_RESP                                  |                    |

|           |      | 3.2.3   | DTI TBU TRANS RESPEX                                |                    |

|           |      | 3.2.4   | DTI_TBU_TRANS_FAULT                                 |                    |

|           |      | 3.2.5   | Additional rules on permitted translation responses |                    |

|           |      | 3.2.6   |                                                     |                    |

|           |      |         | Calculating transaction attributes                  |                    |

|           |      | 3.2.7   | Speculative transactions and translations           |                    |

|           |      | 3.2.8   | Cache lookup process                                |                    |

|           | 3.3  |         | ation and synchronization message group             |                    |

|           |      | 3.3.1   | DTI_TBU_INV_REQ                                     |                    |

|           |      | 3.3.2   | DTI_TBU_INV_ACK                                     |                    |

|           |      | 3.3.3   | DTI_TBU_SYNC_REQ                                    |                    |

|           |      | 3.3.4   | DTI_TBU_SYNC_ACK                                    | 3-70               |

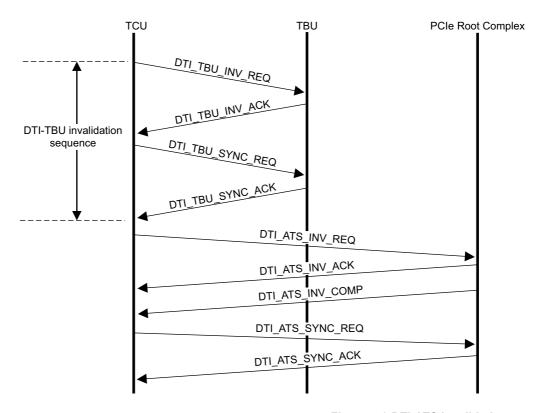

|           |      | 3.3.5   | DTI-TBU invalidation sequence                       | 3-70               |

|           |      | 3.3.6   | DTI-TBU invalidation operations                     | 3-73               |

|           | 3.4  | Regist  | er access message group                             | 3-81               |

|           |      | 3.4.1   | DTI_TBU_REG_WRITE                                   |                    |

|           |      | 3.4.2   | DTI_TBU_REG_WACK                                    |                    |

|           |      | 3.4.3   | DTI TBU REG READ                                    |                    |

|           |      | 3.4.4   | DTI_TBU_REG_RDATA                                   |                    |

|           |      | 3.4.5   | Deadlock avoidance in register accesses             |                    |

|           | 3.5  |         | ge dependencies for DTI-TBU                         |                    |

|           |      |         |                                                     |                    |

| Chapter 4 |      | ATS Me  |                                                     | 4.00               |

|           | 4.1  |         | ction and disconnection message group               |                    |

|           |      | 4.1.1   | DTI_ATS_CONDIS_REQ                                  |                    |

|           |      | 4.1.2   | DTI_ATS_CONDIS_ACK                                  |                    |

|           | 4.2  | Transla | ation request message group                         | 4-94               |

|           |      | 4.2.1   | DTI_ATS_TRANS_REQ                                   | 4-94               |

|           |      | 4.2.2   | DTI_ATS_TRANS_RESP                                  | 4-97               |

|           |      | 4.2.3   | DTI_ATS_TRANS_FAULT                                 | 4-103              |

|           |      | 4.2.4   | The ATS translation sequence                        |                    |

|           | 4.3  | Invalid | ation and synchronization message group             |                    |

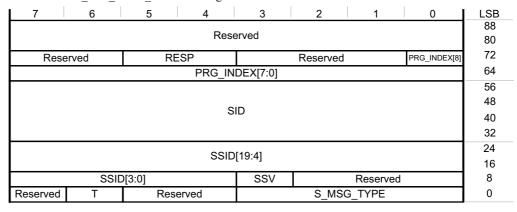

|           |      | 4.3.1   | DTI ATS INV REQ                                     |                    |

|           |      | 4.3.2   | DTI ATS INV ACK                                     |                    |

|           |      | 4.3.3   | DTI ATS INV COMP                                    |                    |

|           |      | 4.3.4   | DTI_ATS_SYNC_REQ                                    |                    |

|           |      | 4.3.4   |                                                     |                    |

|           |      |         | DTI_ATS_SYNC_ACK                                    |                    |

|           |      | 4.3.6   | The DTI-ATS invalidation sequence                   |                    |

|           |      | 4.3.7   | DTI-ATS invalidation operations                     |                    |

|           | 4.4  |         | request message group                               |                    |

|           |      | 4.4.1   | DTI_ATS_PAGE_REQ                                    |                    |

|           |      | 4.4.2   | DTI_ATS_PAGE_ACK                                    |                    |

|           |      | 4.4.3   | DTI_ATS_PAGE_RESP                                   | 4-120              |

|           |      | 4.4.4   | DTI_ATS_PAGE_RESPACK                                | 4-122              |

|           |      | 4.4.5   | Generating the page response                        |                    |

|           | 4.5  | Messa   | ge dependencies for DTI-ATS                         |                    |

|           |      |         | • • • • • • • • • • • • • • • • • • • •             | · · <del>-</del> · |

| Chapter 5  | Tran | sport L |                                    |       |

|------------|------|---------|------------------------------------|-------|

|            | 5.1  | Introdu | uction                             | 5-128 |

|            | 5.2  | AXI4-S  | Stream transport protocol          | 5-129 |

|            |      | 5.2.1   | AXI4-Stream signals                | 5-129 |

|            |      | 5.2.2   | Interleaving                       | 5-130 |

|            |      | 5.2.3   | Usage of the TID and TDEST signals | 5-130 |

| Chapter 6  | Pseu | ıdocode | e                                  |       |

|            | 6.1  | Memoi   | ry attributes                      | 6-132 |

|            |      | 6.1.1   | Memory attribute types             | 6-132 |

|            |      | F.1.2   | Memory attribute decoding          | 6-133 |

|            |      | 6.1.3   | Memory attribute processing        | 6-134 |

|            | 6.2  | Cache   | lookup                             |       |

|            |      | 6.2.1   | MatchTranslation                   |       |

|            |      | 6.2.2   | MatchFault                         | 6-139 |

|            |      | 6.2.3   | PermissionCheck                    | 6-139 |

|            |      | 6.2.4   | Shared pseudocode                  | 6-140 |

| Annendix A | Revi | eione   |                                    |       |

### **Preface**

This preface introduces the AMBA Distributed Translation Interface protocol specification.

It contains the following sections:

- About this specification on page xii

- Additional reading on page xiv

- Feedback on this specification on page xv

#### About this specification

This specification describes the AMBA Distributed Translation Interface (DTI) protocol. It includes information on DTI messages, caching model, transport layer, and the pseudocode that describes various features of the DTI protocol.

#### Intended audience

This specification is intended for the following audiences:

- Root Complex designers implementing ATS functionality.

- Designers of components implementing TBU functionality.

#### Using this specification

This specification is organized into the following chapters:

#### Chapter 1 Introduction

This chapter introduces the DTI protocol.

#### Chapter 2 DTI Protocol Overview

This chapter provides an overview of the DTI protocol.

#### Chapter 3 DTI-TBU Messages

This chapter describes the message groups of the DTI-TBU protocol.

#### Chapter 4 DTI-ATS Messages

This chapter describes the message groups of the DTI-ATS protocol.

#### Chapter 5 Transport Layer

This chapter describes the transport layer of the DTI protocol.

#### Chapter 6 Pseudocode

This chapter provides example implementations of the requirements specified in this specification.

#### Appendix A Revisions

Information about the technical changes between released issues of this specification.

#### Conventions

The following sections describe conventions that this specification can use:

- Typographic conventions

- Signals on page xiii

- Numbers on page xiii

#### Typographic conventions

The typographical conventions are:

italic Highlights important notes, introduces special terminology, and indicates internal

cross-references and citations.

bold Denotes signal names, and is used for terms in descriptive lists, where appropriate.

monospace Used for assembler syntax descriptions, pseudocode, and source code examples.

Also used in the main text for instruction mnemonics and for references to other items appearing in assembler syntax descriptions, pseudocode, and source code examples.

SMALL CAPITALS Used for a few terms that have specific technical meanings.

#### **Signals**

The signal conventions are:

Signal level The level of an asserted signal depends on whether the signal is active-HIGH or

active-LOW. Asserted means:

• HIGH for active-HIGH signals

• LOW for active-LOW signals

**Lowercase n** At the start or end of a signal name denotes an active-LOW signal.

**Lowercase x** At the second letter of a signal name denotes a collective term for both Read and Write.

#### **Numbers**

Numbers are normally written in decimal. Binary numbers are preceded by 0b, and hexadecimal numbers by 0x. In both cases, the prefix and the associated value are written in a monospace font, for example, 0xFFFF0000.

#### **Additional reading**

This section lists relevant publications from Arm. See Arm Developer, https://developer.arm.com/documentation for access to Arm documentation.

#### **Arm publications**

- AMBA® LTI Protocol Specification (ARM IHI 0089)

- Arm® System Memory Management Unit Architecture Specification SMMU architecture version 3 (ARM IHI 0070)

- AMBA® AXI-Stream Protocol Specification (ARM IHI 0051)

#### Other publications

- PCI Express Base Specification, Revision 6, PCI-SIG

- Compute Express Link Specification, Compute Express Link<sup>TM</sup> Consortium, Inc., Revision 3

#### Feedback on this specification

Arm welcomes feedback on its documentation.

If you have any comments or suggestions for additions and improvements, create a ticket at <a href="https://support.developer.arm.com">https://support.developer.arm.com</a>. As part of the ticket, please include:

- The title, AMBA DTI Protocol Specification.

- The number, ARM IHI 0088G.

- The page number(s) that your comments apply.

- A concise explanation of your comments.

| —— Note –        |                                                                                             |

|------------------|---------------------------------------------------------------------------------------------|

| Arm tests PDFs o | only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the appearance or behavior o |

| any document wh  | nen viewed with any other PDF reader.                                                       |

#### Inclusive language commitment

Arm values inclusive communities. Arm recognizes that we and our industry have used terms that can be offensive. Arm strives to lead the industry and create change.

Previous issues of this document included terms that can be offensive. We have replaced these terms. If you find offensive terms in this document, please contact terms@arm.com.

Preface Feedback on this specification

## Chapter 1 **Introduction**

This chapter introduces the DTI protocol.

It contains the following sections:

- About the DTI protocols on page 1-18

- DTI protocol specification terminology on page 1-20

#### 1.1 About the DTI protocols

This section introduces the AMBA Distributed Translation Interface (DTI) protocols and describes the components of a DTI-compliant implementation.

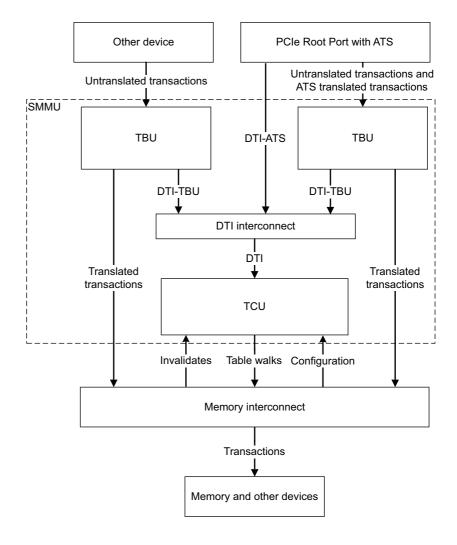

The DTI protocol is used by implementations of the *Arm*\* *System MMUv3* (SMMUv3) *Architecture Specification*. An SMMUv3 implementation that is built using the DTI interface consists of the following components:

- A Translation Control Unit (TCU) that performs translation table walks and implements the SMMUv3 programmers' model.

- At least one Translation Buffer Unit (TBU). The TBU intercepts transactions in need of translation and provides translations for them. The TBU requests translations from the TCU and caches those translations for use by other transactions.

The TCU communicates with the TBU to invalidate cached translations when necessary.

- A PCI Express (PCIe) Root Port with Address Translation Services (ATS) support. For more information, see

the PCI Express Base Specification. When PCIe ATS functionality is required, this component communicates

directly with the TCU to retrieve ATS translations, and then uses a TBU to:

- Translate transactions that have not already been translated using ATS.

- Perform stage 2 translation for transactions that have been subject to stage 1 translation using ATS.

- Ensure that only trusted PCIe endpoints can issue transactions with ATS translations, by performing security checks on ATS translated traffic.

- A DTI interconnect that manages the communication between TBUs and the TCU, and between PCIe Root Ports implementing ATS and the TCU.

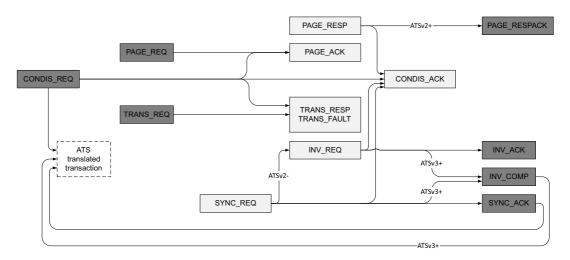

This specification specifies two protocols, which have different purposes:

- DTI-TBU protocol defines communication between a TBU and a TCU.

- DTI-ATS protocol defines communication between a PCIe Root Port and a TCU.

These two protocols are collectively referred to as the DTI protocol. The current versions of the DTI protocol are as follows:

| DTI-TBUv1 | Describes DTI-TBU version 1. |

|-----------|------------------------------|

| DTI-TBUv2 | Describes DTI-TBU version 2. |

| DTI-TBUv3 | Describes DTI-TBU version 3. |

| DTI-TBUv4 | Describes DTI-TBU version 4. |

| DTI-ATSv1 | Describes DTI-ATS version 1. |

| DTI-ATSv2 | Describes DTI-ATS version 2. |

| DTI-ATSv3 | Describes DTI-ATS version 3. |

| DTI-ATSv4 | Describes DTI-ATS version 4. |

|           |                              |

This specification does not describe DTI-TBUv1 and DTI-TBUv2. For information on these versions, see Arm Developer, https://developer.arm.com/documentation.

#### 1.1.1 Protocol interaction

The DTI protocol is a point-to-point protocol. Each channel consists of a link between a TBU or PCIe Root Port implementing ATS, and a TCU.

Components using the SMMU must provide the correct StreamID and SubstreamID. For ATS translated transactions, a PCIe Root Port must provide additional information.

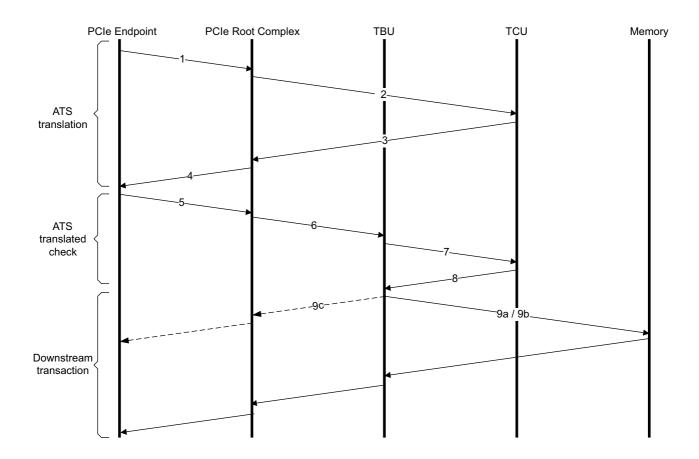

Figure 1-1 shows an example SMMU system that implements DTI.

Figure 1-1 An example SMMU system

Figure 1-1 includes the necessary components of a DTI-compliant implementation. However, DTI connections can cover large distances across an SoC. Most implementations do not include a standalone SMMU component. DTI allows an implementation to distribute the functions of the SMMU across the SoC with TBUs located close to the devices that require translation.

It is possible for a device to implement its own TBU functionality. This allows the following behavior:

- A device can incorporate advanced or specialized prefetching or translation caching requirements that cannot be met by a general-purpose TBU design.

- A device that can require a fully coherent connection to the memory interconnect and require very low

latency translation. For fully coherent operations, all caches in the device must be tagged with physical

addresses. This requires that translation is performed before the first level of caching. In such systems, the

translation must be fast and is normally tightly integrated into the design of the device.

#### 1.1.2 Field references

The behavior or values returned by the component sometimes depends on previous messages. Since some message pairs have the same field names, it is necessary to specify which message has the field (FIELD) being referenced. Fields from the corresponding message (MSG) are referenced as MSG.FIELD. Fields from the message are referenced as FIELD, without the qualifier.

#### 1.2 DTI protocol specification terminology

This document uses the following terms and abbreviations.

**ASID**

Address Space ID, distinguishing TLB entries for separate address spaces. For example, address spaces of different PE processes are distinguished by ASID.

**ATS**

PCI Express term, Address Translation Services, which are provided for remote endpoint TLBs.

**Downstream**

A direction of information flow where the information is flowing away from the TBU or the Root Complex.

DTI-ATSv1

Describes characteristics of DTI-ATS version 1.

DTI-ATSv2

Describes characteristics of DTI-ATS version 2.

DTI-ATSv3

Describes characteristics of DTI-ATS version 3.

DTI-ATSv4

Describes characteristics of DTI-ATS version 4.

DTI-TBUv1

Describes characteristics of DTI-TBU version 1.

DTI-TBUv2

Describes characteristics of DTI-TBU version 2.

DTI-TBUv3

Describes characteristics of DTI-TBU version 3.

DTI-TBUv4

Describes characteristics of DTI-TBU version 4.

E2H

EL2 Host mode. The Virtualization Host Extensions, introduced in the *Arm Architecture Reference Manual for A-profile architecture, Issue B*, extend the EL2 translation regime providing ASID-tagged translations.

Endpoint

A PCI Express function, which is used in the context of a device that is a client of the SMMU.

HTTU

Hardware Translation Table Update. The act of updating the Access flag or Dirty state of a page in a given TTD that is automatically done in hardware on an access or write to the corresponding page.

#### IMPLEMENTATION DEFINED

Means that the behavior is not architecturally defined but must be defined and documented by individual implementations.

IPA

Intermediate Physical Address

PA

Physical Address

**PASID**

PCI Express term: Process Address Space ID, an endpoint-local ID. There might be many distinct uses of a specific PASID value in a system.

**PCI**

Peripheral Component Interconnect specification

**PCIe**

PCI Express

#### **PCIe Root Complex**

A PCIe System Element that includes at least one Host Bridge, Root Port, or Root Complex Integrated Endpoint.

PCIe RP

A port on a PCIe Root Complex

PRI

ATS Page Request Interface mechanism

**SMMU**

System MMU. Unless otherwise specified, this term is used to mean SMMUv3.

#### StreamWorld

SMMUv3 translations have a StreamWorld property that denotes the translation regime and is directly equivalent to an Exception level on a PE.

#### StreamID

A StreamID uniquely identifies a stream of transactions that can originate from different devices but are associated with the same context.

#### SubstreamID

A SubstreamID might optionally be provided to an SMMU implementing stage 1 translation.

The SubstreamID differentiates streams of traffic originating from the same logical block to associate different application address translations to each.

#### Upstream

A direction of information flow where the information is flowing towards the TBU or Root Complex.

VA

Virtual address

#### **VMID**

Virtual Machine ID, distinguishing TLB entries for addresses from separate virtual machines.

| 1  | Introduction                  |             |

|----|-------------------------------|-------------|

| 1. | .2 DTI protocol specification | terminology |

## Chapter 2 **DTI Protocol Overview**

This chapter is an overview of the DTI protocol. It contains the following sections:

- DTI protocol messages on page 2-24

- Managing DTI connections on page 2-28

#### 2.1 DTI protocol messages

This section contains the following subsections:

- Message groups

- Message listing

- Flow control on page 2-27

- Reserved fields on page 2-27

- IMPLEMENTATION DEFINED fields on page 2-27

#### 2.1.1 Message groups

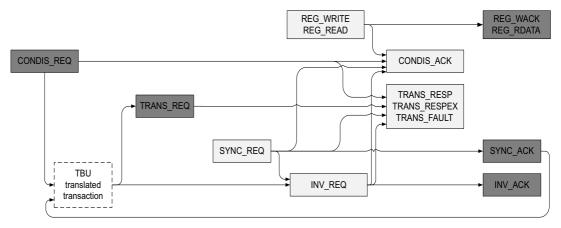

DTI protocol messages are grouped according to function. Table 2-1 shows the DTI message groups:

Table 2-1 Message groups of the DTI Protocol

| Message group                    | Direction of first message | DTI-TBU protocol function                                                                                                                                                                         | DTI-ATS protocol function                                                               |

|----------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Connection and disconnection     | Downstream                 | Establishes or terminates the connection.                                                                                                                                                         | Establishes or terminates the connection.                                               |

| Translation request              | Downstream                 | Retrieves a non-ATS translation.  Performs permission checks and stage 2 translations, if necessary, on translations that have been translated by ATS.  Performs Granule Protection Checks (GPC). | Retrieves an ATS<br>translation.<br>Performs GPC.                                       |

| Invalidation and synchronization | Upstream                   | Invalidates cached translations.                                                                                                                                                                  | Invalidates cached ATS translations.                                                    |

| Page request                     | Downstream                 | -                                                                                                                                                                                                 | Requests that pages are available using the ATS Page Request Interface (PRI) mechanism. |

| Register access                  | Upstream                   | Provides access to local IMPLEMENTATION DEFINED registers.                                                                                                                                        | -                                                                                       |

#### 2.1.2 Message listing

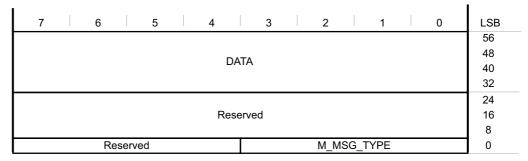

DTI messages are fixed length and have a whole number of bytes in size. The transport medium must preserve the correct number of bytes for each message.

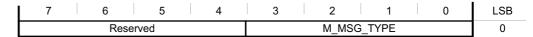

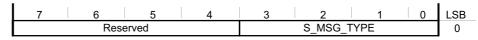

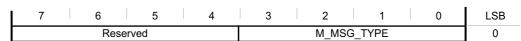

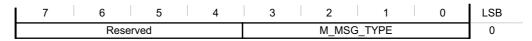

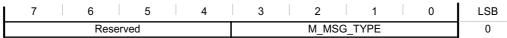

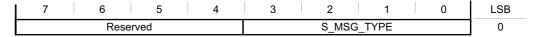

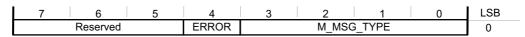

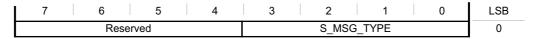

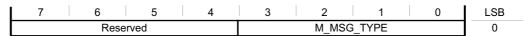

The four least significant bits of every message are used to encode the message type.

Some message types include a protocol field. In that case, the message is identified by the combination of its message type and protocol field values.

The message type encodings are defined independently for upstream and downstream messages.

2-24

#### **DTI-TBU** protocol downstream messages

Table 2-2 shows the downstream messages of the DTI-TBU protocol.

Table 2-2 DTI-TBU protocol downstream messages

| Message            | M_MSG_TYPE field encoding                                                                  | Message length in bits                                                                                                                       |  |

|--------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| DTI_TBU_CONDIS_REQ | 0x0                                                                                        | 32                                                                                                                                           |  |

| DTI_TBU_TRANS_REQ  | 0x2                                                                                        | 160                                                                                                                                          |  |

| DTI_TBU_INV_ACK    | 0x4                                                                                        | 8                                                                                                                                            |  |

| DTI_TBU_SYNC_ACK   | 0x5                                                                                        | 8                                                                                                                                            |  |

| DTI_TBU_REG_WACK   | 0x6                                                                                        | 8                                                                                                                                            |  |

| DTI_TBU_REG_RDATA  | 0x7                                                                                        | 64                                                                                                                                           |  |

| -                  | 0xE                                                                                        | -                                                                                                                                            |  |

| -                  | 0xF                                                                                        | -                                                                                                                                            |  |

|                    | DTI_TBU_CONDIS_REQ  DTI_TBU_TRANS_REQ  DTI_TBU_INV_ACK  DTI_TBU_SYNC_ACK  DTI_TBU_REG_WACK | DTI_TBU_CONDIS_REQ 0x0  DTI_TBU_TRANS_REQ 0x2  DTI_TBU_INV_ACK 0x4  DTI_TBU_SYNC_ACK 0x5  DTI_TBU_REG_WACK 0x6  DTI_TBU_REG_RDATA 0x7  - 0xE |  |

#### **DTI-TBU** protocol upstream messages

Table 2-3 shows the upstream messages of the DTI-TBU protocol.

Table 2-3 DTI-TBU protocol upstream messages

| Message group                | Message              | S_MSG_TYPE field encoding | Message length in bits |

|------------------------------|----------------------|---------------------------|------------------------|

| Connection and disconnection | DTI_TBU_CONDIS_ACK   | 0x0                       | 32                     |

| Translation request          | DTI_TBU_TRANS_FAULT  | 0x1                       | 32                     |

|                              | DTI_TBU_TRANS_RESP   | 0x2                       | 160                    |

|                              | DTI_TBU_TRANS_RESPEX | 0x3                       | 192                    |

| Invalidation and             | DTI_TBU_INV_REQ      | 0x4                       | 128                    |

| synchronization              | DTI_TBU_SYNC_REQ     | 0x5                       | 8                      |

| Register access              | DTI_TBU_REG_WRITE    | 0x6                       | 64                     |

|                              | DTI_TBU_REG_READ     | 0x7                       | 32                     |

| IMPLEMENTATION               | -                    | 0xE                       | -                      |

| DEFINED                      | -                    | 0xF                       | -                      |

#### **DTI-ATS** protocol downstream messages

Table 2-4 shows the downstream messages of the DTI-ATS protocol.

Table 2-4 DTI-ATS protocol downstream message

| Message               | M_MSG_TYPE field encoding                                                                                     | Message<br>length in bits                                                                                                                                               |

|-----------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DTI_ATS_CONDIS_REQ    | 0x0                                                                                                           | 32                                                                                                                                                                      |

| DTI_ATS_TRANS_REQ     | 0x2                                                                                                           | 160                                                                                                                                                                     |

| DTI_ATS_INV_ACK       | 0xC                                                                                                           | 8                                                                                                                                                                       |

| DTI_ATS_INV_COMPa     | 0xB                                                                                                           | 96                                                                                                                                                                      |

| DTI_ATS_SYNC_ACK      | 0xD                                                                                                           | 8                                                                                                                                                                       |

| DTI_ATS_PAGE_REQ      | 0x8                                                                                                           | 128                                                                                                                                                                     |

| DTI_ATS_PAGE_RESPACKb | 0x9                                                                                                           | 8                                                                                                                                                                       |

| -                     | 0xE                                                                                                           | -                                                                                                                                                                       |

| -                     | 0xF                                                                                                           | -                                                                                                                                                                       |

|                       | DTI_ATS_CONDIS_REQ  DTI_ATS_TRANS_REQ  DTI_ATS_INV_ACK  DTI_ATS_INV_COMPa  DTI_ATS_SYNC_ACK  DTI_ATS_PAGE_REQ | DTI_ATS_CONDIS_REQ 0x0  DTI_ATS_TRANS_REQ 0x2  DTI_ATS_INV_ACK 0xC  DTI_ATS_INV_COMPa 0xB  DTI_ATS_SYNC_ACK 0xD  DTI_ATS_PAGE_REQ 0x8  DTI_ATS_PAGE_RESPACKb 0x9  - 0xE |

a. DTI-ATSv3 or later

#### **DTI-ATS** protocol upstream message

Table 2-5 shows the upstream messages of the DTI-ATS protocol.

Table 2-5 DTI-ATS protocol upstream messages

| Message group                    | Message             | S_MSG_TYPE field encoding | Message length in bits |

|----------------------------------|---------------------|---------------------------|------------------------|

| Connection and disconnection     | DTI_ATS_CONDIS_ACK  | 0x0                       | 32                     |

| Translation request              | DTI_ATS_TRANS_FAULT | 0x1                       | 32                     |

|                                  | DTI_ATS_TRANS_RESP  | 0x2                       | 160                    |

| Invalidation and synchronization | DTI_ATS_INV_REQ     | 0xC                       | 128                    |

|                                  | DTI_ATS_SYNC_REQ    | 0xD                       | 8                      |

| Page request                     | DTI_ATS_PAGE_ACK    | 0x8                       | 8                      |

|                                  | DTI_ATS_PAGE_RESP   | 0x9                       | 96                     |

| IMPLEMENTATION                   | -                   | 0xE                       | -                      |

| DEFINED                          | -                   | 0xF                       | -                      |

#### **IMPLEMENTATION DEFINED messages**

Messages with bits [3:0] equal to 0xE or 0xF can be used for IMPLEMENTATION DEFINED purposes.

b. DTI-ATSv2 or later

IMPLEMENTATION DEFINED messages must only be exchanged between components that are designed to expect them when in permitted channel states. See *Channel states* on page 2-28.

The mechanism for discovering this, if required, is IMPLEMENTATION DEFINED.

#### 2.1.3 Flow control

The DTI protocol uses tokens to provide flow control. The tokens are used to manage the number of messages of different types that can be outstanding at a point in time.

The DTI protocol uses the following types of tokens:

#### **Translation tokens**

Used in translation requests to limit the number of outstanding translation requests.

#### **Invalidation tokens**

Used in invalidation messages to limit the number of outstanding invalidation requests.

Request messages consume tokens and response messages return them. See *Flow control result* section of respective message. If a response message is received over multiple cycles, then the token is only returned when the complete message has been received.

IDs are used to track some outstanding messages. A new request message cannot reuse an ID until a response message with that ID is received. If a response message is received over multiple cycles when the width of DTI interface is narrower than width of the response message, then the ID can only be reused when the complete message has been received. If a request message has multiple response messages associated with it, then the ID can only be reused when the final response message has been received. More details can be found in the *Flow control result* section of each message.

| Note —                            |                                     |          |         |       |      |

|-----------------------------------|-------------------------------------|----------|---------|-------|------|

| The only response message that is | not the final response message is I | DTI_TBU_ | _TRANS_ | FAULT | with |

| FAULT TYPE = TranslationStall.    |                                     |          |         |       |      |

#### 2.1.4 Reserved fields

Reserved fields in messages are described as either Should-Be-Zero (SBZ) or Should-Be-One (SBO).

The recipient of a message with Reserved fields must ignore these fields. It is recommended that the sender drive a Reserved field to 0 if it is described as SBZ, and 1 if it is described as SBO.

#### 2.1.5 Reserved encodings

When a field is not Reserved but it has Reserved encodings, it is a protocol error to use a Reserved encoding.

#### 2.1.6 IMPLEMENTATION DEFINED fields

Some message fields are defined as being IMPLEMENTATION DEFINED. These fields can be used by implementations for any defined purpose.

These fields are treated as Reserved by components that do not require them.

#### 2.1.7 Ignored fields

If a message has Ignored fields, the sender can drive any value to these fields, and the recipient must ignore these fields.

#### 2.2 Managing DTI connections

This section contains the following subsections:

- Channel states

- Handshaking

- Initialization and disconnection on page 2-30

- Connecting multiple TBUs or PCIe RPs to a TCU on page 2-30

#### 2.2.1 Channel states

The four possible states of a DTI channel are:

#### DISCONNECTED

The TBU or PCIe RP might be powered down. A TCU must always be able to accept a Connect Request whenever a TBU or PCIe RP is powered up and able to send one. The method that is used to meet this requirement is outside the scope of this specification.

#### REQ\_CONNECT

The TBU or PCIe RP has issued a Connect Request. The TCU must provide a handshaking response to either establish or reject the connection.

#### **CONNECTED**

The channel is connected.

#### REQ DISCONNECT

The TBU or PCIe RP has issued a Disconnect Request. The TCU issues a Disconnect Accept in response.

#### 2.2.2 Handshaking

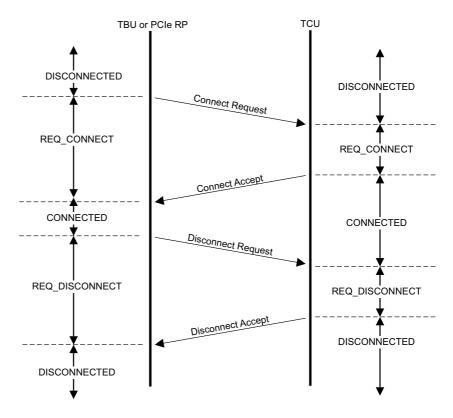

On power up, the channel is initially in the DISCONNECTED state. Figure 2-1 on page 2-29 shows how the channel state changes in response to connect and disconnect messages.

Figure 2-1 Handshake accept

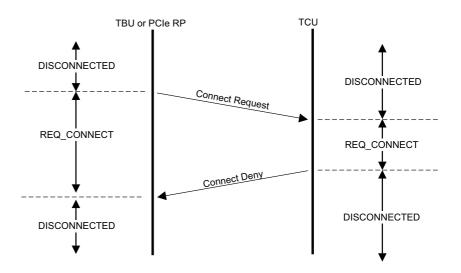

Alternatively, a Connect Request might be denied, as shown in Figure 2-2.

Figure 2-2 Handshake deny

A Connect Deny indicates a system failure, for example, due to a badly configured system. Subsequent attempts to connect are also likely to be denied until there is a system configuration change.

Table 2-6 describes the connection or disconnection messages that are permitted in each channel state.

Table 2-6 Connection or disconnection messages permitted in each channel state

| Channel state  | Downstream permitted messages      | Upstream permitted messages        |  |  |  |  |

|----------------|------------------------------------|------------------------------------|--|--|--|--|

| DISCONNECTED   | Connect Request only               | None                               |  |  |  |  |

| REQ_CONNECT    | None                               | Connect Accept or Connect Deny     |  |  |  |  |

| CONNECTED      | Any, subject to the protocol rules | Any, subject to the protocol rules |  |  |  |  |

| REQ_DISCONNECT | None                               | Any, subject to the protocol rules |  |  |  |  |

#### Channel behavior in the REQ\_DISCONNECT state

When the channel is in the REQ DISCONNECT state:

- Any outstanding invalidation or synchronization responses are not returned. All invalidation requests are

considered to be completed when the TBU or PCIe RP enters DISCONNECTED state and invalidates its

caches.

- Outstanding register access responses, DTI\_TBU\_REG\_RDATA or DTI\_TBU\_REG\_WACK, are not returned.

- Outstanding DTI ATS PAGE RESPACK messages are not returned.

- The TBU or PCIe RP must continue to accept protocol-appropriate requests from the TCU. No response is

given to the requests, and they can be ignored.

#### 2.2.3 Initialization and disconnection

When the TBU enters the DISCONNECTED state, all state information is lost, including cache and register contents. The TBU must invalidate its caches before entering CONNECTED state. The TCU must reinitialize any necessary register contents after the connection handshake.

The DTI channel must not be disconnected while ATS is enabled in any PCIe Endpoint. DTI-ATS has no register messages.

#### 2.2.4 Connecting multiple TBUs or PCle RPs to a TCU

A DTI channel is a point-to-point link between a single TBU or PCIe RP and a single TCU. If a TCU is connected to multiple physical TBUs or PCIe RPs using a single interface, then each has its own DTI channel.

#### Therefore:

- If a TCU is required to send a message to multiple TBUs or PCIe RPs, then it must issue multiple messages.

- Each channel has its own flow control tokens.

- Outstanding message IDs, for example DTI\_TBU\_TRANS\_REQ.TRANSLATION\_ID, are specific to a

channel. Multiple channels can have messages outstanding with the same ID at the same time.

- A DTI channel has a single connection state. It cannot be connected as both DTI-TBU and DTI-ATS at the same time.

## Chapter 3 **DTI-TBU Messages**

This chapter describes the message groups of the DTI-TBU protocol.

It contains the following sections:

- Connection and disconnection message group on page 3-32

- Translation request message group on page 3-37

- Invalidation and synchronization message group on page 3-66

- Register access message group on page 3-81

#### 3.1 Connection and disconnection message group

The DTI-TBU protocol is designed to enable a single TCU to connect to multiple TBUs implementing different versions of the DTI-TBU.

However, it is expected that all TBUs connected to a TCU use the same version of DTI-TBU. This is because the SMMU architecture does not permit TBUs in the same implementation to have different feature sets.

- If using SMMUv3.2, it is required that all TBUs support DTI-TBUv2 or later.

- If using SMMU extensions for RME or RME Device Assignment, it is required that all TBUs support DTI-TBUv3 or later.

This section contains the following subsections:

- DTI TBU CONDIS REQ

- DTI TBU CONDIS ACK on page 3-34

#### 3.1.1 DTI\_TBU\_CONDIS\_REQ

The DTI TBU CONDIS REQ message is used to initiate a connection or disconnection handshake.

#### Description

Connection state change request.

Source

TBU

#### Usage constraints

The TBU can only send a disconnect request when:

- The channel is in the CONNECTED state.

- There are no outstanding translation requests.

- The conditions for completing any future invalidation and synchronization are met. In practice, the result is that all downstream transactions must be complete.

The TBU can only send a connect request when the channel is in the DISCONNECTED state.

#### Flow control result

None

#### Field descriptions

The DTI TBU CONDIS REQ bit assignments are:

| 7                   | 6        | 5        | 4     | 3          |                    | 2 |   | 1  | 0       | LSB |  |

|---------------------|----------|----------|-------|------------|--------------------|---|---|----|---------|-----|--|

| TOK_TRANS_REQ[11:8] |          |          |       |            | STAGES             | 3 | 5 | PD | SUP_REG | 24  |  |

| TOK_INV_GNT         |          |          |       |            | TOK_TRANS_REQ[7:4] |   |   |    |         |     |  |

| TOK_TRANS_REQ[3:0]  |          |          |       |            | VERSION            |   |   |    |         |     |  |

| IMP DEF             | Reserved | PROTOCOL | STATE | M_MSG_TYPE |                    |   |   |    |         | 0   |  |

#### TOK\_TRANS\_REQ[11:8], bits [31:28]

TOK\_TRANS\_REQ[7:0] is bits [19:12].

The meaning of this field depends on the value of the STATE field.

#### STATE = 0

This field indicates the number of translation tokens returned.

The number of translation tokens returned is equal to the value of this field plus one.

This field must be the value of TOK\_TRANS\_GNT that was received in the DTI\_TBU\_CONDIS\_ACK message that acknowledged the connection of the channel.

#### STATE = 1

This field indicates the number of translation tokens requested.

The number of translation tokens requested is equal to the value of this field plus one.

#### **STAGES, bits [27:26]**

This field indicates the security stages. STAGES[1:0] is encoded as follows:

**0b00** M: SMMUv3 defined translation stages only

**0b01** MG: SMMUv3 defined translation stages, plus Granule Protection Checks

(GPC)

0b10 G: GPC only0b11 Reserved

When STATE is 0, this field is ignored.

#### SPD, bit [25]

Same Power Domain (SPD). This extension is micro-architectural to make it easier to integrate power control.

The TBU and TCU are in different power domains.

1 The TBU and TCU are in the same power domain.

When STATE is 0, this field is ignored.

This field is Reserved in versions prior to DTI-TBUv3 and will be ignored by TCUs that do not support DTI-TBUv3 and DTI-TBUv4.

#### SUP REG, bit [24]

This field indicates when register accesses are supported.

Register accesses are not supported.

Register accesses are supported.

When STATE is 1 and the value of this bit is 0, the TCU must not issue DTI\_TBU register access messages on this channel.

When STATE is 0, this field is ignored.

#### TOK\_INV\_GNT, bits [23:20]

This field indicates the number of invalidation tokens granted.

The number of invalidation tokens granted is equal to the value of this field plus one.

This field is ignored when the STATE field has a value of 0.

#### **TOK\_TRANS\_REQ[7:0], bits [19:12]**

See TOK\_TRANS\_REQ[11:8], bits [31:28].

#### VERSION, bits [11:8]

This field identifies the requested protocol version.

| 0b0000 | DTI-TBUv1 |

|--------|-----------|

| 0b0001 | DTI-TBUv2 |

| 0b0010 | DTI-TBUv3 |

| 0b0011 | DTI-TBUv4 |

All other encodings are for future protocol versions and are currently not defined.

This specification describes only DTI-TBUv3 and DTI-TBUv4. For information on DTI-TBUv1 and DTI-TBUv2, see Arm Developer,

https://developer.arm.com/documentation.

A TBU can request any protocol version it supports. A DTI-TBU TCU must process requests for all protocol versions, including those not yet defined.

The DTI TBU CONDIS ACK message indicates the protocol version to use.

#### **IMPLEMENTATION DEFINED, bit [7]**

IMPLEMENTATION DEFINED

Bit [6]

Reserved, SBZ

#### PROTOCOL, bit [5]

This bit identifies the protocol that is used by this TBU.

0 DTI-TBU

This bit must be 0.

#### STATE, bit [4]

This bit identifies the new channel state requested.

Disconnect request

1 Connect request

A Disconnect request can only be issued when the channel is in the CONNECTED state.

A Connect request can only be issued when the channel is in the DISCONNECTED state.

#### M\_MSG\_TYPE, bits [3:0]

This field identifies the message type. The value of this field is taken from the list of encodings for downstream messages, see *DTI-TBU protocol downstream messages* on page 2-25.

0b0000 DTI TBU CONDIS REQ

#### 3.1.2 DTI\_TBU\_CONDIS\_ACK

The DTI\_TBU\_CONDIS\_ACK message is used to accept or deny a request as part of the connection or disconnection handshake process.

#### Description

A connection state change acknowledgment.

Source

TCU

#### Usage constraints

The TBU must have previously issued an unacknowledged DTI TBU CONDIS REQ message.

#### Flow control result

None

#### Field descriptions

The DTI TBU CONDIS ACK bit assignments are:

| 7                   | 6       |        | 5  |         | 4     |                    | 3 |  | 2 |  | 1 |   | 0      | LSB |

|---------------------|---------|--------|----|---------|-------|--------------------|---|--|---|--|---|---|--------|-----|

| TOK_TRANS_GNT[11:8] |         |        |    |         |       | Reserved OAS[3]    |   |  |   |  |   |   | OAS[3] | 24  |

|                     | OAS[2:0 | 0]     |    | Rese    | erved | TOK_TRANS_GNT[7:4] |   |  |   |  |   |   | 16     |     |

| TOK_TRANS_GNT[3:0]  |         |        |    | VERSION |       |                    |   |  |   |  |   | 8 |        |     |

| IMP DEF             | Re      | eserve | ed | STA     | ATE   | S_MSG_TYPE         |   |  |   |  |   | 0 |        |     |

#### TOK TRANS GNT[11:8], bits [31:28]

TOK TRANS GNT[7:0] is bits [19:12].

This field indicates the number of preallocated tokens for translation requests that have been granted. The number of translation tokens granted is equal to the value of this field plus one.

When the value of STATE is 1, the value of this field must equal the value of the

TOK\_TRANS\_REQ field in the DTI\_TBU\_CONDIS\_REQ message that initiated the connection.

When the value of STATE is 0, this field is ignored.

#### Bits [27:25]

Reserved, SBZ

#### OAS, bits [24:21]

This indicates the output address size, which is the maximum address size permitted for translated addresses.

0b0000

32 bits (4GB)

0b0001

36 bits (64GB)

0b0010

40 bits (1TB)

0b0011

42 bits (4TB)

0b0100

44 bits (16TB)

0b0101

48 bits (256TB)

0b0110

52 bits (4PB)

All other values are Reserved.

The TBU must ensure that the output address does not exceed the OAS.

#### Bit [20]

Reserved, SBZ

#### TOK TRANS GNT[7:0], bits [19:12]

See TOK\_TRANS\_GNT[11:8], bits [31:28].

#### VERSION, bits [11:8]

The protocol version that is granted by the TCU.

0b0000

DTI-TBUv1

0b0001

DTI-TBUv2

0b0010

DTI-TBUv3

0b0011

DTI-TBUv4

All other encodings are Reserved.

The value of this field must not be greater than the value of the VERSION field in the DTI\_TBU\_CONDIS\_REQ Connect Request message.

—— Note ———

This specification describes only DTI-TBUv3 and DTI-TBUv4. For information on DTI-TBUv1 and DTI-TBUv2, see Arm Developer,

https://developer.arm.com/documentation.

#### **IMPLEMENTATION DEFINED, bit [7]**

IMPLEMENTATION DEFINED

#### Bits [6:5]

Reserved, SBZ

#### STATE, bit [4]

Identifies the new state. The possible values of this bit are:

0 DISCONNECTED1 CONNECTED

When the value of STATE in the unacknowledged DTI\_TBU\_CONDIS\_REQ message is 0, the value of this bit must be 0.

When the value of STATE in the unacknowledged DTI\_TBU\_CONDIS\_REQ message is 1, this field can be 0 or 1 where value 0 denies the connection and value 1 accepts the connection.

For example, it can be 0 if there are no translation tokens available. This normally indicates a serious system configuration failure.

#### S\_MSG\_TYPE, bits [3:0]

Identifies the message type. The value of this field is taken from the list of encodings for upstream messages, see *DTI-TBU protocol upstream messages* on page 2-25.

0b0000 DTI\_TBU\_CONDIS\_ACK

# 3.2 Translation request message group

The DTI-TBU translation request messages enable the TBU to find the translation for a given transaction, or prefetch a translation. The TCU responds with either a successful translation or a fault.

\_\_\_\_\_Note \_\_\_\_\_

Unless the description indicates otherwise, behavior and reference to DTI\_TBU\_TRANS\_RESP and DTI\_TBU\_TRANS\_RESPEX messages are equivalent.

This section contains the following subsections:

- DTI TBU TRANS REQ

- DTI\_TBU\_TRANS\_RESP on page 3-41

- DTI\_TBU\_TRANS\_RESPEX on page 3-55

- DTI TBU TRANS FAULT on page 3-57

- Additional rules on permitted translation responses on page 3-59

- Calculating transaction attributes on page 3-60

- Speculative transactions and translations on page 3-64

- Cache lookup process on page 3-65

# 3.2.1 DTI\_TBU\_TRANS\_REQ

The DTI TBU TRANS REQ message is used to initiate a translation request.

Description

A translation request.

Source

TBU

Usage constraints

The TBU must have at least one translation token.

Flow control result

The TBU consumes a translation token.

#### Field descriptions

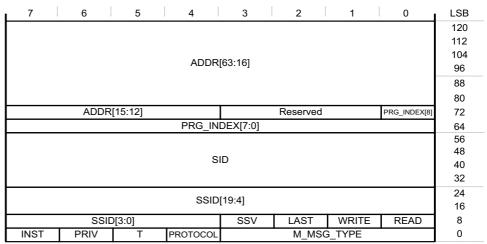

The DTI TBU TRANS REQ bit assignments are:

| 7 6                  | 5 4            | 3       | 2          | 1    | 0        | LSB |

|----------------------|----------------|---------|------------|------|----------|-----|

|                      |                |         |            |      |          | 152 |

|                      |                |         |            |      |          | 144 |

|                      |                |         |            |      |          | 136 |

|                      | I/             | Δ       |            |      |          | 128 |

|                      | "              | •       |            |      |          | 120 |

|                      |                |         |            |      |          | 112 |

|                      |                |         |            |      |          | 104 |

|                      |                |         |            |      |          | 96  |

| SSID[19:4]           |                |         |            |      | 88       |     |

|                      |                |         |            |      | 80       |     |

| SSID[3:0] IMP DEF    |                |         |            |      | 72       |     |

| FLOW[1] Reserved     | MMUV REQEX     |         | Reser      | ved  |          | 64  |

|                      |                |         |            |      |          | 56  |

|                      | SI             | חו      |            |      |          | 48  |

|                      | OI             | ID.     |            |      |          | 40  |

|                      |                |         |            |      |          | 32  |

| TRANSLATIO           | N_ID[11:8]     | IDENT   | SEC_SID[1] | NSE  | NS       | 24  |

| PERM[1] FLOW[0]      | SSV SEC_SID[0] | PERM[0] | InD        | PnU  | PROTOCOL | 16  |

| TRANSLATION_ID[7: 0] |                |         |            |      |          | 8   |

| QO                   | S              |         | M_MSG      | TYPE |          | 0   |

#### IA, bits [159:96]

This field holds the input address, IA[63:0], to be used in the translation.

# SSID, bits [95:76]

This field indicates the SubstreamID value that is used for the translation.

When the value of SSV is 0, this field is Reserved, SBZ.

When MMUV is 0, SSID is Reserved, SBZ.

# **IMPLEMENTATION DEFINED, bit [75:72]**

IMPLEMENTATION DEFINED

## FLOW[1], bit [71]

FLOW[0] is bit [22]. This field indicates the translation flow required.

### 0b00 Stall

If enabled, the SMMU stall fault flow can be used for this request.

A translation request can only be stalled by the TCU if FLOW = Stall.

Selecting FLOW = Stall does not cause a stall to occur. A stall only occurs if software enables stall faulting for the translation context.

# 0b01 ATST

The transaction has been translated by ATS.

When FLOW = ATST, it indicates that this transaction was the result of a previous ATS translation request made using DTI-ATS.

# 0b10 NoStall

If a translation fault occurs, then even if the SMMU has enabled stall faulting for this translation context, a fault response is returned without dependence on software activity.

# 0b11 PRI

If a translation fault occurs, a fault response is returned indicating that a PRI request might resolve the fault. Architecturally, the request is treated as an ATS request and translation faults do not result in an event record. This option is for use by PCIe enumerated endpoints.

PRI requests must be sent using a DTI-ATS connection. There is no mechanism to issue a PRI request from a DTI-TBU connection.

| —— Note ——— |

|-------------|

|-------------|

If FLOW = PRI and PERM = SPEC, then translation faults are reported as NonAbort. For more information, see FAULT TYPE field in DTI TBU TRANS FAULT on page 3-57.

When MMUV is 0, FLOW is Reserved, SBZ.

#### Bit [70]

Reserved, SBZ

#### MMUV, bit [69]

When MMUV is 0, no SMMU stage 1 or 2 checking is performed, only the Realm Management Extension (RME) Granule Protection Check is performed. When DTI TBU CONDIS REQ.STAGES is G, MMUV must be 0.

When DTI TBU CONDIS REQ.STAGES is M, MMUV must be 1.

- Note -

When MMUV = 0, a translation can be requested where REQ.IA exceeds DTI TBU CONDIS ACK.OAS. The TCU must return a fault in this case, similar to the behavior with BYPASS responses.

Rules dependent on the value of fields that are Reserved when MMUV = 0, are valid only when MMUV = 1.

### REQEX, bit [68]

This field controls whether the TCU can return a DTI TBU TRANS RESPEX

When REQEX = 0, the translation response cannot be DTI TBU TRANS RESPEX. When REQEX = 1, the translation response can be DTI TBU TRANS RESPEX.

The response is never required by DTI to be DTI TBU TRANS RESPEX. It can always be DTI TBU TRANS RESP or DTI TBU TRANS FAULT.

# Bits [67:64]

Reserved, SBZ

# SID, bits [63:32]

This field indicates the StreamID value that is used for the translation.

When MMUV is 0. SID is Reserved, SBZ.

### **TRANSLATION ID[11:8], bits [31:28]**

TRANSLATION ID[7:0] is bits [15:8].

This field gives the identification number of this translation.

The value of this field must not be in use by any translation request that has not yet received a DTI TBU TRANS RESP or DTI TBU TRANS FAULT with FAULT TYPE != TranslationStall response.

Any 12-bit translation ID can be used, if the maximum number of outstanding translation requests is not exceeded.

#### IDENT, bit [27]

This field indicates whether an identity translation is required.

When IDENT is 1, DTI TBU TRANS RESP.OA must always be equal to IA.

The encodings of IDENT are as follows:

Identity translation is not required.

Identity translation is required.

When IDENT is 1, FLOW must be ATST.

When MMUV is 0, IDENT is Reserved, SBZ.

## SEC\_SID[1], bit [26]

This field indicates the Security states of StreamID. The encodings of SEC\_SID[1:0] are as follows:

0b00 Non-secure0b01 Secure0b10 Realm0b11 Reserved

When DTI\_TBU\_CONDIS\_REQ.STAGES is M, SEC\_SID must be Non-secure or Secure.

When MMUV is 0, SEC\_SID is Reserved, SBZ.

If FLOW = ATST, SEC SID must be Non-secure or Realm.

### NSE, bit [25]

{NSE, NS} indicates the physical address space of the untranslated transaction. For more information, see NS, bit [24].

#### NS, bit [24]

{NSE, NS} indicates the physical address space of the untranslated transaction. The encodings of {NSE, NS} are as follows:

0b00 Secure

0b01 Non-secure

0b10 Root

0b11 Realm

When MMUV is 1 and SEC\_SID is Non-secure, {NSE,NS} must be Non-secure. When MMUV is 1 and SEC\_SID is Secure, {NSE,NS} must be Non-secure or Secure. When MMUV is 1 and SEC\_SID is Realm, {NSE,NS} must be Non-secure or Realm.

### PERM[1], bit [23]

PERM[1] and PERM[0] indicate permissions a translation request requires to avoid causing a permission fault.

The encoding of PERM[1:0] is:

0b00 W: Write permission required.0b01 R: Read permission required.

**0b11** SPEC: Neither permission required. The translation request is speculative and cannot cause a permission fault.

**0b10** RW: Read and write permission required.

#### FLOW[0], bit [22]

See FLOW[1], bit [71].

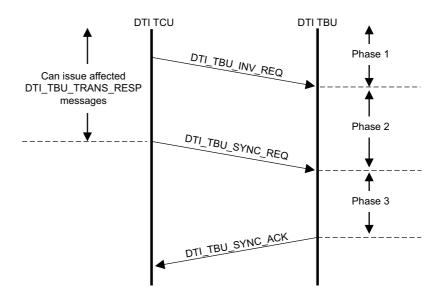

#### SSV, bit [21]