# arm

# SME Programmer's Guide

Version 1.0

Non-Confidential

Copyright  $\ensuremath{\mathbb{C}}$  2024 Arm Limited (or its affiliates). All rights reserved.

**Issue 01** 109246\_0100\_01\_en

# SME Programmer's Guide

Copyright © 2024 Arm Limited (or its affiliates). All rights reserved.

## **Release information**

#### Document history

| Issue   | Date        | Confidentiality  | Change        |

|---------|-------------|------------------|---------------|

| 0100-01 | 23 May 2024 | Non-Confidential | First release |

### **Proprietary Notice**

This document is protected by copyright and other related rights and the use or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm Limited ("Arm"). No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether the subject matter of this document infringes any third party patents.

The content of this document is informational only. Any solutions presented herein are subject to changing conditions, information, scope, and data. This document was produced using reasonable efforts based on information available as of the date of issue of this document. The scope of information in this document may exceed that which Arm is required to provide, and such additional information is merely intended to further assist the recipient and does not represent Arm's view of the scope of its obligations. You acknowledge and agree that you possess the necessary expertise in system security and functional safety and that you shall be solely responsible for compliance with all legal, regulatory, safety and security related requirements concerning your products, notwithstanding any information or support that may be provided by Arm herein. conjunction with any Arm technology described in this document, and to minimize risks, adequate design and operating safeguards should be provided for by you.

This document may include technical inaccuracies or typographical errors. THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, any patents, copyrights, trade secrets, trademarks, or other rights. TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Reference by Arm to any third party's products or services within this document is not an express or implied approval or endorsement of the use thereof.

This document consists solely of commercial items. You shall be responsible for ensuring that any permitted use, duplication, or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of this document shall prevail.

The validity, construction and performance of this notice shall be governed by English Law.

The Arm corporate logo and words marked with ® or <sup>™</sup> are registered trademarks or trademarks of Arm Limited (or its affiliates) in the US and/or elsewhere. Please follow Arm's trademark usage guidelines at https://www.arm.com/company/policies/trademarks. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

PRE-1121-V1.0

### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

### **Product Status**

The information in this document is Final, that is for a developed product.

## Feedback

Arm welcomes feedback on this product and its documentation. To provide feedback on the product, create a ticket on https://support.developer.arm.com

To provide feedback on the document, fill the following survey: https://developer.arm.com/ documentation-feedback-survey.

## Inclusive language commitment

Arm values inclusive communities. Arm recognizes that we and our industry have used language that can be offensive. Arm strives to lead the industry and create change.

We believe that this document contains no offensive language. To report offensive language in this document, email terms@arm.com.

# Contents

| 1. Introduction                                                       | 8  |

|-----------------------------------------------------------------------|----|

| 1.1 The Scalable Matrix Extensions                                    | 8  |

| 1.1.1 Streaming SVE mode and ZA storage                               | 9  |

| 2. SME Overview                                                       | 12 |

| 2.1 SME and SME2                                                      | 12 |

| 2.1.1 If SME and SME2 are supported                                   | 13 |

| 2.1.2 SME2 lookup table                                               | 13 |

| 2.1.3 SME2 multi-vector predication                                   | 15 |

| 2.2 Streaming SVE mode                                                | 15 |

| 2.3 SME ZA storage                                                    | 16 |

| 2.3.1 ZA array vector access and ZA tile mapping                      |    |

| 2.4 SME2 multi-vector operands                                        |    |

| 2.4.1 Z multi-vector operands                                         | 31 |

| 2.4.2 ZA multi-slice operands                                         | 31 |

| 2.4.3 ZA multi-vector operands                                        |    |

| 2.5 SME context save restore                                          |    |

| 2.5.1 Context save restore on entry or exit from Streaming SVE mode   |    |

| 2.5.2 Context save restore in supervisory software                    |    |

| 3. Toolchains and model support                                       |    |

| 3.1 Quick start example for SME/SME2                                  |    |

| 3.1.1 Step 1: Create a new project with SME/SME2 instruction          |    |

| 3.1.2 Step 2: Build the project                                       | 41 |

| 3.1.3 Step 3: Connect a Debugger and configure                        | 42 |

| 3.2 Compiler support                                                  | 42 |

| 3.2.1 Compiler options and pragmas                                    | 43 |

| 3.3 Calling conventions                                               |    |

| 3.3.1 Preparation for entering and exiting streaming mode             | 46 |

| 3.3.2 Controlling the use of streaming mode                           | 47 |

| 3.3.3 Controlling the use of ZA storage                               |    |

| 3.4 How to run an SME application                                     |    |

| 3.5 Debug tools                                                       |    |

| Convright © 2024 Arm Limited (or its affiliates). All rights reserved |    |

| 4. SME2 code examples                                                                                                                               |         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 5. matmul_fp32: Single precision matrix-by-matrix multiplication                                                                                    |         |

| 5.1 Overview of the matmul_fp32 algorithm                                                                                                           |         |

| 5.2 preprocess_I code                                                                                                                               |         |

| 5.3 preprocess_I function overview                                                                                                                  | 60      |

| 5.4 preprocess_l function details                                                                                                                   |         |

| 5.5 matmul_opt code                                                                                                                                 | 65      |

| 5.6 matmul_opt function overview                                                                                                                    | 67      |

| 5.7 matmul_opt function details                                                                                                                     | 68      |

| 4 material into 9 bit integer to 22 bit integer matrix by matrix multiplication                                                                     | 70      |

| <ul><li>6. matmul_int8: 8-bit integer to 32-bit integer matrix-by-matrix multiplication</li><li>6.1 Overview of the matmul_int8 algorithm</li></ul> |         |

| 6.2 preprocess_r code                                                                                                                               |         |

| 6.3 preprocess_r function overview                                                                                                                  |         |

| 6.4 preprocess_r function details                                                                                                                   |         |

| 6.5 preprocess_I code                                                                                                                               |         |

| 6.6 preprocess_I code                                                                                                                               |         |

| 6.7 preprocess_I function details                                                                                                                   |         |

| 6.8 matmul opt code                                                                                                                                 |         |

| 6.9 matmul opt function overview                                                                                                                    |         |

|                                                                                                                                                     |         |

| 7. gemv_cm_int8: 8-bit integer to 32-bit integer matrix-by-vector multiplication                                                                    | 85      |

| 7.1 Overview of the gemv_cm_int8 algorithm                                                                                                          |         |

| 7.2 gemv_opt code                                                                                                                                   | 86      |

| 7.3 gemv_opt function overview                                                                                                                      |         |

| 7.4 gemv_opt function details                                                                                                                       | 92      |

| 8. lut_gemv_rm_int8: Compressed 8-bit integer to 32-bit integer matrix-by                                                                           | -vector |

| multiplication                                                                                                                                      |         |

| 8.1 Overview of the lut_gemv_rm_int8 algorithm                                                                                                      | 95      |

| 8.2 lut_gemv_opt code                                                                                                                               | 96      |

| 8.3 lut_gemv_opt function overview                                                                                                                  | 99      |

| 8.4 lut_gemv_opt function details                                                                                                                   | 100     |

| 9. cplx_matmul_fp16fp32: Complex-valued half-precision to single precision floating-point                                                           | matrix- |

| by-matrix multiplication                                                                                                                            |         |

| 9.1 Overview of the cplx_matmul_fp16fp32 algorithm                                                                                                  | 102     |

| 10. Related information               |  |

|---------------------------------------|--|

|                                       |  |

| 9.7 cplx matmul opt function details  |  |

| 9.6 cplx_matmul_opt function overview |  |

| 9.5 cplx_matmul_opt code              |  |

| 9.4 preprocess_I function details     |  |

| 9.3 preprocess_I function overview    |  |

|                                       |  |

| 9.2 preprocess_I code                 |  |

# 1. Introduction

As the technology is evolving faster than ever before in the digital world, so is the demand for accelerated computing. The Arm architecture is evolving continuously to cope with the ever-rising demand for computing complex data, making it the perfect choice for emerging digital technology. This guide describes the Scalable Matrix Extensions, SME and SME2. This extension is introduced into Armv9-A to improve the efficiency and performance of matrix operations.

The Armv7-A Advanced SIMD Extension enabled parallel data-processing on multiple lanes within the fixed length 64-bit and 128-bit vector registers. With SIMD, the explicit data parallelization technique helped improve performance in applications involving large amounts of data processing. Industry applications involving large amounts of data processing demanded a larger vector length. Arm adopted a novel approach and created a unique instruction set that scaled to different vector lengths called the Scalable Vector Extension (SVE). SVE is an architectural extension to Armv8-A. SVE enabled implementation defined vector register length which must be a power of two, from 128 bits to 2048 bits.

The vector length agnostic (VLA) coding style of the SVE architecture enables binaries, built for SVE, to be portable across systems with different vector lengths. The programs built for the SVE architecture can be executed on any Arm-based systems with SVE and are able to use the full vector length across different platforms with different vector lengths without the need to recompile the source code. The SVE architecture significantly enhanced the computing performance for 'High Performance Computing', making Arm the perfect choice for HPC designs.

The SVE2 architecture (a superset of SVE), introduced as part of Armv9-A, further extended the SVE ISA to support DSP/Media processing which expands its scope from supercomputers to personal devices.

The vectorization techniques introduced in SVE and SVE2 improved the performance of complex data computation workloads significantly. However, efficient matrix computation commonly used in Artificial Intelligence (AI) and Computer Vision remained a challenge. The architectural challenge for matrices computation is to enable efficient data parallelism with minimal memory bandwidth to achieve the best balance of compute ability and memory bandwidth. The Scalable Matrix Extension (SME) introduced in this guide is an architectural solution by Arm to accelerate matrix operations.

# 1.1 The Scalable Matrix Extensions

The Scalable Matrix Extensions (SME and SME2) define:

- Streaming SVE mode

- ZA storage

# **1.1.1** Streaming SVE mode and ZA storage

The features of Streaming SVE mode and ZA storage are as follows:

- When the Processing Element (PE) is in Streaming SVE mode, the Streaming SVE register state is defined. The Streaming SVE register state consists of:

- Streaming vector registers ZO-Z31

- Streaming predicate registers PO-P15

- Streaming SVE mode supports execution of a subset of SVE2 instructions with SME defined vector length known as Streaming SVE Vector Length (SVL). When the PE is in Streaming SVE mode, the effective SVE Vector Length (VL) is equal to a power of two in the range 128-2048 bits inclusive.

In a vector of SVL bits:

- $\circ$  SVL<sub>B</sub> is the number of 8-bit elements

- $\circ~~SVL_{H}$  is the number of 16-bit elements

- $SVL_S$  is the number of 32-bit elements

- SVL<sub>D</sub> is the number of 64-bit elements

- SVL<sub>O</sub> is the number of 128-bit elements

- The ZA storage is an architectural register state consisting of a two-dimensional ZA array of [SVL<sub>B</sub> x SVL<sub>B</sub>] bytes

- The ZA array can be accessed as vectors of SVL bits represented by ZA[N], where N is in the range 0 to SVL\_B-1 inclusive

- An elementwise vector access to the ZA array is shown in this document by appending an element size qualifier and a vector index "[N]" to the ZA array name where N is in the range 0 to SVL<sub>B</sub>-1 inclusive, as follows:

- ZA.B[N] represents an 8-bit element vector access to the ZA array

- ZA.H[N] represents an 16-bit element vector access to the ZA array

- ZA.S[N] represents an 32-bit element vector access to the ZA array

- ZA.D[N] represents an 64-bit element vector access to the ZA array

- ZA.Q[N] represents an 128-bit element vector access to the ZA array

A sub-array of elements within the ZA array can be accessed as a tile. A ZA tile is a square, two-dimensional sub-array of elements within the ZA array. As the architecture defines ZA tile as a square, the ZA array is treated as containing one or more ZA tiles depending on the element size with which the ZA array is accessed. A ZA tile is represented by appending the tile number to the ZA name followed by an element qualifier.

Also, a one-dimensional set of horizontally or vertically contiguous elements within a ZA tile can be accessed as a ZA tile slice. An access to horizontal tile slices is indicated by an "H" suffix on the ZA tile name. An access to vertical tile slices is indicated by a "V" suffix on the ZA tile name.

#### Accessing an 8-bit element ZA tile

There is a single tile ZA0.B which consists of  $[SVL_B \times SVL_B]$  8-bit elements and occupies all of the ZA storage.

#### Accessing a 16-bit element ZA tile

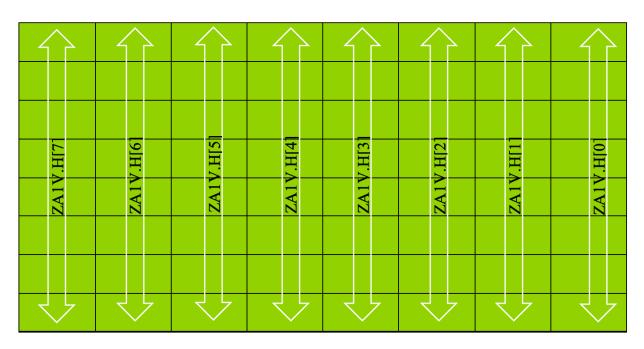

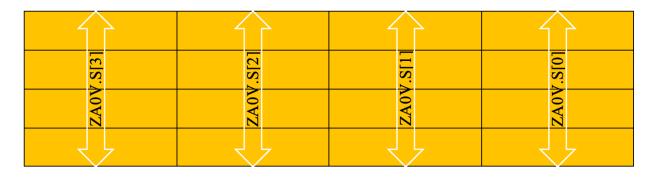

There are two tiles, ZAO.H and ZA1.H. Each tile consists of  $[SVL_H \times SVL_H]$  16-bit elements and occupies half of the ZA storage.

#### Accessing a 32-bit element ZA tile

There are four tiles, ZA0.S, ZA1.S, ZA2.S, and ZA3.S . Each tile consists of  $[SVL_S\times SVL_S]$  32-bit elements and occupies a quarter of the ZA storage.

#### Accessing a 64-bit element ZA tile

There are eight tiles, ZA0.D, ZA1.D, ZA2.D, ZA3.D, ZA4.D, ZA5.D, ZA6.D, and ZA7.D. Each tile consists of  $[SVL_D \times SVL_D]$  64-bit elements and occupies an eighth of ZA storage.

#### Accessing a 128-bit element ZA tile

There are sixteen tiles, ZA0.Q, ZA1.Q, ZA2.Q, ZA3.Q, ZA4.Q, ZA5.Q, ZA6.Q, ZA7.Q, ZA8.Q, ZA9.Q, ZA10.Q, ZA11.Q, ZA12.Q, ZA13.Q, ZA14.Q, and ZA15.Q. Each tile consists of  $[SVL_Q \times SVL_Q]$  128-bit elements and occupies a sixteenth of ZA storage.

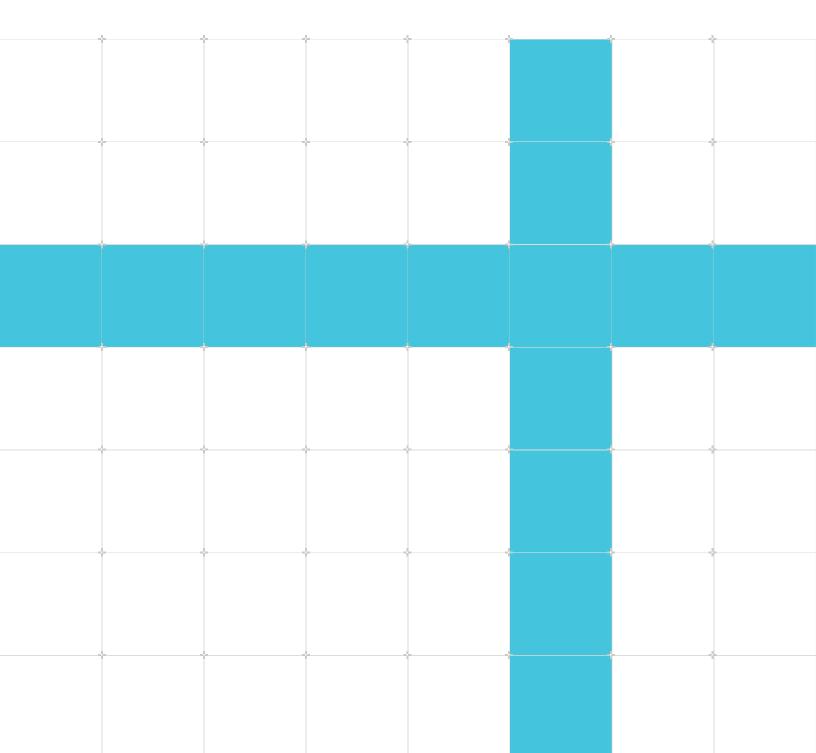

Figure 1-1 shows tile ZAO.B when SVL is 256 bits consisting of  $SVL_B \times SVL_B$ 8-bit elements.

In Figure 1-1:

- ZAOH.B[0], ZAOH.B[15], ZAOH.B[31] indicates horizontal tile slice selection of 8-bit element ZA tile

- ZAOV.B[0], ZAOV.B[15], ZAOV.B[31] indicates vertical 8-bit element ZA tile slice selection

#### Figure 1-1: 8-bit element ZA tile, SVL = 256 bits

# 2. SME Overview

This chapter gives an overview of SME and SME2.

# 2.1 SME and SME2

The Scalable Matrix Extension (SME) is an extension to Armv9-A architecture. It adds a new architecture state: ZA storage. It introduces a new execution mode: Streaming SVE mode in which the new SME instructions and a subset of SVE2 instructions can be executed. The SME instructions operating on ZA include:

- Outer product computation with results in ZA tile

- Insert/extract ZA tile slice from/to Z vector register

- Load and store of ZA tile slice

The above SME instructions enable matrix operations, such as multiplication, inversion, and onthe-fly transposition. These instructions are useful in digital filtering, linear equation solvers, and convolutions. SME further extends a PE's Process state or PSTATE with the SM and ZA fields. For more details refer sections Streaming SVE mode and SME ZA storage.

The Scalable Matrix Extension version 2 (SME2) extends the SME architecture by accelerating vector operations to increase the number of applications that can benefit from the computational efficiency of SME, beyond its initial focus on outer products and matrix-matrix multiplication.

SME2 extends SME by introducing multi-vector data-processing instructions, load to and store from multi-vectors, and a multi-vector predication mechanism.

Additional architectural features of SME2 include:

- Multi-vector multiply-accumulate instructions, with Z vectors as multiplier and multiplicand inputs and accumulating results into ZA array vectors, including widening multiplies that accumulate into more vectors than they read

- Multi-vector load, store, move, permute, and convert instructions, that use multiple SVE Z vectors as source and destination registers to pre-process inputs and post-process outputs of the ZA-targeting SME2 instructions

- "Predicate-as-counter", an alternative predication mechanism is added to the original SVE predication mechanism, to control operations performed on multiple vector registers

- Compressed neural network capability using dedicated lookup table instructions and outer product instructions that support binary neural networks

SME2 adds a 512-bit architectural register ZTO, that supports the lookup table feature.

# 2.1.1 If SME and SME2 are supported

Implementation of SME is represented by the feature FEAT\_SME which is an optional extension from Armv9.2-A. The ID\_AA64PFR1\_EL1.SME system register field contains the value 1 or higher to indicate the presence of FEAT\_SME.

Implementation of SME2 is represented by the feature FEAT\_SME2 which is an optional extension from Armv9.2-A. The following fields show the presence of FEAT\_SME2:

- ID\_AA64PFR1\_EL1.SME contains the value 2 or higher, and

- ID\_AA64SMFR0\_EL1.SMEver contains the 1 or higher

FEAT\_SME2 requires FEAT\_SME.

System registers (ID\_AA64PFR1\_EL1 and ID\_AA64SMFR0\_EL1) might not be directly accessible by an application program. The operating system might provide this information to an application via an alternative means, such as the Linux hwcap mechanism.

# 2.1.2 SME2 lookup table

The 512-bit architectural register ZTO, supports the lookup table feature. The ZTO contains a 16entry lookup table. Each entry is 32 bits wide and can hold an element that can be 8 bits, 16 bits, or 32 bits. The ZTO register can be loaded from memory and stored to memory.

#### Loading the ZTO register

LDR (table), Load ZTO register from the memory address provided in the 64-bit scalar base register. For example: - LDR ZTO, [X0].

#### Storing the ZTO register

STR (table), Store ZTO register to the memory address provided in the 64-bit scalar base register. For example: - str zto, [x0].

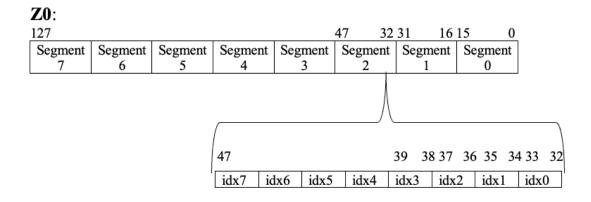

#### Lookup in the ZTO register

LUTI2 and LUTI4, Lookup table read instructions, copy 8-bit, 16-bit or 32-bit elements from ZTO to one or more of the destination vector registers using packed indices from a segment of the source vector register. The indices can be 2 bits (LUTI2) or 4-bits (LUTI4). When using 2-bit indices, only the first four entries of the ZTO table are accessible. When using 4-bit indices, all sixteen entries of the ZTO table are accessible.

#### Lookup table example

The following instruction decompresses a sequence of 2-bit index values from the second segment of the ZO register by extracting the indexed 16-bit entries from ZTO and placing the 16-bit results into the Z5 vector:

- `LUTI2 Z5.H, ZTO, ZO[2]`

Because the index is 2 bits, only the first four entries of the lookup table can be accessed by this instruction. The element size in this instruction is 16 bits. The number of segments is determined by the element size divided by product of index size and number of registers to be loaded. For this example the number of segments is 8 and the segment size is 16 bits for an example 128-bit SVL. Eight 2-bit indices are used from the second segment of the ZO register (as indicated in the instruction using ZO[2]) to index the first four table entries in ZTO register. The indexed 16-bit table entries are copied to Z5 register as Figure 2-1 shows.

#### Figure 2-1: Example LUTI2 instrcution operation

#### ZT0: Sixteen 32-bit table entries, first four entries accessible

|   |       | <br>011 10010 | ••••••, |         | • • • • • • • |         | -       |         |

|---|-------|---------------|---------|---------|---------------|---------|---------|---------|

|   | Entry | <br>Entry 6   | Entry 5 | Entry 4 | Entry 3       | Entry 2 | Entry 1 | Entry 0 |

| L | 15    |               |         |         |               |         |         |         |

| 75 |   |

|----|---|

| 10 | • |

|    | ٠ |

| <b>L</b> J. |            |            |            |            |            |            |             |

|-------------|------------|------------|------------|------------|------------|------------|-------------|

| 127         |            |            |            |            | 47 32      | 31 16      | 15 0        |

| ZT0[idx7]   | ZT0[idx6]  | ZT0[idx5]  | ZT0[idx4]  | ZT0[idx3]  | ZT0[idx2]  | ZT0[idx1]  | ZT0[idx0]   |

| bits[15:0]  | bits[15:0] | bits[15:0] | bits[15:0] | bits[15:0] | bits[15:0] | bits[15:0] | bits [15:0] |

|             |            |            |            |            |            |            | "Lower      |

|             |            |            |            |            |            |            | 16-bits of  |

|             |            |            |            |            |            |            | one of      |

|             |            |            |            |            |            |            | first four  |

|             |            |            |            |            |            |            | entries of  |

|             |            |            |            |            |            |            | ZT0         |

|             |            |            |            |            |            |            | selected    |

|             |            |            |            |            |            |            | by idx0"    |

# 2.1.3 SME2 multi-vector predication

The SME2 architecture introduces multi-vector instructions that operate on groups of Z vector registers and ZA array vectors. The multi-vector load and store instructions use an alternative predication mechanism to the original SVE predication mechanism, to control operations performed on a group of Z vector registers. The multi-vector predication concept is referred to as predicate-as-counter.

Unlike predication in SVE, which is a bitmask based, predicate-as-counter uses an encoded element count in the predicate register. The encoded value indicates the number of consecutive elements starting from element 0 that are Active, with the remaining elements Inactive, or vice versa.

# 2.2 Streaming SVE mode

An implementation of SME supports Streaming SVE mode. The Streaming SVE mode is a dedicated mode for SME operations that can be enabled or disabled by software by programming the PSTATE.SM field.

When the PE is in Streaming SVE mode:

- The streaming vector registers ZO-Z31, streaming predicate registers PO-P15 and SME architecture state are accessible by SME instructions and a subset of SVE2 instructions executable in Streaming SVE mode.

- The effective vector length changes to streaming vector length. The SMCR\_EL1, Streaming SVE Mode Control Register for EL1 configures the Effective Streaming SVE vector length when the PE is in Streaming SVE mode and executing at EL1 or EL0. For EL2 and EL3, corresponding SMCR register configures the Effective Streaming SVE vector length.

SVL is independent of SVE Vector length (referred to as VL which is the vector length when not in Streaming SVE mode). The Effective Streaming SVE vector length, SVL, is a power of two in the range 128-2048 bits inclusive. SVL can vary between implementations. When streaming SVE mode is disabled, the ZCR\_ELx register determines the effective SVE vector length (VL).

Streaming SVE mode is enabled when PSTATE.SM=1. When PSTATE.SM is changed from 0 to 1, Streaming SVE mode is entered and SVE registers Z0-Z31 and P0-P15 in the new mode are set to 0.

You cannot directly program the PSTATE.SM field. The PSTATE.SM field can be programmed by using the SVCR register. You can use the following instruction to independently set or clear PSTATE.SM field:

• MSR SVCRSM, #<imm1>

Also, you can use SMSTART SM instruction, alias of the MSR SVCRSM, #1 and SMSTOP SM instruction, alias of the MSR SVCRSM, #0.

You can use the MRS instruction to read the SVCR register.

When the PSTATE.SM is changed from 1 to 0, an exit from Streaming SVE mode is performed, and each implemented bit of the SVE registers Z0-Z31 and P0-P15 in the new mode will set to zero.

SMSTART SM enters Streaming SVE mode, but does not enable the SME ZA storage.

# 2.3 SME ZA storage

Streaming SVE mode permits access to the ZA array when ZA storage is enabled. When ZA storage is enabled, the ZA-targeting instructions are available.

You can enable or disable the SME ZA storage in software by programming the PSTATE.ZA field. The SME ZA storage is enabled when PSTATE.ZA is 1. When ZA storage is enabled:

- The content of ZA storage is valid and is retained by hardware irrespective of whether the PE is in Streaming SVE mode.

- If SME2 is implemented ZTO register is enabled.

You cannot directly program the PSTATE.ZA field. The PSTATE.ZA field can be programmed using the SVCR register. You can use the following instruction to independently set or clear PSTATE.ZA field: - MSR SVCRZA, #<imm1>

Also, you can use the smstart za instruction, an alias of the msr svcrza, #1 and smstop za instruction, an alias of the msr svcrza, #0.

You can use the MRS instruction to read the SVCR register.

You can use the SMSTART instruction to enable both Streaming SVE mode, and SME ZA array storage. You can use the SMSTOP instruction to disable Streaming SVE mode, and SME ZA array storage.

SMSTART ZA enables the SME ZA array storage, but does not cause an entry to Streaming SVE mode.

### 2.3.1 ZA array vector access and ZA tile mapping

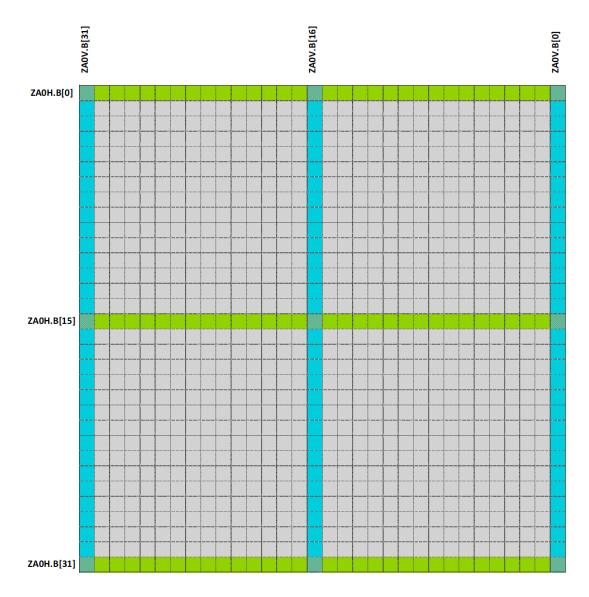

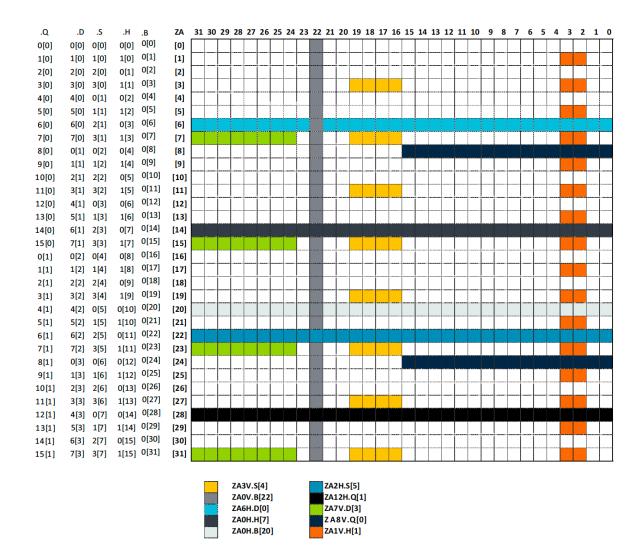

This section describes the ZA Storage, ZA array vector access, and ZA tile mappings for 8-bit, 16bit, and 32-bit data types in an example 128-bit SVL implementation.

## 2.3.1.1 ZA storage access for 8-bit element size

Each small box in the figures of this section represents an 8-bit element.

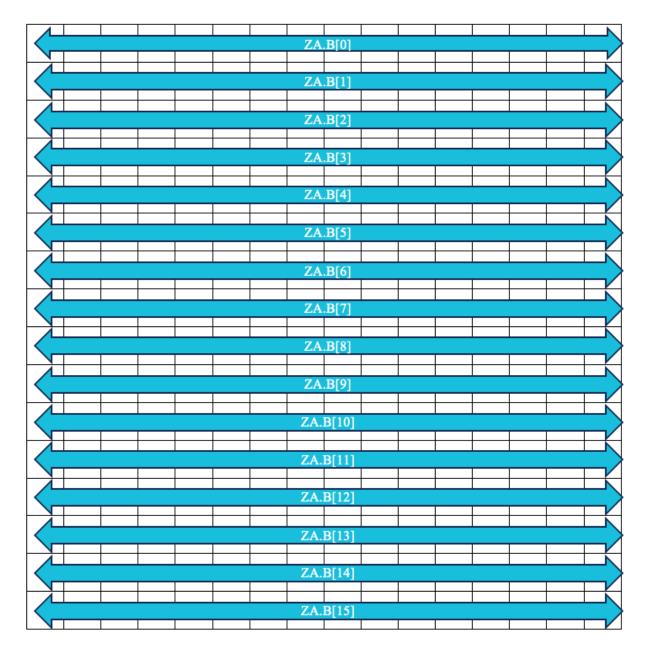

#### ZA array vector access for 8-bit element size

Figure 2-2 shows ZA Storage with ZA array vector access for 8-bit element size.

# Figure 2-2: ZA array vector access in ZA storage for 8-bit element size for an 128-bit SVL implementation

Accessing ZA tile for 8-bit element size

Copyright © 2024 Arm Limited (or its affiliates). All rights reserved. Non-Confidential When accessing 8-bit element ZA tile, there is a single tile ZA0.B which consists of  $[16 \times 16]$  8-bit elements and occupies all of the ZA storage.

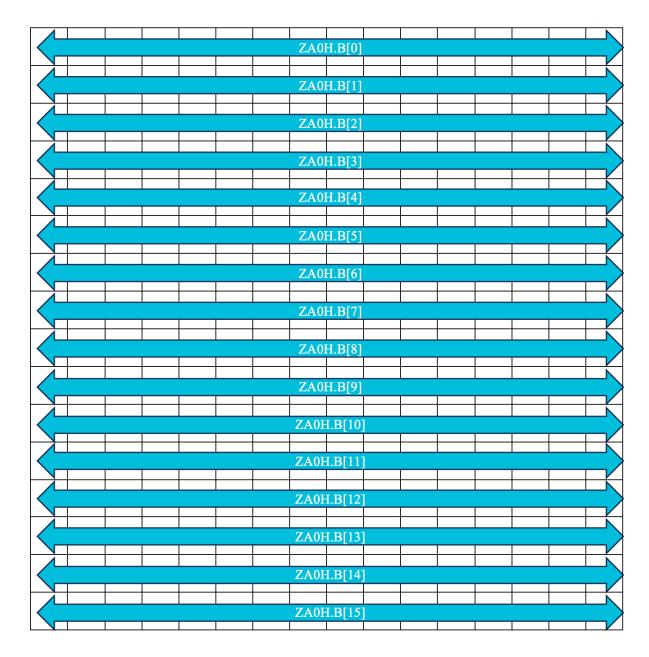

Figure 2-3 shows the horizontal slice of ZAO.B tile.

Figure 2-3: Horizontal slices in ZAO.B tile

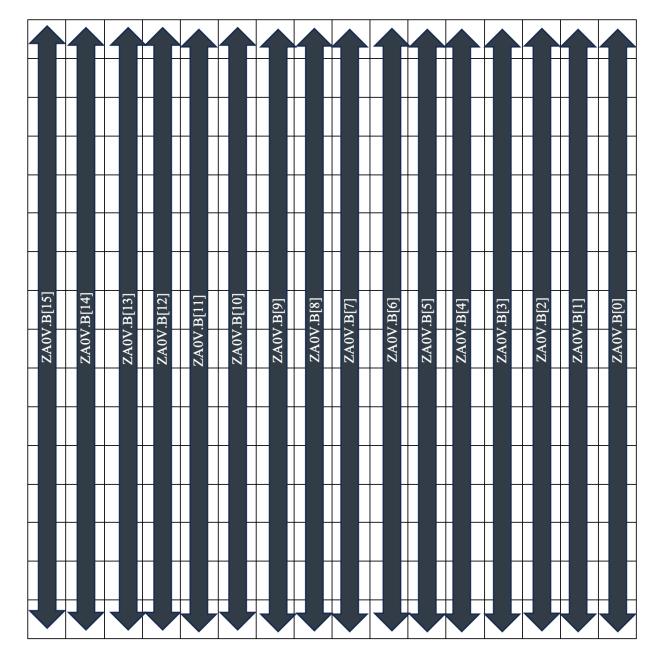

Figure 2-4 shows the vertical slice of ZAO.B tile.

Figure 2-4: Vertical slices in ZAO.B tile

Figure 2-2, Figure 2-3, and Figure 2-4 show ZA storage being accessible as:

- Vectors of 8-bit element size

- Horizontal and vertical slices in a tile of 8-bit element size

The subsequent sections depict ZA storage being accessible as:

- Vectors of 16-bit and 32-bit element sizes

- Horizontal and vertical slices in a tile of 16-bit and 32-bit element sizes

### 2.3.1.2 ZA storage access for 16-bit element size

Each small box in the figures of this section represents an 16-bit element.

#### ZA array vector access for 16-bit element size

Figure 2-5 shows ZA Storage with ZA array vector access for 16-bit element size. The color coding used in the following figure shows how the vectors are mapped to different tiles that are described in subsequent sections.

Figure 2-5: ZA array vector access in ZA Storage for 16-bit element size for an 128-bit SVL implementation

|                         | ZA H[0]              |   |

|-------------------------|----------------------|---|

|                         |                      |   |

| /                       |                      | N |

| <                       | ZA H[1]              |   |

|                         |                      |   |

|                         | ZAH[2]               | / |

|                         |                      | / |

|                         |                      |   |

| $\langle $              | ZAH[3]               |   |

|                         |                      |   |

| /                       |                      | N |

|                         | ZA H[4]              |   |

|                         |                      |   |

|                         | ZA H[5]              |   |

|                         |                      | / |

|                         |                      |   |

| $\langle \cdot \rangle$ | ZAH[6]               |   |

|                         |                      |   |

|                         |                      | N |

|                         | ZA H[7]              |   |

|                         |                      |   |

| /                       | ZA <mark>H[8]</mark> |   |

|                         |                      | / |

|                         |                      |   |

| $\langle $              | ZAH[9]               |   |

|                         |                      |   |

|                         |                      | / |

|                         | ZA.H[10]             | / |

|                         |                      |   |

| $\langle -$             | ZA.H[11]             |   |

|                         |                      |   |

| ∕                       |                      | N |

|                         | ZA.H[12]             |   |

|                         |                      |   |

|                         | ZA.H[13]             |   |

|                         |                      |   |

|                         |                      |   |

| <hr/>                   | ZA.H[14]             |   |

|                         |                      |   |

|                         |                      |   |

|                         | ZA.H[15]             |   |

|                         |                      |   |

#### Accessing ZA tile for 16-bit element size

While accessing 16-bit element ZA tile, there are two tiles, ZAO.H and ZA1.H. Each tile consists of  $[8 \times 8]$  16-bit elements and occupies half of the ZA storage.

Figure 2-6 shows the horizontal slices of ZAO.H tile in the ZA storage.

|           | ZA0H.H[0] |                   |

|-----------|-----------|-------------------|

|           |           | /                 |

|           |           |                   |

|           |           |                   |

|           |           | N                 |

|           | ZA0H.H[1] |                   |

|           |           |                   |

|           |           |                   |

|           |           |                   |

|           |           |                   |

| $\langle$ | ZA0H.H[2] |                   |

|           |           |                   |

|           |           |                   |

|           |           |                   |

|           |           | N                 |

| $\leq$    | ZA0H.H[3] | /                 |

|           |           | <u> </u>          |

|           |           |                   |

|           |           |                   |

|           |           | $\sim$            |

|           | ZA0H.H[4] |                   |

|           |           |                   |

|           |           |                   |

|           |           |                   |

|           | ZA0H.H[5] | ' ``' ``' ``' ``' |

|           |           |                   |

|           |           |                   |

|           |           |                   |

|           |           |                   |

| $\leq$    | ZA0H.H[6] |                   |

|           |           |                   |

|           |           |                   |

|           |           |                   |

|           |           |                   |

|           | ZA0H.H[7] |                   |

|           |           |                   |

|           |           |                   |

|           |           |                   |

#### Figure 2-6: Horizontal slices in ZA0.H tile in ZA storage

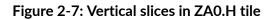

Figure 2-7 shows vertical slices in the ZAO.H tile.

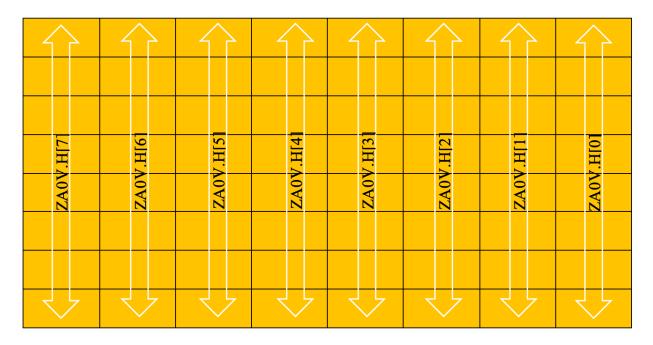

Figure 2-8 shows the horizontal slices of ZA1.H tile in the ZA storage.

| Image: Constraint of the second se      |                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| N       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |

| N       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |

| N       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | N                        |

| N       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | レノ                       |

| No.       N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ^۲                       |

| No.       N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                        |

| Normalization       Normalization       Normalization       Normalization         ZA1H.H[2]       ZA1H.H[2]       Normalization       Normalization         ZA1H.H[3]       ZA1H.H[3]       Normalization       Normalization         ZA1H.H[4]       ZA1H.H[4]       Normalization       Normalization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |

| No.       N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |

| Normalized       Image: Constraint of the second seco               |                          |

| Normalized       Image: Constraint of the second seco               |                          |

| N       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $\overline{\mathcal{V}}$ |

| N       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |

| N       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |

| N       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |

| N       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |

| ZA1H.H[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ٦/                       |

| ZA1H.H[4]     Image: state s | V                        |

| ZA1H.H[4]     Image: state s |                          |

| ZA1H.H[4]     Image: state s |                          |

| ZA1H.H[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | N                        |

| ZA1H.H[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |

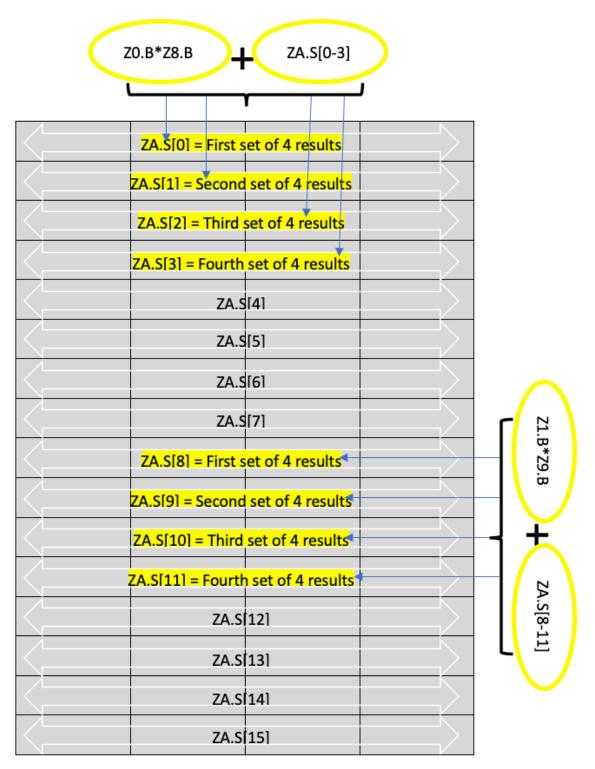

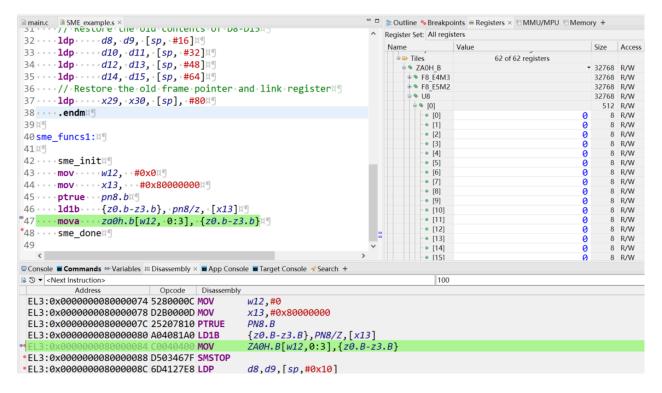

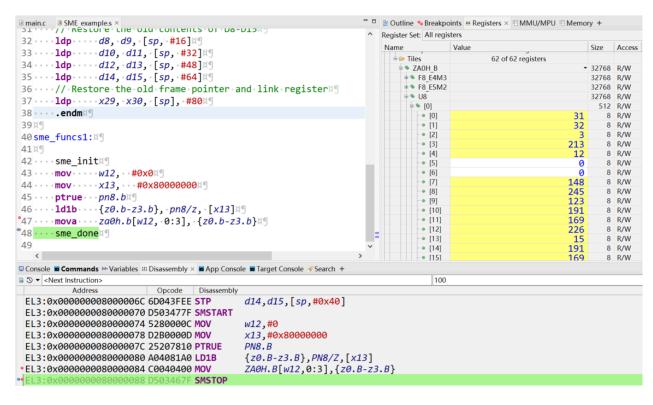

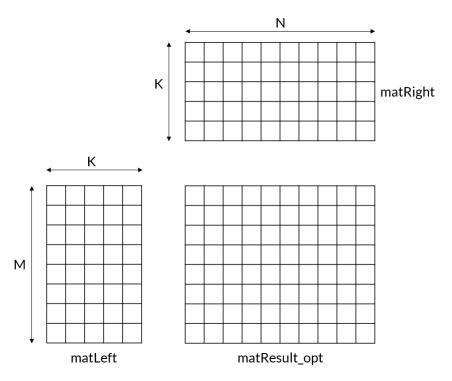

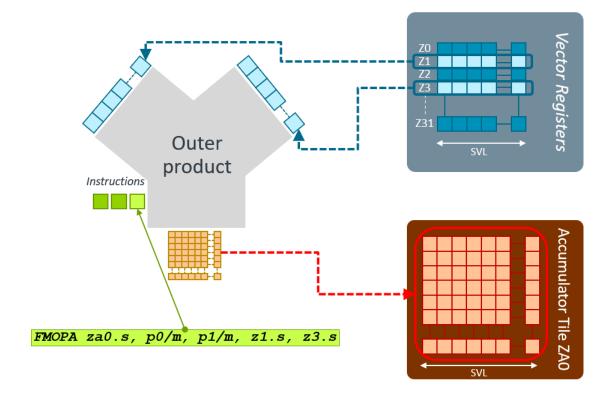

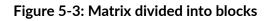

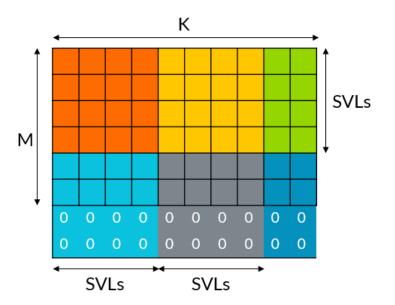

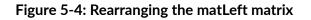

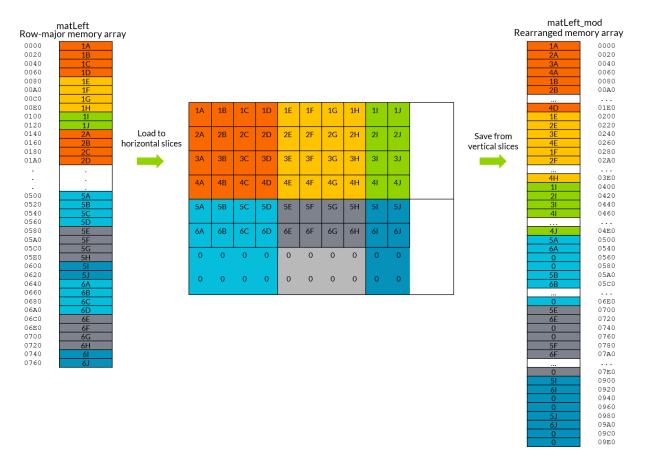

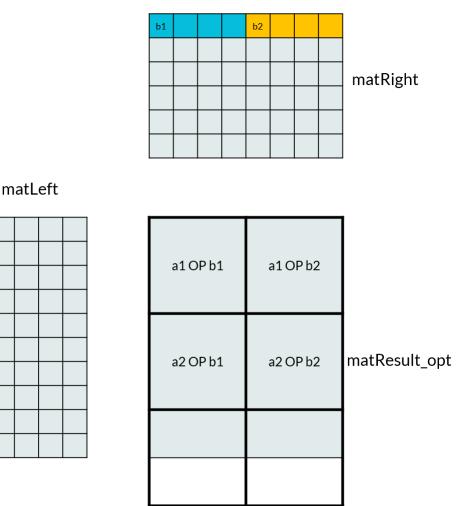

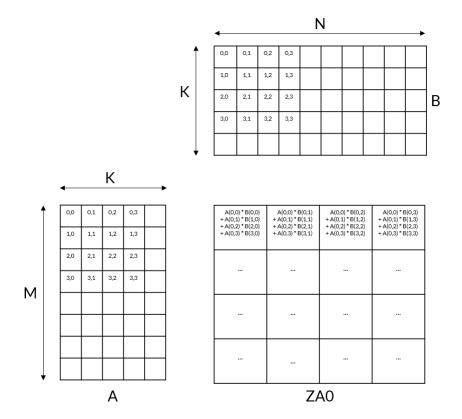

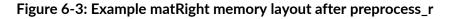

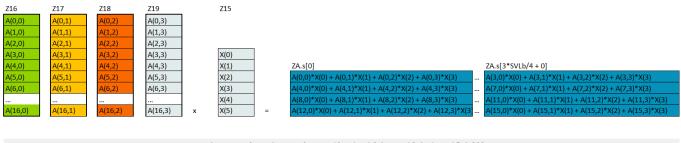

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |