# IO Remapping Table Platform Design Document

Non-confidential

Copyright © 2015, 2017, 2018, 2020-2022, 2024 Arm Limited (or its affiliates). All rights reserved. Document number: ARM DEN 0049E.f

System Software on Arm

Copyright © 2015, 2017, 2018, 2020, 2021, 2022, 2024 Arm Limited (or its affiliates). All rights reserved.

#### **Release information**

The Change History table lists the changes made to this document.

#### Table 1-1 Change history

| Date           | Issue | Confidentiality  | Change                                                                                                                                                                                                                                                |

|----------------|-------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17 April 2015  | А     | Non-Confidential | First release.                                                                                                                                                                                                                                        |

| 1 October 2015 | В     | Non-Confidential | Added SMMUv3                                                                                                                                                                                                                                          |

| 15 May 2017    | С     | Non-Confidential | Fixed support for MSIs in SMMUv3 added PMCG                                                                                                                                                                                                           |

| March 2018     | D     | Non-Confidential | PMCG page 1 support. SMMUv3 fix or proximity node. PASID width added to named nodes. DMA mask added to roo complex node.                                                                                                                              |

| July 2020      | E     | Non-Confidential | Bumped up the revisions of the table<br>header, the RC node, the named<br>component node and the SMMU nodes<br>Added an Identifier field in the node<br>descriptors to aid table cross-<br>referencing.<br>Added the Reserved Memory Range            |

|                |       |                  | (RMR) node.                                                                                                                                                                                                                                           |

|                |       |                  | Tightened the language on permitted I<br>mappings for certain nodes such as th<br>SMMU node.                                                                                                                                                          |

|                |       |                  | Introduced a flag in the RC node to express support for PRI.                                                                                                                                                                                          |

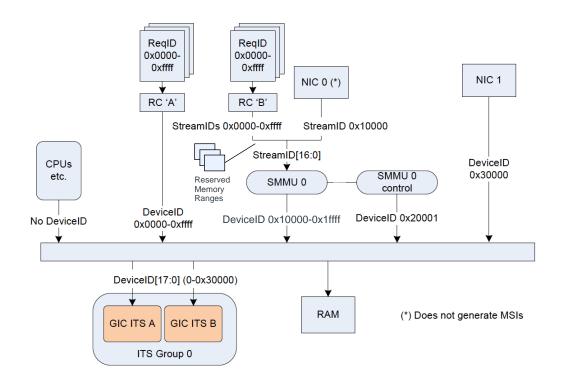

|                |       |                  | Updated Figure 2 to reflect the right<br>DeviceIDs being output from SMMU 0<br>(since NIC 0 does not generate an MS<br>as per the example).                                                                                                           |

|                |       |                  | Added a note on use of IMP_DEF inpu<br>IDs in ID mappings within Named<br>Component nodes.                                                                                                                                                            |

| November 2020  | E.a   | Non-confidential | Deprecated the Revision field in<br>individual nodes. The table header<br>Revision is the one and only Revision<br>indicator. Any change within the table<br>must result in an update to the header<br>revision. This simplifies software<br>support. |

|                |       |                  | Bumped up the Identifier field of the<br>nodes to 32 bits, to establish overall<br>consistency, and parity with existing<br>ACPI_UID definitions.                                                                                                     |

|                |       |                  | Added a flag called DMAO, and<br>clarifying text to explicitly call out the<br>relation between memory access size<br>limitations and related properties<br>defined in the _DMA object of a name                                                      |

Copyright © 2015, 2017, 2018, 2020-2022, 2024 Arm Limited (or its affiliates). All rights reserved. ARM DEN 0049E.f Non-confidential

|               |     |                  | component that is a bridge, with the<br>device memory address size limit<br>property of the device defined in the<br>Named Component node.<br>Added a Flags field to the RMR node<br>with a flag that specifies whether it is<br>permitted for the OS to remap the<br>reserved memory ranges at runtime.<br>Added a clause in the RMR node to<br>mandate the use of the PCI _DSM<br>method for boot configuration, to allow<br>live devices using reserved memory<br>regions to remain functionally<br>operational during OS boot.<br>Added clarifying language on the usa |

|---------------|-----|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |     |                  | of the COHACC and HTTU override<br>bits in the SMMUv3 node.<br>Added a flag in the Root complex nod<br>to declare support for forwarding PAS<br>information to the SMMU on translate<br>transactions.                                                                                                                                                                                                                                                                                                                                                                      |

| February 2021 | E.b | Non-confidential | Reintroduced the Revision field within<br>IORT node descriptors to support<br>legacy dependencies.<br>Moved flags field in RMR node to the<br>node-specific section to maintain<br>consistency with other nodes and the<br>generic IORT node descriptor format.                                                                                                                                                                                                                                                                                                            |

|               |     |                  | Deprecated the DMAO flag and<br>replaced it with a clarifying note.<br>Added a clarifying note on the use of<br>PCIe _DSM Function 5 for continuity<br>operation.                                                                                                                                                                                                                                                                                                                                                                                                          |

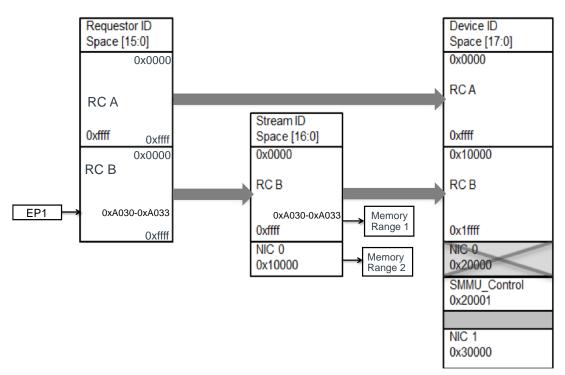

|               |     |                  | Minor fixes to the RMR node example<br>in Appendix A. Notably, NIC 1 is<br>replaced with NIC 0 to match<br>illustration. Also, updated the<br>terminology used in the examples to<br>match definitions in the main section<br>the specification, notably the ID<br>mapping structures.                                                                                                                                                                                                                                                                                     |

| January 2022  | E.c | Non-confidential | Added descriptor in the root complex<br>node for specifying PASID width<br>supported by the root complex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               |     |                  | Added note in the root complex node<br>description that allows the node to vie<br>a root complex as a PCIe domain tha<br>is not necessarily a physical root<br>complex. This allows PCIe EPs to be<br>variously configured with different<br>properties.                                                                                                                                                                                                                                                                                                                   |

|               |     |                  | Removed restriction on number of<br>Stream IDs that can be associated wi<br>memory ranges in an RMR node.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

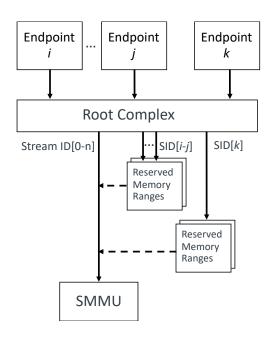

|               |     |                  | Updated Figure 1 and Figure 3 to reflect the fact that it is permissible to have multiple Stream IDs associated with a single RMR node.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Page 3 of 38

|                |     |                  | Added clarity on correlation between<br>_DMA methods on named components<br>and root complexes and how they<br>relate to the "Device memory address<br>size limit" and "Memory address size<br>limit" fields of these nodes, respectively.<br>Introduced memory access attributes in |

|----------------|-----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |     |                  | the the RMR node.                                                                                                                                                                                                                                                                    |

| February 2022  | E.d | Non-confidential | Readjusted fields in the RMR node to<br>preserve its original length. This is to<br>ensure backward compatibility with<br>existing software developed for version<br>E.b.                                                                                                            |

|                |     |                  | Note: Issue E.c is deprecated and must not be referenced.                                                                                                                                                                                                                            |

| September 2022 | E.e | Non-confidential | Added flags in SMMUv3 node for<br>validity of ID mappings for MSIs related<br>to control interrupts.                                                                                                                                                                                 |

| April 2024     | E.f | Non-confidential | Moved memory access flags and property tables to the common section.                                                                                                                                                                                                                 |

|                |     |                  | Added CANWBS Memory access flag.                                                                                                                                                                                                                                                     |

|                |     |                  | New version of Arm Non-Confidential<br>Document Licence.                                                                                                                                                                                                                             |

## Arm Non-Confidential Document Licence ("Licence")

This License is a legal agreement between you and Arm Limited ("**Arm**") for the use of Arm's intellectual property (including, without limitation, any copyright) embodied in the document accompanying this License ("**Document**"). Arm licenses its intellectual property in the Document to you on condition that you agree to the terms of this License. By using or copying the Document you indicate that you agree to be bound by the terms of this License.

"Subsidiary" means any company the majority of whose voting shares is now or hereafter owned or controlled, directly or indirectly, by you. A company shall be a Subsidiary only for the period during which such control exists.

This Document is **NON-CONFIDENTIAL** and any use by you and your Subsidiaries ("Licensee") is subject to the terms of this License between you and Arm.

Subject to the terms and conditions of this License, Arm hereby grants to Licensee under the intellectual property in the Document owned or controlled by Arm, a non-exclusive, non-transferable, non-sub-licensable, royalty-free, worldwide License to:

- (i) use and copy the Document for the purpose of designing and having designed products that comply with the Document;

- (ii) manufacture and have manufactured products which have been created under the License granted in (i) above; and

- (iii) sell, supply and distribute products which have been created under the License granted in (i) above.

# Licensee hereby agrees that the Licenses granted above shall not extend to any portion or function of a product that is not itself compliant with part of the Document.

Except as expressly licensed above, Licensee acquires no right, title or interest in any Arm technology or any intellectual property embodied therein.

The content of this document is informational only. Any solutions presented herein are subject to changing conditions, information, scope, and data. This document was produced using reasonable efforts based on information available as of the date of issue of this document. The scope of information in this document may exceed that which Arm is required to provide, and such additional information is merely intended to further assist the recipient and does not represent Arm's view of the scope of its obligations. You acknowledge and agree that you possess the necessary expertise in system security and functional safety and that you shall be solely responsible for compliance with all legal, regulatory, safety and security related requirements concerning your products, notwithstanding any information or support that may be provided by Arm herein. In addition, you are responsible for any applications which are used in conjunction with any Arm technology described in this document, and to minimize risks, adequate design and operating safeguards should be provided for by you.

Reference by Arm to any third party's products or services within this document is not an express or implied approval or endorsement of the use thereof.

THE DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. Arm may make changes to the Document at any time and without notice. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

NOTWITHSTANDING ANYTHING TO THE CONTRARY CONTAINED IN THIS LICENSE, TO THE FULLEST EXTENT PERMITTED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, IN CONTRACT, TORT OR OTHERWISE, IN CONNECTION WITH THE SUBJECT MATTER OF THIS LICENSE (INCLUDING WITHOUT LIMITATION) (I) LICENSEE'S USE OF THE DOCUMENT; AND (II) THE IMPLEMENTATION OF THE DOCUMENT IN ANY PRODUCT CREATED BY LICENSEE UNDER THIS LICENSE). THE EXISTENCE OF MORE THAN ONE CLAIM OR SUIT WILL NOT ENLARGE OR EXTEND THE LIMIT. LICENSEE RELEASES ARM FROM ALL OBLIGATIONS, LIABILITY, CLAIMS OR DEMANDS IN EXCESS OF THIS LIMITATION.

Page 5 of 38

This License shall remain in force until terminated by Licensee or by Arm. Without prejudice to any of its other rights, if Licensee is in breach of any of the terms and conditions of this License then Arm may terminate this License immediately upon giving written notice to Licensee. Licensee may terminate this License at any time. Upon termination of this License by Licensee or by Arm, Licensee shall stop using the Document and destroy all copies of the Document in its possession. Upon termination of this License, all terms shall survive except for the License grants.

Any breach of this License by a Subsidiary shall entitle Arm to terminate this License as if you were the party in breach. Any termination of this License shall be effective in respect of all Subsidiaries. Any rights granted to any Subsidiary hereunder shall automatically terminate upon such Subsidiary ceasing to be a Subsidiary.

The Document consists solely of commercial items. Licensee shall be responsible for ensuring that any use, duplication or disclosure of the Document complies fully with any relevant export laws and regulations to assure that the Document or any portion thereof is not exported, directly or indirectly, in violation of such export laws.

This License may be translated into other languages for convenience, and Licensee agrees that if there is any conflict between the English version of this License and any translation, the terms of the English version of this License shall prevail.

The Arm corporate logo and words marked with ® or ™ are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. No License, express, implied or otherwise, is granted to Licensee under this License, to use the Arm trade marks in connection with the Document or any products based thereon. Visit Arm's website at <a href="https://www.arm.com/company/policies/trademarks">https://www.arm.com/company/policies/trademarks</a> for more information about Arm's trademarks.

The validity, construction and performance of this License shall be governed by English Law.

Copyright © [2015, 2017, 2018, 2020-2022, 2024] Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England. 110 Fulbourn Road, Cambridge, England CB1 9NJ.

Arm document reference: PRE-21585 version 5.0, March 2024

# Contents

| 1   | ABOUT THIS DOCUMENT         1.1       References         1.2       Terms and abbreviations         1.3       Feedback         1.3.1       Feedback on this manual |                 |  |  |  |  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|

| 2   | INTRODUCTION                                                                                                                                                      | 10              |  |  |  |  |

| 3   | IO REMAPPING TABLE<br>3.1.1 IORT node types                                                                                                                       | <b>11</b><br>16 |  |  |  |  |

| APF | PENDIX A RATIONALE AND EXAMPLES                                                                                                                                   | 28              |  |  |  |  |

| APF | APPENDIX B OS USAGE OF MEMORY ATTRIBUTES                                                                                                                          |                 |  |  |  |  |

This document provides a proposal for an ACPI representation of IO topology to be used by Arm-based systems.

## 1.1 References

This document refers to the following documents.

| Reference | Document Number | Title                                                                                                          |

|-----------|-----------------|----------------------------------------------------------------------------------------------------------------|

| [ACPI]    | ACPI            | Advanced Configuration and Power Interface Specification                                                       |

| [GIC]     | ARM IHI 0069    | Arm Generic Interrupt Controller Architecture Specification, GIC architecture version 3.0 and version 4.0      |

| [SBSA]    | ARM DEN 0029    | Server Base System Architecture                                                                                |

| [SMMUv2]  | ARM IHI 0062    | Arm System Memory Management<br>Unit Architecture Specification, SMMU architecture version 2.0                 |

| [SMMUv3]  | ARM IHI 0070    | Arm System Memory Management Unit Architecture<br>Specification, SMMU architecture version 3.0 and version 3.1 |

| [PCIFW]   |                 | PCI <sup>™</sup> Firmware Specification, Revision 3.1                                                          |

## 1.2 Terms and abbreviations

This document uses the following terms and abbreviations.

| Term        | Meaning                                                                                                                                                                                 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RID         | Requestor ID for a PCI express device.                                                                                                                                                  |

| BDF         | Bus Device Function. Equivalent to a RID.                                                                                                                                               |

| DeviceID    | Identifier for a device exposed to the GICv3/4 Interrupt Translation Service. See [GIC] for more details.                                                                               |

| IOVA        | Input Output Virtual Address. The virtual addresses seen by IO devices.                                                                                                                 |

| ITS         | GIC Interrupt Translation Service. See [GIC] for more details.                                                                                                                          |

| StreamID    | A StreamID uniquely identifies to an SMMU a stream of transactions that can originate from one or more devices but are associated with the same context. See [SMMUv2] for more details. |

| SBSA        | Server Base System Architecture.                                                                                                                                                        |

| IO Coherent | A device is IO Coherent with the processor caches if its transactions snoop the processor caches for cacheable regions of memory. The processor does not snoop the device cache.        |

## 1.3 Feedback

Arm welcomes feedback on its documentation.

Page 8 of 38

## **1.3.1 Feedback on this manual**

If you have comments on the content of this manual, send an email to errata@arm.com. Give:

- The title.

- The document and version number, ARM DEN 0049E.f.

- The page numbers to which your comments apply.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

## 2 Introduction

This document describes the *Input Output Remapping Table* (IORT), which represents the IO topology of an Armbased system for use with the *Advanced Configuration and Power Interface* (ACPI). The IORT describes how various components are connected together, and how those components that need identification reserve values in the appropriate identification space.

In particular, the IORT:

- Provides an ACPI description for IO topology, SMMUs, and GIC ITSs.

- Identifies which components are behind which SMMU.

- Identifies which components are behind an ITS or group of ITSs.

- Describes the IO relationships of PCIe root complexes and relates this description to the MCFG table [PCIFW] and the ACPI namespace.

- Describes the IO relationships between devices represented in the ACPI namespace.

- Represents the following ID mapping relationships:

- From BDF requestor ID, for a PCIe device, to a StreamID for an SMMU, and then to a DeviceID for an ITS.

- From BDF requestor ID to a DeviceID, for a device that is not connected to SMMU but which can generate MSIs.

- Individual endpoint StreamIDs.

- Individual endpoint DeviceIDs.

- Does not support arbitrarily complex ID mappings. Only simple offset-based mappings are supported.

The next section describes the IORT in detail. Appendix A explains how the IORT is used to describe a system and provides examples. Finally, Appendix B describes how the memory attributes that are described for a device can be used to ascertain when cache management is required.

Table 2 shows the structure of the IORT. Apart from the basic header, the table contains a number of IORT Nodes. Each node represents a component, which can be an SMMU, an ITS Group, a root complex, or a component that is described in the namespace.

| Field                            | Byte<br>Length | Byte<br>Offset | Description                                                                                                                             |

|----------------------------------|----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Header                           |                |                | Standard ACPI format for header.                                                                                                        |

| Signature                        | 4              | 0              | 'IORT'. IO Remapping Table.                                                                                                             |

| Length                           | 4              | 4              | Length, in bytes, of the entire IORT.                                                                                                   |

| Revision                         | 1              | 8              | 6                                                                                                                                       |

| Checksum                         | 1              | 9              | The entire table must sum to zero.                                                                                                      |

| OEMID                            | 6              | 10             | OEM ID.                                                                                                                                 |

| OEM Table ID                     | 8              | 16             | For the IORT, the table ID is the manufacture model ID.                                                                                 |

| OEM Revision                     | 4              | 24             | OEM revision of the IORT for the supplied OEM Table ID.                                                                                 |

| Creator ID                       | 4              | 28             | The vendor ID of the utility that created the table. For tables containing Definition Blocks, this is the ID for the ASL Compiler.      |

| Creator Revision                 | 4              | 32             | The revision of the utility that created the table. For tables containing Definition Blocks, this is the revision for the ASL Compiler. |

| Body                             |                |                |                                                                                                                                         |

| Number of IORT<br>Nodes          | 4              | 36             | The number of nodes in the IORT Node Array.                                                                                             |

| Offset to Array of<br>IORT Nodes | 4              | 40             | The offset from the start of the table to the first node in the array of IORT nodes.                                                    |

| Reserved                         | 4              | 44             | Reserved, must be zero.                                                                                                                 |

| Optional padding                 |                |                |                                                                                                                                         |

| Array of IORT Nodes              |                |                | Array of IORT Nodes.                                                                                                                    |

Nodes describe component *identifiers* (IDs) and the mapping between the input space of those IDs and the output space. For example, a root complex node, sitting behind an SMMU, describes how the input RID space of the root complex maps onto the output StreamID space that is directed to the SMMU. Not every node needs IDs. Some nodes, such as those that represent ITS groups, only consume IDs. ITSs consume DeviceIDs. Table 3 shows the format of IORT Nodes.

Page 11 of 38

#### **Table 3 Node Format**

| Field                      | Byte<br>Length | Byte Offset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------|----------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Generic data:              |                |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Туре                       | 1              | 0           | <ul> <li>Possible values and their meanings are:</li> <li>0: ITS Group.</li> <li>1: Named component.</li> <li>2: Root complex.</li> <li>3: SMMUv1 or SMMUv2.</li> <li>4: SMMUv3.</li> <li>5: PMCG.</li> <li>6: Memory range.</li> <li>7-255: Reserved.</li> </ul>                                                                                                                                                                                                                          |

| Length                     | 2              | 1           | Length of node in bytes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Revision                   | 1              | 3           | Revision of the IORT node.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Identifier                 | 4              | 4           | Unique identifier for this node that can be used to locate<br>it in the parent table. This identifier enables other ACPI<br>tables and DSDT objects to locate this node. This field<br>serves in the same capacity as the _UID object<br>associated with ACPI device objects.<br>IMPLEMENTATION NOTE: In the simplest scheme, the<br>Identifier might be set to the node's index in the array of<br>IORT nodes in the parent IORT table. Other schemes<br>are also possible and permitted. |

| Number of ID<br>mappings   | 4              | 8           | Number of ID entries in the ID Array.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Reference to ID Array      | 4              | 12          | Offset from the start of the IORT node to the start of its<br>Array of ID mappings. This field has a value of 0 in the<br>case of an ITS that has no IDs.                                                                                                                                                                                                                                                                                                                                  |

| Data that varies for nod   | e type:        |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Data specific to a<br>Node | х              | 16          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ID Section:                |                | -           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Array of ID mappings       | 20xN           | 16+X        | ID mapping Array, where N is the number of ID mappings.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

ID mappings represent the formula by which an ID from a source is converted to an ID in a destination. For example, for a root complex behind an SMMU, the RID originating from that root complex must be converted to a StreamID in the destination SMMU. With IORT, ID mappings are declared in the source node. Each mapping describes the destination of the IDs, also known as the output, as well as the numerical relationship that must hold between input IDs and output IDs. The format of each entry in the array of ID mappings is shown in Table 4.

#### Table 4 ID mapping format

| Field         | Byte<br>Length | Byte<br>Offset | Description                               |

|---------------|----------------|----------------|-------------------------------------------|

| Input base    | 4              | 0              | The lowest value in the input range.      |

| Number of IDs | 4              | 4              | The number of IDs in the range minus one. |

| Output base      | 4 | 8  | The lowest value in the output range.                                                                                                                                                                                                                                                                                                 |

|------------------|---|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output Reference | 4 | 12 | A reference to the output IORT Node. This field contains the<br>address offset of the IORT Node relative to the start of the IORT.<br>For example, if this ID mapping is for a root complex outputting to<br>an SMMU, the value of this field is the difference between the start<br>of the SMMU IORT node and the start of the IORT. |

| Flags            | 4 | 16 | See Table 5.                                                                                                                                                                                                                                                                                                                          |

Table 5 shows the format of the ID flags.

## Table 5 ID flags format

| Field          | Bit<br>Length | Bit<br>Offset | Description                                                                                                                                                                                   |

|----------------|---------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Single mapping | 1             | 0             | Single mapping. Apply the output base regardless of the input IDs.<br>This flag is only valid when the mapping is contained inside a named component, root complex node, SMMUv3 or PMCG node. |

| Reserved       | 31            | 1             | Reserved, must be zero.                                                                                                                                                                       |

Table 6 describes device node memory access properties.

#### Table 6 Memory access properties

| Field                               | Byte<br>Length | Byte<br>Offset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|-------------------------------------|----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CCA: Cache<br>Coherent<br>Attribute | 4              | 0              | This value must match the value returned by the _CCA object that is defined<br>in the DSDT for the device represented by this node. The attribute can take<br>the following values:                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                                     |                |                | 0x1: The device is fully coherent. No cache maintenance* is required for<br>memory that is shared with the device that is mapped on CPUs as<br><i>Inner Write-Back</i> (IWB), <i>Outer Write-back</i> (OWB), <i>and Inner</i><br><i>shareable</i> (ISH). In addition, during system initialization at cold<br>boot, or after wakeup from low-power state, if the cache coherency<br>requires an SMMU override or some specific device configuration,<br>the platform firmware has to ensure that this has been done.<br>Therefore the semantics represented by a value of 0x1 are always<br>correct at the time of hand-off from firmware to OS. |  |

|                                     |                |                | 0x0: The device is not coherent. Therefore:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                                     |                |                | <ul> <li>Cache maintenance is required for memory that is shared with the device that is mapped on CPUs as IWB-OWB-ISH.</li> <li>No cache maintenance is required for memory that is shared with the device that is mapped on CPUs as device or Non-cacheable.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                        |  |

|                                     |                |                | All other values are reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| AH: Allocation<br>Hints             | 1              | 4              | This field can be ignored without loss of correctness.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                                     |                |                | Allocation hints have the following format:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                                     |                |                | <ul> <li>Bits[7:4] are ignored by the OS and must be zero.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Field                       | Byte<br>Length | Byte<br>Offset | Description                                                                                                                                                                                                                                                                           |  |

|-----------------------------|----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                             |                |                | <ul> <li>Bit 3: Allocation Hints Override (AHO).</li> <li>0: If the bit is clear, use the incoming Read Allocate (RA), Write Allocate (WA), and Transient (TR) hints.</li> <li>1: If the bit is set, override allocation hints based on the values in bits RA, WA, and TR.</li> </ul> |  |

|                             |                |                | <ul> <li>Bit 2: Read Allocate (RA).</li> <li>0: Clear read allocation hint if AHO is set to 1.</li> <li>1: Set read allocation hint if AHO is set to 1.</li> </ul>                                                                                                                    |  |

|                             |                |                | <ul> <li>Bit 1: Write Allocate (WA).</li> <li>0: Clear write allocation hint if AHO is set to 1.</li> <li>1: Set write allocation hint if AHO is set to 1.</li> </ul>                                                                                                                 |  |

|                             |                |                | <ul> <li>Bit 0: Transient (TR).</li> <li>0: Clear transient hint if AHO is set to 1.</li> <li>1: Set transient hint if AHO is set to 1.</li> </ul>                                                                                                                                    |  |

| Reserved                    | 2              | 5              | Reserved, must be zero.                                                                                                                                                                                                                                                               |  |

| MAF: Memory<br>Access Flags | 1              | 7              | See Table 7.                                                                                                                                                                                                                                                                          |  |

\* Note: Caching operations described in this document apply to the CPU caches and any other caches in the system where device memory accesses can hit.

Table 7 describes the memory access properties flags field format.

## Table 7 Memory Access Flags

| Field                           | Bit<br>Length | Bit<br>Offset | Description                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------|---------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPM: Coherent<br>Path to Memory | 1             | 0             | 0x1: If set, this indicates that the device has path to memory that allows<br>coherency with the CPU cache hierarchy. This means that if<br>the CPU maps the memory as IWB, OWB, ISH, and the device<br>is outputting the same attributes, or being overridden through<br>an SMMU to provide the same attributes, no cache<br>maintenance is required. |

|                                 |               |               | 0x0: The device does not have a path to memory that is coherent with the CPU cache hierarchy. Therefore:                                                                                                                                                                                                                                               |

|                                 |               |               | <ul> <li>Cache maintenance is required for memory that is shared with the device that is mapped on the CPU as IWB-OWB-ISH.</li> <li>No cache maintenance is required for memory that is shared with the device that is mapped on the CPU as device or Non-cacheable.</li> </ul>                                                                        |

|                                 |               |               | Note that if CCA is 0x1, CPM must also be 0x1. Conversely, If CPM is 0x0 then CCA must be 0x0. However, it possible for the system to boot with CCA set to 0x0 and CPM set to 0x1. See Table 8 for further details.                                                                                                                                    |

| DACS: Device attributes are     | 1             | 1             | The device outputs IWB-OWB-ISH attributes:                                                                                                                                                                                                                                                                                                             |

| Cacheable and                   |               |               | 0x1: The device outputs IWB-OWB-ISH attributes.                                                                                                                                                                                                                                                                                                        |

Page 14 of 38

| Field                                                                                          | Bit<br>Length | Bit<br>Offset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|------------------------------------------------------------------------------------------------|---------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Inner-Shareable                                                                                |               |               | 0x0: The device does not output IWB-OWB-ISH attributes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| CANWBS:<br>Coherency of<br>Accesses not<br>marked<br>Inner/Outer WB<br>Cacheable,<br>Shareable | 1             | 2             | <ul> <li>0x0: Use of mismatched memory attributes for accesses made by this device may lead to a loss of coherency.</li> <li>0x1: Coherency of accesses made by this device to locations in Conventional memory are ensured as follows, even if the memory attributes for the accesses presented by the device or provided by the SMMU are different from Inner and Outer Write-back cacheable, Shareable.</li> <li>Accesses made by this device to locations in Conventional memory are coherent with accesses made by PEs that have the same locations mapped as Inner and Outer Write-back cacheable, Shareable.</li> <li>Accesses made by this device to locations in Conventional memory are coherent with accesses made by PEs that have the same locations mapped as Inner and Outer Write-back cacheable, Shareable.</li> <li>Accesses made by this device to locations in Conventional memory are coherent with accesses made by other devices that have this property.</li> </ul> Note: Examples of device-originated accesses not having a memory type of Inner and Outer Write-back Cacheable, Shareable include cases where the S2FWB feature is not implemented or not enabled, and cases relating to the PCI No snoop attribute. |  |

| Reserved                                                                                       | 5             | 3             | Reserved must be zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

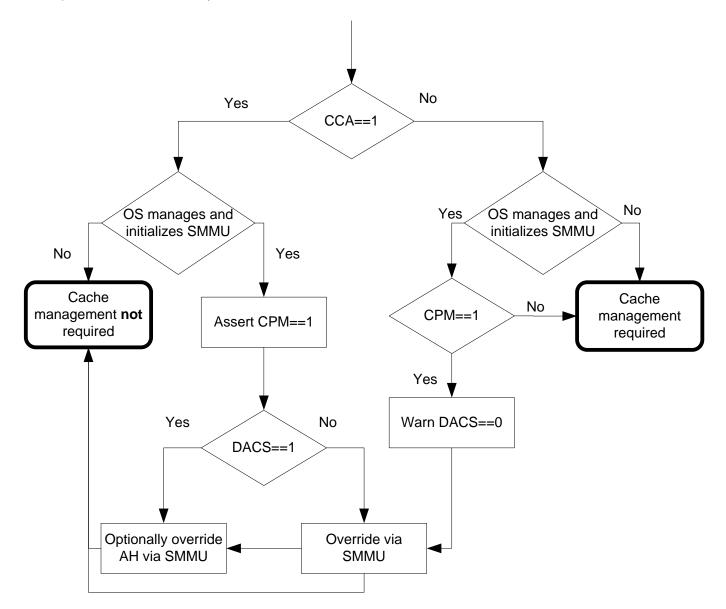

Not every combination of memory attribute values is valid or useful. Table 8 lists the valid combinations and their uses:

### **Table 8 Valid Memory Attributes**

| CCA | CPM | DACS | CANWBS | AH             | Comment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|-----|------|--------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | 1   | 1    | *      | Can be applied | The device outputs the correct attributes that enable<br>cache coherency (IWB-OWB-ISH). If the shared<br>memory is mapped on the CPU with the same<br>attributes, no cache management is necessary, and<br>the device exploits cache coherency.<br>If the device is behind an SMMU, the OS might<br>override the allocation hint attributes using the values<br>that are supplied in the AH. However, in this case the<br>OS must maintain the coherency guarantee indicated<br>by the CCA value of 1. Therefore, it must not change<br>the cacheability and shareability attributes provided by<br>the device (IWB-OWB-ISH). |

| CCA | CPM | DACS | CANWBS | AH             | Comment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|-----|------|--------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | 1   | 0    | *      | Can be applied | The device does not natively provide IWB-OWB-ISH<br>attributes, and cache coherency is provided by an<br>override through an SMMU.<br>The value of 1 for CCA shows that boot firmware has<br>configured the SMMU to ensure cache coherency.<br>The OS might apply the allocation hints supplied in AH<br>when overriding the device attributes.<br>A device with this combination of flag values must be<br>behind an SMMU. Therefore, it must have an ID in its<br>array of ID mappings that has an SMMU IORT node as<br>its output reference.                          |

| 1   | 0   | -    | -      | N/A            | Illegal. If CPM is 0, CCA cannot be 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0   | 1   | 0    | *      | Can be applied | The device does not natively provide IWB-OWB-ISH<br>attributes, but cache coherency can be provided by an<br>override through an SMMU.<br>The OS can provide cache coherency by using an<br>SMMU to override the device attributes to IWB-OWB-<br>ISH. In this case, the OS might apply the allocation<br>hints supplied in AH when overriding the device<br>attributes.<br>A device with this combination of flag values must be<br>behind an SMMU. Therefore, it must have an ID in its<br>array of ID mappings that has an SMMU IORT node as<br>its output reference. |

| 0   | 1   | 1    | -      | Can be applied | Illegal. If the device has a coherent path to memory,<br>and natively outputs IWB-OWB-ISH attributes then<br>CCA must be set to 1.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0   | 0   | *    | 0      | N/A            | The device is not coherent and cannot be made<br>coherent.<br>If the CPU maps memory that is shared with the<br>device as IWB-OWB-ISH, cache maintenance is<br>required. If the CPU maps the memory as Non-<br>cacheable, then no cache maintenance is required.                                                                                                                                                                                                                                                                                                         |

| 0   | 0   | *    | 1      | N/A            | Coherency of accesses made by this device to<br>locations in Conventional memory are ensured as<br>described in the CANWBS flag description.<br>If the CPU maps memory that is shared with the<br>device as IWB-OWB-ISH, cache maintenance is not<br>required. If the CPU maps the memory as Non-<br>cacheable, then no cache maintenance is required.                                                                                                                                                                                                                   |

Appendix B describes how an OS can use this information and when caching operations are required.

The following sections describe IORT nodes for SMMUs, ITS groups, named components, and root complexes.

## 3.1.1 IORT node types

The following sections describe each type of IORT node.

### 3.1.1.1 SMMUv1 or SMMUv2 node

This section describes the format of the IORT node for SMMUv1 or SMMUv2.

| Field                                   | Byte<br>Length | Byte<br>Offset | Description                                                                                                                                                                                                                                                                                                            |  |  |

|-----------------------------------------|----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Туре                                    | 1              | 0              | This field has a value of 3 for SMMUv1 or SMMUv2.                                                                                                                                                                                                                                                                      |  |  |

| Length                                  | 2              | 1              | The length of the node.                                                                                                                                                                                                                                                                                                |  |  |

| Revision                                | 1              | 3              | 3                                                                                                                                                                                                                                                                                                                      |  |  |

| Identifier                              | 4              | 4              | Unique identifier for this node that can be used to locate it in the parent table.                                                                                                                                                                                                                                     |  |  |

| Number of ID mappings                   | 4              | 8              | The number of ID mappings.                                                                                                                                                                                                                                                                                             |  |  |

| Reference to ID Array                   | 4              | 12             | Offset from the start of the IORT node to the start of its Array of ID mappings.                                                                                                                                                                                                                                       |  |  |

| SMMUv1/2 specific data.                 |                |                |                                                                                                                                                                                                                                                                                                                        |  |  |

| Base address                            | 8              | 16             | The SMMU base address.                                                                                                                                                                                                                                                                                                 |  |  |

| Span                                    | 8              | 24             | The length of the memory range that is covered by SMMU memory-mapped IO.                                                                                                                                                                                                                                               |  |  |

| Model                                   | 4              | 32             | <ul> <li>Possible values are:</li> <li>0: Generic SMMUv1.</li> <li>1: Generic SMMUv2.</li> <li>2: Arm Corelink<sup>™</sup> MMU-400.</li> <li>3: Arm Corelink<sup>™</sup> MMU-500.</li> <li>4: Arm Corelink<sup>™</sup> MMU-401.</li> <li>5: Cavium ThunderX SMMUv2.</li> <li>All other values are reserved.</li> </ul> |  |  |

| Flags                                   | 4              | 36             | The SMMU flags. See Table 10.                                                                                                                                                                                                                                                                                          |  |  |

| Reference to Global<br>Interrupt Array  | 4              | 40             | The offset from the start of this IORT node to the start of its global interrupt array section.                                                                                                                                                                                                                        |  |  |

| Number of context interrupts            | 4              | 44             | The number of context interrupts.                                                                                                                                                                                                                                                                                      |  |  |

| Reference to Context<br>Interrupt Array | 4              | 48             | The offset from the start of this IORT node to the start of its context interrupt array section.                                                                                                                                                                                                                       |  |  |

| Number of PMU<br>interrupts             | 4              | 52             | The number of PMU Interrupts.                                                                                                                                                                                                                                                                                          |  |  |

| Reference to PMU<br>Interrupt Array     | 4              | 56             | The offset from the start of this IORT node to the start of its PMU interrupt array section.                                                                                                                                                                                                                           |  |  |

| Global Interrupt Array section          |                |                |                                                                                                                                                                                                                                                                                                                        |  |  |

| SMMU_NSglrpt                            | 4              |                | The GSIV of the SMMU_NSgIrpt interrupt. This field has a value of 0 if not implemented.                                                                                                                                                                                                                                |  |  |

| SMMU_NSgIrpt<br>interrupt flags         | 4              |                | The SMMU_NSgIrpt interrupt flags. See Table 11.                                                                                                                                                                                                                                                                        |  |  |

| SMMU_NSgCfgIrpt                         | 4              |                | The GSIV of the SMMU_NSgCfgIrpt interrupt. This field has a value of 0 if not implemented.                                                                                                                                                                                                                             |  |  |

#### Table 9 Node format for SMMUv1 or SMMUv2