# Arm<sup>®</sup> Realm Management Extension (RME) System Architecture

Document numberARM DEN 0129Document qualityEACDocument versionB.aDocument confidentialityNon-confidential

Copyright © 2021-2023 Arm Limited or its affiliates. All rights reserved.

# Arm® Realm Management Extension (RME) System Architecture

## **Release information**

| Date        | Version | Changes                                                                                                                               |

|-------------|---------|---------------------------------------------------------------------------------------------------------------------------------------|

| 2023/Nov/10 | B.a     | • Introduces requirements for supporting RME Device Assignment (RME-DA),<br>Memory Encryption Contexts (MEC), and multi-chip systems. |

| 2022/Oct/12 | A.d     | • Updated EAC release.                                                                                                                |

| 2022/Feb/07 | A.c     | • Updated EAC release.                                                                                                                |

| 2021/Nov/02 | A.b     | • Updated EAC release.                                                                                                                |

| 2021/Jun/23 | A.a     | • First EAC publication.                                                                                                              |

## Arm Non-Confidential Document Licence ("Licence")

This Licence is a legal agreement between you and Arm Limited ("**Arm**") for the use of Arm's intellectual property (including, without limitation, any copyright) embodied in the document accompanying this Licence ("**Document**"). Arm licenses its intellectual property in the Document to you on condition that you agree to the terms of this Licence. By using or copying the Document you indicate that you agree to be bound by the terms of this Licence.

"**Subsidiary**" means any company the majority of whose voting shares is now or hereafter owner or controlled, directly or indirectly, by you. A company shall be a Subsidiary only for the period during which such control exists.

This Document is **NON-CONFIDENTIAL** and any use by you and your Subsidiaries ("Licensee") is subject to the terms of this Licence between you and Arm.

Subject to the terms and conditions of this Licence, Arm hereby grants to Licensee under the intellectual property in the Document owned or controlled by Arm, a non-exclusive, non-transferable, non-sub-licensable, royalty-free, worldwide licence to:

- (i) use and copy the Document for the purpose of designing and having designed products that comply with the Document;

- (ii) manufacture and have manufactured products which have been created under the licence granted in (i) above; and

- (iii) sell, supply and distribute products which have been created under the licence granted in (i) above.

# Licensee hereby agrees that the licences granted above shall not extend to any portion or function of a product that is not itself compliant with part of the Document.

Except as expressly licensed above, Licensee acquires no right, title or interest in any Arm technology or any intellectual property embodied therein.

THE DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. Arm may make changes to the Document at any time and without notice. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

NOTWITHSTANING ANYTHING TO THE CONTRARY CONTAINED IN THIS LICENCE, TO THE FULLEST EXTENT PETMITTED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, IN CONTRACT, TORT OR OTHERWISE, IN CONNECTION WITH THE SUBJECT MATTER OF THIS LICENCE (INCLUDING WITHOUT LIMITATION) (I) LICENSEE'S USE OF THE DOCUMENT; AND (II) THE IMPLEMENTATION OF THE DOCUMENT IN ANY PRODUCT CREATED BY LICENSEE UNDER THIS LICENCE). THE EXISTENCE OF MORE THAN ONE CLAIM OR SUIT WILL NOT ENLARGE OR EXTEND THE LIMIT. LICENSEE RELEASES ARM FROM ALL OBLIGATIONS, LIABILITY, CLAIMS OR DEMANDS IN EXCESS OF THIS LIMITATION.

This Licence shall remain in force until terminated by Licensee or by Arm. Without prejudice to any of its other rights, if Licensee is in breach of any of the terms and conditions of this Licence then Arm may terminate this Licence immediately upon giving written notice to Licensee. Licensee may terminate this Licence at any time. Upon termination of this Licence by Licensee or by Arm, Licensee shall stop using the Document and destroy all copies of the Document in its possession. Upon termination of this Licence, all terms shall survive except for the licence grants.

Any breach of this Licence by a Subsidiary shall entitle Arm to terminate this Licence as if you were the party in breach. Any termination of this Licence shall be effective in respect of all Subsidiaries. Any rights granted to any Subsidiary hereunder shall automatically terminate upon such Subsidiary ceasing to be a Subsidiary.

The Document consists solely of commercial items. Licensee shall be responsible for ensuring that any use, duplication or disclosure of the Document complies fully with any relevant export laws and regulations to assure that the Document or any portion thereof is not exported, directly or indirectly, in violation of such export laws.

This Licence may be translated into other languages for convenience, and Licensee agrees that if there is any conflict between the English version of this Licence and any translation, the terms of the English version of this Licence shall prevail.

The Arm corporate logo and words marked with ® or <sup>TM</sup> are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may

be the trademarks of their respective owners. No licence, express, implied or otherwise, is granted to Licensee under this Licence, to use the Arm trade marks in connection with the Document or any products based thereon. Visit Arm's website at http://www.arm.com/company/policies/trademarks for more information about Arm's trademarks.

The validity, construction and performance of this Licence shall be governed by English Law.

Copyright © 2021-2023 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-21585 version 4.0

### **Product Status**

The information in this document is final, that is for a developed product.

The information in this Manual is at EAC quality, which means that all features of the specification are described in the manual.

## Contents

## Arm<sup>®</sup> Realm Management Extension (RME) System Architecture

| Arm <sup>®</sup> Realm Management Extension (RME) System<br>Release information |  |

|---------------------------------------------------------------------------------|--|

| Preface                                                                         |  |

| Conventions                                                                     |  |

| Typographical conventions                                                       |  |

| Numbers                                                                         |  |

| Pseudocode descriptions                                                         |  |

| Assembler syntax descriptions                                                   |  |

| Rules-based writing                                                             |  |

| Content item identifiers                                                        |  |

| Content item rendering                                                          |  |

| Content item classes                                                            |  |

| Additional reading                                                              |  |

|                                                                                 |  |

| Feedback on this book                                                           |  |

| Inclusive terminology commitment                                                |  |

### Part A Overview

| Chapter A1 | Introduction                     |   |

|------------|----------------------------------|---|

| -          | A1.1 Overview                    | 6 |

|            | A1.1.1 Context                   | 6 |

|            | A1.2 Scope and intended audience | 8 |

## Part B Architecture

| Chapter B1 | Identifiers                                |

|------------|--------------------------------------------|

| •          | B1.1 Physical Address Space tag            |

|            | B1.2 Memory Encryption Context Identifier  |

| Chapter B2 | System capabilities                        |

| •          | B2.1 Execution isolation                   |

|            | B2.1.1 Security states                     |

|            | B2.1.2 Security model                      |

|            | B2.2 Memory isolation and protection       |

|            | B2.2.1 Granular PAS filtering              |

|            | B2.2.2 Cache Maintenance                   |

|            | B2.2.3 Main memory (DRAM) protection       |

|            | B2.3 Device isolation and protection       |

|            | B2.3.1 Peripheral isolation                |

|            | B2.3.2 Non-PE requesters (Devices)         |

|            | B2.3.3 Programmable completer-side filters |

|            | B2.3.4 RME Device Assignment               |

|            |                                            |

### Contents

| Chapter B3              | Resources and Components                                             |

|-------------------------|----------------------------------------------------------------------|

| •                       | B3.1 Shielded memory                                                 |

|                         | B3.2 Components                                                      |

|                         | B3.2.1 PE                                                            |

|                         | B3.2.2 SMMU                                                          |

|                         | B3.2.3 Interconnect and caches                                       |

|                         | B3.2.4 Memory Protection Engine System Requirements                  |

|                         | B3.2.5 Trusted System Control Processor                              |

|                         | B3.2.6 PCIe Root Port support for TDISP                              |

|                         | B3.2.7 Root Complex Integrated Endpoint (RCiEP) support for TDISP 48 |

|                         | B3.2.8 MEC support in system components                              |

|                         | B3.3 Resource discovery                                              |

|                         |                                                                      |

| Chapter B4              | System security properties                                           |

|                         | B4.1 Root of Trust Services                                          |

|                         | B4.1.1 Non-volatile storage                                          |

|                         | B4.1.2 Root watchdog 52                                              |

|                         | B4.1.3 Random Number Generator                                       |

|                         | B4.1.4 Cryptographic Services                                        |

|                         | B4.1.5 Hardware Enforced Security                                    |

|                         | B4.2 System isolation properties                                     |

|                         | B4.2.1 System configuration integrity                                |

|                         | B4.2.2 Reporting of critical errors                                  |

|                         | B4.3 RAS                                                             |

|                         | B4.3.1 Confidential information in RAS Error Records                 |

|                         | B4.3.2 RAS Error signaling                                           |

|                         | B4.3.3 RAS for Memory Protection Engine                              |

|                         | B4.4 MPAM                                                            |

|                         | B4.5 MTE                                                             |

|                         |                                                                      |

|                         | B4.6 Side channel resistance                                         |

|                         | B4.6.1 System PMU counters                                           |

|                         | B4.6.2 Fault attacks using signal and power manipulations            |

|                         | B4.7   Architectural differences   62                                |

| Chapter B5              | Power Management                                                     |

|                         | B5.1 System power management                                         |

|                         | B5.1.1 Power states                                                  |

|                         | B5.1.2 PE power management                                           |

|                         | B5.1.3 System and PE-cluster power management                        |

|                         | B5.1.4 System power states                                           |

|                         | B5.2 RME components power management                                 |

| <b>0</b> 1 1 <b>D</b> 0 |                                                                      |

| Chapter B6              | Debug                                                                |

| Chapter B7              | System boot                                                          |

|                         | B7.1 Reset requirements                                              |

|                         | B7.2 RME disable                                                     |

| Chapter B8              | System construction                                                  |

|                         | B8.1 Using RME IP in a legacy system                                 |

|                         |                                                                      |

|                         | B8.1.1 Peripheral isolation in legacy systems                        |

|                         | B8.2 Using legacy IP in an RME system                                |

|                         | B8.3 Memory hot plug                                                 |

|                         | B8.4 Multi-chip systems                                              |

|                         | B8.4.1 Link protection                                               |

|                         | B8.4.2 Multi-chip RME system initialization                          |

|                         |                                                                      |

Contents Contents

| Chapter B9 | Appendix: System flows |                            |    |

|------------|------------------------|----------------------------|----|

|            | B9.1                   | System Initialization flow | 79 |

Glossary

## Preface

This book describes a system architecture for an arm-based system that supports RME. It must be read in conjunction with the *Arm<sup>®</sup> Architecture Reference Manual for A-profile architecture* [1].

Issue B of this book introduces system requirements for supporting RME Device Assignment (RME-DA), Memory Encryption Contexts (MEC), and multi-chip systems.

It is assumed that the reader is familiar with both:

- The Arm A-profile architecture.

- PCI Express (PCIe).

## Conventions

### **Typographical conventions**

The typographical conventions are:

italic

Introduces special terminology, and denotes citations.

### bold

Denotes signal names, and is used for terms in descriptive lists, where appropriate.

### monospace

Used for assembler syntax descriptions, pseudocode, and source code examples.

Also used in the main text for instruction mnemonics and for references to other items appearing in assembler syntax descriptions, pseudocode, and source code examples.

#### SMALL CAPITALS

Used for some common terms like IMPLEMENTATION DEFINED.

Used for a few terms that have specific technical meanings, and are included in the Glossary.

### Red text

Indicates an open issue.

### Blue text

Indicates a link. This can be:

- A cross-reference to another location within the document

- A URL, for example http://developer.arm.com

### **Numbers**

Numbers are normally written in decimal. Binary numbers are preceded by 0b, and hexadecimal numbers by 0x. In both cases, the prefix and the associated value are written in a monospace font, for example 0xFFFF0000. To improve readability, long numbers can be written with an underscore separator between every four characters, for example  $0xFFFF_0000_0000_0000$ . Ignore any underscores when interpreting the value of a number.

### **Pseudocode descriptions**

This book uses a form of pseudocode to provide precise descriptions of the specified functionality. This pseudocode is written in a monospace font. The pseudocode language is described in the Arm Architecture Reference Manual.

### Assembler syntax descriptions

This book contains numerous syntax descriptions for assembler instructions and for components of assembler instructions. These are shown in a monospace font.

## **Rules-based writing**

This specification consists of a set of individual *content items*. A content item is classified as one of the following:

- Declaration

- Rule

- Goal

- Information

- Rationale

- Implementation note

- Software usage

Declarations and Rules are normative statements. An implementation that is compliant with this specification must conform to all Declarations and Rules in this specification that apply to that implementation.

Declarations and Rules must not be read in isolation. Where a particular feature is specified by multiple Declarations and Rules, these are generally grouped into sections and subsections that provide context. Where appropriate, these sections begin with a short introduction.

Arm strongly recommends that implementers read *all* chapters and sections of this document to ensure that an implementation is compliant.

Content items other than Declarations and Rules are informative statements. These are provided as an aid to understanding this specification.

### **Content item identifiers**

A content item may have an associated identifier which is unique among content items in this specification.

After this specification reaches beta status, a given content item has the same identifier across subsequent versions of the specification.

### **Content item rendering**

In this document, a content item is rendered with a token of the following format in the left margin:  $L_{iiiii}$

- *L* is a label that indicates the content class of the content item.

- *iiiii* is the identifier of the content item.

### **Content item classes**

### Declaration

A Declaration is a statement that does one or more of the following:

- · Introduces a concept

- Introduces a term

- Describes the structure of data

- Describes the encoding of data

A Declaration does not describe behavior.

A Declaration is rendered with the label *D*.

### Rule

A Rule is a statement that describes the behavior of a compliant implementation.

A Rule explains what happens in a particular situation.

- A Rule does not define concepts or terminology.

- A Rule is rendered with the label *R*.

### Goal

A Goal is a statement about the purpose of a set of rules.

A Goal explains why a particular feature has been included in the specification.

A Goal is comparable to a "business requirement" or an "emergent property."

A Goal is intended to be upheld by the logical conjunction of a set of rules.

A Goal is rendered with the label *G*.

### Information

An Information statement provides information and guidance as an aid to understanding the specification. An Information statement is rendered with the label *I*.

### Rationale

A Rationale statement explains why the specification was specified in the way it was.

A Rationale statement is rendered with the label X.

### Implementation note

An Implementation note provides guidance on implementation of the specification.

An Implementation note is rendered with the label U.

### Software usage

A Software usage statement provides guidance on how software can make use of the features defined by the specification.

A Software usage statement is rendered with the label S.

## **Additional reading**

This section lists publications by Arm and by third parties.

See Arm Developer (http://developer.arm.com) for access to Arm documentation.

[1] Arm<sup>®</sup> Architecture Reference Manual, for A-profile architecture. (ARM DDI 0487) Arm Ltd.

[2] Arm<sup>®</sup> Confidential Compute Architecture (CCA) Security Model. (ARM DEN 0096) Arm Ltd.

[3] Arm<sup>®</sup> System Memory Management Unit Architecture Specification. (ARM IHI 0070) Arm Ltd.

[4] PCI Express<sup>®</sup> Base Specification Revision 6.1. PCI-SIG.

[5] AMBA<sup>®</sup> AXI Protocol Specification. (ARM IHI 0022) Arm Ltd.

[6] Arm<sup>®</sup> Base System Architecture Platform Design Document. (ARM DEN 0094) Arm Ltd.

[7] Arm<sup>®</sup> Server Base System Architecture Platform Design Document. (ARM DEN 0029) Arm Ltd.

[8] Arm<sup>®</sup> Architecture Reference Manual Supplement, Memory System Resource Partitioning and Monitoring (MPAM), for A-profile architecture. (ARM DDI 0598) Arm Ltd.

[9] Arm<sup>®</sup> CoreSight<sup>™</sup> Performance Monitoring Unit Architecture. (ARM IHI 0091) Arm Ltd.

[10] Arm<sup>®</sup> Power State Coordination Interface. (ARM DEN 0022) Arm Ltd.

## Feedback

Arm welcomes feedback on its documentation.

### Feedback on this book

If you have any comments or suggestions for additions and improvements, please create a ticket at:

• https://support.developer.arm.com.

As part of the ticket, please include:

- The title (Arm® Realm Management Extension (RME) System Architecture).

- The number (ARM DEN 0129 B.a).

- The section name to which your comments apply.

- The rule identifiers to which your comments apply, if applicable.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

### Note

Arm tests PDFs only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the appearance or behavior of any document when viewed with any other PDF reader.

# Inclusive terminology commitment

Arm values inclusive communities. Arm recognizes that we and our industry have used terms that can be offensive. Arm strives to lead the industry and create change.

We believe that this document contains no offensive terms. If you find offensive terms in this document, please contact terms@arm.com.

Part A Overview

## Chapter A1 Introduction

## A1.1 Overview

### A1.1.1 Context

This chapter introduces the Realm Management Extension (RME) system architecture.

The Arm Architecture Reference Manual for A-profile architecture [1] includes specification of the RME architecture for a *Processing Element* (PE), that defines the set of hardware features and properties required for a PE to comply with the Arm Confidential Compute Architecture (CCA).

The Arm CCA enables the construction of protected execution environments called Realms. Realms allow lower-privileged software, such as application or a Virtual Machine to protect its content and execution from attacks by higher-privileged software, such as an OS or a hypervisor.

Higher-privileged software retains the responsibility for allocating and managing the resources that are utilized by a Realm, but cannot access its contents, nor affect its execution flow.

This document describes the required system properties for implementing the RME functionality.

This includes definitions of:

- Concepts and terms of the RME system architecture.

- System resources, capabilities, and components required by the architecture.

- System flows and identifiers.

- Security properties of an RME system.

IP that supports RME complies with the System Architecture defined by this specification.

The RME system architecture is applicable to multiple topologies and platform use-cases, for example Cloud, Mobile, and IoT.

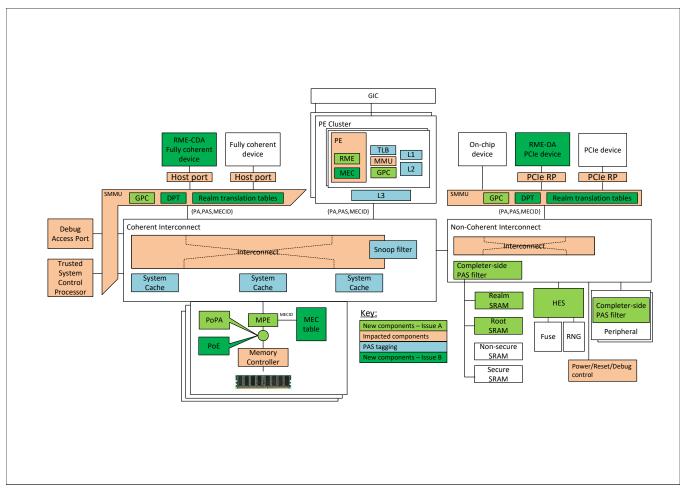

Figure A1.1 provides an example illustration of the RME impact on a representative single-socket system topology.

Figure A1.1: RME System Architecture

## A1.2 Scope and intended audience

This specification forms part of the Arm guide to implementing RME.

The intended audiences for this specification include:

- SoC architects and micro-architects.

- System IP and CPU micro-architects.

- System Firmware developers.

# Part B Architecture

# Chapter B1 Identifiers

This chapter specifies the RME-specific identifiers that are sent in transactions across the system fabric.

## B1.1 Physical Address Space tag

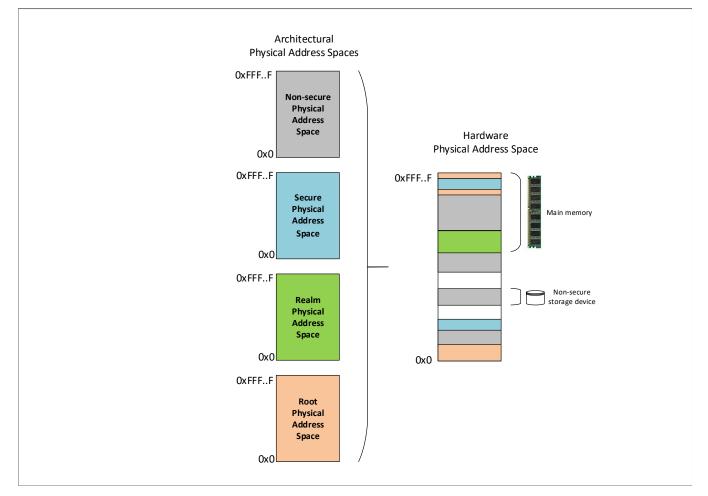

I<sub>TVRTM</sub> An RME memory system supports multiple physical address spaces.

A Physical Address of any memory-mapped Resource in the system (*Hardware Physical Address*) is associated with an architectural *Physical Address Space* (PAS).

I<sub>RZSTK</sub> The following architectural physical address spaces are defined by RME:

- Non-secure PAS.

- Secure PAS.

- Realm PAS.

- Root PAS.

Figure B1.1 illustrates the concept of architectural physical address spaces.

Figure B1.1: Physical Address Spaces

I<sub>HTPJJ</sub> Associating memory-mapped Resources with architectural physical address spaces can be done in several ways:

- The association of a Resource with a PA in one physical address space can make it inaccessible through other physical address spaces.

- For example, main memory in a RME-enabled system is associated this way using the Granule Protection Table.

### Chapter B1. Identifiers B1.1. Physical Address Space tag

- Two distinct Resources can be each assigned to a different PAS while each Resource is accessed through the same PA within that PAS.

- This banked assignment method might be used for peripheral registers.

- In specific cases, a single Resource can be simultaneously accessible through the same PA in multiple physical address spaces.

- For example, peripheral registers in the Secure PAS can be accessible also in the Root PAS.

- Arm strongly recommends that this approach is only used with peripherals, and only with peripherals that are PAS tag-aware.

- I<sub>CWKBT</sub> The Physical Address Space tag (PAS tag) is an Address Space Identifier which permits the forming of multiple physical address spaces in the system. A Physical Address (PA) is associated with a physical address space by qualifying it with a PAS tag.

All accesses are associated with a PAS, which is checked by PAS filters assigned to protect memory resources. Depending on system implementation, requester type, and memory type, this can be the requester-side PAS filter implemented within PEs and System MMUs, referred to as the Granule Protection Check, or a completer-side PAS filter, or a combination of both.

Accesses to a region of memory that can be marked as cacheable retain their associated PAS until reaching the Point of Physical Aliasing (PoPA).

Accesses to a region of memory that cannot be marked as cacheable, for example memory-mapped peripheral registers, retain their associated PAS at least until reaching the PAS filter assigned to protect that region.

A component, for example a peripheral or an interconnect, is said to be *PAS tag-aware* if that component observes the full PAS tag such that it can distinguish between all physical address spaces defined by RME.

## **B1.2 Memory Encryption Context Identifier**

- I<sub>FDJJW</sub> Memory Encryption Contexts (MEC) [1] is an optional RME system feature for encrypting all memory Locations of a Realm, using an encryption context unique to that Realm. In an RME system with MEC, each access to a physical address is assigned a Memory Encryption Context Identifier (MECID), which associates the access with a memory encryption context.

I<sub>JQGRL</sub> Common MECID width is a parameter indicating the number of MECID bits that an RME system supports. It is resolved as the minimal MECID width that all MEC-capable components in the system can support.

- IRPPVXEach physical address space has an independent MECID namespace. In the Realm physical address space, the<br/>usable MECID namespace is from zero to 2<sup>c</sup> common MECID width 1. The Root, Secure and Non-secure physical<br/>address spaces each have one MECID, which is the default MECID of zero.

- IPXJSNFor systems with a high number of concurrently executing Realms, such as in Cloud and Data Center deployments,<br/>Arm recommends a common MECID width of at least 12 bits.

See also:

• B2.2 Memory isolation and protection

# Chapter B2 System capabilities

This chapter specifies the system capabilities required by RME for guaranteeing Arm CCA security and isolation properties for Realms.

## **B2.1 Execution isolation**

An RME system supports the following Security states:

### B2.1.1 Security states

I<sub>QPTSX</sub>

| AT TOW             |                                                                                                                                                                                                                                           |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | • Non-secure.                                                                                                                                                                                                                             |

|                    | <ul><li>Secure.</li><li>Realm.</li></ul>                                                                                                                                                                                                  |

|                    | • Realm.<br>• Root.                                                                                                                                                                                                                       |

| I <sub>cltdc</sub> | The term <i>requester</i> refers to a hardware agent that is capable of initiating accesses. A requester can be a PE or a non-PE agent.                                                                                                   |

| $R_{DFYXL}$        | In an RME system, any access by a requester and any instruction executed by a PE is associated with a single Security state.                                                                                                              |

| I <sub>ljddc</sub> | The Realm Management Extension capability defined in [1] specifies how PE execution context is mapped to Security states.                                                                                                                 |

| I <sub>VHCHD</sub> | RME provides hardware-based isolation that allows execution contexts to run in different Security states and share resources in the system while ensuring that:                                                                           |

|                    | • Execution in the:                                                                                                                                                                                                                       |

|                    | <ul> <li>Realm Security state cannot be observed or modified by an agent associated with either the Non-secure<br/>Security state or the Secure Security state.</li> </ul>                                                                |

|                    | <ul> <li>Secure Security state cannot be observed or modified by an agent associated with either the Non-secure<br/>Security state or the Realm Security state.</li> </ul>                                                                |

|                    | <ul><li>Root Security state cannot be observed or modified by an agent associated with any other Security state.</li><li>Memory assigned to the:</li></ul>                                                                                |

|                    | - Realm Security state cannot be read or modified by an agent associated with either the Non-secure                                                                                                                                       |

|                    | Security state or the Secure Security state.<br>– Secure Security state cannot be read or modified by an agent associated with either the Non-secure                                                                                      |

|                    | Security state or the Realm Security state.                                                                                                                                                                                               |

|                    | <ul><li>Root Security state cannot be read or modified by an agent associated with any other Security state.</li><li>An assignable device interface assigned to the Realm Security state cannot be read or modified by an agent</li></ul> |

|                    | associated with either the Non-secure Security state or the Security state.                                                                                                                                                               |

|                    | • An assignable device interface associated with a VMID in the Realm Security state can only access memory associated with that VMID, or memory associated with the Non-secure Security state.                                            |

|                    | This specification uses the term RME security guarantee to describe the preceding properties.                                                                                                                                             |

| I <sub>JTCVV</sub> | The RME security guarantee applies to a system in the Secured lifecycle state.                                                                                                                                                            |

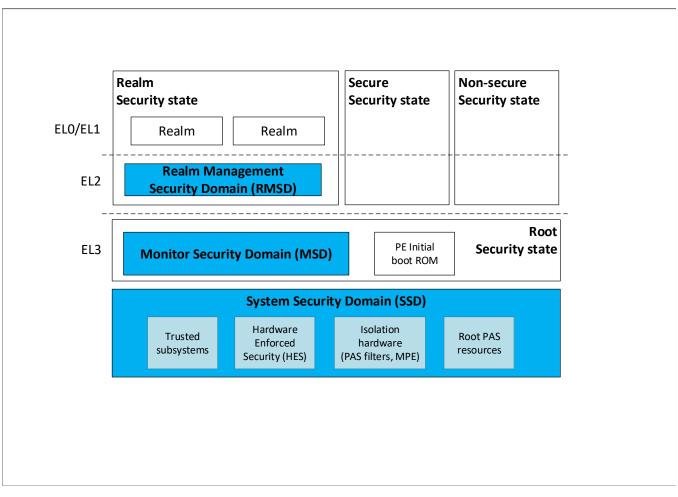

| B2.1.2             | Security model                                                                                                                                                                                                                            |

| I <sub>lydgx</sub> | The Arm CCA System Security Domain (SSD) includes all hardware agents capable of affecting the Arm CCA and RME security guarantees. Examples include isolation hardware and Trusted subsystems.                                           |

| I <sub>PPRLG</sub> | A <i>Trusted subsystem</i> is a system function with private resources, configuration, and firmware that are attestable, for example a Trusted SCP.                                                                                       |

| I <sub>wpqrt</sub> | The Monitor Security Domain (MSD) is updatable PE firmware executing in the Root Security state at EL3 that is responsible for enforcing the Arm CCA and RME security guarantees.                                                         |

| I <sub>YRMHM</sub> | The Realm Management Security Domain (RMSD) is updatable PE firmware executing in the Realm Security state at EL2 that is responsible for enforcing the Arm CCA security guarantee for Realms.                                            |

|                    |                                                                                                                                                                                                                                           |

The terms in this section are formally defined in [2]. Figure B2.1 provides an illustration of the security model.

Chapter B2. System capabilities B2.1. Execution isolation

Figure B2.1: Arm CCA security model

## **B2.2 Memory isolation and protection**

The concept of architecturally-separate physical address spaces enables the formation of robust isolation boundaries for memory protection.

This chapter defines rules for guaranteeing memory isolation using physical address spaces and methods for mapping resources to Security states through these spaces.

IBHZXC

The physical address spaces that can be reached from each Security state are defined in [1] and captured in Table

B2.1, the PAS Access Table:

|                   | Secure state | Non-secure state | Root state | Realm state |

|-------------------|--------------|------------------|------------|-------------|

| PAS[1:0]          |              |                  |            |             |

| 0b00 - Secure     | Yes          | No               | Yes        | No          |

| 0b01 - Non-secure | Yes          | Yes              | Yes        | Yes         |

| 0b10 - Root       | No           | No               | Yes        | No          |

| 0b11 - Realm      | No           | No               | Yes        | Yes         |

### Table B2.1: PAS Access Table

- I<sub>YLXPX</sub> A *Resource* is an addressable physical entity that is formally defined in [1]. A Resource in an RME system is accessible only when it is associated with a *Resource PAS*.

- R<sub>ODWVC</sub> Association of a Resource with a Resource PAS is controlled by either SSD or MSD.

- IJVLCJAssociation of a Resource with a Resource PAS can be set statically by isolation hardware or can change during<br/>runtime, for example by MSD firmware.

- R<sub>BJVZS</sub> An access to a Resource is associated with:

- An Access PAS, in accordance with the PAS Access Table (Table B2.1).

- A MECID, in accordance with the rules specified in [1] and [3].

- ITYMYY

For requesters that access Resources through a stage 1 or stage 2 MMU, assigning the Access PAS in accordance with the PAS Access Table is enforced by MMU SSD hardware.

For requesters that do not access Resources through a stage 1 or stage 2 MMU, such as the Generic Interrupt Controller (GIC) or a Debug Access Port, assigning the Access PAS and MECID in compliance with  $R_{BJVZS}$  is enforced at the requester side by SSD hardware.

SSD hardware is hardware that is either immutable or exclusively controlled by an SSD component, for example a Trusted subsystem.

The PAS tag attached to a request conveys its associated Access PAS.

- I<sub>TFRNC</sub> [1] and [3] define the programming model for setting the Access PAS from each Security state.

- R<sub>YXFMV</sub> A requester that is accessing memory-mapped resources not through a stage 1 or stage 2 MMU/SMMU must support a method that is enforced by SSD hardware for tagging accesses with an Access PAS, in accordance with the PAS Access Table (Table B2.1).

For example:

• A Debug Access Port (DAP) can expose a programming register to an external debugger that allows setting an Access PAS to one of the permitted values, as implied by the debug authentication interface state, for any access that targets main memory or an APB peripheral.

|                    | <ul> <li>then DAP hardware would reject an attempt to program the register to Access PAS == Secure.</li> <li>Furthermore, if the debug authentication interface permits RMSD external debugging then DAP hardware can permit accesses with Access PAS == Realm to specify a programmed MECID.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R <sub>SCDLL</sub> | Once assigned, the value of an Access PAS cannot be altered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| I <sub>JFTJL</sub> | The system must not expose any registers or debug mechanisms that permit the value of an Access PAS to be overridden.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| R <sub>ykvjk</sub> | A <i>PAS filter</i> enforces the PAS protection check by permitting access to a Resource only if the Access PAS matches a Resource PAS associated with that Resource.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| R <sub>MZJXC</sub> | Every requester in the system is subjected to the PAS protection check.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| I <sub>CDDPM</sub> | A requester in this context includes any of the following:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    | <ul> <li>Processing elements (PEs) used by the host operating system or hypervisor to execute user applications or kernel threads.</li> <li>The term <i>application PEs</i> is also used in this specification to make a distinction between processing elements visible to host software and processing elements embedded in system devices.</li> <li>Non-PE requesters that might be fully coherent, IO-coherent, or Non-coherent.</li> <li>This includes any device that supports initiation of a memory access, such as cache prefetchers, the Generic Interrupt Controller (GIC), or a Debug Access Port.</li> <li>Other examples are peripheral devices, including PCIe devices or control processors that might contain non-application PEs.</li> </ul> |

| I <sub>tjrfz</sub> | Certain Trusted requesters comply with the PAS protection check without going through a PAS filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    | <ul> <li>A PAS filter can directly access resources in the Root PAS such as protection tables stored in DRAM.</li> <li>A Memory Protection Engine (MPE) can directly access resources in the Root PAS, such as integrity tags stored in DRAM.</li> <li>Trusted subsystems can directly access peripheral registers or SMEM using a hardwired map that associates resources with the Root PAS.</li> </ul>                                                                                                                                                                                                                                                                                                                                                       |

| I <sub>NDZHH</sub> | The term <i>completer</i> refers to a component that contains Resources and responds to accesses.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| I <sub>hqdwz</sub> | For certain Resources such as peripherals or SMEM, the PAS filter can be located at the completer-side. For other Resources, such as DRAM, a PAS filter must be attached to all requesters that access that Resource. RME system architecture rules guarantee that isolation is maintained in either construction.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| I <sub>VPYFG</sub> | MSD Resources are in the Root PAS and are managed by software running at EL3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| R <sub>wrgtf</sub> | Access to the Root PAS is only permitted for Trusted requesters.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| I <sub>CNYKS</sub> | Trusted requesters are:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

• If the debug authentication interface permits RMSD external debugging but not Secure external debugging

- A PE executing in the Root Security state (EL3).

- Trusted subsystems. For example, a Trusted SCP, or a subsystem hosting HES.

- Memory Protection Engines.

- PAS filters.

```

RMSD Resources are in the Realm PAS and are managed by software running at EL2 in the Realm Security state.

IONNTR

```

The term Resource X is in PAS Y means that Resource X is accessible only in PAS Y unless where the text  ${\tt I}_{\rm FPLKV}$ explicitly permits the Resource to be accessible in more than one PAS.

See also:

• B2.2.1 Granular PAS filtering

### B2.2.1 Granular PAS filtering

# Chapter B2. System capabilities B2.2. Memory isolation and protection

| I <sub>BYTBH</sub> | Granular PAS filtering is the programmable association of a Resource with a PAS at a granularity of a page (Physical Granule).                                                                                                                                                                                                                                                                |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sub>XXXPR</sub> | A Granular PAS filter checks the Access PAS against a Physical Granule Resource PAS as specified in a Granule Protection Table (GPT). If the check fails, the access is aborted and a Granule Protection Fault (GPF) is reported.                                                                                                                                                             |

| R <sub>kgdvk</sub> | A Resource can be associated with a PAS using a Granule Protection Table if the following conditions are met:                                                                                                                                                                                                                                                                                 |

|                    | <ul> <li>There is only a single PA within each PAS through which the Resource can be reached and the value of the PA is the same across all physical address spaces.</li> <li>The Resource can be assigned to a PAS at page granularity.</li> </ul>                                                                                                                                           |

| I <sub>RSGHN</sub> | The term Granule Protection Check (GPC) refers to a requester-side Granular PAS filter as specified by [1] and [3], where such filter can be attached to an MMU or an SMMU.                                                                                                                                                                                                                   |

| I <sub>kqqjg</sub> | GPC is a requester-side PAS filter. By system construction, any access from an application PE or an SMMU-attached requester first goes through a requester-side PAS filter and then can reach a completer-side PAS filter. The programming of the GPT must therefore take into account the potential existence of completer-side PAS filters for specific Resources.                          |

|                    | The Granule Protection Check can be omitted for Resources that are protected by a completer-side PAS filter, and in this scenario the Resource is marked in the GPT as "All Accesses Permitted".                                                                                                                                                                                              |

| I <sub>WVWZP</sub> | MSD guarantees that all requesters subject to the Granule Protection Check observe a consistent view of the Granule Protection Table.                                                                                                                                                                                                                                                         |

| I <sub>hdltb</sub> | The memory encryption rules imply that granule contents are not preserved when the PAS association of a granule is changed. Nevertheless, software cannot rely on the transition of a granule to a new PAS as an implicit scrubbing event and must explicitly scrub granule contents before transitioning the granule to the Non-secure PAS.                                                  |

| $R_{WJNMD}$        | Granule Protection Check for on-chip Resources can only rely on Granule Protection Tables that are stored on-chip or are stored off-chip with equivalent level of integrity and replay protection.                                                                                                                                                                                            |

| R <sub>gqcqt</sub> | A Granule Protection Check that applies to non-idempotent locations does not permit any access to be speculatively performed to a non-idempotent location before the Granule Protection Check for the access is complete.                                                                                                                                                                     |

| I <sub>kymls</sub> | An example for a non-idempotent location is a read-sensitive memory-mapped peripheral register. Speculative read access to non-idempotent memory can result in UNPREDICTABLE behavior. Correspondingly, a system that is using GPC for assigning non-idempotent locations to Realm, Secure, or Root PAS must complete the GPC for any non-idempotent location before permitting access to it. |

| $R_{GFGZM}$        | If a requester-side Granular PAS filter is in reset state, any requester that is associated with it is either in reset state or blocked from accessing memory.                                                                                                                                                                                                                                |

| I <sub>KVHFL</sub> | This permits for a predictable access control behavior when initializing the system.                                                                                                                                                                                                                                                                                                          |

|                    | See also:                                                                                                                                                                                                                                                                                                                                                                                     |

|                    | <ul> <li>B2.3 Device isolation and protection.</li> <li>Chapter B5 Power Management.</li> </ul>                                                                                                                                                                                                                                                                                               |

### B2.2.2 Cache Maintenance

## B2.2.2.1 Point of Physical Aliasing (PoPA)

| I <sub>kwfwg</sub> | The Point of Physical Aliasing (PoPA) is a reference location for cache maintenance operations that is defined in [1]. |

|--------------------|------------------------------------------------------------------------------------------------------------------------|

| R <sub>wfqkd</sub> | A PA that targets memory that can be cached is associated with a PAS until reaching the PoPA.                          |

| R <sub>FRMJJ</sub> | Where a PA is associated with a PAS, any PA compare operation includes the PAS.                                        |

# Chapter B2. System capabilities B2.2. Memory isolation and protection

- I<sub>KHSYM</sub> R<sub>FRMJJ</sub> applies to any cache or snoop filter that is before the PoPA (between the requesters and the PoPA) at any hierarchy level of the system including L1 data and instruction caches. This is needed to maintain the principle of separate physical address spaces as a global security property of the system.

- I<sub>SQJLC</sub> An RME system supports cache maintenance operations to the PoPA in compliance with [1]. The scope of a cache maintenance operation to the PoPA (*PoPA CMO*) is the Outer Shareable shareability domain.

- R<sub>QBNJF</sub> A PoPA CMO affects any cached copy in the system with the specified {PAS, PA} regardless of all of the following:

- The shareability domain it was cached with.

- Whether the system supports a single or multiple Outer Shareable shareability domains.

- The MECID that it was cached with, in a system with MEC.

- $I_{JQSYD}$  As an example, implementations must guarantee that a PoPA CMO sent from one PE affects cache-lines that were allocated as Non-shareable by other PEs. Such a guarantee typically requires snoop filter registration for any allocation into a fully-coherent cache that is located past the Granule Protection Check, regardless of the shareability attribute of the access causing the allocation.

An implementation can support that by having application PEs artificially convert Non-shareable Cacheable accesses to either Inner Shareable Cacheable or Outer Shareable Cacheable but must guarantee that memory consistency and coherency semantics are preserved when other requesters continue to use the Non-shareable attribute when accessing the same Location.

Non-PE requesters can continue using the Non-shareable Cacheable attribute when allocating into a cache that is located before the Granule Protection Check, as later write-backs from such cache always go through a PAS protection check.

### B2.2.2.2 Point of Encryption (PoE)

- I\_VDHGSThe Point of Encryption (PoE) is a reference location for cache maintenance operations, as defined in [1]. An<br/>RME system with MEC supports cache maintenance operations to the PoE in compliance with [1].

- R<sub>TRBZM</sub> An access to a cacheable memory Location is associated with a MECID until reaching the PoE.

- I<sub>CRDLH</sub> When a copy of a Location is allocated into cache, it is stored with the MECID of the allocating access.

- $\mathbb{R}_{KMNQX}$  Memory accesses resulting from a cache Clean operation, due to cache maintenance operations and natural evictions, use the MECID that the entry was cached with.

### B2.2.3 Main memory (DRAM) protection

### B2.2.3.1 Memory encryption and integrity

I<sub>FPJXZ</sub> There are several memory encryption and integrity schemes that are applicable to an RME system.

The baseline encryption requirement is supporting encryption for external memory, using a separate encryption key or tweak for each PAS and providing spatial isolation using an address tweak. RME prevents runtime software access to ciphertext in external memory, in accordance with [2].

Cryptographic memory integrity and freshness are additional, threat-model dependent, capabilities for complying with the Arm CCA security guarantees as specified in [2].

This specification uses the term Memory Protection Engine (MPE) to describe the component that provides external memory encryption and integrity services.

A taxonomy of memory protection schemes that can be used with an Arm CCA system is defined in [2].

- R<sub>MLFBL</sub> External memory assigned to Secure PAS, Realm PAS, or Root PAS must be encrypted using a method that provides at least all the following:

- A unique encryption context for each PAS.

# Chapter B2. System capabilities B2.2. Memory isolation and protection

- A unique address tweak for each encryption data block, such as a 128-bit memory block.

- If cryptographic memory integrity is not supported, an encryption mode that ensures bit diffusion over an encryption data block.

- In a system with MEC, a different encryption context for each MECID in the Realm PAS.

- R<sub>MYWVB</sub> Data is encrypted before being written to external memory or to any shared cache that resides past the PoPA. In a system with MEC, data is encrypted before being written to external memory or to any shared cache that resides past the PoE.

- I<sub>JMZJK</sub> In a system with MEC, MECIDs identify encryption contexts such as encryption keys or tweaks, that might be stored in MECID-indexed tables or MECID-tagged caches.

- R<sub>RQZBK</sub> Memory-mapped data structures that store encryption contexts must reside in SMEM in the Root PAS, such as MSD SMEM.

See also:

• B3.2.4 Memory Protection Engine System Requirements.

### B2.2.3.2 DRAM scrubbing

- IDGWPKThe term *scrubbing* is used in this specification to describe an operation that guarantees that the previous contents<br/>of a memory location are no longer readable.

- I<sub>MLKLZ</sub> The term ECC-scrubbing is used to describe the operation of refreshing DRAM ECC state.

- $I_{KQPGL}$  On system boot, memory that could have been assigned to Secure PAS, Realm PAS, or Root PAS must be scrubbed before any requester that is not a *Trusted requester* is granted access to that memory. Because an RME system supports memory encryption, scrubbing is performed implicitly by resetting all stored copies of the memory encryption key on an RME system reset.

- R<sub>BNSQB</sub> An ECC-scrubbing engine located after the PoPA must not leak confidential information, for example through error record registers.

See also:

• B4.3 RAS.

## **B2.3** Device isolation and protection

MMU-attached Granule Protection Checks are applicable to Normal memory and Device memory. This system capability can be augmented with PAS filters on the completer side for isolating specific Resources. For example, a completer-side PAS filter might be useful where protection at register granularity is required or where it is required immediately after reset for an SSD resource.

- R<sub>GDVSZ</sub> A PA of an access to a memory-mapped peripheral is associated with a PAS until reaching the PAS filter assigned to protect the peripheral.

- IQXXCQFor memory-mapped peripherals that are not protected by a completer-side PAS filter the PAS tag can be stripped<br/>at an IMPLEMENTATION DEFINED location. For example, a PAS tag of an access to a PCIe memory-mapped<br/>peripheral can be stripped at the Root Port.

### B2.3.1 Peripheral isolation

- I<sub>SKDDD</sub> A peripheral can include a private completer-side PAS filter for autonomously controlling access to its memory-mapped registers.

- R<sub>DVPGT</sub> A private PAS filter allows access to a register only if the Access PAS matches a Resource PAS that the register is associated with.

- I<sub>LDBCM</sub> A peripheral might associate a memory-mapped register with multiple physical address spaces, for example to expose different values to software in different Security states. In such a case, the PAS filter allows access to the register from multiple physical address spaces.

- I<sub>FLNFT</sub> An interconnect can include a PAS filter for controlling access to completer nodes that are not PAS-aware.

- $I_{TKRBJ}$  For example, an interconnect can be configured to assign an attached device to a specific PAS, and block any accesses to that device unless they use the correct PAS.

### B2.3.2 Non-PE requesters (Devices)

The term *Non-PE requester* as defined in I<sub>CDDPM</sub> is a generic term for describing DMA-capable system components, for example PCIe devices, interrupt controllers and control processors.

R<sub>RHBJN</sub> The Security state of a non-PE requester in an RME system can be one of the following:

- Non-secure.

- Secure.

- Realm, if the system supports RME Device Assignment (RME-DA) and the requester is a *TEE Device Interface* (TDI) in the *RUN* TDISP [4] state.

- Root, if the requester is a Trusted subsystem.

- I\_CPKZTThe Security state of a non-PE requester defines which PA spaces it is allowed to access, in accordance with the<br/>PAS Access Table (Table B2.1).

- I<sub>CRPCL</sub>

An RME system can include non-PE requesters which are fully coherent and therefore capable of emitting snoop responses.

- R<sub>MCMSH</sub> A fully coherent non-PE requester, that is not part of the System Security Domain (SSD), will not observe coherency traffic for addresses in the Secure, Realm, or Root PAS.

- I<sub>PPVTC</sub> For example, a fully coherent external device that is attached to an RME system over a coherent link must not be able to track access patterns by observing snoop requests in the Secure, Realm or Root PAS. A cache of a coherent non-PE requester that is part of the System Security Domain is permitted to observe snoop requests in any PAS but will not make these requests visible to the hosted context.

### B2.3.3 Programmable completer-side filters

| I <sub>TPLYX</sub> | A completer-side PAS filter can be software programmable. Examples include:                                                                                                                                                                                                              |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | • A completer-side PAS filter that can be programmed to assign memory-mapped portions of a Resource or granules of a Resource to a specific PAS.                                                                                                                                         |

|                    | • A completer-side PAS filter for SMEM that can be programmed to assign an SMEM address range to a                                                                                                                                                                                       |

|                    | <ul><li>specific PAS.</li><li>A completer-side PAS filter on an interconnect port that can be programmed to assign a completer attached</li></ul>                                                                                                                                        |

|                    | to that port to a specific PAS.                                                                                                                                                                                                                                                          |

| R <sub>rgqrt</sub> | If a programmable completer-side PAS filter can assign resources to all physical address spaces then:                                                                                                                                                                                    |

|                    | <ul><li>The registers that control the filter are in the Root PAS.</li><li>On an RME system reset, Resources controlled by the filter are either assigned to the Root PAS or are reset to a known value.</li></ul>                                                                       |

| $R_{GLLZY}$        | If a programmable completer-side PAS filter assigns resources only to the Secure PAS and Non-secure PAS then:                                                                                                                                                                            |

|                    | <ul><li>The registers that control the filter are in the Secure PAS or in the Root PAS.</li><li>On an RME system reset, Resources controlled by the filter are either assigned to the Secure PAS or the Root PAS or are reset to a known value.</li></ul>                                |

| I <sub>TCSGH</sub> | Resources suitable for protection using a completer-side PAS filter include memory-mapped peripherals and on-chip SRAM (SMEM).                                                                                                                                                           |

| B2.3.4             | RME Device Assignment                                                                                                                                                                                                                                                                    |

| I <sub>lfspw</sub> | The term <i>Assignable Device Interface</i> refers to a portion of a device that can be independently assigned to software executing in one of the Security states. An assignable device interface can act as an independent requester and have its own private memory-mapped resources. |

|                    | <i>RME Device Assignment</i> (RME-DA) is an RME system feature that enables the secure assignment of assignable device interfaces to the Realm Security state.                                                                                                                           |

| I <sub>PTDLG</sub> | There is the following related terminology:                                                                                                                                                                                                                                              |

|                    | PCIe refers to devices that comply with the TEE Device Interface Security Protocol (TDISP [4]) as <i>TEE-I/O capable devices</i> . This specification refers to them as <i>TDISP-compliant devices</i> .                                                                                 |

|                    | PCIe uses TEE Device Interface (TDI) to refer to an assignable device interface of TDISP-compliant devices.                                                                                                                                                                              |

|                    | TDISP defines both:                                                                                                                                                                                                                                                                      |

|                    | <ul> <li>A <i>TEE Security Manager</i> (TSM) which is a logical entity at the host that enforces security policies.</li> <li>A <i>Device Security Manager</i> (DSM) which is a logical entity in the device that enforces security policies on the device.</li> </ul>                    |

| R <sub>WBJJT</sub> | TSM functionality in RME-DA is implemented within RMSD.                                                                                                                                                                                                                                  |

| I <sub>XQHNF</sub> | SMMU for RME-DA [3] defines SMMU requirements for supporting the assignment of TDIs to software executing in the Realm Security state.                                                                                                                                                   |

|                    | The RME system architecture defines memory system and PCIe Root Port requirements for supporting the assignment of PCIe TDIs to the Realm Security state.                                                                                                                                |

|                    | B2.3.4.1 Device Permission Table (DPT)                                                                                                                                                                                                                                                   |

| Thurse             | SMMU for RME-DA [3] introduces a Device Permission Table (DPT) that contains permission attributes associated                                                                                                                                                                            |

I<sub>NMXPZ</sub> SMMU for RME-DA [3] introduces a Device Permission Table (DPT) that contains permission attributes associated with physical addresses and specifies a corresponding set of DPT checks that apply to translated accesses from devices.

# Chapter B2. System capabilities B2.3. Device isolation and protection

- R<sub>QRMPD</sub> A translated access from a TDI that is assigned to Realm state is subject to DPT checks, unless where stated otherwise.

- R<sub>PGSTQ</sub> An RME system can include on-chip TDISP-compliant devices that are measured and attested by HES or MSD. For such a device:

- DPT checks can be skipped.

- GPC cannot be skipped.

# Chapter B3 Resources and Components

This chapter outlines properties of system resources and components that are part of an RME system, including systems that support RME-DA or MEC.