# Arm<sup>®</sup> Lifecycle Manager (LCM)

Version 1.0

# Specification

Non-Confidential

Copyright  $\ensuremath{\mathbb{C}}$  2023 Arm Limited (or its affiliates). All rights reserved.

**Issue 01** 107616\_0000\_01\_en

## Arm<sup>®</sup> Lifecycle Manager (LCM)

## Specification

Copyright © 2023 Arm Limited (or its affiliates). All rights reserved.

## **Release information**

#### Document history

| lssue    | Date        | Confidentiality  | Change          |

|----------|-------------|------------------|-----------------|

| 00000-01 | 31 May 2023 | Non-Confidential | Initial release |

## **Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws

and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or ™ are registered trademarks or trademarks of Arm Limited (or its affiliates) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at https://www.arm.com/company/policies/trademarks.

Copyright © 2023 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

(LES-PRE-20349|version 21.0)

## **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

## Feedback

Arm welcomes feedback on this product and its documentation. To provide feedback on the product, create a ticket on https://support.developer.arm.com

To provide feedback on the document, fill the following survey: https://developer.arm.com/ documentation-feedback-survey.

## Inclusive language commitment

Arm values inclusive communities. Arm recognizes that we and our industry have used language that can be offensive. Arm strives to lead the industry and create change.

We believe that this document contains no offensive language. To report offensive language in this document, email terms@arm.com.

# Contents

| 1. Introduction                               | 9  |

|-----------------------------------------------|----|

| 1.1 Conventions                               | 9  |

| 1.2 Useful resources                          |    |

| 1.3 Other information                         |    |

| 2. Terms and Abbreviations                    | 12 |

| 3. LCM overview                               |    |

| 3.1 LCM features and assets                   |    |

| 3.2 Topology                                  | 14 |

| 4. Functional description                     | 16 |

| 4.1 TP mode                                   |    |

| 4.2 Lifecycle states                          |    |

| 4.2.1 Chip Manufacturing LCS                  |    |

| 4.2.2 Device Manufacturing LCS                |    |

| 4.2.3 Secure Enable LCS                       | 22 |

| 4.2.4 Return Merchandise Authorization LCS    |    |

| 4.3 LCM FSM states                            |    |

| 4.3.1 Reset FSM state                         |    |

| 4.3.2 Ready FSM state                         |    |

| 4.3.3 Fatal Error FSM state                   |    |

| 4.4 Hardware keys                             |    |

| 4.4.1 RTL key, KRTL                           |    |

| 4.4.2 HW Unique Key, HUK                      | 34 |

| 4.4.3 Group Unique Key, GUK                   |    |

| 4.4.4 Chip vendor Provisioning key, KP_CM     |    |

| 4.4.5 Chip vendor code encryption key, KCE_CM |    |

| 4.4.6 OEM Provisioning Key, KP_DM             |    |

| 4.4.7 OEM code encryption key, KCE_DM         |    |

| 4.4.8 RoT key export                          |    |

| 4.4.9 OTP keys integrity protection           |    |

| 4.5 OTP manager                               | 41 |

| 4.6 OTP memory map                                                                                                                                                                                                                                                                                                                                                                                                              |               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 4.7 OTP memory masking                                                                                                                                                                                                                                                                                                                                                                                                          |               |

| 4.8 DRBG module                                                                                                                                                                                                                                                                                                                                                                                                                 |               |

| 4.9 Debug Control Unit                                                                                                                                                                                                                                                                                                                                                                                                          |               |

| 4.9.1 DCU in LCM Reset FSM state                                                                                                                                                                                                                                                                                                                                                                                                |               |

| 4.9.2 DCU in LCM Ready FSM state                                                                                                                                                                                                                                                                                                                                                                                                |               |

| 4.9.3 DCU in LCM Fatal Error FSM state                                                                                                                                                                                                                                                                                                                                                                                          |               |

| 4.10 General Purpose Persistent Configuration                                                                                                                                                                                                                                                                                                                                                                                   |               |

| 4.11 Register integrity protection                                                                                                                                                                                                                                                                                                                                                                                              |               |

| 4.12 Hardware interfaces                                                                                                                                                                                                                                                                                                                                                                                                        |               |

| 4.12.1 LCM APB3 subordinate interface                                                                                                                                                                                                                                                                                                                                                                                           |               |

| 4.12.2 OTP APB3 manager interface                                                                                                                                                                                                                                                                                                                                                                                               |               |

| 4.12.3 Direct key APB3 manager interface                                                                                                                                                                                                                                                                                                                                                                                        |               |

| 4.12.4 LCM generic signal interface                                                                                                                                                                                                                                                                                                                                                                                             |               |

| 4.12.5 LFSR seed signal interface                                                                                                                                                                                                                                                                                                                                                                                               |               |

| 4.12.6 Clock interface                                                                                                                                                                                                                                                                                                                                                                                                          |               |

| 4.12.7 Reset interface                                                                                                                                                                                                                                                                                                                                                                                                          |               |

| 4.12.8 Q-Channel interface                                                                                                                                                                                                                                                                                                                                                                                                      |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5.0           |

| 4.12.9 Scan interface                                                                                                                                                                                                                                                                                                                                                                                                           |               |

| <ul><li>4.12.9 Scan interface</li><li>5. Configuration parameters</li></ul>                                                                                                                                                                                                                                                                                                                                                     |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                 | 60            |

| 5. Configuration parameters                                                                                                                                                                                                                                                                                                                                                                                                     | 60            |

| <ol> <li>Configuration parameters</li> <li>Integration requirements</li> </ol>                                                                                                                                                                                                                                                                                                                                                  | 60<br>        |

| <ul><li>5. Configuration parameters</li><li>6. Integration requirements</li><li>7. Signal descriptions</li></ul>                                                                                                                                                                                                                                                                                                                |               |

| <ul> <li>5. Configuration parameters</li> <li>6. Integration requirements</li> <li>7. Signal descriptions</li></ul>                                                                                                                                                                                                                                                                                                             |               |

| <ul> <li>5. Configuration parameters</li></ul>                                                                                                                                                                                                                                                                                                                                                                                  |               |

| <ul> <li>5. Configuration parameters</li></ul>                                                                                                                                                                                                                                                                                                                                                                                  | <b>60</b><br> |

| <ul> <li>5. Configuration parameters</li></ul>                                                                                                                                                                                                                                                                                                                                                                                  |               |

| <ul> <li>5. Configuration parameters</li></ul>                                                                                                                                                                                                                                                                                                                                                                                  |               |

| <ul> <li>5. Configuration parameters</li></ul>                                                                                                                                                                                                                                                                                                                                                                                  | <b></b>       |

| <ul> <li>5. Configuration parameters.</li> <li>6. Integration requirements.</li> <li>7. Signal descriptions.</li> <li>7.1 APB3 subordinate interface signals.</li> <li>7.2 OTP APB3 manager interface signals.</li> <li>7.3 Direct key APB3 manager signals.</li> <li>7.4 LCM generic signals.</li> <li>7.5 LFSR seed signals.</li> <li>7.6 Clock logic and reset signals.</li> <li>7.7 Q-Channel interface signals.</li> </ul> | <b></b>       |

| <ul> <li>5. Configuration parameters</li></ul>                                                                                                                                                                                                                                                                                                                                                                                  |               |

| 8.2.1 LCS_VALUE, Lifecycle State Indication register                        | 71  |

|-----------------------------------------------------------------------------|-----|

| 8.2.2 KEY_ERR, Error Status of the OTP Keys register                        | 72  |

| 8.2.3 TP_MODE, Test or Production Mode register                             | 73  |

| 8.2.4 FATAL_ERR, the Fatal Error FSM State register                         | 74  |

| 8.2.5 DM_RMA_LOCK, DM RMA Flag Lock Enable register                         | 75  |

| 8.2.6 SP_ENABLE, Secure Provisioning Enable register                        |     |

| 8.2.7 OTP_ADDR_WIDTH, OTP Address Width Parameter Value register            | 77  |

| 8.2.8 OTP_SIZE_IN_BYTES, OTP Memory Size in Bytes register                  | 78  |

| 8.2.9 GPPC, General Purpose Persistent Configuration register               | 79  |

| 8.3 DCU register summary                                                    |     |

| 8.3.1 DCU_EN0, DCU Enable register 0                                        | 81  |

| 8.3.2 DCU_EN1, DCU Enable register 1                                        | 82  |

| 8.3.3 DCU_EN2, DCU Enable register 2                                        | 82  |

| 8.3.4 DCU_EN3 DCU Enable register 3                                         | 83  |

| 8.3.5 DCU_LOCK0, DCU Lock register 0                                        | 84  |

| 8.3.6 DCU_LOCK1, DCU Lock register 1                                        | 85  |

| 8.3.7 DCU_LOCK2, DCU Lock register 2                                        | 86  |

| 8.3.8 DCU_LOCK3, DCU Enable register 3                                      | 87  |

| 8.3.9 DCU_SP_DISABLE_MASKO, DCU_SP_DISABLE_MASK Parameter Value register 0  | 87  |

| 8.3.10 DCU_SP_DISABLE_MASK1, DCU_SP_DISABLE_MASK Parameter Value register 1 | 88  |

| 8.3.11 DCU_SP_DISABLE_MASK2, DCU_SP_DISABLE_MASK Parameter Value register 2 | 89  |

| 8.3.12 DCU_SP_DISABLE_MASK3, DCU_SP_DISABLE_MASK Parameter Value register 3 | 90  |

| 8.3.13 DCU_DISABLE_MASKO, DCU_DISABLE_MASK Parameter Value register 0       | 91  |

| 8.3.14 DCU_DISABLE_MASK1, DCU_DISABLE_MASK Parameter Value register 1       | 92  |

| 8.3.15 DCU_DISABLE_MASK2, DCU_DISABLE_MASK Parameter Value register 2       | 93  |

| 8.3.16 DCU_DISABLE_MASK3, DCU_DISABLE_MASK Parameter Value register 3       | 94  |

| 8.4 PID and CID register summary                                            | 95  |

| 8.4.1 PIDR4, Peripheral ID register 4                                       | 95  |

| 8.4.2 PIDRO, Peripheral ID O register                                       | 96  |

| 8.4.3 PIDR1, Peripheral ID 1 register                                       | 97  |

| 8.4.4 PIDR2, Peripheral ID 02 register                                      | 98  |

| 8.4.5 PIDR3, Peripheral ID 03 register                                      | 98  |

| 8.4.6 CIDRO, Component ID 0 register                                        | 99  |

| 8.4.7 CIDR1, Component ID 1 register                                        | 100 |

| 8.4.8 CIDR2, Component ID 2 register                                        | 101 |

| 8.4.9 CIDR3, Component ID 3 register                                        | 102 |

| 8.5 OTP register region                                       | 102 |

|---------------------------------------------------------------|-----|

| A. Software guidelines                                        | 104 |

| A.1 Read lifecycle state routines                             | 104 |

| A.2 Secure provisioning programmer flow                       | 105 |

| A.2.1 Step 1: Transition from Virgin to PCI or TCI TP mode    | 105 |

| A.2.2 Step 2: Transition from CM to DM LCS                    | 106 |

| A.2.3 Step 3: Transition from DM to SE LCS                    | 108 |

| A.2.4 Step 4: Transition from any LCS into RMA (Phase 1 - CM) | 109 |

| A.2.5 Transition from any LCS into RMA (Phase 2 - DM)         | 110 |

| A.2.6 LCM lockdown                                            | 110 |

# 1. Introduction

## 1.1 Conventions

The following subsections describe conventions used in Arm documents.

## Glossary

The Arm Glossary is a list of terms used in Arm documentation, together with definitions for those terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

See the Arm Glossary for more information: developer.arm.com/glossary.

## Typographic conventions

Arm documentation uses typographical conventions to convey specific meaning.

| Convention                 | Use                                                                                                                                                                                                                               |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| italic                     | Citations.                                                                                                                                                                                                                        |

| bold                       | Interface elements, such as menu names.                                                                                                                                                                                           |

|                            | Terms in descriptive lists, where appropriate.                                                                                                                                                                                    |

| monospace                  | Text that you can enter at the keyboard, such as commands, file and program names, and source code.                                                                                                                               |

| monospace <u>underline</u> | A permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.                                                                                                   |

| <and></and>                | Encloses replaceable terms for assembler syntax where they appear in code or code fragments.                                                                                                                                      |

|                            | For example:                                                                                                                                                                                                                      |

|                            | MRC p15, 0, <rd>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></rd>                                                                                                                                                            |

| SMALL CAPITALS             | Terms that have specific technical meanings as defined in the <i>Arm</i> <sup>®</sup> <i>Glossary</i> . For example, <b>IMPLEMENTATION DEFINED</b> , <b>IMPLEMENTATION SPECIFIC</b> , <b>UNKNOWN</b> , and <b>UNPREDICTABLE</b> . |

| Caution                    | Recommendations. Not following these recommendations might lead to system failure or damage.                                                                                                                                      |

| Warning                    | Requirements for the system. Not following these requirements might result in system failure or damage.                                                                                                                           |

| Danger                     | Requirements for the system. Not following these requirements will result in system failure or damage.                                                                                                                            |

| Note                       | An important piece of information that needs your attention.                                                                                                                                                                      |

| Convention | Use                                                                                |

|------------|------------------------------------------------------------------------------------|

| -Ç         | A useful tip that might make it easier, better or faster to perform a task.        |

| Remember   | A reminder of something important that relates to the information you are reading. |

## 1.2 Useful resources

This document contains information that is specific to this product. See the following resources for other useful information.

Access to Arm documents depends on their confidentiality:

- Non-Confidential documents are available at developer.arm.com/documentation. Each document link in the following tables goes to the online version of the document.

- Confidential documents are available to licensees only through the product package.

| Arm product resources                                                                            | Document ID | Confidentiality  |

|--------------------------------------------------------------------------------------------------|-------------|------------------|

| Arm <sup>®</sup> CoreLink <sup>™</sup> SIE-200 System IP for Embedded Technical Reference Manual | DDI 0571    | Non-Confidential |

| Arm architecture and specifications                                                                      | Document<br>ID | Confidentiality      |

|----------------------------------------------------------------------------------------------------------|----------------|----------------------|

| AMBA® APB Protocol Specification                                                                         | IHI 0024       | Non-<br>Confidential |

| Arm <sup>®</sup> Key Management Unit (KMU) Specification                                                 | 107715         | Non-<br>Confidential |

| Arm® Platform Security Architecture Trusted Base System Architecture for Arm®v6-M, Arm®v7-M and Arm®v8-M | DEN 0083       | Non-<br>Confidential |

| Arm® v8-M Architecture Reference Manual                                                                  | DDI 0553       | Non-<br>Confidential |

| Non-Arm resources                                          | Document ID | Organization                                   |

|------------------------------------------------------------|-------------|------------------------------------------------|

| FIPS 140-2 Security Requirements for Cryptographic Modules | FIPS 140-2  | National Institute of Standards and Technology |

Arm tests its PDFs only in Adobe Acrobat and Acrobat Reader. Arm cannot guarantee the quality of its documents when used with any other PDF reader.

Adobe PDF reader products can be downloaded at http://www.adobe.com

## 1.3 Other information

See the Arm website for other relevant information.

- Arm<sup>®</sup> Developer.

- Arm<sup>®</sup> Documentation.

- Technical Support.

- Arm<sup>®</sup> Glossary.

# 2. Terms and Abbreviations

The following table lists the terms and abbreviations used throughout this document.

| Term   | Description                        |

|--------|------------------------------------|

| СМ     | Chip Manufacturer                  |

| DM     | Device Manufacturer                |

| DRBG   | Deterministic Random Bit Generator |

| HW     | Hardware                           |

| НИК    | Hardware unique key                |

| KMU    | Key management unit                |

| LCM    | Lifecycle manager                  |

| LCS    | Lifecycle state                    |

| LFSR   | Linear-Feedback Shift register     |

| NVM    | Non-Volatile Memory                |

| OEM    | Original Equipment Manufacturer    |

| OTP    | One-Time Programmable              |

| PCI    | Production Chip Indicator          |

| PoR    | Power-on reset                     |

| PSA    | Platform security architecture     |

| RAZ/WI | Read as Zero, Write Ignore         |

| RMA    | Return Merchandise Authorization   |

| RoT    | Root-of-Trust                      |

| SE     | Security Enabled                   |

| SoC    | System-on-Chip                     |

| SW     | Software                           |

| ТСІ    | Test Chip Indicator                |

# 3. LCM overview

The Arm<sup>®</sup> Lifecycle Manager (LCM) is a security component that is intended for use in Trusted Execution Environments, such as Armv8-M architectures.

The LCM is aimed at the IoT market or security subsystems that are part of infrastructure, client, or automotive markets. The LCM provides foundational security functions for the system, such as *Root-of-Trust* (RoT) key management, lifecycle management, and Secure debug domain control. These functions allow you to build security services such as Secure boot, Secure firmware update, attestation, Secure storage, and Secure partitioning (for example, Arm Trusted Firmware). The LCM is a critical component for a system that aims for PSA Level 2+ certification.

The LCM hardware core integrates with the hosting platform using APB3 interfaces, including manager ports and a subordinate port. Other interfaces provide more specialized functionality by indicating the current security state of the LCM to the system and controlling the system behavior.

## 3.1 LCM features and assets

The LCM provides the following security features.

- Secure lifecycle states

- Persistent storage of RoT keys

- Secure export of RoT keys through the APB interface.

- Debug control and hardware feature enable signals, with properties dependent on LCS

- OTP programmer (user) partition for read and write access

- Secure provisioning for manufacturer asset provisioning in a Non-trusted environment

The LCM manages the following assets and Roots-of-Trust:

- The Secure lifecycle states, which are encoded and stored securely in the OTP memory

- The device owner's hash of the *Root of Trust Public Key* (ROTPK), which is stored securely in the OTP memory

- The device Hardware Unique Key (HUK)

- The Group Unique Key (GUK)

- A set of two keys owned by the chip vendor, typically used for code encryption and provisioning

- A set of two keys owned by the *Original Equipment Manufacturer* (OEM) typically used for code encryption and provisioning

- General-purpose OTP flags and signals intended to be used by the chip vendor

- An RTL secret key for Secure provisioning in a Non-trusted environment

- An RTL secret mask to protect confidential fields of the OTP memory

- General-purpose OTP memory partition (code or data), which the programmer can use

# 3.2 Topology

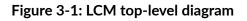

The following top-level figure shows an example system that includes an LCM.

## Lifecycle state and debug control unit

The LCM defines a set of lifecycle states (LCS). The LCM also includes a mechanism for controlling debugging capabilities and HW feature enablement, which is defined by the LCS. For more information, see Lifecycle states and Debug Control Unit.

## **OTP** manager

The LCM includes an OTP manager that is responsible for controlling the OTP assets. The OTP manager uses the OTP APB3 manager interface that is connected to the OTP. For more information, see OTP manager.

## Read Integrity Checker:

Part of the OTP manager. An engine (state machine) that performs integrity checks on the fields in the OTP that are used to store keys and to determine the LCS.

## Key mask

The secret OTP keys are protected using an RTL mask. For more information, see OTP keys integrity protection.

## DRBG

The LCM includes a *Deterministic Random Bit Generator* (DRBG) that is used to generate masking values and random delay values. For more information, see DRBG module.

## LCM APB3 subordinate interface

The LCM includes an APB3 subordinate interface which is used to control the LCM operations, read the LCM FSM state and the LCS, and read and write to the OTP memory. For more information, see LCM APB3 subordinate interface.

## Direct key APB3 manager interface

The LCM includes a direct key APB3 manager interface that exports the LCM keys to an external peripheral for key management. For more information, see Direct key APB3 manager interface.

## Clock, reset

The LCM requires a single clock input and reset signal that is controlled by the system. For more information, see Clock logic and reset signals.

#### Scan

The LCM supports scan cell insertion methodology for SoC DFT strategy. For more information, see Scan signals.

# 4. Functional description

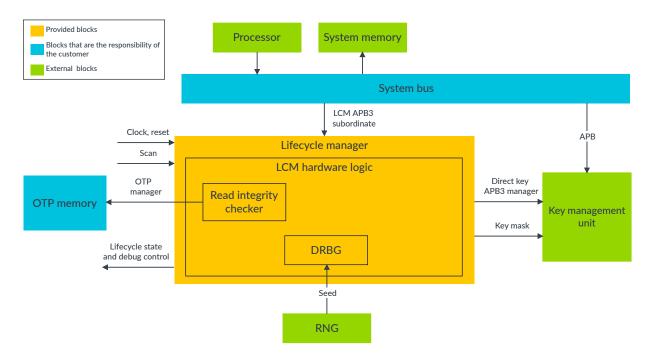

The LCM manages the security of the device by using security modes and states to control its behavior and its debug control capabilities.

The chip vendor first defines the Test or Production Mode (TP mode) of the device, depending on whether the device is intended for testing purposes (TCI TP mode) or is part of a fully secured production batch (PCI TP mode).

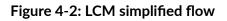

The LCM uses lifecycle states (LCS) to control which features of the device are enabled during the various stages of its life. The chip vendor and the OEM can use Secure provisioning to load their secret keys to the LCM during Chip Manufacturing (CM) LCS and Device Manufacturing (DM) LCS. In Secure Enable LCS Secure provisioning is disabled. Debug features are also disabled in SE LCS, unless the the device is in TCI TP mode. The LCM also includes a Return Merchandise Authorization (RMA) LCS, which is a terminal state for devices that are returned to the manufacturer for analysis of fatal errors.

Within the lifecycle states, the LCM *Finite State Machine* (FSM) uses Reset, Ready, and Fatal Error FSM states to control the behavior of the LCM depending on its internal state and whether any errors have been detected.

The following figure shows the relationships between the security modes and states.

## Figure 4-1: LCM security modes and states

The following figure shows a simplified lifetime flow for a device which includes the LCM. At any point in the lifetime of the device, the LCS can be changed to RMA LCS.

To protect the assets and hardware keys stored in the OTP memory when the device is in PCI TP mode, the LCM uses OTP masking. Keys stored in the OTP memory are further protected with built-in integrity checking functionality.

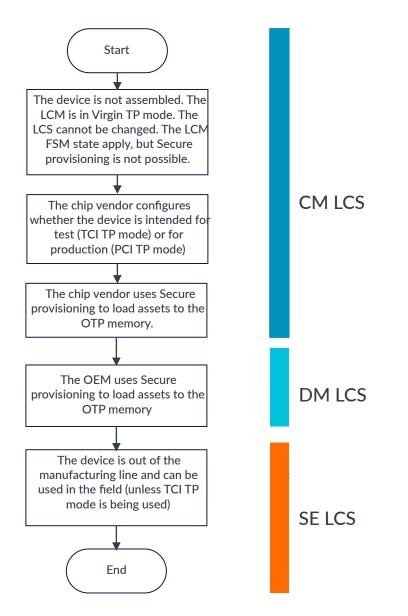

## 4.1 TP mode

The LCM includes a mechanism, *Test or Production Mode* (TP mode), that allows the chip vendor to define whether the chip or device is part of a fully secured production batch or is intended for testing purposes.

The LCM defines the following TP modes.

## Virgin TP mode

The device is in a non-initialized state. The silicon chip is expected to be blank. The OTP memory is expected to be all zeros (empty). As the first step before initiating the key provisioning process, the programmer must set either the TCI or PCI TP mode value in TP mode Configuration OTP memory field. Otherwise, the OTP fields containing the keys and security configurations cannot be programmed.

## Production Chip Indication (PCI) TP mode

The Production Chip Indicator is set. The Secure provisioning functionality of LCM uses the actual secret RTL OTP mask values.

## Test Chip Indication (TCI) TP mode

The Test Chip Indicator is set. The RTL secret key and the and RTL OTP masks are disabled, and their related functionality uses zeros instead of the actual RTL secret values. The Secure provisioning functionality of the LCM can still be used, but with zeroized RTL OTP mask values. For more details on the RTL key, see Hardware keys.

#### Invalid TP mode

When an Invalid TP mode value is written to the OTP memory, the LCM is permanently locked. Debug is disabled. Intentional transition to Invalid TP mode is possible only from Virgin TP mode. For more information, see LCM lockdown. During certain types of attacks, such as electromagnetic interference, the device may appear to be in Invalid TP mode for the duration of the attack. After reset and if the attack is no longer present, the device returns to its previous TP mode, since no permanent change was made to the value written in the OTP memory.

The *Production Chip Indication* (PCI) TP mode and *Test Chip Indication* (TCI) TP mode affect the Secure services and security mitigations that are used for the provisioning of device secret keys.

The following figure shows the transition between the TP modes.

## Figure 4-3: TP mode transitions

The value of the TP mode register is reflected through the tp\_mode output signals as defined in the LCM generic signals. The tp\_mode output must be valid before the lcs\_is\_valid output is asserted. The value of the TP mode register is readable from the APB-S interface and encoded as defined in the TP\_MODE, Test or Production Mode register.

The following table defines the TP mode policies:

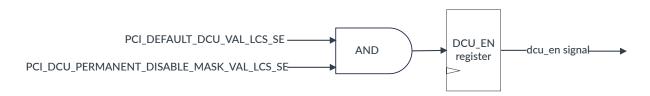

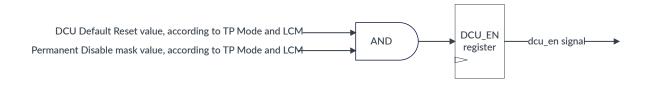

#### Table 4-1: TP mode policies

| TP<br>mode | RTL Key<br>usage                     | RTL<br>mask<br>usage | OTP access to secret keys                                                               | Transition to<br>TCI or PCI          | DCU default reset<br>value                                   | DCU permanent disable<br>mask                                      |

|------------|--------------------------------------|----------------------|-----------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------|

| Virgin     | Disabled                             | Disabled             | OTP write is disabled                                                                   | Can be done<br>to both TCI<br>or PCI | DCUs default value is according to CM LCS.                   | PCI permanent disable<br>mask according to<br>parameter for CM LCS |

| TCI        | Disabled                             | Disabled             | Write or read enabled according to<br>LCS                                               | Disabled                             | TCI default reset value<br>according to parameter<br>for LCS | TCI permanent disable<br>mask according to<br>parameter for LCS    |

| PCI        | Enabled<br>in Secure<br>provisioning | Enabled              | Write or read enabled according<br>to LCS and whether Secure<br>provisioning is enabled | Disabled                             | PCI default reset value<br>according to parameter<br>for LCS | PCI permanent disable<br>mask according to<br>parameter for LCS    |

| Invalid    | Disabled                             | Disabled             | OTP memory write is disabled                                                            | Disabled                             | PCI default reset value is according to SE LCS.              | PCI permanent disable<br>mask according to SE LCS<br>parameter     |

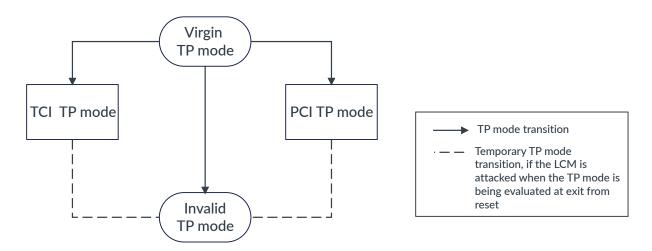

## 4.2 Lifecycle states

The LCM defines four *Lifecycle States* (LCS). The lifecycle states enable the device (both hardware and software) to behave differently in various stages of its life, depending on whether it is in production or in the field. These changes in device behavior protect any security assets after they have been introduced into the device and reduce the risk of IP theft and reverse engineering. The lifecycle states only apply if the TP mode of the device is in Virgin, TCI, or PCI.

The lifecycle states are:

- Chip Manufacturing LCS

- Device Manufacturing LCS

- Secure Enable LCS

- Return Merchandise Authorization LCS

The following figure shows the possible transitions between the lifecycle states.

## Figure 4-4: LCM lifecycle states

The LCM determines the LCS by reading the OTP fields immediately after reset. The LCS must not be affected by any input to LCM, other than the OTP memory-related values. The calculation of the LCS depends on the values of the following fields in OTP memory:

- CM Configuration 1

- CM Configuration 2

- DM Configuration

- CM RMA OTP flag

- DM RMA OTP flag

After the LCS is calculated according to the OTP fields, the LCM stores it in the LCS\_VALUE register.

An integrity error or any invalid LCS state in the OTP memory that does not map to the CM, DM, SE, or RMA lifecycle states, causes the LCM to leave the lcs\_is\_valid signal deasserted and also assert the fatal\_err signal. When the fatal\_err signal is asserted, LCM is disabled, and the keys are invalidated and not exported.

The following table describes how the lifecycle states defined by this specification map to the PSA lifecycle states.

#### Table 4-2: LCM lifecycle states and PSA lifecycle states

| LCM lifecycle state                    | PSA lifecycle state      |

|----------------------------------------|--------------------------|

| Chip Manufacturing (CM)                | Device Assembly and Test |

| Device Manufacturing (DM)              | Provisioning             |

| Secure Enable (SE)                     | Secured                  |

| Return Merchandise Authorization (RMA) | Decommissioned           |

Manufacturing test access is not blocked in the DM LCS.

## 4.2.1 Chip Manufacturing LCS

The *Chip Manufacturing* (CM) LCS indicates the device has, typically, not been assembled into a device yet, and has not left production line of the chip vendor.

In CM LCS, Arm recommends all debugging and testing facilities of the chip are enabled (depending on configuration), even those that enable access to security-sensitive information (for example, chip test modes and validation functionality such as "external NOR-flash in place of boot ROM").

The LCM is in CM LCS by default when it is in Virgin TP mode. To perform Secure provisionming, the programmer must set either the TCI or PCI TP mode value in the TP mode Configuration OTP memory field. The LCM cannot move to DM LCS unless Secure provisioning has been performed.

Transition to the next LCS (DM) is done by programming the OTP memory fields with chip vendorrelated secrets. However, if only some of the CM configuration 1 or CM Configuration 2 bits are set, it is possible for the device to remain in CM LCS without transitioning to DM LCS. The transition to the RMA LCS is done by programming both the CM and the DM RMA OTP flags.

When the device is in CM LCS, the lcs signal indication value is 0b000.

In CM LCS, the following capabilities are enabled:

- Debugging and software development capabilities. These capabilities are configurable and could be restricted.

- External-testing capabilities, such as JTAG boundary scan.

## Conditions

The device is in CM LCS if the following conditions are met on reset in the OTP memory:

- Bits [31:0] of the CM configuration 1 flag (OTP memory offset 0x00E4) are not set.

- Bits [7:0] of the CM configuration 2 glag (OTP memory offset  $0 \times 00 \equiv 8$ ) are not set.

- Bits [15:0] of the DM configuration flag (OTP memory offset 0x00EC) are not set.

- Either the CM RMA OTP flag (OTP memory offset 0x00F0) or the DM RMA OTP flag (OTP memory offset 0x00F4) is not set. For the LCM LCS to change to RMA LCS, both of these flags must be set.

## 4.2.2 Device Manufacturing LCS

The *Device Manufacturing* (DM) LCS is typically used during device assembly on the production line of the OEM.

In the DM LCS, the following capabilities are enabled:

• Debugging and software development capabilities. These capabilities are configurable and could be restricted.

• External-testing capabilities, such as JTAG boundary scan.

Internal testing capabilities (for example, full-chip internal scan) are typically disabled.

Transition to the next lifecycle state (SE) is done by programming the OTP fields with OEM-related secrets. Transition to the RMA lifecycle is done by programming the CM and DM RMA OTP flags.

When the device is in DM LCS, the lcs signal indication value is 0b001.

#### Conditions

The device is in DM LCS if the following conditions are met in the OTP memory on reset:

- Either bits [31:0] of the CM configuration 1 flag (OTP memory offset 0x00E4) are set to a value other than zero or bits [7:0] of the CM configuration 2 glag (OTP memory offset 0x00E8) are set to a value other than zero.

- Bits [15:0] of the DM configuration flag (OTP memory offset 0x00EC) are not set.

- Either the CM RMA OTP flag (OTP memory offset 0x00F0) is not set or the DM RMA OTP flag (OTP memory offset 0x00F4) is not set. For the LCM LCS to change to RMA LCS, both of these flags must be set.

## 4.2.3 Secure Enable LCS

The Secure Enable (SE) LCS is used for devices out of the manufacturing line and in the field.

A device in SE state may freely use all security functions, but its debugging and testing capabilities which are based on the Secure debug are typically fully blocked, unless the LCM is in TCI TP mode.

The only possible transition from SE LCS is into RMA LCS state.

When the device is in SE LCS, the lcs signal indication value is 0b101.

#### Conditions

The device is in SE LCS if the following conditions are met on reset in the OTP memory:

- Either bits [31:0 of CM configuration 1 flag (OTP memory offset 0x00E4) are set to a value other than zero or bits [7:0 of CM configuration 2 flag (OTP memory offset 0x00E8) are set to a value other than zero.

- Bits [15:0] of DM configuration flag (OTP memory offset 0x00EC) are set to a value other than zero.

- Either the CM RMA OTP flag (OTP memory offset 0x00F0) is not set or the DM RMA OTP flag (OTP memory offset 0x00F4) is not set. For the LCM LCS to change to RMA LCS, both of these flags must be set.

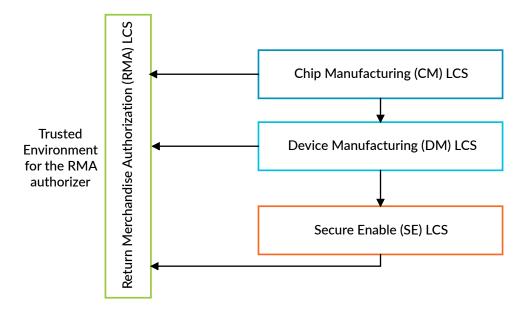

## 4.2.4 Return Merchandise Authorization LCS

The *Return Merchandise Authorization* (RMA) lifecycle state is a terminal state for devices that are returned to the manufacturer for analysis of fatal errors.

When a device is put into RMA state, it loses its secret keys and therefore its ability to perform most security functions. However, depending on the partner's use of the PERMANENT\_DISABLE\_MASK\_VAL\_LCS\_RMA configuration parameters, the device may regain full access to all debugging and testing capabilities. For more information, see Configuration parameters.

Any RMA Flag value that is different than all zeroes or all ones causes the LCM to leave the lcs\_is\_valid signal deasserted and assert the fatal\_err signal.

When the device is in RMA LCS, the lcs signal indication value is 0b111.

## Conditions

The device is in RMA LCS if both of the following conditions are met on reset in the OTP memory:

- The CM RMA OTP flag (OTP memory offset 0x00F0) is set to all ones.

- The DM RMA OTP flag (OTP memory offset 0x00F4) is set to all ones.

## 4.2.4.1 Transition into RMA LCS

The LCM supports a two-phase RMA LCS transition to allow both the chip vendor and the OEM to be involved in the RMA transition. RMA LCS is set only if the CM RMA OTP flag and the DM RMA OTP flags are set. One flag is programmed by the chip vendor and the other by the OEM.

The chip vendor can lock the DM RMA OTP flag using the DMA\_RMA\_LOCK register. The OEM can set the DM RMA OTP flag only if it was not locked by the chip vendor in advance. For security reasons, the DM RMA OTP flag should only be unlocked after successful authorization by the chip vendor boot loader code.

The DM RMA OTP flag lock feature prevents unauthorized transitions into RMA LCS.

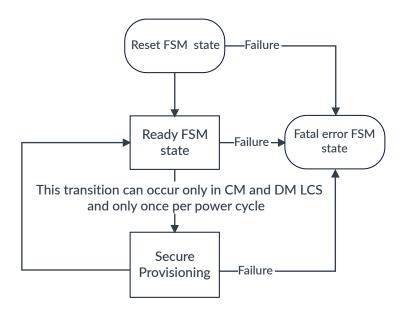

## 4.3 LCM FSM states

The LCM *Finite State Machine* (FSM) transitions between three FSM states depending on whether the device is reset, operational, or if an error has been detected. The FSM checks the values stored in the LCM OTP memory are correct.

## Reset FSM state

Reset FSM state occurs after LCM performs a Cold reset. The transition between Reset FSM state and Ready FSM state forms the LCM start-up flow.

## Ready FSM state

Ready FSM state is is the default FSM state once the LCM start-up flow is completed. Once for each power cycle, the LCM can transition from Ready FSM state to Secure provisioning. However, the transition from Ready FSM state to Secure provisioning can only happen in CM or DM LCS.

## Fatal Error FSM state

Fatal Error FSM state is triggered by the LCM FSM or can by initiated by software. In Fatal Error FSM state, writes to the LCM are disabled.

The FSM states are different from the LCS states. Reset, Ready, and Fatal Error FSM states refer to the operation of the LCM, not necessarily the system as a whole. They can occur when the device is in CM, DM, SE, or RMA LCS.

Figure 4-5: LCM FSM states on page 24 provides a high-level overview of the possible transitions between the different FSM states. The FSM transitions are triggered by the FSM itself except the transition to Secure provisioning, which is controlled by software.

The LCM FSM can also move to Fatal Error FSM state, when the programmer sets the FATAL\_ERR register to the FATAL\_ERR\_SET value (0xFA7A\_1EEE) through the APB-S interface.

## Figure 4-5: LCM FSM states

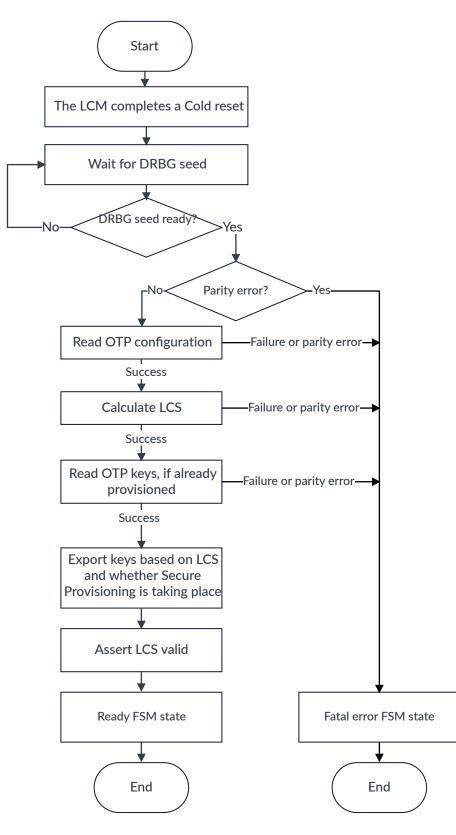

## 4.3.1 Reset FSM state

Reset FSM state occurs when the LCM completes a Cold reset. On reset, regardless of the LCS, the LCM copies the 16b *General Purpose Persistent Configuration* (GPPC) field from the OTP memory to the GPPC register. The GPPC register reflects its value at the GPPC signals interface.

Reset FSM state occurs in all lifecycle states. The LCM can transition from Reset FSM state either to Ready FSM state or to Fatal Error FSM state. The transition between Reset FSM state and Ready FSM state forms the LCM start-up flow.

The following figure shows the high-level flow of Reset FSM state, which is triggered when the LCM completes Cold reset.

## Figure 4-6: LCM Reset FSM state

Copyright  $\ensuremath{\mathbb{C}}$  2023 Arm Limited (or its affiliates). All rights reserved. Non-Confidential

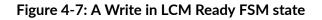

## 4.3.2 Ready FSM state

Once LCM start-up flow is complete, the LCM is in Ready FSM state.

The Ready FSM state can occur in all lifecycle states. After a successful read or write, the LCM remains in Ready FSM state. Transition to Fatal Error FSM state occurs if there is a parity mismatch, or if the internal register duplication compare fails, or if the programmer sets the FATAL\_ERR register to the FATAL\_ERR\_SET value (0xFA7A 1EEE).

The following figure shows a high-level flow for a Write in Ready FSM State.

For more information about the transition between Ready FSM state and Secure provisioning, see Secure provisioning.

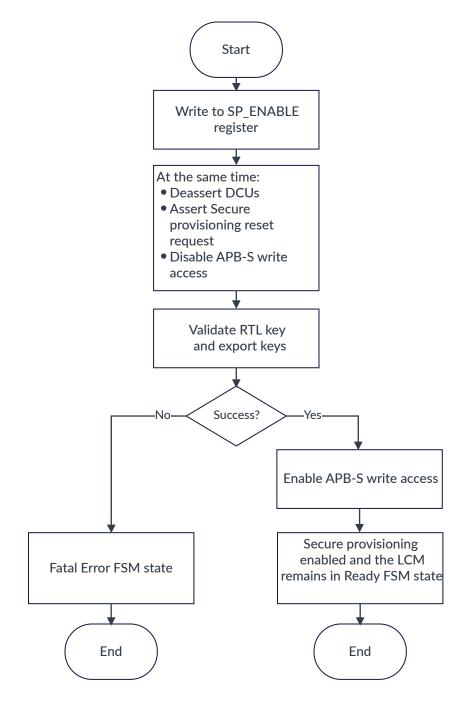

## 4.3.2.1 Secure provisioning

The LCM allows the chip vendor and OEM to provision their assets into the OTP memory in an untrusted environment, for example during production.

Once for each power cycle, the LCM can transition from Ready FSM state to Secure provisioning. However, the transition from Ready FSM state to Secure provisioning can only happen in CM or DM LCS.

The LCM includes a Secure provisioning reset request signal, sp\_rst\_req, to indicate to the system that Secure provisioning was enabled.

If the provisioning environment is not Trusted, the LCM provides an RTL group key that can be used to protect the assets. The RTL key is usable and exported only after Secure provisioning is enabled and only if the LCM is in PCI TP mode. The RTL key is protected by the LCM, which does not allow the scan interface and the debug interface to access it.

To enable the RTL key and initiate the Secure provisioning flow, the programmer should set the SP\_ENABLE register to the specified value (0x5EC1\_0E1E) from the APB-S interface. The LCM asserts the sp\_rst\_req interface signal, validates the KRTL HW key, and exports all valid keys by writing to the direct key APB interface. The LCM then enables Secure provisioning with the DCU settings deasserted according to value of the DCU\_SP\_DISABLE\_MASK\_VAL configuration parameter in PCI TP mode. If no errors occur, lcs\_is\_valid remains asserted.

The sp\_rst\_req signal remains asserted when LCM Secure provisioning is enabled until the next reset cycle.

After a Secure provisioning reset request, Arm expects that all software returns to the most Trusted boot loader state, for example, the ROM bootloader. Following the reset request, the LCM reexports all valid keys through the direct key APB3 manager interface.

The following figure shows the behavior of the LCM in Secure provisioning.

## **Related information**

Secure provisioning programmer flow on page 105 RoT key export on page 39 Hardware keys on page 32 Direct key APB3 manager interface on page 56

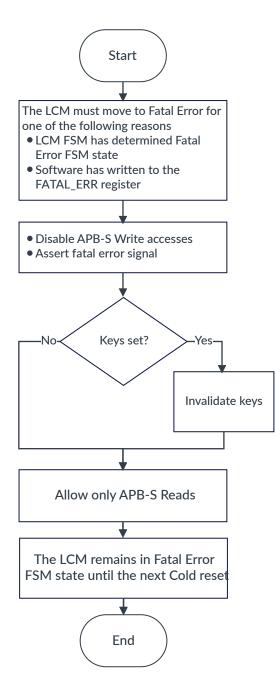

## 4.3.3 Fatal Error FSM state

Fatal Error FSM state is triggered by the LCM FSM or can be initiated by software. When the LCM is in Fatal Error FSM satate, the fatal\_err signal is asserted. A fatal error does not always trigger SW to transition the device to RMA LCS. A reset of the device may recover the LCM, if the fatal error has been caused by a transient fault.

Fatal Error FSM state can occur in all LCS states.

The LCM determines a Fatal Error FSM state, if one of the following conditions applies:

- The OTP read integrity check fails

- The internal register parity check fails

- The internal register duplication compare fails

- The lifecycle state is invalid

- The TP Mode state is invalid.

If the programmable FATAL\_ERR\_EN field in the FATAL\_ERR register is set to FATAL\_ERR\_SET value or the LCM enters Fatal Error FSM state, the following actions are taken:

- All keys are invalidated

- The fatal\_err signal is asserted

- APB-S write transactions return a bus error

- The LCM remains in Fatal Error FSM and it cannot change its FSM state until Cold reset

In Fatal Error FSM state, all LCM indications are treated as invalid. The lcs\_is\_valid signal indication remains asserted. Reads are permitted in Fatal Error FSM state.

The following figure shows the behaviors occuring when the LCM moves to Fatal Error FSM state.

## Figure 4-9: LCM Fatal Error FSM state

## 4.4 Hardware keys

The LCM hardware embedded secret keys are stored in the OTP memory, except for one key stored in RTL. Only the LCM can access the OTP and RTL keys until they are exported through

Copyright © 2023 Arm Limited (or its affiliates). All rights reserved. Non-Confidential

the direct key manager interface, where they are managed by a dedicated module, such as a *Key Management Unit* (KMU) or cryptographic engine.

On reset and after determining the lifecycle status:

- The LCM copies the OTP keys into the HW key shadow registers, according to the conditions defined in the Table 4-4: OTP memory map on page 42. The LCM includes HW key shadow registers for all OTP and RTL keys as defined in Table 4-3: HW Keys on page 33.

- All valid key registers are exported through the direct key APB3 manager interface before the lcs\_is\_valid signal is asserted, according to the conditions described in the Table 4-3: HW Keys on page 33. Invalid key registers should not be exported through the direct key APB3 manager interface.

When the FATAL\_ERR register is set to FATAL\_ERR\_SET value by the programmer through the APB-S interface, all the LCM key registers are invalidated and zeroized.

When the fatal\_err signal is asserted by the LCM, the OTP keys are not copied to the HW key shadow registers and if they have already been copied, the key registers are invalidated and zeroized.

The following assets must not be accessible through the APB-S interface or leak to any other blocks other than the LCM HW key shadow registers:

- HW keys in OTP memory

- HW key shadow registers

- RTL key (KRTL)

If the unmasked OTP key is all ones or all zeros:

- The LCM does not copy the key from OTP to the shadow register, so that if lcs\_is\_valid is asserted, the HW key shadow register is zeroized and invalidated.

- The LCM asserts the readable key zero count error indication register bit and the LCM HW key shadow register is zeroized and invalidated.

The LCM supports seven 256-bit HW keys:

| Key ID | Address offset (in bytes) | Key name                                 | Key type |

|--------|---------------------------|------------------------------------------|----------|

| 0      | 0x00                      | RTL Key (KRTL)                           | RTL      |

| 1      | 0x20                      | Hardware Unique Key (HUK)                | OTP      |

| 2      | 0x40                      | Group Unique Key (GUK)                   | OTP      |

| 3      | 0x60                      | Chip vendor Provisioning key (KP_CM)     | OTP      |

| 4      | 0x80                      | Chip vendor Code Encryption key (KCE_CM) | OTP      |

| 5      | 0xA0                      | OEM Provisioning key (KP_DM)             | OTP      |

| 6      | 0xC0                      | OEM Code Encryption key (KCE_DM)         | OTP      |

#### Table 4-3: HW Keys

## 4.4.1 RTL key, KRTL

The RTL key (KRTL) is owned by the chip vendor and configured into the RTL. The KRTL is used for Secure provisioning during CM or DM LCS in PCI TP mode and is not available in other lifecycle states and TP modes.

## Key ID

0

## Key export address offset (in bytes)

0x00

## Key type

RTL key

## Guidance

To avoid security vulnerabilities, you should use the RTL key only for key derivation purposes.

## Key is invalid and shadow register is zeroized, if any of the following conditions are true

- FATAL\_ERR register is set to FATAL\_ERR\_SET value by the programmer

- LCM fatal\_err signal asserted by LCM

- LCS = SE or RMA

- TP mode = TCI or Virgin

## Export key through direct key APB interface, if all of the following conditions are true

- LCM not in Fatal Error FSM state

- Key is valid

- LCS = CM or DM

- TP mode = PCI

## 4.4.2 HW Unique Key, HUK

The HW Unique Key (HUK) is randomized on the device and provisioned into the OTP memory.

## Key ID

1

## Key export address offset (in bytes)

0x20

## Key type

OTP key

## Guidance

To avoid security vulnerabilities, you should use the HUK only for key derivation purposes. The HUK is revealed only to the system that contains the LCM and the OTP memory.

# The HUK is invalid and its HW key shadow register is zeroized, if any of the following conditions are true

- FATAL\_ERR register is set to FATAL\_ERR\_SET value by the programmer

- LCM fatal\_err signal asserted by LCM

- Number of zeros mismatch

- All key bits are set

- All key bits are cleared

- LCS = CM or RMA

- TP mode = Virgin

## Export key through direct key APB interface, if all of the following conditions are true

- LCM not in Fatal Error FSM state

- Key is valid

- LCS = DM or SE

- TP mode = TCI or PCI

## 4.4.3 Group Unique Key, GUK

The Group Unique Key (GUK) is owned by the chip vendor and provisioned into the OTP memory.

## Key ID

2

## Key export address offset (in bytes)

0x40

## Key type

OTP key

## Guidance

To avoid security vulnerabilities, you should use the GUK only for key derivation purposes. The GUK is known only to a group of systems containing the LCM and the OTP memory.

The GUK is invalid and its HW key shadow register is zeroized, if any of the following conditions are true

- FATAL\_ERR register is set to FATAL\_ERR\_SET value by the programmer

- LCM fatal\_err signal asserted by LCM

- Number of zeros mismatch

- All key bits are set

- All key bits are cleared

- LCS = CM or RMA

- TP mode = Virgin

## Export key through direct key APB interface, if all of the following conditions are true

- LCM not in Fatal Error FSM state

- Key is valid

- LCS = DM or SE

- TP mode = TCI or PCI

## 4.4.4 Chip vendor Provisioning key, KP\_CM

The chip vendor Provisioning key (KP\_CM ) is owned by the chip vendor and provisioned into the OTP memory.

## Key ID

3

## Key export address offset (in bytes)

0x60

## Key type

OTP key

## Guidance

To avoid security vulnerabilities, you should use the KP\_CM only for key derivation purposes.

# The KP\_CM is invalid and its HW key shadow register is zeroized, if any of the following conditions are true

- FATAL\_ERR register is set to FATAL\_ERR\_SET value by the programmer

- LCM fatal\_err signal asserted by LCM

- Number of zeros mismatch

- All key bits are set

- All key bits are cleared

- LCS = CM or RMA

- TP mode = Virgin

## Export key through direct key APB interface, if all of the following conditions are true

- LCM not in Fatal Error FSM state

- Key is valid

- LCS = DM or SE

- TP mode = TCI or PCI

### 4.4.5 Chip vendor code encryption key, KCE\_CM

The chip vendor code encryption key (KCE\_CM) owned by the chip vendor and provisioned into the OTP memory.

#### Key ID

4

#### Key export address offset (in bytes)

0x80

#### Key type

OTP key

#### Guidance

To avoid security vulnerabilities, you should use the KCE\_CM only for key derivation purposes.

# The KCE\_CM is invalid and its HW key shadow register is zeroized, if any of the following conditions are true

- FATAL\_ERR register is set to FATAL\_ERR\_SET value by the programmer

- LCM fatal\_err signal asserted by LCM

- Number of zeros mismatch

- All key bits are set

- All key bits are cleared

- LCS = CM or RMA

- TP mode = Virgin

#### Export key through direct key APB interface, if all of the following conditions are true

- LCM not in Fatal Error FSM state

- Key is valid

- LCS = DM or SE

- TP mode = TCI or PCI

### 4.4.6 OEM Provisioning Key, KP\_DM

The OEM Provisioning Key (KP\_DM) is owned by the OEM and provisioned into the OTP memory.

#### Key ID

5

#### Key export address offset (in bytes)

0xA0

#### Key type

OTP key

#### Guidance

To avoid security vulnerabilities, you should use the KP\_DM only for key derivation purposes.

# The KP\_DM is invalid and its HW key shadow register is zeroized, if any of the following conditions are true

- FATAL\_ERR register is set to FATAL\_ERR\_SET value by the programmer

- LCM fatal\_err signal asserted by LCM

- Number of zeros mismatch

- All key bits are set

- All key bits are cleared

- LCS = CM or DM or RMA

- TP mode = Virgin

#### Export key through direct key APB interface, if all of the following conditions are true

- LCM not in Fatal Error FSM state

- Key is valid

- LCS = SE

- TP mode = TCI or PCI

### 4.4.7 OEM code encryption key, KCE\_DM

The OEM code encryption key (KCE\_DM) is owned by the OEM and provisioned into the OTP memory.

#### Key ID

6

#### Key export address offset (in bytes)

0xC0

#### Key type

OTP key

#### Guidance

To avoid security vulnerabilities, you should use the KCE\_DM only for key derivation purposes.

# The KCE\_DM is invalid and its HW key shadow register is zeroized, if any of the following conditions are true

- FATAL\_ERR register is set to FATAL\_ERR\_SET value by the programmer

- LCM fatal\_err signal asserted by LCM

- Number of zeros mismatch

- All key bits are set

- All key bits are cleared

- LCS = CM or DM or RMA

- TP mode = Virgin

#### Export key through direct key APB interface, if all of the following conditions are true

- LCM not in Fatal Error FSM state

- Key is valid

- LCS = SE

- TP mode = TCI or PCI

### 4.4.8 RoT key export

The LCM includes an APB interface used to export the KRTL and the secret keys stored in the OTP memory to a system peripheral that can manage the keys, such as a *Key Management Unit* (KMU) or a cryptographic engine, which complies with the LCM key export design.

For more information about the KMU, see the Arm<sup>®</sup> Key Management Unit (KMU) Specification.

Arm expects that the interface is implemented as a point-to-point path between the LCM and the KMU. Neither the processor nor any other manager port with access to any interconnect has visibility to the transactions on this APB interface.

The LCM does not provide key locking or key access control capabilities for the programmer during boot time or runtime of the system firmware. Since the LCM cannot provide access control to the secret keys during boot time or runtime, Arm recommends that you connect a KMU to the LCM direct key APB3 manager interface. Arm assumes that the KMU manages usage policies for each key and provides key locking capabilities to the programmer.

### 4.4.9 OTP keys integrity protection

The LCM includes built-in integrity checking functionality for some of the OTP secret keys (key IDs one to six).

- HUK

- GUK

- KP\_CM

- KCE\_CM

- KP\_DM

- KCE\_DM

Integrity checking protection is required because OTP-programmed values could be forced by an attacker to transition from zero to one (non-programmed to programmed state), assuming that the initial state of the OTP memory is all zeros (non-programmed state).

Integrity checking is achieved by counting the number of zeros in a key and programming and storing that zero count value alongside each key, so that the zero count value can be checked when the key is accessed in the future. The zero count calculation and the storage of the zero count value alongside each key is known as the integrity code. The zero-count integrity code value from the OTP memory is never exposed to the programmer, because it can leak information about the secret RTL mask value.

For all the OTP secret keys:

- If the number of zeros does not match the zero count value, the key zero count error indications are asserted and the relevant key register are invalidated and zeroized.

- The zero counting occurs only when the key is read from OTP memory (depending on lifecycle), according to the conditions defined in Table 4-3: HW Keys on page 33.

Since the keys are also protected using an RTL mask, the zero counting is performed on the actual values programmed in OTP, after the key bits were XORed with the RTL mask bits.

The RTL mask value is not used in TCl mode, so the zero counting operation is performed on the raw key values. This is reasonable because the key values for TCl mode are test keys rather than confidential production keys.

The masked version of the OTP key value is never exposed to the programmer through the APB-S interface (during provisioning phase).

An APB-S write transaction to the relevant OTP secret key memory addresses and triggers the LCM to calculate and write the integrity code. The LCM then verifies that the integrity codes were written correctly. The verification is done by comparing a precalculated integrity code value to the value returned by a read transaction issued by the LCM. If the comparison is successful, the LCM responds with all zeros data value to the programmer through the APB-S interface. If the comparison fails, the LCM responds with all-ones data value to the programmer through the APB-S interface.

If a key slot value is left blank (all-zeros), the integrity code overflows above the maximal value of 255 zero count. In this case, the LCM does not calculate and store the integrity code and the key is marked as invalid (not used). The comparison operation ignores the invalid key and the comparison is marked as successful.

The programmer interface provides an error status bit for each key to indicate the key comparison failure.

#### The number of zeroes in the HUK, GUK, KP\_CM, KCE\_CM, and ROTPK keys

The CM configuration flags (OTP Offset 0x00E4 and 0x00E8) in the OTP memory indicate the number of zeros in the HUK, GUK, KP\_CM, KCE\_CM, and ROTPK keys. See Table 4-6: CM configuration 1 (OTP memory offset 00E4) on page 45 and Table 4-7: CM configuration 2 (OTP memory offset 00E8) on page 45 for the bit ranges assigned to each of these keys. These OTP fields are not accessible from the APB-S interface.

#### Writes to the CM configuration flags

When the LCS and TP mode match the conditions described in Table 4-4: OTP memory map on page 42, the LCM replaces the value that is written to the field with the HW calculated number of zeros of the HUK OTP words after applying the relevant key XOR masks. If the LCS and TP mode do not match the conditions described in Table 4-4: OTP memory map on page 42, the LCM ignores the write and returns a bus error.

#### Reads to the CM configuration flags

When the LCS and TP mode match the conditions described in Table 4-4: OTP memory map on page 42, the LCM compares the read value from OTP with the HW calculated number of zeros of the respective OTP key words after applying the relevant key XOR masks, and number of zeros of the respective OTP key words after applying the relevant key XOR masks, and replaces the key bits number of zeros field in the read data with zeros if the comparison succeeds, and with all ones in case of the comparison fails. If the LCS and TP mode do not match the conditions described in Table 4-4: OTP memory map on page 42, the LCM returns a bus error and clears the data from the LCM HW key shadow registers.

## 4.5 OTP manager

The LCM includes an OTP manager that is responsible for controlling the OTP memory assets. The OTP manager uses the OTP APB3 manager interface that is connected to the OTP memory.

The OTP manager provides the following:

- Reading and integrity verification of the OTP keys (zero count). For more information, see OTP keys integrity protection.

- Providing double read and compare to specific OTP memory addresses. The OTP manager asserts the LCM fatal\_err signal if the comparison of the two read results do not match. Only 32-bit read transactions are supported. The protected word addresses are described in Table 4-4: OTP memory map on page 42.

- Providing access control for programmer read and write requests depending on the current LCS and FSM state.

Access to and from OTP fields is described in the Table 4-4: OTP memory map on page 42.

- Any read access to a non-readable OTP word, as described in the Table 4-4: OTP memory map on page 42, returns zeros.

- Any write access to a non-writable OTP word, as described in the Table 4-4: OTP memory map on page 42, is ignored (Security requirement)

- If the DM\_RMA\_LOCK register bits are all set to ones, the DM RMA Flag must not be writable.

When lcs\_is\_valid signal is deasserted, accesses through the APB-S interface to the OTP are not served (writes are ignored and an APB error is signaled, the read data is zero).

To avoid OTP data leakage, due to resetting the LCM during an access to the OTP memory, the LCM generates a dummy read after reset. This dummy read cleans the OTP read data bus

by reading a non-protected 32-bit word from any byte address in the user region ( $0 \times 00F8$  to OTP\_SIZE\_IN\_BYTES).

#### **Related information**

- OTP APB3 manager interface

- OTP APB3 manager interface signals

# 4.6 OTP memory map

The following table describes the OTP memory content, access permissions, OTP mask bit allocations, and the OTP double read integrity protection settings.

If the system requires access to the LCM OTP memory, the LCM must be powered on.

| Table 4-4: OTP | memory map |

|----------------|------------|

|----------------|------------|

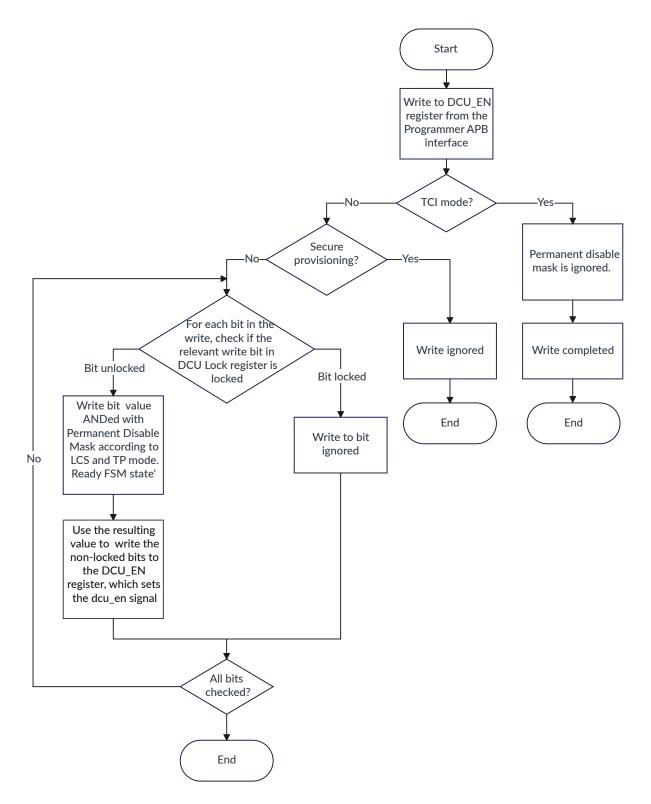

| Byte<br>address | Field description | AP | ritable from<br>B-S if any of the<br>nditions are true                   | AP                                                                                      | adable from<br>B-S if any of the<br>nditions are true       | HW LCM<br>operation                                                     | OTP mask<br>bits | Protected<br>by double<br>read and<br>compare? |