## Arm<sup>®</sup> DynamIQ<sup>™</sup> Shared Unit-120

Revision: r1p0

## **Technical Reference Manual**

Non-Confidential

Issue 04

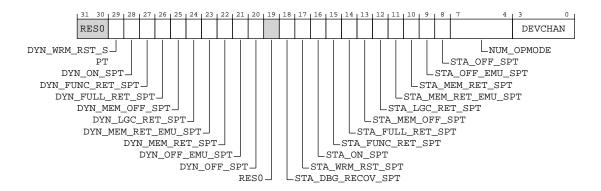

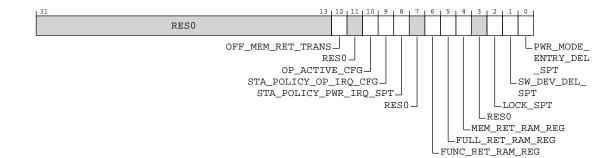

Copyright © 2021–2023 Arm Limited (or its affiliates).  $102547_0100_04_en$  All rights reserved.

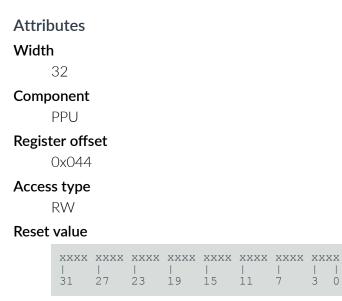

## Arm<sup>®</sup> DynamIQ<sup>™</sup> Shared Unit-120

## Technical Reference Manual

Copyright  $\ensuremath{\mathbb{C}}$  2021–2023 Arm Limited (or its affiliates). All rights reserved.

## **Release Information**

## Document history

| Issue   | Date             | Confidentiality  | Change                                |

|---------|------------------|------------------|---------------------------------------|

| 0000-01 | 30 November 2021 | Confidential     | First beta release for rOpO           |

| 0000-02 | 8 April 2022     | Confidential     | First limited access release for rOpO |

| 0100-03 | 29 July 2022     | Confidential     | First early access release for r1p0   |

| 0100-04 | 29 May 2023      | Non-Confidential | Second early access release for r1p0  |

## **Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND

> Copyright © 2021–2023 Arm Limited (or its affiliates). All rights reserved. Non-Confidential

# REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or <sup>™</sup> are registered trademarks or trademarks of Arm Limited (or its affiliates) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at https://www.arm.com/company/policies/trademarks.

Copyright © 2021–2023 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

(LES-PRE-20349|version 21.0)

## **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

## **Product Status**

The information in this document is Final, that is for a developed product.

## Feedback

Arm welcomes feedback on this product and its documentation. To provide feedback on the product, create a ticket on https://support.developer.arm.com.

To provide feedback on the document, fill the following survey: https://developer.arm.com/ documentation-feedback-survey.

## Inclusive language commitment

Arm values inclusive communities. Arm recognizes that we and our industry have used language that can be offensive. Arm strives to lead the industry and create change.

This document includes language that can be offensive. We will replace this language in a future issue of this document.

To report offensive language in this document, email terms@arm.com.

# Contents

| 1. Introduction                                                             | 13 |

|-----------------------------------------------------------------------------|----|

| 1.1 Product revision status                                                 | 13 |

| 1.2 Intended audience                                                       | 13 |

| 1.3 Conventions                                                             |    |

| 1.4 Useful resources                                                        | 15 |

| 2. The DynamIQ <sup>™</sup> Shared Unit-120                                 |    |

| 2.1 DynamIQ <sup>™</sup> Shared Unit-120 features                           |    |

| 2.2 DynamIQ <sup>™</sup> Shared Unit-120 configuration parameters           |    |

| 2.3 Cluster configurations                                                  | 22 |

| 2.3.1 What is a complex?                                                    | 25 |

| 2.3.2 L3 memory system variants                                             |    |

| 2.4 Supported standards and specifications                                  |    |

| 2.4.1 Realm management extension                                            |    |

| 2.5 Test features                                                           |    |

| 2.6 Design Tasks                                                            |    |

| 2.7 Core, complex, and processing element numbering                         |    |

| 2.8 Product revisions                                                       |    |

| 3. Technical overview                                                       |    |

| 3.1 DynamlQ cluster components                                              | 34 |

| 3.1.1 Integration of the cores in the cluster                               |    |

| 3.2 DynamlQ <sup>™</sup> cluster shared logic components                    |    |

| 3.3 DebugBlock components                                                   |    |

| 3.4 Interfaces                                                              |    |

| 3.4.1 Page-Based Hardware Attribute                                         | 45 |

| 3.4.2 Sequential hint                                                       |    |

| 4. Clocks and resets                                                        |    |

| 4.1 Clocks                                                                  |    |

| 4.2 Clock domains                                                           |    |

| 4.3 Resets                                                                  |    |

| 4.4 Resetting with Power Policy Units                                       | 51 |

| Copyright © 2021–2023 Arm Limited (or its affiliates). All rights reserved. |    |

| 5. Power management                                              | 53 |

|------------------------------------------------------------------|----|

| 5.1 Power management in the DSU-120                              | 53 |

| 5.2 DSU-120 supported power domains                              |    |

| 5.3 Cluster power modes                                          |    |

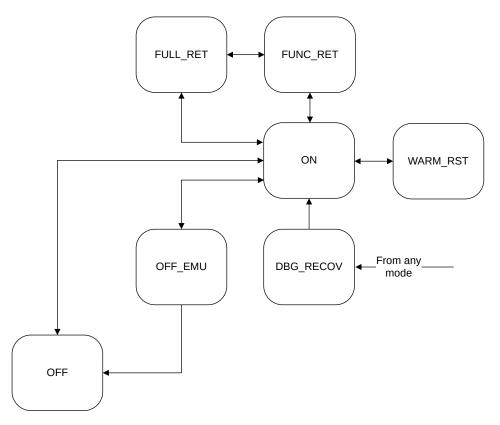

| 5.3.1 On mode (ON)                                               | 57 |

| 5.3.2 Off mode (OFF)                                             | 57 |

| 5.3.3 Functional retention mode (FUNC_RET)                       | 57 |

| 5.3.4 Cluster full retention mode (FULL_RET)                     | 57 |

| 5.3.5 Memory retention mode (MEM_RET)                            | 58 |

| 5.3.6 Emulated off mode (OFF_EMU)                                |    |

| 5.3.7 Emulated memory retention mode (MEM_RET_EMU)               | 59 |

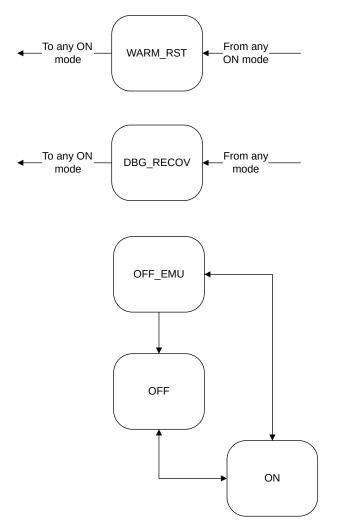

| 5.3.8 Warm reset mode (WARM_RST)                                 | 59 |

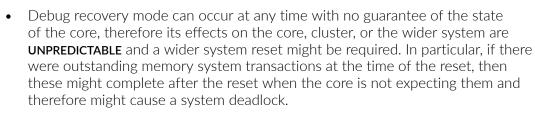

| 5.3.9 Debug recovery mode (DBG_RECOV)                            | 59 |

| 5.4 L3 RAM power control                                         | 61 |

| 5.4.1 L3 cache RAM powerdown                                     | 61 |

| 5.4.2 L3 cache slice powerdown                                   | 65 |

| 5.5 Cluster operating modes                                      |    |

| 5.6 Power states for the cluster RAM instances                   | 67 |

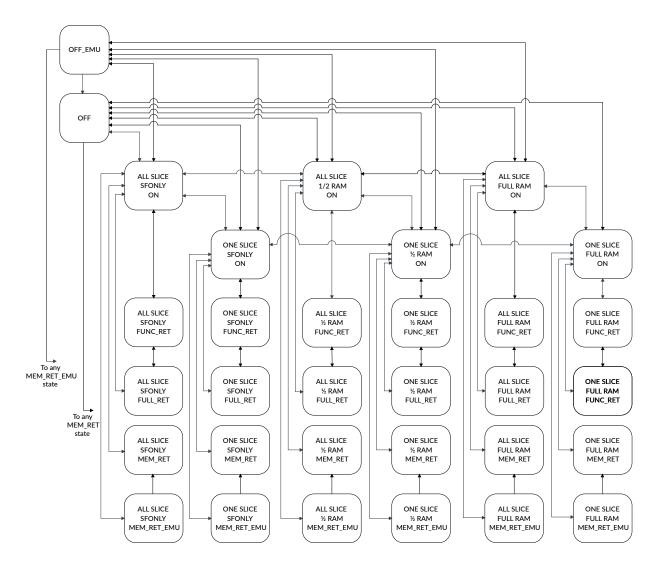

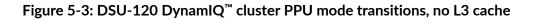

| 5.7 Cluster PPU mode transitions                                 |    |

| 5.7.1 Rules governing cluster PPU mode transitions               | 73 |

| 5.7.2 PPU mode transition behavior                               | 73 |

| 5.7.3 DebugBlock power modes                                     | 74 |

| 5.8 Core PPU modes                                               | 74 |

| 5.8.1 Core PPU mode transitions                                  | 75 |

| 5.9 Complex power management                                     | 78 |

| 5.9.1 Complex power modes                                        | 78 |

| 5.9.2 Power mode transition dependencies for a dual-core complex | 79 |

| 5.10 Maximum Power Mitigation Mechanism                          |    |

| 5.11 DSU-120 voltage domains                                     | 81 |

| 6. Power and reset control with Power Policy Units               |    |

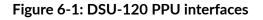

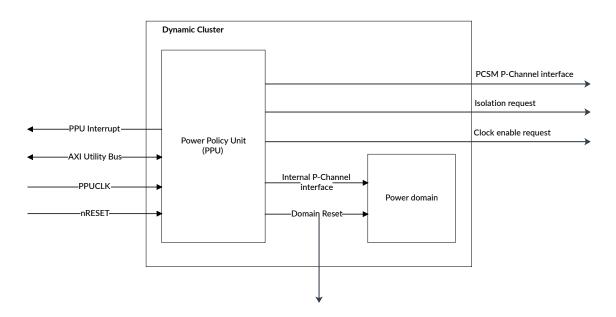

| 6.1 The Power Policy Unit                                        |    |

| 6.2 Power policy unit operation                                  | 84 |

| 6.2.1 Implicit resets from power modes                           |    |

| 6.2.2 nRESET sequence                                            |    |

| 6.2.3 Initial cluster operating mode                             |    |

| 6.3 Utility bus accesses                                                                          | 87  |

|---------------------------------------------------------------------------------------------------|-----|

| 6.4 Cluster PPU mode control                                                                      | 88  |

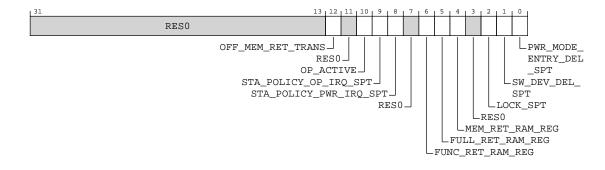

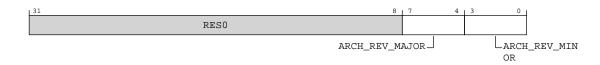

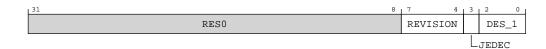

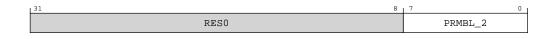

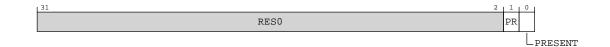

| 6.4.1 External cluster PPU registers                                                              | 88  |

| 6.4.2 Encodings for cluster power and operating modes                                             | 89  |

| 6.5 Core power mode control                                                                       | 91  |

| 6.5.1 External core PPU registers                                                                 | 91  |

| 6.5.2 Encodings for core power modes                                                              | 93  |

| 6.6 Programming sequences for the cluster and the core                                            | 94  |

| 6.6.1 Programming sequence to bring the cluster and cores from Off to On mode                     | 94  |

| 6.6.2 Programming sequence to bring the cluster and cores from On to Off mode                     | 95  |

| 6.6.3 Programming sequence for an interrupt controller to control transitions between On and mode |     |

| 6.7 Explicit reset of cluster and cores and debug recovery mode                                   | 96  |

| 6.8 Power mode dependencies between the core and the cluster                                      | 98  |

| 6.9 ECC errors during power transitions                                                           | 99  |

| 6.10 Core Full retention mode and static mode restrictions                                        | 100 |

| 7. L3 cache                                                                                       | 101 |

| 7.1 L3 cache allocation policy                                                                    | 101 |

| 7.2 Available number of cache ways                                                                | 102 |

| 7.3 Memory System Resource Partitioning and Monitoring control                                    | 102 |

| 7.4 L3 cache partitioning                                                                         | 103 |

| 7.5 Bandwidth partitioning                                                                        | 105 |

| 7.6 Cache stashing                                                                                | 107 |

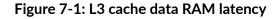

| 7.7 L3 cache data RAM latency                                                                     | 108 |

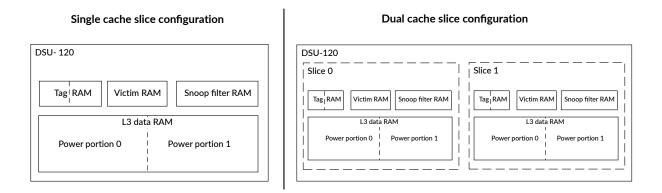

| 7.8 Cache slices and power portions                                                               | 109 |

| 7.8.1 Cache slice and master port selection                                                       | 110 |

| 8. CHI master interface                                                                           | 111 |

| 8.1 Multiple CHI bus master port configurations                                                   | 111 |

| 8.2 Configure CHI bus master ports to use address target groups                                   | 111 |

| 8.2.1 Hashing for CHI transaction distribution                                                    | 112 |

| 8.2.2 Mapping for address target groups to CHI bus master ports                                   | 114 |

| 8.2.3 CHI id bit setting                                                                          | 115 |

| 8.3 CHI transaction routing with multiple master ports                                            | 115 |

| 8.4 CHI features                                                                                  | 118 |

| 8.5 CHI configurations                                                                            | 119 |

|                                                                                                   |     |

| 8.6 Attributes of the CHI master interface                      |     |

|-----------------------------------------------------------------|-----|

| 8.7 CHI channel properties                                      | 121 |

| 8.8 CHI transactions                                            |     |

| 8.9 Use of DataSource field                                     |     |

| 8.10 Support for memory types                                   | 126 |

| 9. AXI master interface                                         | 127 |

| 9.1 Multiple AXI bus master port configurations                 |     |

| 9.2 Configure AXI bus master ports to use address target groups |     |

| 9.2.1 Hashing for AXI transaction distribution                  | 128 |

| 9.2.2 Mapping for address target groups to AXI bus master ports |     |

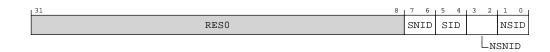

| 9.2.3 AXI id bit setting                                        | 131 |

| 9.3 AXI transaction routing with multiple master ports          | 131 |

| 9.4 AXI master port interface properties                        |     |

| 9.5 AXI configurations                                          | 133 |

| 9.6 AXI 256-bit master interface attributes                     |     |

| 9.7 AXI transactions                                            |     |

| 9.8 Support for memory types                                    |     |

| 9.9 Read response                                               | 136 |

| 9.10 Write response                                             |     |

| 9.11 Barriers                                                   |     |

| 9.12 AXI privilege information                                  |     |

| 10. ACP slave interface                                         |     |

| 10.1 ACP features                                               | 138 |

| 10.2 ACP ACE5-LiteDVM protocol subset                           |     |

| 10.3 ACP transactions                                           |     |

| 10.4 ACP performance                                            |     |

| 10.5 DVM snoop transaction support                              |     |

| 10.5.1 Control the receiving of DVM snoop transactions          |     |

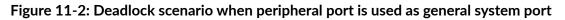

| 11. AXI or CHI master peripheral port                           |     |

| 11.1 Supported memory and transaction types                     |     |

| 11.2 Mapping peripheral port address ranges                     |     |

| 11.2.1 Changing peripheral port address range                   |     |

| 11.3 AXI 64-bit peripheral port interface properties            |     |

| 11.4 AXI 256-bit peripheral port interface properties           |     |

| 11.5 AXI 64-bit peripheral port transactions                           |     |

|------------------------------------------------------------------------|-----|

| 11.6 AXI 256-bit peripheral port transactions                          | 154 |

| 11.7 Attributes of the CHI peripheral port                             | 155 |

| 11.8 CHI peripheral port interface properties                          |     |

| 11.9 CHI peripheral port transactions                                  |     |

| 11.10 Read and write capabilities and transaction ID encoding          |     |

| 11.11 Peripheral port and ACP interface usage                          | 161 |

| 11.12 AXI privilege information for the AXI-configured peripheral port |     |

| 12. RAS extension support                                              |     |

| 12.1 Cache protection behavior                                         | 164 |

| 12.2 Error containment                                                 | 166 |

| 12.3 Fault detection and reporting                                     |     |

| 12.4 Error detection and reporting                                     | 167 |

| 12.4.1 Error reporting and performance monitoring                      |     |

| 12.4.2 Errors not counted                                              | 169 |

| 12.4.3 Double error reporting                                          |     |

| 12.5 Error injection                                                   |     |

| 12.6 ECC errors during power transitions                               |     |

| 12.7 Cluster RAS registers                                             | 171 |

| 12.7.1 AArch64 RAS registers                                           |     |

| 12.7.2 External cluster RAS registers                                  |     |

| 13. Utility bus                                                        | 175 |

| 13.1 Utility bus accesses                                              |     |

| 13.1.1 Core access to system component registers                       |     |

| 13.1.2 Cluster and core PPU register access                            |     |

| 13.2 Base addresses for system components                              |     |

| 14. System control registers                                           | 179 |

| 14.1 AArch64 generic-system-control registers                          |     |

| 15. Debug                                                              |     |

| 15.1 Cache debug                                                       |     |

| 15.2 Supported debug methods                                           |     |

| 15.3 Terminology                                                       |     |

| 15.4 Simplified PE and Debug power domains                             |     |

| 15.5 DebugBlock overview                                       |     |

|----------------------------------------------------------------|-----|

| 15.6 DebugBlock subcomponents                                  |     |

| 15.7 Embedded Cross Trigger overview                           |     |

| 15.7.1 CTI triggers                                            |     |

| 15.8 External CTI registers                                    |     |

| 15.9 Trace output from cores and DynamIQ cluster               |     |

| 15.10 CoreSight component identification                       |     |

| 16. ROM tables                                                 |     |

| 16.1 Debug system address map                                  |     |

| 16.2 DebugBlock ROM table                                      |     |

| 16.3 Cluster ROM table                                         |     |

| 16.4 ROM table power request registers for cluster and cores   |     |

| 16.5 External cluster ROM registers                            |     |

| 16.6 External debug ROM registers                              | 211 |

| 17. Performance Monitors Extension support                     |     |

| 17.1 PMU features                                              |     |

| 17.2 PMU events                                                |     |

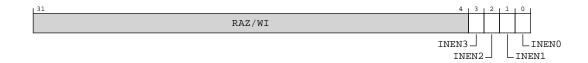

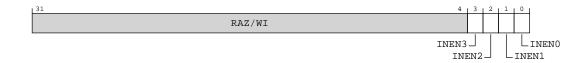

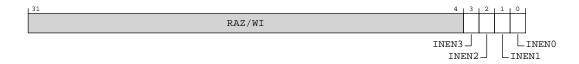

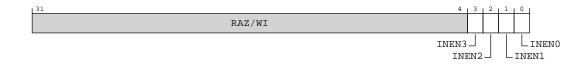

| 17.3 PMU interrupt                                             |     |

| 17.4 External cluster PMU registers                            |     |

| 18. Activity Monitors Extension support                        |     |

| 18.1 Activity monitors access                                  |     |

| 18.2 Activity monitors counters                                |     |

| 18.3 External cluster AMU registers                            |     |

| 18.4 Activity monitors events                                  |     |

| A. AArch64 registers                                           | 227 |

| A.1 AArch64 generic system control registers summary           |     |

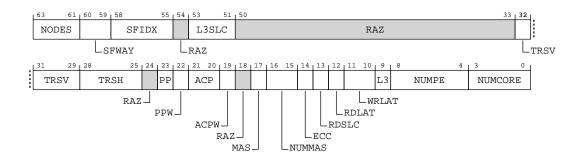

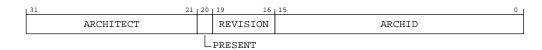

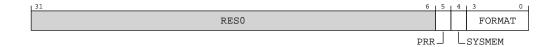

| A.1.1 IMP_CLUSTERCFR_EL1, Cluster Configuration Register       |     |

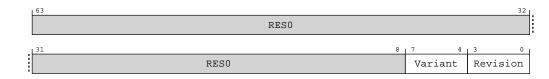

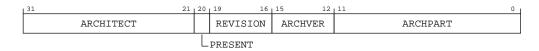

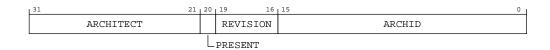

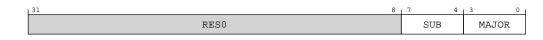

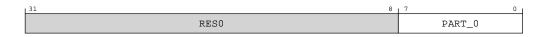

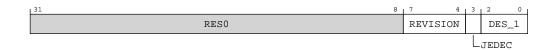

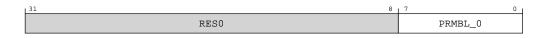

| A.1.2 IMP_CLUSTERIDR_EL1, Cluster Main Revision Register       | 234 |

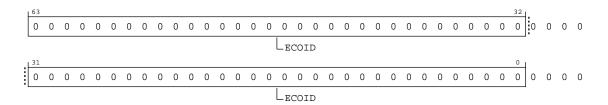

| A.1.3 IMP_CLUSTERREVIDR_EL1, Cluster ECO ID Register           |     |

| A.1.4 IMP_CLUSTERACTLR_EL1, Cluster Auxiliary Control Register |     |

| A.1.5 IMP_CLUSTERECTLR_EL1, Cluster Extended Control Register  |     |

| A.1.6 IMP_CLUSTERPWRCTLR_EL1, Cluster Power Control Register   |     |

| A.1.7 IMP_CLUSTERPWRDN_EL1, Cluster Power Down Register        |     |

| A.1.8 IMP_CLUSTERPWRSTAT_EL1, Cluster Power Status Register                         | 250         |

|-------------------------------------------------------------------------------------|-------------|

| A.1.9 IMP_CLUSTERL3DNTH0_EL1, Cluster L3 Downsize Threshold0 Register               | 253         |

| A.1.10 IMP_CLUSTERL3DNTH1_EL1, Cluster L3 Downsize Threshold1 Register              | 255         |

| A.1.11 IMP_CLUSTERL3UPTH0_EL1, Cluster L3 Upsize ThresholdO Register                | 257         |

| A.1.12 IMP_CLUSTERL3UPTH1_EL1, Cluster L3 Upsize Threshold1 Register                | 259         |

| A.1.13 IMP_CLUSTERBUSQOS_EL1, Cluster Bus QoS Control Register                      | 261         |

| A.1.14 IMP_CLUSTERL3HIT_EL1, Cluster L3 Hit Counter Register                        | 262         |

| A.1.15 IMP_CLUSTERL3MISS_EL1, Cluster L3 Miss Counter Register                      | 264         |

| A.1.16 IMP_CLUSTERPPSTART_EL1, Cluster Peripheral Port Start Address Register       | 266         |

| A.1.17 IMP_CLUSTERPPEND_EL1, Cluster Peripheral Port End Address Register           | 268         |

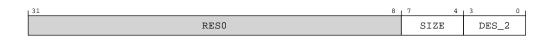

| A.1.18 IMP_CLUSTERCFR2_EL1, Cluster Configuration Register 2                        | 270         |

| A.1.19 IMP_CLUSTERRSVD_9_3_EL1, RESERVED                                            | 272         |

| A.1.20 IMP_CLUSTERCDBG_EL3, Cluster Cache Debug Register                            | 274         |

| A.1.21 IMP_CLUSTERPMMDCR_EL3, Monitor Debug Configuration Register (EL3)            | 276         |

| A.2 AArch64 performance monitors registers summary                                  | 278         |

| A.2.1 IMP_CLUSTERPMCR_EL1, Performance Monitors Control Register                    | 280         |

| A.2.2 IMP_CLUSTERPMCNTENSET_EL1, Performance Monitors Count Enable Set Register     | . 282       |

| A.2.3 IMP_CLUSTERPMCNTENCLR_EL1, Performance Monitors Count Enable Clear Register.  | 285         |

| A.2.4 IMP_CLUSTERPMOVSSET_EL1, Performance Monitors Overflow Flag Status Register   |             |

| A.2.5 IMP_CLUSTERPMOVSCLR_EL1, Performance Monitors Overflow Flag Status Register   |             |

| A.2.6 IMP_CLUSTERPMSELR_EL1, Performance Monitors Event Counter Selection Register  | 294         |

| A.2.7 IMP_CLUSTERPMINTENSET_EL1, Performance Monitors Interrupt Enable Set Register |             |

| A.2.8 IMP_CLUSTERPMINTENCLR_EL1, Performance Monitors Interrupt Enable              | Clear       |

| Register                                                                            | 300         |

| A.2.9 IMP_CLUSTERPMCCNTR_EL1, Performance Monitors Cycle Count Register             | 303         |

| A.2.10 IMP_CLUSTERPMXEVTYPER_EL1, Performance Monitors Selected Event Register      | Type<br>305 |

| A.2.11 IMP_CLUSTERPMXEVCNTR_EL1, Performance Monitors Selected Event (Register      |             |

| A.2.12 IMP_CLUSTERPMCEIDO_EL1, Performance Monitors Common Event Identification Re  | gister      |

| A.2.13 IMP_CLUSTERPMCEID1_EL1, Performance Monitors Common Event Identification Re  | gister      |

| A.3 AArch64 RAS registers summary                                                   |             |

| A.3.1 ERXFR_EL1, Selected Error Record Feature Register                             |             |

| A.3.2 ERXCTLR_EL1, Selected Error Record Control Register                           |             |

|                                                                                     |             |

Copyright © 2021–2023 Arm Limited (or its affiliates). All rights reserved. Non-Confidential

| A.3.3 ERXSTATUS_EL1, Selected Error Record Primary Status Register       | . 331 |

|--------------------------------------------------------------------------|-------|

| A.3.4 ERXPFGF_EL1, Selected Pseudo-fault Generation Feature Register     | .339  |

| A.3.5 ERXPFGCTL_EL1, Selected Pseudo-fault Generation Control Register   | . 342 |

| A.3.6 ERXPFGCDN_EL1, Selected Pseudo-fault Generation Countdown Register | . 347 |

| A.3.7 ERXMISCO_EL1, Selected Error Record Miscellaneous Register 0       | .349  |

| A.3.8 ERXMISC1_EL1, Selected Error Record Miscellaneous Register 1       | .353  |

| A.3.9 ERXMISC2_EL1, Selected Error Record Miscellaneous Register 2       | .355  |

| A.3.10 ERXMISC3_EL1, Selected Error Record Miscellaneous Register 3      | . 357 |

|                                                                          |       |

| B. External registers                                   |     |

|---------------------------------------------------------|-----|

| B.1 Registers accessed over the utility bus             |     |

| B.1.1 External cluster system control registers summary |     |

| B.1.2 External MPAM registers summary                   |     |

| B.1.3 External cluster RAS registers summary            |     |

| B.1.4 External cluster PPU registers summary            |     |

| B.1.5 External cluster AMU registers summary            |     |

| B.1.6 External core PPU registers summary               |     |

| B.2 Registers accessed over the Debug APB bus           | 616 |

| B.2.1 External cluster and core CTI registers summary   | 617 |

| B.2.2 External cluster ROM registers summary            |     |

| B.2.3 External debug ROM registers summary              | 812 |

| B.2.4 External cluster PMU registers summary            |     |

| C. Revisions                                            |     |

# 1. Introduction

## **1.1 Product revision status**

The  $r_{xp_y}$  identifier indicates the revision status of the product described in this manual, for example,  $r_{1p_2}$ , where:

rx py Identifies the major revision of the product, for example, r1. Identifies the minor revision or modification status of the product, for example, p2.

## 1.2 Intended audience

This manual is for system designers, system integrators, and programmers who are designing or programming a *System on Chip* (SoC) that uses a DynamIQ<sup>™</sup> Shared Unit-120 along with an Arm core or cores.

## 1.3 Conventions

The following subsections describe conventions used in Arm documents.

## Glossary

The Arm<sup>®</sup> Glossary is a list of terms used in Arm documentation, together with definitions for those terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

| Convention                 | Use                                                                                                                             |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| italic                     | Citations.                                                                                                                      |

| bold                       | Terms in descriptive lists, where appropriate.                                                                                  |

| monospace                  | Text that you can enter at the keyboard, such as commands, file and program names, and source code.                             |

| monospace <u>underline</u> | A permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name. |

See the Arm Glossary for more information: developer.arm.com/glossary.

| Convention     | Use                                                                                                                                                                                                                               |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <and></and>    | Encloses replaceable terms for assembler syntax where they appear in code or code fragments.                                                                                                                                      |

|                | For example:                                                                                                                                                                                                                      |

|                | MRC p15, 0, <rd>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></rd>                                                                                                                                                            |

| SMALL CAPITALS | Terms that have specific technical meanings as defined in the <i>Arm</i> <sup>®</sup> <i>Glossary</i> . For example, <b>IMPLEMENTATION DEFINED</b> , <b>IMPLEMENTATION SPECIFIC</b> , <b>UNKNOWN</b> , and <b>UNPREDICTABLE</b> . |

Recommendations. Not following these recommendations might lead to system failure or damage.

Requirements for the system. Not following these requirements might result in system failure or damage.

Requirements for the system. Not following these requirements will result in system failure or damage.

An important piece of information that needs your attention.

A useful tip that might make it easier, better or faster to perform a task.

A reminder of something important that relates to the information you are reading.

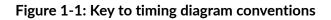

## **Timing diagrams**

The following figure explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

## Signals

The signal conventions are:

## Signal level

The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

- HIGH for active-HIGH signals.

- LOW for active-LOW signals.

## Lowercase n

At the start or end of a signal name, n denotes an active-LOW signal.

## 1.4 Useful resources

This document contains information that is specific to this product. See the following resources for other useful information.

Access to Arm documents depends on their confidentiality:

- Non-Confidential documents are available at developer.arm.com/documentation. Each document link in the following tables goes to the online version of the document.

- Confidential documents are available to licensees only through the product package.

#### Table 1-2: Arm publications

| Document Name                            | Document ID | Licensee only |

|------------------------------------------|-------------|---------------|

| AMBA® AXI and ACE Protocol Specification | IHI 0022    | No            |

| AMBA® APB Protocol Specification         | IHI 0024    | No            |

| AMBA® ATB Protocol Specification         | IHI 0032    | No            |

| Document Name                                                                                                                                  | Document ID | Licensee only |

|------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------|

| AMBA® 5 CHI Architecture Specification                                                                                                         | IHI 0050    | No            |

| AMBA® Low Power Interface Specification                                                                                                        | IHI 0068    | No            |

| Arm® Architecture Reference Manual<br>Supplement, Memory System Resource<br>Partitioning and Monitoring (MPAM), for A-<br>profile architecture | DDI 0598    | No            |

| Arm <sup>®</sup> Power Control System Architecture                                                                                             | DEN 0050    | No            |

| Arm <sup>®</sup> Power Policy Unit Architecture<br>Specification                                                                               | DEN 0051    | No            |

| Arm®Corelink® PCK-600 Power Control Kit<br>Technical Reference Manual                                                                          | 101150      | No            |

| Arm <sup>®</sup> Architecture Reference Manual for A-<br>profile architecture                                                                  | DDI 0487    | No            |

| Arm® Architecture Reference Manual<br>Supplement Armv9, for Armv9-A architecture<br>profile                                                    | DDI 0608    | No            |

| Arm <sup>®</sup> Generic Interrupt Controller Architecture<br>Specification, GIC architecture version 3 and<br>version 4                       | IHI 0069    | No            |

| Arm® Architecture Reference Manual<br>Supplement, The Realm Management Extension<br>(RME), for Armv9-A                                         | DDI0615     | No            |

| Arm® Architecture Reference Manual<br>Supplement, Reliability, Availability, and<br>Serviceability (RAS), for A-profile architecture           | DDI 0587    | No            |

| Arm <sup>®</sup> CoreSight <sup>™</sup> Architecture Specification<br>v3.0                                                                     | IHI 0029    | No            |

| Arm® CoreSight™ DAP-Lite2 Technical<br>Reference Manual                                                                                        | 100572      | No            |

| Arm <sup>®</sup> CoreSight <sup>™</sup> System-on-Chip SoC-600<br>Technical Reference Manual                                                   | 100806      | No            |

| Arm <sup>®</sup> Embedded Trace Macrocell Architecture<br>Specification ETMv4                                                                  | IHI 0064    | No            |

| Arm® CoreSight™ ELA-600 Embedded Logic<br>Analyzer Technical Reference Manual                                                                  | 101088      | No            |

| Arm® DynamlQ <sup>™</sup> Shared Unit-120<br>Configuration and Integration Manual                                                              | 102548      | Yes           |

#### Table 1-3: Other publications

| Document ID | Document Name |

|-------------|---------------|

| -           | -             |

Arm tests its PDFs only in Adobe Acrobat and Acrobat Reader. Arm cannot guarantee the quality of its documents when used with any other PDF reader.

Adobe PDF reader products can be downloaded at http://www.adobe.com.

# 2. The DynamIQ<sup>™</sup> Shared Unit-120

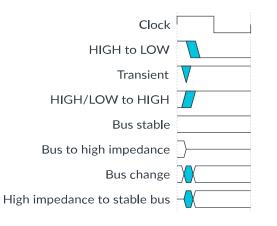

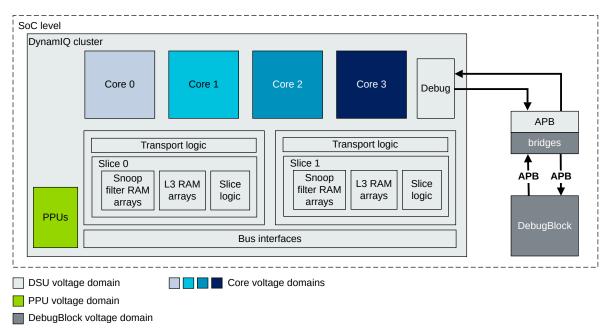

The DynamlQ<sup>™</sup> Shared Unit-120 (DSU-120) provides a shared L3 memory system, snoop control and filtering, and other control logic to support a cluster of A-class architecture cores. The cluster is called the DSU-120 DynamlQ<sup>™</sup> cluster. Also, all the external interfaces to the System on Chip (SoC) are provided through the DSU-120.

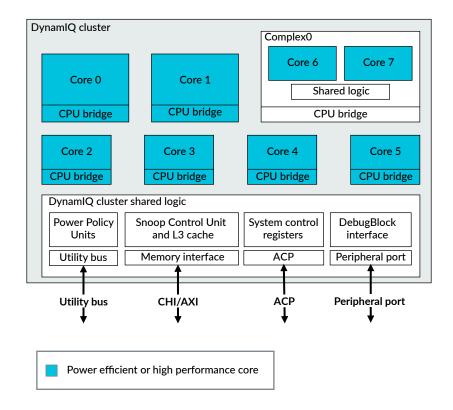

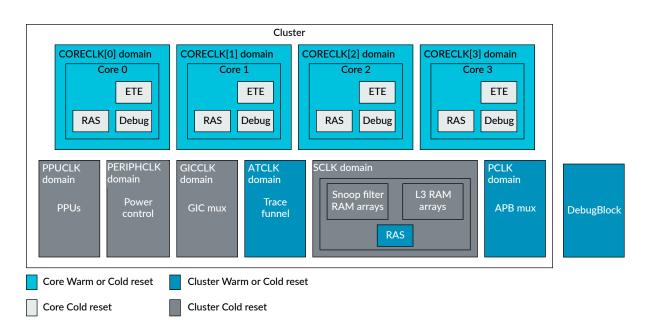

The following figure shows an example of a DSU-120-based cluster.

Figure 2-1: DSU-120 DynamIQ<sup>™</sup> cluster

Note

In this book, the DSU-120 DynamIQ<sup>™</sup> cluster is referred to as a cluster in cases where distinguishing between the DSU-120 DynamIQ<sup>™</sup> cluster and DSU-120 is not important to the context.

A DSU-120 DynamIQ<sup>™</sup> cluster consists of between one and 14 cores, with up to three different types of cores in the same cluster. Cores can be configured for various performance points during macrocell implementation and run at different frequencies and voltages.

The DSU-120 DynamlQ<sup>m</sup> cluster also supports complexes where typically two cores are linked together and share logic. Examples of shared logic include a floating-point unit and an L2 cache. For more information on complexes, see 2.3.1 What is a complex? on page 25.

All cores in the DSU-120 DynamIQ<sup>™</sup> cluster, including those in complexes, are coherently connected to an L3 memory system that includes an L3 cache and a *Snoop Control Unit* (SCU). The SCU maintains coherency between caches in the cores and the L3 cache, and includes a snoop filter to optimize coherency maintenance operations. The shared L3 cache simplifies process migration between the cores.

The DSU-120 DynamIQ<sup>™</sup> cluster can be implemented with various power domains to target power performance levels. These power domains are managed through the *Power Policy Units* (PPUs). The DSU-120 DynamIQ<sup>™</sup> cluster supports many mechanisms to reduce static and dynamic power dissipation. For example, placing the cores and L3 cache into retention and powering down parts of the L3 cache.

All the external interfaces including those to the cores are provided through the DSU-120 to the *System on Chip* (SoC). Main system transactions are supported through the memory interface which can be implemented as a coherent or non-coherent interface. A peripheral port is provided to support low latency access to external system components but also can be used as a non-coherent master interface. The *Accelerator Coherency Port* (ACP) provides coherent access for non-cached masters that need I/O coherency with the cluster. The utility bus is a memory-mapped port that provides a programming interface to the PPUs and some of the other system components.

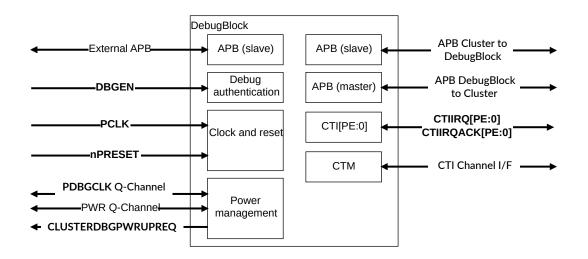

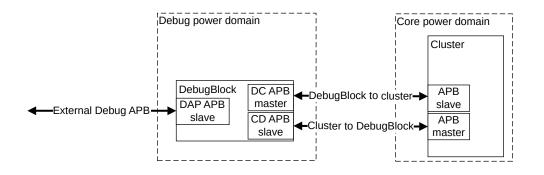

A dedicated debug component, called the DebugBlock, forms part of the DSU-120 that provides the interface for debug capability. The DebugBlock is instanced as a separate unit for supporting debug over powerdown.

Finally, there are several asynchronous bridges automatically built in across the cluster to resynchronize timing across various clock domain boundaries.

- For information on the behavior and features of your core, including whether your core is supported in a complex, see the *Technical Reference Manual* (TRM) for your core.

- For information on the DSU-120 macrocell implementation, see Arm<sup>®</sup> DynamlQ<sup>™</sup> Shared Unit-120 Configuration and Integration Manual.

## 2.1 DynamIQ<sup>™</sup> Shared Unit-120 features

Some features in the *DynamIQ<sup>™</sup>* Shared Unit-120 (DSU-120) are fixed and some features are optional. You can configure optional features in the RTL during build time configuration, to meet your requirements.

## **Cache features**

Note

The DSU-120 has the following cache features:

- Optional unified 16-way set-associative L3 cache, configurable from 256KB to 32MB

- 64-byte cache lines

- L3 cache slice support, for improved bandwidth and cache RAM layout, up to eight slices supported

- L3 cache powerdown based either on cache slices or cache ways

- Cache partitioning support, compliant with *Memory System Resource Partitioning and Monitoring* (MPAM) architecture

- Error Correcting Code (ECC) protection on L3 cache RAM instances

- L3 cache system can be clocked at a rate synchronous to the external system interconnect or at integer multiples

## Coherency and snoop control

The DSU-120 has the following coherency and snoop control features:

- *Snoop Control Unit* (SCU) maintains coherency and consistency in the memory system internal to the cluster, and (optionally) external to the cluster.

- SCU includes a set of snoop filters, automatically sized, one for each cache slice

## **Cluster features**

The DSU-120 has the following cluster features:

- Support for Arm<sup>®</sup>v9.2-A architecture cores

- Support for Realm Management Extension (RME)

- Support for up to three types of core, and a maximum of 14 cores in the cluster

- Power Policy Units (PPUs) providing autonomous power management of the L3 cache and the cores

- Support for cores running independently at different frequencies and voltages known as *Dynamic Voltage Frequency Scaling* (DVFS). For cores in a complex, DVFS is only possible for the whole complex not for individual cores

- The DSU-120 has an internal transport mechanism that is responsible for all communication between components in the design. The topology of the transport is defined by the number of cores and number of L3 cache slices.

## Interface features

The DSU-120 has the following interface features:

- Optional AMBA 5 CHI Issue E 256-bit coherent master bus interface, supports up to four CHI bus master ports.

- Optional AMBA AXI5 Issue H 256-bit non-coherent master bus interface, supports up to four AXI bus master ports.

- Configurable address target group methodology for CHI and AXI bus master ports. The address target groups are used to optimize the interconnect connectivity between the bus master ports and the system.

- Optional 128-bit or 256-bit wide I/O-coherent *Accelerator Coherency Port* (ACP) interfaces based on AMBA ACE5-Lite. Supports up to two ACP interfaces.

- AMBA AXI5 utility bus providing programming interface to PPUs, and other system components.

- Optional Peripheral Port interface that is implemented as either an AXI 64-bit wide port, AXI 256-bit wide port, or CHI Issue E 256-bit wide port.

- Simplified system integration for interfaces such as debug and trace which are already in the correct clock domain at the output of the cluster.

If RME is supported in the DSU-120, the bus master interface uses the CHI Issue F protocol and the utility bus interface uses the AXI Issue J protocol. For more information on RME support in DSU-120, see 2.4.1 Realm management extension on page 30.

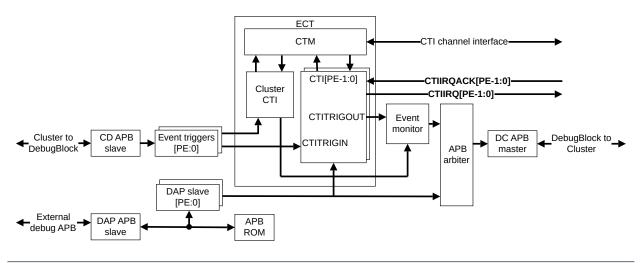

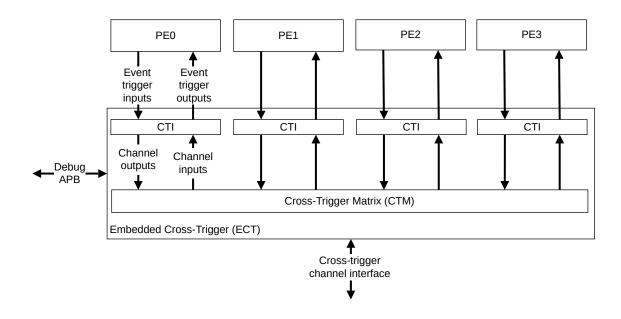

## Debug and trace features

The DSU-120 has the following debug and trace features:

- Debug-over-powerdown support

- CoreSight SoC-600 support for *Embedded Trace Extension* (ETE) and *Cross Trigger Interface* (CTI) for each core

- Optional CoreSight Embedded Logic Analyzer (ELA)-600 support

The ELA-600 is a separately licensable product.

## **Related information**

2.2 DynamIQ Shared Unit-120 configuration parameters on page 20

## 2.2 DynamIQ<sup>™</sup> Shared Unit-120 configuration parameters

You must configure the *DynamIQ<sup>™</sup>* Shared Unit-120 (DSU-120) RTL for your implementation requirements prior to hardware synthesis at build time configuration. Configuration for the DSU-120 is carried out together with configuration for the cores in your cluster.

For a complete list of the configuration parameters and guidelines, see RTL configuration process in Arm<sup>®</sup> DynamIQ<sup>™</sup> Shared Unit-120 Configuration and Integration Manual (DSU-120 CIM).

The DSU-120 implementation options include:

## Number of cores

You can configure the cluster to have between one and 14 cores. Each core within a complex counts towards the total number of cores in the cluster. This is in addition to any cores in the cluster that are not in complexes (stand-alone cores).

#### Core type

You can have a cluster that includes up to three different types of cores. See 2.3 Cluster configurations on page 22, for more information on the types of core that are supported.

#### Direct connect

You can configure the cluster for Direct connect memory system variant. For more information on Direct connect, see 2.3.2 L3 memory system variants on page 27.

#### L3 cache size

You can configure the L3 cache size to be:

- 0KB

- 256KB

- 512KB

- 1MB

- 1.5MB

- 2MB

- 3MB

- 4MB

- 6MB

- 8MB

- 12MB

- 16MB

- 24MB

- 32MB

Setting the size of OKB implements the DSU-120 without an L3 cache, see 2.3.2 L3 memory system variants on page 27.

### L3 cache slices

You can configure the DSU-120 to have 1, 2, 4, or 8 cache slices. For more information on cache slices, see 7.8 Cache slices and power portions on page 109.

#### **Transport configuration**

The topology of the transport mechanism is automatically determined, dependent on the number of cores and L3 cache slices in your cluster. However, you can set transport data

path width. For information on the DSU-120 transport, see RTL configuration process in Arm<sup>®</sup> DynamIQ<sup>™</sup> Shared Unit-120 Configuration and Integration Manual.

## Memory interface configuration

You can configure the main memory interface to either use a CHI coherent interface or an AXI non-coherent interface. For either type of memory interface, you can configure the DSU-120 to have 1, 2, 3, or 4 bus master interfaces.

#### ACP interface

You can include up to two Accelerator Coherency Port (ACP) interfaces and specify their size.

### **Peripheral Port**

You can include the Peripheral Port and specify its size. You can also configure it to be a noncoherent bus master interface.

### SCU cache protection

You can configure the L3 cache and snoop filter RAMs with *Error Correcting Code* (ECC) support.

### **Timing closure**

You can configure the L3 cache RAM timing latency and optionally include register slices.

### ELA

Include support for integrating the CoreSight *Embedded Logic Analyzer* (ELA)-600 into the DSU-120.

The ELA-600 is a separately licensable product.

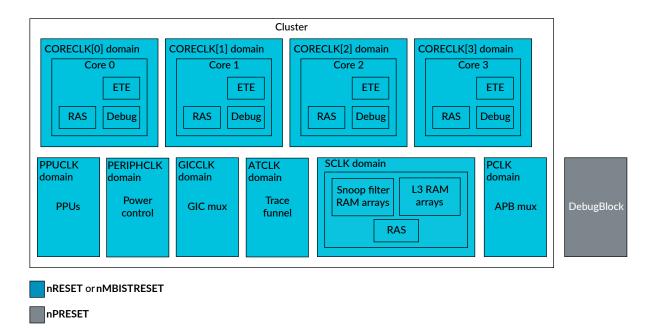

## 2.3 Cluster configurations

A cluster can be configured with up to three different types of cores in the same cluster. Each core type targeting different power efficiency and performance levels. This arrangement allows for an intermediate core that has an intermediate performance and efficiency level. The cluster also supports complexes.

A cluster can be configured in many arrangements. Examples of cluster arrangements are:

- One or more cores of the same type.

- Various arrangements of two types of cores. For example, one or more cores targeting either a high-performance level or a higher power efficiency level.

- Various arrangements of three of cores. For example, one or more high-performance cores, power-efficient cores, and intermediate cores.

- One or more complexes and no individual cores. For information on complexes, see 2.3.1 What is a complex? on page 25.

• One or more complexes and individual cores.

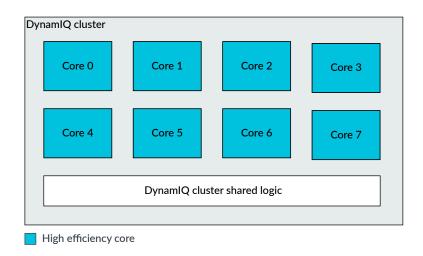

The following figure shows a cluster that is configured with all the same type of core.

Figure 2-2: DynamIQ cluster with one type of core

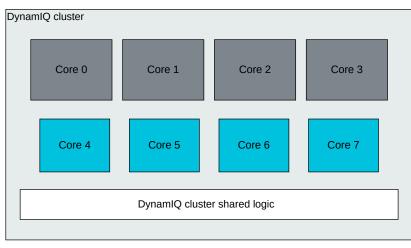

The following figure shows a cluster that is configured with two types of core.

Figure 2-3: DynamIQ cluster with two types of cores

High efficiency core

High performance core

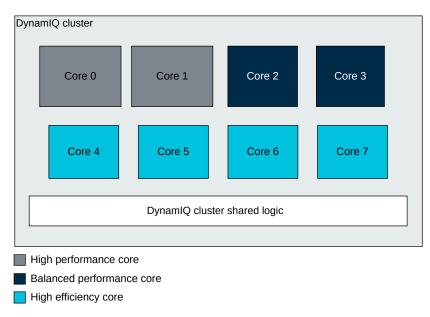

The following figure shows a cluster that is configured with three types of core.

Figure 2-4: DynamIQ cluster with three types of cores

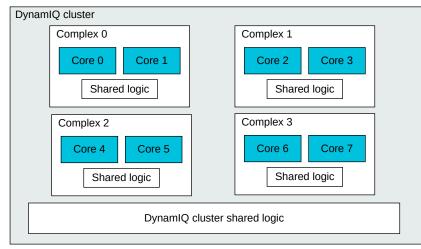

The following figure shows a cluster that is configured with four complexes.

Figure 2-5: DynamIQ cluster with four complexes

Supported core in complex

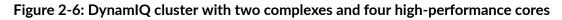

The following figure shows a cluster that is configured with two complexes, and four individual cores.

Supported core in complex

Most DSU-120-compatible cores support use in a multi-core cluster. Any combination of these cores should be configurable in the cluster provided that:

- The total number of cores does not exceed 14.

- There are no more than three different types of core in the cluster.

For any combinations that are specifically not permitted see the.*Arm*® *DSU-120* (*MP147*) *Release Note*

Not all cores support use in a multi-core cluster. For example, some types of core might only support a Direct connect configuration, so that only a single core can be instantiated in the cluster. For information about the type of core you have licensed, for example, if it only supports Direct connect configuration, see your core Release Note.

## 2.3.1 What is a complex?

The DSU-120 DynamIQ<sup>™</sup> cluster supports blocks that are called complexes which contain up to two cores of the same type and some shared logic. Sharing some logic between the two cores of a dual core complex can make the dual core complex area efficient. However, this area efficiency is at the cost of reduced performance compared with using two single-core complexes.

Only certain types of cores which have a merged-core microarchitecture can be used in a complex. To see if your core is supported in a complex and for further details of complexes, see your core *Technical Reference Manual* (TRM). The maximum number of cores instantiated in the cluster is 14. This number includes:

- Any cores that are not instantiated in a complex. These cores are called standalone cores.

- Any cores instantiated in single core complexes.

- Any cores instantiated in dual core complexes.

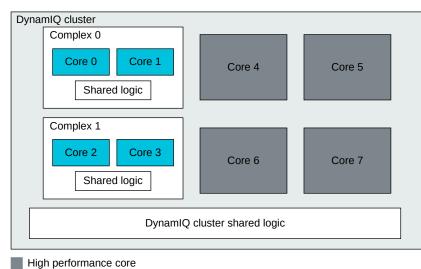

The following figure shows a cluster that contains a dual-core complex and a single-core complex.

## Figure 2-7: Cluster with a dual-core complex and a single-core complex

Supported core in complex

When a core type can be defined as part of a complex, then all instances of that core type (in the cluster) are implemented as complexes. This is either as part of a single-core complex or dual-core complex. Having all instances of a core type formed into complexes within the cluster, ensures consistent clock and power management control.

Within a dual-core complex, logic such as a Vector Processing Unit (VPU), L2 Translation Lookaside Buffer (TLB), and L2 cache logic is shared between the cores and is collectively known as shared logic. In a single-core complex, the same logic resides outside the core but is collectively known as dedicated logic.

There is a tradeoff in area and performance between implementing a dual-core complex compared with two single-core complexes or two single cores. A dual-core complex provides better area efficiency but with some reduced performance.

In this document, where reference to a core is made on its own, unless otherwise stated, you can assume this refers to all cores within the cluster. Therefore, this usage applies to both cores within complexes, called complexed cores, and standalone cores.

When describing functionality of the cores, the complexed core is assumed to include the complex shared logic and the unified cache unless otherwise stated. If the functionality being described only applies to either standalone cores or complexed cores, this is stated. In certain situations, appropriate for emphasis, where functionality applies to both standalone cores and complexed cores it is also stated.

## **Related information**

2.3 Cluster configurations on page 22

2.7 Core, complex, and processing element numbering on page 32

## 2.3.2 L3 memory system variants

By default the *DynamlQ<sup>™</sup>* Shared Unit-120 (DSU-120) is implemented with an L3 cache. Depending on your requirements, you can instead implement the DSU-120 without an L3 cache. Alternatively you can implement the DSU-120 to support a Direct connect connection to your core if your core supports this.

Not all cores support Direct connect. To check if your core supports Direct connect, see your core *Technical Reference Manual* (TRM).

There are three possible L3 memory system implementations:

### L3 cache present

This is the default implementation. It provides the most functionality and is suitable for general-purpose workloads.

### L3 cache not present

In this implementation, the L3 cache is not present but snoop filter and *Snoop Control Unit* (SCU) logic are present.

This variant allows multiple cores in the cluster and manages the coherency between them. It supports other implementation options such as *Accelerator Coherency Port* (ACP), Peripheral Port, and AXI or CHI master ports. Excluding the L3 cache RAMs saves layout area but performance of typical workloads is reduced. Therefore, Arm recommends that this variant is only used in specialized use cases, or when there is a system cache present that can be used by the cores.

## Direct connect

In the Direct connect implementation, the L3 cache, snoop filter, and SCU logic are not present.

This variant is specifically for use with a CHI interconnect. It offers extra area savings and reduced latency when compared to the previous variants. Because there is no L3 cache in the cluster, this variant relies on the system cache in the interconnect for performance. To check if your core supports this variant, see the *DSU-120 dependent features* section in your core TRM.

Because this variant does not include any coherency logic, it is only supported when there is a single core or single-complex in the cluster. When the DSU-120 is configured for Direct connect, optional interfaces such as ACP or the peripheral port are not supported. See the *hayden.yaml configuration parameters* section in the *RTL configuration process* chapter of the

Arm<sup>®</sup> DynamIQ<sup>™</sup> Shared Unit-120 Configuration and Integration Manual for more information. The master port must be a single 256-bit CHI interface.

The following diagram shows the DSU-120 implemented with Direct connect.

For more information on how to implement the DSU-120 with one of the L3 memory system variants, see the Configuration Guidelines chapter in Arm<sup>®</sup> DynamlQ<sup>™</sup> Shared Unit-120 Configuration and Integration Manual.

## **Related information**

2.2 DynamIQ Shared Unit-120 configuration parameters on page 202.1 DynamIQ Shared Unit-120 features on page 18

## 2.4 Supported standards and specifications

The *DynamlQ<sup>™</sup> Shared Unit-120* (DSU-120) complies with the Arm<sup>®</sup>v9.2-A architecture and all previous Arm<sup>®</sup>v8-A architectures up to Arm<sup>®</sup>v8.7-A.

The following table lists the architectures that the DSU-120 is compliant with.

### Table 2-1: Standards and specifications support in the DSU-120

| Standard of specification                                                                                        | Version                                                  | Notes                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arm architecture                                                                                                 | Arm®v9.2-A                                               | The DSU-120 supports cores based on<br>the Arm®v9.2-A architecture. These<br>cores also support previous Arm®v8-A<br>architectures up to Arm®v8.7-A,<br>dependent on the core. |

|                                                                                                                  |                                                          | See the section Supported standards<br>and specifications in your core Technical<br>Reference Manual (TRM) for details.                                                        |

| FEAT_RAS, Reliability, Availability, and<br>Serviceability (RAS)                                                 | RAS v8.4                                                 | The DSU-120 supports RAS features that<br>conform to the v8.4 RAS architecture,<br>see 12. RAS extension support on page<br>164.                                               |

| FEAT_RME, Realm Management Extension<br>(RME)                                                                    | Arm®v9.2-A                                               | The DSU-120 supports RME, see 2.4.1<br>Realm management extension on page<br>30.                                                                                               |

| Advanced Microcontroller Bus Architecture                                                                        | AMBA 5 CHI Issue E                                       | For more information on what AMBA                                                                                                                                              |

| (AMBA)                                                                                                           | AMBA 5 CHI Issue F                                       | protocols the DSU-120 interfaces support, see 3.4 Interfaces on page                                                                                                           |

|                                                                                                                  | AMBA AXI5 Issue H                                        | 41.                                                                                                                                                                            |

|                                                                                                                  | AMBA AXI5 Issue J                                        |                                                                                                                                                                                |

|                                                                                                                  | AMBA APB5 Issue D.                                       |                                                                                                                                                                                |

|                                                                                                                  | If RME is supported, AMBA APB5 Issue E protocol is used. |                                                                                                                                                                                |

| CoreSight <sup>™</sup> architecture                                                                              | v3.0                                                     | For more information on CoreSight <sup>™</sup><br>architecture, see the Arm <sup>®</sup> CoreSight <sup>™</sup><br>Architecture Specification v3.0.                            |

| Debug                                                                                                            | Arm®v9.2-A                                               | Arm®v9.2-A architecture that is<br>implemented with Arm®v8.4-A Debug<br>architecture support and Arm®v8.3-A<br>FEAT_DoPD, Debug over PowerDown<br>support.                     |

|                                                                                                                  |                                                          | See FEAT_DoPD in the Arm <sup>®</sup> Architecture<br>Reference Manual for A-profile architecture<br>for information on this architectural<br>feature.                         |

| FEAT_GICv4p1, Generic Interrupt<br>Controller (GIC) architecture CPU<br>interface and Stream Protocol interface. | GICv4.1                                                  | The DSU-120 uses Affinity level 1 to<br>distinguish between different cores. This<br>level is not supported by some interrupt<br>controllers, such as GIC-500.                 |

|                                                                                                                  |                                                          | For information on FEAT_GICv4p1,<br>see Arm <sup>®</sup> Generic Interrupt Controller<br>Architecture Specification, GIC architecture                                          |

|                                                                                                                  |                                                          | version 3 and version 4.                                                                                                                                                       |

## **Related information**

3.2 DynamIQ cluster shared logic components on page 363.4 Interfaces on page 41

## 2.4.1 Realm management extension

The DynamlQ<sup>™</sup> Shared Unit-120 (DSU-120) can use the Realm Management Extension (RME) for a core that supports RME, provided that the cluster is configured in Direct connect and the input signal LEGACYTZEN is LOW.

Throughout this book, where reference is made to the phrase, RME supported, for example when referring to what bus protocols are supported, this indicates that:

- The cluster is in Direct connect.

- The core in the cluster supports RME.

Throughout this book, where reference is made to the phrase, RME enabled, for example when referring to register access, this indicates that:

- RME is supported

- The input signal LEGACYTZEN is LOW.

If any of the previous conditions are not satisfied, then RME cannot be used. For example, a core could be configured for Direct connect, and support RME, but if the signal LEGACYTZEN is HIGH, then the DSU-120 reverts to TrustZone security.

For more information on RME, see Arm<sup>®</sup> Architecture Reference Manual Supplement, The Realm Management Extension (RME), for Armv9-A.

## 2.5 Test features

The DynamlQ<sup>™</sup> Shared Unit-120 (DSU-120) provides test signals that enable the use of Automatic Test Pattern Generation (ATPG) to test the Snoop Control Unit (SCU) and other logic in the DSU-120. Additionally, internal Memory Built-In Self Test (MBIST) interfaces are provided to test the L3 cache and other memory arrays of the DSU-120.

The DSU-120 includes an ATPG test interface that provides signals to control the *Design for Test* (DFT) features of the DSU-120, and the cores in the cluster. For example, there are signals to control the resets on the flip-flops during scan shift. Consideration of how you use these signals can help to prevent problems with DFT implementation.

Arm<sup>®</sup> also provides an MBIST interface that enables you to test the DSU-120 RAMs at operational frequency. You can add your own MBIST controllers to automatically generate test patterns and perform result comparisons. Optionally, you can use your EDA MBIST interfaces instead of the MBIST interfaces supplied by Arm<sup>®</sup>.

For a list of external scan control signals and information on their usage, see the Design for Test integration guidelines chapter in the Arm<sup>®</sup> DynamlQ<sup>™</sup> Shared Unit-120 Configuration and Integration Manual. For information about the test signals related to your core, see your core Configuration and Integration Manual.

## 2.6 Design Tasks

Both the DynamlQ<sup>M</sup> Shared Unit-120 (DSU-120) and the cores in the cluster are delivered as synthesizable RTL descriptions in Verilog HDL. Before you can use the DSU-120 and the cores, you must implement them, integrate them, and program them.

A different party can perform each of the following tasks. Each task can include implementation and integration choices that affect the behavior and features of the DSU-120 and the cores.

### Implementation

The implementer configures and synthesizes the RTL to produce a hard macrocell. This task includes integrating RAMs into the design.

#### Integration

The integrator connects the macrocell into a System on Chip (SoC). This task includes connecting the macrocell to the memory system and peripherals.

### Programming

In the final task, the system programmer develops the software to configure and initialize the DSU-120 and the cores in the cluster and tests the application software.

The operation of the final device depends on the following:

## **Build configuration**

The implementer chooses the options that affect how the RTL source files are pre-processed.

These options usually include or exclude logic that affects one or more of the area, maximum frequency, and features of the resulting macrocell.

## **Configuration inputs**

The integrator configures some features of the DSU-120 and cores in the cluster by tying inputs to specific values.

These configuration settings affect the start-up behavior before any software configuration is made. They can also limit the options available to the software.

## Software configuration

The programmer configures the DSU-120 and the cores in the cluster by programming values into registers. The configuration choices affect the behavior of the DSU-120 and the cores.

For implementation options, see the following:

- RTL configuration process in the Configuration and Integration Manual for your licensed core

- RTL configuration process in the Arm<sup>®</sup> DynamIQ<sup>™</sup> Shared Unit-120 Configuration and Integration Manual

## **Related information**

14. System control registers on page 179

## 2.7 Core, complex, and processing element numbering

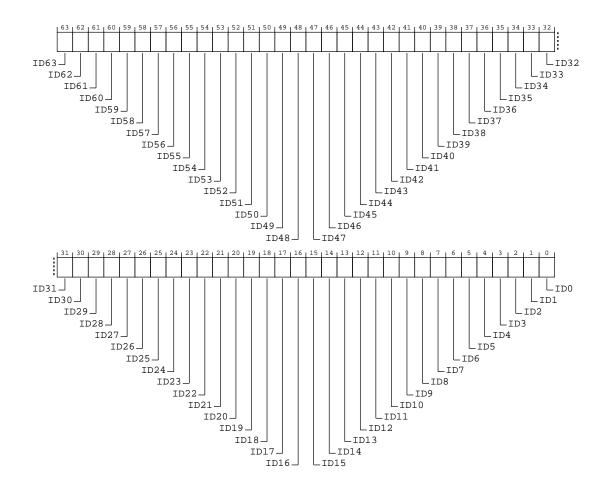

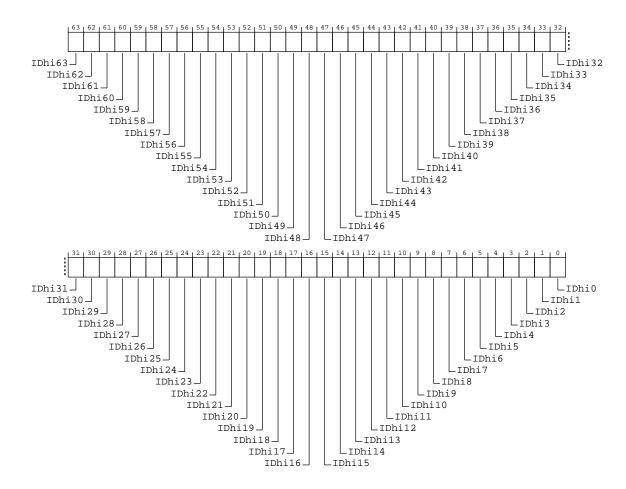

A cluster contains one or more cores. The cluster can also contain one or more complexes which can be made up of either a single core or two cores. Because certain parts of the design, such as signal names and register bit values, depend on the number of cores and complexes within the cluster, a numbering system has been created.

Throughout this document, the following numbering is used for cores, *Processing Elements* (PEs), and complexes:

### Core

The numbering of core instances in the cluster ranges from zero to CN, where CN has the value of the total number of cores minus one. This numbering also includes cores instantiated within a complex. For example, CN = 5 for a cluster comprised of two dual-core complexes and two standalone cores.

For individual core instances, the term y is used, which ranges from zero to CN. For example, when referring to the second instance of a core, y = 1. The term y is called the core instance number.

#### Complexes

The numbering of complex instances in the cluster ranges from zero to CX, where CX has the value of total number of complexes minus one. For example, CX = 1 for a cluster comprised of two complexes.

For individual complex instances, the term x is used, which ranges from zero to CX. For example, when referring to the second instance of a complex, x = 1. The term x is called the complex instance number.

## **Processing element**

The Arm architecture allows for cores to support multiple *Processing Elements* (PEs).

The *DynamlQ<sup>™</sup>* Shared Unit-120 (DSU-120) supports cores with multiple PEs. Where a reference to a core is made, the core could be a core with only one PE (single-threaded core) or multiple PEs (multi-threaded core).

PEN is the total number of PEs in the cluster, starting from zero. This numbering also includes cores within complexes. For example, PEN = 5 for a cluster comprised of two dual-core complexes and two standalone cores, with all cores having one PE each.

For reference to individual PEs, the term z is used, which ranges from zero to PEN. For example, when referring to the second PE, z = 1.

In the current DSU-120, each core only has one PE. Therefore, PEN = CN.

For more information on the instance numbering for cores and complexes in the cluster, see *RTL* configuration process in the *Arm*<sup>®</sup> *DynamIQ*<sup>™</sup> *Shared Unit-120 Configuration and Integration Manual.*

## 2.8 Product revisions

The product revision increments at each release.

The following table indicates the main differences in functionality between product revisions.

Table 2-2: Product revisions

| Revision | Notes                                                                                          |

|----------|------------------------------------------------------------------------------------------------|

| r0p0     | First release                                                                                  |

| r1p0     | Support for L2 cache stashing and Accelerator Coherency Port (ACP) peripheral port dependency. |

Changes in functionality that have an impact on the documentation also appear in C. Revisions on page 945.

# 3. Technical overview

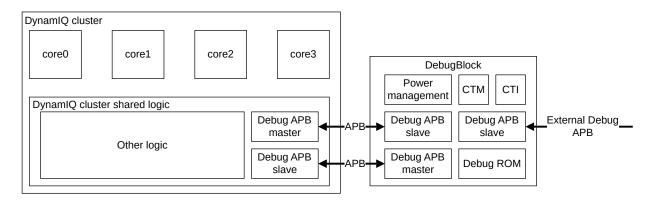

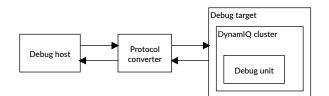

A DynamlQ<sup>™</sup> Shared Unit-120 (DSU-120) cluster-based system is also known as a DSU-120.

The DSU-120 comprises two top-level modules, these are:

## A module to form a DSU-120 DynamlQ<sup> $\mathrm{M}$ </sup> cluster

This module includes the cores, complexes and the DynamlQ<sup>™</sup> cluster shared logic.

## A separate module for the DebugBlock

Separating the debug components from the DSU-120 DynamlQ<sup>™</sup> cluster enables the debug components to be implemented in a separate power domain, or to be combined with an existing system power domain, allowing debug over power down.

All the main *System on Chip* (SoC) interfaces appear at the top level of the DSU-120. The DSU-120 connects the cores and complexes to an external memory system and the rest of the SoC.

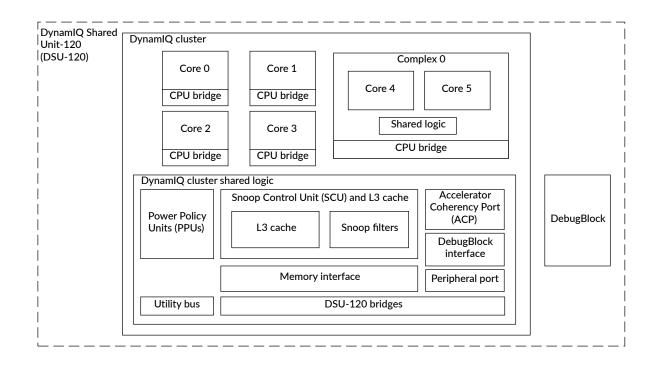

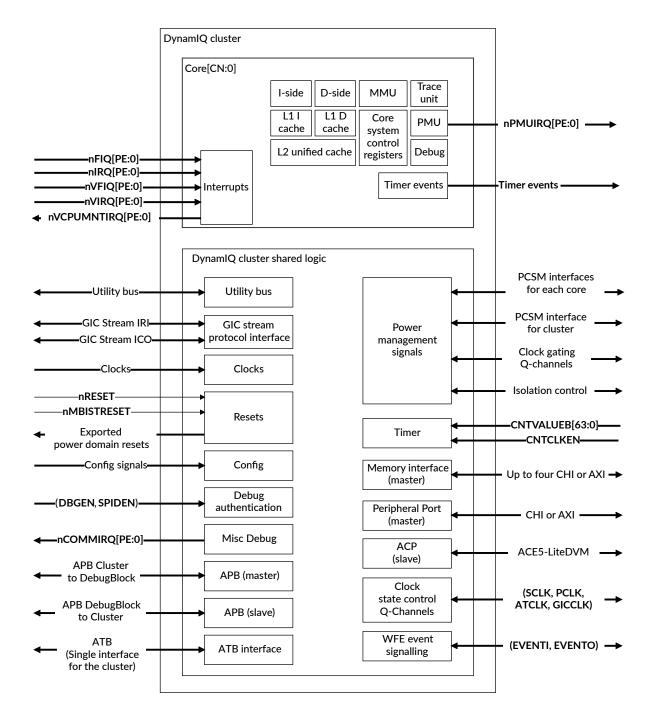

## 3.1 DynamIQ cluster components

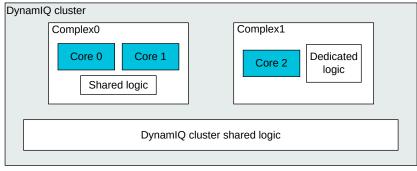

The DSU-120 DynamIQ<sup>™</sup> cluster contains all the cores and complexes together with the DynamIQ<sup>™</sup> cluster shared logic. All the DynamIQ<sup>™</sup> cluster shared logic is automatically connected to the cores and complexes by the configuration script during build-time configuration.

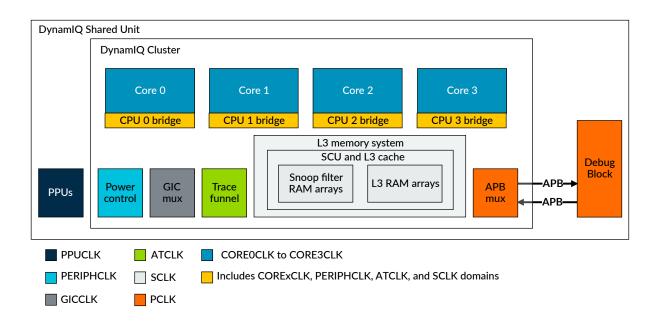

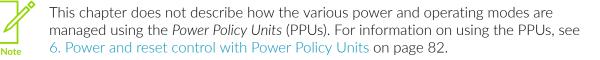

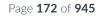

The following figure shows the main components that make up the DSU-120 DynamlQ<sup>T</sup> cluster within the DSU-120.

## Figure 3-1: DSU-120 DynamIQ<sup>™</sup> cluster components

## Cores

There can be up to 14 cores in the DSU-120 DynamlQ<sup>™</sup> cluster, with up to three different types of core. For information on the behavior and features of each core, see the *Technical Reference Manual* (TRM) of each core.

## Complexes

The DSU-120 DynamIQ<sup>™</sup> cluster also supports up to either 14 single-core complexes, or seven dual- core complexes. Complexes are made up of specialized cores. See 2.3.1 What is a complex? on page 25. See the *DSU-120 dependent features* section in your core TRM to determine if your core is supported in a complex.

## DynamIQ<sup>™</sup> cluster shared logic

The DynamIQ<sup>™</sup> cluster shared logic forms part of the DSU-120 DynamIQ<sup>™</sup> cluster. See 3.2 DynamIQ cluster shared logic components on page 36.

## **Related information**

- 3.2 DynamIQ cluster shared logic components on page 36

- 3.3 DebugBlock components on page 39

- 2.3 Cluster configurations on page 22

- 2.3.1 What is a complex? on page 25

## 3.1.1 Integration of the cores in the cluster

When you implement a DSU-120 DynamlQ<sup>M</sup> cluster, all interfacing between the cores, complexes, and the DynamlQ<sup>M</sup> Shared Unit-120 (DSU-120) is implemented automatically. All the external signal inputs and outputs pass through the DSU-120. The DSU-120 buffers and resynchronizes many of these signals to allow cores and complexes to be clocked at different speeds.

The memory interfacing of each core is internally connected to the DSU-120 L3 memory system. Where necessary, the DSU-120 implements additional buffering to compensate for different clock rates of the core and DSU-120 L3 memory system.

Each core has an external clock interface, which is routed through the DSU-120 to the respective core.

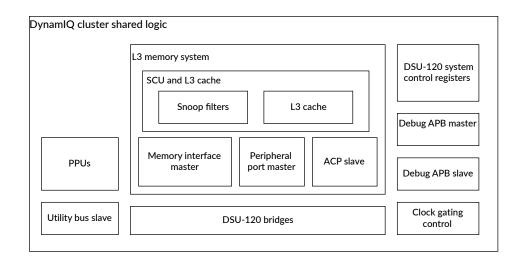

## 3.2 DynamIQ<sup>™</sup> cluster shared logic components

The DynamIQ<sup>™</sup> cluster shared logic includes the following components:

## **Snoop Control Unit**

The Snoop Control Unit (SCU) maintains coherency between all the data caches in the cluster.

The SCU contains buffers that can handle direct cache-to-cache transfers between cores without having to read or write data to the L3 cache. Cache line migration enables dirty lines to be moved between cores. Also, there is no requirement to write back transferred cache line data to the L3 cache.

The SCU contains a set of snoop filters that track the addresses for locations cached in the core caches. Including the snoop filters means that the SCU does not need to request a look up in the core caches when it receives a coherent memory request. These snoop filters are accessed by the coherent requests from the other cores or from the system. If there is a simultaneous hit in the L3 tags and the SCU snoop filters, then the L3 cache normally provides the data in preference to a core. The size of the snoop filter is automatically determined from the configured number of cores and the cache sizes in those cores.

## **Clock management**

Clock gating is supported through Q-Channel requests from an external clock controller to the DSU-120. The Q-Channels allow individual control of the following clock input signals:

- ATCLK

- COREyCLK where y is the core instance number

- COMPLEXxCLK where x is the complex instance number

- GICCLK

- PCLK

- PERIPHCLK

- PPUCLK

- SCLK

### L3 memory interfaces

#### Main memory master

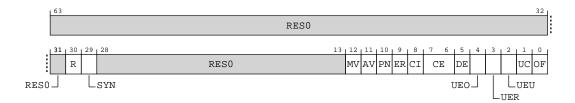

The main memory master provides an interface between the DynamIQ<sup>™</sup> Shared Unit-120 and the external interconnect. For a connection to an external coherent interconnect, the memory interface must be configured to use the AMBA 5 CHI (Issue E) protocol. For connection to a non-coherent external interconnect, the memory interface can either be configured to use the CHI protocol or AXI5 (Issue H) protocol. In either configuration, the interfaces are 256-bit wide, with support up to four bus master ports.

#### **Accelerator Coherency Port**

The Accelerator Coherency Port (ACP) is an optional slave interface. The ACP provides direct memory access to cacheable memory. The SCU maintains cache coherency by checking ACP accesses for allocation in the core and L3 caches. The ACP implements a subset of the ACE-Lite protocol. Up to two ACP interfaces can be configured, with each interface configured to either 128-bit wide or 256-bit wide.

#### Peripheral port

The peripheral port is an optional master interface and provides accesses to tightly coupled accelerators. The port implements the AXI5 or CHI Issue E master interface protocol.

#### Utility bus

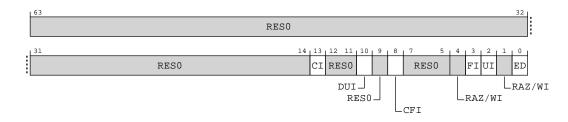

The utility bus is a 64-bit AXI5 slave interface that provides access to the control registers for various system components in the cluster. The control registers are memory-mapped onto the utility bus. The utility bus provides programming access to the following system components:

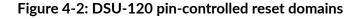

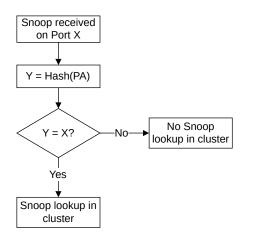

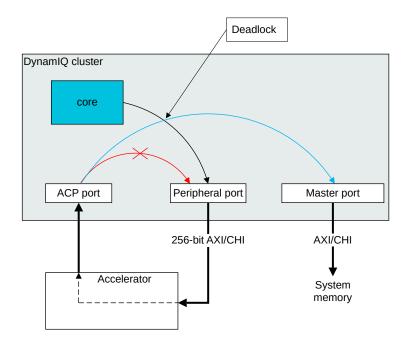

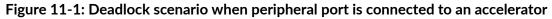

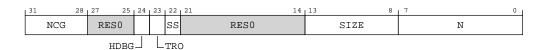

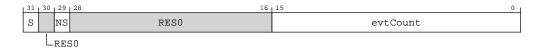

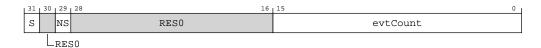

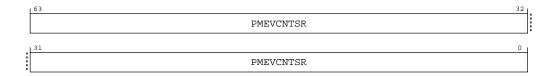

- PPUs