# **Arm<sup>®</sup> Compiler for Embedded**

Version 6.20

# **User Guide**

Non-Confidential

Issue 00

Copyright © 2019-2023 Arm Limited (or its affiliates). 100748\_6.20\_00\_en All rights reserved.

### Arm® Compiler for Embedded

#### **User Guide**

Copyright © 2019–2023 Arm Limited (or its affiliates). All rights reserved.

#### Release information

#### **Document history**

| Issue       | Date                | Confidentiality      | Change                                                 |

|-------------|---------------------|----------------------|--------------------------------------------------------|

| 0613-<br>00 | 9 October 2019      | Non-<br>Confidential | Arm Compiler v6.13 Release.                            |

| 0614-<br>00 | 26 February 2020    | Non-<br>Confidential | Arm Compiler v6.14 Release.                            |

| 0615-<br>00 | 7 October 2020      | Non-<br>Confidential | Arm Compiler v6.15 Release.                            |

| 0615-<br>01 | 14 December<br>2020 | Non-<br>Confidential | Documentation update 1 for Arm Compiler v6.15 Release. |

| 0616-<br>00 | 3 March 2021        | Non-<br>Confidential | Arm Compiler v6.16 Release.                            |

| 0616-<br>01 | 12 March 2021       | Non-<br>Confidential | Documentation update 1 for Arm Compiler v6.16 Release. |

| 0617-<br>00 | 20 October 2021     | Non-<br>Confidential | Arm Compiler for Embedded v6.17 Release.               |

| 0618-<br>00 | 22 March 2022       | Non-<br>Confidential | Arm Compiler for Embedded v6.18 Release.               |

| 0619-<br>00 | 12 October 2022     | Non-<br>Confidential | Arm Compiler for Embedded v6.19 Release.               |

| 0620-<br>00 | 15 March 2023       | Non-<br>Confidential | Arm Compiler for Embedded v6.20 Release.               |

### **Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied,

by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or ™ are registered trademarks or trademarks of Arm Limited (or its affiliates) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at https://www.arm.com/company/policies/trademarks.

Copyright © 2019–2023 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

(LES-PRE-20349|version 21.0)

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

#### **Product Status**

The information in this document is Final, that is for a developed product.

#### **Feedback**

Arm® welcomes feedback on this product and its documentation. To provide feedback on the product, create a ticket on https://support.developer.arm.com

To provide feedback on the document, fill the following survey: https://developer.arm.com/documentation-feedback-survey.

### Inclusive language commitment

Arm values inclusive communities. Arm recognizes that we and our industry have used language that can be offensive. Arm strives to lead the industry and create change.

We believe that this document contains no offensive language. To report offensive language in this document, email terms@arm.com.

# **Contents**

| List of | Figures1 | .3 |

|---------|----------|----|

| List of | Tables   | .5 |

| 1. Introduction                                                             | 17 |

|-----------------------------------------------------------------------------|----|

| 1.1 Conventions                                                             | 17 |

| 1.2 Useful resources                                                        | 18 |

| 1.3 Other information                                                       | 20 |

| 2. Getting Started                                                          | 21 |

| 2.1 Introduction to Arm Compiler for Embedded 6                             | 21 |

| 2.2 About the Arm Compiler for Embedded toolchain assemblers                | 24 |

| 2.3 System requirements and installation                                    | 25 |

| 2.4 Accessing Arm Compiler for Embedded from Arm Development Studio         | 28 |

| 2.5 Accessing Arm Compiler for Embedded from the Arm Keil $\mu Vision\ IDE$ | 28 |

| 2.6 Compiling a Hello World example                                         | 28 |

| 2.7 Using the integrated assembler                                          | 31 |

| 2.8 Running bare-metal images                                               | 34 |

| 2.9 Architectures supported by Arm Compiler for Embedded 6                  | 35 |

| 2.10 Using Arm Compiler for Embedded securely in a shared environment       | 36 |

| 2.11 Providing source code to Arm support                                   | 36 |

| 2.12 Build attributes                                                       | 37 |

| 3. Using Common Compiler Options                                            | 40 |

| 3.1 Mandatory armclang options                                              | 4C |

| 3.2 Common Arm Compiler for Embedded toolchain options                      | 42 |

| 3.3 Selecting source language options                                       | 45 |

| 3.4 Selecting optimization options                                          | 50 |

| 3.5 Building to aid debugging                                               | 54 |

| 3.6 Linking object files to produce an executable                           | 56 |

| 3.7 Linker options for mapping code and data to target memory               | 56 |

| 3.8 Passing options from the compiler to the linker                         | 58 |

| 3.9 Controlling diagnostic messages                                         | 59 |

| 3.10 Selecting floating-point options                                       | 65 |

| 3.11 Compilation tools command-line option rules                            | 69 |

| 4. Writing Optimized Code                                                   | 70 |

| 4.1 Effect of the volatile keyword on compiler optimization                 | 7C |

| 4.2 Optimizing loops                                                        | 73 |

| 4.3 Inlining functions                                                      |    |

| 4.4 Stack use in C and C++                                                  | 81 |

| 4.5 Packing data structures                                                      | 85  |

|----------------------------------------------------------------------------------|-----|

| 4.6 Optimizing for code size or performance                                      | 89  |

| 4.7 Methods of minimizing function parameter passing overhead                    | 91  |

| 4.8 Optimizing across modules with Link-Time Optimization                        | 92  |

| 4.8.1 Enabling Link-Time Optimization                                            | 93  |

| 4.8.2 Restrictions with Link-Time Optimization                                   | 94  |

| 4.8.3 Removing unused code across multiple object files                          | 96  |

| 4.9 Scatter file section or object placement with Link-Time Optimization         | 98  |

| 4.10 How optimization affects the debug experience                               | 105 |

| 4.11 Literal pool options in armclang                                            | 106 |

| 5. Assembling Assembly Code                                                      | 107 |

| 5.1 Assembling GNU syntax and armasm assembly code                               | 107 |

| 5.2 How to get a backtrace through assembler functions                           | 109 |

| 5.3 Preprocessing assembly code                                                  | 110 |

| 6. Using Assembly and Intrinsics in C or C++ Code                                | 112 |

| 6.1 Using intrinsics                                                             | 112 |

| 6.2 Custom Datapath Extension support                                            | 115 |

| 6.3 Writing inline assembly code                                                 | 117 |

| 6.4 Calling assembly functions from C and C++                                    | 120 |

| 7. SVE Coding Considerations with Arm Compiler for Embedded 6                    | 123 |

| 7.1 Introducing SVE                                                              | 123 |

| 7.2 Assembling SVE code                                                          | 124 |

| 7.3 Disassembling SVE object files                                               | 125 |

| 7.4 Running a binary in an AEMv8-A Base Fixed Virtual Platform (FVP)             | 126 |

| 7.5 Embedding SVE assembly code directly into C and C++ code                     | 130 |

| 7.6 Using SVE and SVE2 intrinsics directly in your C code                        | 135 |

| 8. Mapping Code and Data to the Target                                           | 143 |

| 8.1 What the linker does to create an image                                      | 143 |

| 8.1.1 What you can control with a scatter file                                   | 144 |

| 8.1.2 Interaction of OVERLAY and PROTECTED attributes with armlink merge options | 144 |

| 8.2 Support for Position Independent code                                        | 145 |

| 8.3 Placing data items for target peripherals with a scatter file                | 154 |

| 8.4 Placing the stack and heap with a scatter file                               | 155 |

| 8.5 Root region                                                                             | 156     |

|---------------------------------------------------------------------------------------------|---------|

| 8.5.1 Effect of the ABSOLUTE attribute on a root region                                     | 157     |

| 8.5.2 Effect of the FIXED attribute on a root region                                        | 158     |

| 8.6 Placing functions and data in a named section                                           | 160     |

| 8.7 Loading armlink-generated ELF files that have complex scatter-files                     | 162     |

| 8.8 Placement of functions and data at specific addresses                                   | 165     |

| 8.8.1 Placement ofat sections at a specific address                                         |         |

| 8.8.2 Restrictions on placingat sections                                                    | 166     |

| 8.8.3 Automatic placement ofat sections                                                     | 167     |

| 8.8.4 Manual placement ofat sections                                                        | 168     |

| 8.8.5 Place a key in flash memory with anat section                                         | 169     |

| 8.8.6 Placing constants at fixed locations                                                  | 170     |

| 8.8.7 Placing jump tables in ROM                                                            | 171     |

| 8.8.8 Placing a variable at a specific address without scatter-loading                      | 172     |

| 8.8.9 Placing a variable at a specific address with scatter-loading                         | 173     |

| 8.9 Bare-metal Position Independent Executables                                             | 175     |

| 8.10 Placement of Arm C and C++ library code                                                | 178     |

| 8.10.1 Placement of code in a root region                                                   | 178     |

| 8.10.2 Placement of Arm C library code                                                      | 179     |

| 8.10.3 Placing Arm C++ library code                                                         | 179     |

| 8.11 Manual placement of unassigned sections                                                | 180     |

| 8.11.1 Default rules for placing unassigned sections                                        | 181     |

| 8.11.2 Command-line options for controlling the placement of unassigned sections            | 182     |

| 8.11.3 Prioritizing the placement of unassigned sections                                    | 183     |

| 8.11.4 Specify the maximum region size permitted for placing unassigned sections            | 183     |

| 8.11.5 Examples of using placement algorithms for .ANY sections                             | 184     |

| 8.11.6 Example of next_fit algorithm showing behavior of full regions, selectors, and prior | ity 186 |

| 8.11.7 Examples of using sorting algorithms for .ANY sections                               | 188     |

| 8.11.8 Behavior when .ANY sections overflow because of linker-generated content             | 189     |

| 8.12 Placing veneers with a scatter file                                                    | 193     |

| 8.13 Preprocessing a scatter file                                                           | 194     |

| 8.14 Reserving an empty block of memory                                                     | 195     |

| 8.14.1 Characteristics of a reserved empty block of memory                                  | 195     |

| 8.14.2 Example of reserving an empty block of memory                                        | 196     |

| 8.15 Alignment of regions to page boundaries                                                | 197     |

| 8.16 Alignment of execution regions and input sections.                                     | 198     |

| 9. Overlays                                                              | 200 |

|--------------------------------------------------------------------------|-----|

| 9.1 Overlay support in Arm Compiler for Embedded 6                       | 200 |

| 9.2 Automatic overlay support                                            | 201 |

| 9.2.1 Automatically placing code sections in overlay regions             | 201 |

| 9.2.2 Overlay veneer                                                     | 203 |

| 9.2.3 Overlay data tables                                                | 204 |

| 9.2.4 Limitations of automatic overlay support                           | 205 |

| 9.2.5 About writing an overlay manager for automatically placed overlays | 206 |

| 9.3 Manual overlay support                                               | 207 |

| 9.3.1 Manually placing code sections in overlay regions                  | 207 |

| 9.3.2 Writing an overlay manager for manually placed overlays            | 209 |

| 10. Embedded Software Development                                        | 216 |

| 10.1 About embedded software development                                 | 216 |

| 10.2 Default compilation tool behavior                                   | 216 |

| 10.3 C library structure                                                 | 217 |

| 10.4 Default memory map                                                  | 218 |

| 10.5 Application startup                                                 | 219 |

| 10.6 Tailoring the C library to your target hardware                     | 221 |

| 10.7 Reimplement the C library functions                                 | 222 |

| 10.8 Tailoring the image memory map to your target hardware              | 224 |

| 10.9 About the scatter-loading description syntax                        | 225 |

| 10.10 Root regions                                                       | 226 |

| 10.11 Region Table format                                                | 226 |

| 10.12 Placing the stack and heap                                         | 228 |

| 10.13 Run-time memory models                                             | 229 |

| 10.14 Reset and initialization                                           | 230 |

| 10.15 The vector table                                                   | 232 |

| 10.16 ROM and RAM remapping                                              | 232 |

| 10.17 About Run-Time Type Information                                    | 233 |

| 10.18 Avoid linking in Run-Time Type Information                         | 234 |

| 10.19 Avoid linking in the Arm Compiler for Embedded libraries           | 236 |

| 10.20 Avoid linking in the Arm C library                                 | 239 |

| 10.21 Local memory setup considerations                                  | 241 |

| 10.22 Stack pointer initialization                                       | 242 |

| 10.23 Hardware initialization                                            | 243 |

| 10.24 Execution mode considerations                                               | 243 |

|-----------------------------------------------------------------------------------|-----|

| 10.25 Target hardware and the memory map                                          | 244 |

| 10.26 Execute-only memory                                                         | 245 |

| 10.27 Building applications for execute-only memory                               | 245 |

| 10.28 Vector table for AArch32 A and R profiles                                   | 246 |

| 10.29 Vector table for M-profile architectures                                    | 247 |

| 10.30 Vector Table Offset Register                                                | 248 |

| 10.31 Integer division-by-zero errors in C and C++ code                           | 248 |

| 10.32 Floating-point division-by-zero errors in C and C++ code                    | 249 |

| 10.33 Dealing with leftover debug data for code and data removed by armlink       | 251 |

| 10.34 Building images that are compatible with third-party tools                  | 252 |

| 11. Security features supported in Arm Compiler for Embedded                      | 254 |

| 11.1 Overview of Arm Compiler for Embedded security-related features              | 254 |

| 11.2 How optimization can interfere with security                                 | 259 |

| 11.3 Hardware errata and vulnerabilities                                          | 260 |

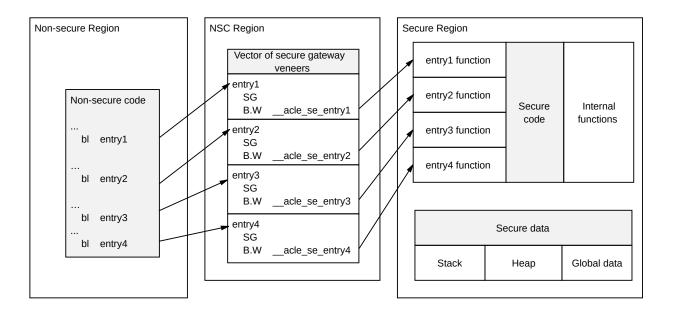

| 11.4 Overview of building Secure and Non-secure images with the Armv8-M Extension |     |

| 11.5 Building a Secure image using the Armv8-M Security Extension                 | 265 |

| 11.6 Building a Non-secure image that can call a Secure image                     | 269 |

| 11.7 Building a Secure image using a previously generated import library          | 270 |

| 11.8 Armv8.1-M PACBTI extension mitigations against ROP and JOP style attacks     | 275 |

| 11.9 Overview of the Realm Management Extension                                   | 279 |

| 11.10 Overview of memory tagging                                                  | 279 |

| 11.11 Overview of Control Flow Integrity                                          | 281 |

| 11.12 Overview of Undefined Behavior Sanitizer                                    | 283 |

| 12. Overview of the Linker                                                        | 284 |

| 12.1 About the linker                                                             | 284 |

| 12.1.1 Summary of the linker features                                             | 284 |

| 12.1.2 What the linker can accept as input                                        | 285 |

| 12.1.3 What the linker outputs                                                    | 286 |

| 12.2 armlink command-line syntax                                                  | 286 |

| 12.3 What the linker does when constructing an executable image                   | 287 |

| 13. Getting Image Details                                                         | 288 |

| 13.1 Options for getting information about linker-generated files                 | 288 |

| 13.2 Identifying the source of some link errors                                | 289 |

|--------------------------------------------------------------------------------|-----|

| 13.3 Example of using theinfo linker option                                    | 289 |

| 13.4 How to find where a symbol is placed when linking                         | 293 |

| 14. SysV Dynamic Linking                                                       | 295 |

| 14.1 Build a SysV shared object                                                | 295 |

| 14.2 Build a SysV executable                                                   | 296 |

| 15. Overview of the fromelf Image Converter                                    | 298 |

| 15.1 About the fromelf image converter                                         | 298 |

| 15.2 fromelf execution modes                                                   | 299 |

| 15.3 Getting help on the fromelf command                                       | 299 |

| 15.4 fromelf command-line syntax                                               | 300 |

| 16. Using fromelf                                                              | 301 |

| 16.1 General considerations when using fromelf                                 | 301 |

| 16.2 Examples of processing ELF files in an archive                            | 301 |

| 16.3 Options to protect code in image files with fromelf                       | 302 |

| 16.4 Options to protect code in object files with fromelf                      | 303 |

| 16.5 Option to print specific details of ELF files                             | 305 |

| 16.6 Using fromelf to find where a symbol is placed in an executable ELF image | 305 |

| 17. Overview of the Arm Librarian                                              | 308 |

| 17.1 About the Arm Librarian                                                   | 308 |

| 17.2 Considerations when working with library files                            | 308 |

| 17.3 armar command-line syntax                                                 | 309 |

| 17.4 Option to get help on the armar command                                   | 309 |

| 18. Overview of the armasm Legacy Assembler                                    | 311 |

| 18.1 Key features of the armasm assembler                                      | 311 |

| 18.2 How the assembler works                                                   | 312 |

| 19. Supporting reference information                                           | 314 |

| 19.1 Support level definitions                                                 | 314 |

| 19.2 Standards compliance in Arm Compiler for Embedded 6                       | 318 |

| 19.3 Compliance with the ABI for the Arm Architecture (Base Standard)          | 320 |

| 19.4 GCC compatibility provided by Arm Compiler for Embedded 6                 | 321 |

| 19.5 Locale support in Arm Compiler for Embedded 6                             | 322 |

| 19.6 Toolchain environment variables                     | 322 |

|----------------------------------------------------------|-----|

| 19.7 Clang and LLVM documentation                        | 324 |

| 19.8 typinfo.s example source code                       | 325 |

| 19.9 Further reading                                     | 330 |

| A. Arm Compiler for Embedded User Guide Changes          | 333 |

| A.1 Changes for the Arm Compiler for Embedded User Guide | 333 |

# List of Figures

| Figure 2-1: A typical tool usage flow diagram                    | 24  |

|------------------------------------------------------------------|-----|

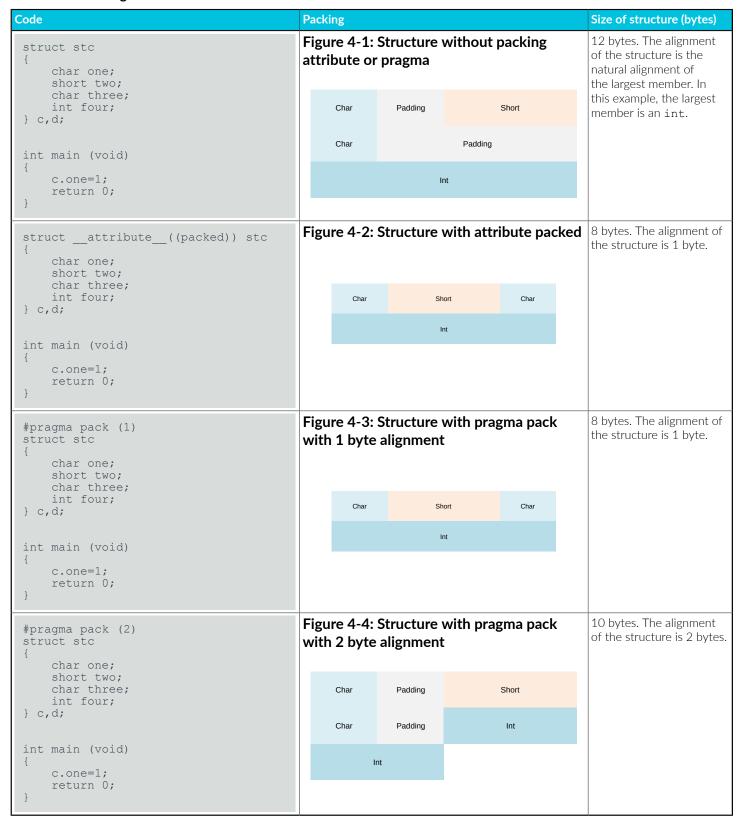

| Figure 4-1: Structure without packing attribute or pragma        | 87  |

| Figure 4-2: Structure with attribute packed                      | 87  |

| Figure 4-3: Structure with pragma pack with 1 byte alignment     | 87  |

| Figure 4-4: Structure with pragma pack with 2 byte alignment     | 87  |

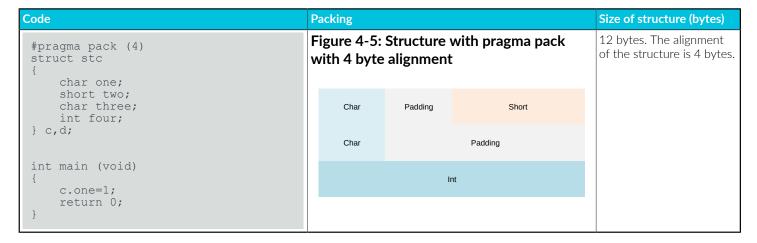

| Figure 4-5: Structure with pragma pack with 4 byte alignment     | 88  |

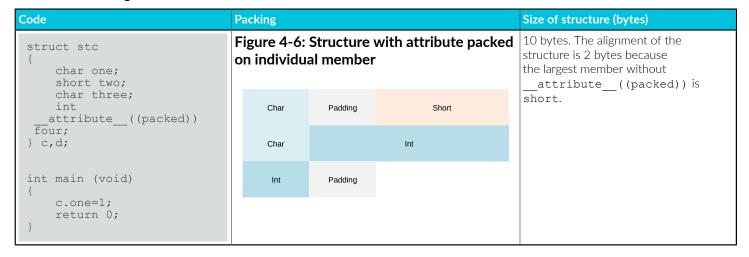

| Figure 4-6: Structure with attribute packed on individual member | 88  |

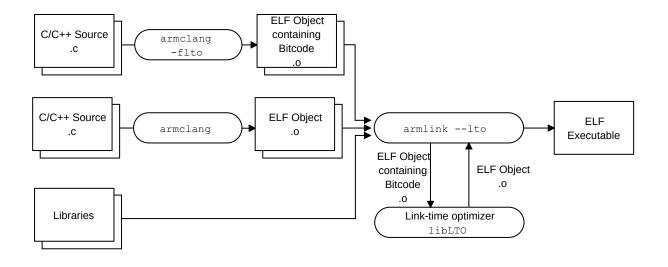

| Figure 4-7: Link-Time Optimization                               | 92  |

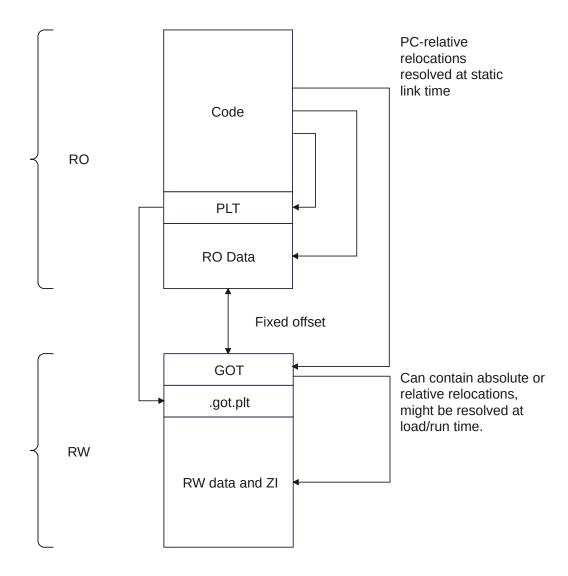

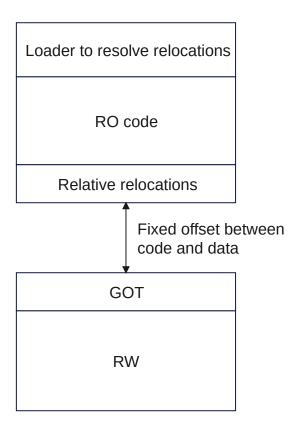

| Figure 8-1: Position Independent Code layout                     | 147 |

| Figure 8-2: Position Independent Code relative relocations       | 148 |

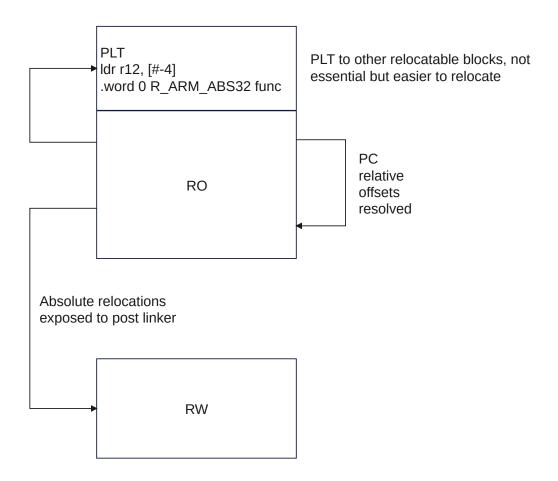

| Figure 8-3: Bare-metal PIE                                       | 149 |

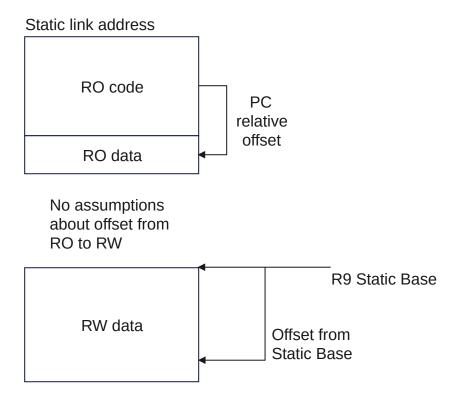

| Figure 8-4: ROPI and RWPI                                        | 151 |

| Figure 8-5: Base Platform                                        | 153 |

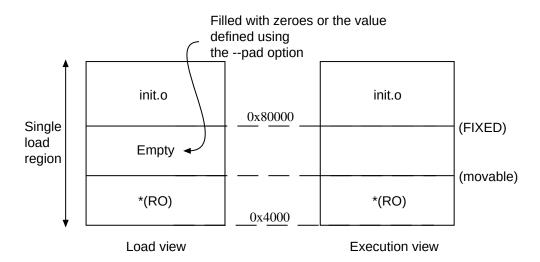

| Figure 8-6: Memory map for fixed execution regions               | 158 |

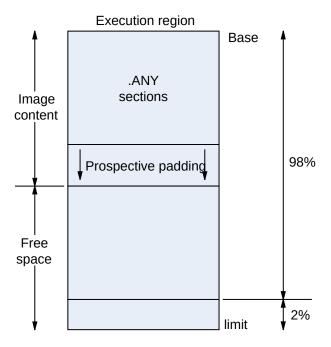

| Figure 8-7: .ANY contingency                                     | 190 |

| Figure 8-8: Reserving a region for the stack                     | 197 |

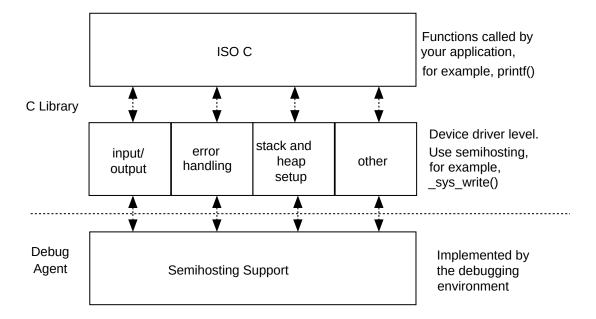

| Figure 10-1: C library structure                                 | 217 |

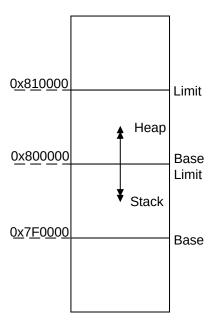

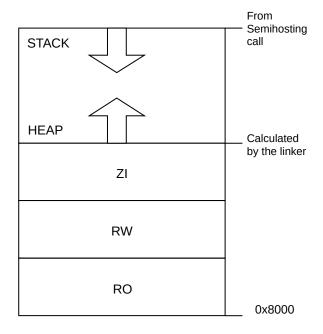

| Figure 10-2: Default memory map                                  | 218 |

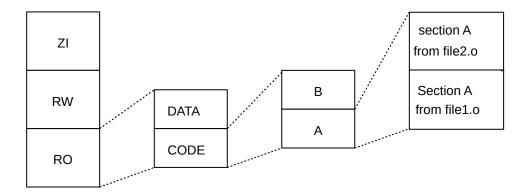

| Figure 10-3: Linker placement rules                              | 219 |

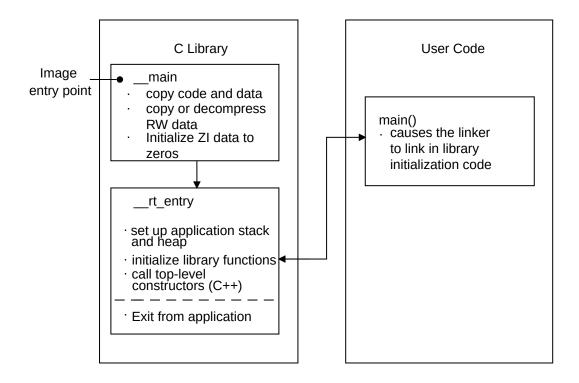

| Figure 10-4: Default initialization sequence                     | 220 |

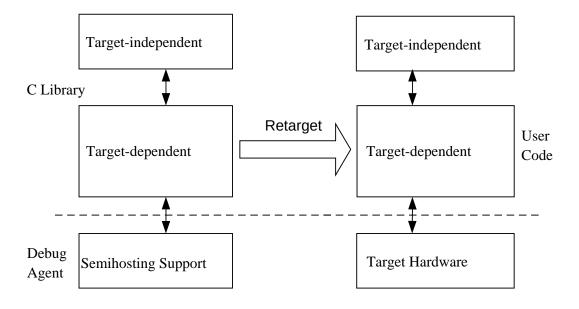

| Figure 10-5: Retargeting the C library                           | 221 |

| Figure 10-6: Scatter-loading description syntax                  | 225 |

| Figure 10-7: One-region model                                    | 229 |

| Figure 10-8: Two-region model                           | 230           |

|---------------------------------------------------------|---------------|

| Figure 10-9: Initialization sequence                    | 231           |

| Figure 19-1: Integration boundaries in Arm Compiler for | Embedded 6316 |

# List of Tables

| Table 2-1: Supported C and C++ source language variants               | 21 |

|-----------------------------------------------------------------------|----|

| Table 3-1: armclang common options                                    | 42 |

| Table 3-2: armlink common options                                     | 43 |

| Table 3-3: armar common options                                       | 44 |

| Table 3-4: fromelf common options                                     | 44 |

| Table 3-5: armasm common options                                      | 45 |

| Table 3-6: Supported C and C++ source language variants               | 46 |

| Table 3-7: Exceptions to the support for the language standards       | 48 |

| Table 3-9: Example code generation with -O0                           | 54 |

| Table 3-10: Example code generation with -O1                          | 54 |

| Table 3-11: armclang linker control options                           | 58 |

| Table 3-12: Common diagnostic options                                 | 60 |

| Table 3-13: Options for floating-point selection                      | 65 |

| Table 3-14: Floating-point linkage for AArch32                        | 68 |

| Table 4-1: C code for nonvolatile and volatile buffer loops           | 72 |

| Table 4-2: Disassembly for nonvolatile and volatile buffer loop       | 72 |

| Table 4-3: Loop unrolling pragmas                                     | 73 |

| Table 4-4: Loop optimizing example                                    | 74 |

| Table 4-5: Loop examples                                              | 74 |

| Table 4-6: Example loops                                              | 75 |

| Table 4-7: Assembly code from vectorizable and non-vectorizable loops | 76 |

| Table 4-8: C code for incrementing and decrementing loops             | 77 |

| Table 4-9: C disassembly for incrementing and decrementing loops      | 78 |

| Table 4-10: Function inlining                                               | 79  |

|-----------------------------------------------------------------------------|-----|

| Table 4-11: Effect of -fno-inline-functions                                 | 81  |

| Table 4-12: Packing members in a structure or union                         | 85  |

| Table 4-13: Packing structures                                              | 87  |

| Table 4-14: Packing individual members                                      | 88  |

| Table 7-1: Element selection by predicate type svbool_t                     | 137 |

| Table 7-2: Common addressing mode disambiguators                            | 138 |

| Table 8-3: Input section properties for placement of .ANY sections          | 184 |

| Table 8-4: Input section properties for placement of sections with next_fit | 186 |

| Table 8-6: Sort order for descending_size algorithm                         | 188 |

| Table 8-7: Sort order for cmdline algorithm                                 | 189 |

| Table 9-1: Using relative offset in overlays                                | 208 |

| Table 10-4: Types of library function                                       | 237 |

| Table 11-3: PACRET-M build attributes                                       | 276 |

| Table 11-4: Build attributes and linker behavior                            | 278 |

| Table 11-5:library_security options and linker behavior                     | 278 |

| Table 11-6: Control Flow Integrity schemes supported                        | 282 |

| Table 19-1: Environment variables used by the toolchain                     | 323 |

| Table A-1: Changes between 6.20 and 6.19                                    | 333 |

| Table A-2: Changes between 6.19 and 6.18                                    | 333 |

| Table A-3: Changes between 6.18 and 6.17                                    | 334 |

| Table A-4: Changes between 6.17 and 6.16                                    | 335 |

| Table A-5: Changes between 6.16 and 6.15                                    | 336 |

| Table A-6: Changes between 6.15 and 6.14                                    | 337 |

# 1. Introduction

The Arm® Compiler for Embedded User Guide provides information for users new to Arm Compiler for Embedded 6.

### 1.1 Conventions

The following subsections describe conventions used in Arm documents.

#### Glossary

The Arm Glossary is a list of terms used in Arm documentation, together with definitions for those terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

See the Arm® Glossary for more information: developer.arm.com/glossary.

#### Typographic conventions

Arm documentation uses typographical conventions to convey specific meaning.

| Convention                 | Use                                                                                                                                                                    |  |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| italic                     | Citations.                                                                                                                                                             |  |

| bold                       | Interface elements, such as menu names.                                                                                                                                |  |

|                            | Terms in descriptive lists, where appropriate.                                                                                                                         |  |

| monospace                  | Text that you can enter at the keyboard, such as commands, file and program names, and source code.                                                                    |  |

| monospace <u>underline</u> | A permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.                                        |  |

| <and></and>                | Encloses replaceable terms for assembler syntax where they appear in code or code fragments.                                                                           |  |

|                            | For example:                                                                                                                                                           |  |

|                            | MRC p15, 0, <rd>, <crn>, <opcode_2></opcode_2></crn></rd>                                                                                                              |  |

| SMALL CAPITALS             | Terms that have specific technical meanings as defined in the Arm® Glossary. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE. |  |

| Caution                    | Recommendations. Not following these recommendations might lead to system failure or damage.                                                                           |  |

| Warning                    | Requirements for the system. Not following these requirements might result in system failure or damage.                                                                |  |

| Danger                     | Requirements for the system. Not following these requirements will result in system failure or damage.                                                                 |  |

| Convention | Use                                                                                |

|------------|------------------------------------------------------------------------------------|

| Note       | An important piece of information that needs your attention.                       |

| Tip        | A useful tip that might make it easier, better or faster to perform a task.        |

| Remember   | A reminder of something important that relates to the information you are reading. |

# 1.2 Useful resources

This document contains information that is specific to this product. See the following resources for other useful information.

Access to Arm documents depends on their confidentiality:

- Non-Confidential documents are available at developer.arm.com/documentation. Each document link in the following tables goes to the online version of the document.

- Confidential documents are available to licensees only through the product package.

| Arm product resources                                                                          | Document ID | Confidentiality  |

|------------------------------------------------------------------------------------------------|-------------|------------------|

| Arm Compiler for Embedded Reference<br>Guide                                                   | 101754      | Non-Confidential |

| Arm Compiler for Embedded Migration and Compatibility Guide                                    | 100068      | Non-Confidential |

| Arm Compiler for Embedded Arm C and C+<br>+ Libraries and Floating-Point Support User<br>Guide | 100073      | Non-Confidential |

| Arm Compiler for Embedded Errors and<br>Warnings Reference Guide                               | 100074      | Non-Confidential |

| Arm Support                                                                                    | -           | -                |

| Arm Compiler for Linux                                                                         | -           | -                |

| Arm Development Studio Getting Started<br>Guide                                                | 101469      | Non-Confidential |

| Arm Development Studio User Guide                                                              | 101470      | Non-Confidential |

| Arm Compiler for Embedded Licensing Configuration                                              | -           | -                |

| Request a license                                                                              | -           | -                |

| Manage Arm Compiler Versions                                                                   | -           | Non-Confidential |

| User-based licensing User Guide                                                                | 102516      | Non-Confidential |

| CMSIS 5                                                                                        | -           | Non-Confidential |

| Arm® architecture and specifications                                      | Document ID | Confidentiality  |

|---------------------------------------------------------------------------|-------------|------------------|

| Arm Architecture Reference Manual for A-<br>profile architecture          | DDI 0487    | Non-Confidential |

| ARM Architecture Reference Manual<br>ARMv7-A and ARMv7-R edition          | DDI 0406    | Non-Confidential |

| A-Profile Architecture                                                    | -           | Non-Confidential |

| M-Profile Architecture                                                    | -           | Non-Confidential |

| R-Profile Architecture                                                    | -           | Non-Confidential |

| ABI for the Arm Architecture                                              | -           | Non-Confidential |

| Base Platform ABI for the Arm Architecture                                | -           | Non-Confidential |

| C Library ABI for the Arm Architecture                                    | -           | Non-Confidential |

| C++ ABI for the Arm Architecture                                          | -           | Non-Confidential |

| C++ Application Binary Interface Standard for the Arm 64-bit Architecture | -           | Non-Confidential |

| DWARF for the Arm Architecture                                            | -           | Non-Confidential |

| ELF for the Arm Architecture                                              | -           | Non-Confidential |

| Exception Handling ABI for the Arm<br>Architecture                        | -           | Non-Confidential |

| Procedure Call Standard for the Arm<br>Architecture                       | -           | Non-Confidential |

| Run-time ABI for the Arm Architecture                                     | -           | Non-Confidential |

| Support for Debugging Overlaid Programs                                   | -           | Non-Confidential |

| Addenda to, and Errata in, the ABI for the Arm Architecture               | -           | Non-Confidential |

| Whitepaper - Armv8-M Architecture<br>Technical Overview                   | -           | Non-Confidential |

| Armv8-M Stack Sealing vulnerability                                       | -           | Non-Confidential |

| Non-Arm resources                                                                 | Document ID | Organization                              |

|-----------------------------------------------------------------------------------|-------------|-------------------------------------------|

| GCC                                                                               | -           | https://gcc.gnu.org/onlinedocs/gcc        |

| GNU Binutils                                                                      | -           | https://sourceware.org/binutils           |

| Itanium C++ ABI                                                                   | -           | https://itanium-cxx-abi.github.io/cxx-abi |

| The Security Implications Of Compiler<br>Optimizations On Cryptography - A Review | -           | https://arxiv.org                         |

| Using Clang as a Compiler                                                         | -           | https://clang.llvm.org/docs               |

| Automatic variable initialization                                                 | -           | https://reviews.llvm.org                  |

| C++ implementation status in LLVM Clang                                           | -           | https://clang.llvm.org/docs               |

| Undefined Behavior Sanitizer                                                      | -           | https://clang.llvm.org/docs               |

| Update for Universal C Runtime in Windows                                         | -           | https://support.microsoft.com             |

# 1.3 Other information

See the Arm website for other relevant information.

- Arm® Developer.

- Arm® Documentation.

- Technical Support.

- Arm® Glossary.

# 2. Getting Started

This chapter introduces Arm® Compiler for Embedded 6 and helps you to start working with Arm Compiler for Embedded 6 quickly. You can use Arm Compiler for Embedded 6 from Arm Development Studio, Arm Keil MDK, or as a standalone product.

# 2.1 Introduction to Arm Compiler for Embedded 6

Arm® Compiler for Embedded 6 is the most advanced C and C++ compilation toolchain from Arm for Arm® Cortex® and Arm® Neoverse® processors. Arm Compiler for Embedded 6 is developed alongside the Arm architecture. Therefore, Arm Compiler for Embedded 6 is tuned to generate highly efficient code for embedded bare-metal applications ranging from small sensors to 64-bit devices.

Arm Compiler for Embedded 6 is a component of Arm Development Studio and Arm Keil MDK. Alternatively, you can use Arm Compiler for Embedded 6 as a standalone product. The features and processors that Arm Compiler for Embedded 6 supports depend on the product edition. See Compare Editions for Arm Development Studio.

#### Tools and libraries provided with Arm Compiler for Embedded 6

Arm Compiler for Embedded 6 combines the optimized tools and libraries from Arm with a modern LLVM-based compiler framework. The components in Arm Compiler for Embedded 6 are:

#### armclang

The compiler and integrated assembler that compiles C, C++, and GNU assembly language sources.

Arm Compiler for Embedded supports Standard and GNU variants of C and C++ as shown in the following table:

Table 2-1: Supported C and C++ source language variants

| Standard C      | GNU C             | Standard C++ | GNU C++ |

|-----------------|-------------------|--------------|---------|

| c90             | gnu90             | c++98        | gnu++98 |

| c99             | gnu99             | c++03        | gnu++03 |

| c11 [COMMUNITY] | gnu11 [COMMUNITY] | c++11        | gnu++11 |

| -               | -                 | c++14        | gnu++14 |

| -               | -                 | c++17        | gnu++17 |

Some C and C++ language standards are supported as [COMMUNITY] features. See Support level definitions.

The compiler is based on LLVM and Clang technology (Clang is a compiler front end for LLVM that supports the C and C++ programming languages).

#### armasm

The legacy assembler. Only use armasm for legacy Arm-syntax assembly code. Use the armclang integrated assembler and GNU syntax for all new assembly files.

The armasm legacy assembler is deprecated, and it has not been updated since Arm Compiler 6.10. Also, armasm does not support:

- Armv8.4-A or later architectures.

- Certain backported options in Armv8.2-A and Armv8.3-A.

- Assembling sve instructions.

- Armv8.1-M or later architectures, including MVE.

- All versions of the Armv8-R architecture.

As a reminder, armasm always reports the deprecation warning A1950w. To suppress this message, specify the --diag suppress=1950 option.

#### armlink

The linker combines the contents of one or more object files with selected parts of one or more object libraries to produce an executable program.

#### armar

The archiver enables sets of ELF object files to be collected together and maintained in archives or libraries. If you do not change the files often, these collections reduce compilation time as you do not have to recompile from source every time you use them. You can pass such a library or archive to the linker in place of several ELF files. You can also use the archive for distribution to a third-party application developer as you can share the archive without giving away the source code.

#### fromelf

The image conversion utility can convert Arm ELF images to binary formats. It can also generate textual information about the input image, such as its disassembly, code size, and data size.

#### Arm C++ libraries

The Arm C++ libraries are based on the LLVM libc++ project:

- The libc++abi library is a runtime library providing implementations of low-level language features.

- The libc++ library provides an implementation of the ISO C++ library standard. It depends on the functions that are provided by libc++abi.

Arm does not guarantee the compatibility of C++ compilation units compiled with different major or minor versions of Arm Compiler for Embedded and linked into a single image. Therefore, Arm recommends that you always build your C++ code from source with a single version of the toolchain.

You can mix C++ with C code or C libraries.

#### **Arm C libraries**

The Arm C libraries provide:

- An implementation of the library features as defined in the C standards.

- Nonstandard extensions common to many C libraries.

- POSIX extended functionality.

- Functions standardized by POSIX.

Comments inside source files and header files that are provided by Arm might not be accurate and must not be treated as documentation about the product.

#### Application development

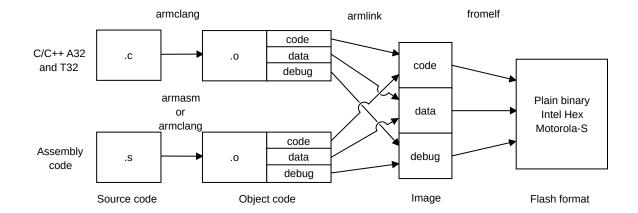

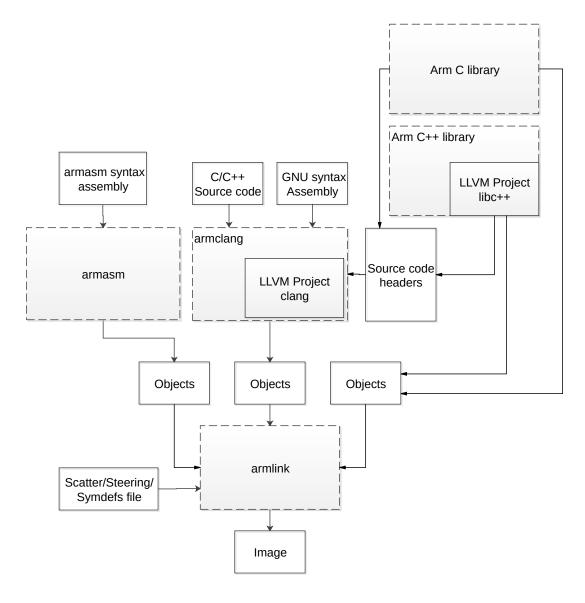

A typical application development flow might involve the following:

- Developing C/C++ source code for the main application (armclang).

- Developing assembly source code for near-hardware components, such as interrupt service routines (armclang, or armasm for legacy assembly code).

- Linking all objects together to generate an image (armlink).

- Converting an image to flash format in plain binary, Intel Hex, and Motorola-S formats (fromelf).

The following figure shows how the compilation tools are used for the development of a typical application.

Figure 2-1: A typical tool usage flow diagram

Arm Compiler for Embedded 6 has more functionality than the set of product features that is described in the documentation. The various features in Arm Compiler for Embedded 6 can have different levels of support and guarantees. For more information, see Support level definitions.

- If you are migrating your toolchain from Arm Compiler 5 to Arm Compiler for Embedded 6, see the Migration and Compatibility Guide. It contains information on how to migrate your source code and toolchain build options.

- For a list of Arm Compiler for Embedded 6 documents, see the documentation on Arm Developer.

Be aware of the following:

- Generated code might be different between two Arm Compiler for Embedded releases.

- For a feature release, there might be significant code generation differences.

#### Related information

Compiling a Hello World example on page 28 Common Arm Compiler for Embedded toolchain options on page 42 -S (armclang)

# 2.2 About the Arm Compiler for Embedded toolchain assemblers

The Arm® Compiler for Embedded toolchain provides different assemblers.

They are:

- The armclang integrated assembler. Use this to assemble assembly language code written in GNU syntax.

- An optimizing inline assembler built into armclang. Use this to assemble assembly language code written in GNU syntax that is used inline in C or C++ source code.

- The freestanding legacy assembler, armasm. Use armasm to assemble existing A64, A32, and T32 assembly language code written in armasm syntax.

The armasm legacy assembler is deprecated, and it has not been updated since Arm Compiler 6.10. Also, armasm does not support:

- Armv8.4-A or later architectures.

- Certain backported options in Armv8.2-A and Armv8.3-A.

- Armv8.1-M or later architectures, including MVE.

- All versions of the Army8-R architecture.

As a reminder, armasm always reports the deprecation warning A1950w. To suppress this message, specify the --diag suppress=1950 option.

The command-line option descriptions and related information in the Arm Compiler for Embedded Reference Guide describe all the features that Arm Compiler for Embedded supports. Any features not documented are not supported and are used at your own risk. You are responsible for making sure that any generated code using community features is operating correctly. See Support level definitions.

#### Related information

Using Assembly and Intrinsics in C or C++ Code on page 112

Assembling GNU syntax and armasm assembly code on page 107

Arm Compiler for Embedded Reference Guide

## 2.3 System requirements and installation

The system requirements for running Arm® Compiler for Embedded and instructions to guide you through the installation process.

#### **System Requirements**

Arm Compiler for Embedded 6 is available for the following:

- x86 64 Windows

- x86 64 Windows for Arm<sup>®</sup> Keil<sup>®</sup> MDK

- x86\_64 Linux

- AArch64 Linux

For more information on system requirements see the Release Note on the Arm Compiler for Embedded downloads page.

#### Installing Arm Compiler for Embedded

You can install Arm Compiler for Embedded as a standalone product on supported Windows and Linux platforms. If you use Arm Compiler for Embedded as part of a development suite such as Arm Development Studio or Arm Keil MDK, installing the development suite also installs Arm Compiler for Embedded. The following instructions are for installing Arm Compiler for Embedded as a standalone product.

#### Prerequisites:

- 1. Download Arm Compiler for Embedded 6. The download pack provided for use with Keil MDK is not suitable for standalone use.

- 2. Obtain a license. Contact your Arm sales representative or Request a license.

If you are using a user-based license, see the User-based licensing User Guide.

#### Installing a standalone Arm Compiler for Embedded on x86\_64 Windows platforms

To install Arm Compiler for Embedded as a standalone product on Windows for x86\_64, you need the Arm Compiler for Embedded <N>.<nn>.msi installer on your machine. <N>.<nn> is the product version number. This file is in the Arm Compiler for Embedded 6 downloads package.

#### To install:

- 1. Run win-x86 64\Arm Compiler for Embedded <N>.<nn>.msi.

- 2. Follow the on-screen installation instructions.

- 3. Some license types require you to complete further configuration steps. To check if your license requires further configuration, and to learn how to configure that license, see Arm Compiler for Embedded Licensing Configuration.

If you have an older version of Arm Compiler for Embedded 6 and you want to upgrade, Arm recommends that you uninstall the older version of Arm Compiler for Embedded 6 before installing the new version of Arm Compiler for Embedded 6.

Arm Compiler for Embedded requires the Universal C Runtime in Windows to be installed. For more information, see Update for Universal C Runtime in Windows.

To update the compiler toolchain in an existing Keil MDK installation, download the Arm Compiler for Embedded 6.20 (for Keil MDK) package and run win-x86\_32\<file>.msi. Follow the on-screen instructions and ensure the new compiler toolchain is installed in the correct location. This variant of the compiler toolchain is provided for use with Keil MDK only and is only supported on 64-bit Windows.

#### Installing a standalone Arm Compiler for Embedded on x86\_64 Linux platforms

To install Arm Compiler for Embedded as a standalone product on x86\_64 Linux platforms, you need the <code>install\_x86\_64.sh</code> installer on your machine. This file is in the Arm Compiler for Embedded 6 download package.

#### To install:

- 1. Run install x86 64.sh normally, without using the source Linux command.

- 2. Follow the on-screen installation instructions.

- 3. Some license types require you to complete further configuration steps. To check if your license requires further configuration, and to learn how to configure that license, see Arm Compiler for Embedded Licensing Configuration.

The armclang binary is dynamically linked to a copy of libstdc++ that is installed under your chosen directory as part of Arm Compiler for Embedded.

#### Installing a standalone Arm Compiler for Embedded on AArch64 Linux platforms

To install Arm Compiler for Embedded as a standalone product on AArch64 Linux platforms, you need the <code>install\_aarch64.sh</code> installer on your machine. This file is in the Arm Compiler for Embedded 6 downloads package.

#### To install:

- 1. Run install aarch64.sh normally, without using the source Linux command.

- 2. Follow the on-screen installation instructions.

- 3. Some license types require you to complete additional configuration steps. To check if your license requires additional configuration, and to learn how to configure that license, see Arm Compiler for Embedded Licensing Configuration.

The armclang binary is dynamically linked to a copy of libstdc++ that is installed under your chosen directory as part of Arm Compiler for Embedded.

#### Uninstalling a standalone Arm Compiler for Embedded

To uninstall Arm Compiler for Embedded on Windows, use the Control Panel:

- Select Control Panel > Programs > Programs and Features > Uninstall a program.

- 2. Select the version that you want to uninstall, for example **Arm Compiler for Embedded 6.20**.

- 3 Click Uninstall.

To uninstall Arm Compiler for Embedded on Linux, delete the Arm Compiler for Embedded installation directory for the compiler version you want to delete.

For more information on installation, see the Release Note on the Arm Compiler for Embedded 6 downloads page.

#### Related information

Accessing Arm Compiler for Embedded from Arm Development Studio on page 28

Accessing Arm Compiler for Embedded from the Arm Keil µVision IDE on page 28

# 2.4 Accessing Arm Compiler for Embedded from Arm Development Studio

Arm® Development Studio is a development suite that provides Arm Compiler for Embedded as a built-in toolchain.

For more information, see Create a new C or C++ project in the Arm Development Studio Getting Started Guide.

#### Related information

System requirements and installation on page 25

# 2.5 Accessing Arm Compiler for Embedded from the Arm Keil µVision IDE

MDK is a microprocessor development suite that provides the  $\mu$ Vision® IDE, and Arm® Compiler for Embedded as a built-in toolchain.

For more information, see Manage Arm Compiler Versions in the μVision User's Guide.

#### Related information

System requirements and installation on page 25

## 2.6 Compiling a Hello World example

These examples show how to use the Arm $^{\$}$  Compiler for Embedded toolchain to build and inspect an executable image from C/C++ source files.

#### A simple example

The source code that is used in the examples is a single C source file, hello.c, to display a greeting message:

```

#include <stdio.h>

int main() {

printf("Hello World\n");

return 0;

}

```

#### Building an executable in a single step

For simple programs, you can use a single command to compile the source code file to an executable image.

You must first decide which target the executable is to run on. An Armv8-A target can run in different states:

- AArch64 state targets execute A64 instructions using 64-bit and 32-bit general-purpose registers.

- AArch32 state targets execute A32 or T32 instructions using 32-bit general-purpose registers.

The --target option determines which target state to compile for. This option is a mandatory option.

#### Compiling for an AArch64 target

To create an executable for an AArch64 target in a single step:

```

armclang --target=aarch64-arm-none-eabi hello.c

```

This command creates an executable file with the default name a.out. You can use the -o option to specify a different name for the executable file.

This example compiles for an AArch64 state target. Because only --target is specified, the compiler defaults to generating code that runs on any Armv8-A target. You can also use - mcpu to target a specific processor.

#### Compiling for an AArch32 target

To create an executable for an AArch32 target in a single step:

```

armclang --target=arm-arm-none-eabi -mcpu=cortex-a53 hello.c

```

There is no default target for AArch32 state. You must specify either <code>-march</code> to target an architecture or <code>-mcpu</code> to target a processor. This example uses <code>-mcpu</code> to target the Cortex<sup>®</sup>-A53 processor. The compiler generates code that is optimized specifically for the Cortex-A53, but might not run on other processors.

Use -mcpu=list or -march=list to see all available processor or architecture options.

#### Beyond the defaults

Compiler options let you specify precisely how the compiler behaves when generating code.

The Arm Compiler for Embedded Reference Guide describes all the supported options. Some of the most common options are listed in Common Arm Compiler for Embedded toolchain options.

#### Examining the executable

The frome1f tool lets you examine a compiled binary, extract information about it, or convert it.

For example, you can:

• Disassemble the code that is contained in the executable:

```

fromelf --text -c a.out

main

.H-.

0x000081a0: e92d4800

PUSH

MOV

SUB

{r11,lr}

0x000081a4: e1a0b00d

0x000081a8: e24dd010

r11,sp

sp, sp, #0x10

..M.

0x000081ac: e3a00000

. . . .

MOV

r0,#0

0x000081b0: e50b0004

0x000081b4: e30a19cc

r0,[r11,#-4]

STR

MOV

. . . .

r1, #0xa9cc

. . . .

```

Examine the size of code and data in the executable:

```

fromelf --text -z a.out

Code (inc. data) RO Data RW Data ZI Data Debug Object Name

10436 492 596 16 348 3468 a.out

10436 492 596 16 0 0 ROM Totals for

a.out

```

Convert the ELF executable image to another format, for example a plain binary file:

```

fromelf --bin --output=outfile.bin a.out

```

See fromelf Command-line Options for the options from the fromelf tool.

#### Compiling and linking as separate steps

For simple projects with small numbers of source files, compiling to an executable image in a single step might be the simplest option. You can compile multiple source files into an executable with a command such as the following:

```

armclang --target=aarch64-arm-none-eabi file1.c file2.c -o image.axf

```

This command compiles the two source files file1.c and file2.c into an executable file for an AArch64 state target. The -o option specifies that the filename of the generated executable file is image.axf.

However, more complex projects might have a large number of source files. It is not efficient to compile every source file at every compilation, because many of the source files are unlikely to change. To avoid compiling unchanged source files, you can compile and link as separate steps. In this way, you can then use a build system (such as make) to compile only those source files that have changed, then link the object code together. The armclang -c option tells the compiler to compile to object code and stop before calling the linker:

```

armclang -c --target=aarch64-arm-none-eabi file1.c armclang -c --target=aarch64-arm-none-eabi file2.c armlink file1.o file2.o -o image.axf

```

These commands do the following:

- Compile file1.c to object code, and save using the default name file1.o.

- Compile file2.c to object code, and save using the default name file2.o.

- Link the object files file1.0 and file2.0 to produce an executable that is called image.axf.

In future, if you modify file2.c, you can rebuild the executable by recompiling only file2.c then linking the new file2.o with the existing file1.o to produce a new executable:

```

armclang -c --target=aarch64-arm-none-eabi file2.c armlink file1.o file2.o -o image.axf

```

#### Related information

- --target (armclang)

- -march (armclang)

- -mcpu (armclang)

Summary of armclang command-line options

# 2.7 Using the integrated assembler

These examples show how to use the armclang integrated assembler to build an object from assembly source files, and how to call functions in this object from C/C++ source files.

The integrated assembler sets a minimum alignment of 4 bytes for a .text section. However, if you define your own sections with the integrated assembler, then you must include the .balign directive to set the correct alignment. For a section containing T32 instructions, set the alignment to 2 bytes. For a section containing A32 instructions, set the alignment to 4 bytes.

#### The assembly source code

The assembly example is a single assembly source file, mystrcopy.s, containing a function to perform a simple string copy operation:

The .section directive creates a new section in the object file named stringcopy. The characters in the string following the section name are the flags for this section. The  $\alpha$  flag marks this section as allocatable. The  $\alpha$  flag marks this section as executable.

The .balign directive aligns the subsequent code to a 4-byte boundary. The alignment is required for compliance with the *Procedure Call Standard for the Arm Architecture* (AAPCS).

The .global directive marks the symbol mystrcopy as a global symbol. This enables the symbol to be referenced by external files.

The .type directive sets the type of the symbol mystrcopy to function. This helps the linker use the proper linkage when the symbol is branched to from A32 or T32 code.

#### Assembling a source file

When assembling code, you must first decide which target the executable is to run on. The -- target option determines which target state to compile for. This option is a mandatory option.

To assemble the above source file for an Arm®v8-M Mainline target:

```

armclang --target=arm-arm-none-eabi -c -march=armv8-m.main mystrcopy.s

```

This command creates an object file, mystrcopy.o.

The --target option selects the target that you want to assemble for. In this example, there is no default target for A32 state, so you must specify either -march to target an architecture or -mcpu to target a processor. This example uses -march to target the Armv8-M Mainline architecture. The integrated assembler accepts the same options for --target, -march, -mcpu, and -mfpu as the compiler.

Use -mcpu=list or -march=list to see all available options.

#### Examining the executable

You can use the fromelf tool to:

- examine an assembled binary.

- extract information about an assembled binary.

- convert an assembled binary to another format.

For example, you can disassemble the code that is contained in the object file:

```

fromelf --text -c mystrcopy.o

** Section #3 'StringCopy' (SHT PROGBITS) [SHF ALLOC + SHF EXECINSTR]

Size : 14 bytes (alignment 4)

Address: 0x00000000

$t.0

mystrcopy

0x00000000:

f8112b01

r2, [r1], #1

0x00000004:

f8002b01

STRB

r2,[r0],#1

2a00

0x00000008:

CMP

r2,#0

0x0000000a:

d1f9

BNE

mystrcopy; 0x0

0x000000c:

4770

```

The example shows the disassembly for the section stringcopy as created in the source file.

The code is marked as T32 by default because Armv8-M Mainline does not support A32 code. For processors that support A32 and T32 code, you can explicitly mark the code as A32 or T32 by adding the GNU assembly .arm or .thumb directive, respectively, at the start of the source file.

#### Calling an assembly function from C/C++ code

It can be useful to write optimized functions in an assembly file and call them from C/C++ code. When doing so, ensure that the assembly function uses registers in compliance with the AAPCS.

The C example is a single C source file main.c, containing a call to the mystrcopy function to copy a string from one location to another:

```

const char *source = "String to copy.";

char *dest;

extern void mystrcopy(char *dest, const char *source);

int main(void) {

mystrcopy(dest, source);

return 0;

}

```

An extern function declaration has been added for the mystrcopy function. The return type and function parameters must be checked manually.

If you want to call the assembly function from a C++ source file, you must disable C++ name mangling by using extern "c" instead of extern. For the above example, use:

```

extern "C" void mystrcopy(char *dest, const char *source);

```

#### Compiling and linking the C source file

To compile the above source file for an Armv8-M Mainline target:

```

armclang --target=arm-arm-none-eabi -c -march=armv8-m.main main.c

```

This command creates an object file, main.o.

To link the two object files main.o and mystrcopy.o and generate an executable image:

```

armlink main.o mystrcopy.o -o image.axf

```

This command creates an executable image file image.axf.

#### Related information

Mandatory armclang options on page 40 Summary of armclang command-line options

Sections

## 2.8 Running bare-metal images

By default, Arm® Compiler for Embedded produces bare-metal images. Bare-metal images can run without an operating system. The images can run on a hardware target or on a software application that simulates the target, such as Fast Models or Fixed Virtual Platforms.

The linker creates information to initialize global and static objects (data) and uninitialized global and static objects (.bss). Bare-metal images initialize the data by copying and decompressing initialized data and set the .bss to zero.

See your Arm *Integrated Development Environment* (IDE) documentation for more information on configuring and running images. For Arm Development Studio, see the Arm Development Studio Getting Started Guide and Arm Development Studio User Guide.

By default, the C library in Arm Compiler for Embedded uses special functions to access the input and output interfaces on the host computer. These functions implement a feature called semihosting. Semihosting is useful when the input and output on the hardware is not available during the early stages of application development.

When you want your application to use the input and output interfaces on the hardware, you must retarget the required semihosting functions in the C library.

See your Arm IDE documentation for more information on configuring debugger settings. For Arm Debugger settings, see Configuring a connection to a bare-metal hardware target in the Arm Development Studio Getting Started Guide.

#### Outputting debug messages from your application

The semihosting feature enables your bare-metal application, running on an Arm processor, to use the input and output interface on a host computer. This feature requires the use of a debugger that supports semihosting, for example Arm Debugger, on the host computer.

A bare-metal application that uses semihosting does not use the input and output interface of the development platform. When the input and output interfaces on the development platform are available, you must reimplement the necessary semihosting functions to use them.

For more information, see how to use the libraries in semihosting and nonsemihosting environments.

#### Related information

Arm Development Studio Getting Started Guide Arm Development Studio User Guide Semihosting for AArch32 and AArch64

# 2.9 Architectures supported by Arm Compiler for Embedded 6

Arm® Compiler for Embedded supports a number of different architecture profiles.

Some update releases and architecture extensions might not be fully supported in this release. Where these are described, the level of support is indicated. See Support level definitions.

Arm Compiler for Embedded supports the following architectures:

- Armv9-A.

- Armv8-A and all update releases, for bare-metal targets.

- Armv8-R.

- Armv8-M.

- Armv7-A for bare-metal targets.

- Armv7-R.

- Armv7-M.

- Armv6-M.

When compiling code, the compiler needs to know which architecture to target in order to take advantage of features specific to that architecture.

To specify a target, you must supply the target execution state (AArch32 or AArch64), together with either a target architecture (for example Armv8-A) or a target processor (for example, the Cortex®-A53 processor).

To specify a target execution state (AArch64 or AArch32) with armclang, use the mandatory -- target command-line option:

--target=<arch>-<vendor>-<os>-<abi>

Supported targets include:

#### aarch64-arm-none-eabi

Generates A64 instructions for AArch64 state. Implies -march=armv8-a unless -march or -mcpu is specified.

#### arm-arm-none-eabi

Generates A32 and T32 instructions for AArch32 state. Must be used in conjunction with – march (to target an architecture) or –mcpu (to target a processor).

To generate generic code that runs on any processor with a particular architecture, use the -march option. Use the -march=list option to see all supported architectures.

To optimize your code for a particular processor, use the -mcpu option. Use the -mcpu=list option to see all supported processors.

The --target, -march, and -mcpu options are armclang options. For all of the other tools, such as armlink, use the --cpu option to specify target processors and architectures.

#### Related information

- --target (armclang)

- -march (armclang)

- -mcpu (armclang)

- --cpu (armlink)

**Arm Glossary**

# 2.10 Using Arm Compiler for Embedded securely in a shared environment

Arm® Compiler for Embedded provides features and language support in common with other toolchains. Misuse of these common features and language support can provide access to arbitrary files, execute system commands, and reveal the contents of environment variables.

If deploying Arm Compiler for Embedded into environments where security is a concern, then Arm strongly recommends that you do all the following:

- Sandbox the tools to limit their access to only necessary files.

- Remove all non-essential environment variables.

- Prevent execution of other binaries.

- Segregate different users from each other.

- Limit execution time.

# 2.11 Providing source code to Arm support

When you encounter a problem that requires you to provide source code to Arm support, then you might want to create a minimal example that demonstrates the problem.

Preprocessing your source files with the armclang option -E might be useful when creating the minimal example as part of a support case. To help the investigation, try to send only the single image, object, source file, or function that is causing the issue, together with the command-line options used.

If your source code contains preprocessor macros, it might be necessary to use the compiler to preprocess the source before sharing it. That is, to take account of files added with #include, pass the file through the preprocessor as follows:

armclang <options> -E sourcefile.c > PPsourcefile.c

Where <options> are your normal compile switches, such as -o2, -g, -I, -D, but without -c.

#### Related information

Common Arm Compiler for Embedded toolchain options on page 42 -E (armclang)

# 2.12 Build attributes

armclang or a standalone assembler annotate ELF object files with build attributes. armlink uses this data to determine the compatibility of the files that it links.

Arm® Compiler for Embedded supports build attributes only for AArch32.

Build attributes primarily model two kinds of compatibility:

- The compatibility of binary code with target hardware conforming to a revision of the Arm architecture.

- The procedure-call compatibility between functions conforming to variants of the ABI for the Arm Architecture.

Build attributes approximate your intentions for the compatibility of the relocatable file produced by the tool when compiling or assembling code. You express the intentions to the tool as configuration options such as <code>-mcpu</code> or <code>-mno-unaligned-access</code>.

When compiling C and C++ code, armclang is in control of code generation and can guarantee that the object file generated conforms to the intention. When using the assembler, you are in control of code generation. In some cases the assembler can check that the source code conforms to the intentions given on the command-line. For example, if the specified processor does not support a particular instruction, the assembler can give an error message that the instruction is not supported. However, some intentions cannot be easily checked by the assembler.

You can use the armclang integrated assembler with options that permit using unaligned data accesses or options that affect the passing of arguments. When using such options, you must ensure that the object file generated conforms to the intentions and purpose of the options:

• Compatibility can be given a mathematically precise definition using sets of demands placed on an execution environment.

For example, a program is compatible with a processor if, and only if, the set of instructions the program might try to execute is a subset of the instructions implemented by that processor.

• Target-related attributes describe the hardware-related demands a relocatable file places on an execution environment through being included in an executable file for that environment.

For example, target-related attributes record whether use of the Arm® Thumb® *Instruction Set Architecture* (ISA) is permitted, and at what architectural revision use is permitted. A pair of values for these attributes describes the set of Thumb instructions that code is permitted to execute and that the target processor must implement.

- Procedure call-related attributes describe features of the ABI contract that the ABI allows to vary. Features such as:

- Whether floating-point parameters are passed in floating-point registers.

- The size of wchar t.

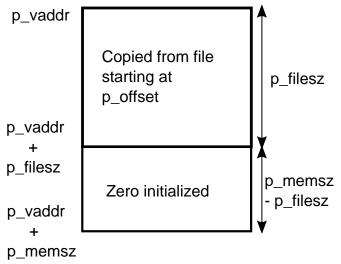

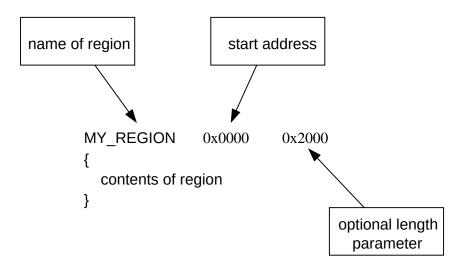

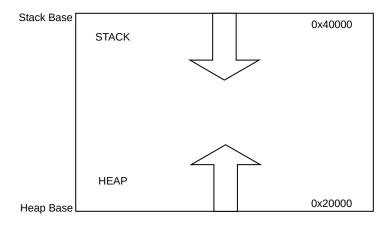

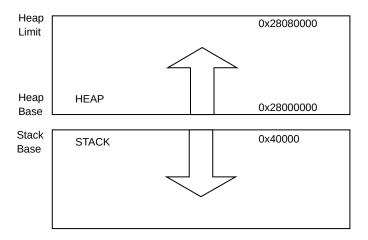

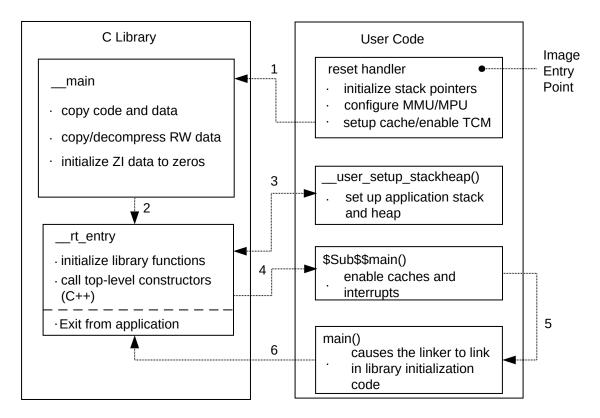

- Whether enumerated values are containerized according to their size.