## ARM® Design Simulation Model

for SystemC

**User Guide**

### ARM Design Simulation Model User Guide

Copyright © 2016 ARM. All rights reserved.

#### **Release Information**

The following changes have been made to this book.

#### Change history

| Date           | Issue | Confidentiality  | Change                     |

|----------------|-------|------------------|----------------------------|

| September 2016 | A     | Non-Confidential | First release for SystemC. |

#### **Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of ARM. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, ARM makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to ARM's customers is not intended to create or refer to any partnership relationship with any other company. ARM may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any signed written agreement covering this document with ARM, then the signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

Words and logos marked with ® or ™ are registered trademarks or trademarks of ARM Limited or its affiliates in the EU and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow ARM's trademark usage guidelines at http://www.arm.com/about/trademark-usage-guidelines.php

Copyright © 2016 ARM. All rights reserved. ARM Limited or its affiliates.

ARM Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

### **Product Status**

The information in this document is final, that is for a developed product.

### Web Address

http://www.arm.com

ίV

### Contents

### **ARM Design Simulation Model User Guide**

|           | Pref   | face                                    |     |

|-----------|--------|-----------------------------------------|-----|

|           |        | About this book                         | vii |

|           |        | Intended audience                       | vii |

|           |        | Using this book                         | vii |

|           |        | Glossary                                |     |

|           |        | Conventions                             | vii |

|           |        | Additional reading                      | i   |

|           |        | Feedback                                |     |

|           |        | Feedback on this product                |     |

|           |        | Feedback on content                     | >   |

| Chapter 1 | Intro  | oduction                                |     |

|           | 1.1    | About Design Simulation Models          | 1-2 |

|           |        | 1.1.1 Features of ARM DSMs              |     |

|           | 1.2    | DSM package contents                    |     |

|           | 1.3    | Simulation with DSMs                    |     |

| Chapter 2 | Initia | al DSM Configuration                    |     |

|           | 2.1    | Prerequisites                           | 2-2 |

|           | 2.2    | Extracting and Installing the DSM       |     |

|           |        | 2.2.1 Installing Using the Command Line |     |

|           | 2.3    | How to test the DSM                     |     |

|           | 2.4    | Integrating with Simulators             |     |

|           |        | 2.4.1 VCS                               |     |

|           |        | 2.4.2 Cadence Incisive                  |     |

|           |        | 2.4.3 Mentor QuestaSim (ModelSim)       |     |

|           | 2.5    | TARMAC Trace                            |     |

|           | 3      | 2.5.1 Enabling TARMAC Trace             |     |

|           |        | 2.5.2 Disabling TARMAC Trace            |     |

|           |        |                                         |     |

| Chapter 3  | Model Limitations |       |                                  |     |

|------------|-------------------|-------|----------------------------------|-----|

|            | 3.1               |       | tions of useSupported simulators |     |

|            |                   | 3.1.2 | Unsupported simulator functions  | 3-2 |

|            |                   |       | Internal scan chain modeling     |     |

|            |                   | 3.1.4 | Caches and registers             | 3-2 |

|            |                   | 3.1.5 | Waveform dumping                 | 3-2 |

| Appendix A | Revi              | sions |                                  |     |

### **Preface**

This preface introduces the ARM® Design Simulation Model (DSM) User Guide. It contains the following sections:

- About this book on page viii.

- Feedback on page x.

### About this book

This book is for the ARM Design Simulation Model (DSM) for SystemC.

### Intended audience

This book is written for experienced hardware engineers, software engineers and System-on-Chip (SoC) designers who might have experience of ARM products. You are expected to have experience of SystemC.

### Using this book

This book is organized into the following chapters:

### Chapter 1 Introduction

Read this for a high-level description of DSMs and how they are used in simulations. This chapter describes the contents of the package and potential simulation inaccuracies when using DSMs.

### Chapter 2 Initial DSM Configuration

Read this for a description of how to install, set up, and test a DSM.

### **Chapter 3 Model Limitations**

This chapter describes some of the limitations of DSMs.

### Appendix A Revisions

Read this for a description of the technical changes between released issues of this book

### Glossary

The ARM® Glossary is a list of terms used in ARM documentation, together with definitions for those terms. The ARM® Glossary does not contain terms that are industry standard unless the ARM meaning differs from the generally accepted meaning.

The *ARM*® *Glossary* is available on the ARM Infocenter at http://infocenter.arm.com/help/topic/com.arm.doc.aeg0014-/index.html.

### Conventions

Conventions that this book can use are described in:

• Typographical conventions.

### Typographical conventions

The following table describes the typographical conventions:

| Style     | Purpose                                                                                                                               |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------|

| italic    | Introduces special terminology, denotes cross-references, and citations.                                                              |

| bold      | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate. |

| monospace | Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.                           |

### (continued)

| Style             | Purpose                                                                                                                                                                                      |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>mono</u> space | Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.                                                      |

| monospace italic  | Denotes arguments to monospace text where the argument is to be replaced by a specific value.                                                                                                |

| monospace bold    | Denotes language keywords when used outside example code.                                                                                                                                    |

| <and></and>       | Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example: MRC p15, 0 <rd>, <crn>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></crn></rd> |

| SMALL CAPITALS    | Used in body text for a few terms that have specific technical meanings, that are defined in the <i>ARM® glossary</i> . For example, IMPLEMENTATION DEFINED, UNKNOWN, and UNPREDICTABLE.     |

### Additional reading

This section lists publications by ARM and by third parties.

See Infocenter http://infocenter.arm.com for access to ARM documentation.

### **Feedback**

ARM welcomes feedback on this product and its documentation.

### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

### Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

ARM also welcomes general suggestions for additions and improvements.

- The title.

- The number, ARM DUI 1031A.

- The page numbers to which your comments apply.

- A concise explanation of your comments.

## Chapter 1 **Introduction**

This chapter introduces the ARM Design Simulation Model (DSM) for SystemC. It contains the following sections:

- About Design Simulation Models on page 1-2.

- DSM package contents on page 1-3.

- Simulation with DSMs on page 1-4.

### 1.1 About Design Simulation Models

DSMs are cycle accurate, simulation models that you can include in a range of target HDL simulators. Each DSM is specific to a host platform. The DSM fully matches the architecture and functionality of the RTL model.

The DSMs are derived directly from the RTL model. DSMs can function with a wide range of industry-standard Verilog simulators. Performance depends on:

- The simulator interface efficiency.

- The complexity of the design in which it is instantiated.

- The complexity of the original design.

The DSM consists of:

- A functional core block.

- A SystemC wrapper.

The wrapper uses the foreign language interface of the host simulator to instantiate the functional model. The DSM is generally derived from the RTL source of the ARM design using the *ARM Cycle Model* compiler. For some ARM products, this might be augmented with extra functionality, such as TARMAC trace, added by ARM.

The DSM interfaces to the wrapper using technology developed by ARM to enable a single compiled model to function with a variety of logic simulators. For some products, the DSMs might include behavioral debug facilities, such as TARMAC trace. When you use compiled models, it enables distribution of models without compromising the intellectual property that they embody.

| Note                                                                                     |                     |

|------------------------------------------------------------------------------------------|---------------------|

| The DSM is intended for functional simulation and verification only, not design signoff. | for timing or final |

### 1.1.1 Features of ARM DSMs

Table 1-1 shows the main features of ARM DSMs.

Table 1-1 ARM DSM features

| Feature                             | Description                                                                                                                                                                                                  |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Full device functionality           | Unless otherwise noted, the DSM fully matches the architecture and functionality of the RTL model.                                                                                                           |

| Phase accuracy                      | You can expect the DSM to exhibit the same intra-cycle timing as the RTL model.                                                                                                                              |

| Register visibility                 | For register visibility, use the TARMAC trace or see the included README for a list of registers that support visibility. Refer to the <i>ARM TARMAC Specification</i> available with your DSM installation. |

| Cache and memory size configuration | You can configure the size of the cache, or TCM, for each particular DSM instance, where applicable.                                                                                                         |

|                                     | Note                                                                                                                                                                                                         |

|                                     | This feature does not apply if your ARM product has no such configuration, or where your DSM generation flow does not support multiple configurations.                                                       |

| Disassembler                        | To view disassembled code, use the TARMAC trace.                                                                                                                                                             |

### 1.2 DSM package contents

Each DSM contains the following components:

- DSM SystemC wrapper.

- DSM library, including a dynamic .so file, static .a file, and header files.

- One or more implementation libraries as .so files.

- A testbench file to check the DSM setup.

- Documentation, including the ARM TARMAC Specification, this document, and a README.

### 1.3 Simulation with DSMs

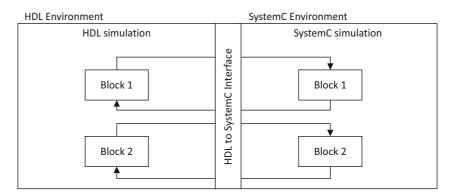

Figure 1-1 shows the integration of DSMs (Block 1 and Block 2) into an HDL simulation. During simulation, the DSM interfaces to the simulator through the HDL to the SystemC Interface, which synchronizes between the two environments.

Figure 1-1 DSM integration

| ——— Note ————                                                                             |

|-------------------------------------------------------------------------------------------|

| For synthesizable cores, the DSM is a pre-implementation, pre-synthesis model. It does no |

| contain any scan test insertion or BIST and is not a Sign-Off Model (SOM).                |

# Chapter 2 **Initial DSM Configuration**

This chapter describes the functionality of the ARM Design Simulation Model for SystemC (DSM).

### It contains the following sections:

- Prerequisites on page 2-2

- Extracting and Installing the DSM on page 2-3.

- How to test the DSM on page 2-4.

- Integrating with Simulators on page 2-5.

- TARMAC Trace on page 2-8

### 2.1 Prerequisites

This section describes prerequisites to using the DSM.

- DSM built and downloaded in .tgz format from ARM IP Exchange (www.armipexchange.com).

- GCC Compiler. If you are using Synopsys VCS, refer to the Synopsys documentation for the required gcc versions.

- Refer to the README file in your installation directory for specific tool versions required, model-specific limitations or restrictions, and supported registers.

### 2.2 Extracting and Installing the DSM

Before proceeding, ensure you have built and downloaded the *<dsm package>*.tgz for the desired IP from ARM IP Exchange (*www.armipexchange.com*).

### 2.2.1 Installing Using the Command Line

To install using the command line, follow the instructions below:

- 1. cd to the directory where you wish to install the DSM.

- 2. Extract the files from the *<dsm package>*.tgz as follows:

```

% tar -xvzf <dsm package>.tgz

gcc/EULA.pdf

gcc/docs

gcc/dsm

gcc/testbench

```

The directory now contains the DSM release.

### 2.3 How to test the DSM

| — Note |  |

|--------|--|

| 11010  |  |

You must set the DSM\_MODEL\_PATH environment variable to point to the directory that contains the DSM implementation libraries. If you do not set the variable, the [DSM MODULE NAME]\_TESTBENCH.sh script assume the DSM\_MODEL\_PATH is one directory above the scripts location in the dsm directory. If the path is not set correctly, the simulator compiler exits with an error looking for the [DSM MODULE NAME] files or library files.

For all simulators, the module search path must include the path to the DSM libraries. Reference the [DSM MODULE NAME]\_TESTBENCH.sh for a detailed example. In the following sections, variables are defined as follows:

- [DSM PATH] is the path the DSM release dsm directory (i.e., \$DSM RELEASE DIR/dsm).

- [DSM MODULE NAME] is the Component name specified on the portal.

- [PRODUCT NAME] is the ARM IP name.

Execute the [DSM MODULE NAME]\_TESTBENCH.sh executable within the expanded package to check that operation is valid. The DSM is contained within a testbench that is supplied with the package. The script requires that you select a system-installed simulator. You can specify the simulator to use by setting one of the following parameters:

vcs Selects the VCS simulator.

ius Selects the Cadence Incisive simulator.

mti Selects the QuestaSim simulator.

—— Note ———

The DSM is not intended for use with Accellera (OSCI) simulations.

A test that executes correctly prints the following message at the end of the simulation:

DSM: \*\*\* TEST PASSED \*\*\*

### 2.4 Integrating with Simulators

To use the DSM Model, add the following environment variables to your environment:

#### bash commands:

- export PATH=[DSM\_PATH]/univentUtil/bin:\$PATH

- export LD LIBRARY PATH=[DSM PATH]/univentUtil/lib:[DSM PATH]:\$LD LIBRARY PATH

### C shell commands:

- setenv PATH [DSM PATH]/univentUtil/bin:\$PATH

- setenv LD LIBRARY PATH [DSM PATH]/univentUtil/lib:[DSM PATH]:\$LD LIBRARY PATH

### 2.4.1 VCS

### To integrate the DSM with VCS:

1. Create the Verilog wrapper:

syscan -full64 -sysc=230 -cflags "-DCM\_SYSC\_IO\_UNIVENT\_TARMAC -DCM\_SYSC\_REMOVE\_SCOPE" [DSM\_PATH]/[DSM\_MODULE NAME].cpp:[DSM\_MODULE NAME]

2. Add the following to the VCS command line:

-full64 -sysc=230 -sysc=adjust\_timeres -LDFLAGS "-L[DSM\_PATH] " [DSM\_PATH]/univentUtil/lib/[PRODUCT NAME]\_tarmac\_dpi.so [DSM\_PATH]/libcarbon5.so [DSM\_PATH]/lib[DSM MODULE NAME].a [DSM\_PATH]/univent\_tarmac.cpp

### 2.4.2 Cadence Incisive

To integrate the DSM with Cadence Incisive, add the following to the irun command line:

-64bit [DSM\_PATH]/univentUtil/lib/[PRODUCT NAME]\_tarmac\_dpi.so -sysc -scautoshell verilog -DCM\_SYSC\_IO\_UNIVENT\_TARMAC -DCM\_SYSC\_REMOVE\_SCOPE -I[DSM\_PATH] -L[DSM\_PATH] [DSM\_PATH]/[DSM\_MODULE NAME].cpp [DSM\_PATH]/univent\_tarmac.cpp -L[DSM\_PATH] -lcarbon5 [DSM\_PATH]/lib[DSM\_MODULE NAME].a

### 2.4.3 Mentor QuestaSim (ModelSim)

To integrate the DSM with Mentor QuestaSim:

Before running vsim, compile and link the libraries as follows:

sccom -64 -g -suppress 6102 -DCM\_SYSC\_IO\_UNIVENT\_TARMAC -DCM\_SYSC\_REMOVE\_SCOPE -I[DSM\_PATH] [DSM\_PATH]/[DSM\_MODULE NAME].cpp [DSM\_PATH]/univent\_tarmac.cpp sccom -64 -link -suppress 6102 -L[DSM\_PATH] -I[DSM\_MODULE NAME] -lcarbon5 [DSM\_PATH]/univentUtil/lib/[DSM\_MODULE NAME] tarmac\_dpi.so

### 2.5 TARMAC Trace

This section describes enabling and disabling TARMAC trace.

### 2.5.1 Enabling TARMAC Trace

To enable the TARMAC trace, refer to the TARMAC specifications in the docs directory of the DSM release, or review the [DSM MODULE NAME]\_TESTBENCH.sh file for the \*TARMAC\* environment variables.

You must also compile with the define CM\_SYS\_IO\_UNIVENT (for example, -DCM\_SYS\_IO\_UNIVENT) to enable.

### 2.5.2 Disabling TARMAC Trace

To disable the TARMAC trace, remove the CM\_SYS\_IO\_UNIVENT define from the compile. Or, set the environment variable \*\_TARMAC\_ENABLE to never.

## Chapter 3 **Model Limitations**

This chapter contains the following sections:

• Limitations of use on page 3-2.

### 3.1 Limitations of use

Although DSMs match the architecture and functionality of the appropriate core designs, they are subject to the limitations that the following sections describe:

- Supported simulators

- Unsupported simulator functions.

- *Internal scan chain modeling.*

- Caches and registers.

### 3.1.1 Supported simulators

The DSM model is limited to Linux 64-bit. It has been tested and is supported on the following simulators:

- Synopsys VCS

- Cadence Incisive

- Mentor QuestaSim

### 3.1.2 Unsupported simulator functions

The following simulator functions are not supported:

### Save and Restore, also known as checkpointing

Save the simulation at a determined point of time, also known as a snapshot, and restore the simulation to that point of time.

### **Power-aware simulation**

Power-aware simulation

### 3.1.3 Internal scan chain modeling

DSMs are derived from the RTL description of the core that they model. The final netlist for the core might contain internal scan chains that were added during synthesis. It is not possible to use DSMs to model these scan chains because they do not exist in the device RTL. However, the *Sign-Off Model* (SOM) of a device models the scan chains.

### 3.1.4 Caches and registers

The DSM Model provides visibility into certain registers. Refer to the README file included with your DSM Model for a list of supported registers.

### 3.1.5 Waveform dumping

Refer to the README file included with your DSM Model for instructions and limitations of Waveform dumping for your particular model.

## Appendix A **Revisions**

This appendix describes the technical changes between released issues of this book.

### Table A-1 Issue A

| Change                           | Location | Affects |

|----------------------------------|----------|---------|

| First release for SystemC models | -        | -       |