# arm

# Arm® Corstone<sup>™</sup>-1000 for MPS3 Application Note AN550

Issue D

DAI 0550

Non-Confidential Copyright© 2021-2023 Arm Limited (or its subsidiaries). All rights reserved.

## Arm® Corstone<sup>™</sup>-1000 for MPS3

## Application Note AN550

Copyright © 2021-2023 Arm Limited (or its subsidiaries). All rights reserved.

#### Release information

#### Document history

| Issue | Date        | Confidentiality  | Change                                                                                                                                                                                                                                                                                                                                     |

|-------|-------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| А     | 25 May 2021 | Confidential     | First release                                                                                                                                                                                                                                                                                                                              |

| В     | 7 Dec 2021  | Confidential     | V1 bitfile and updated image captures                                                                                                                                                                                                                                                                                                      |

| С     | 20 Jan 2022 | Non-Confidential | Non-Confidential proprietary Notice<br>1.9 Additional required hardware – section added<br>Figure 2-1: System Overview – updated<br>2.4.7 Flash - updated                                                                                                                                                                                  |

| D     | 04 Jan 2023 | Non-Confidential | Version of bitfile changed to V2 and updated image<br>captures, fixed hyperlink captions<br>8.10 Other applications - updated<br>7.3.3 Creating a Development Studio Debug<br>Connection - updated<br>7.5 Establishing a Debug Session – minor fixes.<br>8.7 Preload of the SE ROM, EXTSYSO Code SRAM,<br>OTP and the QSPI Flash - updated |

#### Non-Confidential Proprietary Notice

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third-party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Copyright © 2021-2023 Arm Limited (or its subsidiaries). All rights reserved. Non-Confidential This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail. The Arm corporate logo and words marked with ® or ™ are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at http://www.arm.com/company/policies/trademarks.

Copyright © 2021-2023 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

(LES-PRE-20349)

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

#### **Product Status**

The information in this document is Final, that is for a developed product.

#### Web Address

#### developer.arm.com

#### Inclusive language commitment

Arm values inclusive communities. Arm recognizes that we and our industry have used terms that can be offensive. Arm strives to lead the industry and create change.

We believe that this document contains no offensive language. To report offensive language in this document, email **terms@arm.com**.

#### LICENCE GRANTS

THE END USER LICENCE AGREEMENT FOR THE ARM SYSTEM OR SUBSYSTEM FOR AN ARM FPGA PROTOTYPING BOARD ("THE LICENCE"), LES-PRE-21902, DEFINES THE LICENCE GRANTS.

#### DELIVERABLES

Part A

#### Hardware Binaries: Encrypted FPGA bitstream file containing the Corstone-1000 product and other Arm technology.

#### **Software Binaries:**

Motherboard Configuration Controller binary, including Arm<sup>®</sup> Keil<sup>®</sup> USB and SD card drivers, and Analog Devices FMC EEPROM reader. Self-test binary.

#### Documentation:

Documentation, provided as **PDF**

#### Part B

#### Example Code:

Platform initialisation source code Platform specific libraries and source code Selftest example source code Arm source code portions of the Selftest software project

#### Part C

None

#### Part D

None

# Contents

| 1 Introduction                        |    |

|---------------------------------------|----|

| 1.1 Purpose of this application note  |    |

| 1.2 Intended audience                 |    |

| 1.3 Conventions                       |    |

| 1.3.1 Glossary                        |    |

| 1.3.2 Typographical conventions       |    |

| 1.4 Additional reading                |    |

| 1.5 Feedback                          |    |

| 1.5.1 Feedback on this product        | 11 |

| 1.5.2 Feedback on content             | 11 |

| 1.5.3 Other information               | 11 |

| 1.6 Terms and Abbreviations           |    |

| 1.7 Subsystem version details         |    |

| 1.8 Encryption key                    |    |

| 1.9 Additional required hardware      | 14 |

| 2 Overview                            |    |

| 2.1 SSE-710 Subsystem                 |    |

| 2.2 System Block Diagram              |    |

| 2.3 EXTSYS0 - External System 0       | 17 |

| 2.3.1 EXTSYS0 Block Diagram           |    |

| 2.4 Components                        |    |

| 2.4.1 SSE-710 Subsystem               |    |

| 2.4.2 NIC-400                         |    |

| 2.4.3 Xilinx QSPI Controller          | 21 |

| 2.4.4 Xilinx MIG - DDR4               | 21 |

| 2.4.5 DDR4 (OCVM) SODIMM EEPROM SBCon | 21 |

| 2.4.6 Debug UART Peripheral           | 21 |

| 2.4.7 Flash                           | 21 |

| 2.4.8 USB                             | 21 |

| 2.4.9 10/100 Ethernet                 |    |

| 2.4.10 Audio                          |    |

| 2.4.11 FPGA Version ID Register                                                                   | 22 |

|---------------------------------------------------------------------------------------------------|----|

| 2.4.12 FPGA Utilization                                                                           | 22 |

| 2.5 Memory Map Overview                                                                           | 23 |

| 2.5.1 SSE-710 Host System Memory Map                                                              | 23 |

| 2.5.2 SSE-710 AON Expansion Memory Map                                                            | 24 |

| 2.5.3 SSE-710 Secure Enclave Memory Map                                                           | 24 |

| 2.5.4 EXTSYS0 Memory Map                                                                          | 25 |

| 2.5.5 Memory Sizes – Summary                                                                      | 27 |

| 3 Programmers Model                                                                               | 28 |

| 3.1 Xilinx Internal BRAM                                                                          | 28 |

| 3.2 XNVM QSPI Flash                                                                               | 28 |

| 3.3 SE QSPI Flash                                                                                 | 28 |

| 3.4 OCVM DDR4                                                                                     | 28 |

| 3.5 UART Support                                                                                  | 28 |

| 3.6 SSE-710 Implementation                                                                        | 29 |

| 3.6.1 SSE-710 Power Control                                                                       | 29 |

| 3.6.2 SSE-710 Host AON Expansion RTC                                                              | 29 |

| 3.6.3 SSE-710 Expansion Shared Interrupt Map                                                      | 30 |

| 3.7 EXTSYS0                                                                                       | 31 |

| 3.7.1 System Control Registers                                                                    | 31 |

| 3.7.2 EXTSYS0 Interrupt Connectivity                                                              | 32 |

| 3.8 SBCon I <sup>2</sup> C                                                                        | 33 |

| 3.9 Audio I <sup>2</sup> S                                                                        | 33 |

| 3.10 SMM Registers                                                                                | 36 |

| 3.11 LEDs                                                                                         | 36 |

| 3.12 FPGA Serial Communication Controller (SCC)                                                   | 37 |

| 3.13 FPGA System Control and I/O Registers                                                        | 40 |

| 4 Clock Architecture                                                                              | 41 |

| 4.1 Clocks                                                                                        | 41 |

| 4.1.1 FPGA External Clocks                                                                        | 41 |

| 4.1.2 FPGA Generated Internal Clocks                                                              | 41 |

| 4.1.3 SSE-710 Clocks                                                                              | 42 |

| 4.1.4 EXTSYS0 Clocks                                                                              | 42 |

| 5 Reset Architecture                                                                              | 43 |

| Copyright © 2021-2023 Arm Limited (or its subsidiaries). All rights reserved.<br>Non-Confidential |    |

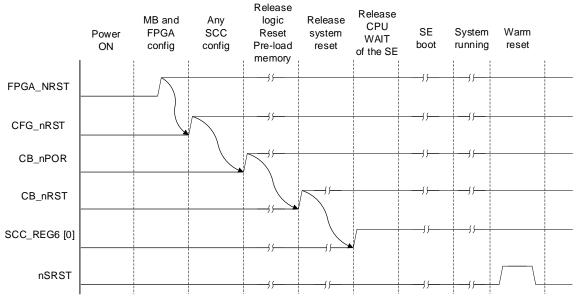

| 5.1 Resets                                                                                                                        | 43 |

|-----------------------------------------------------------------------------------------------------------------------------------|----|

| 5.1.1 FPGA Resets                                                                                                                 | 43 |

| 6 ZIP Bundle Description                                                                                                          | 45 |

| 6.1 Overall Structure                                                                                                             |    |

| 6.2 Documentation                                                                                                                 |    |

| 6.3 MPS3 Board Revision and Support                                                                                               | 46 |

| 6.3.1 Identifying the MPS3 Board Revision                                                                                         |    |

| 6.3.2 Bundle Support for Specific MPS3 Board Revisions                                                                            | 46 |

| 6.4 Bundle Directory Tree/Structure                                                                                               |    |

| 7 Software and Debug                                                                                                              | 49 |

| 7.1 Overview                                                                                                                      | 49 |

| 7.2 Example Software Project                                                                                                      | 49 |

| 7.3 Debug Support                                                                                                                 | 50 |

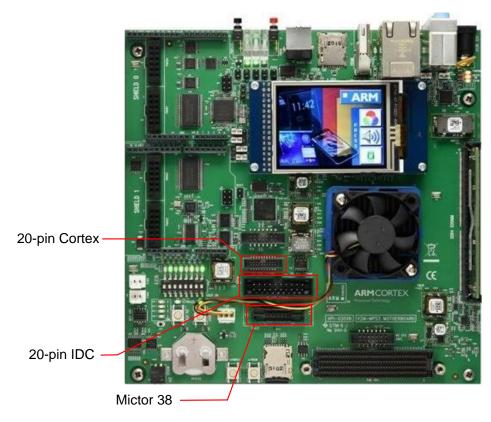

| 7.3.1 DSTREAM Debug Hardware                                                                                                      | 50 |

| 7.3.2 Debug Connectivity                                                                                                          | 50 |

| 7.3.3 Creating a Development Studio Debug Connection                                                                              | 51 |

| 7.4 Building the Software                                                                                                         | 54 |

| 7.5 Establishing a Debug Session                                                                                                  | 56 |

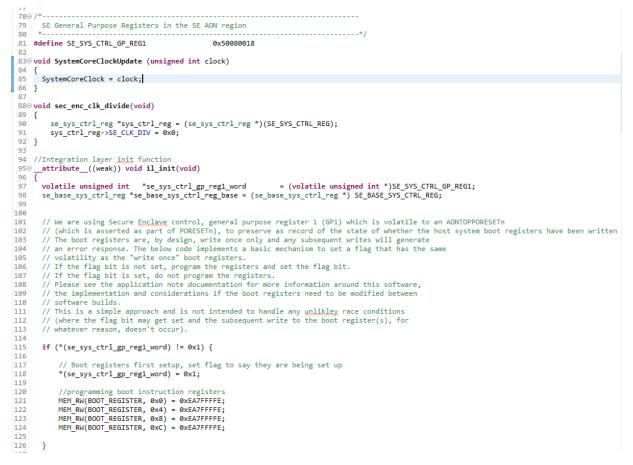

| 7.6 Modifying the SSE-710 Boot Register                                                                                           | 61 |

| 7.6.1 SSE-710 Boot Register Overview and Volatility                                                                               | 61 |

| 7.6.2 MPS3 Boot Register Control                                                                                                  | 61 |

| 8 Using AN550 on the MPS3 Board                                                                                                   | 64 |

| 8.1 Pre-Requisites                                                                                                                | 64 |

| 8.2 Loading the Boardfiles onto the MPS3 SD Card                                                                                  | 65 |

| 8.3 UART Serial Port Terminal Emulator Settings                                                                                   | 66 |

| 8.4 MPS3 USB Serial Port Drivers for Windows                                                                                      | 66 |

| 8.5 Running the FPGA image file on the MPS3 Board                                                                                 | 67 |

| 8.6 MCC Debug UART – Serial Port 0                                                                                                | 70 |

| 8.6.1 MCC Debug UART – Verbose Output                                                                                             | 71 |

| 8.6.2 MCC Debug UART – Reboot Control                                                                                             | 72 |

| 8.7 Preload of the SE ROM, EXTSYS0 Code SRAM, OTP and the QSPI Flash                                                              | 72 |

| 8.7.1 The Preload Sequence                                                                                                        | 72 |

| 8.7.2 Preload Image Configuration (images.txt)                                                                                    | 73 |

| <b>8.7.3 Preloading QSPI Memories</b><br>Copyright <sup>©</sup> 2021-2023 Arm Limited (or its subsidiaries). All rights reserved. | 74 |

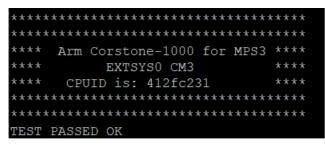

| 8.7.4 Preload selftest software                                                   | .74 |

|-----------------------------------------------------------------------------------|-----|

| 8.8 Supported Preload SE ROM, EXTSYSO Code SRAM, OTP and Flash File Types         | .76 |

| 8.9 Supported Preload SE ROM, EXTSYSO Code SRAM, OTP and Flash File Naming Format | .76 |

| 8.10 Other applications                                                           | .76 |

# **1** Introduction

# 1.1 Purpose of this application note

This document describes the features and functionality of AN550 SMM. AN550 SMM is an FPGA implementation based on the Corstone-1000 product, which is extended to support a single external system and hardware peripherals.

# **1.2 Intended audience**

This application note document is written for experienced hardware, System-on-Chip (SoC) and software engineers who might or might not have experience with Arm products. Such engineers typically have experience in writing Verilog and of performing synthesis but might have limited experience of integrating and implementing Arm products.

# **1.3 Conventions**

The following subsections describe conventions used in Arm documents.

## 1.3.1 Glossary

The Arm Glossary is a list of terms used in Arm documentation, together with definitions for those terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

See the **Arm® Glossary** for more information.

| Convention             | Use                                                                                                                                                                                    |  |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| italic                 | Introduces citations.                                                                                                                                                                  |  |

| bold                   | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.                                                  |  |

| monospace              | Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.                                                                            |  |

| monospace <b>bold</b>  | Denotes language keywords when used outside example code.                                                                                                                              |  |

| monospace<br>underline | Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.                                                |  |

| <and></and>            | Encloses replaceable terms for assembler syntax where they appear in code or code fragments.<br>For example:<br>MRC p15, 0, <rd>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></rd> |  |

## 1.3.2 Typographical conventions

Copyright <sup>©</sup> 2021-2023 Arm Limited (or its subsidiaries). All rights reserved. Non-Confidential

| Convention     | Use                                                                                                                                                                                                                   |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMALL CAPITALS | Used in body text for a few terms that have specific technical meanings, that are defined in the Arm <sup>®</sup> Glossary. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE. |

| Caution        | This represents a recommendation which, if not followed, might lead to system failure or damage.                                                                                                                      |

| Warning        | This represents a requirement for the system that, if not followed, might result in system failure or damage.                                                                                                         |

| Danger         | This represents a requirement for the system that, if not followed, will result in system failure or damage.                                                                                                          |

| Note           | This represents an important piece of information that needs your attention.                                                                                                                                          |

| - Č            | This represents a useful tip that might make it easier, better or faster to perform a task.                                                                                                                           |

| Remember       | This is a reminder of something important that relates to the information you are reading.                                                                                                                            |

# 1.4 Additional reading

This document contains information that is specific to this product. See the following documents for other relevant information:

#### Table 1-1 Arm publications

| Document name                                                         | Document ID       | Licensee only |

|-----------------------------------------------------------------------|-------------------|---------------|

| Arm® MPS3 FPGA Prototyping Board Technical Reference Manual           | 100765            | No            |

| Arm® Cortex®-M System Design Kit Technical Reference Manual           | DDI 0479          | No            |

| Arm® Corstone™ SSE-710 Subsystem Technical Reference Manual           | 102342_0000_01_en | No            |

| Arm® Corstone™ SSE-710 Subsystem Configuration and Integration Manual | 102343_0000_01_en | Yes           |

| Arm® CoreLink™ SSE-050 Subsystem Technical Reference Manual           | 100918_0001_00_en | No            |

#### Table 1-2 Other publications

| Document name                         | Document ID |

|---------------------------------------|-------------|

| Xilinx Vivado Design Suite User Guide | UG909       |

Copyright  $^{\odot}$  2021-2023 Arm Limited (or its subsidiaries). All rights reserved. Non-Confidential

# 1.5 Feedback

Arm welcomes feedback on this product and its documentation.

## 1.5.1 Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

## 1.5.2 Feedback on content

If you have comments on content, send an email to errata@arm.com and give:

- The title Arm® Corstone<sup>™</sup>-1000 for MPS3 Application Note AN550.

- The number DAI 0550, Issue D.

- If applicable, the page number(s) to which your comments refer.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

Arm tests the PDF only in Adobe Acrobat and Acrobat Reader and cannot guarantee the quality of the represented document when used with any other PDF reader.

## 1.5.3 Other information

- Arm Documentation, https://developer.arm.com/documentation/

- Arm Technical Support Knowledge Articles, https://www.arm.com/support/technical-support

- Arm Support, https://www.arm.com/support

- Arm Glossary, https://developer.arm.com/documentation/aeg0014/g

The Arm Glossary is a list of terms used in Arm documentation, together with definitions for those terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

# **1.6 Terms and Abbreviations**

| ADB      | AMBA Domain Bridge                                                            |

|----------|-------------------------------------------------------------------------------|

| AHB      | Advanced High-performance Bus                                                 |

| APB      | Advanced Peripheral Bus                                                       |

| AXI      | Advanced Extensible Interface                                                 |

| BRAM     | FPGA Block RAM                                                                |

| CA       | Cryptographic Accelerator                                                     |

| CMSDK    | Cortex-M System Design Kit                                                    |

| CPU      | Central Processing Unit                                                       |

| CVM      | On-Chip Volatile Memory                                                       |

| DPRAM    | Dual Port RAM                                                                 |

| EIS      | Engineering Implementation Specification                                      |

| EXPMST   | Expansion Manager                                                             |

| EXTSYS0  | External System O                                                             |

| FPGA     | Field Programmable Gate Array                                                 |

| FW       | Firewall                                                                      |

| GIC      | Generic Interrupt Controller                                                  |

| JTAG     | Joint Test Action Group                                                       |

| KB       | Kilo Byte                                                                     |

| LAR      | Long Address Range (preloading mechanism)                                     |

| LUTs     | Lookup tables                                                                 |

| MB       | Mega Byte                                                                     |

| MCC      | Motherboard Configuration Controller                                          |

| MHU      | Message Handling Unit                                                         |

| MIG      | Memory Interface Generator                                                    |

| MPS3     | Microcontroller Prototyping System 3                                          |

| NIC      | Network Interconnect                                                          |

| OCVM     | Off-Chip Volatile Memory                                                      |

| RAM      | Random Access Memory                                                          |

| RAZ      | Read as Zero                                                                  |

| ROM      | Read Only Memory                                                              |

| RTC      | Real Time Clock                                                               |

| RTL      | Register Transfer Level                                                       |

| SCB      | Security Control Bits                                                         |

| SCC      | Serial Configuration Controller                                               |

| SE       | Secure Enclave                                                                |

| SMM      | Soft Macrocell Model system implemented as an FPGA image and                  |

| <u> </u> | described in this AN                                                          |

| SoC      | System on Chip                                                                |

| SWD      | Serial Wire Debug                                                             |

| TBD      | To Be Defined                                                                 |

|          | Technical Reference Manual                                                    |

| UART     | Universal Asynchronous Receiver/Transmitter                                   |

|          | Copyright © 2021-2023 Arm Limited (or its subsidiaries). All rights reserved. |

|          | Non-Confidential<br>Page                                                      |

| UPC  | Universal Part Code                         |

|------|---------------------------------------------|

| USB  | Universal Serial Bus                        |

| WI   | Write Ignored                               |

| XIP  | eXecute-In-Place                            |

| XNVM | eXecute-in-place Non-volatile Memory (XNVM) |

## **1.7 Subsystem version details**

| Version | Descriptions               |

|---------|----------------------------|

| r1p2    | CoreLink NIC-400           |

| r1p1    | Cortex-M System Design Kit |

| r0p0    | Corstone SSE-710 Subsystem |

| r0p1    | CoreLink SSE-050 Subsystem |

| r0p1    | Cortex-M0+ MCU             |

| r1p0    | Cortex-A35 CPU             |

| r2p1    | Cortex-M3 MCU              |

Table 1-3: IP Versions

# **1.8 Encryption key**

Arm supplies the MPS3 prototyping board with a decryption key programmed into the FPGA. This key is needed to enable loading of prebuilt encrypted images.

The FPGA programming file that is supplied as part of the bundle is encrypted.

A battery supplies power to the key storage area of the FPGA. Any keys stored in the FPGA might be lost when battery power is lost. If this happens you must return the board to Arm for reprogramming of the key.

# 1.9 Additional required hardware

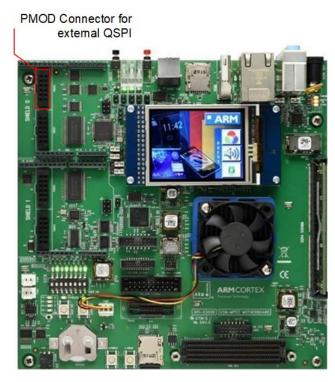

A 32 MB QSPI flash PMOD module is required to support the XNVM memory (see section **3.2**) in this implementation. If this is not fitted, the software application referenced in section **8.10** and section **7.2**, will not function as described in this document.

#### The table below shows the PMOD module required for this implementation:

| Description                    | Manufacturer | UPC          |

|--------------------------------|--------------|--------------|

| PMOD 32MB SF3 QSPI Flash Board | Digilent     | 645220775590 |

#### Table 1-4: Additional hardware

The PMOD module is not distributed as part of the orderable MPS3 board product.

If the module is not fitted, the following may be observed when running the software applications in section 7.2 and 8.10:

- When running the sefltest program (described in section 7.2), and selecting the #2 Test XNVM (QSPI FLASH), the test will initiate but never complete.

- When not preloading selftest the SE will initiate preload test code in 8.5 but never complete.

- The software application, referenced in section **8.10** will not successfully boot and run as expected.

# 2 Overview

This SMM is based on the Corstone-1000 product. The product is then extended to add a single external system and peripherals to support software development.

# 2.1 SSE-710 Subsystem

The SSE-710 Subsystem has configurable options. These options are documented in Arm<sup>®</sup> Corstone SSE-710 Configuration and Integration Manual, Chapter 2 Installation, Configuration, and the OoB test.

The following table shows some of the most important configuration settings and also where AN550 SMM uses non-default values:

| Parameter          | Implemented Values | Default Values | Description                                         |

|--------------------|--------------------|----------------|-----------------------------------------------------|

| NEON_FP            | "TRUE"             | "FALSE"        | NEON_FP and FPU present                             |

| HOST_CPU_TYPE      | Cortex-A35 {2}     | Cortex-A32{1}  | Host CPU type                                       |

| HOST_CPU_NUM_CORES | 1                  | 4              | Number of Host CPU cores                            |

| SEC_ENC_ROM_SIZE   | 64                 | 32             | Size of Secure Enclave ROM in KB                    |

| SEC_ENC_RAM_SIZE   | 512                | 128            | Size of Secure Enclave RAM in KB                    |

| EXPMSTO_NUM_RGN    | 8                  | 32             | Number of regions for EXPMSTO<br>Firewall Component |

| EXPMST1_NUM_RGN    | 8                  | 32             | Number of regions for EXPMST1<br>Firewall Component |

#### Table 2-1: SSE-710 configuration options

The following table shows some of the most important external to SSE-710 Subsystem settings:

| Port     | Implemented Values | Meaning             | Description                          |

|----------|--------------------|---------------------|--------------------------------------|

| SOCID    | 0x76B0023B         | AN550 (CS1000 FPGA) | SoC Identification                   |

| OCVMSIZE | Ox1F               | 2GB                 | Off-Chip Volatile Memory             |

| XNVMSIZE | 0x19               | 32MB                | eXecute in place Non-Volatile Memory |

| CVMSIZE  | 0x16               | 4MB                 | On-Chip Volatile Memory              |

#### Table 2-2: SSE-710 external setting

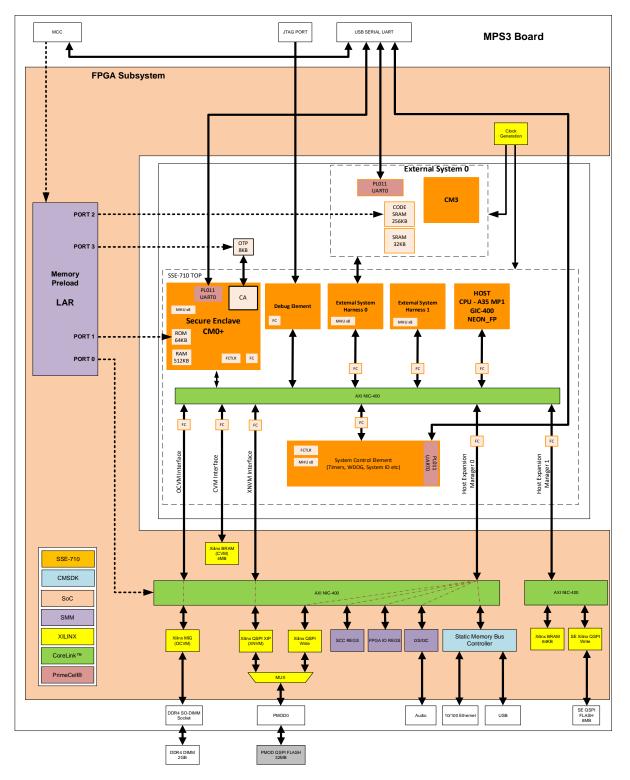

# 2.2 System Block Diagram

The diagram below shows a high-level view of the full MPS3 Prototyping Board Corstone-1000 product implementation.

Figure 2-1: System Overview

Copyright <sup>©</sup> 2021-2023 Arm Limited (or its subsidiaries). All rights reserved. Non-Confidential

# 2.3 EXTSYS0 - External System 0

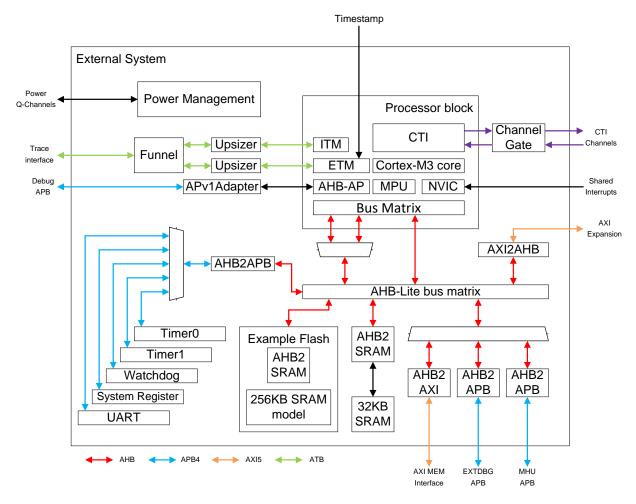

The implementation supports a single external system populating one of the EXTSYS sockets in SSE-710. The External System 0 is based on a modified SSE-050, a Cortex-M3 based subsystem.

## 2.3.1 EXTSYS0 Block Diagram

The following diagram shows the External System 0, which is based on SSE-050 with minor modifications.

Figure 2-2: EXTSYS0 System Overview

# 2.4 Components

The following sections detail the components used in the FPGA Subsystem.

## 2.4.1 SSE-710 Subsystem

The following sections detail the components used in the SSE-710 Subsystem.

#### 2.4.1.1 Secure Enclave

The following sections detail components and models used in the Secure Enclave.

#### 2.4.1.1.1 Secure Enclave ROM Model and Preload Support

The Secure Enclave ROM is implemented as a Dual Port RAM (DPRAM) within the FPGA. The Secure Enclave boots from this ROM. The implementation within AN550 SMM supports:

- Default boot ROM embedded as a preload on the SE ROM in the FPGA programming (.bit) file.

- Debug access to the SE ROM/RAM. In cases where the MCC does not preload the memory, the FPGA image implements a pre-load of this SE ROM to enable the processor to reach a state where debug is accessible.

- Preload of ROM from a file on the config SD card. The MCC holds the target SE Cortex-MO+ in reset and CPUWAIT asserted during preload. The MCC then releases the reset, then CPUWAIT on the SE Cortex-MO+ to enable the SE Cortex-MO+ to boot from the SE ROM.

#### 2.4.1.2 Single External System (EXTSYS0)

External System 0 includes the following:

- Modified SSE-050 Cortex-M3 based System with Arm<sup>®</sup> CoreSight<sup>™</sup> SoC-600 support and Cortex-M3 ETM.

- 256KB Code SRAM

- Code SRAM replaced with DPRAM to provide support for preload from MPS3 MCC.

- 32KB SRAM

- PL011 UART

- Timers, Watchdog, and System Register.

- AXI, AHB, and APB interconnect to support connection to different SSE-710 interfaces.

- ATB network modules to enable connection all trace sources to the SSE-710.

- Channel Gate to be able to limit cross-trigger functionality based on the SE Life Cycle State.

- Addition of PL011 UART to APBTARGEXP2.

#### 2.4.1.2.1 EXTSYS0 - Cortex-M3 Code SRAM Preload Support

The EXTSYSO code RAM is implemented as a DPRAM within the FPGA. The Cortex-M3 boots from this RAM. The implementation within AN550 SMM supports the following:

- Default boot RAM embedded as a preload on the Cortex-M3 Code SRAM in the FPGA programming (.bit) file.

- Debug access to the Cortex-M3 Code SRAM. In cases where the MCC does not preload the memory as the above, the FPGA image implements a pre-load of this RAM to enable the processor to reach a state where debug is accessible.

- Preload of Cortex-M3 Code RAM from a file on the MPS3 SD card. The MCC holds the target SE Cortex-M0+ CPUWAIT asserted during preload. As the Cortex-M0+ is held in CPUWAIT, the EXTSYS0 CPUWAIT is held asserted as the reset default. The MCC then releases the CPUWAIT on the SE Cortex-M0+ to enable the SE Cortex-M0+ to boot from the SE ROM. The EXTSYS0 CPUWAIT must be de-asserted by software in order to boot the EXTSYS0 from the Cortex-M3 Code SRAM.

#### 2.4.1.3 Host System CPU Configuration

The Host System CPU is a Cortex-A35 (MP1 single core), which is configured with the following parameters:

- NEON\_FP: "TRUE"

- CRYPTO: "FALSE" (not present)

- L1\_ICACHE\_SIZE: "32KB"

- L1\_DCACHE\_SIZE: "32KB"

- L2\_CACHE\_SIZE: "512KB"

#### 2.4.1.4 Host System Configuration

The Host System is configured with the following parameters:

- SSE-710 Expansion SLV0 & SLV1 tied off/un-used.

- Shared Interrupts: 64

- MHU Channels:

- o 32 channels between SE and Host

- o 4 channels between Host and EXTSYS0

- o 4 Channels between SE and EXTSYS0

- o 1 Channel for all MHUs related to External System 1 (External system 1 is not implemented)

#### 2.4.1.5 Host FW Configuration

The following table shows the FW Configuration settings:

| FW Configuration         | Value                                  |

|--------------------------|----------------------------------------|

| XNVM_RSE_LVL             | 1                                      |

| XNVM_NUM_RGN             | 32                                     |

| CVM_RSE_LVL              | 1                                      |

| CVM_NUM_RGN              | 32                                     |

| DBG_NUM_RGN              | 8                                      |

| EXTSYS0_NUM_RGN          | 8                                      |

| EXTSYS1_NUM_RGN          | 8                                      |

| EXPSLV0_NUM_RGN          | 8                                      |

| EXPSLV1_NUM_RGN          | 8                                      |

| EXPMSTO_PE_LVL           | 2                                      |

| EXPMSTO_RSE_LVL          | 1                                      |

| EXPMSTO_NUM_RGN          | 8                                      |

| EXPMSTO_MXRS             | 29                                     |

| EXPMST1_PE_LVL           | 2                                      |

| EXPMST1_RSE_LVL          | 1                                      |

| EXPMST1_NUM_RGN          | 8                                      |

| EXPMST1_MXRS             | 29                                     |

| OCVM_RSE_LVL             | 1                                      |

| OCVM_NUM_RGN             | 32                                     |

| HOST_FC_ERR_RESP_DEF_32  | 0xdeaddeaddead                         |

| HOST_FC_ERR_RESP_DEF_64  | Oxdeaddead                             |

| HOST_FC_ERR_RESP_DEF_128 | 0xDEADDEADDEADDEADDEADDEADDEADD<br>EAD |

## 2.4.2 NIC-400

The NIC-400 connects the SSE-710 Subsystem to the FPGA Subsystem peripherals.

Copyright <sup>©</sup> 2021-2023 Arm Limited (or its subsidiaries). All rights reserved. Non-Confidential

DAI 0550 Issue D Overview

## 2.4.3 Xilinx QSPI Controller

The QSPI controllers connect the QSPI flash interfaces to the NIC-400 implemented in the FPGA Subsystem.

## 2.4.4 Xilinx MIG – DDR4

The Xilinx MIG controller connects the DDR4 Memory interface to the NIC-400 that is implemented in the FPGA Subsystem.

## 2.4.5 DDR4 (OCVM) SODIMM EEPROM SBCon

The SMM implements a single SBC on  $I^2C$  module to read the EEPROM on the DDR4 SODIMM Module. See section 3.8 for more details.

## 2.4.6 Debug UART Peripheral

The following UARTs are accessible over USB on the MPS3 board:

- Secure Enclave UARTO (PrimeCell PL011).

- HOST Subsystem UARTO (PrimeCell PL011).

- HOST Subsystem UART1 Secure (PrimeCell PL011).

- EXTSYSO UARTO (PrimeCell PL011).

- MCC debug UART. The MPS3 board supports a debug serial port connection to the MCC that enables functions such as reset to be initiated by a host terminal. See section 8.6 on MCC Debug UART for more details.

## 2.4.7 Flash

- 32MB of QSPI flash is supported on the platform and is accessible for reading and writing through the EXPMSTO interface, and for read only XIP through the XNVM interface. The external QSPI PMOD flash module fitting is shown in the Loading the Boardfiles onto the MPS3 SD Card section. The QSPI flash can be preloaded by the MCC and is accessible from the SE Cortex-M0+, Host Cortex-A35 CPU and EXTSYSO. The QSPI Xilinx controller is utilized to support QSPI flash.

- SE 8MB of QSPI flash is supported on the platform and is connected to the SSE-710 EXPMST1 port and the intention is to be accessible only from the SE Cortex-MO+. The QSPI Xilinx controller is utilized to support QSPI flash.

## 2.4.8 USB

The implementation connects to an ST Microelectronics Hi-Speed USB OTG controller (ISP1763) device through a static memory interface.

## 2.4.9 10/100 Ethernet

The implementation connects a Microchip LAN9220 device through a static memory interface. The device is accessible from the SSE-710 Expansion MSTRO interface.

## 2.4.10 Audio

The SMM implements a single I<sup>2</sup>S and a single I<sup>2</sup>C module directly connected to the MPS3 back panel audio sockets. I<sup>2</sup>S is used for data and I<sup>2</sup>C is used for control. The device is accessible from the SSE-710 Expansion MSTR0 interfaces.

## 2.4.10.1 SBCon I<sup>2</sup>C

A single two-wire I<sup>2</sup>C SBCon module supports configuration of the Cirrus Logic, Stereo CODEC (CS42L52) on the MPS3 board. See section 3.8 for more details.

#### 2.4.10.2 I<sup>2</sup>S Interface

A single I<sup>2</sup>S module connects the internal APB bus to the external I<sup>2</sup>S Audio CODEC. See section 3.9 for more details.

## 2.4.11 FPGA Version ID Register

A version register is supported and implemented within the SCC registers. The location of the SCC registers is defined in the memory map.

## 2.4.12 FPGA Utilization

AN550 SMM is designed for MPS3 board which uses a Xilinx Kintex Ultrascale XCKU115 FPGA. The FPGA features up to 8MB BRAM (2160 BlockRAM tiles) and up to 663,360 LUTs.

Full part number: XCKU115-FLVB1760-1-C.

The following table shows the total number of LUTs and BRAMs that are used in the SD card image.

| Site Type     | Used   | Util% |  |

|---------------|--------|-------|--|

| LUTs          | 519262 | 79    |  |

| BlockRAM Tile | 1486   | 69    |  |

Table 2-3 AN550 utilization summary

These numbers relate to the complete image, not individual IP blocks. The numbers must not be used to infer IP size, or the relative sizes of different IP blocks, because the implementation and system design can significantly differ.

# 2.5 Memory Map Overview

## 2.5.1 SSE-710 Host System Memory Map

The memory map implementation aligns with SSE-710 subsystem Host System memory map. The memory map is expanded to show the supported MPS3 peripherals in the Expansion Manager Regions and their mapping.

See Arm® Corstone SSE-710 Subsystem Technical Reference Manual for information on the SSE-710 subsystem Host System memory map.

| ROW<br>ID | Addro       | ess         | Size   | Region<br>Name      | Description                                                                                                             |

|-----------|-------------|-------------|--------|---------------------|-------------------------------------------------------------------------------------------------------------------------|

|           | From        | То          |        |                     |                                                                                                                         |

| 1         | 0x0000_0000 | 0x0000_0FFF | 4KB    | Boot Register       |                                                                                                                         |

| 2         | 0x0000_1000 | 0x000F_FFFF | 1024KB | Reserved            | Reserved                                                                                                                |

| 3         | 0x0010_0000 | 0x00FF_FFFF | 15MB   | Reserved            | Reserved                                                                                                                |

| 4         | 0x0100_0000 | 0x01FF_FFFF | 16MB   | Reserved            | Reserved                                                                                                                |

| 5         | 0x0200_0000 | 0x023F_FFFF | 4MB    | CVM                 | Volatile Memory implemented as BRAM                                                                                     |

| 6         | 0x0240_0000 | 0x03FF_FFFF | 28MB   | Reserved            | CVM space that is not implemented                                                                                       |

| 7         | 0x0400_0000 | 0x07FF_FFFF | 64MB   | Reserved            | Reserved                                                                                                                |

| 8         | 0x0800_0000 | 0x09FF_FFFF | 32MB   | XNVM                | eXecute-in-place Non-volatile Memory (Note: an external<br>QPSI PMOD Flash module should be connected to MPS3<br>board) |

| 9         | 0x0A00_0000 | OxOFFF_FFFF | 95MB   | Reserved            | XNVM space that is not implemented                                                                                      |

| 10        | 0x1000_0000 | Ox19FF_FFFF | 160MB  | Debug               |                                                                                                                         |

| 11        | 0x1A00_0000 | 0x3FFF_FFFF | 608MB  | Host<br>Peripherals |                                                                                                                         |

| 12        | 0x4000_0000 | 0x4000_FFFF | 64KB   | EXPMSTO             | FPGA – SCC Registers (note only 4KB of registers<br>implemented)                                                        |

| 13        | 0x4001_0000 | 0x4001_FFFF | 64KB   | EXPMSTO             | FPGA – I/O Registers (note only 4KB of registers<br>implemented)                                                        |

| 14        | 0x4002_0000 | 0x4002_FFFF | 64KB   | EXPMST0             | Audio I <sup>2</sup> S                                                                                                  |

| 15        | 0x4003_0000 | 0x4003_FFFF | 64KB   | EXPMST0             | SBCon Audio I <sup>2</sup> C (Configuration)                                                                            |

| 16        | 0x4004_0000 | 0x4004_FFFF | 64KB   | EXPMST0             | SBCon DDR4 (OCVM) SODIMM EEPROM                                                                                         |

| 17        | 0x4005_0000 | 0x4005_FFFF | 64KB   | EXPMST0             | R/W Xilinx QSPI controller (PG153 v3.2)                                                                                 |

| 18        | 0x4006_0000 | 0x400F_FFFF | 704KB  | EXPMSTO             | Reserved                                                                                                                |

| 19        | 0x4010_0000 | 0x401F_FFFF | 1MB    | EXPMSTO             | Ethernet Controller (LAN9220)                                                                                           |

Copyright <sup>©</sup> 2021-2023 Arm Limited (or its subsidiaries). All rights reserved. Non-Confidential

| ROW<br>ID | Addro       | ess         | Size   | Region<br>Name | Description                                           |

|-----------|-------------|-------------|--------|----------------|-------------------------------------------------------|

|           | From        | То          |        |                |                                                       |

| 20        | 0x4020_0000 | 0x402F_FFFF | 1MB    | EXPMST0        | USB Controller (ISP1763)                              |

| 21        | 0x4030_0000 | Ox5FFF_FFFF | 1021MB | EXPMST0        | Reserved                                              |

| 22        | 0x6000_0000 | 0x6000_FFFF | 64KB   | EXPMST11       | Volatile Memory implemented as BRAM                   |

| 23        | 0x6001_0000 | 0x6001_FFFF | 64KB   | EXPMST11       | SE R/W Xilinx QSPI controller (PG153 v3.2)            |

| 24        | 0x6002_0000 | 0x7FFF_FFFF | 511MB  | EXPMST1        | Reserved                                              |

| 25        | 0x8000_0000 | OxFFFF_FFFF | 2GB    | OCVM           | Off Chip Volatile Memory implemented as off chip DDR4 |

|           |             |             |        |                |                                                       |

#### Table 2-4 : SSE-710 Host System Memory Map

<sup>1</sup> – intention is to be accessible only by SE (depends on the software implementation).

## 2.5.2 SSE-710 AON Expansion Memory Map

The AON expansion interface resides with the SSE-710 Host Peripheral region in the SSE-710 Host System. The implementation supports an RTC within this region. The mapping details can be found below.

| ROW | Addre       | ess         | Size Region<br>Name |                   | Description                                     |  |

|-----|-------------|-------------|---------------------|-------------------|-------------------------------------------------|--|

| ID  | D From To   |             | 5120                | <sup>e</sup> Name | Description                                     |  |

| 1   | 0x1A60_0000 | 0x1A60_0FFF | 4KB                 | RTC               | PrimeCell RTC (PL031)                           |  |

| 2   | 0x1A60_1000 | 0x1A6F_FFFF | 1020KB              | RESERVED          | Default subordinate generates an error response |  |

#### Table 2-5: SSE-710 AON Expansion Memory Map

#### 2.5.3 SSE-710 Secure Enclave Memory Map

See the Arm® Corstone SSE-710 Subsystem TRM for memory map details.

## 2.5.4 EXTSYS0 Memory Map

The following table shows the EXTSYSO memory map.

| ROW | N Address   |             | Sino  | Design Name    | Description                                     |

|-----|-------------|-------------|-------|----------------|-------------------------------------------------|

| ID  | From        | То          | Size  | Region Name    | Description                                     |

| 1   | 0x0000_0000 | 0x0003_FFFF | 256KB | TARGFLASHO     | Code Memory                                     |

| 2   | 0x0004_0000 | Ox1FFF_FFFF | 512MB | TARGEXP1       | EXTSYSO MEM Interface of the Harness            |

| 3   | 0x2000_0000 | 0x2000_7FFF | 32KB  | TARGSRAMO      | SRAMO                                           |

| 4   | 0x2000_8000 | 0x3FFF_FFFF | 512MB | TARGEXP1       | EXTSYSO MEM Interface of the Harness            |

| 5   | 0x4000_0000 | 0x4000_0FFF | 4KB   | TARGAPBO       | Timer0                                          |

| 6   | 0x4000_1000 | 0x4000_1FFF | 4KB   | TARGAPB1       | Timer1                                          |

| 7   | 0x4000_2000 | 0x4000_2FFF | 4KB   | TARGAPB2       | EXTSYSO UART                                    |

| 8   | 0x4000_3000 | 0x4000_3FFF | 4KB   | TARGAPB3       | RESERVED (RAZ/WI)                               |

| 9   | 0x4000_4000 | 0x4000_7FFF | 16KB  | TARGAPB<4-7>   | RESERVED (RAZ/WI)                               |

| 10  | 0x4000_8000 | 0x4000_8FFF | 4KB   | TARGAPB8       | Watchdog                                        |

| 11  | 0x4000_9000 | 0x4000_9FFF | 4KB   | TARGAPB9       | RESERVED (RAZ/WI)                               |

| 12  | 0x4000_A000 | 0x4000_AFFF | 4KB   | TARGAPB10      | RESERVED (RAZ/WI)                               |

| 13  | 0x4000_B000 | 0x4000_BFFF | 4KB   | TARGAPB11      | System register                                 |

| 14  | 0x4000_C000 | 0x4000_FFFF | 16KB  | TARGAPB<12-15> | RESERVED (RAZ/WI)                               |

| 15  | 0x4001_0000 | 0x400F_FFFF | 960KB | TARGEXP1       | EXTSYS0 MEM Interface of the Harness            |

| 16  | 0x4010_0000 | 0x4010_0FFF | 4KB   | TARGEXP1       | HES MHUO Receiver – EXTSYSO MHU<br>interface *  |

| 17  | 0x4010_1000 | 0x4010_FFFF | 60KB  | TARGEXP1       | RESERVED EXTSYS0 MHU interface                  |

| 18  | 0x4011_0000 | 0x4011_0FFF | 4KB   | TARGEXP1       | ESH MHUO Sender – EXTSYSO MHU<br>Interface *    |

| 19  | 0x4011_1000 | 0x4011_FFFF | 60KB  | TARGEXP1       | RESERVED EXTSYS0 MHU interface                  |

| 20  | 0x4012_0000 | 0x4012_0FFF | 4KB   | TARGEXP1       | HES MHU1 Receiver – EXTSYSO MHU<br>interface *  |

| 21  | 0x4012_1000 | 0x4012_FFFF | 60KB  | TARGEXP1       | RESERVED EXTSYS0 MHU interface                  |

| 22  | 0x4013_0000 | 0x4013_0FFF | 4KB   | TARGEXP1       | ESH MHU1 Sender – EXTSYS0 MHU<br>interface *    |

| 23  | 0x4013_1000 | 0x4013_FFFF | 60KB  | TARGEXP1       | RESERVED EXTSYS0 MHU interface                  |

| 24  | 0x4014_0000 | 0x4014_0FFF | 4KB   | TARGEXP1       | SEES MHUO Receiver – EXTSYSO MHU<br>interface * |

| 25  | 0x4014_1000 | 0x4014_FFFF | 60KB  | TARGEXP1       | RESERVED EXTSYS0 MHU interface                  |

Copyright  $^{\odot}$  2021-2023 Arm Limited (or its subsidiaries). All rights reserved. Non-Confidential

| ROW Address |             | ess         |         |              |                                                  |

|-------------|-------------|-------------|---------|--------------|--------------------------------------------------|

| ID          | From        | То          | Size    | Region Name  | Description                                      |

| 26          | 0x4015_0000 | 0x4015_0FFF | 4KB     | TARGEXP1     | ESSE MHUO Sender – EXTSYSO MHU<br>interface *    |

| 27          | 0x4015_1000 | 0x4015_FFFF | 60KB    | TARGEXP1     | RESERVED EXTSYS0 MHU interface                   |

| 28          | 0x4016_0000 | 0x4016_0FFF | 4KB     | TARGEXP1     | SEES MHU1 Receiver – EXTSYSO MHU<br>interface *  |

| 29          | 0x4016_1000 | 0x4016_FFFF | 60KB    | TARGEXP1     | RESERVED EXTSYS0 MHU interface                   |

| 30          | 0x4017_0000 | 0x4017_0FFF | 4KB     | TARGEXP1     | ESSE MHU1 Sender – EXTSYSO MHU<br>interface *    |

| 31          | 0x4017_1000 | 0x4017_FFFF | 60KB    | TARGEXP1     | RESERVED EXTSYS0 MHU interface                   |

| 32          | 0x4018_0000 | 0x43FF_FFFF | 64000KB | TARGEXP1     | EXTSYSO MEM Interface of the Harness             |

| 33          | 0x4400_0000 | 0x447F_FFFF | 8MB     | TARGEXP1     | EXTSYSO EXT DBG Interface of the Harness         |

| 34          | 0x4480_0000 | Ox5FFF_FFFF | 440MB   | TARGEXP1     | EXTSYSO MEM Interface of the Harness             |

| 35          | 0x6000_0000 | 0x9FFF_FFFF | 1GB     | TARGEXP1     | EXTSYSO MEM Interface of the Harness             |

| 36          | 0xA000_0000 | 0xA000_FFFF | 64KB    | TARGEXPO     | Default subordinate (Error response)             |

| 37          | 0xA001_0000 | 0xDFFF_FFFF | 1023MB  | TARGEXPO     | EXTSYSO MEM Interface of the Harness             |

| 38          | 0xE000_0000 | 0xE000_0FFF | 4KB     | Internal PPB | ITM                                              |

| 39          | 0xE000_1000 | 0xE000_1FFF | 4KB     | Internal PPB | DWT                                              |

| 40          | 0xE000_2000 | 0xE000_2FFF | 4KB     | Internal PPB | FPB                                              |

| 41          | 0xE000_3000 | 0xE000_DFF  | 44KB    | Internal PPB | RESERVED                                         |

| 42          | 0xE000_E000 | 0xE000_EFFF | 4KB     | Internal PPB | SCS (System Control space (NVI, Systick,<br>MPU) |

| 43          | 0xE000_F000 | 0xE003_FFFF | 196KB   | Internal PPB | RESERVED                                         |

| 44          | 0xE004_0000 | 0xE004_0FFF | 4KB     | External PPB | RESERVED (Returns subordinate error)             |

| 45          | 0xE004_1000 | 0xE004_1FFF | 4KB     | External PPB | ETM                                              |

| 46          | 0xE004_2000 | 0xE004_2FFF | 4KB     | External PPB | CTI                                              |

| 47          | 0xE004_4000 | OxEOOF_EFFF | 762KB   | External PPB | RESERVED (Returns subordinate error)             |

| 48          | 0xE00F_F000 | OxEOOF_FFFF | 4KB     | Internal PPB | ROM table                                        |

#### Table 2-6 : EXTSYS0 Memory Map

\* - The letters before the MHU describe the source and the transmitter followed by the receiver of that MHU, where H = Host, ES = External System, SE = Secure Enclave.

## 2.5.5 Memory Sizes – Summary

| Entity            | Memory Type                | Location  | Memory Size |

|-------------------|----------------------------|-----------|-------------|

| Host System       | Shared RAM (CVM)           | FPGA BRAM | 4MB         |

|                   | Host Expansion Manager 1   | FPGA BRAM | 64KB        |

|                   | QSPI Flash (XNVM)          | External  | 32MB        |

|                   | DDR (OCVM)                 | External  | 2GB         |

| Secure Enclave    | ROM                        | FPGA BRAM | 64KB        |

|                   | RAM                        | FPGA BRAM | 512KB       |

|                   | QSPI Flash (Exp Manager 1) | External  | 8MB         |

| External System O | Code SRAM                  | FPGA BRAM | 256KB       |

|                   | RAM                        | FPGA BRAM | 32KB        |

| OTP               | RAM                        | FPGA BRAM | 8KB         |

Table 2-7 : Memory Sizes - Summary

# **3 Programmers Model**

# 3.1 Xilinx Internal BRAM

BRAM is used to implement:

- The Secure Enclave ROM (64KB), which is implemented as Dual Port RAM. This is the primary boot memory. See section 2.5 for mapping details.

- The Secure Enclave RAM (512KB). See section 2.5 for mapping details.

- The CVM RAM (4MB). See section 2.5 for mapping details.

- The OTP (8KB). See section 2.5 for mapping details.

- The EXTSYSO Code SRAM (256KB). See section 2.5.4 for mapping details.

- The EXTSYSO SRAM (32KB).

- Host Cortex-A35 CPU L1 and L2 cache

- Firewall RAM

- 1KB RAM in the EXPMST1 address space. See section **2.5** for mapping details.

# 3.2 XNVM QSPI Flash

The XNVM 32MB memory is implemented using an external QSPI flash PMOD module, which is accessed over a QSPI interface (implemented using a Xilinx QSPI controller). See section **2.5** for mapping details.

# 3.3 SE QSPI Flash

The SE 8MB memory is implemented using on-board Microchip memory, which is accessed over a QSPI interface (implemented using a Xilinx QSPI controller). See section **2.5** for mapping details.

# 3.4 OCVM DDR4

The MPS3 board provides a 4GB DDR module. The SMM in this implementation supports 2GB of this external 4GB DDR module.

## 3.5 UART Support

The PrimeCell PL011 UART is implemented within the SSE-710 Subsystem and EXTSYSO. The UARTs are physically accessible through the USB interface on the MPS3 board. See the memory map in section 2.5 for information on the USB interface.

Copyright <sup>©</sup> 2021-2023 Arm Limited (or its subsidiaries). All rights reserved. Non-Confidential Arm® Corstone™-1000 for MPS3 Application Note AN550

UART Clock input to every UART is connected to REFCLK24MHZ (24MHz).

This implementation provides the UARTs described in chapter 2.4.6.

# 3.6 SSE-710 Implementation

## 3.6.1 SSE-710 Power Control

Power control is not supported as it is a limitation of the FPGA implementation.

## 3.6.2 SSE-710 Host AON Expansion RTC

The PrimeCell RTC (PL031) is a real time clock module. The RTC module uses the S32KCLK for counting. The reset of this slow part is done by the AONTOPWARMRESETn signal also, but it is synchronized by the S32KCLK clock to de-assert it synchronously. S32KCLK must run to allow the RTC module to count. The interrupt signal of the RTC is connected to the EXPSHDINT interface of the SSE-710 subsystem.

Please refer to the Arm® Corstone SSE-710 Subsystem Technical Reference Manual for further details on S32KCLK, AONTOPWARMRESETn and EXPSHDINT.

### 3.6.3 SSE-710 Expansion Shared Interrupt Map

The following table shows the interrupt connections of the **EXPSHDINT** interface of the SSE-710. These interrupts can be exposed to the Host CPU, the Secure Enclave, or EXTSYSO by the Interrupt Router inside SSE-710.

| IRQ line         | Level/Edge | Connection                                       |

|------------------|------------|--------------------------------------------------|

| EXPSHDINT[0]     | Level      | EXTSYSO PPU interrupt                            |

| EXPSHDINT[1]     | Level      | RESERVED                                         |

| EXPSHDINT[2]     | Level      | EXTSYSO Watchdog or Lockup reset request         |

| EXPSHDINT[3]     | Level      | RESERVED                                         |

| EXPSHDINT[4]     | Level      | RESERVED                                         |

| EXPSHDINT[5]     | Level      | RTC interrupt                                    |

| EXPSHDINT[28:6]  | -          | RESERVED                                         |

| EXPSHDINT[29]    | Level      | MPS3 USB peripheral interrupt                    |

| EXPSHDINT[30]    | Level      | MPS3 I <sup>2</sup> S Audio peripheral interrupt |

| EXPSHDINT[31]    | Level      | MPS3 Ethernet peripheral interrupt               |

| EXPSHDINT[63:32] | Level      | RESERVED                                         |

Table 3-1: SSE-710 Expansion Shared Interrupt Map

# 3.7 **EXTSYS0**

## 3.7.1 System Control Registers

EXTSYSO contains a set of 32-bit system control registers. These registers are mapped into the EXTSYSO memory map base address. The following table describes how the registers are decoded:

| Name        | Address<br>Offset | Туре | Reset Source   | Reset Value | Description                                                                                                                                                                                                                                                                  |

|-------------|-------------------|------|----------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESETINFO   | 0x00              | RW   | EXTSYSPORESETn | 0x00        | Reset syndrome register. This register logs the reset sources in the system.                                                                                                                                                                                                 |

|             |                   |      |                |             | A write to a bit of this register of:                                                                                                                                                                                                                                        |

|             |                   |      |                |             | ObO clears a logged reset syndrome<br>Ob1 is ignored                                                                                                                                                                                                                         |

|             |                   |      |                |             | Decoding:<br>[0]: Power-on reset<br>[1]: nSRST<br>[2]: RESERVED<br>[3]: HOST System reset request<br>[4]: EXTSYS reset request<br>[5]: EXTSYS internal system reset<br>request<br>[31:6]: RESERVED                                                                           |

| POWERDOWNEN | 0x04              | RW   | EXTSYSPORESETn | 0x0         | 1-bit register. When the bit is set, if<br>all other requirements are met, the<br>power down of the EXTSYS domain<br>is enabled.<br>[31:1]: RESERVED                                                                                                                         |

| CLK_CTL     | 0x08              | RW   | EXTSYSPORESETn | 0x0000_3E1F | Clock control register:<br>[0]: Force the EXTSYSAONCLK to<br>run<br>[8:1]: AON Clock Controller entry<br>delay value<br>[9]: Force the EXTSYSHCLK and<br>EXTSYSDCLK to run<br>[17:10]: CORE HCLK and CORE<br>DCLK Clock Controller entry delay<br>value<br>[31:18]: RESERVED |

#### Table 3-2: EXTSYS0 System Control Registers

Other addresses in this interface behave as RAZ/WI. Reserved registers bits behave as RAZ/WI. The System Register module never returns a subordinate error from its APB interface and it never inserts a wait state.

## 3.7.2 EXTSYS0 Interrupt Connectivity

This following table describes the interrupts that are handled by the Cortex-M3 core in EXTSYSO.

| No.   | Level/Edge | Priority     | Description                                                                          |

|-------|------------|--------------|--------------------------------------------------------------------------------------|

| 16    | Level      | Programmable | Timer O interrupt                                                                    |

| 17    | Level      | Programmable | Timer 1 interrupt                                                                    |

| 18    | Level      | Programmable | HES MHUO Combined interrupt                                                          |

| 19    | Level      | Programmable | ESH MHUO Combined interrupt                                                          |

| 20    | Level      | Programmable | HES MHU1 Combined interrupt                                                          |

| 21    | Level      | Programmable | ESH MHU1 Combined interrupt                                                          |

| 22    | Level      | Programmable | SEES MHU0 Combined interrupt                                                         |

| 23    | Level      | Programmable | ESSE MHU0 Combined interrupt                                                         |

| 24    | Level      | Programmable | SEES MHU1 Combined interrupt                                                         |

| 25    | Level      | Programmable | ESSE MHU1 Combined interrupt                                                         |

| 26    | Edge       | Programmable | HXB-Bridge error interrupt                                                           |

| 27    | Level      | Programmable | EXTSYSO UART                                                                         |

| 28    | -          | -            | Reserved                                                                             |

| 29-60 | -          | Programmable | EXTSYSO SHDINT[31:0] from the External System Harness.                               |

|       |            |              | Note                                                                                 |

|       |            |              | EXTSYSO SHDINT[0] is routed to interrupt number 29                                   |

|       |            |              | EXTSYSO SHDINT[31] is routed to interrupt number 60                                  |

|       |            |              | See the Arm® Corstone SSE-710 Subsystem Technical Reference Manual for more details. |

| 61    | Level      | Programmable | EXTSYS0 SHDINT[32] - EXTSYS0 PPU interrupt                                           |

| 62    | -          | -            | Reserved                                                                             |

| 63    | Level      | Programmable | EXTSYSO SHDINT[34] – EXTSYS 0 Watchdog or<br>Lockup reset request                    |

| 64    | -          | -            | Reserved                                                                             |

| 65    | -          | -            | Reserved                                                                             |

| 66    | Level      | Programmable | EXTSYS0 SHDINT[37] – RTC interrupt                                                   |

| 67    | -          | -            | Reserved                                                                             |

#### Table 3-3 : EXTSYS0 System Interrupt Connectivity

Copyright <sup>©</sup> 2021-2023 Arm Limited (or its subsidiaries). All rights reserved. Non-Confidential

# 3.8 SBCon I<sup>2</sup>C

| The following table shows the | e register map | o for the two-wir | e SBCon. |  |

|-------------------------------|----------------|-------------------|----------|--|

|                               |                |                   |          |  |

| Address    | Name        | Access | Description                                                    |

|------------|-------------|--------|----------------------------------------------------------------|

| 0x40030000 | SB_CONTROL  | Read   | Read serial control bits:<br>Bit [0] is SCL<br>Bit [1] is SDA  |

| 0x40030000 | SB_CONTROLS | Write  | Set serial control bits:<br>Bit [0] is SCL<br>Bit [1] is SDA   |

| 0x40030004 | SB_CONTROLC | Write  | Clear serial control bits:<br>Bit [0] is SCL<br>Bit [1] is SDA |

#### Table 3-4 SBCon Register Map

# 3.9 Audio I<sup>2</sup>S

The I<sup>2</sup>S interface supports transfer of digital audio to and from the Audio CODEC.

The following table shows the register memory map for I<sup>2</sup>S Audio registers.

| Address    | Name    | Description      |                                            |

|------------|---------|------------------|--------------------------------------------|

| 0x40020000 | CONTROL | Control Register |                                            |

|            |         | Bits[31:18]      | Reserved                                   |

|            |         | Bit[17]          | Audio codec reset control (output pin)     |

|            |         | Bit[16]          | FIFO reset                                 |

|            |         | Bit[15]          | Reserved                                   |

|            |         | Bits[14:12]      | Rx Buffer IRQ Water Level - Default 2      |

|            |         | (IRQ triggers wh | en less than two-word space is available). |

|            |         | Bit[11]          | Reserved                                   |

|            |         | Bits[10:8]       | TX Buffer IRQ Water Level - Default 2      |

|            |         | (IRQ triggers wh | en more than two-word space is available). |

|            |         | Bits[7:4] Reserv | ed                                         |

|            |         | Bit[3]           | Rx Interrupt Enable                        |

|            |         | Bit[2]           | Rx Enable                                  |

| Address     | Name     | Description                                                      |                                                    |

|-------------|----------|------------------------------------------------------------------|----------------------------------------------------|

|             |          | Bit[1]                                                           | Tx Interrupt Enable                                |

|             |          | Bit[O]                                                           | Tx Enable                                          |

| 0x40020004  | STATUS   | Status Register                                                  |                                                    |

|             |          | Bits[31:6]                                                       | Reserved                                           |

|             |          | Bit[5]                                                           | Rx Buffer Full                                     |

|             |          | Bit[4]                                                           | Rx Buffer Empty                                    |

|             |          | Bit[3]                                                           | Tx Buffer Full                                     |

|             |          | Bit[2]                                                           | Tx Buffer Empty                                    |

|             |          | Bit[1]                                                           | Rx Buffer Alert (Depends on Water level)           |

|             |          | Bit[0]                                                           | Tx Buffer Alert (Depends on Water level)           |

| 0x40020008  | ERROR    | Error Status Reg                                                 | zister                                             |

|             |          | Bits[31:2]                                                       | Reserved                                           |

|             |          | Bit[1]                                                           | Rx overrun. Set this bit to clear.                 |

|             |          | Bit[0]                                                           | Tx overrun or underrun. Set this bit to clear.     |

| 0x4002000C  | DIVIDE   | Clock Divide Ratio Register (for left or right clock)            |                                                    |

|             |          | Bits[31:10]                                                      | Reserved                                           |

|             |          | Bits[9:0] LRDIV<br>0x80.                                         | (Left/Right). The default value is                 |

|             |          |                                                                  | 12.288MHz / 48kHz / 2*(L+R) = 128.                 |

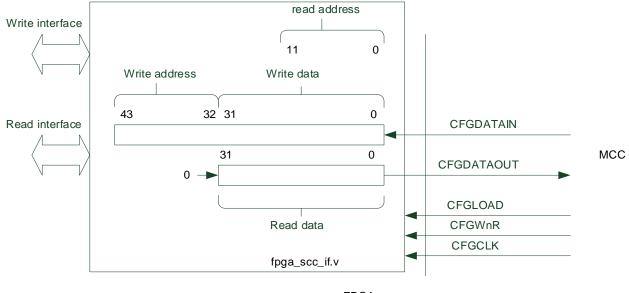

| 0x40020010  | TXBUF    | Transmit Buffer                                                  | FIFO Data Register. This is a write-only register. |