# Arm<sup>®</sup> Functional Fixed Hardware Specification Platform Design Document

**Non-Confidential**

Version 1.2

# **Contents**

| RELE | EASE               | INFORM <i>A</i>         | ATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3                    |

|------|--------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| ARM  | NON-               | CONFIDE                 | ENTIAL DOCUMENT LICENCE ("LICENCE")                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4                    |

| 1    | <b>ABO</b> 1.1 1.2 | Referen                 | DOCUMENT ces nd abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6                    |

|      | 1.3                | Feedbac<br>1.3.1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6<br>7<br>7          |

|      | 1.4                | Progress                | sive terminology commitment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7                    |

| 2    | INTR               | ODUCTIO                 | ON CONTRACTOR OF THE PROPERTY | 8                    |

| 3    |                    | CASES                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9                    |

|      | 3.1                | 3.1.1<br>3.1.2<br>3.1.3 | agement and Low Power Idle states FFH Usage in LPI state entry methods FFH Usage in LPI residency and usage counter registers Save and restore flags                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9<br>9<br>10<br>10   |

|      | 3.2                | 3.2.1                   | ance management and Collaborative Processor Performance Control FFH Usage in _CPC object to monitor processor performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12<br>12             |

|      | 3.3                | Operation 3.3.1         | on Regions FFH usage in Operation Region Space for Secure Monitor Calls (SVC) and Hypervisor Calls (HVC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13<br>13             |

| APPI | ENDIX              |                         | PSCI STATE COMPOSITION FROM LPI STATES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15                   |

|      | A.1<br>A.2         |                         | StateID power_state parameter format: PSCI0.2 or above d StateID power_state parameter format: PSCI 1.0 or above                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16<br>19             |

| APPI | ENDIX              | B<br>TEMS               | PROCESSOR PERFORMANCE MONITORING AND CONTROL IN HETEROGENOUS 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | i                    |

|      | B.1<br>B.2         | Monitorii               | ng Processor Performance through CPPC ng Processor Performance through CPPC Performance Capabilities/Thresholds Performance Controls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 22<br>24<br>24<br>24 |

| APPI | ENDIX<br>C.1       |                         | FFH OPERATION REGIONS of FFH Operation Regions which trigger SMC or HVC calls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>27</b><br>27      |

Copyright © 2015 - 2022 Arm Limited. All rights reserved.

# **Release Information**

The Change History table lists the changes made to this document.

**Table 0-1 Change history**

| Date          | Issue Confidentiality          |                  | Change                                                                                                |  |

|---------------|--------------------------------|------------------|-------------------------------------------------------------------------------------------------------|--|

| 17 April 2015 | Α                              | Non-Confidential | First release.                                                                                        |  |

| 17 June 2020  | В                              | Non-Confidential | Support for Processor Performance Monitoring through CPPC.                                            |  |

| 27 Sep 2022   | 27 Sep 2022 C Non-Confidential |                  | <ul><li>Support for Operation Regions.</li><li>Fix typographical mistake in Table 8 header.</li></ul> |  |

# Arm Non-Confidential Document Licence ("Licence")

This Licence is a legal agreement between you and Arm Limited ("Arm") for the use of Arm's intellectual property (including, without limitation, any copyright) embodied in the document accompanying this Licence ("Document"). Arm licenses its intellectual property in the Document to you on condition that you agree to the terms of this Licence. By using or copying the Document you indicate that you agree to be bound by the terms of this Licence.

"Subsidiary" means any company the majority of whose voting shares is now or hereafter owner or controlled, directly or indirectly, by you. A company shall be a Subsidiary only for the period during which such control exists.

This Document is **NON-CONFIDENTIAL** and any use by you and your Subsidiaries ("Licensee") is subject to the terms of this Licence between you and Arm.

Subject to the terms and conditions of this Licence, Arm hereby grants to Licensee under the intellectual property in the Document owned or controlled by Arm, a non-exclusive, non-transferable, non-sub-licensable, royalty-free, worldwide licence to:

- (i) use and copy the Document for the purpose of designing and having designed products that comply with the Document;

- (ii) manufacture and have manufactured products which have been created under the licence granted in (i) above; and

- (iii) sell, supply and distribute products which have been created under the licence granted in (i) above.

Licensee hereby agrees that the licences granted above shall not extend to any portion or function of a product that is not itself compliant with part of the Document.

Except as expressly licensed above, Licensee acquires no right, title or interest in any Arm technology or any intellectual property embodied therein.

THE DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. Arm may make changes to the Document at any time and without notice. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

NOTWITHSTANING ANYTHING TO THE CONTRARY CONTAINED IN THIS LICENCE, TO THE FULLEST EXTENT PETMITTED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, IN CONTRACT, TORT OR OTHERWISE, IN CONNECTION WITH THE SUBJECT MATTER OF THIS LICENCE (INCLUDING WITHOUT LIMITATION) (I) LICENSEE'S USE OF THE DOCUMENT; AND (II) THE IMPLEMENTATION OF THE DOCUMENT IN ANY PRODUCT CREATED BY LICENSEE UNDER THIS LICENCE). THE EXISTENCE OF MORE THAN ONE CLAIM OR SUIT WILL NOT ENLARGE OR EXTEND THE LIMIT. LICENSEE RELEASES ARM FROM ALL OBLIGATIONS, LIABILITY, CLAIMS OR DEMANDS IN EXCESS OF THIS LIMITATION.

This Licence shall remain in force until terminated by Licensee or by Arm. Without prejudice to any of its other rights, if Licensee is in breach of any of the terms and conditions of this Licence then Arm may terminate this Licence immediately upon giving written notice to Licensee. Licensee may terminate this Licence at any time. Upon termination of this Licence by Licensee or by Arm, Licensee shall stop using the Document and destroy all copies of the Document in its possession. Upon termination of this Licence, all terms shall survive except for the licence grants.

Any breach of this Licence by a Subsidiary shall entitle Arm to terminate this Licence as if you were the party in breach. Any termination of this Licence shall be effective in respect of all Subsidiaries. Any rights granted to any Subsidiary hereunder shall automatically terminate upon such Subsidiary ceasing to be a Subsidiary.

The Document consists solely of commercial items. Licensee shall be responsible for ensuring that any use, duplication or disclosure of the Document complies fully with any relevant export laws and regulations to assure that the Document or any portion thereof is not exported, directly or indirectly, in violation of such export laws.

This Licence may be translated into other languages for convenience, and Licensee agrees that if there is any conflict between the English version of this Licence and any translation, the terms of the English version of this Licence shall prevail.

The Arm corporate logo and words marked with ® or ™ are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. No licence, express, implied or otherwise, is granted to Licensee under this Licence, to use the Arm trade marks in connection with the Document or any products based thereon. Visit Arm's website at <a href="https://www.arm.com/company/policies/trademarks">https://www.arm.com/company/policies/trademarks</a> for more information about Arm's trademarks.

The validity, construction and performance of this Licence shall be governed by English Law.

Copyright © 2017 - 2022 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England. 110 Fulbourn Road, Cambridge, England CB1 9NJ.

Arm document reference: LES-PRE-21585 version 4.0

# 1 About this Document

This document provides the specification for Arm reserved uses of Functional Fixed Hardware for ACPI-based systems.

### 1.1 References

This document refers to the following documents.

| Reference | <b>Document Number</b> | Title                                                                                                                                                                                                      |

|-----------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [ACPI6.0] | ACPI 6.0               | Advanced Configuration and Power Interface Specification version 6.0                                                                                                                                       |

| [ACPI6.3] | ACPI 6.3               | Advanced Configuration and Power Interface Specification version 6.3                                                                                                                                       |

| [ACPI6.4] | ACPI 6.4               | Advanced Configuration and Power Interface Specification version 6.4.                                                                                                                                      |

| [ACPI6.5] | ACPI 6.5               | Advanced Configuration and Power Interface Specification version 6.5.                                                                                                                                      |

| [Arm ARM] | DDI0487                | Arm Architecture Reference Manual ARMv8, for ARMv8-A architecture profile. See <a href="https://developer.arm.com/documentation/ddi0487/latest">https://developer.arm.com/documentation/ddi0487/latest</a> |

| [FF-A]    | DEN0077                | Arm Firmware Framework for Arm A-profile. See <a href="https://developer.arm.com/documentation/den0077/latest/">https://developer.arm.com/documentation/den0077/latest/</a>                                |

| [PSCI]    | DEN0028                | Power State Coordination Interface. See <a href="https://developer.arm.com/documentation/den0022/latest/">https://developer.arm.com/documentation/den0022/latest/</a>                                      |

| [SMCCC]   | DEN0028                | Arm SMC Calling Convention. See <a href="https://developer.arm.com/documentation/den0028/latest/">https://developer.arm.com/documentation/den0028/latest/</a>                                              |

### 1.2 Terms and abbreviations

This document uses the following terms and abbreviations.

| Term | Meaning                                                                                                                 |

|------|-------------------------------------------------------------------------------------------------------------------------|

| AMU  | Activity Monitor Unit                                                                                                   |

| CPC  | Continuous Performance Control                                                                                          |

| CPPC | Collaborative Processor Performance Control                                                                             |

| FFH  | Functional Fixed Hardware. This refers to <i>software</i> (SW) operations that replace a <i>hardware</i> (HW) function. |

| LPI  | Low Power Idle                                                                                                          |

| MRS  | Move to Arm register from System Register Instruction                                                                   |

| OSPM | Operating System-directed configuration and Power Management                                                            |

### 1.3 Feedback

Arm welcomes feedback on its documentation.

### 1.3.1 Feedback on this manual

If you have comments on the content of this manual, send an e-mail to errata@arm.com. Give:

- The title.

- The document and version number, DEN0048C.

- The page numbers to which your comments apply.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

# 1.4 Progressive terminology commitment

Arm values inclusive communities. Arm recognizes that we and our industry have used terms that can be offensive. Arm strives to lead the industry and create change.

We believe that this document contains no offensive terms. If you find offensive terms in this document, please contact terms@arm.com.

# 2 Introduction

This document provides a specification for *Functional Fixed Hardware* (FFH) in Arm-based systems that use the *Advanced Configuration and Power Interface* (ACPI) specification.

At the time of writing, the three use cases are:

- Idle Management and Low Power Idle (LPI) states. See [ACPI6.0].

- Performance Management and Collaborative Processor Performance Control (CPPC). See Section 8.4.7 of [ACPI 6.3]

- Operation Regions. See [ACPI6.5].

# 3 Use Cases

### 3.1 Idle management and Low Power Idle states

ACPI 6.0 [ACPI6.0] introduces *Low Power Idle* (LPI) states, which allow an operating system to manage the power states of the processor power domain hierarchy. This section describes how FFH is used in Arm-based systems to allow the operating system to discover:

- The entry method into a low power state.

- How to collect power state residency, and usage count statistics.

This section also defines the flags used in an LPI state object to describe the architectural context that is lost when the LPI state is entered.

### 3.1.1 FFH Usage in LPI state entry methods

ACPI ASL uses the Register keyword to define HW register addresses, or SW functions, when using FFH. The Register keyword has the following format:

**Register** (AddressSpaceKeyword, RegisterBitWidth, RegisterBitOffset, RegisterAddress, AccessSize, DescriptorName)

For further information, see section 19.6.108 of [ACPI6.0]. Registers are used to specify one of the following two entry methods into an LPI state:

- A Wait For Interrupt (WFI) instruction.

- A PSCI CPU\_SUSPEND call. In this case, the entry method provides a way of describing the power state parameter of the CPU SUSPEND call as specified by [PSCI].

When using FFH to describe LPI entry methods, the register field entries must be set as follows:

- AddressSpaceKeyword must be set to 0x7f. This denotes usage of the FFH address space.

- RegisterBitWidth must be set to 32.

- RegisterBitOffset must be set to 0.

- AccessSize must be set to 3 (Dword).

- WFIs states must be represented in the \_LPI objects of processors. In the WFI case, the RegisterAddress

in the entry method of the LPI state has the following format:

| Bits[63:32] | Bits[31:0] |

|-------------|------------|

| 0x0000000   | 0xFFFFFFF  |

• A PSCI power state parameter is represented in the RegisterAddress field as follows:

| Bits[63:32] | Bits[31:0]                                                                                   |

|-------------|----------------------------------------------------------------------------------------------|

| 0.00000000  | PSCI power_state parameter for CPU_SUSPEND call. See section 5.4 of [PSCI] for more details. |

- For LPI entry methods, all other possible encodings of RegisterAddress, RegisterBitWidth,

RegisterBitOffset, and AccessSize where 0x7f is used for the AddressSpaceKeyword are reserved for

future use.

- DescriptorName is optional. See section 19.6.108 of [ACPI6.0] for further details.

When the OS is working in OS Initiated mode, as defined by both [PSCI] and [ACPI6.0], the OS must regard cores using the WFI state as being in a running state, for the purposes of last man tracking. To enter OS Initiated mode, the OS must use the PSCI SET SUSPEND MODE call described in sections 5.1.19 and 5.20 of [PSCI].

Appendix A provides a description and examples of how PSCI power states are composed from LPI entry methods and LPI LevelID. The examples cover platform coordinated and OS Initiated systems.

### 3.1.2 FFH Usage in LPI residency and usage counter registers

PSCI1.0 introduces the PSCI\_STAT\_RESIDENCY and PSCI\_STAT\_COUNT functions. For systems that implement these functions, ASL Registers in the FFH space can be used for the residency and usage counter register fields of LPI states. This allows matching those registers to a PSCI call. In this case, the format of the Register provided is as follows:

- AddressSpaceKeyword must be 0x7f. This denotes usage of the FFH address space.

- RegisterBitWidth must be 32.

- RegisterBitOffset must be 0.

- AccessSize must be 3 (Dword).

- For both the residency and usage counter registers, the *RegisterAddress* field must have the following encoding:

| Bits[63:32] | Bits[31:0]                                            |  |

|-------------|-------------------------------------------------------|--|

| 0x0000000   | PSCI power_state parameter for PSCI_STAT_* functions. |  |

| 0,0000000   | See section 5.21.1 of [PSCI].                         |  |

- For residency and usage counter registers of LPI entries, all other possible encodings of *RegisterAddress*, *RegisterBitWidth*, *RegisterBitOffset*, and *AccessSize* where 0x7f is used for the *AddressSpaceKeyword* are reserved for future use.

- DescriptorName is optional and can be omitted. See section 19.6.108 of [ACPI6.0] for further details.

In the case of the residency counter register, this encoding instructs the processor driver of the OS to issue a PSCI\_STAT\_RESIDENCY call. The residency counter frequency of the LPI must be set to 1000000, to indicate that the count is in microseconds.

In the case of the usage counter register, this encoding instructs the processor driver of the OS to issue a PSCI STAT COUNT call.

**Note**: The OSPM must use the PSCI\_FEATURES API to ensure that PSCI\_STAT\_RESIDENCY and PSCI\_STAT\_COUNT are provided by the PSCI implementation. See [PSCI] for more details.

### 3.1.3 Save and restore flags

LPI states provide an architectural context loss flags field that can be used to describe the context that might be lost when an LPI state is entered. For Arm-based systems, the flags have the following format:

**Table 2 Arm Architecture context loss flags**

| Flag              | Bit<br>offset | Bit<br>length | Description                                                                                                      |  |

|-------------------|---------------|---------------|------------------------------------------------------------------------------------------------------------------|--|

| Core context Lost | 0x0           | 0x1           | All core context is lost. This includes:  • General purpose registers.                                           |  |

|                   |               |               | <ul><li>Floating point and SIMD registers.</li><li>System registers, include the System register based</li></ul> |  |

|                    |     |      | generic timer for the core.                                  |  |

|--------------------|-----|------|--------------------------------------------------------------|--|

|                    |     |      | <ul> <li>Debug register in the core power domain.</li> </ul> |  |

|                    |     |      | <ul> <li>PMU registers in the core power domain.</li> </ul>  |  |

|                    |     |      | <ul> <li>Trace register in the core power domain.</li> </ul> |  |

| Trace context loss | 0x1 | 0x1  | Trace registers outside of the core power domain are lost.   |  |

| GICR               | 0x2 | 0x1  | GIC Redistributor logic.                                     |  |

| GICD 0x3 0x1       |     | 0x1  | GIC Distributor logic.                                       |  |

| Reserved 0x4 0x    |     | 0x1c | Reserved must be zero.                                       |  |

# 3.2 Performance management and Collaborative Processor Performance Control

ACPI uses collaborative processor performance control (CPPC) to define an abstracted and flexible mechanism for Operating System-directed configuration and Power Management (OSPM) to collaborate with an entity in the platform to manage the performance of a logical processor. In this scheme, the platform entity is responsible for creating and maintaining a performance definition that backs a continuous, abstract, unit-less performance scale. During runtime, OSPM requests desired performance on this abstract scale and the platform entity is responsible for translating the OSPM performance requests into actual hardware performance states. The control mechanisms are abstracted by the Continuous Performance Control (\_CPC) object method, which describes how to control and monitor processor performance in a generic manner.

This section describes how FFH is used in Arm-based systems to monitor the performance of a logical processor using the Activity Monitor Unit (AMU).

### 3.2.1 FFH Usage in \_CPC object to monitor processor performance

ACPI ASL uses the Register keyword to define HW register addresses, or SW functions, when using FFH. The Register keyword has the following format:

**Register** (AddressSpaceKeyword, RegisterBitWidth, RegisterBitOffset, RegisterAddress, AccessSize, DescriptorName)

For further information, see section 19.6.114 of [ACPI6.3].

Arm cores which implement the Activity Monitor Unit (AMU), can use ASL Registers in the FFH space to specify the following two fields of the CPC package to monitor the performance of a logical processor:

- DeliveredPerformanceCounterRegister

- ReferencePerformanceCounterRegister

ASL registers in the FFH space allow to map:

- a read from the *DeliveredPerformanceCounterRegister* to a corresponding read from the AMU event counter that counts cycles at core frequency (AMEVCNTR0\_EL0[0]).

- a read from the *ReferencePerformanceCounterRegister* to a corresponding read from the AMU event counter that counts cycles at constant frequency (AMEVCNTR0\_EL0[1]).

The AMU Event Counters can be read through a system register read using the MRS instruction. Details on AMU event counters can be found in the [Arm ARM].

When FFH is used to describe the *DeliveredPerformanceCounterRegister* and the *ReferencePerformanceCounterRegister* fields of the \_CPC package, the register field entries must be set as follows:

- AddressSpaceKeyword must be set to 0x7f. This denotes usage of the FFH address space.

- RegisterBitWidth must be set to 64.

- RegisterBitOffset must be set to 0.

- AccessSize must be set to 4 (Qword).

- RegisterAddress must be set to

- o 0x0 for DeliveredPerformanceCounterRegister.

- o 0x1 for ReferencePerformanceCounterRegister.

- DescriptorName is optional. See section 19.6.114 of [ACPI6.3] for further details.

All other possible encodings of *RegisterAddress*, *RegisterBitWidth*, *RegisterBitOffset*, and *AccessSize* where 0x7f is used for the *AddressSpaceKeyword* are reserved for future use.

Appendix B describes the fields of the \_CPC package that should be provided to monitor and control processor performance through CPPC for Arm-based systems.

# 3.3 Operation Regions

ACPI Control Methods can read and write data to locations in address spaces by using the *Field* operator to declare a data element within an entity known as an "Operation Region". Control methods must have exclusive access to any address accessed via fields declared in Operation Regions. FFH can be used to describe an Operation Region space. For more details on Operation Regions, see [ACPI6.5].

This section describes how FFH can be used in Arm-based systems to describe Operation Region spaces and the expected behavior when reading or writing FFH Operation Region fields.

# 3.3.1 FFH usage in Operation Region Space for Secure Monitor Calls (SVC) and Hypervisor Calls (HVC)

FFH Operation Region space can be used to trigger SMC or HVC calls, using the Arm SMC Calling Convention (SMCCC). For more details see [SMCCC]. The choice of conduit (SMC or HVC) is implementation defined and outside the scope of the FFH Operation Region definition.

The syntax of the *OperationRegion* term is described below:

### Where:

- RegionName specifies a name for this Operation Region (for example, "AFFH").

- RegionSpace must be set to 0x7F (FFixedHW). This denotes usage of the FFH address space.

- Offset is used to identify the functionality offered by this FFH address space. It must be set to one of the following values:

- o 0x0 to indicate usage of 32-bit calling convention.

- o *0x1* to indicate usage of 64-bit calling convention.

- All other values are reserved.

- Length specifies the higher of either the number of argument bytes, or the number of result bytes, exchanged over the SMC/HVC call. It is used to interpret the number of registers to use for the call. The registers are listed sequentially, beginning from, and including, the Function Identifier (W0/R0). For example, when Length is 12, registers W0, W1, W2 are used in a SMC32 call.

*Length* must be set to one of the following values, where 'N' denotes the higher of either the number of argument registers or the number of result registers used for the call:

- If Offset is 0 (32 bit calling convention):

- Length must be 4\*N, where  $1 \le N \le 8$ .

- o If *Offset* is 1 (64 bit calling convention):

- Length must be 8\*N, where  $1 \le N \le 18$ .

- All other values of Length are reserved.

FFH operation regions are only accessible via the Field term. The syntax of the Field term is described below:

```

Field (

RegionName, //NameString

AccessType, //AccessTypeKeyword

LockRule, //LockRuleKeyword

UpdateRule //UpdateRuleKeyword

) {FieldUnitList}

```

#### Where:

- RegionName specifies the operation region name previously defined for this FFH Operation Region.

- Accesstype must be set to BufferAcc. This denotes usage of the FFH address space.

- LockRule indicates if access to this Operation Region requires acquisition of the Global Lock for synchronization. This field must be set to NoLock, as required for HW-reduced ACPI platforms.

- *UpdateRule* is not applicable for FFH Operation Regions since each virtual register is accessed in its entirety.

- FieldUnitList comprises of a single element representing the entire Operation Region and the total data

exchanged over the SMC or HVC call. Writing to this field element triggers the call.

This means that each argument register cannot be broken down within the field definition. Access to

argument registers can be done only outside of the field definition. This limitation is imposed both to

simplify the interface and to maintain consistency with the model defined by the Arm SMC Calling

Convention [SMCCC].

An example Operation Region and Field definition is shown below. Here we declare 5 argument registers used for a SMC32 call.

```

OperationRegion(AFFH, FFixedHW, 0, 20)

Field (AFFH, BufferAcc, NoLock, Preserve) { SMCC, 160 }

```

Appendix C describes detailed examples of FFH Operation Region Usage in various calling modes.

#### 3.3.1.1 Restrictions

The usage of FFH Operation Region space for SMC or HVC calls is subject to the following restrictions:

- All calls must be compliant with the Arm SMC Calling Convention.

- Function Identifiers from only the following ranges are allowed:

- SMCCC SiP Service call range.

- SMCCC OEM Service call range.

- FF-A specific Function Identifiers. For more details see [FF-A].

- It is recommended to use Fast Service Calls to simplify the usage model. The call appears to be atomic

from the perspective of the calling PE and returns when the requested operation has completed. If

Yielding Service Calls are used, then it is the responsibility of the caller to safely resume the operation

post pre-emption.

### 3.3.1.2 Error handling

There might be circumstances where the SMC or HVC call cannot be triggered when the Operation Region field element is written to. Examples could be when the Function Identifier (R0/W0) of the SMC call is malformed, or when the restrictions specified in Section 3.3.1.1 are violated. In such cases, an appropriate negative integer return code from the Arm SMC Calling Convention [SMCCC] can be used to specify the error condition in:

- The first 32 bits (W0) of the Operation Region field element when 32-bit calling convention is used.

- The first 64 bits (X0) of the Operation Region field element when 64-bit calling convention is used.

# Appendix A PSCI state composition from LPI states

Section 8.4.4.3.4 of [ACPI6.0] describes how entry methods of local LPI states are composed to produce the final command that is issued to platform firmware to enter a composite power state. This appendix describes how this composition takes place in Arm systems that provide a PSCI implementation. In such systems, the composition results in the value of the power state parameter that is passed to a CPU SUSPEND call to enter the composite

Each LPI state provides an entry method field that is used to determine the PSCI power state parameter to be used with a CPU SUSPEND call. The parameter is composed through the following steps:

- 1. The OS extracts an initial base power state parameter from the lower 32 bits of the RegisterAddress field of the entry method of a processor LPI. For processors, entry methods must be a register that adheres to the definition provided in section see 3.1.1.

- 2. If the composite power state selected by an OS affects power levels above the processor, the OS must walk the LPI states defined in processor containers above the processor. For the LPI states in those containers, the entry method can be an integer or a register:

- a. If the entry method is an integer value, then the base power state parameter obtained in step 1 must have this integer value added to it.

- b. If the entry method defined is a register, then the lower 32 bits of the RegisterAddress field becomes the new base power state parameter

This process is repeated across the LPIs that form the target power state. For OS and PSCI firmware working in platform coordinated mode, the base power state parameter obtained in steps 1 and 2 forms the final power state parameter that is passed to a CPU SUSPEND call.

3. For OS and PSCI firmware working in OS Initiated mode, the OS must indicate the power level in which it observes that the calling processor is the last to go idle. To do so, the OS adds the value of the LevelID field of the \_LPI object [ACPI6.0], defined at the appropriate power level, to the base power state parameter, to form the final power state argument for the CPU SUSPEND call.

The steps are described in the following pseudocode:

```

// Initially LPIx points to a processor-level LPI state

LPIx = ChooseLPIStateForLevel(LevelOf(CurrentProcessor),NULL)

power state = LPIx.EntryMethod.Address

if power state == uint 64(-1) // WFI case

doWFI()

return

for level = Parent(CurrentProcessor) to system

LPIx = ChooseLPIStateForLevel(level,LPIx)

If LocalState == Run

break

EM = LPIx.EntryMethod

if IsInteger (EM)

power_state = power_state+ZeroExtend(IntegerValue(EM))

else

power state = EM.Address

```

```

If IdleMode == OS_Initiated

LastProc = ProcessorContainerWhereCallingIsLastToIdle()

LastProcLPI = LastProc.LPI

power_state = power_state+LastProcLPI.LevelID

doCPU_SUSPEND(power_state)

return

```

The following sections provide examples of how power states can be represented in systems using the original StateID power\_state parameter format, and the extended StateID power\_state parameter format. The first example applies to PSCI 0.2 or PSCI 1.0, while the second applies only to PSCI 1.0.

# A.1 Original StateID power\_state parameter format: PSCI0.2 or above

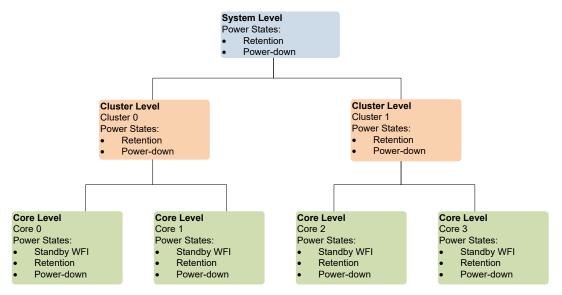

PSCI 0.2 supports only the original power\_state parameter format with a 16-bit StateID field. See [PSCI] for further details. Figure 1 shows an example system.

Figure 1 Example system

Figure 1 shows an example system composed of three power levels, core, cluster, and system. For each power level, the local power states are shown. Our example system PSCI supports the composite power states shown in Table 3.

Table 3 Supported power states in the example system and PSCI power\_state parameter encoding in original StateID format

| Composite power  |                        |                    |                           |

|------------------|------------------------|--------------------|---------------------------|

| Core local state | Cluster<br>local state | System local state | PCI power_state parameter |

| Retention        | Run                    | Run                | 0x00000001                |

| Power-down       | Run                    | Run                | 0x00010002                |

| Retention        | Retention              | Run                | 0x01000011                |

| Power-down | Retention  | Run        | 0x01010012 |

|------------|------------|------------|------------|

| Power-down | Power-down | Run        | 0x01010022 |

| Retention  | Retention  | Retention  | 0x02000111 |

| Power-down | Retention  | Retention  | 0x02010112 |

| Power-down | Power-down | Retention  | 0x02010122 |

| Power-down | Power-down | Power-down | 0x02010222 |

Note: Standby WFI is not listed as this state is entered via a WFI instruction and not via PSCI.

Table 3 shows the supported power states and their PSCI encoding. The example uses the following encoding:

- The power state StateID field, bits[15:0], is broken into sections that indicate the local power state of the core, cluster, and system. The possible values for each level are:

- 0: The entity is in the Run state.

- 1: The entity is in the Retention state.

- 2: The entity is in is the Power-down state.

The bit fields of the StateID field are as follows:

- o Bits[1:0] indicate the local power state at the core level.

- o Bits[5:4] indicate the local power state at the cluster level.

- Bits[9:8] indicate the local power state at the system level.

- Bits[13:12] are used by an OS working in OS Initiated mode to indicate the level in which the calling core is the last man. The OS might write:

- 0x0 if the core is not the last man at cluster or system level.

- 0x1 if the core is the last man at cluster level.

- 0x2 if the core is the last man in the system.

- All other bits are set to zero.

- As indicated in [PSCI], the PowerLevel field, bits[25:24], of the power\_state parameter reflects the highest power level affected by the state.

- As indicated in [PSCI], the StateType bit, bit 16, of the power\_state parameter is set whenever the

local state of the core is Power-down.

Table 4 shows how this PSCI encoding for power states can be represented in LPI entry methods.

**Table 4 LPI States**

| Core Level – LevelID 0 |             |              |                               |                                                          |  |  |

|------------------------|-------------|--------------|-------------------------------|----------------------------------------------------------|--|--|

| State                  | Description | Entry Method | Entry method value            | Enabled Parent State                                     |  |  |

| LPI1                   | Standby WFI | Register     | RegisterAddress<br>0xffffffff | 0 // Does not enable states in cluster or system levels. |  |  |

| LPI2                   | Retention   | Register     | RegisterAddress<br>0x00000001 | 1 // Enables cluster retention.                          |  |  |

| LPI3                   | Power-down  | Register     | RegisterAddress<br>0x00010002 | 2 // Enables cluster retention and power-down.           |  |  |

| Cluster Level – LevelID 0x1000 |            |         |            |                                               |

|--------------------------------|------------|---------|------------|-----------------------------------------------|

| LPI1                           | Retention  | Integer | 0x01000010 | 1 // Enables system retention.                |

| LPI2                           | Power-down | Integer | 0x01000020 | 2 // Enables system retention and power-down. |

| System Level – LevelID 0x2000  |            |         |            |                                               |

| LPI1                           | Retention  | Integer | 0x01000100 | 0 // N/A.                                     |

| LPI2                           | Power-down | Integer | 0x01000200 | 0 // N/A.                                     |

Table 5 demonstrates how the entry methods for the LPI states are combined to produce the correct PSCI power-state parameters.

Table 5 PSCI power\_state composition from LPI states

| Composite power state |                     |                    |                           |

|-----------------------|---------------------|--------------------|---------------------------|

| Core local state      | Cluster local state | System local state | PCI power_state parameter |

| LPI2: Retention       | + LPI0: Run         | + LPI0: Run        |                           |

| 0x00000001            | + 0                 | + 0                | = 0x00000001              |

| LPI3: Power-down      | + LPI0: Run         | + LPI0: Run        |                           |

| 0x00010002            | +0                  | +0                 | = 0x00010002              |

| LPI2: Retention       | + LPI1: Retention   | + LPI0: Run        |                           |

| 0x00000001            | + 0x01000010        | + 0                | = 0x01000011              |

| LPI3: Power-down      | + LPI1: Retention   | + LPI0: Run        |                           |

| 0x00010002            | + 0x01000010        | + 0                | = 0x01010012              |

| LPI3: Power-down      | +LPI2: Power-down   | + LPI0: Run        |                           |

| 0x00010002            | +0x01000020         | + 0                | = 0x01010022              |

| LPI2: Retention       | + LPI1: Retention   | + LPI1: Retention  |                           |

| 0x00000001            | + 0x01000010        | +0x01000100        | = 0x02000111              |

| LPI3: Power-down      | + LPI1: Retention   | + LPI1: Retention  |                           |

| 0x00010002            | + 0x01000010        | +0x01000100        | = 0x02010112              |

| LPI3: Power-down      | +LPI2: Power-down   | + LPI1: Retention  |                           |

| 0x00010002            | + 0x01000020        | +0x01000100        | = 0x02010122              |

| LPI3: Power-down      | +LPI2: Power-down   | +LPI2: Power-down  |                           |

| 0x00010002            | +0x01000020         | +0x01000200        | = 0x02010222              |

A system using OS Initiated mode adds the LevelID field value to the  $power\_state$  parameter obtained by combining the LPI state entry methods:

- If a core is not the last man in the cluster or system, no addition is required.

- If a core is the last man in the cluster, the LevelID value of 0x1000 must be added to the power\_state parameter.

- If a core is the last man in the system, the LevelID value of 0x2000 must be added to the power\_state parameter.

# A.2 Extended StateID power\_state parameter format: PSCI 1.0 or above

PSCI 1.0 introduces an optional new format for the power\_state parameter with an extended StateID field. This provides more flexibility to PSCI implementers on how to encode power states. Referring to the example system from Figure 1, Table 6 shows a possible PSCI 1.0 encoding using the extended ID format.

Table 6 Supported power states in the example system and PSCI power\_state parameter encoding in the extended StateID format

| Composite power     |                     |                    |                           |

|---------------------|---------------------|--------------------|---------------------------|

| Core<br>local state | Cluster local state | System local state | PCI power_state parameter |

| Retention           | Run                 | Run                | 0x00000001                |

| Power-down          | Run                 | Run                | 0x40000002                |

| Retention           | Retention           | Run                | 0x00000011                |

| Power-down          | Retention           | Run                | 0x40000012                |

| Power-down          | Power-down          | Run                | 0x40000022                |

| Retention           | Retention           | Retention          | 0x00000111                |

| Power-down          | Retention           | Retention          | 0x40000112                |

| Power-down          | Power-down          | Retention          | 0x40000122                |

| Power-down          | Power-down          | Power-down         | 0x40000222                |

Note: Standby WFI is not listed as this state is entered via a WFI instruction and not via PSCI.

Table 6 shows the supported power states and their PSCI encoding. The example uses the following encoding:

#### StateID:

- Bits[1:0] represent the power state of the core power level, where 0 represents the Run state, 1 the Retention state, and 2 the Power-down state.

- Bits[5:4] represent the power state of the cluster power level. 0 represents the Run state, 1 the Retention state, and 2 the Power-down state.

- Bits[9:8] represent the power state of the system power level. 0 represents the Run state, 1 the Retention state, and 2 the Power-down state.

- o Bits[25:24] are used by an OS working in OS Initiated mode to indicate the level in which the calling core is the last man. The OS might write:

- 0x0 if the core is not the last man at cluster or system level.

- 0x1 if the core is the last man at cluster level.

- 0x2 if the core is the last man in the system.

- o All other bits are set to zero

• As indicated in [PSCI] the StateType bit, bit 30, of the power\_state parameter is set whenever the local state of the core is Power-down.

Table 7 shows how this PSCI encoding for power states can be represented in LPI entry methods.

**Table 7 LPI States**

| Core Level – LevelID 0            |                                    |              |                               |                                                          |  |

|-----------------------------------|------------------------------------|--------------|-------------------------------|----------------------------------------------------------|--|

| State                             | Description                        | Entry Method | Entry method value            | Enables Parent State                                     |  |

| LPI1                              | Standby WFI                        | Register     | RegisterAddress<br>0xffffffff | 0 // Does not enable states in cluster or system levels. |  |

| LPI2                              | Retention                          | Register     | RegisterAddress<br>0x00000001 | 1 // Enables cluster retention.                          |  |

| LPI3                              | Power-down                         | Register     | RegisterAddress<br>0x40000002 | 2 // Enables cluster retention and power-down.           |  |

| Cluster Level -                   | Cluster Level – LevelID 0x01000000 |              |                               |                                                          |  |

| LPI1                              | Retention                          | Integer      | 0x0000010                     | 1 // Enables system retention.                           |  |

| LPI2                              | Power-down                         | Integer      | 0x00000020                    | 2 // Enables system retention and power-down.            |  |

| System Level – LevelID 0x02000000 |                                    |              |                               |                                                          |  |

| LPI1                              | Retention                          | Integer      | 0x0000100                     | 0 // N/A.                                                |  |

| LPI2                              | Power-down                         | Integer      | 0x00000200                    | 0 // N/A.                                                |  |

Table 8 demonstrates how the entry methods for the LPI states are combined to produce the correct PSCI power-state parameters:

Table 8 PSCI power state composition from LPI states

| Composite power sta |                     |                    |                            |

|---------------------|---------------------|--------------------|----------------------------|

| Core local state    | Cluster local state | System local state | PSCI power_state parameter |

| LPI2: Retention     | + LPI0: Run         | + LPI0: Run        |                            |

| 0x0000001           | + 0                 | + 0                | = 0x00000001               |

| LPI3: Power-down    | + LPI0: Run         | + LPI0: Run        |                            |

| 0x40000002          | +0                  | +0                 | = 0x40000002               |

| LPI2: Retention     | + LPI1: Retention   | + LPI0: Run        |                            |

| 0x0000001           | + 0x0000010         | + 0                | = 0x00000011               |

| LPI3: Power-down    | + LPI1: Retention   | + LPI0: Run        |                            |

| 0x40000002       | + 0x00000010      | + 0               | = 0x40000012 |

|------------------|-------------------|-------------------|--------------|

| LPI3: Power-down | +LPI2: Power-down | + LPI0: Run       |              |

| 0x40000002       | + 0x00000020      | + 0               | = 0x40000022 |

| LPI2: Retention  | + LPI1: Retention | + LPI1: Retention |              |

| 0x00000001       | + 0x00000010      | + 0x00000100      | = 0x00000111 |

| LPI3: Power-down | + LPI1: Retention | + LPI1: Retention |              |

| 0x40000002       | + 0x00000010      | + 0x00000100      | = 0x40000112 |

| LPI3: Power-down | +LPI2: Power-down | + LPI1: Retention |              |

| 0x40000002       | + 0x00000020      | + 0x00000100      | = 0x40000122 |

| LPI3: Power-down | +LPI2: Power-down | +LPI2: Power-down |              |

| 0x40000002       | + 0x00000020      | + 0x00000200      | = 0x40000222 |

A system using OS Initiated mode also adds the value of the LevelID field to the <code>power\_state</code> parameter that is obtained by combining the LPI state entry methods:

- If a core is not the last man in the cluster or system, no addition is required.

- If a core is the last man in the cluster, the LevelID value of 0x01000000 must be added to the power state parameter.

- If a core is the last man in the system, the LevelID value of 0x02000000 must be added to the power\_state parameter.

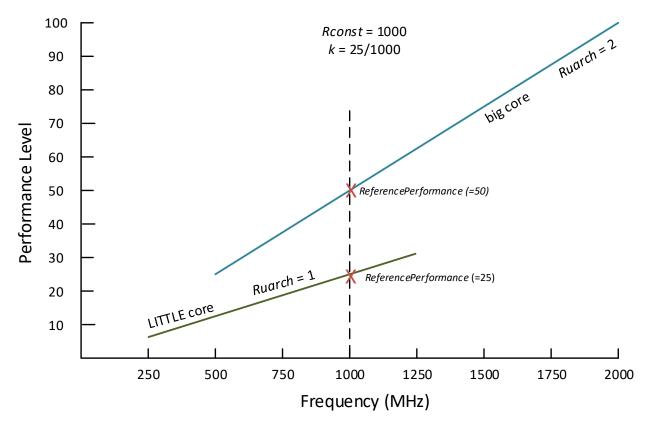

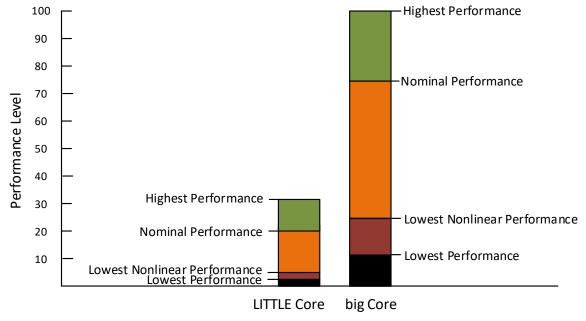

# Appendix B Processor performance monitoring and control in heterogenous systems