# **Arm® Instruction Set**

Version 1.0

**Reference Guide**

#### Arm® Instruction Set

#### Reference Guide

Copyright © 2018 Arm Limited or its affiliates. All rights reserved.

#### **Release Information**

#### **Document History**

| Issue   | Date            | Confidentiality  | Change        |

|---------|-----------------|------------------|---------------|

| 0100-00 | 25 October 2018 | Non-Confidential | First Release |

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or TM are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at http://www.arm.com/company/policies/trademarks.

Copyright © 2018 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

#### **Product Status**

The information in this document is Final, that is for a developed product.

#### Web Address

http://www.arm.com

## Contents

## **Arm® Instruction Set Reference Guide**

|            | Prefac | CE  About this book                                                 | 42    |

|------------|--------|---------------------------------------------------------------------|-------|

| Part A     | Instr  | ruction Set Overview                                                |       |

| Chapter A1 | Overv  | view of the Arm® Architecture                                       |       |

| •          | A1.1   | About the Arm® architecture                                         | A1-48 |

|            | A1.2   | Differences between the A64, A32, and T32 instruction sets          | A1-49 |

|            | A1.3   | Changing between AArch64 and AArch32 states                         | A1-50 |

|            | A1.4   | Advanced SIMD                                                       | A1-51 |

|            | A1.5   | Floating-point hardware                                             | A1-52 |

| Chapter A2 | Overv  | view of AArch32 state                                               |       |

|            | A2.1   | Changing between A32 and T32 instruction set states                 | A2-54 |

|            | A2.2   | Processor modes, and privileged and unprivileged software execution | A2-55 |

|            | A2.3   | Processor modes in Armv6-M, Armv7-M, and Armv8-M                    | A2-56 |

|            | A2.4   | Registers in AArch32 state                                          | A2-57 |

|            | A2.5   | General-purpose registers in AArch32 state                          | A2-59 |

|            | A2.6   | Register accesses in AArch32 state                                  | A2-60 |

|            | A2.7   | Predeclared core register names in AArch32 state                    | A2-61 |

|            | A2.8   | Predeclared extension register names in AArch32 state               | A2-62 |

|            | A2.9   | Program Counter in AArch32 state                                    | A2-63 |

|            | A2.10  | The Q flag in AArch32 state                                         | A2-64 |

|            | 712.70 | The Quegarite Concession                                            |       |

|            | A2.11 | Application Program Status Register                                  | A2-65         |

|------------|-------|----------------------------------------------------------------------|---------------|

|            | A2.12 | Current Program Status Register in AArch32 state                     | A2-66         |

|            | A2.13 | Saved Program Status Registers in AArch32 state                      | A2-67         |

|            | A2.14 | A32 and T32 instruction set overview                                 | A2-68         |

|            | A2.15 | Access to the inline barrel shifter in AArch32 state                 | A2-69         |

| Chapter A3 | Over  | view of AArch64 state                                                |               |

|            | A3.1  | Registers in AArch64 state                                           | A3-72         |

|            | A3.2  | Exception levels                                                     | A3-73         |

|            | A3.3  | Link registers                                                       | A3-74         |

|            | A3.4  | Stack Pointer register                                               | A3-75         |

|            | A3.5  | Predeclared core register names in AArch64 state                     | A3-76         |

|            | A3.6  | Predeclared extension register names in AArch64 state                | A3-77         |

|            | A3.7  | Program Counter in AArch64 state                                     | <i>A3-</i> 78 |

|            | A3.8  | Conditional execution in AArch64 state                               | <i>A3-7</i> 9 |

|            | A3.9  | The Q flag in AArch64 state                                          | A3-80         |

|            | A3.10 | Process State                                                        | A3-81         |

|            | A3.11 | Saved Program Status Registers in AArch64 state                      | A3-82         |

|            | A3.12 | A64 instruction set overview                                         | A3-83         |

| Part B     | Adv   | anced SIMD and Floating-point Programming                            |               |

| Chapter B1 | Adva  | nced SIMD Programming                                                |               |

| •          | B1.1  | Architecture support for Advanced SIMD                               | B1-88         |

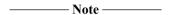

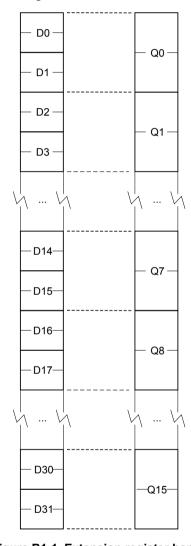

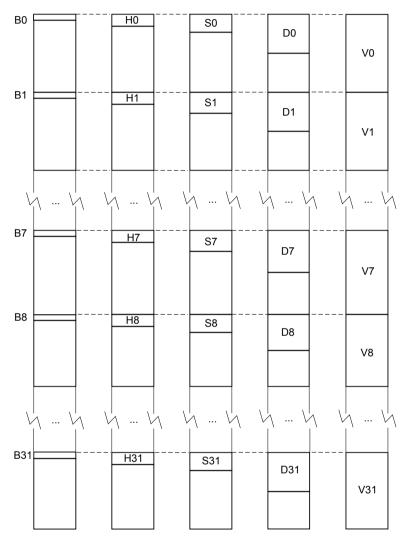

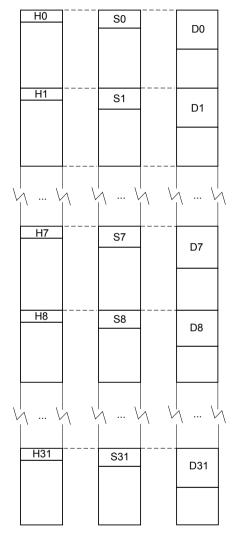

|            | B1.2  | Extension register bank mapping for Advanced SIMD in AArch32 state   |               |

|            | B1.3  | Extension register bank mapping for Advanced SIMD in AArch64 state   |               |

|            | B1.4  | Views of the Advanced SIMD register bank in AArch32 state            |               |

|            | B1.5  | Views of the Advanced SIMD register bank in AArch64 state            |               |

|            | B1.6  | Differences between A32/T32 and A64 Advanced SIMD instruction syntax |               |

|            | B1.7  | Load values to Advanced SIMD registers                               |               |

|            | B1.8  | Conditional execution of A32/T32 Advanced SIMD instructions          | B1-98         |

|            | B1.9  | Floating-point exceptions for Advanced SIMD in A32/T32 instructions  | B1-99         |

|            | B1.10 | Advanced SIMD data types in A32/T32 instructions                     |               |

|            | B1.11 | Polynomial arithmetic over {0,1}                                     |               |

|            | B1.12 | Advanced SIMD vectors                                                |               |

|            | B1.13 | Normal, long, wide, and narrow Advanced SIMD instructions            | B1-103        |

|            | B1.14 | Saturating Advanced SIMD instructions                                | B1-104        |

|            | B1.15 | Advanced SIMD scalars                                                | B1-105        |

|            | B1.16 | Extended notation extension for Advanced SIMD in A32/T32 code        | B1-106        |

|            | B1.17 | Advanced SIMD system registers in AArch32 state                      | B1-107        |

|            | B1.18 | Flush-to-zero mode in Advanced SIMD                                  | B1-108        |

|            | B1.19 | When to use flush-to-zero mode in Advanced SIMD                      | B1-109        |

|            | B1.20 | The effects of using flush-to-zero mode in Advanced SIMD             | B1-110        |

|            | B1.21 | Advanced SIMD operations not affected by flush-to-zero mode          |               |

| Chapter B2 | Float | ing-point Programming                                                |               |

|            | B2.1  | Architecture support for floating-point                              | B2-114        |

|            | B2.2  | Extension register bank mapping for floating-point in AArch32 state  | B2-115        |

|            | B2.3  | Extension register bank mapping in AArch64 state                     | B2-117        |

|            | B2.4  | Views of the floating-point extension register bank in AArch32 state | B2-118        |

|            |       |                                                                      |               |

|            | B2.5  | Views of the floating-point extension register bank in AArch64 state         | B2-119   |

|------------|-------|------------------------------------------------------------------------------|----------|

|            | B2.6  | Differences between A32/T32 and A64 floating-point instruction syntax        | B2-120   |

|            | B2.7  | Load values to floating-point registers                                      | B2-121   |

|            | B2.8  | Conditional execution of A32/T32 floating-point instructions                 | B2-122   |

|            | B2.9  | Floating-point exceptions for floating-point in A32/T32 instructions         | B2-123   |

|            | B2.10 | Floating-point data types in A32/T32 instructions                            | . B2-124 |

|            | B2.11 | Extended notation extension for floating-point in A32/T32 code               | B2-125   |

|            | B2.12 | Floating-point system registers in AArch32 state                             | B2-126   |

|            | B2.13 | Flush-to-zero mode in floating-point                                         | B2-127   |

|            | B2.14 | When to use flush-to-zero mode in floating-point                             | B2-128   |

|            | B2.15 | The effects of using flush-to-zero mode in floating-point                    | B2-129   |

|            | B2.16 | Floating-point operations not affected by flush-to-zero mode                 | . B2-130 |

| Part C     | A32   | /T32 Instruction Set Reference                                               |          |

| Chapter C1 | Cond  | lition Codes                                                                 |          |

|            | C1.1  | Conditional instructions                                                     | . C1-134 |

|            | C1.2  | Conditional execution in A32 code                                            | C1-135   |

|            | C1.3  | Conditional execution in T32 code                                            | C1-136   |

|            | C1.4  | Condition flags                                                              | C1-137   |

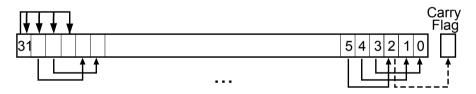

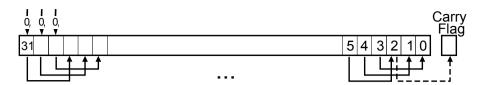

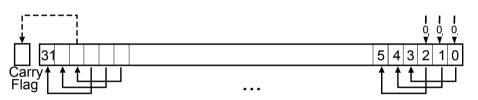

|            | C1.5  | Updates to the condition flags in A32/T32 code                               | . C1-138 |

|            | C1.6  | Floating-point instructions that update the condition flags                  | C1-139   |

|            | C1.7  | Carry flag                                                                   | C1-140   |

|            | C1.8  | Overflow flag                                                                | . C1-141 |

|            | C1.9  | Condition code suffixes                                                      | . C1-142 |

|            | C1.10 | Condition code suffixes and related flags                                    | . C1-143 |

|            | C1.11 | Comparison of condition code meanings in integer and floating-point code     | . C1-144 |

|            | C1.12 | Benefits of using conditional execution in A32 and T32 code                  | . C1-146 |

|            | C1.13 | Example showing the benefits of conditional instructions in A32 and T32 code | C1-147   |

|            | C1.14 | Optimization for execution speed                                             | C1-150   |

| Chapter C2 | A32 a | and T32 Instructions                                                         |          |

|            | C2.1  | A32 and T32 instruction summary                                              | C2-156   |

|            | C2.2  | Instruction width specifiers                                                 | C2-161   |

|            | C2.3  | Flexible second operand (Operand2)                                           | . C2-162 |

|            | C2.4  | Syntax of Operand2 as a constant                                             |          |

|            | C2.5  | Syntax of Operand2 as a register with optional shift                         | . C2-164 |

|            | C2.6  | Shift operations                                                             | . C2-165 |

|            | C2.7  | Saturating instructions                                                      | C2-168   |

|            | C2.8  | ADC                                                                          | C2-169   |

|            | C2.9  | ADD                                                                          | C2-171   |

|            | C2.10 | ADR (PC-relative)                                                            | . C2-174 |

|            | C2.11 | ADR (register-relative)                                                      | C2-176   |

|            | C2.12 | AND                                                                          | C2-178   |

|            | C2.13 | ASR                                                                          | . C2-180 |

|            | C2.14 | В                                                                            | C2-182   |

|            | C2.15 | BFC                                                                          | . C2-184 |

|            | C2.16 | BFI                                                                          | C2-185   |

|            | C2.17 | BIC                                                                          | C2-186   |

|            | C2.18 | BKPT                                                                         | . C2-188 |

|            |       |                                                                              |          |

| C2.19 | BL                                                                 | C2-189 |

|-------|--------------------------------------------------------------------|--------|

| C2.20 | BLX, BLXNS                                                         | C2-190 |

| C2.21 | BX, BXNS                                                           | C2-192 |

| C2.22 | BXJ                                                                | C2-194 |

| C2.23 | CBZ and CBNZ                                                       | C2-195 |

| C2.24 | CDP and CDP2                                                       |        |

| C2.25 | CLREX                                                              |        |

| C2.26 | CLZ                                                                |        |

| C2.27 | CMP and CMN                                                        |        |

| C2.28 | CPS                                                                |        |

| C2.29 | CRC32                                                              |        |

| C2.30 | CRC32C                                                             |        |

| C2.31 | CSDB                                                               |        |

| C2.32 | DBG                                                                |        |

| C2.33 | DCPS1 (T32 instruction)                                            |        |

| C2.34 | DCPS2 (T32 instruction)                                            |        |

|       | DCPS3 (T32 instruction)                                            |        |

| C2.35 |                                                                    |        |

| C2.36 | DMB                                                                |        |

| C2.37 | DSB                                                                |        |

| C2.38 | EOR                                                                |        |

| C2.39 | ERET                                                               |        |

| C2.40 | ESB                                                                |        |

| C2.41 | HLT                                                                |        |

| C2.42 | HVC                                                                |        |

| C2.43 | ISB                                                                |        |

| C2.44 | <i>IT</i>                                                          |        |

| C2.45 | LDA                                                                | C2-225 |

| C2.46 | LDAEX                                                              |        |

| C2.47 | LDC and LDC2                                                       |        |

| C2.48 | LDM                                                                |        |

| C2.49 | LDR (immediate offset)                                             |        |

| C2.50 | LDR (PC-relative)                                                  | C2-234 |

| C2.51 | LDR (register offset)                                              | C2-236 |

| C2.52 | LDR (register-relative)                                            | C2-238 |

| C2.53 | LDR, unprivileged                                                  | C2-240 |

| C2.54 | LDREX                                                              | C2-242 |

| C2.55 | LSL                                                                | C2-244 |

| C2.56 | LSR                                                                | C2-246 |

| C2.57 | MCR and MCR2                                                       | C2-248 |

| C2.58 | MCRR and MCRR2                                                     | C2-249 |

| C2.59 | MLA                                                                | C2-250 |

| C2.60 | MLS                                                                |        |

| C2.61 | MOV                                                                | C2-252 |

| C2.62 | MOVT                                                               |        |

| C2.63 | MRC and MRC2                                                       |        |

| C2.64 | MRRC and MRRC2                                                     |        |

| C2.65 | MRS (PSR to general-purpose register)                              |        |

| C2.66 | MRS (system coprocessor register to general-purpose register)      |        |

| C2.67 | MSR (general-purpose register to system coprocessor register)      |        |

| C2.68 | MSR (general-purpose register to PSR)                              |        |

|       | 10 - 1 - 1 - 1 - 2 - 2 - 2 - 3 - 1 - 1 - 3 - 1 - 1 - 1 - 1 - 1 - 1 | '      |

| C2.69  | MUL                | C2-263 |

|--------|--------------------|--------|

| C2.70  | MVN                | C2-264 |

| C2.71  | NOP                | C2-266 |

| C2.72  | ORN (T32 only)     | C2-267 |

| C2.73  | ORR                | C2-268 |

| C2.74  | PKHBT and PKHTB    | C2-270 |

| C2.75  | PLD, PLDW, and PLI | C2-272 |

| C2.76  | POP                | C2-274 |

| C2.77  | PUSH               | C2-275 |

| C2.78  | QADD               | C2-276 |

| C2.79  | QADD8              | C2-277 |

| C2.80  | QADD16             | C2-278 |

| C2.81  | QASX               | C2-279 |

| C2.82  | QDADD              | C2-280 |

| C2.83  | QDSUB              |        |

| C2.84  | QSAX               |        |

| C2.85  | QSUB               | C2-283 |

| C2.86  | QSUB8              |        |

| C2.87  | QSUB16             | C2-285 |

| C2.88  | RBIT               |        |

| C2.89  | REV                |        |

| C2.90  | REV16              |        |

| C2.91  | REVSH              |        |

| C2.92  | RFE                |        |

| C2.93  | ROR                |        |

| C2.94  | RRX                |        |

| C2.95  | RSB                |        |

| C2.96  | RSC                |        |

| C2.97  | SADD8              |        |

| C2.98  | SADD16             |        |

| C2.99  | SASX               |        |

| C2.100 | SBC                |        |

|        | SBFX               |        |

|        | SDIV               |        |

|        | SEL                |        |

|        | SETEND             |        |

|        | SETPAN             |        |

|        | SEV                |        |

|        | SEVL               |        |

|        | SG                 |        |

|        | SHADD8             |        |

|        | SHADD16            |        |

|        | SHASX              |        |

|        | SHSAX              |        |

|        | SHSUB8             |        |

|        | SHSUB16            |        |

|        | SMC                |        |

|        | SMLAxy             |        |

|        | SMLAD              |        |

|        | SMLAL              |        |

|        |                    | 321    |

| C2.119                     | SMLALD                 | C2-328                               |

|----------------------------|------------------------|--------------------------------------|

| C2.120                     | SMLALxy                | C2-329                               |

| C2.121                     | SMLAWy                 | C2-331                               |

| C2.122                     | SMLSD                  | C2-332                               |

| C2.123                     | SMLSLD                 | C2-333                               |

| C2.124                     | SMMLA                  | C2-334                               |

| C2.125                     | SMMLS                  | C2-335                               |

| C2.126                     | SMMUL                  | C2-336                               |

| C2.127                     | SMUAD                  | C2-337                               |

|                            | SMULxy                 |                                      |

|                            | SMULL                  |                                      |

|                            | SMULWy                 |                                      |

|                            | SMUSD                  |                                      |

|                            | SRS                    |                                      |

|                            | SSAT                   |                                      |

|                            | SSAT16                 |                                      |

|                            | SSAX                   |                                      |

|                            | SSUB8                  |                                      |

|                            | SSUB16                 |                                      |

|                            | STC and STC2           |                                      |

|                            | STL                    |                                      |

|                            | STLEX                  |                                      |

|                            | STM                    |                                      |

|                            | STR (immediate offset) |                                      |

|                            | STR (register offset)  |                                      |

|                            | STR, unprivileged      |                                      |

|                            | STREX                  |                                      |

|                            | SUB                    |                                      |

|                            | SUBS pc, Ir            |                                      |

|                            | SVC                    |                                      |

|                            | SWP and SWPB           |                                      |

|                            | SXTAB                  |                                      |

|                            |                        |                                      |

|                            | SXTAB16                |                                      |

|                            | SXTAH                  |                                      |

|                            | SXTB                   |                                      |

|                            | SXTB16                 |                                      |

|                            | SXTH                   |                                      |

|                            | SYS                    |                                      |

|                            | TBB and TBH            |                                      |

|                            | TEQ                    |                                      |

|                            | TST                    |                                      |

|                            | TT, TTT, TTA, TTAT     |                                      |

|                            | UADD8                  |                                      |

|                            | UADD16                 |                                      |

|                            |                        |                                      |

| C2 164                     | UASX                   |                                      |

|                            | UBFX                   | C2-399                               |

| C2.165                     | UBFX                   | C2-399<br>C2-400                     |

| C2.165<br>C2.166           | UBFX                   | C2-399<br>C2-400<br>C2-401           |

| C2.165<br>C2.166<br>C2.167 | UBFX                   | C2-399<br>C2-400<br>C2-401<br>C2-402 |

|            | C2.169 | UHASX                                                                       | C2-404 |

|------------|--------|-----------------------------------------------------------------------------|--------|

|            | C2.170 | UHSAX                                                                       | C2-405 |

|            | C2.171 | UHSUB8                                                                      | C2-406 |

|            | C2.172 | UHSUB16                                                                     | C2-407 |

|            | C2.173 | UMAAL                                                                       | C2-408 |

|            | C2.174 | UMLAL                                                                       | C2-409 |

|            | C2.175 | UMULL                                                                       | C2-410 |

|            | C2.176 | UQADD8                                                                      | C2-411 |

|            | C2.177 | UQADD16                                                                     | C2-412 |

|            | C2.178 | UQASX                                                                       | C2-413 |

|            | C2.179 | UQSAX                                                                       | C2-414 |

|            | C2.180 | UQSUB8                                                                      | C2-415 |

|            | C2.181 | UQSUB16                                                                     | C2-416 |

|            | C2.182 | USAD8                                                                       | C2-417 |

|            | C2.183 | USADA8                                                                      | C2-418 |

|            | C2.184 | USAT                                                                        | C2-419 |

|            | C2.185 | USAT16                                                                      | C2-420 |

|            | C2.186 | USAX                                                                        | C2-421 |

|            | C2.187 | USUB8                                                                       | C2-423 |

|            | C2.188 | USUB16                                                                      | C2-425 |

|            | C2.189 | UXTAB                                                                       | C2-426 |

|            | C2.190 | UXTAB16                                                                     | C2-428 |

|            | C2.191 | UXTAH                                                                       | C2-430 |

|            |        | UXTB                                                                        |        |

|            | C2.193 | UXTB16                                                                      | C2-434 |

|            | C2.194 | UXTH                                                                        | C2-435 |

|            |        | WFE                                                                         |        |

|            |        | WFI                                                                         |        |

|            |        | YIELD                                                                       |        |

|            |        |                                                                             |        |

| Chapter C3 | Advar  | nced SIMD Instructions (32-bit)                                             |        |

|            | C3.1   | Summary of Advanced SIMD instructions                                       | C3-445 |

|            | C3.2   | Summary of shared Advanced SIMD and floating-point instructions             | C3-448 |

|            | C3.3   | Interleaving provided by load and store element and structure instructions  | C3-449 |

|            | C3.4   | Alignment restrictions in load and store element and structure instructions | C3-450 |

|            | C3.5   | FLDMDBX, FLDMIAX                                                            | C3-451 |

|            | C3.6   | FSTMDBX, FSTMIAX                                                            | C3-452 |

|            | C3.7   | VABA and VABAL                                                              | C3-453 |

|            | C3.8   | VABD and VABDL                                                              | C3-454 |

|            | C3.9   | VABS                                                                        | C3-455 |

|            | C3.10  | VACLE, VACLT, VACGE and VACGT                                               | C3-456 |

|            | C3.11  | VADD                                                                        | C3-457 |

|            | C3.12  | VADDHN                                                                      |        |

|            | C3.13  | VADDL and VADDW                                                             |        |

|            | C3.14  | VAND (immediate)                                                            |        |

|            | C3.15  | VAND (register)                                                             |        |

|            | C3.16  | VBIC (immediate)                                                            |        |

|            | C3.17  | VBIC (register)                                                             |        |

|            | C3.18  | VBIF                                                                        |        |

|            |        | VBIT                                                                        |        |

|            |        |                                                                             | 5.5    |

| C3.20 | VBSL                                                               | C3-466 |

|-------|--------------------------------------------------------------------|--------|

| C3.21 | VCADD                                                              | C3-467 |

| C3.22 | VCEQ (immediate #0)                                                | C3-468 |

| C3.23 | VCEQ (register)                                                    | C3-469 |

| C3.24 | VCGE (immediate #0)                                                | C3-470 |

| C3.25 | VCGE (register)                                                    | C3-471 |

| C3.26 | VCGT (immediate #0)                                                | C3-472 |

| C3.27 | VCGT (register)                                                    | C3-473 |

| C3.28 | VCLE (immediate #0)                                                | C3-474 |

| C3.29 | VCLS                                                               | C3-475 |

| C3.30 | VCLE (register)                                                    | C3-476 |

| C3.31 | VCLT (immediate #0)                                                |        |

| C3.32 | VCLT (register)                                                    |        |

| C3.33 | VCLZ                                                               |        |

| C3.34 | VCMLA                                                              |        |

| C3.35 | VCMLA (by element)                                                 |        |

| C3.36 | VCNT                                                               |        |

| C3.37 | VCVT (between fixed-point or integer, and floating-point)          |        |

| C3.38 | VCVT (between half-precision and single-precision floating-point)  |        |

| C3.39 | VCVT (from floating-point to integer with directed rounding modes) |        |

| C3.40 | VCVTB, VCVTT (between half-precision and double-precision)         |        |

| C3.41 | VDUP                                                               |        |

| C3.42 | VEOR                                                               |        |

| C3.43 | VEXT                                                               |        |

| C3.44 | VFMA, VFMS                                                         |        |

| C3.45 | VFMAL (by scalar)                                                  |        |

| C3.46 | VFMAL (vector)                                                     |        |

| C3.47 | VFMSL (by scalar)                                                  |        |

| C3.48 | VFMSL (vector)                                                     |        |

| C3.49 | VHADD                                                              |        |

| C3.50 | VHSUB                                                              |        |

|       |                                                                    |        |

| C3.51 | VLDn (single n-element structure to one lane)                      |        |

| C3.52 | VLDn (single n-element structure to all lanes)                     |        |

| C3.53 | VLDn (multiple n-element structures)                               |        |

| C3.54 | VLDM                                                               |        |

| C3.55 | VLDR                                                               |        |

| C3.56 | VLDR (post-increment and pre-decrement)                            |        |

| C3.57 | VLDR pseudo-instruction                                            |        |

| C3.58 | VMAX and VMIN                                                      |        |

| C3.59 | VMAXNM, VMINNM                                                     |        |

| C3.60 | VMLA                                                               |        |

| C3.61 | VMLA (by scalar)                                                   |        |

| C3.62 | VMLAL (by scalar)                                                  |        |

| C3.63 | VMLAL                                                              |        |

| C3.64 | VMLS (by scalar)                                                   |        |

| C3.65 | VMLS                                                               | C3-514 |

| C3.66 | VMLSL                                                              |        |

| C3.67 | VMLSL (by scalar)                                                  | C3-516 |

| C3.68 | VMOV (immediate)                                                   | C3-517 |

| C3.69 | VMOV (register)                                                    | C3-518 |

| C3.70  | VMOV (between two general-purpose registers and a 64-bit extension register) |        |

|--------|------------------------------------------------------------------------------|--------|

|        |                                                                              |        |

| C3.71  | VMOV (between a general-purpose register and an Advanced SIMD scalar)        |        |

| C3.72  | VMOVL                                                                        |        |

| C3.73  | VMOVN                                                                        |        |

| C3.74  | VMOV2                                                                        | C3-523 |

| C3.75  | VMRS                                                                         |        |

| C3.76  | VMSR                                                                         |        |

| C3.77  | VMUL                                                                         |        |

| C3.78  | VMUL (by scalar)                                                             | C3-527 |

| C3.79  | VMULL                                                                        | C3-528 |

| C3.80  | VMULL (by scalar)                                                            | C3-529 |

| C3.81  | VMVN (register)                                                              | C3-530 |

| C3.82  | VMVN (immediate)                                                             | C3-531 |

| C3.83  | VNEG                                                                         | C3-532 |

| C3.84  | VORN (register)                                                              | C3-533 |

| C3.85  | VORN (immediate)                                                             | C3-534 |

| C3.86  | VORR (register)                                                              | C3-535 |

| C3.87  | VORR (immediate)                                                             | C3-536 |

| C3.88  | VPADAL                                                                       | C3-537 |

| C3.89  | VPADD                                                                        | C3-538 |

| C3.90  | VPADDL                                                                       |        |

| C3.91  | VPMAX and VPMIN                                                              |        |

| C3.92  | VPOP                                                                         |        |

| C3.93  | VPUSH                                                                        |        |

| C3.94  | VQABS                                                                        |        |

| C3.95  | VQADD                                                                        |        |

| C3.96  | VQDMLAL and VQDMLSL (by vector or by scalar)                                 |        |

| C3.97  | VQDMULH (by vector or by scalar)                                             |        |

| C3.98  | VQDMULL (by vector or by scalar)                                             |        |

| C3.99  | VQMOVN and VQMOVUN                                                           |        |

|        | VQNEG                                                                        |        |

|        | VQRDMULH (by vector or by scalar)                                            |        |

|        | VQRSHL (by signed variable)                                                  |        |

|        | VQRSHRN and VQRSHRUN (by immediate)                                          |        |

|        | VQSHL (by signed variable)                                                   |        |

|        | VQSHL and VQSHLU (by immediate)                                              |        |

|        | VQSHRN and VQSHRUN (by immediate)                                            |        |

|        | VQSUB                                                                        |        |

|        | VRADDHN                                                                      |        |

|        |                                                                              |        |

|        | VRECPE                                                                       |        |

|        | VRECPS                                                                       |        |

|        | VREV16, VREV32, and VREV64                                                   |        |

|        | VRHADD                                                                       |        |

|        | VRSHL (by signed variable)                                                   |        |

|        | VRSHR (by immediate)                                                         |        |

|        | VRSHRN (by immediate)                                                        |        |

|        | VRINT                                                                        |        |

|        | VRSQRTE                                                                      |        |

| C3.118 | VRSQRTS                                                                      | C3-567 |

|            | C3.119 | VRSRA (by immediate)                                               | C3-568 |

|------------|--------|--------------------------------------------------------------------|--------|

|            | C3.120 | VRSUBHN                                                            | C3-569 |

|            | C3.121 | VSDOT (vector)                                                     | C3-570 |

|            | C3.122 | VSDOT (by element)                                                 | C3-571 |

|            | C3.123 | VSHL (by immediate)                                                | C3-572 |

|            | C3.124 | VSHL (by signed variable)                                          | C3-573 |

|            | C3.125 | VSHLL (by immediate)                                               | C3-574 |

|            | C3.126 | VSHR (by immediate)                                                | C3-575 |

|            | C3.127 | VSHRN (by immediate)                                               | C3-576 |

|            | C3.128 | VSLI                                                               | C3-577 |

|            | C3.129 | VSRA (by immediate)                                                | C3-578 |

|            | C3.130 | VSRI                                                               | C3-579 |

|            | C3.131 | VSTM                                                               | C3-580 |

|            | C3.132 | VSTn (multiple n-element structures)                               | C3-581 |

|            | C3.133 | VSTn (single n-element structure to one lane)                      | C3-583 |

|            | C3.134 | VSTR                                                               | C3-585 |

|            | C3.135 | VSTR (post-increment and pre-decrement)                            | C3-586 |

|            | C3.136 | VSUB                                                               | C3-587 |

|            | C3.137 | VSUBHN                                                             | C3-588 |

|            | C3.138 | VSUBL and VSUBW                                                    | C3-589 |

|            | C3.139 | VSWP                                                               | C3-590 |

|            | C3.140 | VTBL and VTBX                                                      | C3-591 |

|            | C3.141 | VTRN                                                               | C3-592 |

|            | C3.142 | VTST                                                               | C3-593 |

|            | C3.143 | VUDOT (vector)                                                     | C3-594 |

|            | C3.144 | VUDOT (by element)                                                 | C3-595 |

|            | C3.145 | VUZP                                                               | C3-596 |

|            | C3.146 | VZIP                                                               | C3-597 |

| Chapter C4 | Floati | ing-point Instructions (32-bit)                                    |        |

|            | C4.1   | Summary of floating-point instructions                             | C4-601 |

|            | C4.2   | VABS (floating-point)                                              | C4-603 |

|            | C4.3   | VADD (floating-point)                                              | C4-604 |

|            | C4.4   | VCMP, VCMPE                                                        | C4-605 |

|            | C4.5   | VCVT (between single-precision and double-precision)               | C4-606 |

|            | C4.6   | VCVT (between floating-point and integer)                          | C4-607 |

|            | C4.7   | VCVT (from floating-point to integer with directed rounding modes) | C4-608 |

|            | C4.8   | VCVT (between floating-point and fixed-point)                      | C4-609 |

|            | C4.9   | VCVTB, VCVTT (half-precision extension)                            | C4-610 |

|            | C4.10  | VCVTB, VCVTT (between half-precision and double-precision)         | C4-611 |

|            | C4.11  | VDIV                                                               | C4-612 |

|            | C4.12  | VFMA, VFMS, VFNMA, VFNMS (floating-point)                          | C4-613 |

|            | C4.13  | VJCVT                                                              | C4-614 |

|            | C4.14  | VLDM (floating-point)                                              |        |

|            | C4.15  | VLDR (floating-point)                                              | C4-616 |

|            | C4.16  | VLDR (post-increment and pre-decrement, floating-point)            | C4-617 |

|            | C4.17  | VLLDM                                                              |        |

|            | C4.18  | VLSTM                                                              |        |

|            | C4.19  | VMAXNM, VMINNM (floating-point)                                    | C4-620 |

|            | C4.20  | VMLA (floating-point)                                              | C4-621 |

|            |        |                                                                    |        |

|             | C4.21 | VMLS (floating-point)                                                       | C4-622         |

|-------------|-------|-----------------------------------------------------------------------------|----------------|

|             | C4.22 | VMOV (floating-point)                                                       | C4-623         |

|             | C4.23 | VMOV (between one general-purpose register and single precision floating-p  | oint           |

|             |       | register)                                                                   | C4-624         |

|             | C4.24 | VMOV (between two general-purpose registers and one or two extension reg    | isters)        |

|             |       |                                                                             | C4-625         |

|             | C4.25 | VMOV (between a general-purpose register and half a double precision floati | ng-point       |

|             |       | register)                                                                   | C4-626         |

|             | C4.26 | VMRS (floating-point)                                                       | C4-627         |

|             | C4.27 | VMSR (floating-point)                                                       | C4-628         |

|             | C4.28 | VMUL (floating-point)                                                       | C4-629         |

|             | C4.29 | VNEG (floating-point)                                                       | C4-630         |

|             | C4.30 | VNMLA (floating-point)                                                      | C4-631         |

|             | C4.31 | VNMLS (floating-point)                                                      | C4-632         |

|             | C4.32 | VNMUL (floating-point)                                                      | C4-633         |

|             | C4.33 | VPOP (floating-point)                                                       | C4-634         |

|             | C4.34 | VPUSH (floating-point)                                                      | C4-635         |

|             | C4.35 | VRINT (floating-point)                                                      | C4-636         |

|             | C4.36 | VSEL                                                                        | C4-637         |

|             | C4.37 | VSQRT                                                                       | C4-638         |

|             | C4.38 | VSTM (floating-point)                                                       | C4-639         |

|             | C4.39 | VSTR (floating-point)                                                       | C4-640         |

|             | C4.40 | VSTR (post-increment and pre-decrement, floating-point)                     | C4-641         |

|             | C4.41 | VSUB (floating-point)                                                       | C4-642         |

| Chapter C5  | A32/7 | T32 Cryptographic Algorithms                                                |                |

|             | C5.1  | A32/T32 Cryptographic instructions                                          | C5-644         |

|             |       |                                                                             |                |

| Part D      | A64   | Instruction Set Reference                                                   |                |

| Chapter D1  | Cond  | lition Codes                                                                |                |

| omaptor 2 : | D1.1  | Conditional execution in A64 code                                           | D1-648         |

|             | D1.1  | Condition flags                                                             |                |

|             |       | Updates to the condition flags in A64 code                                  |                |

|             | D1.4  | Floating-point instructions that update the condition flags                 |                |

|             | D1.4  | Carry flag                                                                  |                |

|             | D1.6  | Overflow flag                                                               |                |

|             | D1.7  | Condition code suffixes                                                     |                |

|             | D1.7  | Condition code suffixes and related flags                                   |                |

|             | D1.9  | Optimization for execution speed                                            |                |

| Oh t D0     | 4046  | 2                                                                           |                |

| Chapter D2  |       | General Instructions                                                        |                |

|             | D2.1  | A64 instructions in alphabetical order                                      |                |

|             | D2.2  | Register restrictions for A64 instructions                                  |                |

|             | D2.3  | ADC                                                                         |                |

|             | D2.4  | ADCS                                                                        |                |

|             | D2.5  | ADD (extended register)                                                     |                |

|             | D2.6  | ADD (immediate)                                                             |                |

|             | D2.7  | ADD (shifted register)                                                      |                |

|             | D2.8  | ADDG                                                                        | <i>D2</i> -676 |

| D2.9  | ADDS (extended register)                  | D2-677 |

|-------|-------------------------------------------|--------|

| D2.10 | ADDS (immediate)                          | D2-679 |

| D2.11 | ADDS (shifted register)                   | D2-680 |

| D2.12 | ADR                                       | D2-681 |

| D2.13 | ADRP                                      | D2-682 |

| D2.14 | AND (immediate)                           | D2-683 |

| D2.15 | AND (shifted register)                    | D2-684 |

| D2.16 | ANDS (immediate)                          | D2-685 |

| D2.17 | ANDS (shifted register)                   |        |

| D2.18 | ASR (register)                            |        |

| D2.19 | ASR (immediate)                           |        |

| D2.20 | ASRV                                      |        |

| D2.21 | AT                                        |        |

| D2.22 | AUTDA, AUTDZA                             |        |

| D2.23 | AUTDB, AUTDZB                             |        |

| D2.24 | AUTIA, AUTIZA, AUTIA1716, AUTIASP, AUTIAZ |        |

| D2.25 | AUTIB, AUTIZB, AUTIB1716, AUTIBSP, AUTIBZ |        |

| D2.26 | AXFlag                                    |        |

| D2.27 | B.cond                                    |        |

| D2.28 | В                                         |        |

| D2.29 | BFC                                       |        |

| D2.29 | BFI                                       |        |

| D2.30 | BFM                                       |        |

| D2.31 | BFXIL                                     |        |

|       |                                           |        |

| D2.33 | BIC (shifted register)                    |        |

| D2.34 | BICS (shifted register)                   |        |

| D2.35 | BL                                        |        |

| D2.36 | BLR                                       |        |

| D2.37 | BLRAA, BLRAAZ, BLRAB, BLRABZ              |        |

| D2.38 | BR                                        |        |

| D2.39 | BRAA, BRAAZ, BRAB, BRABZ                  |        |

| D2.40 | BRK                                       |        |

| D2.41 | BTI                                       | D2-711 |

| D2.42 | CBNZ                                      | D2-712 |

| D2.43 | CBZ                                       |        |

| D2.44 | CCMN (immediate)                          | D2-714 |

| D2.45 | CCMN (register)                           | D2-715 |

| D2.46 | CCMP (immediate)                          | D2-716 |

| D2.47 | CCMP (register)                           | D2-717 |

| D2.48 | CINC                                      | D2-718 |

| D2.49 | CINV                                      | D2-719 |

| D2.50 | CLREX                                     | D2-720 |

| D2.51 | CLS                                       | D2-721 |

| D2.52 | CLZ                                       | D2-722 |

| D2.53 | CMN (extended register)                   | D2-723 |

| D2.54 | CMN (immediate)                           | D2-725 |

| D2.55 | CMN (shifted register)                    | D2-726 |

| D2.56 | CMP (extended register)                   |        |

| D2.57 | CMP (immediate)                           |        |

| D2.58 | CMP (shifted register)                    |        |

| CMPP                               | D2-731                                                                                                                                                           |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CNEG                               | D2-732                                                                                                                                                           |

| CRC32B, CRC32H, CRC32W, CRC32X     | D2-733                                                                                                                                                           |

| CRC32CB, CRC32CH, CRC32CW, CRC32CX | D2-734                                                                                                                                                           |

| CSDB                               | D2-735                                                                                                                                                           |

| CSEL                               | D2-737                                                                                                                                                           |

| CSET                               | D2-738                                                                                                                                                           |

| CSETM                              | D2-739                                                                                                                                                           |

| CSINC                              | D2-740                                                                                                                                                           |

|                                    |                                                                                                                                                                  |

|                                    |                                                                                                                                                                  |

|                                    |                                                                                                                                                                  |

|                                    |                                                                                                                                                                  |

|                                    |                                                                                                                                                                  |

|                                    |                                                                                                                                                                  |

|                                    |                                                                                                                                                                  |

|                                    |                                                                                                                                                                  |

|                                    |                                                                                                                                                                  |

|                                    |                                                                                                                                                                  |

|                                    |                                                                                                                                                                  |

|                                    |                                                                                                                                                                  |

|                                    |                                                                                                                                                                  |

|                                    |                                                                                                                                                                  |

| •                                  |                                                                                                                                                                  |

|                                    |                                                                                                                                                                  |

|                                    |                                                                                                                                                                  |

|                                    |                                                                                                                                                                  |

|                                    |                                                                                                                                                                  |

|                                    |                                                                                                                                                                  |

|                                    |                                                                                                                                                                  |

|                                    |                                                                                                                                                                  |

|                                    |                                                                                                                                                                  |

|                                    |                                                                                                                                                                  |

|                                    |                                                                                                                                                                  |

|                                    |                                                                                                                                                                  |

|                                    |                                                                                                                                                                  |

| ·                                  |                                                                                                                                                                  |

| LSLV                               | D2-770                                                                                                                                                           |

| LSR (register)                     | D2-771                                                                                                                                                           |

| LSR (immediate)                    | D2-772                                                                                                                                                           |

| LSRV                               | D2-773                                                                                                                                                           |

| MADD                               | D2-774                                                                                                                                                           |

| MNEG                               | D2-775                                                                                                                                                           |

| MOV (to or from SP)                | D2-776                                                                                                                                                           |

| MOV (inverted wide immediate)      | D2-777                                                                                                                                                           |

| MOV (wide immediate)               | D2-778                                                                                                                                                           |

| MOV (bitmask immediate)            |                                                                                                                                                                  |

| MOV (register)                     |                                                                                                                                                                  |

| MOVK                               |                                                                                                                                                                  |

| MOVN                               |                                                                                                                                                                  |

| MOVZ                               |                                                                                                                                                                  |

|                                    | LSR (immediate)  LSRV  MADD  MNEG  MOV (to or from SP)  MOV (inverted wide immediate)  MOV (wide immediate)  MOV (bitmask immediate)  MOV (register)  MOVK  MOVN |

| D2.109 | MRS                                       | D2-784 |

|--------|-------------------------------------------|--------|

| D2.110 | MSR (immediate)                           | D2-785 |

| D2.111 | MSR (register)                            | D2-786 |

| D2.112 | MSUB                                      | D2-787 |

| D2.113 | MUL                                       | D2-788 |

| D2.114 | MVN                                       | D2-789 |

| D2.115 | NEG (shifted register)                    | D2-790 |

| D2.116 | NEGS                                      | D2-791 |

| D2.117 | NGC                                       | D2-792 |

| D2.118 | NGCS                                      | D2-793 |

| D2.119 | NOP                                       | D2-794 |

| D2.120 | ORN (shifted register)                    | D2-795 |

| D2.121 | ORR (immediate)                           | D2-796 |

|        | ORR (shifted register)                    |        |

| D2.123 | PACDA, PACDZA                             | D2-798 |

| D2.124 | PACDB, PACDZB                             | D2-799 |

| D2.125 | PACGA                                     | D2-800 |

| D2.126 | PACIA, PACIZA, PACIA1716, PACIASP, PACIAZ | D2-801 |

|        | PACIB, PACIBB, PACIBIT16, PACIBSP, PACIBZ |        |

|        | PSB                                       |        |

|        | RBIT                                      |        |

|        | RET                                       |        |

| D2.131 | RETAA, RETAB                              | D2-806 |

|        | REV16                                     |        |

|        | REV32                                     |        |

|        | REV64                                     |        |

|        | REV                                       |        |

|        | ROR (immediate)                           |        |

|        | ROR (register)                            |        |

|        | RORV                                      |        |

|        | SBC                                       |        |

|        | SBCS                                      |        |

|        | SBFIZ                                     |        |

|        | SBFM                                      |        |

|        | SBFX                                      |        |

|        | SDIV                                      |        |

|        | SEV                                       |        |

|        | SEVL                                      |        |

|        | SMADDL                                    |        |

|        | SMC                                       |        |

|        | SMNEGL                                    |        |

|        | SMSUBL                                    |        |

|        | SMULH                                     |        |

|        | SMULL                                     |        |

|        | ST2G                                      |        |

|        | STG                                       |        |

|        | STGP                                      |        |

|        | STGV                                      |        |

|        | STZ2G                                     |        |

|        | STZG                                      |        |

|        | · · · · · · · · · · · · · · · · · · ·     |        |

|            | D2.159 S | SUB (extended register)                                | D2-834 |

|------------|----------|--------------------------------------------------------|--------|

|            | D2.160 S | SUB (immediate)                                        | D2-836 |

|            | D2.161 S | SUB (shifted register)                                 | D2-837 |

|            | D2.162 S | SUBG                                                   | D2-838 |

|            | D2.163 S | SUBP                                                   | D2-839 |

|            | D2.164 S | SUBPS                                                  | D2-840 |

|            | D2.165   | SUBS (extended register)                               | D2-841 |

|            | D2.166 S | SUBS (immediate)                                       | D2-843 |

|            | D2.167 S | SUBS (shifted register)                                | D2-844 |

|            |          | SVC                                                    |        |

|            | D2.169 S | SXTB                                                   | D2-846 |

|            | D2.170 S | SXTH                                                   | D2-847 |

|            |          | SXTW                                                   |        |

|            |          | SYS                                                    |        |

|            | D2.173 S | SYSL                                                   | D2-850 |

|            |          | TBNZ                                                   |        |

|            |          | TBZ                                                    |        |

|            |          | TLBI                                                   |        |

|            |          | TST (immediate)                                        |        |

|            |          | TST (shifted register)                                 |        |

|            |          | UBFIZ                                                  |        |

|            |          | UBFM                                                   |        |

|            |          | UBFX                                                   |        |

|            |          | UDIV                                                   |        |

|            |          | UMADDL                                                 |        |

|            |          | UMNEGL                                                 |        |

|            |          | UMSUBL                                                 |        |

|            |          | UMULH                                                  |        |