# PCIe AMBA Integration Guide

| Document number: | ARM DEN 0114     |

|------------------|------------------|

| Release Quality: | ALP              |

| Issue Number:    | 1.0              |

| Confidentiality: | Non-Confidential |

| Date of Issue:   | 10/02/2022       |

|                  |                  |

© Copyright Arm Limited 2022. All rights reserved.

# Contents

| Abou | t this do | ocument                                                                                                                                                                                                                                                                                                                                                              | v    |  |

|------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|

|      | Release   | e Information                                                                                                                                                                                                                                                                                                                                                        | v    |  |

|      | Refere    | nces                                                                                                                                                                                                                                                                                                                                                                 | viii |  |

|      | Terms     | and abbreviations                                                                                                                                                                                                                                                                                                                                                    | viii |  |

|      | Potent    | ial for change                                                                                                                                                                                                                                                                                                                                                       | viii |  |

|      | Conver    |                                                                                                                                                                                                                                                                                                                                                                      | viii |  |

|      |           |                                                                                                                                                                                                                                                                                                                                                                      | viii |  |

|      |           | Numbers                                                                                                                                                                                                                                                                                                                                                              | ix   |  |

|      | Curren    | t status and anticipated changes                                                                                                                                                                                                                                                                                                                                     | ix   |  |

|      | Feedba    | ick                                                                                                                                                                                                                                                                                                                                                                  | ix   |  |

|      |           | Feedback on this book                                                                                                                                                                                                                                                                                                                                                | ix   |  |

| 1    |           | Introduction                                                                                                                                                                                                                                                                                                                                                         | 10   |  |

|      | 1.1       | Introduction 10                                                                                                                                                                                                                                                                                                                                                      |      |  |

| 2    |           | Terminology                                                                                                                                                                                                                                                                                                                                                          | 11   |  |

|      | 2.1       | Transaction Terminology                                                                                                                                                                                                                                                                                                                                              | 11   |  |

|      | 2.2       | Arm Terminology                                                                                                                                                                                                                                                                                                                                                      | 11   |  |

|      |           | 2.2.1 Device memory                                                                                                                                                                                                                                                                                                                                                  | 11   |  |

|      |           | 2.2.2 Normal memory                                                                                                                                                                                                                                                                                                                                                  | 13   |  |

|      | 2.3       | PCIe Terminology                                                                                                                                                                                                                                                                                                                                                     | 15   |  |

|      | 2.0       | 2.3.1 Inbound and Outbound                                                                                                                                                                                                                                                                                                                                           | 16   |  |

| 3    |           | ARM Memory Type USAGE FOR INBOUND AND OUTBOUND PCIE transactions                                                                                                                                                                                                                                                                                                     | 18   |  |

|      | 3.1       | Memory Type Assumptions 18                                                                                                                                                                                                                                                                                                                                           |      |  |

|      | 3.2       | Outbound Transaction Memory Type 18                                                                                                                                                                                                                                                                                                                                  |      |  |

|      | 3.3       | <ul> <li>Inbound Transaction Memory Type</li> <li>3.3.1 Step 1: Determining the Arm memory type, cacheability and shareability attributes</li> <li>3.3.2 Step 2: Modifying the cacheability attribute based on the transaction's No Snoop bit value</li> <li>2.2.2 Step 2: Mapping the Arm memory type, cacheability and shareability attributes to AVI/A</li> </ul> | 19   |  |

|      |           | 3.3.3 Step 3: Mapping the Arm memory type, cacheability and shareability attributes to AXI/A memory attributes.                                                                                                                                                                                                                                                      | 20   |  |

|     | 3.3.4 Coherency management for Inbound transactions                                                                                                                                                                                                                                                                                                                                                            | 20                                |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

|     | COMPLYING TO ARM memory model FOR PE GENERATED PCIE TRANSACTIONs                                                                                                                                                                                                                                                                                                                                               | 23                                |

| 4.1 | <ul> <li>Device-nGnRnE and Device-nGnRE</li> <li>4.1.1 PE and Interconnect requirements for handling Outbound requests to Device-nGnRnE Device-nGnRE mapped locations</li> <li>4.1.2 PCle interface requirements for handling Outbound requests to Device-nGnRnE or Deving nGnRE mapped locations</li> <li>4.1.3 Example use cases for Device-nGnRnE and Device-nGnRE mapping of PCle address space</li> </ul> | 24<br>vice-<br>25                 |

| 4.2 | <ul> <li>Device-nGRE and Device-GRE</li> <li>4.2.1 PCIe interface requirements for handling Outbound requests to Device-nGRE and Dev GRE mapped locations</li> </ul>                                                                                                                                                                                                                                           | <b>26</b><br>ice-<br>26           |

| 4.3 | <ul> <li>Normal with Non-cacheable as the cacheability attribute</li> <li>4.3.1 PCIe interface requirements for handling Outbound requests to Normal Non-cacheabl mapped memory locations</li> </ul>                                                                                                                                                                                                           | e 27                              |

| 4.4 | <ul> <li>Complying with internal visibility requirement of the Arm memory model</li> <li>4.4.1 PCIe interface requirements for complying with internal visibility requirement for Outbound transactions from PEs</li> </ul>                                                                                                                                                                                    | <b>27</b><br>28                   |

| 4.5 | PCIe interface requirements for handling transactions with the same AXI ID                                                                                                                                                                                                                                                                                                                                     | 28                                |

| 4.6 | Interconnect requirements for preserving barrier-ordered-before ordering relation                                                                                                                                                                                                                                                                                                                              | 29                                |

| 4.7 | Setting RO and IDO for PE transactions4.7.1Setting RO for Root-SoC PE transactions4.7.2Setting IDO for Root-SoC PE transactions4.7.3Setting RO for Endpoint-SoC PE transactions4.7.4Setting IDO for Endpoint-SoC PE transactions                                                                                                                                                                               | <b>29</b><br>29<br>29<br>29<br>30 |

| 4.8 | <ul> <li>Ordering guarantees available to software for accesses targeting PCIe destinations</li> <li>4.8.1 Achieving producer consumer ordering for transactions from PE to PCIe destinations</li> <li>4.8.2 Multiple PCIe address spaces mapped as Device-nGnRnE or Device-nGnRE</li> </ul>                                                                                                                   | <b>30</b><br>32<br>33             |

|     | COMPLYING TO PCIE ORDERING MODEL                                                                                                                                                                                                                                                                                                                                                                               | 34                                |

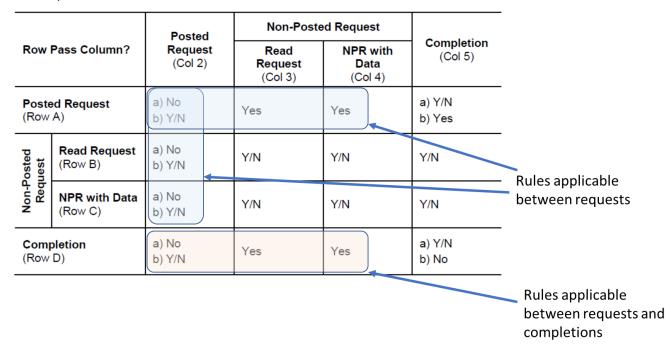

| 5.1 | Ordering table coverage                                                                                                                                                                                                                                                                                                                                                                                        | 34                                |

| 5.2 | Overtaking and Ordering                                                                                                                                                                                                                                                                                                                                                                                        | 36                                |

| 5.3 | Overtaking Rules5.3.1Both requests Outbound5.3.2Both requests Inbound5.3.3Outbound request / Inbound Completion5.3.4Outbound completion/ Inbound request                                                                                                                                                                                                                                                       | <b>38</b><br>38<br>39<br>40<br>41 |

5

4

| 5.4 | Ordering Rules |                                                                                   | 42   |

|-----|----------------|-----------------------------------------------------------------------------------|------|

|     | 5.4.1          | Both requests Outbound                                                            | 42   |

|     | 5.4.2          | Posted Write, Read Request, or Configuration Write must not overtake Posted Write | [A2, |

|     |                | B2, C2]                                                                           | 42   |

|     | 5.4.3          | Example Use Cases                                                                 | 43   |

|     | 5.4.4          | Both requests Inbound                                                             | 44   |

|     | 5.4.5          | Outbound request/Inbound completion                                               | 47   |

|     | 5.4.6          | Inbound request/Outbound completion                                               | 49   |

| 5.5 | Order          | ng and overtaking rules - quick reference                                         | 52   |

| 5.6 | IDO ar         | d RO for Outbound PCIe transactions                                               | 53   |

|     | 5.6.1          | Root-SoC                                                                          | 53   |

|     | 5.6.2          | Endpoint-SoC                                                                      | 53   |

|     | Topolo         | ogy Considerations                                                                | 54   |

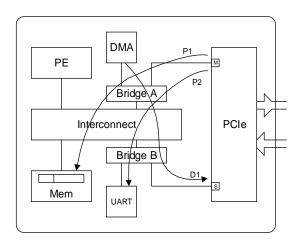

| 6.1 | Bridge         | Topology Considerations                                                           | 54   |

|     | 6.1.1          | Bridge A                                                                          | 54   |

|     | 6.1.2          | Bridge B                                                                          | 55   |

| 6.2 | IO Coł         | erent PCIe Traffic                                                                | 55   |

| 6.3 | Interm         | ediate Components                                                                 | 56   |

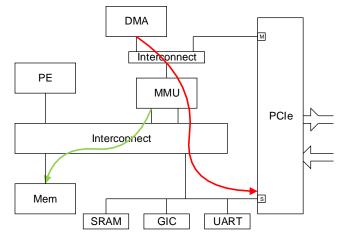

|     | 6.3.1          | System MMU and PCIe Example                                                       | 57   |

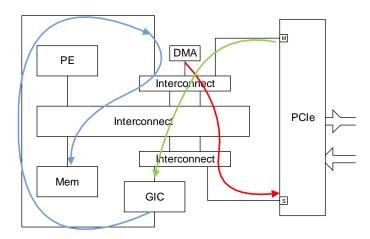

|     | 6.3.2          | GIC and PCIe Example                                                              | 57   |

6

# About this document

# **Release Information**

The change history table lists the changes that have been made to this document.

| Date     | Version | Confidentiality  | Change                                                                                                                                                                            |

|----------|---------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Feb 2022 | 1.0     | Non-Confidential | First release of 1.0 ALP version – This is a comprehensive update of the 0.7 version dated 04/06/2013 (ARM-EPM-033524).                                                           |

|          |         |                  | Key changes:                                                                                                                                                                      |

|          |         |                  | <ol> <li>Updated the requirements to be in accordance<br/>with the specifications listed in References<br/>section.</li> </ol>                                                    |

|          |         |                  | <ol><li>Updated terminology to be in accordance with<br/>the specifications listed in References section.</li></ol>                                                               |

|          |         |                  | <ol> <li>Added IDO and RO related recommendations<br/>and requirements.</li> </ol>                                                                                                |

|          |         |                  | <ol> <li>Restructured the content to bring all Arm<br/>memory model related content into section 4<br/>and all PCIe ordering model related content<br/>into section 5.</li> </ol> |

## PCIe AMBA Integration Guide

Copyright ©2022 Arm Limited or its affiliates. All rights reserved. The copyright statement reflects the fact that some draft issues of this document have been released, to a limited circulation.

Arm Non-Confidential Document Licence ("Licence")

This Licence is a legal agreement between you and Arm Limited ("Arm") for the use of Arm's intellectual property (including, without limitation, any copyright) embodied in the document accompanying this Licence ("Document"). Arm licenses its intellectual property in the Document to you on condition that you agree to the terms of this Licence. By using or copying the Document you indicate that you agree to be bound by the terms of this Licence.

"Subsidiary" means any company the majority of whose voting shares is now or hereafter owner or controlled, directly or indirectly, by you. A company shall be a Subsidiary only for the period during which such control exists.

This Document is NON-CONFIDENTIAL and any use by you and your Subsidiaries ("Licensee") is subject to the terms of this Licence between you and Arm.

Subject to the terms and conditions of this Licence, Arm hereby grants to Licensee under the intellectual property in the Document owned or controlled by Arm, a non-exclusive, non-transferable, non-sub-licensable, royalty-free, worldwide licence to:

(i) use and copy the Document for the purpose of designing and having designed products that comply with the Document;

(ii) manufacture and have manufactured products which have been created under the licence granted in (i) above; and

(iii) sell, supply and distribute products which have been created under the licence granted in (i) above.

Licensee hereby agrees that the licences granted above shall not extend to any portion or function of a product that is not itself compliant with part of the Document.

Except as expressly licensed above, Licensee acquires no right, title or interest in any Arm technology or any intellectual property embodied therein.

THE DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. Arm may make changes to the Document at any time and without notice. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

NOTWITHSTANING ANYTHING TO THE CONTRARY CONTAINED IN THIS LICENCE, TO THE FULLEST EXTENT PETMITTED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, IN CONTRACT, TORT OR OTHERWISE, IN CONNECTION WITH THE SUBJECT MATTER OF THIS LICENCE (INCLUDING WITHOUT LIMITATION) (I) LICENSEE'S USE OF THE DOCUMENT; AND (II) THE IMPLEMENTATION OF THE DOCUMENT IN ANY PRODUCT CREATED BY LICENSEE UNDER THIS LICENCE). THE EXISTENCE OF MORE THAN ONE CLAIM OR SUIT WILL NOT ENLARGE OR EXTEND THE LIMIT. LICENSEE RELEASES ARM FROM ALL OBLIGATIONS, LIABILITY, CLAIMS OR DEMANDS IN EXCESS OF THIS LIMITATION.

This Licence shall remain in force until terminated by Licensee or by Arm. Without prejudice to any of its other rights, if Licensee is in breach of any of the terms and conditions of this Licence then Arm may terminate this Licence immediately upon giving written notice to Licensee. Licensee may terminate this Licence at any time. Upon termination of this Licence by Licensee or by Arm, Licensee shall stop using the Document and destroy all

copies of the Document in its possession. Upon termination of this Licence, all terms shall survive except for the licence grants.

Any breach of this Licence by a Subsidiary shall entitle Arm to terminate this Licence as if you were the party in breach. Any termination of this Licence shall be effective in respect of all Subsidiaries. Any rights granted to any Subsidiary hereunder shall automatically terminate upon such Subsidiary ceasing to be a Subsidiary.

The Document consists solely of commercial items. Licensee shall be responsible for ensuring that any use, duplication or disclosure of the Document complies fully with any relevant export laws and regulations to assure that the Document or any portion thereof is not exported, directly or indirectly, in violation of such export laws.

This Licence may be translated into other languages for convenience, and Licensee agrees that if there is any conflict between the English version of this Licence and any translation, the terms of the English version of this Licence shall prevail.

The Arm corporate logo and words marked with <sup>®</sup> or <sup>™</sup> are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. No licence, express, implied or otherwise, is granted to Licensee under this Licence, to use the Arm trade marks in connection with the Document or any products based thereon. Visit Arm's website at https://www.arm.com/company/policies/trademarks for more information about Arm's trademarks.

The validity, construction and performance of this Licence shall be governed by English Law.

Copyright © 2022 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

Arm document reference: LES-PRE-21585 version 4.0

### References

| Ref | Document Number               | Title                                                                                     |

|-----|-------------------------------|-------------------------------------------------------------------------------------------|

| 1   | ARM IHI 0022G<br>(ID073019)   | AMBA <sup>®</sup> AXI and ACE<br>Protocol Specification                                   |

| 2   | ARM DDI 0487E.a<br>(ID070919) | Arm <sup>®</sup> Architecture Reference Manual<br>Armv8, for Armv8-A architecture profile |

| 3   |                               | PCI Express <sup>®</sup> Base Specification Revision 5.0<br>Version 1.0                   |

| 4   |                               | PCI Local Bus Specification Revision 3.0                                                  |

This document refers to the following documents.

### **Terms and abbreviations**

This document uses the following terms and abbreviations.

Term Meaning

### **Potential for change**

The contents of this specification are subject to change. In particular, the following may change:

- Feature addition, modification, or removal

- Parameter addition, modification, or removal

- Numerical values, encodings, bit maps

### Conventions

### Typographical conventions

The typographical conventions are:

italic

Introduces special terminology and denotes citations.

bold

Denotes signal names, and is used for terms in descriptive lists, where appropriate.

monospace

Used for assembler syntax descriptions, pseudocode, and source code examples.

Also used in the main text for instruction mnemonics and for references to other items appearing in assembler syntax descriptions, pseudocode, and source code examples. SMALL CAPITALS

Used for some common terms such as IMPLEMENTATION DEFINED.

Used for a few terms that have specific technical meanings, and are included in the Glossary.

#### Red text

Indicates an open issue.

#### Blue text

Indicates a link. This can be

- A cross-reference to another location within the document

- A URL, for example http://infocenter.arm.com

#### Numbers

Numbers are normally written in decimal. Binary numbers are preceded by 0b, and hexadecimal numbers by 0x.

In both cases, the prefix and the associated value are written in a monospace font, for example  $0 \times FFFF0000$ . To improve readability, long numbers can be written with an underscore separator between every four characters, for example  $0 \times FFFF_0000\_0000\_0000$ . Ignore any underscores when interpreting the value of a number.

### **Current status and anticipated changes**

Alpha version. Changes expected.

### Feedback

Arm welcomes feedback on its documentation.

### Feedback on this book

If you have comments on the content of this book, send an e-mail to errata@arm.com . Give:

- The title (PCIe AMBA integration guide).

- The number and issue (ARM DEN 0114 ALP 1.0).

- The page numbers to which your comments apply.

- The rule identifiers to which your comments apply, if applicable.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

# **1** Introduction

## **1.1 Introduction**

This document is intended to provide guidance on PCIe interface integration into an AMBA based System-On - Chip (SoC). It is assumed that the PCIe interface is connected to the rest of the SoC through an AXI or ACE protocol-based interconnect. The reader is assumed to be conversant with the PCIe, AMBA AXI and AMBA ACE protocols and Arm architecture.

The document covers the following topics:

- Description of Terminologies used in this document.

- Guidance on Arm memory type usage for PCIe transactions.

- How to comply with Arm Memory Model Requirements for PCIe transactions from Arm Processing Elements (PEs).

- How to comply with PCIe ordering model in an AMBA based system.

- Topology considerations while integrating PCIe interface into an AMBA based system.

# 2 Terminology

## 2.1 Transaction Terminology

A transaction is typically a read or write. The term transaction describes all aspects including the request, any data, and any responses.

In PCIe a transaction is made up of one or more packets. Each packet travels in one direction only.

In AMBA a transaction is made up of one or more transfers. Each transfer travels in one direction only.

An AMBA transfer is synonymous with a PCIe packet.

## 2.2 Arm Terminology

This document will use terminology as defined in the Arm Architecture Reference Manual [2] for describing the memory type and other memory attributes. This document does not attempt to give a full definition of all the memory types that can be used but gives an overview and describes the different terminology that is used. In keeping with the AMBA AXI and ACE focus of this document, the mapping of Arm memory types and memory attributes to AXI and ACE attributes is provided in sections 3.2 and 3.3.3.

Note: In this document, the term "AMBA interconnect" stands for an AXI or ACE protocol-based interconnect.

In Arm architecture, memory types can be broadly divided into Device memory types and Normal memory [see section B2.7 in [2]].

### 2.2.1 Device memory

Arm architecture defines the following attributes for Device memory:

| Early Write Acknowledgment - | An early acknowledgement for a write transaction can be given before the transaction reaches the peripheral. |

|------------------------------|--------------------------------------------------------------------------------------------------------------|

| Reordering –                 | Transactions to the same peripheral can be re-ordered with respect to each other.                            |

| Gathering –                  | Multiple transactions can be merged into a single transaction.                                               |

Note: Speculative access to Device memory type is never permitted.

The Device memory types in ARMv8 are:

ARMv8 Memory Type Definition

| Device-nGnRnE | No Early Write Acknowledgement<br>No Reordering<br>No Gathering |

|---------------|-----------------------------------------------------------------|

| Device-nGnRE  | Early Write Acknowledgement<br>No Reordering<br>No Gathering    |

| Device-nGRE   | Early Write Acknowledgement<br>Reordering<br>No Gathering       |

| Device-GRE    | Early Write Acknowledgement<br>Reordering<br>Gathering          |

|               |                                                                 |

For accesses to Device memory, the table below shows the different terminology used in ARM v8 and AMBA.

| ARMv8         | AMBA AXI and ACE                                                                                                 | Key characteristics of the Arm memory type.                                                                                                                                                                                    |

|---------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device-nGnRnE | Device Non-bufferable<br>(AxCACHE = 0b0000).<br>Same AXI ID.<br>(See Note below)                                 | Response comes from target peripheral.<br>Transactions to the same peripheral must<br>remain in order.                                                                                                                         |

| Device-nGnRE  | Device Bufferable<br>(AxCACHE = 0b0001)<br>Same AXI ID.<br>(See Note below)                                      | Early response is permitted before the<br>transaction has reached the peripheral.<br>(Typically, this only relates to write<br>transactions.)<br>Transactions to the same peripheral must<br>remain in order.                  |

| Device-nGRE   | Device Bufferable<br>(AxCACHE = 0b0001)<br>Re-ordering is not<br>explicit. It is implied by<br>different AXI ID. | Early response is permitted.<br>Transactions to the same peripheral can be re-<br>ordered.                                                                                                                                     |

| Device-GRE    | Not supported.<br>Will be treated as<br>Device-nGRE.                                                             | Early response is permitted.<br>Transactions to the same peripheral can be re-<br>ordered.<br>Multiple transactions to the same peripheral<br>can be merged into a single transaction.<br>Note: Since AXI/ACE does not support |

|               |                                                                                                                  | gathering, any merging must be done prior to<br>the transaction entering the AXI/ACE<br>interconnect.                                                                                                                          |

Note: In AXI using the same AXI ID does not ensure ordering between read and write transactions. To ensure this ordering it is necessary to wait for a response to an early transaction before issuing the later transaction.

Note: Where it is stated that order is achieved using the same AXI ID, it is also possible to obtain order by ensuring that the later transaction is only issued once the earlier transaction has completed. The later transaction can then be issued using a different AXI ID.

### 2.2.2 Normal memory

Normal memory has two key attributes:

Shareability – Determines the agents/observers in a system that access the same address region.

Cacheability – Determines if it is permitted to allocate a memory location in a given cache and, if it can be allocated, whether the line is permitted to be dirty (Write-Back) or must be clean (Write-Through).

Shareability can be one of:

- Non-shareable

- Inner Shareable

- Outer Shareable

Cacheability can be one of:

- Normal Non-cacheable

- Normal Write-Through Cacheable

- Normal Write-Back Cacheable

Cacheability can be defined for both Inner and Outer caches. Inner caches are expected to be within a PE cluster and only the Outer cache memory type is exposed on an AMBA interface. The terms Inner and Outer when used for cacheability are different from the terms Inner and Outer when used for shareability – this is a common source of confusion.

For the purposes of this document Inner Cacheability is assumed to be the same as Outer Cacheability. No further use will be made of the terms Inner and Outer to refer to Cacheability and any reference to Inner and Outer later in this document refers to shareability.

For the purposes of this document it is assumed that Write-Through Cacheable is not supported. This is common for most Arm processor implementations.

The combination of Inner Shareable and Non-cacheable is not a supported combination. This is because Inner Shareable implies that the location can be held in the cache of another component, so the memory type (that must be compatible between components) cannot be non-cacheable.

If all observers (i.e. requesters) in an Outer Shareable domain are also in the same Inner Shareable domain, then there is no difference between Inner Shareable and Outer Shareable.

For the rest of this document, Inner Shareable is not considered due to the following reasons:

- The difference between Inner and Outer Shareable is deprecated in ACE5, ACE5-Lite, ACE5-LiteDVM, ACE5-LiteACP [see section F5.1 of [1]].

- The requirements for Inner Shareable and Outer Shareable are identical and the difference between Inner and Outer Shareable is only in the number of agents that need to be snooped.

- It is expected that for majority of systems, the Inner and Outer Shareability domains will have the same set of observers. In such cases, the software visible behaviour would be the same regardless of whether shareability attribute is programmed as Inner Shareable or Outer Shareable.

Note: In some AMBA documents, the word "Snoopable" is used instead of "Shareable". In this document, the word "Shareable" is used throughout.

The table below shows the supported combinations of cacheability and shareability that need to be considered.

| Cacheability         | Shareability    |  |

|----------------------|-----------------|--|

| Non-cacheable        | Outer Shareable |  |

| Write-Back Cacheable | Non-Shareable   |  |

| Write-Back Cacheable | Inner Shareable |  |

| Write-Back Cacheable | Outer Shareable |  |

|                      |                 |  |

The mapping of permitted combinations of Arm memory type, cacheability and shareability attribute to AMBA AXI attributes [see table A4-5 in section A4.4 of [1]] and ACE attributes [see table D3-3 in section D3.1.1 of [1]] is given in section 3.3 for Inbound transactions and in section 3.2 for Outbound transactions.

### 2.3 PCIe Terminology

The PCIe specification [3] defines the following terminology:

| Term                                              | Definition                                                                                                                                                                                                                            |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Downstream                                        | <ol> <li>The relative position that is farther from the Root<br/>Complex.</li> <li>A direction of information flow where the<br/>information is flowing away from the Root Complex.</li> </ol>                                        |

| Upstream                                          | <ol> <li>The relative position that is closer to the Root<br/>Complex.</li> <li>A direction of information flow where the<br/>information is flowing towards the Root Complex.</li> </ol>                                             |

| Transmitting Port                                 | The Port that transmits the Packet on a given Link.                                                                                                                                                                                   |

| Receiving Port                                    | The Port that receives the Packet on a given Link.                                                                                                                                                                                    |

| Egress Port                                       | The Transmitting Port: that is, the Port that sends outgoing traffic.                                                                                                                                                                 |

| Ingress Port                                      | The Receiving Port: that is, the Port that accepts incoming traffic.                                                                                                                                                                  |

| Completer                                         | The PCIe function that completes a request (usually the destination of the request).                                                                                                                                                  |

| Relaxed Ordering (RO) and ID based ordering (IDO) | These are packet attribute fields defined in the PCIe specification. The value of these attributes influences the order in which requests and completions arrive at the destination. Refer to the PCIe specification for details [3]. |

| Process Address Space ID (PASID). | This is an ID that used to identify the address space of a transaction. Refer to the PCIe specification for details [3].                             |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fabric                            | A PCIe fabric is composed of point-to-point Links that interconnect a set of components (Endpoints, Switches and Root Complex) [section 1.3 of [3]]. |

This document will use the following terminology to describe the different aspects of a transaction.

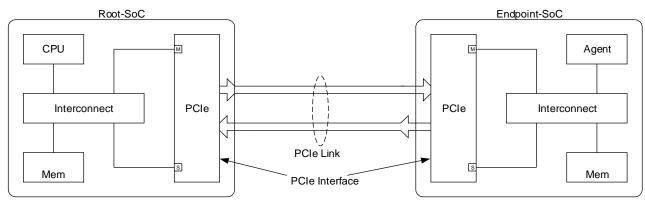

- PCIe Interface is used to describe the IP block that interfaces between an on-chip AMBA system and a PCIe Link. A PCIe Interface will have both AMBA Manager (M) and Subordinate (S) ports. A PCIe Interface could be either a Root Complex or an Endpoint in the PCIe domain.

- Root-SoC is used to describe the SoC that contains the PCIe Root Complex.

- Endpoint-SoC is used to describe an SoC that contains a PCIe Endpoint.

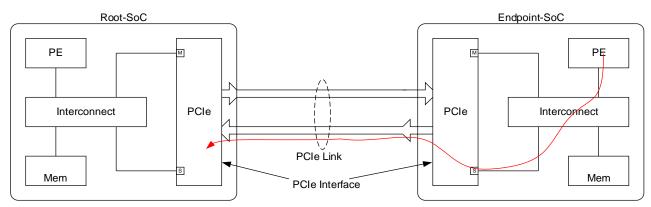

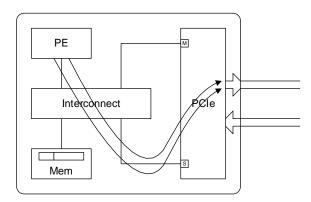

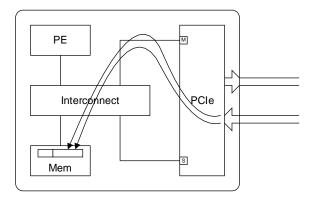

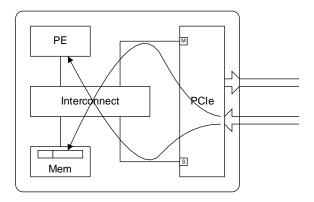

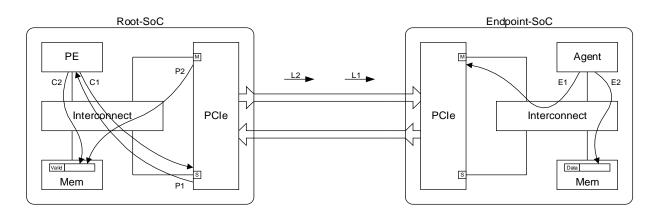

Figure 1 below illustrates the PCIe interface in Root-SoC and Endpoint-SoC

Figure 1 PCIe Interface in Root-SoC and Endpoint-SoC

For this document, PCIe switches are not considered.

### 2.3.1 Inbound and Outbound

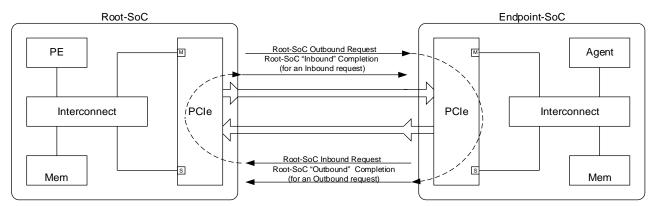

The terms Outbound and Inbound are used to describe a transaction.

An Outbound transaction has an Outbound Request and (optionally) an Outbound Completion, which returns in the opposite direction. Note that in the case of a completion "Outbound" refers to the direction of the original transaction request, not the direction of the completion.

Likewise, an Inbound transaction has an Inbound Request and (optionally) an Inbound Completion, which returns in the opposite direction. Note that in the case of a completion "Inbound" refers to the direction of the original transaction request, not the direction of the completion.

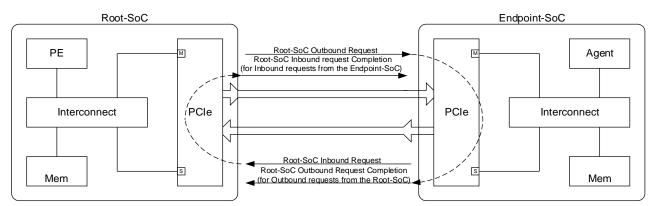

For a Root-SoC, containing the PCIe Root Complex:

An Outbound Request travels downstream to the Endpoint.

An Outbound Completion returns upstream to the Root Complex.

An Inbound Request travels upstream to the Root Complex.

An Inbound Completion returns downstream to the Endpoint.

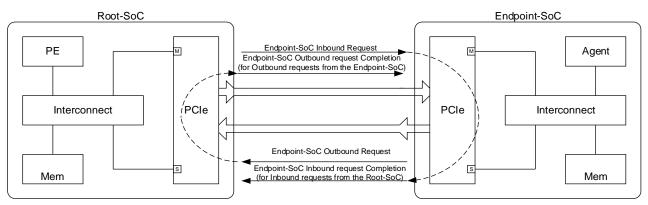

For an Endpoint-SoC:

An Outbound Request travels upstream to the Root Complex.

An Outbound Completion returns downstream to the Endpoint.

An Inbound Request travels downstream to the Endpoint.

An Inbound Completion returns upstream to the Root Complex.

Note: Care is required when using the terms "upstream" and "downstream". For example, "arrives from upstream" is the same as "travels downstream".

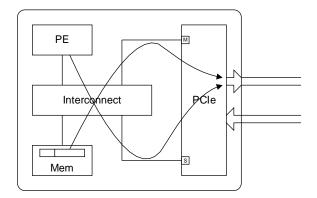

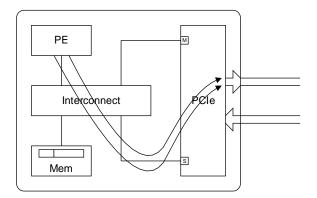

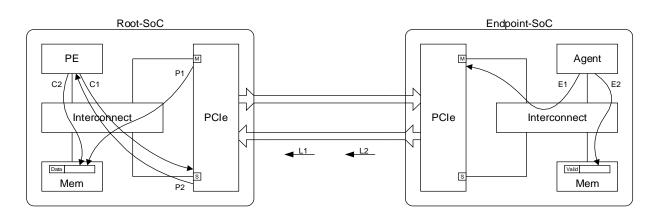

The Figure 2 below shows Inbound and Outbound traffic for a Root-SoC.

Figure 2 Inbound and Outbound traffic for a Root-SoC

All the examples given in this document are described from the perspective of the Root-SoC.

# 3 ARM Memory Type USAGE FOR INBOUND AND OUTBOUND PCIE transactions

### 3.1 Memory Type Assumptions

The following assumptions are made about the memory type for all transactions.

- The cacheability of the memory type is the same for all levels of cache. The allocation hints may differ, but the architectural requirements of the memory type are the same.

- Write-Through Cacheable is not supported.

### 3.2 Outbound Transaction Memory Type

All Outbound transactions destined for PCIe will have one of the following Arm memory type attributes:

- Device-nGnRnE

- Device-nGnRE

- Device-nGRE

- Device-GRE

- Normal Non-cacheable

Use of any cacheable memory type is **not** expected for Outbound transactions. Cache maintenance would be required to ensure visibility of transactions.

Use of cacheable memory is expected for Inbound transaction, see section 3.3 for further details.

Table below shows the mapping of Arm memory type to AMBA AXI and ACE memory attributes for Outbound transactions.

| Arm memory type and<br>cacheability attribute of the<br>Outbound transaction | Outbound Transaction AXI<br>Memory attributes<br>(AxCACHE) | Outbound Transaction ACE<br>memory attributes (AxCACHE)<br>and shareability domain<br>(AxDOMAIN) |

|------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Device-nGnRnE                                                                | Device Non-bufferable                                      | Device Non-bufferable, System                                                                    |

| Device-nGnRE or Device-nGRE<br>or Device-GRE                                 | Device Bufferable                                          | Device Bufferable, System                                                                        |

| Normal, Non-cacheable                                                        | Normal Non-cacheable<br>Bufferable                         | Normal Non-cacheable<br>Bufferable, System                                                       |

# **3.3 Inbound Transaction Memory Type**

Inbound transactions from the PCIe interface must have appropriate AXI or ACE memory attributes. It is expected that these attributes are derived in a three-step process as follows:

- Step 1: The Arm memory type, Cacheability and Shareability attributes of the Inbound transaction is determined.

- Step 2: If required, the Cacheability attribute determined in step 1 is overridden based on the transaction's No Snoop bit value.

- Step 3: The Arm memory type and Shareability attribute from step 1 and the cacheability attribute from step 2 is used to determine the AXI or ACE memory attributes of the Inbound transaction.

### 3.3.1 Step 1: Determining the Arm memory type, cacheability and shareability attributes

For deriving the Arm memory type, cacheability and shareability, the following configurations need to be considered:

1. The PCIe interface has an associated System Memory Management Unit (MMU) and the System MMU is enabled to provide translations:

In this case, the System MMU must be accessed to get the Arm memory type, cacheability and shareability attributes of the transaction.

2. PCIe interface does not have an associated System MMU or the System MMU is bypassed or disabled:

In this configuration, the PCIe interface must be able to determine the Arm memory type, cacheability and shareability attributes of the location an Inbound transaction is targeting. Typically, this can be done using a primitive address decode to associate specific address ranges with specific Arm memory type, cacheability and shareability attributes. It is expected that this association is configurable to allow maximum flexibility.

It is expected that the Arm memory type for a location that is in a peripheral is determined based on the properties of the location, as defined in the Arm Architecture reference manual [see section B2.7.1 and B2.7.2 of [2]].

It is strongly recommended that DRAM memory is mapped as Normal memory with Write-Back as the cacheability attribute.

Note: The constraint to be considered while setting the memory type of a location is that the weakest memory type that can be used is determined by the properties of the location. It is permitted to use a stronger memory type although it might not be performance optimal.

### 3.3.2 Step 2: Modifying the cacheability attribute based on the transaction's No Snoop bit value

The "No Snoop" bit is a transaction attribute provided by PCIe specification for a requester to indicate whether hardware coherency management is expected or not [see section 2.2.6.5 and 7.5.3.4 of [3]].

For an SoC with software visible caches, the cacheability attribute of the transaction must be forced to Noncacheable if "No Snoop" bit for the transaction is 1 and the Arm memory type (determined in step 1) is Normal.

For an SoC where all caches are software invisible, it is strongly recommended that cacheability attribute of the transaction is set to Non-cacheable if "No Snoop" bit for the transaction is 1 and the Arm memory type (determined in step 1) is Normal.

In both cases, if the "No Snoop" bit is 0, then the cacheability attribute from step 1 is retained.

# **3.3.3** Step 3: Mapping the Arm memory type, cacheability and shareability attributes to AXI/ACE memory attributes.

In this step, Arm memory type and shareability attributes from Step 1 and the cacheability attribute from step 2 is mapped to AXI or ACE memory attributes prior to issuing into the AMBA interconnect.

The table below provides the mapping information:

- AMBA AXI memory attribute [see table A4-5 in section A4.4 of [1]] for the transaction given its final Arm memory type, cacheability attribute, shareability attribute.

- AMBA ACE memory attributes [see table D3-3 in section D3.1.1 of [1]] for the transaction given its final Arm memory type, cacheability attribute, shareability attribute.

Note: As explained in section 2.2.2, this section only considers Outer Shareable.

| Inbound PCIe<br>transaction: Arm<br>memory type,<br>cacheability and<br>shareability attributes<br>(after Step 2) | PCIe Transaction AXI Memory<br>attribute (excluding the<br>allocate attributes) | PCIe Transaction ACE<br>memory attribute<br>(excluding the allocate<br>attributes) and<br>shareability domain |

|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Device-nGnRnE                                                                                                     | Device Non-bufferable                                                           | Device Non-bufferable,<br>System                                                                              |

| Device-nGnRE or<br>Device-nGRE or Device-<br>GRE                                                                  | Device Bufferable                                                               | Device Bufferable, System                                                                                     |

| Normal, Write-Back,<br>Outer Shareable                                                                            | WriteBack                                                                       | WriteBack, Outer<br>Shareable                                                                                 |

| Normal, Non-<br>cacheable, Outer<br>Shareable                                                                     | Normal Non-cacheable,<br>Bufferable                                             | Normal Non-cacheable<br>Bufferable, System                                                                    |

### 3.3.4 Coherency management for Inbound transactions

For an Inbound PCIe transaction, the table below provides the following information:

- For a given location, possible combinations of the Inbound PCIe transaction attributes (after step 2 see section 3.3.2) and PE side attributes for exchanging data between Software running on a PE and a PCIe Requester.

- Whether or not software cache maintenance is required to maintain coherency.

- The AXI and ACE attributes corresponding to the Inbound PCIe transaction attributes.

- Note: As explained in section 2.2.2, this section only considers Outer Shareable.

| PE transaction:<br>Arm memory type,<br>cacheability and<br>shareability<br>attributes | Inbound PCIe<br>transaction: Arm<br>memory type,<br>cacheability and<br>shareability<br>attributes (after<br>step 2 -i.e. after<br>considering No<br>Snoop attribute) | Coherency Management                                                                                                                                                     | PCIe<br>Transaction AXI<br>Memory<br>attribute<br>(excluding the<br>allocate<br>attributes) | PCIe Transaction<br>ACE memory<br>attribute<br>(excluding the<br>allocate<br>attributes) and<br>shareability<br>domain |

|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Normal, Write-<br>Back, Outer<br>Shareable                                            | Normal, Write-<br>Back, Outer<br>Shareable                                                                                                                            | Hardware managed.                                                                                                                                                        | WriteBack                                                                                   | WriteBack, Outer<br>Shareable                                                                                          |

| Normal, Write-<br>Back, Non-<br>shareable                                             | Normal, Write-<br>Back, Outer<br>Shareable                                                                                                                            | Software cache<br>maintenance (This<br>assumes that PE<br>transaction looks up the<br>cache in which PCIe<br>transaction might be<br>cached).                            | WriteBack                                                                                   | WriteBack, Outer<br>Shareable                                                                                          |

| Normal, Non-<br>cacheable, Outer<br>Shareable                                         | Normal, Write-<br>Back, Outer<br>Shareable                                                                                                                            | Not permitted unless all<br>caches in the system are<br>invisible to software.<br>With software invisible<br>caches, hardware would<br>ensure coherence.                 | WriteBack                                                                                   | WriteBack, Outer<br>Shareable                                                                                          |

| Normal, Write-<br>Back, Outer<br>Shareable                                            | Normal, Non-<br>cacheable, Outer<br>Shareable                                                                                                                         | Software cache<br>maintenance unless all<br>caches in the system are<br>invisible to software.<br>With software invisible<br>caches, hardware would<br>ensure coherence. | Normal Non-<br>cacheable,<br>Bufferable                                                     | Normal Non-<br>cacheable<br>Bufferable,<br>System                                                                      |

| Normal, Write-<br>Back, Non-<br>shareable                                             | Normal, Non-<br>cacheable, Outer<br>Shareable                                                                                                                         | Software cache<br>maintenance                                                                                                                                            | Normal Non-<br>cacheable,<br>Bufferable                                                     | Normal Non-<br>cacheable<br>Bufferable,<br>System                                                                      |

| Normal, Non-<br>cacheable, Outer<br>Shareable                                         | Normal, Non-<br>cacheable, Outer<br>Shareable                                                                                                                         | Not cached.                                                                                                                                                              | Normal Non-<br>cacheable,<br>Bufferable                                                     | Normal Non-<br>cacheable<br>Bufferable,<br>System                                                                      |

For a location which is mapped as one of the Device memory types for both the PE transaction and the PCle Inbound transaction, there is no hardware or software cache maintenance required as Device memory type locations are never cached. The Device memory type assigned to the location on the PE side can be different from the Device memory type assigned to the location on the PCle Inbound side. However, software (or a combination of software and firmware) is responsible for ensuring that both PE transaction and PCle Inbound transaction uses a Device memory type that matches with the properties of the target location.

It is expected that software (or the combination of software and firmware) will not map a location as Normal memory for the PE transaction and map the same location as Device memory for the PCIe Inbound transaction. Similarly, it is expected that software (or the combination of software and firmware) will not map a location as Device memory for the PE transaction and map the same location as Normal memory for the PCIe Inbound transaction. If software (or the software-firmware combination) behaves contrary to these expectations, then it is software's (or the software-firmware combination's) responsibility to manage the errors that can happen due to such a mapping.

Note: With software invisible caches, the assumption is that hardware would ensure coherence by accessing the caches regardless of the cacheability and shareability attributes.

# 4 COMPLYING TO ARM memory model FOR PE GENERATED PCIE TRANSACTIONs

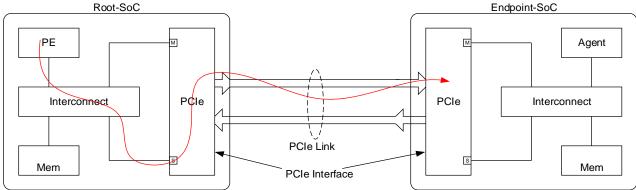

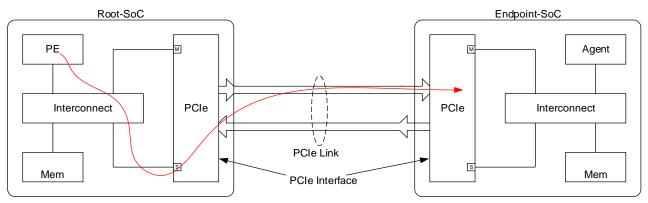

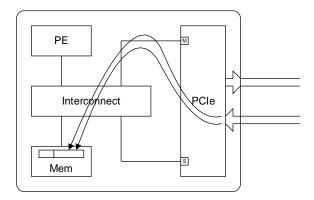

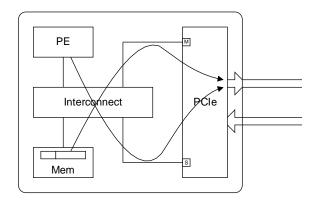

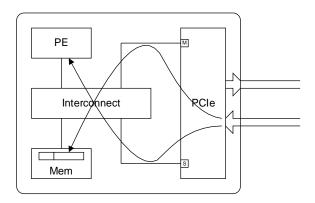

PE generated PCIe transactions are Outbound transactions as shown in Figure 3 for a Root-SoC and as shown in Figure 4 for an Endpoint-SoC.

This section describes the following:

- Arm memory type mapping options for PCIe address spaces.

- Requirements that the PCIe interface, the SoC interconnect and the PE must meet to preserve Arm memory model's guarantees.

- End to end ordering guarantees provided by the system for a PE request targeting a PCIe completer.

Figure 3 PE generated PCIe transaction in a Root-SoC

Figure 4 PE generated PCIe transaction in an Endpoint-SoC

From a PE perspective, all memory locations in a PCIe completer will be mapped in the PE's translation tables as one of the following:

- Device-nGnRnE.

- Device-nGnRE.

- Device-nGRE.

- Device-GRE.

- Normal with Non-cacheable as the cacheability attribute.

Sections 4.1,4.2 and 4.3 details the requirements to be met for preserving the guarantees given to software for each Arm memory type.

### 4.1 Device-nGnRnE and Device-nGnRE

For Device-nGnRnE and Device-nGnRE memory types, the Endpoint arrival order must match program order and read speculation is not permitted.

The nGnRnE memory type can be used to target the configuration, prefetchable and non-prefetchable PCIe address spaces.

The nGnRE memory type can be used to target the prefetchable and non-prefetchable PCIe address spaces.

Note: Writes to prefetchable and non-prefetchable memory space of a PCIe completer are posted- i.e. the completer will not send a response back to the requester. Despite the lack of an explicit response back from the completer, the Arm architecture permits mapping the prefetchable and non-prefetchable memory spaces as Device-nGnRnE [see section E.2.7.2 of [2]]. There are no restrictions on mapping the prefetchable and non-prefetchable and non-prefetchable memory spaces as Device-nGnRE.

# **4.1.1** PE and Interconnect requirements for handling Outbound requests to Device-nGnRnE or Device-nGnRE mapped locations

For ensuring that Device-nGnRnE and Device-nGnRE memory type works correctly, the PE and the interconnect needs to meet the following requirements:

- Transactions to a location mapped as Device-nGnRnE must have "Device Non-bufferable" as the AXI memory type. For ACE, the memory type is "Device Non-bufferable" with "System" as the shareability domain.

- Transactions to a location mapped as Device-nGnRE must have "Device Bufferable" or "Device Nonbufferable" as the AXI memory type. For ACE, the memory type is "Device Bufferable" or "Device Nonbufferable" with "System" as the shareability domain.

- If there is a read request outstanding to a peripheral, then any new read request to the same peripheral must use the same AXI ID as that of the outstanding read.

- If there is a write request outstanding to a peripheral, then any new write request to the same peripheral must use the same AXI ID as that of the outstanding write.

- Determination of which peripheral region an Outbound PE request falls into is done by implementation defined methods. If such a determination is not possible, then it must be assumed that all Device Bufferable and Device Non-bufferable transactions from a PE are to the same peripheral region and must obey the AXI ID requirements stated above.

- AMBA interconnect does not guarantee any order between read and write transactions. Therefore, to preserve program order between reads and writes, the PE needs to wait for completion of previously issued read transactions to a given peripheral before issuing write transactions to the same peripheral and vice versa.

### 4.1.2 PCIe interface requirements for handling Outbound requests to Device-nGnRnE or DevicenGnRE mapped locations

For the PCIe interface, requests to a Device-nGnRnE mapped location would be received with "Device Nonbufferable" attribute from the AMBA interconnect. Requests to a Device-nGnRE mapped location would be received with "Device Bufferable" attribute from the AMBA interconnect.

On top of being compliant with the PCIe ordering model (see section 5 for the rules) and the AMBA specification [1], the PCIe interface needs to meet the following requirements:

- Read transactions can get re-ordered with respect to program order while traversing the PCIe fabric. Therefore, the PCIe interface must send out a Device Non-bufferable or Device Bufferable read only after completion has been received for earlier read transactions with the same AXI ID targeting the same peripheral region [for definition of peripheral region see section A6.2 of [1]].

- Configuration writes can get re-ordered with respect to program order while traversing the PCIe fabric. Therefore, the PCIe interface must send out a Device Non-bufferable configuration write only after completion has been received for earlier configuration writes with the same AXI ID targeting the same peripheral region.

- Posted writes with Device Bufferable or Device Non-bufferable attribute targeting the same peripheral region (i.e. having the same AXI ID) must not be allowed to overtake each other while transiting through the PCIe interface to the PCIe link.

- Note that this applies even if one write has Device Bufferable attribute and the second write has Device Non-bufferable attribute.

- For configuration writes, the PCIe interface must return the write completion response to the requester only after completion from the PCIe completer has been received.

- RO must not be set for transactions with the Device Bufferable or Device Non-bufferable attribute.

- IDO attribute is not set for any transaction from a PE or if IDO is set for transactions from a PE, then all requests from that PE has the same PCIe Requester ID and same PASID.

- It is expected that PASID will be set only for Outbound transactions from an Endpoint-SoC.

- It is expected that all transactions from a Root-SoC PE would have the same PCIe Requester ID.

### 4.1.3 Example use cases for Device-nGnRnE and Device-nGnRE mapping of PCIe address spaces

The most important use case for Device-nGnRnE mapping is configuration writes. This is illustrated by the following example:

If we imagine a case where software writes to a configuration register and then reads a prefetchable BAR space location whose value depends on the configuration register, then it is important that the software does the read only after it knows that the configuration write has reached the target and is complete. The only way for software to know that a configuration write is complete is to make sure that the configuration write uses the Device-nGnRnE attribute and have a DSB between the configuration write and the read.

Secondly, the Device-nGnRnE and Device-nGnRE types provide the ability to pipeline transactions to PCIe targets even if those transactions need to arrive in program order at the target. This illustrated by the following examples:

- Two read transactions, the first of which is a read from the receive buffer and the second of which is a read from the buffer status register, are required to remain in program order to give the correct behaviour. If the transactions are re-ordered on the PCIe fabric then it would be possible to read a status register which indicates that the receive buffer still contains entries when, in reality, the buffer will be emptied by the read from the receive buffer. In this scenario, if both transactions have the Device-nGnRnE or Device-nGnRE attribute, then they will arrive in program order at the target as desired even if they are pipelined.

- A similar situation exists for two Outbound configuration write requests. An example would be software needing to write to Device Control register to set the Max Payload size of write requests by a Device prior to doing a second configuration write to set the Bus Master Enable bit in the Device's Command register. In this case, it is necessary that the first configuration write arrives at the Device before the second configuration write for correct operation. In this scenario, if both transactions have the Device-nGnRnE attribute, then they will arrive in order program order at the target as desired even if they are pipelined.

### 4.2 Device-nGRE and Device-GRE

For Device-nGRE and Device-GRE memory types, read speculation is not permitted. However, it is permitted for the arrival order of transactions at the destination peripheral to be different from program order except for transactions targeting the same location (see section 4.4).

Any gathering permitted by the Device-GRE memory type must occur prior to entering the AXI or ACE interconnect. This is because AXI and ACE does not support signalling of gathering via attributes.

Device-nGRE memory type can be used to target non-prefetchable and prefetchable PCIe address spaces.

Device-GRE memory type can be used to target prefetchable PCIe address space.

On AXI interconnect, transactions targeting locations mapped with these types will have "Device Bufferable" as the memory type. For ACE, the memory type is "Device Bufferable" and the shareability domain is "System".

The only restriction on usage of AXI IDs is that transactions to the same address must have the same AXI ID if multiple such transactions are outstanding concurrently. The rules for handling two transactions to the same address is given in 4.4.

# **4.2.1** PCIe interface requirements for handling Outbound requests to Device-nGRE and Device-GRE mapped locations

Requests to a Device-nGRE or Device-GRE mapped location would be received with "Device Bufferable" attribute from the AMBA interconnect by the PCIe interface.

On top of being compliant with the PCIe ordering model (see section 5 for the rules) and the AMBA specification [1], the requirements in section 4.4, 4.5 and 4.6 apply.

Note: It is a software error to map configuration space as Device-nGRE or Device-GRE (see section 4.8, note 1). With such a mapping, program order arrival of configuration accesses will not be guaranteed by the system. If configuration space is mapped as Device-nGRE or Device-GRE, the PCIe interface is not expected to send out configuration reads or configuration writes one at a time unless they have the same AXI ID.

### 4.3 Normal with Non-cacheable as the cacheability attribute

For the Normal memory type, read speculation is permitted and the Endpoint arrival order of transactions can be different from program order except for transactions targeting the same location (see section 4.4). It is expected that this memory type is only used to target an address space that is prefetchable.

Transactions targeting Normal memory type locations with Non-Cacheable attribute will have "Normal Non-cacheable Bufferable" as the AXI memory type. For ACE, the memory type is "Normal Non-cacheable Bufferable" and the Shareability domain is "System".

The only restriction on usage of AXI IDs is that transactions to the same address must have the same AXI ID if multiple such transactions are outstanding concurrently. The rules for handling two transactions to the same address is given in 4.4.

# **4.3.1** PCIe interface requirements for handling Outbound requests to Normal Non-cacheable mapped memory locations

Requests to a Normal memory type location with the Non-cacheable attribute would be received with "Normal Non-cacheable Bufferable" attribute from the AMBA interconnect by the PCIe interface.

On top of being compliant with the PCIe ordering model (see section 5 for the rules) and the AMBA specification [1], the requirements in section 4.4,4.5 and 4.6 apply.

Note: It is a software error to map configuration space as Normal Non-cacheable (see section 4.8, note 1). With such a mapping, program order arrival of configuration accesses will not be guaranteed by the system. If configuration space is mapped as Normal Non-cacheable, the PCIe interface is not expected to send out configuration reads or configuration writes one at a time unless they have the same AXI ID.

Note: If software maps non-prefetchable space as Normal Non-cacheable, then it is the responsibility of software to deal with the consequences of speculative accesses to non-prefetchable space. The PCIe interface is not expected to flag an error if a request with "Normal Non-cacheable Bufferable" attribute is targeting the non-prefetchable space. It is expected that the PCIe interface would forward such requests to the completer in the same way as it would forward a "Normal Non-cacheable Bufferable" request targeting the prefetchable space.

## 4.4 Complying with internal visibility requirement of the Arm memory model

Internal visibility requirement of the Arm memory model [see section B2.3.3 of [2]] requires that all accesses from a PE to the same location happens in program order.

To comply with this requirement, the PE and the interconnect must comply with the following requirements:

- If there is a write request outstanding from a PE to a given location, then any new write request to that location from the same PE must use the same AXI ID as that of the outstanding write.

- If there is a read request outstanding from a PE to a given location, then any new read request to that location from the same PE must use the same AXI ID as that of the outstanding read.

- If there is a write request outstanding from a PE to a given location, then any new read request to that location from the same PE must not be issued until the response for the outstanding write request has been received.

• If there is a read request outstanding from a PE to a given location, then any new write request to that location from the same PE must not be issued until the response for the outstanding read request has been received.

# **4.4.1** PCIe interface requirements for complying with internal visibility requirement for Outbound transactions from PEs

The PCIe interface must comply with the following requirements:

• For ensuring that multiple reads from the same location happens in program order:

In this case, the PCIe interface will receive all such reads with the same AXI ID from the AMBA interconnect. Therefore, the rules in section 4.5 applies.

• For ensuring that program order is maintained for multiple writes to the same location:

In this case, the PCIe interface will receive all such writes with the same AXI ID from the AMBA interconnect. Therefore, the rules in section 4.5 applies.

- For ensuring that program order is maintained for a read after write sequence to the same location:

- IDO attribute is not set for any transaction from a requester (e.g. from a PE) or if IDO is set for transactions from a requester, then all requests from that requester has the same PCIe Requester ID and same PASID.

- Note: It is expected that PASID will be set only for Outbound transactions from an Endpoint-SoC.

- Note: It is expected that all transactions from a Root-SoC PE would have the same PCIe Requester ID.

If program order is maintained for a read after write sequence for the same location, then the PE can issue a read transaction before a posted write transaction to the same location has reached its endpoint, as long as the PE has received the write completion response from the PCIe Interface.

• For ensuring that program order is maintained for a write after read sequence to the same location:

The PCIe interface does not need to do anything for ensuring that program order is maintained for a write after read sequence to the same location. The PE must wait till the earlier read has completed before issuing the write.

### 4.5 PCIe interface requirements for handling transactions with the same AXI ID

- Read transactions can get re-ordered with respect to program order while traversing the PCIe fabric. Therefore, an AMBA read transaction must be sent out on PCIe only after completion has been received from the PCIe side for earlier AMBA reads with the same AXI ID.

- Writes with the same AXI ID must not be allowed to overtake each other while transiting through the PCIe interface to the PCIe link.

- RO must not be set for write requests.

- IDO attribute is not set for any transaction from a requester (e.g. from a PE) or if IDO is set for transactions from a requester, then all requests from that requester has the same PCIe Requester ID and same PASID.

- Note: It is expected that PASID will be set only for Outbound transactions from an Endpoint-SoC.