# **Arm Cortex-M23 Processor Datasheet**

# arm

### Datasheet

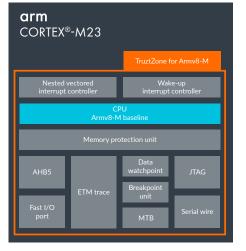

Figure 1: Block diagram of the Cortex-M23 processor

## Overview

The Arm Cortex-M23 processor is a very compact, two-stage pipelined processor that supports the Armv8-M baseline architecture. Cortex-M23 with TrustZone is the ideal processor for the most constrained IoT and embedded applications where security is a key requirement.

TrustZone for Armv8-M provides hardware-enforced isolation between the trusted and the untrusted resources on the Cortex-M23 device, while maintaining the efficient exception handling and determinism that have been the hallmark of all Cortex-M processors.

### **Features**

| Feature                    | Description                                                                                                                                        |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Architecture               | Armv8-M Baseline                                                                                                                                   |  |

| Pipeline                   | 2-stage                                                                                                                                            |  |

| Bus Interface              | AMBA 5 AHB (Von Neumann bus architecture)<br>Optional single-cycle I/O interface                                                                   |  |

| ISA Support                | Thumb/Thumb-2 instruction subset                                                                                                                   |  |

| Software Security          | Optional Arm TrustZone Technology<br>Optional Security Attribution Unit (SAU) of up to 8 regions<br>Stack limit checking for Secure stack pointers |  |

| Memory Protection          | Optional Memory Protection Unit (MPU) with up to 16 regions per security state                                                                     |  |

| Interrupts                 | Non-maskable Interrupt (NMI) and up to 240 physical interrupts with 4 priority levels                                                              |  |

| Wake-up Interrupt<br>(WIC) | Optional for waking up the processor from state retention power gating or when all clocks are stopped                                              |  |

| Sleep Modes                | Integrated Wait For Event (WFE) and Wait For Interrupt (WFI) instructions with Sleep On Exit functionality                                         |  |

| Enhanced Instructions      | Hardware single-cycle (32×32) multiply and fast (32/32) divide option                                                                              |  |

| Debug                      | Optional JTAG and Serial Wire Debug ports<br>Up to 4 Breakpoints and 4 Watchpoints                                                                 |  |

| Trace                      | Optional Embedded Trace Macrocell (ETM) and Micro Trace<br>Buffer (MTB)                                                                            |  |

### About the Processor

The Cortex-M23 processor is a low gate count, two-stage, and highly energy efficient processor. It is intended for microcontroller and deeply embedded applications that require an area optimized, low-power processor for use in environments where security is an important consideration.

The interfaces in the processor for external access include:

- ✤ External AMBA<sup>®</sup> AHB5 interface

- Debug Access Port (DAP)

- ✤ Optional single-cycle I/O port

The processor has optional:

- Arm <u>TrustZone</u> technology, using the Armv8-M Security Extension supporting Secure and Non-secure states

- Secure and Non-secure MPUs which you can configure to protect regions of memory

- Support for ETM and MTB trace

The processor is highly configurable and is intended for a wide range of high-performance, deeply embedded applications that require fast interrupt response features.

# **Block Diagram**

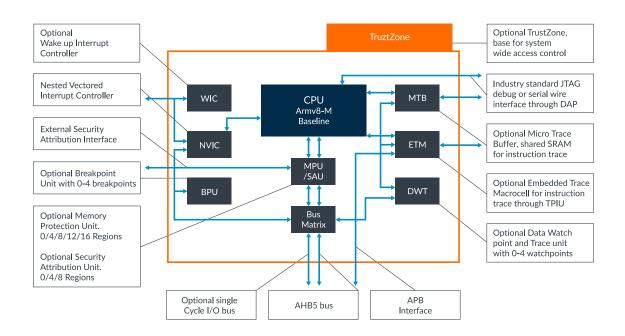

Figure 2: Cortex-M23 processor components

### **Cortex-M23 Components**

### **Processor Overview**

The processor provides:

- + Limited dual-issue of common 16-bit instruction pairs

- ✤ Single cycle 32×32-bit multiplier

- Integer divide unit with support for operand-dependent early termination

- Support for interrupted continuable load and store multiple operations

- ✤ Load and store operations that both support precise bus errors

### **Security Attribution and Memory Protection**

The Cortex-M23 processor supports the Armv8-M Protected Memory System Architecture (PMSA) that provides programmable support for memory protection using software controllable regions.

Memory regions can be programmed to generate faults when accessed inappropriately by unprivileged software reducing the scope of incorrectly written application code. The architecture includes fault status registers to allow an exception handler to determine the source of the fault and to apply corrective action or notify the system.

The Cortex-M23 processor also includes optional support for defining memory regions as Secure or Non-secure, as defined in the Armv8-M Security Extension, and protecting the regions from accesses with an inappropriate level of security.

#### **Nested Vectored Interrupt Controller**

The Nested Vectored Interrupt Controller (NVIC) is closely integrated with the core to achieve low-latency interrupt processing.

Functions of the NVIC include:

- External interrupts, configurable from 1 to 240 with four configurable levels of interrupt priority

- Dedicated NMI input

- Support for both level-sensitive and pulse-sensitive interrupt lines

- + Optional WIC, providing ultra-low power sleep mode support

### **Cross Trigger Interface Unit**

The optional Cross Trigger Interface (CTI) enables the debug logic, MTB, and ETM to interact with each other and with other CoreSight components.

#### **Embedded Trace Macrocell**

- Provides a complete instruction trace solution

- ✤ Configurable by an APB slave

- + For more information see the Arm CoreSight ETM-M23 Technical Reference Manual

#### **Micro Trace Buffer**

- ✤ Provides a simple execution trace capability for the processor

- + Offers a lower-cost alternative that has certain imitations compared to ETM

- + For more information see the Arm CoreSight MTB-M23 Technical Reference Manual

### **External Interfaces**

### AMBA 5 AHB interface

- + Transactions on the AMBA 5 AHB interface are always marked as non-sequential.

- Processor accesses and debug accesses share the same external interface to external AHB peripherals. The processor accesses take priority over debug accesses.

- + Any vendor-specific components can populate this bus.

### Single-cycle I/O port

The processor optionally implements a single-cycle I/O port that provides high-speed access to tightly coupled peripherals, such as General-Purpose I/O (GPIO). The port is accessible both by loads and stores, from the processor and from the debugger. You cannot execute code from the I/O port.

#### **Debug Access Port**

The processor is implemented with either a low gate count Debug Access Port (DAP) or a full CoreSight DAP.

The low gate count DAP provides a Serial Wire or JTAG debug port. It connects to the processor slave port to provide full system-level debug access.

The full CoreSight DAP system enables the processor to provide full multiprocessor debug with simultaneous halt and release cross-triggering capabilities.

For more information on:

- Serial Wire or JTAG debug port, see the ADI v5.1 version of the ARM® Debug Interface Architecture Specification, ADIv5.0 to ADIv5.2.

- + CoreSight DAP, see the Arm<sup>®</sup> CoreSight<sup>™</sup> SoC-400 Technical Reference Manual

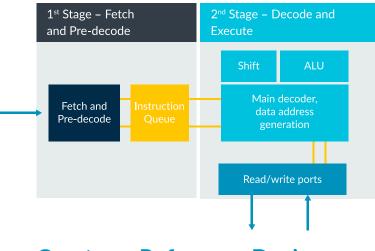

### **Cortex-M23 Pipeline**

# **Corstone Reference Design**

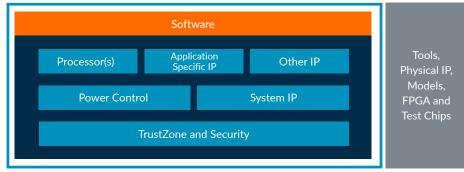

Corstone Reference Designs provide an ideal starting point for any System on Chip (SoC) design, with the lowest risk and development cost. It includes various system IP components and a reference design integrating the processor, security and system IP, as well as having a range of software and development tools available.

Corstone features include:

- + Implementation of an Arm-defined subsystem architecture

- + Integration of the main components

- + Extensively verified

- ✤ Broad software roadmap

- ✤ Build your SoC on top of it

- ✤ Configurable and modifiable

- Tailor it to specific needs

- PSA-certification ready

- Silicon-proven

# arm corstone

Figure 4: Corstone reference design diagram

Figure 3: Cortex-M23

processor pipeline

Separate license required for some IP

### **Processor Configuration Options**

The Cortex-M23 processor has configurable options that you can set during the implementation and integration stages to match your functional requirements.

| Feature                             | Options                                                                                                                                                                                                                                                                                                              |  |  |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <b>T</b> 17                         | No TrustZone for Armv8-M                                                                                                                                                                                                                                                                                             |  |  |

| TrustZone                           | TrustZone for Armv8-M Security Extension                                                                                                                                                                                                                                                                             |  |  |

| Non-secure MPUs                     | 0 region, 4 regions, 8 regions, 12 regions, or 16 regions                                                                                                                                                                                                                                                            |  |  |

| Secure MPUs                         | 0 region, 4 regions, 8 regions, 12 regions, or 16 regions when<br>TrustZone is included                                                                                                                                                                                                                              |  |  |

| SAU                                 | 0 region, 4 regions, or 8 regions when TrustZone is included                                                                                                                                                                                                                                                         |  |  |

| SysTick timers                      | <ul> <li>If the Security Extension is not implemented, can be present<br/>or absent.</li> <li>If the Security Extension is implemented, 0, 1, or 2 SysTick timers<br/>can be present. If only one SysTick timer is present, then software<br/>can configure whether this SysTick is Secure or Non-secure.</li> </ul> |  |  |

| Vector Table Offset Register (VTOR) | <ul> <li>If the Security Extension is not implemented, can be present<br/>or absent.</li> <li>If the Security Extension is implemented, can be either present<br/>or absent for both security states.</li> </ul>                                                                                                     |  |  |

| Reset all registers                 | Present or absent                                                                                                                                                                                                                                                                                                    |  |  |

| Multiplier                          | Fast (one cycle) or slow (32 cycles)                                                                                                                                                                                                                                                                                 |  |  |

| Divider                             | Fast (17 cycles) or slow (34 cycles)                                                                                                                                                                                                                                                                                 |  |  |

| Interrupts                          | External interrupts 1-240                                                                                                                                                                                                                                                                                            |  |  |

| Instruction fetch width             | 16-bit or 32-bit                                                                                                                                                                                                                                                                                                     |  |  |

| Single-cycle I/O port               | Present or absent                                                                                                                                                                                                                                                                                                    |  |  |

| Architectural clock gating present  | When set, architectural clock gating cells are instantiated                                                                                                                                                                                                                                                          |  |  |

| Data endianness                     | Little-endian or byte-invariant big-endian                                                                                                                                                                                                                                                                           |  |  |

| Halting debug support               | Present or absent                                                                                                                                                                                                                                                                                                    |  |  |

| Wake-up interrupt controller        | Supported or not supported                                                                                                                                                                                                                                                                                           |  |  |

| Number of breakpoint comparators    | 0, 1, 2, 3, 4                                                                                                                                                                                                                                                                                                        |  |  |

| Number of watchpoint comparators    | 0, 1, 2, 3, 4                                                                                                                                                                                                                                                                                                        |  |  |

| СТІ                                 | Present or absent                                                                                                                                                                                                                                                                                                    |  |  |

| МТВ                                 | Present or absent                                                                                                                                                                                                                                                                                                    |  |  |

| ETM                                 | Present or absent                                                                                                                                                                                                                                                                                                    |  |  |

| JTAG SW debug protocol              | Selects between JTAG or Serial-Wire interfaces for the DAP                                                                                                                                                                                                                                                           |  |  |

| Multi-drop support for Serial Wire  | Present or absent                                                                                                                                                                                                                                                                                                    |  |  |

| Slave port support for AHB DAP      | When set, includes slave port support for any AHB DAP implementation. Otherwise, supports only the low area DAP.                                                                                                                                                                                                     |  |  |

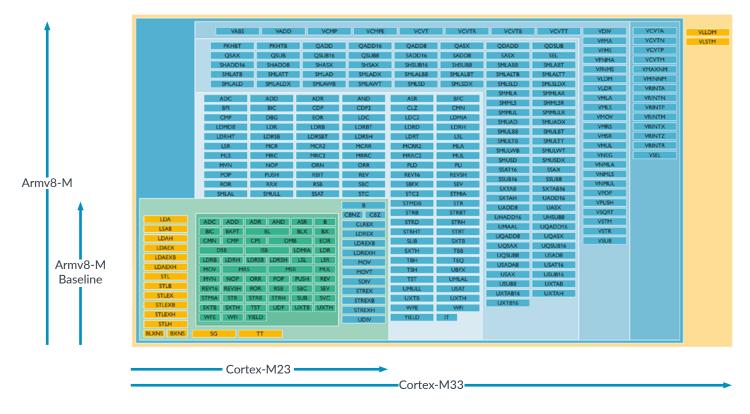

# **Instruction Set**

### New Armv8-M instructions

Figure 5: Instruction set

# Power, Performance and Area

| DMIPS | CoreMark/MHz |

|-------|--------------|

| 0.98  | 2.64         |

| Configuration                    | 40LP<br>Arm SC9 RVT C50 SS<br>0.99V, -40°C |                 | 28HT<br>Arm SC7MC PP140Z SVT HD C40 SSG<br>0.81V 0°C |                 |

|----------------------------------|--------------------------------------------|-----------------|------------------------------------------------------|-----------------|

|                                  | Area<br>mm²                                | Power<br>μW/MHz | Area<br>mm²                                          | Power<br>μW/MHz |

| Minimum<br>Configuration*        | 0.009                                      | 3.86            | 0.004                                                | 2.26            |

| Feature Rich with<br>TrustZone** | 0.034                                      | 8.66            | 0.014                                                | 5.07            |

| Max Freq                                    | 40LP<br>Arm 40LP SC12 RVT C50 SS<br>0.99V, -40°C |

|---------------------------------------------|--------------------------------------------------|

| Feature Rich Configuration with TrustZone** | 155MHz                                           |

\*SECEXT 0; CPIF 0; MPU\_NS 0; MPU\_S 0; SAU 0; NUMIRQ 1; IRQLVL 3; IRQLATENCY 4294967295; IRQDIS 0; DBGLVL 0; ETM 0; MTB 0; MTBAWIDTH 0; WIC 0; WICLINES 0; CTI 0; RAR 0;

\*\*SECEXT 1; CPIF 0; MPU\_NS 8; MPU\_S 8; SAU 0; NUMIRQ 32; IRQLVL 3; IRQLATENCY 4294967295; IRQDIS 0; DBGLVL 2; ETM 1; MTB 0; MTBAWIDTH 0; WIC 1; WICLINES 35; CTI 0; RAR 0;

;

# **Additional Technical documents**

- 1. Cortex-M23 Technical Reference Manual TRM

- 2. Cortex-M23 Integration and Implementation Manual available as part of the Bill of Materials

- 3. Armv8-M Architecture Reference Manual ARM

- 4. CoreSight ETM-M23 Technical Reference Manual ETM

- 5. CoreSight MTB-M23 Technical Reference Manual MTB

### **Glossary of Terms**

| АНВ  | Advanced High-performance Bus           |  |

|------|-----------------------------------------|--|

| АРВ  | Advanced Peripheral Bus                 |  |

| СТІ  | Cross Trigger Interface                 |  |

| ETM  | Embedded Trace Macrocell                |  |

| IDAU | Implementation Defined Attribution Unit |  |

| JTAG | Joint Test Action Group                 |  |

| MPU  | Memory Protection Unit                  |  |

| МТВ  | Micro Trace Buffer                      |  |

| NMI  | Non-maskable Interrupt                  |  |

| NVIC | Nested Vectored Interrupt Controller    |  |

| PMSA | Protected Memory System Architecture    |  |

| PSA  | Platform Security Architecture          |  |

| SAU  | Security Attribution Unit               |  |

| WFE  | Wait for event                          |  |

| WFI  | Wait for interrupt                      |  |

| WIC  | Wake-up Interrupt Controller            |  |

# **Contact details**

#### UK

Salesinfo-eu@Arm.com

**USA** Salesinfo-us@Arm.com Europe

Salesinfo-eu@Arm.com

Salesinfo-us@Arm.com

**Asia Pacific**

### Japan

Salesinfo-eu@Arm.com

### Korea

Salesinfo-us@Arm.com

Taiwan Salesinfo-eu@Arm.com

Israel Salesinfo-us@Arm.com China Salesinfo-eu@Arm.com

### India

Salesinfo-us@Arm.com

# arm

All brand names or product names are the property of their respective holders. Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder. The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given in good faith. All warranties implied or expressed, including but not limited to implied warranties of satisfactory quality or fitness for purpose are excluded. This document is intended only to provide information to the reader about the product. To the extent permitted by local laws Arm shall not be liable for any loss or damage arising from the use of any information in this document or any error or omission in such information.

© Arm Ltd. 2020