# Arm<sup>®</sup> Neoverse<sup>™</sup> N2 reference design

Revision: Release D

## **Technical Overview**

Non-Confidential

Copyright © 2021-2022 Arm Limited (or its affiliates). 102337\_0000\_04\_en

Issue 04

All rights reserved.

## Arm<sup>®</sup> Neoverse<sup>™</sup> N2 reference design

#### **Technical Overview**

Copyright © 2021–2022 Arm Limited (or its affiliates). All rights reserved.

### Release information

#### **Document history**

| Issue   | Date            | Confidentiality  | Change          |

|---------|-----------------|------------------|-----------------|

| 0000-01 | 25 January 2021 | Confidential     | Initial release |

| 0000-02 | 12 May 2021     | Confidential     | Second release  |

| 0000-03 | 4 October 2021  | Confidential     | Third release   |

| 0000-04 | 15 January 2022 | Non-Confidential | Fourth release  |

## **Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND

# REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or ™ are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at https://www.arm.com/company/policies/trademarks.

Copyright © 2021–2022 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

(LES-PRE-20349)

## **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

#### **Product Status**

The information in this document is Final, that is for a developed product.

## **Feedback**

Arm® welcomes feedback on this product and its documentation. To provide feedback on the product, create a ticket on https://support.developer.arm.com

To provide feedback on the document, fill the following survey: https://developer.arm.com/documentation-feedback-survey.

## Inclusive language commitment

Arm values inclusive communities. Arm recognizes that we and our industry have used language that can be offensive. Arm strives to lead the industry and create change.

This document includes language that can be offensive. We will replace this language in a future issue of this document.

To report offensive language in this document, email terms@arm.com.

# **Contents**

| 1 Introduction                                  | 10 |

|-------------------------------------------------|----|

| 1.1 Product revision status                     | 10 |

| 1.2 Intended audience                           |    |

| 1.3 Conventions                                 |    |

| 1.4 Additional reading                          | 12 |

| 2 Overview of Neoverse N2 reference design      | 15 |

| 2.1 Product documentation                       | 16 |

| 2.2 Compliance                                  | 16 |

| 3 Hardware and topology                         | 17 |

| 3.1 IP in RD-N2                                 | 17 |

| 3.2 System architecture                         | 17 |

| 3.3 Interconnect block                          | 20 |

| 3.3.1 CMN-700 Coherent Mesh Network             | 23 |

| 3.3.2 NI-700 Non-coherent Interconnect          | 26 |

| 3.3.3 NIC-450 Network Interconnect              | 27 |

| 3.4 Processor block                             | 27 |

| 3.5 Interrupt block                             | 30 |

| 3.5.1 GIC Interrupt Translation Service options | 31 |

| 3.6 I/O Virtualization block                    | 34 |

| 3.7 Debug block (debug and trace)               | 38 |

| 3.7.1 External debugger connectivity            | 39 |

| 3.7.2 Debug authentication                      | 40 |

| 3.7.3 System debug support                      | 41 |

| 3.7.4 Application core debug support            | 42 |

| 3.7.5 SCP core debug support                    | 43 |

| 3.7.6 MCP core debug support                    | 45 |

| 3.7.7 ROM tables                                | 46 |

| 3.7.8 Trace sources                             | 48 |

| 3.7.9 Cross triggers                            | 49 |

| 3.7.10 System Trace Macrocell                   | 50 |

| 3.7.11 Self-hosted debug                        | 52 |

| 3.7.12 Debug through functional I/O interfaces     | 53 |

|----------------------------------------------------|----|

| 3.8 MSCP block                                     | 53 |

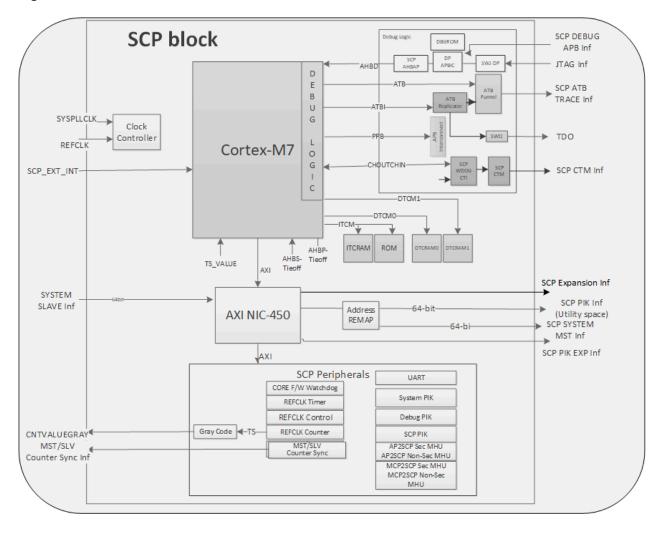

| 3.8.1 System Control Processor block               | 54 |

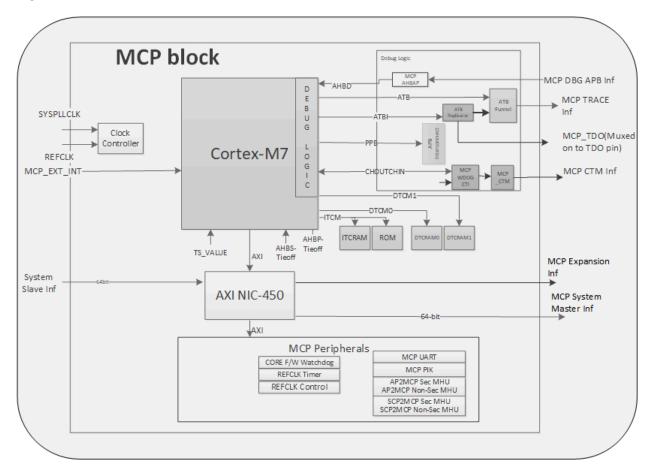

| 3.8.2 Manageability Control Processor block        | 59 |

| 3.8.3 Message communication between processors     | 61 |

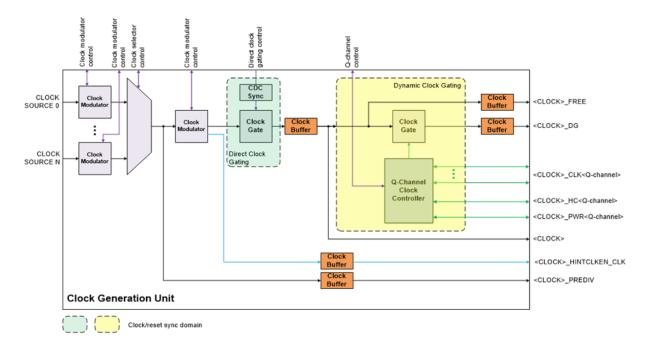

| 3.9 Clock Control block                            | 62 |

| 3.10 Peripheral block                              | 63 |

| 3.11 Dynamic Memory block                          | 64 |

| 4 Functional description                           | 67 |

| 4.1 Clocks                                         | 67 |

| 4.1.1 Input clocks                                 | 67 |

| 4.1.2 Internal clocks                              | 68 |

| 4.1.3 Output clocks                                | 71 |

| 4.1.4 PLL lock control                             | 72 |

| 4.1.5 Clocks by functional block                   | 72 |

| 4.2 Counters and timers                            | 74 |

| 4.2.1 System generic counter                       | 74 |

| 4.2.2 Generic timers                               | 74 |

| 4.2.3 Watchdog timers                              | 77 |

| 4.2.4 Power down considerations                    | 81 |

| 4.3 System power management and domains            |    |

| 4.3.1 Power and voltage domains                    | 83 |

| 4.3.2 Power and voltage domain hierarchy           |    |

| 4.3.3 Compute subsystem power states               | 88 |

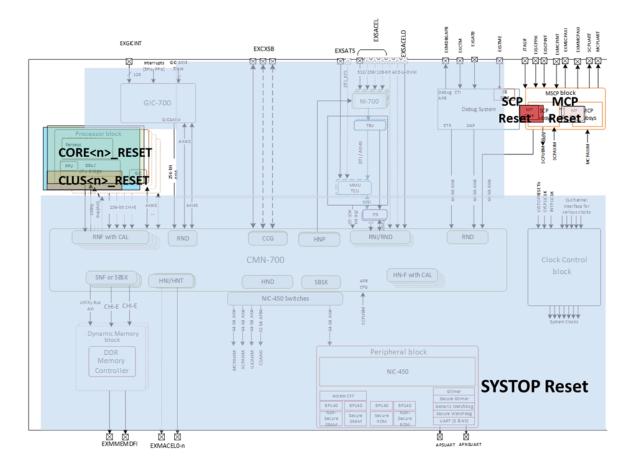

| 4.3.4 SYSTOP reset control                         | 90 |

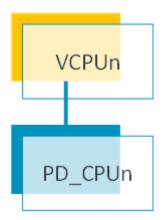

| 4.3.5 PD_CPUn power control                        | 91 |

| 4.3.6 SYSTOP domain reset control sequences        | 92 |

| 4.3.7 PD_CPUn power domain power control sequences | 93 |

| 4.3.8 Core power and performance management        | 95 |

| 4.4 Resets                                         | 96 |

| 4.4.1 Input resets                                 | 97 |

| 4.4.2 Internal resets                              | 98 |

| 4.4.3 Output resets                                | 98 |

| 4.4.4 Power policy unit resets                     | 99 |

| 4.4.5 SCP core Warm reset                          | 99 |

| 4.4.6 MCP core Warm reset                                                                                                           | 99  |

|-------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.4.7 Debug through reset                                                                                                           | 100 |

| 4.5 Top-level I/O interfaces                                                                                                        | 101 |

| 4.5.1 I/O coherent expansion slave interfaces (EXSACEL<0-n>, EXSACELD<0-n>)                                                         | 101 |

| 4.5.2 I/O coherent expansion slave interfaces with integrated inline TBUs (EXSACELT<0-n>).                                          | 101 |

| 4.5.3 Expansion master interfaces (EXMACEL<0-n>, EXMAXI<0-n>)                                                                       | 102 |

| 4.5.4 DFI master interfaces (EXMMEMDFI<0-n>)                                                                                        | 102 |

| 4.5.5 GIC expansion interrupts interface (EXGICINT)                                                                                 | 103 |

| 4.5.6 LTI expansion slave interfaces (EXSLTI<0-n>)                                                                                  | 103 |

| 4.5.7 ATS_DTI expansion slave interfaces (EXSATS<0-n>)                                                                              | 103 |

| 4.5.8 MSI expansion slave interfaces (EXSMSI<0-n>)                                                                                  | 103 |

| 4.5.9 STM event expansion interfaces (EXSSTME<0-n>)                                                                                 | 104 |

| 4.5.10 CoreSight ATB slave trace expansion interfaces (EXSATB<0-n>)                                                                 | 104 |

| 4.5.11 CoreSight APB master expansion interface (EXMDBGAPB)                                                                         | 104 |

| 4.5.12 CoreSight Cross Trigger Interface (EXCTM)                                                                                    | 104 |

| 4.5.13 AMBA CXS expansion master and slave interfaces (EXSCXSB<0-n>, EXMCXSB<0-n>)                                                  | 105 |

| 4.5.14 Power Q-Channel or P-Channel expansion interfaces (EXPWRQ_DBGTOP EXPWRP_DBGTOP<0-n>, EXPWRQ_SYSTOP<0-n>, EXPWRP_SYSTOP<0-n>) |     |

| 4.5.15 SCP expansion interrupts (EXSCPINT)                                                                                          | 106 |

| 4.5.16 MCP expansion interrupts (EXMCPINT)                                                                                          | 106 |

| 4.5.17 SCP PIK expansion interfaces (EXSCPPIK<0-n>)                                                                                 | 106 |

| 4.5.18 SCP AON expansion interface (EXMSCPAXI)                                                                                      | 107 |

| 4.5.19 MCP AON expansion interface (EXMMCPAXI)                                                                                      | 107 |

| 4.5.20 AP, SCP, and MCP UART interfaces (APNSUART, APSUART, SCPUART, MCPUART)                                                       | 107 |

| 4.5.21 JTAG and SWD interface (JTAGIF)                                                                                              | 107 |

| 4.5.22 Debug authentication signals                                                                                                 | 108 |

| 4.5.23 Functional override inputs                                                                                                   | 108 |

| 4.5.24 Miscellaneous output signals                                                                                                 | 109 |

| 4.6 System Boot                                                                                                                     | 109 |

| 4.6.1 Boot flow overview                                                                                                            | 110 |

| 4.7 Security                                                                                                                        | 111 |

| 4.7.1 Application processor security                                                                                                | 112 |

| 4.7.2 Interconnect block security                                                                                                   | 112 |

| 4.7.3 Peripheral block security                                                                                                     | 112 |

| 4.7.4 SCP block security                                                                                                            | 113 |

| 4.7.5 MCP block security                                                                                                            | 113 |

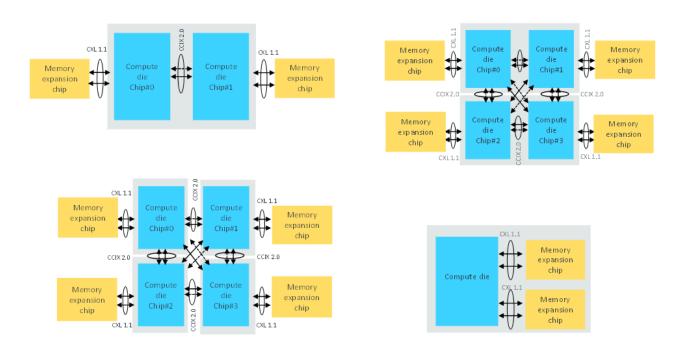

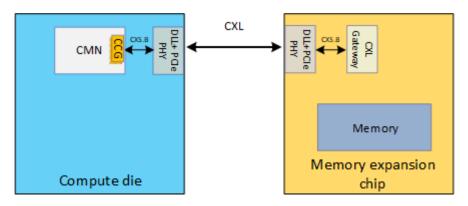

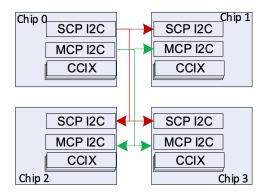

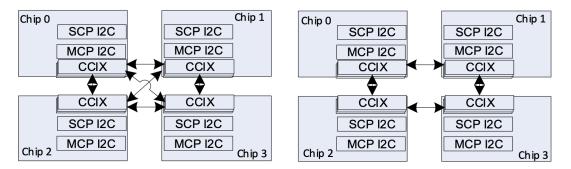

| 4.8 Multichip architecture                | 113 |

|-------------------------------------------|-----|

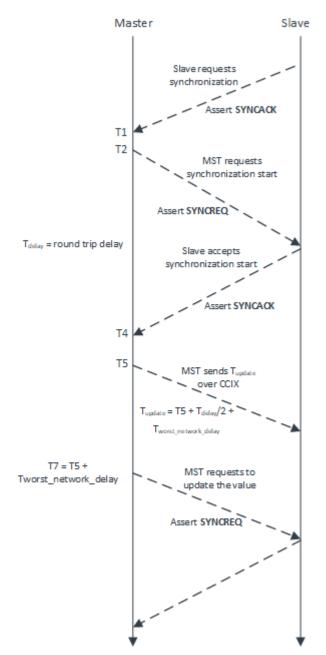

| 4.8.1 Host-to-host SMP multichip use case | 115 |

| 4.8.2 Host-to-accelerator use case        | 126 |

| 4.8.3 Host-to-memory expansion use case   | 128 |

| 5 Fixed Virtual Platform                  | 129 |

| 5.1 About the FVP                         | 129 |

| 5.2 FVP peripherals                       | 129 |

| 6 Software stack                          | 133 |

| 6.1 About the software                    | 133 |

| 6.2 SCP firmware                          | 134 |

| 6.2.1 Power control                       | 135 |

| 6.2.2 SCP boot ROM                        | 135 |

| 6.3 MCP firmware                          | 135 |

| 6.3.1 MCP boot ROM                        | 135 |

| 6.4 Application processor firmware        | 136 |

| 6.4.1 Arm Trusted firmware BL1            | 136 |

| 6.4.2 Arm Trusted firmware BL2            | 136 |

| 6.4.3 Arm Trusted firmware BL31           | 136 |

| 6.4.4 Secure runtime services BL32        | 137 |

| 6.4.5 Bootloader BL33                     | 137 |

| 6.5 Linux kernel                          | 137 |

| 6.5.1 Multiprocessing                     | 138 |

| 6.5.2 UEFI awareness                      | 138 |

| 6.5.3 Device drivers                      | 138 |

| 6.6 Multi-chiplet support                 | 138 |

| 7 Programmers model                       | 139 |

| 7.1 About the programmers model           | 139 |

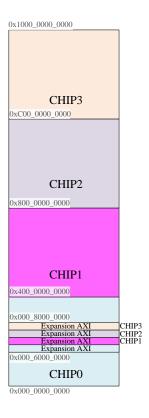

| 7.2 Memory maps                           | 139 |

| 7.2.1 AP system memory map                | 140 |

| 7.2.2 PCIe address mapping                | 153 |

| 7.2.3 SCP memory map                      | 154 |

| 7.2.4 MCP memory map                      | 156 |

| 7.2.5 Address translation table           | 159 |

| 7.2.6 Debug memory maps                   | 159 |

| 7.3 Interrupt maps                                   | 165 |

|------------------------------------------------------|-----|

| 7.3.1 PPI interrupt map                              | 165 |

| 7.3.2 SCP NVIC interrupt map                         | 171 |

| 7.3.3 MCP NVIC interrupt map                         | 173 |

| 7.4 Register descriptions                            | 174 |

| 7.4.1 System ID registers                            | 175 |

| 7.4.2 REFCLK counter registers                       | 184 |

| 7.4.3 Generic timer registers                        | 204 |

| 7.4.4 System generic timer synchronization registers | 218 |

| 7.4.5 Application Processor Watchdog timer registers | 234 |

| 7.4.6 Base SRAM ECC RAS registers                    | 249 |

| 7.4.7 Message Handling Unit registers                | 259 |

| 7.4.8 Core Manager and clock control registers       | 283 |

| 7.4.9 System Power Integration Kit registers         | 311 |

| 7.4.10 Debug Power Integration Kit registers         |     |

| 7.4.11 Debug Chain Power Control Logic registers     | 373 |

| 7.4.12 MSCP Power Control registers                  | 386 |

| 7.4.13 DMC manager registers                         | 434 |

| 7.4.14 PCle integration control registers            | 438 |

| A Revisions                                          | 487 |

## 1 Introduction

## 1.1 Product revision status

For details on the product revision status, see the  $Arm^{\otimes}$  Neoverse<sup>TM</sup> N2 reference design Release Note

## 1.2 Intended audience

The Technical Overview is written for experienced hardware and System-on-Chip (SoC) engineers who might or might not have experience with Arm products. Such engineers typically have experience in writing Verilog and of performing synthesis, but might have limited experience of integrating and implementing Arm products.

## 1.3 Conventions

The following subsections describe conventions used in Arm documents.

#### Glossary

The Arm Glossary is a list of terms used in Arm documentation, together with definitions for those terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

See the Arm® Glossary for more information: developer.arm.com/glossary.

## Typographic conventions

Arm documentation uses typographical conventions to convey specific meaning.

| Convention     | Use                                                                                                 |  |

|----------------|-----------------------------------------------------------------------------------------------------|--|

| italic         | Citations.                                                                                          |  |

| bold           | Interface elements, such as menu names.                                                             |  |

|                | Signal names.                                                                                       |  |

|                | Terms in descriptive lists, where appropriate.                                                      |  |

| monospace      | Text that you can enter at the keyboard, such as commands, file and program names, and source code. |  |

| monospace bold | Language keywords when used outside example code.                                                   |  |

| Convention                 | Use                                                                                                                                                                    |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| monospace <u>underline</u> | A permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.                                        |

| <and></and>                | Encloses replaceable terms for assembler syntax where they appear in code or code fragments.                                                                           |

|                            | For example:                                                                                                                                                           |

|                            | MRC p15, 0, <rd>, <crn>, <opcode_2></opcode_2></crn></rd>                                                                                                              |

| SMALL CAPITALS             | Terms that have specific technical meanings as defined in the Arm® Glossary. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE. |

| Caution                    | Recommendations. Not following these recommendations might lead to system failure or damage.                                                                           |

| Warning                    | Requirements for the system. Not following these requirements might result in system failure or damage.                                                                |

| Danger                     | Requirements for the system. Not following these requirements will result in system failure or damage.                                                                 |

| Note                       | An important piece of information that needs your attention.                                                                                                           |

| -\tip                      | A useful tip that might make it easier, better or faster to perform a task.                                                                                            |

| Remember                   | A reminder of something important that relates to the information you are reading.                                                                                     |

## **Timing diagrams**

The following figure explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

Figure 1-1: Key to timing diagram conventions

## **Signals**

The signal conventions are:

## Signal level

The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

- HIGH for active-HIGH signals.

- LOW for active-LOW signals.

#### Lowercase n

At the start or end of a signal name, n denotes an active-LOW signal.

## 1.4 Additional reading

This document contains information that is specific to this product. See the following documents for other relevant information:

Table 1-2: Arm publications

| Document Name                                                                       | Document ID | Licensee only |

|-------------------------------------------------------------------------------------|-------------|---------------|

| AMBA® 4 AXI-Stream Protocol Specification                                           | IHI 0051    | No            |

| AMBA® 5 CHI Architecture Specification, issue C                                     | IHI 0050C   | No            |

| AMBA® 5 CHI Architecture Specification, issue D                                     | IHI 0050D   | No            |

| AMBA® 5 CHI Architecture Specification, issue E                                     | IHI 0050E   | No            |

| AMBA® AXI and ACE Protocol Specification                                            | IHI 0022    | No            |

| AMBA® CXS Protocol Specification                                                    | IHI 0079    | No            |

| AMBA® Low Power Interface Specification,<br>Arm® Q-Channel and P-Channel Interfaces | IHI 0068    | No            |

| Document Name                                                                                                | Document ID             | Licensee only |

|--------------------------------------------------------------------------------------------------------------|-------------------------|---------------|

| Arm® Architecture Reference Manual Armv8,<br>for Armv8-A architecture profile                                | DDI 0487                | No            |

| Arm® CoreLink™ NIC-400 Network<br>Interconnect Technical Reference Manual                                    | DDI 0475                | No            |

| Arm® CoreSight™ Base System Architecture,<br>version 1.0                                                     | DEN 0068                | No            |

| Arm® CoreSight™ System-on-Chip SoC-600<br>Technical Reference Manual                                         | 100806                  | No            |

| Arm® Cortex®-M7 Processor Technical<br>Reference Manual                                                      | DDI 0489                | No            |

| Arm® Debug Interface Architecture<br>Specification ADIv6.0                                                   | IHI 0074C               | No            |

| Arm® Generic Interrupt Controller Architecture<br>Specification, GIC architecture version 3 and<br>version 4 | IHI 0069                | No            |

| Arm® Neoverse™ CMN-700 Coherent Mesh<br>Network Technical Reference Manual                                   | 102308                  | Yes           |

| Arm® Neoverse™ N2 Core Technical Reference<br>Manual                                                         | 102099                  | No            |

| Arm® Neoverse™ N2 reference design Analysis<br>Report                                                        | PJDOC-1505342170-533091 | Yes           |

| Arm® Neoverse <sup>™</sup> N2 reference design<br>Implementation Guidelines                                  | PJDOC-1505342170-534961 | Yes           |

| Arm® Neoverse™ N2 reference design Release<br>Note                                                           | PJDOC-1505342170-533248 | Yes           |

| Arm® Neoverse™ N2 reference design System<br>Design                                                          | PJDOC-1505342170-531272 | Yes           |

| Arm® Power Control System Architecture, version 2.0                                                          | DEN 0050C               | Yes           |

| Arm® Power Policy Unit Architecture<br>Specification, version 1.1                                            | DEN 0051E               | No            |

| Arm® Server Base System Architecture, version 6.0                                                            | DEN 0029C               | No            |

| Arm® System Memory Management Unit<br>Architecture Specification, SMMU architecture<br>version 3             | IHI 0070                | No            |

| Arm® Theodul DynamlQ™ Shared Unit<br>Technical Reference Manual                                              | 101381                  | Yes           |

| Arm®v7-M Architecture Reference Manual                                                                       | DDI 0403                | No            |

| CoreSight™ Components Technical Reference<br>Manual                                                          | DDI 0314                | No            |

| CoreSight <sup>™</sup> System Trace Macrocell Technical<br>Reference Manual                                  | DDI 0444                | No            |

| Principles of Arm® Memory Maps White Paper                                                                   | DEN 0001C               | No            |

Arm tests its PDFs only in Adobe Acrobat and Acrobat Reader. Arm cannot guarantee the quality of its documents when used with any other PDF reader.

Adobe PDF reader products can be downloaded at http://www.adobe.com

# 2 Overview of Neoverse N2 reference design

Arm® Neoverse<sup>™</sup> N2 reference design (RD-N2) is intended for Silicon Partners (SiPs) that want to create high core-count designs targeted at 5G, enterprise networking, SmartNIC, and cloud computing server applications.

This reference design provides recommended configurations to address Power, Performance, and Area (PPA) targets and other key requirements that are specific to these markets.

RD-N2 provides the following features:

- Thirty-two MP1 Armv9.0-A Arm® Neoverse™ N2 cores with Direct connect and 1MB of dedicated, private L2 cache for each core

- Arm Neoverse CMN-700 6 x 6 mesh interconnect with 32MB System Level Cache (SLC) and 64MB Snoop Filter (SF)

- Eight CCIX 2.0 and CXL 1.1 ports for connections to in-package and off-package accelerators

- Eight CCIX 2.0 links to support in-package die-to-die Multichip Module (MCM) or socket-tosocket Symmetric Multiprocessing (SMP) use cases

- Cache-coherent mesh interconnect with Arm® CoreLink™ NIC-450 Network Interconnect and Arm CoreLink NI-700 Network-on-Chip Interconnect non-coherent interconnects to connect system IP

- Configurations with either eight or four DDR5-5600 40-bit memory interfaces supporting dualchannel DIMM

- System Control Processor (SCP) and Manageability Control Processor (MCP) based on the Arm® Cortex®-M7 processor

- Arm<sup>®</sup> CoreSight<sup>™</sup> debug and trace support

- Targets a representative 5nm process

There are two configurations for RD-N2:

#### CFG32C8M

This configuration includes eight DDR5 40-bit memory interfaces for dual-channel DIMM.

#### CFG32C4M

This configuration includes four DDR5 40-bit memory interfaces for dual-channel DIMM. The memory interfaces are enabled on only one side of the mesh interconnect.

There are no other differences between the two configurations.

## 2.1 Product documentation

RD-N2 includes a set of documentation.

The documentation for RD-N2 comprises:

- Arm<sup>®</sup> Neoverse<sup>™</sup> N2 reference design System Design

- Introduces RD-N2, giving an overview of its features, architecture, configurations, and performance.

- Arm® Neoverse<sup>™</sup> N2 reference design Technical Overview

- Provides a high-level overview of RD-N2, including the system architecture and the functional description.

- Arm<sup>®</sup> Neoverse<sup>™</sup> N2 reference design Analysis Report

- Summarizes the performance characteristics of RD-N2, based on modeling, testing, and analysis of the system.

- Arm<sup>®</sup> Neoverse<sup>™</sup> N2 reference design Implementation Guidelines

- Contains information about the physical implementation of the RD-N2 design.

## 2.2 Compliance

RD-N2 complies with, or includes components that comply with, the following specifications:

- Arm® Architecture Reference Manual Armv8, for Armv8-A architecture profile

- Arm<sup>®</sup> Generic Interrupt Controller Architecture Specification, GIC architecture version 3 and version

- AMBA<sup>®</sup> 5 CHI Architecture Specification, issue E

- Arm<sup>®</sup> Server Base System Architecture, version 6.0

- AMBA<sup>®</sup> AXI and ACE Protocol Specification

- Arm® System Memory Management Unit Architecture Specification, SMMU architecture version 3

- Arm<sup>®</sup> CoreSight<sup>™</sup> Base System Architecture, version 1.0

- Arm<sup>®</sup> Power Policy Unit Architecture Specification, version 1.1

- Arm<sup>®</sup> Power Control System Architecture, version 2.0

- Arm<sup>®</sup> Debug Interface Architecture Specification ADIv6.0

# 3 Hardware and topology

The architecture of RD-N2 supports the design of compute subsystems for infrastructure market segments such as hyperscale data centers, networking, and enterprise storage.

## 3.1 IP in RD-N2

The IP and components in RD-N2 provide a design from which to create a custom SoC.

The RD-N2 subsystem contains the following IP:

- Armv9.0-A Arm Neoverse N2 cores

- Arm Neoverse CMN-700 Coherent Mesh Network

- Arm Cortex-M7 System Control Processor

- Arm Cortex-M7 Manageability Control Processor

- Arm CoreLink GIC-700 Generic Interrupt Controller

- Arm CoreLink MMU-700 System Memory Management Unit

- Arm CoreLink PCK-600 Power Control Kit

- Arm CoreLink NI-700 Network-on-Chip Interconnect

- Arm CoreLink NIC-450 Network Interconnect

- Arm<sup>®</sup> CoreLink<sup>™</sup> ADB-400 AMBA<sup>®</sup> Domain Bridge

- Arm CoreSight System-on-Chip SoC-600

- Arm CoreSight STM-500 System Trace Macrocell

- Clock generators with support for dynamic clock gating

- On-chip ROM, RAM, and other peripherals

- Third-party DDR5-5600 memory controllers

## 3.2 System architecture

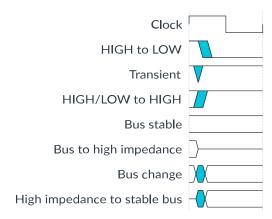

RD-N2 is partitioned into functional blocks that are a combination of major IP and the supporting logic around them. Some features of the design incorporate functionality from multiple blocks. This block-based design approach provides flexibility, scalability, and modularity.

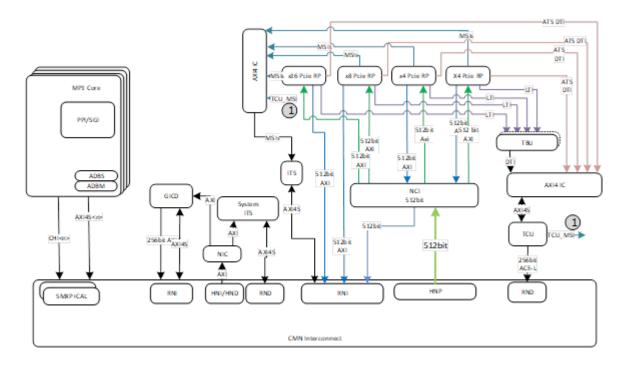

The following figure shows the top-level architecture of RD-N2.

I/O Virtualization block (2) Debug block FXCXSB (6) SCP block Interrupt block (7)(1)MCP block **Processor** block Interconnect Clock HN-F with CAL HN-D SBSX block Control NIC-450 Switches block **}** (8) Dynamic Memory Peripheral block block ăă

Figure 3-1: RD-N2 architecture block diagram

The functional blocks in RD-N2 are:

#### Interconnect block

Includes coherent and non-coherent interconnects.

CMN-700 is a mesh-based coherent interconnect with multichip support using the CCIX standard.

NI-700 connects to the external I/O masters and provides expansion interfaces for CMN-700.

NIC-450 interfaces connect to system peripherals, rest-of-SoC components, and other subsystem connectivity.

Contains other very low performance interconnects such as AMBA AXI4-Stream Interconnect (IC) and Advanced Peripheral Bus (APB) IC.

For more information, see Interconnect block.

#### **Processor block**

Includes Arm Neoverse N2 cores with Direct connect DynamlQ Shared Unit (DSU) and power management components.

Configured with one core plus bridge per cluster (MP1).

RD-N2 implements 32 instances of the Processor block.

For more information, see Processor block.

## Interrupt block

Handles interrupts in the system.

Includes distributed GIC-700 components, such as GIC Distributor and Redistributor, and Interrupt Translation Services (ITS).

For more information, see Interrupt block.

#### I/O Virtualization block

Includes distributed Translation Buffer Unit (TBU) and Translation Control Unit (TCU) components, which provide I/O virtualization for external I/O masters.

For more information, see I/O Virtualization block.

#### Debug block

Supports CoreSight debug and trace in all cores in the compute subsystem, in the mesh network, and in other system IP.

For more information, see Debug block (debug and trace).

#### MSCP block

Includes a System Control Processor and a Manageability Control Processor, both based on the Cortex-M7 processor.

The SCP controls functions such as boot, reset, clock, and power management.

The MCP handles communication with the Baseboard Manageability Controller (BMC).

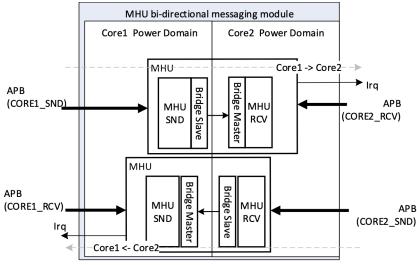

Supports the MHUv2.1 inter-processor communication method.

Includes a PCK-600 Power Control Kit that is distributed across the subsystem to support different reset and power domains.

Provides expansion interfaces for adding SoC peripherals such as Shared Peripheral Interrupt (SPI) and I2C.

For more information, see MSCP block.

#### **Clock Control block**

Includes logic to generate the compute subsystem clocks.

Separate clock control logic is used to generate clocks for each core, for the debug logic, and for the memory controllers.

For more information, see Clock Control block.

## Peripheral block

Includes watchdog timers, Secure and Non-secure generic timers, and Secure and Non-secure Universal Asynchronous Receiver-Transmitters (UARTs).

Also contains scratch RAM, boot ROM, and firmware ROM.

For more information, see Peripheral block.

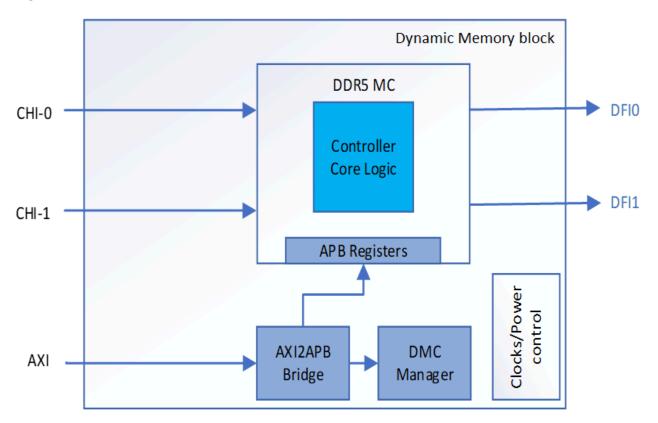

## **Dynamic Memory block**

Contains the third-party memory controller.

For more information, see Dynamic Memory block.

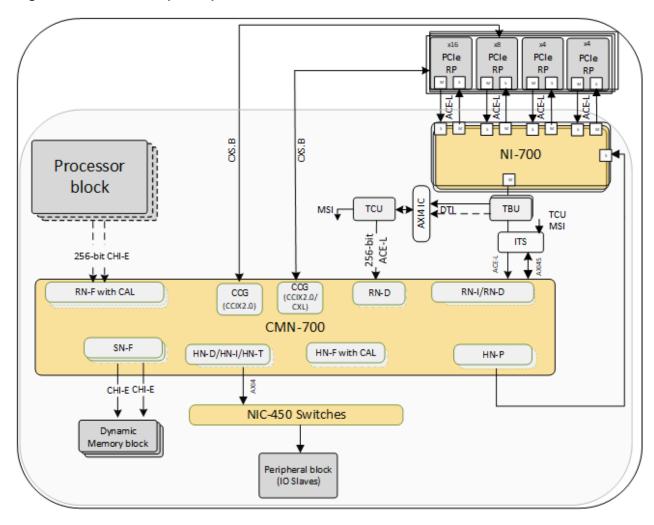

## 3.3 Interconnect block

The Interconnect block in RD-N2 supports coherent and non-coherent accesses.

#### Coherent interconnect

CMN-700 is a mesh-based coherent interconnect with support for AMBA 5 CHI-E, AXI-H, and memory partitioning.

#### Non-coherent interconnects

NI-700 connects to the external I/O masters and provides expansion interfaces for CMN-700

NIC-450 provides interfaces to connect system peripherals, rest-of-SoC components, and other subsystem connectivity.

Other very low performance interconnects, such as AMBA AXI4-Stream Interconnect (IC), APB IC.

The Interconnect block contains:

- A coherent mesh network with coherent multichip support using the CCIX and CXL standard

- I/O master and slave extension interfaces

- NIC-450 switches and expanders for Q-Channels

- Miscellaneous blocks, such as clock domain bridges, power management, pipeline slices, and other wrapper glue logic

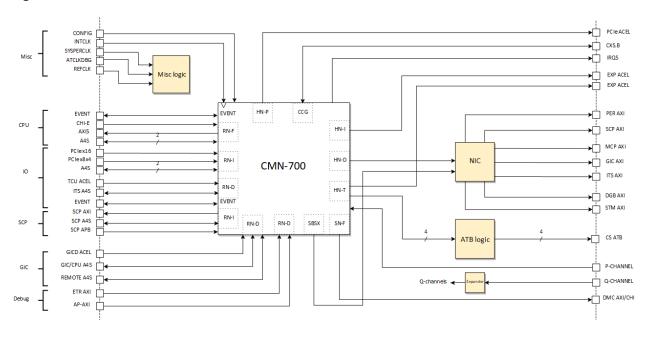

The following figures illustrate the block diagrams of the Interconnect block interfaces and key IP blocks that are connected to those interfaces.

Figure 3-2: Connectivity of key IP blocks with the Interconnect block

Figure 3-3: CMN-700 interconnect interfaces

The final logical structure could differ significantly due to restructuring of the RTL that removes the hierarchical boundaries in favor of physical boundaries. This sort of change might be made to simplify development of the backend implementation flow, such as using a tile-based approach.

The CMN-700 mesh network constitutes the largest part of the overall subsystem. It enables the connection of blocks that have different interfacing requirements to the Interconnect block. Examples of components that have differing interface requirements are the Processor block, memory controllers, and external I/O masters.

The coherent mesh network supports the following interface protocols:

- AMBA<sup>®</sup> 5 CHI Architecture Specification, issue C

- AMBA<sup>®</sup> 5 CHI Architecture Specification, issue D

- AMBA<sup>®</sup> 5 CHI Architecture Specification, issue E

- AMBA ACE-Lite

- AMBA® AXI and ACE Protocol Specification

- AMBA® 4 AXI-Stream Protocol Specification

- AMBA<sup>®</sup> CXS Protocol Specification

Ancillary components such as the internal NIC provide fine grain decoding of the system address map. These components interface to modules that operate in different clock domains and support dynamic control of clocks that can be gated to reduce power.

## 3.3.1 CMN-700 Coherent Mesh Network

In RD-N2, the CMN-700 implementation addresses the PPA requirements of designs with a high core count. This implementation is targeted at the networking and data center markets.

In the RD-N2 design, CMN-700 implements the following features:

- A mesh size of 6 x 6 for both the CFG32C8M and CFG32C4M configurations. The mesh includes 32 Fully coherent Request Nodes (RN-Fs) with support for a Component Aggregation Layer that can connect to two devices (CAL2).

- An SLC of 32MB. The mesh includes 32 Fully coherent Home Nodes (HN-Fs) with CALs. Each HN-F has a cache size of 1MB.

- In the CFG32C8M configuration, eight Fully coherent Slave Nodes (SN-Fs) for connections to the third-party memory controllers over the native AMBA CHI interface.

- The AMBA interfaces from these nodes are connected to components within the subsystem or are exported as expansion interfaces.

- Configured with a single Data (DAT) and Response (RSP) channel.

CMN-700 also has the following features:

- Support for multiple types of nodes, such as:

- I/O coherent Request Nodes (RN-Is).

- I/O coherent Request Nodes with DVM support (RN-Ds).

- I/O coherent Home Nodes (HN-Is).

- I/O coherent Home Nodes with PCle optimization (HN-Ps).

- I/O coherent Home Nodes with Debug Trace Controller (HN-Ts).

- Support for Configurable Mesh Credit Slices (MCSs), Device Credit Slices (DCSs), and CAL Credit Slices (CCSs).

- Fully compliant with AMBA<sup>®</sup> 5 CHI Architecture Specification, issue E and AMBA<sup>®</sup> AXI and ACE Protocol Specification, issue H to optimize coherency and Quality of Service (QoS).

- Configurable option to support all SLC and SF sizes that are available for the mesh to meet various RD-N2 requirements.

- Support for System Cache Group (SCG) and striping capabilities on SLC partitions and memory interfaces.

- Support for Armv9 features.

- Configurable Memory Partitioning and Monitoring (MPAM) for SLC capacity allocation.

- Support for all system-level and interconnect-level QoS features, including Completer Busy (CBusy). Configurable CBusy options are also supported.

- Support for the configurable Request Node System Address Map (RN SAM) QoS override feature.

- Support for Reliability, Availability, and Serviceability (RAS) features and the Performance Monitoring Unit (PMU).

Hardware and topology

- Support for Debug and Trace (DT).

- Configurable support for static route optimizations around mesh hotspots that override the default XY route path between specific Crosspoints (XPs).

- Device ports with CALs and support for more device ports at the boundary and edge XPs for PPA optimization.

- Support for the CMN-700 Utility Bus (PUB) interface, which is a generic transport layer in the mesh. Request and response fields are left for definition and processing by requestor and responder.

- Support for PUB with bridges to connect external AMBA AXI4-Stream and AXI devices outside of the CMN-700 interconnect.

- Support for use of PUB channels to transfer messages between distributed GIC components.

- Support for configurable bus width options, such as 128 bits, 256 bits, and 512 bits on I/O ports.

- Support for Coherent Multichip Link (CML) port-to-port forwarding, which allows the mesh to act as a bridge between two CCIX chips.

- Support for chip-to-chip communication.

- Eight CML links that support both the CCIX 2.0 and CXL 1.1 protocols for connections to accelerators.

- Eight CML links with CCIX 2.0 support for chip-to-chip or socket-to-socket connections.

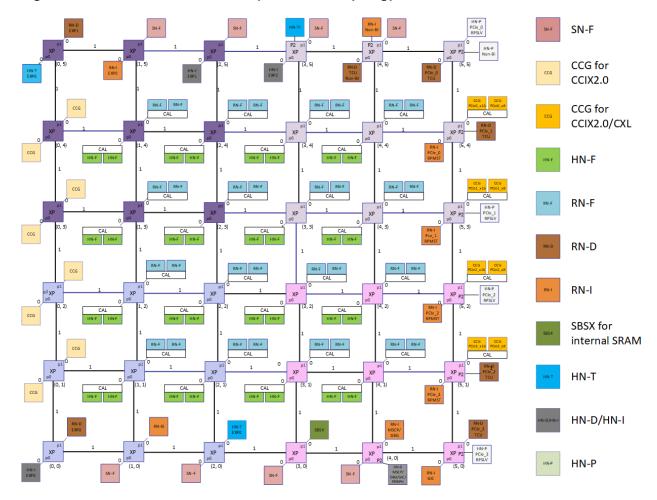

The following figure shows the 6 x 6 CMN-700 interconnect mesh network that is used in RD-N2.

Figure 3-4: RD-N2 6 x 6 CMN-700 system mesh topology

The following selections determine the CMN-700 mesh structure:

## Requesting master selection

The number of masters with coherent caches in the SoC determines the number of RN-F ports that are required.

The number of masters without internal coherent caches in the SoC determines the number of RN-D/RN-I components that are required.

#### Home Node selection

The SLC and SF size requirements determine the number of HN-F instances. The appropriate number of HN-F nodes are selected in the system according to the performance and area requirements.

The total AMBA AXI slave bandwidth requirements and the physical placement of these slave peripherals determine the number of HN-D and HN-I instances.

The HN-I does not support caching of data read from or written to the downstream AMBA interface I/O slave block. Therefore, any cacheable request that is sent to the HN-I is converted to the appropriate AMBA AXI read or write command and sent to the downstream AMBA interface block. No snoops are sent to RN-Fs in the system. If an RN-F caches data read from or written to the downstream AMBA interface I/O slave block, that data is not cached in the SLC. In this case, hardware coherency is not maintained. Any subsequent access to that data is read from or written to the AMBA interface I/O slave block directly, ignoring the cached data. The data can be cached in Processor block caches.

## 3.3.2 NI-700 Non-coherent Interconnect

NI-700 is used for PCle system integration to support the PCle bifurcation feature in RD-N2. The interconnect is configured according to the overall PCle system functional and performance requirements, bus widths, and queue sizes to meet the PPA requirements.

### NI-700 provides:

- A Network on Chip (NoC) based architecture

- Highly configurable and scalable interconnect that extends to higher bandwidths

- A packetized transport layer that allows serialization to reduce wire counts

- Protocol conversion on entry and exit from the AMBA protocol to internal transport for ease of implementation

- Native support for AMBA AXI5, ACE5-Lite, and AHB5 interfaces

- Highly configurable Quality of Service (QoS) features

- Flexible tree or mesh topology

- Reduced routing and area, with easier timing closure

- Configurable options to create a high-performance AMBA protocol-compliant network infrastructure for non-coherent masters, including:

- Multiple AMBA protocols, such as AXI, AHB, APB, AXI4-Stream

- Multiple clock domains

- Single power domain

- Single voltage domain

- Variable link data widths

- Up to 256 slave interfaces

- Up to 255 master interfaces

- Hierarchical clock gating

- Support for complex topologies

- Non-blocking resource planes

The NI-700 topology in RD-N2 includes multilane PCle I/O masters with bifurcation modes. The two four-lane, one eight-lane, and one 16-lane PCle I/O masters are connected through NI-700 to the main CMN-700 interconnect, see Figure 3-8: Example GIC topology with distributed in-line ITS connectivity on page 33.

PCle bifurcation involves splitting a single PCle port into two or more ports with reduced lane widths.

The system functional and performance requirements determine:

- The number of non-coherent interconnects

- The bus width selections

- The number of AMBA AXI Master Network Interfaces (AMNIs) and AMBA AXI Slave Network Interfaces (ASNIs) that are used in each non-coherent interconnect

## 3.3.3 NIC-450 Network Interconnect

Arm Neoverse N2 reference design includes the NIC-450 network interconnect.

NIC-450 provides:

- A network of AMBA AXI cross bars or switches

- Reduced latency, without the protocol conversion that is associated with Network-on-Chip (NoC) architectures

- A flexible tree topology

- Master and slave extension interfaces for low-bandwidth, low-latency connectivity

In Arm Neoverse N2 reference design, NIC-450 is used to provide connectivity for both internal and external compute subsystem interfaces. NIC-450-based external interfaces enable connection of external masters and slaves to the compute subsystem. For example, NIC-450 enables extension of the interfaces by grouping multiple low-performance peripheral interface connections on one CMN-700 HN-D/HN-I device port.

## 3.4 Processor block

Each Processor block contains a high-performance Neoverse N2 core, a direct connect DSU, the GIC Cluster Interface (GCI), debug, clock, and reset control blocks. The direct connect DSU, with minimal DSU logic, contains asynchronous interface bridges, power management PPUs, and debug logic.

The RD-N2 design has 32 Processor blocks. The cores in the Processor block are also referred to as the Application Processor (AP).

The core is configured in direct connect mode. There is no L3 cache or snoop control logic. There is one core in each cluster, directly connected to the CMN-700 interconnect through a CAL

(Component Aggregation Layer). This connection method is used for MP1 clusters that support direct connect with a coherent AMBA CHI interconnect.

#### The Processor block includes:

- One MP1 Arm Neoverse N2 core, which supports the following architectural features:

- Armv9.0-A 48-bit Physical Address (PA) and 48-bit Virtual Address (VA).

- Armv9.0-A Scalable Vector Extensions 2 (SVE2).

- Armv9.0-A SVE2 Cryptographic Extensions supporting SHA2-512, Advanced Encryption Standard (AES), Secure Hash Algorithm 3 (SHA-3), the SM3 and SM4 ciphers, and bit permute instructions.

- Armv9.0-A Embedded Trace Extension (ETE).

- Armv9.0-A Trace Buffer Extension (TRBE).

- Armv8.x Memory System Resource Partitioning and Monitoring (MPAM).

- Armv8.x Activity Monitors Extension.

- Armv8.x Random Number instructions.

- Armv8.x CBusy adaptive prefetching mechanism.

- 1MB private L2 cache per core.

- Direct connect to CMN-700 through a CAL.

- Single 256-bit AMBA CHI master interface to CMN-700.

- A utility bus slave interface that is memory-mapped at the Cluster Utility memory region in AP memory map. This 64-bit AMBA AXI5 interface provides a programming interface to access the control registers for various other system components in the cluster and core registers. The SCP and AP cores can access the following control registers:

- PPUs.

- Activity monitors in the cores.

- Maximum Power Mitigation Mechanism (MPMM) registers in the cores.

- RAS registers.

- A separate voltage domain per core.

- A separate power domain per core and per cluster. There is separate PPU support for core and cluster power management.

- ELA-600 Embedded Logic Analyzer.

- Asynchronous or synchronous options between the DSU and the CMN-700 interconnect.

- Integrated GCI in the cluster power domain. In direct connect mode, one GCI module is supported for each MP1 core to handle all the software-generated interrupts between the cores.

Processor block Processor cluster Clock Control Arm Neoverse N2 PLL Dividers 32b/64b Processor CPU Manager Direct connect DSU Async Bridges AMBA 5 CHI Debug PAPB/ATB ADB GCI 256bit CHI.E 64bit AXI 64bit ATB 32bit APB 64bit AXI4S

Figure 3-5: Processor block with a single MP1 big core in direct connect mode

The Processor block comprises the following interfacing logic outside of the core cluster:

- Integrated GIC Redistributor. A GCI block for each core to support Private Peripheral Interrupts (PPIs) and Software Generated Interrupts (SGIs) between the application cores.

- Clock Control logic to generate all the clocks that are needed for the core and glue logic.

- Core Manager logic, which provides software registers for setting the reset values to the core.

- Daisy chain logic for the following interfaces within each Processor block:

- AMBA Trace Bus (ATB) trace from each core.

- Debug APB interface.

- CoreSight Trigger Interface.

- Generic counter bus that is routed to all the cores in the system. This routing must be balanced across the system. Configurable register slice logic can be used to add register slices for each core to provide the necessary balancing.

- Utility bus interface. This interface can be connected through the CMN-700 PUB control communication network to enable the SCP to access Clock Control registers, power management logic, and sensor logic.

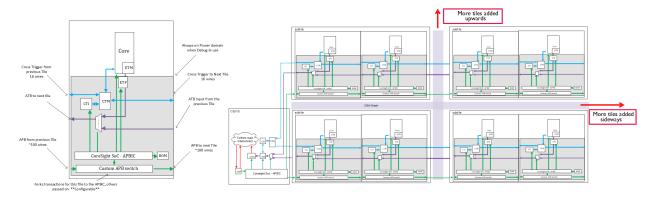

These interfaces are daisy chained, with the interfaces originating from the neighboring Processor block and sent to the destination in a daisy-chained manner. This arrangement enables tile-based physical implementation, which is recommended for the optimal physical implementation of a large core-count infrastructure system. For example, a tile can be a group of one or two processor cores, one or two HN-F slices (SLC caches), and an XP. Instead of designing the system as one flat physical implementation, routing channels can be used to create the complete system with a repeatable macro.

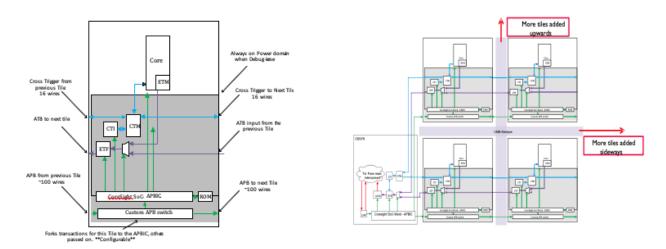

The following figure shows an example of debug interfaces daisy chained through each Processor block. The other interfaces are also daisy chained in a similar manner.

Figure 3-6: Processor block debug daisy chaining with a single MP1 big core in Direct connect mode

## 3.5 Interrupt block

The RD-N2 Interrupt block contains distributed Generic Interrupt Controller (GIC) components.

RD-N2 supports the following GIC-700 features:

- Arm GICv4.1 architecture.

- Distributed architecture GIC Distributor, Redistributor, and ITS blocks can be distributed across the system.

- The number of ITS blocks on the data path is determined based on system functional and performance requirements. Inline ITS, ITS on the side, and system ITS options are supported.

- Distributed Redistributor (GCI-GIC cluster interface). One block for each core in Direct connect mode to support PPIs and SGIs. The PPI assignments comply with Arm® Server Base System Architecture, version 6.0.

- Single global SPI block.

- Security Extensions.

- Distributed architecture, optimized for up to 128 cores or threads for each die or chip. Support for up to four chips.

- Direct injection of virtualized interrupts, bypassing the hypervisor to deliver Locality-specific Peripheral Interrupts (LPIs) and SGIs to VMs.

- Shared peripheral interrupt supported for up to 1984 interrupts. All interrupts are available for single-chip systems and, equally, between chips for multichip systems.

- Support for up to 16,000 virtual Processing Elements (vPEs).

- P-Channel and Q-Channel support for low-power control.

- Multichip support for SMP use cases.

- MPAM support for memory traffic originating from the GIC.

- Support for the AMBA® AXI and ACE Protocol Specification, issue H bus and all the associated commands.

- PUB interface connectivity can be used for local GIC interrupt communications. This interface is also used for GIC chip-to-chip interrupt communications.

- 128 SPIs can be exported as inputs to the compute subsystem for connection to other SoC components. These interrupts are assumed to be level interrupts. Any edge interrupts must be converted to level interrupts before connecting to these interrupt inputs on the compute subsystem.

Backwards compatibility with the GIC architecture, version 2 programmers model is not supported.

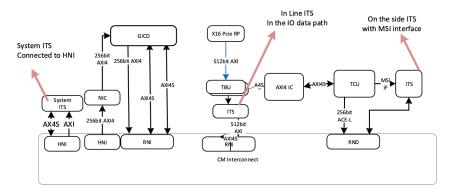

## 3.5.1 GIC Interrupt Translation Service options

RD-N2 supports the following ITS block arrangements:

• Inline ITS: Integrated before RN-I/RN-D ports inline in the I/O path of the master to system memory.

- ITS on the side: Interfaced along the side of the master through the Message Signaled Interrupt (MSI) interface.

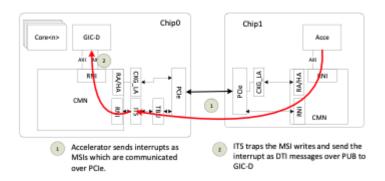

- System ITS: Global ITS that is integrated on the CMN-700 HN-I interface. Multiple masters on the local chip or masters on remote chips can send MSI or MSIx targeting to this system ITS. For more information about interrupt routing from a remote accelerator chip to the system ITS on the host, see Host-to-accelerator use case.

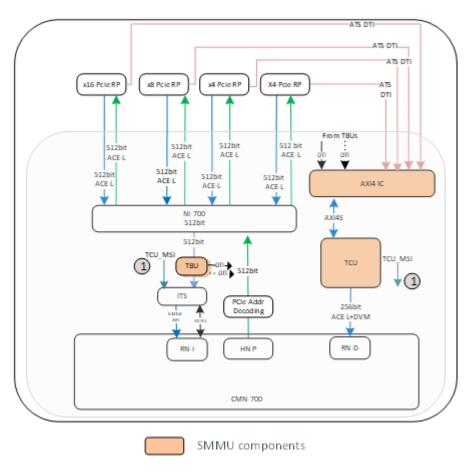

The following figure shows inline ITS, ITS on the side, and system ITS block arrangements.

Figure 3-7: Different ITS types

RD-N2 supports both inline ITS mode or with MSI interface mode. The mode to implement depends on the system requirements. Both ITS modes can exist in the system for different ITS instances. The following figure shows an example GIC topology with inline ITS. The ITS is connected inline on the AMBA AXI data path.

Figure 3-8: Example GIC topology with distributed in-line ITS connectivity

The following figure shows an example GIC topology with distributed ITS using the MSI interface without intercepting the main AMBA AXI data path. In this example, a PCIe Root Complex (PCIe-RC) supports the MSI interface to connect the interrupts directly to the ITS block.

Figure 3-9: Example GIC topology with MSI interface-based ITS connectivity and system ITS

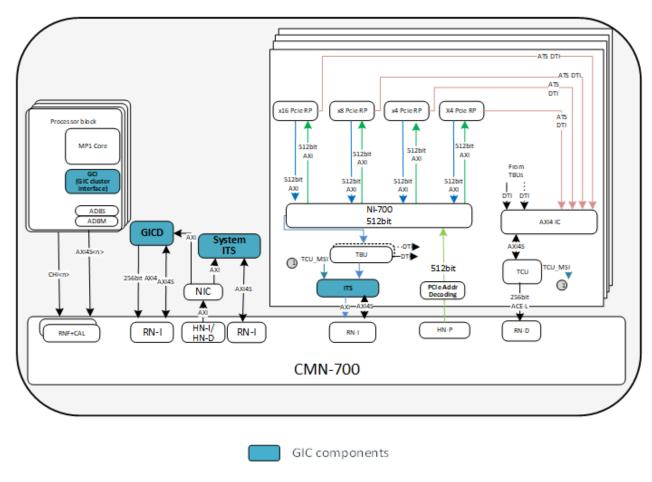

## 3.6 I/O Virtualization block

The I/O Virtualization block is implemented by MMU-700 System Memory Management Unit and other IP. This block includes distributed MMU-700 Translation Buffer Unit (TBU) and Translation Control Unit (TCU) components, which provide I/O virtualization for external I/O masters.

The RD-N2 system architecture supports the following MMU-700 features:

- Compliant with the SMMUv3.2 architecture

- Supports Armv9.0-A and Armv8.x architecture:

- MPAM Secure EL2 for multiple Secure OSs and Translation Lookaside Buffer (TLB) range invalidation

- Hardware Translation Table Update (HTTU) Support for 52-bit Virtual Addresses (VAs) and Physical Addresses (PAs)

- Includes Distributed Translation Buffer Unit (TBU) and Translation Control Unit (TCU) architecture

- Provides address translation (ATS) functions for I/O master devices such as PCle

- Supports Direct Translation Interface Address Translation Services (DTI-ATS) for PCIe

- Provides configurable support for up to eight TBUs per TCU

- Provides single or two-stage address translation for PCle traffic:

- Single stage: From VA to PA

- Two-stage:

- Stage 1 from VA to Intermediate Physical Address (IPA)

- Stage 2 from IPA to PA

- Supports PCle features, including ATS and Process Address Space IDs (PASIDs)

- Scalable to millions of active contexts

- Supports ELA-600 for each TCU with all supported trace port features Support for both internal SRAM buffer mode and trace output mode

- Supports multiple I/O masters, such as x16 PCle data paths, and shared or independent SMMU systems for each path

- Includes a direct write interface from TCU to ITS for MSI writes

RD-N2 supports both inline and LTI TBU modes, and the choice depends on the system requirements. Both inline and LTI modes can coexist in a system for different TBU instances.

- TaaS LTI mode provides the following benefits over inline TBU mode:

- Removes write data buffering and improves system PPA.

- Removes ordering dependency for address translation for I/O masters such as PCIe.

- Enables PCle ACS for peer-to-peer traffic through an external PCle switch.

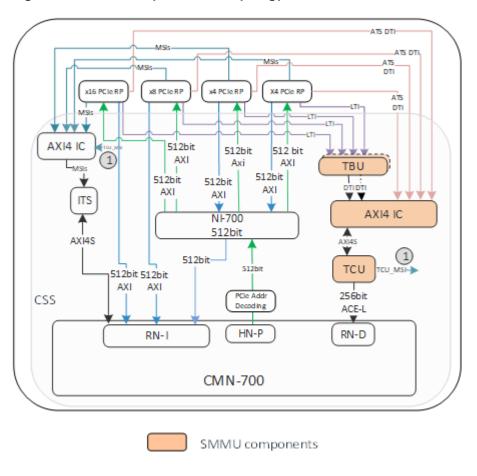

The following figure shows an example SMMU system topology with in-line TBUs in RD-N2 for each I/O master (PCIe) path.

Figure 3-10: An example SMMU topology with inline TBU mode

The following figure shows an example SMMU topology with multilane PCle I/O master connectivity in TaaS LTI configuration mode.

Figure 3-11: An example SMMU topology with TaaS LTI mode

In the LTI mode, the I/O master PCIe-RC in the preceding example sends the address translation requests to the TBU through the LTI interface to get the PA. When the PA is returned from the TBU, then the transaction downward path is sent to the interconnect.

Figure 3-12: Address translation request paths in LTI mode

In a system, the in-line TBU or LTI mode selection is based on the system features and PPA requirements. For example:

- LTI enables feature such as PCIe ACS for peer-to-peer traffic to be routed through the external PCIe switch.

- LTI offers performance and area optimizations. The performance improvement is achieved by performing address translation ahead in the pipeline before the PCIe ordering, which can improve some latencies in the path. Also, with LTI, there is no write buffering requirement in the TBU.

# 3.7 Debug block (debug and trace)

The debug logic is distributed to provide real-time trace facilities for the application processor cores, MCP, SCP, CMN-700 interconnect, and other compute subsystem components.

The following key debug and trace features are supported:

- Compliant with Arm<sup>®</sup> CoreSight<sup>™</sup> Base System Architecture, version 1.0, Combination C.

- Real-time trace facilities for application processor cores, the SCP, the MCP, and the Interconnect block.

- Full support for CoreSight debug and trace for all application processor cores, the SCP, the MCP, and the CMN-700 interconnect.

- Support for the following CoreSight components:

- Embedded Trace FIFO (ETF).

- Embedded Trace Router (ETR).

- System Trace Macrocell (STM).

- Cross Trigger Interface (CTI).

- CoreSight Address Translation Unit (CATU).

- The MSCP debug block is independent of the application processor debug block to enable debug of the clock, reset, and power control devices infrastructure.

- ELA-600 for in-silicon hardware debug.

- Power gating of the CoreSight block.

- Separate cluster debug chain power domain.

- DAP (JTAG) access in the Always-on domain to enable basic debug access when powering up.

- Arm Development Studio, along with transactor from EDA vendors.

- Trace over functional I/O, such as PCle.

- Multichip debug. For more information, see Multichip debug.

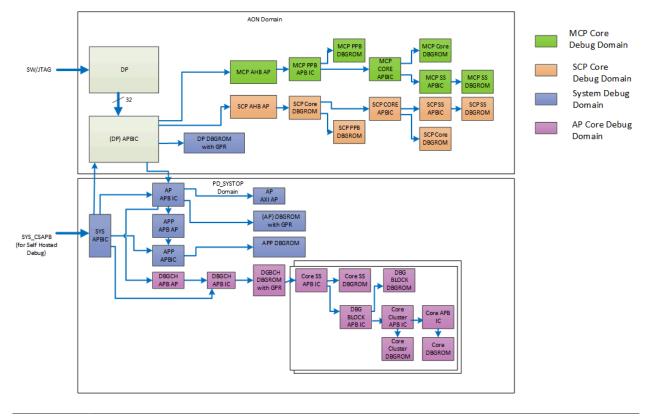

## 3.7.1 External debugger connectivity

The RD-N2 subsystem is connected to the external world through a Debug Access Port (DAP) interface.

A single DAP is used to access the application processor, SCP, and MCP cores. This interface supports the Joint Test Action Group (JTAG) and Serial Wire Debug (SWD) protocols. The DAP is in the Always-on (AON) power domain, which enables basic debug access when powering up.

The following external connections can be made to the DAP interface:

- An external debugger, such as Arm DS-5 Debugger

- Interface hardware, such as the Arm DSTREAM debug and trace unit

RD-N2 is debugged using a common debug JTAG interface connected to a DAP. A Serial Wire JTAG Debug Port (SWJ-DP), which combines a JTAG-DP and a SW-DP, enables debug access through either JTAG or SWD. The application processor, SCP, and MCP cores can be debugged independently in the system.

The following functionality is supported through the DAP interface:

- Access to all the debug components in the system

- Cross-trigger support across cores in the system

- The ability to trace out from all the cores and system components to DDR memory through the trace memory controller

- The ability to trace out from all the cores and system components to off-chip memory through external functional I/Os such as PCle

- Debugger access to the full system memory through a CoreSight debug and trace AMBA AXI-AP interface connected to the CMN-700 interconnect

Figure 3-13: Architectural view of RD-N2 DAP structure

Access to SCP and MCP core debug components for self-hosted debug from the application processor cores is optional.

The compute subsystem supports self-hosted debug. Debug monitor software running on the application processor or SCP cores can access all the debug components without an external debugger.

# 3.7.2 Debug authentication

There are different debug domains in the compute subsystem as shown in Figure 3-13: Architectural view of RD-N2 DAP structure on page 40:

- System debug domain. This domain includes system-level components, such as the CMN-700 interconnect, AXI-AP to access the memory map, etc.

- Application processor core debug domain.

- SCP core debug domain.

- MCP core debug domain.

A different set of authentication signals provides debug authentication for each domain:

- System debug domain components SYSDBGEN, SYSNIDEN, SYSSPIDEN, SYSSPNIDEN

- Application processor core debug components that are part of all the debug domain chains -APPDBGEN, APPSPIDEN

- SCP core debug domain components SCPDBGEN, SCPNIDEN, SCPSPIDEN, SCPSPNIDEN

- MCP core debug domain components MCPDBGEN, MCPNIDEN, MCPSPIDEN, MCPSPNIDEN

The application processor cores implement Armv8.5 debug architecture, in which the **NIDEN** and **SPNIDEN** signals are deprecated.

These signals arrive as inputs to the compute subsystem. The instantiation of these signals is **IMPLEMENTATION DEFINED**. SoC implementations must ensure that these signals are controlled by a Secure entity/root of trust to guard against tampering. Alternatively, the signals can be set using fuses implemented as part of the SoC.

## 3.7.3 System debug support

The system debug logic provides the following debug support:

- Logic to support daisy-chaining of the core debug logic interfaces (Debug APB, Traces, Triggers and Timestamp) to support tile-based floorplan

- An STM that can generate trace data directly from AMBA AXI write transactions (instrumented trace data) and from hardware events (HWEVENT interface) - The STM has its own dedicated STM ETF with 16KB of memory.

- A system trace funnel that takes traces from application processor cores in different daisy chains, the SCP, the MCP, the CMN, and the STM The traces are funneled to 32KB of system ETF memory.

- Trace data routing to the main system memory through the Embedded Trace Router (ETR)

- A CoreSight Address Translation Unit (CATU), which provides address translation on the AMBA AXI interface from the ETR

- A debug APB network to program the debug peripherals

- A dedicated DAP APB bus interface from the external debugger

- A debug APB interface that provides access to all cores in the various debug chains and debug components in the SCP and MCP blocks

- Trace and trigger components across the system

- Access from all the application processor, SCP, and MCP cores for self-hosted software debug

- An AMBA AXI-AP that allows an external debugger to access the system memory backplane directly without having to go through a processor

- Debug authentication for system debug components through the SYSDBGEN, SYSNIDEN, SYSSPIDEN, and SYSSPNIDEN input signals

- Cross-triggering through a CTI and Cross Trigger Matrix (CTM) across all the components in the system

- Expansion Debug interfaces (Debug APB, Expansion Trace and Triggers) to the SoC for components added outside the compute subsystem

- Separate reset domain for the logic in each debug chain Every debug chain has its own dedicated PPU for reset control.

- Support for Granular Power Requester (GPR) functionality through GPR registers for SYSTOP power domain reset requests

- Support for multichip debug

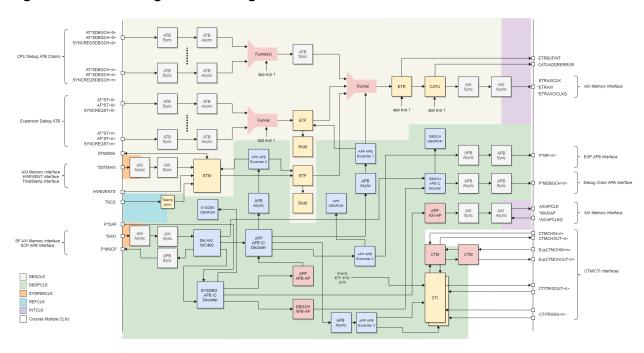

Figure 3-14: Block diagram for Debug block

# 3.7.4 Application core debug support

The debug logic for the application processor core is present in the Direct connect DSU. The debug chain logic is in part of the Processor block, outside the core and the Direct connect DSU.

This arrangement provides the following debug support:

- A local debug ROM table that contains a list of components added in the Processor block. This tables enables the debugger to determine the components that are implemented locally in the Processor block.

- A debug control with APB register interface that provides access to debug registers in the Processor block. The debug APB is routed to the neighboring core by daisy chaining.

- Embedded 8KB trace FIFO for buffering core traces.

- A trace funnel that arbitrates up to two trace sources for the local core and another for the neighboring core to form a daisy chain.

- A CTI for each processor core that is daisy chained with the CTI of the neighboring core and routed to a system-level CTM.

- Debug authentication for system debug components through the **APPDBGEN**, and **APPSPIDEN** input signals.

- Daisy chaining of the debug channel, debug-related interfaces, and global timestamp synchronization network to connect all the cores to the debug components.

Figure 3-15: High-level representation of debug daisy chain structure across Processor blocks

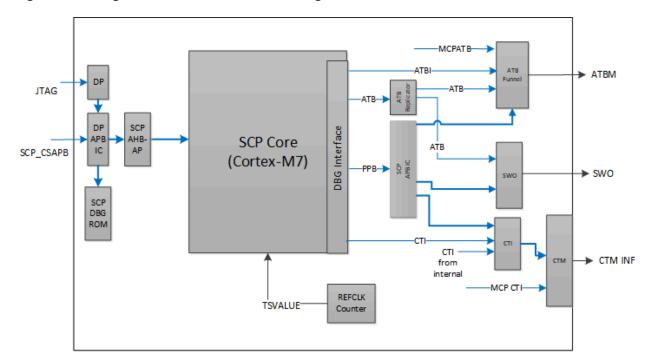

## 3.7.5 SCP core debug support

RD-N2 supports SCP debug.

The following debug support is provided for the SCP core:

- SCP debug ROM tables that enable the debugger to determine which debug components are internal to the Cortex-M7 core and identify others outside the core.

- Components inside the Cortex-M7 core:

- A Flash Patch and Breakpoint (FPB) unit for implementing hardware breakpoints.

- A Data Watch-point and Trace (DWT) unit for implementing watchpoints, data tracing, and system profiling.

- An Instrumentation Trace Macrocell (ITM), which supports printf()-style debugging. This unit generates trace data that is sent to an ATB funnel and to Serial Wire Output (SWO).

- An Embedded Trace Macrocell (ETM) for instruction tracing.

- Components added outside the Cortex-M7 core:

- A trace funnel to combine the trace sources from the ITM, ETM and MCP down to one trace output (ATBM) before it is sent to the primary CoreSight block.

- A replicator to send the ITM trace output to either SWO or to the system ETR through the system funnel.

- A CTI to support cross triggering with other debug components in the system. This CTI also controls the **REFCLK** generic counter, enabling debug triggers to halt the counter.

- A CTM to connect the CTI triggers from the SCP and MCP to the system funnel, enabling triggering of other system components.

- Timestamp value for the Cortex-M7 core provided by the system generic counter.

- Debug authentication for the SCP core debug domain through the **SCPDBGEN**, **SCPNIDEN**, **SCPSPIDEN**, and **SCPSPNIDEN** input signals.

If you want to trace out the SCP core over the Trace Port Interface Unit (TPIU), you must enable authentication of the system components.

The TPIU that is shown in the SCP code debug domain is used for SWO functionality. The Cortex-M7 TPIU is used for this purpose. Only TRACESWO output is used. This TPIU instance has two ATB input interfaces to support trace sources from both the SCP and MCP cores.

Figure 3-16: High-level view of SCP core debug domain

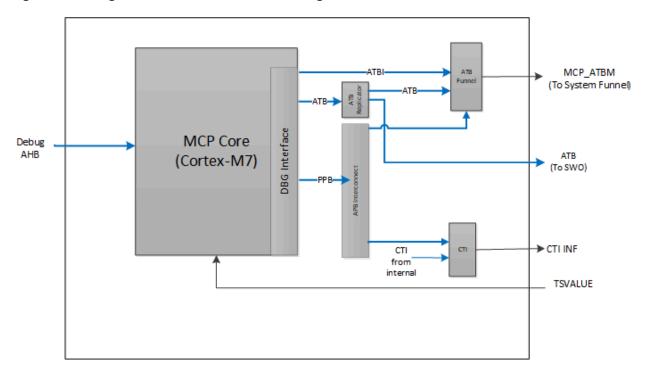

## 3.7.6 MCP core debug support

RD-N2 supports MCP debug.

The following debug support is provided for the MCP core:

- MCP debug ROM tables that enable the debugger to determine which debug components are internal to the Cortex-M7 core and identify others outside the core.

- Components inside the Cortex-M7 core:

- An Flash Patch and Breakpoint (FPB) unit for implementing hardware breakpoints.

- A Data Watch-point and Trace (DWT) unit for implementing watchpoints, data tracing, and system profiling.

- An Instrumentation Trace Macrocell (ITM), which supports printf()-style debugging. This unit generates trace data that is sent to an ATB funnel and to SWO.

- An Embedded Trace Macrocell (ETM) for instruction tracing.

- Components added outside the Cortex-M7 core:

- A trace funnel to combine the trace sources from the ITM and ETM down to one trace output. This output is muxed with the SCP combined trace output before sending it to the system funnel.

- A replicator to send the ITM trace output over SWO. The MCP and SCP ITM trace is muxed onto the same SWD output port.

- A CTI to support cross triggering with other debug components in the system.

- A CTM to connect the triggers from the core and other components in the MCP block to the system funnel, enabling triggering of other system components.

- Timestamp value for the Cortex-M7 core provided by the system generic counter.

- Debug authentication for the MCP core debug domain through the MCPDBGEN, MCPNIDEN, MCPSPIDEN, and MCPSPNIDEN input signals.

If you want to trace out the MCP core over the Trace Port Interface Unit (TPIU), you must enable authentication of the system components.

If you want to trace out the MCP core over SWO, you must enable the SCP core domain authentication signals.

Figure 3-17: High-level view of MCP core debug domain

## 3.7.7 ROM tables

The ROM tables hold the locations of debug components. Debuggers can use the tables to determine which components are implemented.

RD-N2 has multiple ROM tables so that external debuggers can discover all the debug components in the system. The following table lists the types of debug components that can be accessed for each ROM table.

Table 3-1: Components in RD-N2 ROM tables

| Table name   | Table location         | Debug components                                                            |

|--------------|------------------------|-----------------------------------------------------------------------------|

| DP Debug ROM | System debug<br>domain | SCP Cortex-M7 AHB AP.                                                       |

|              |                        | MCP Cortex-M7 AHB AP.                                                       |

|              |                        | SYS DBGROM table.                                                           |

|              |                        | GPR registers for power and reset of PD_SYSTOP and PD_DBGTOP power domains. |

| SYS DBG ROM  | System debug<br>domain | APP APB AP.                                                                 |

|              |                        | DBGCH APB AP.                                                               |

|              |                        | SYSMEM AXI AP.                                                              |

| Table name                  | Table location      | Debug components                                                                                                                              |  |  |  |

|-----------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| APP DBG ROM                 | System debug        | STM ETF.                                                                                                                                      |  |  |  |

|                             | domain              | System ETF.                                                                                                                                   |  |  |  |

|                             |                     | Configurable expansion for system funnels.                                                                                                    |  |  |  |

|                             |                     | Master funnel.                                                                                                                                |  |  |  |

|                             |                     | DBGCH funnel.                                                                                                                                 |  |  |  |

|                             |                     | System ETR.                                                                                                                                   |  |  |  |

|                             |                     | STM.                                                                                                                                          |  |  |  |

|                             |                     | System CTI.                                                                                                                                   |  |  |  |

|                             |                     | System CATU.                                                                                                                                  |  |  |  |

| DBGCH ROM                   | AP debug<br>domain  | CORE <n> SS DBG ROM table.</n>                                                                                                                |  |  |  |

| CORE <n> SS<br/>DBG ROM</n> | AP debug<br>domain  | ETF.                                                                                                                                          |  |  |  |

|                             | domain              | Trace funnel.                                                                                                                                 |  |  |  |

|                             |                     | CTI.                                                                                                                                          |  |  |  |

|                             |                     | Core Debug Block ROM table.                                                                                                                   |  |  |  |

| Core Debug<br>Block ROM     | AP debug<br>domain  | Cluster CTI.                                                                                                                                  |  |  |  |

|                             |                     | PE CTI.                                                                                                                                       |  |  |  |

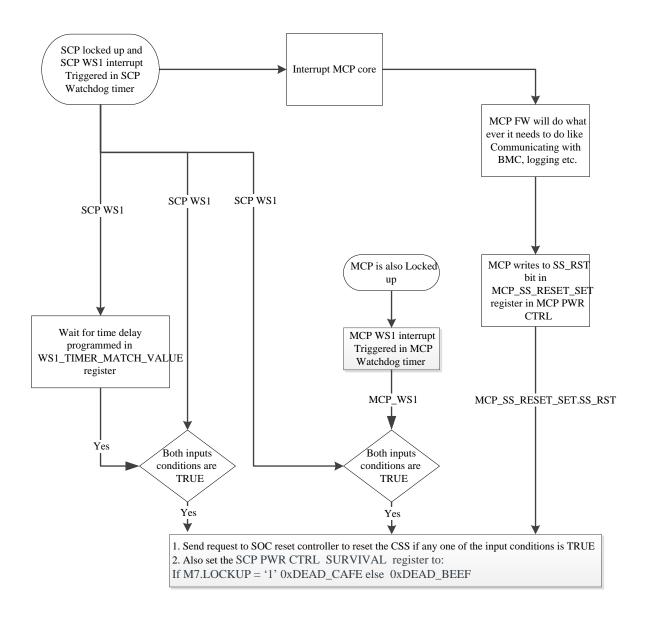

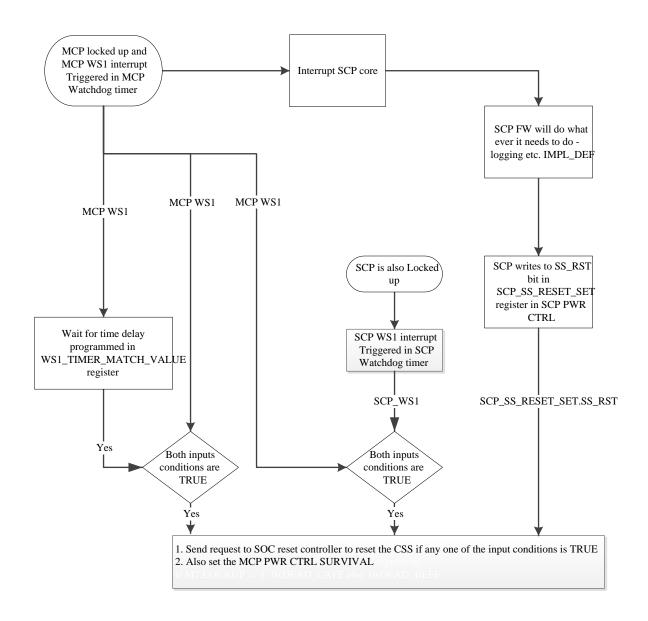

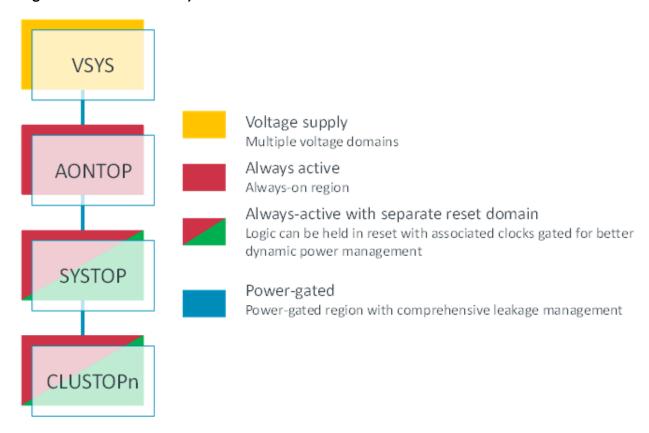

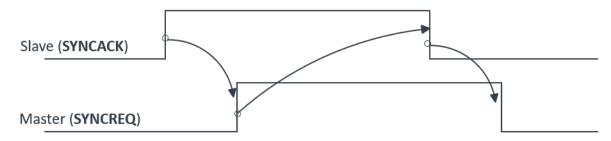

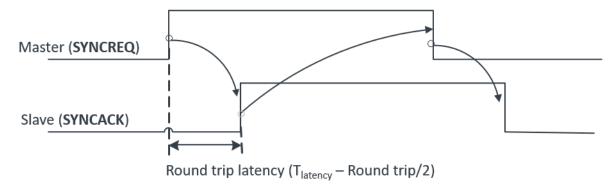

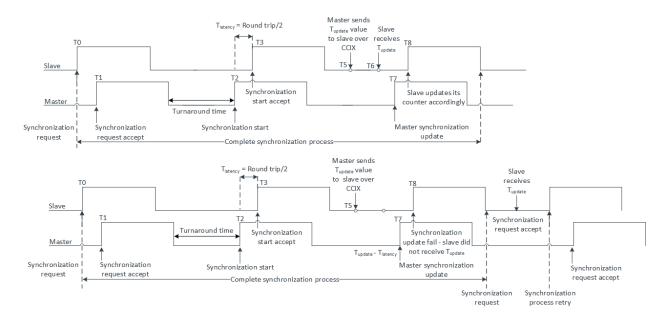

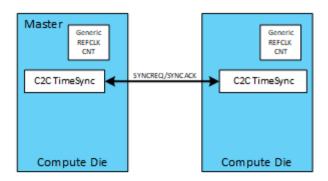

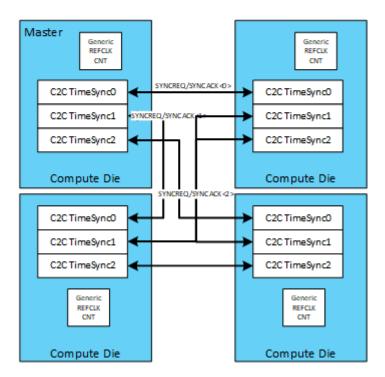

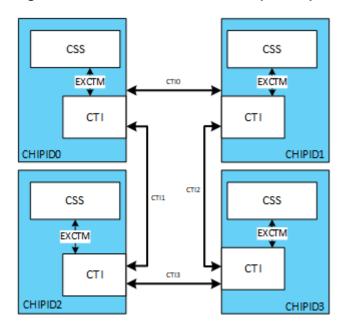

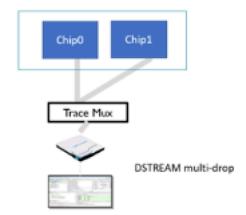

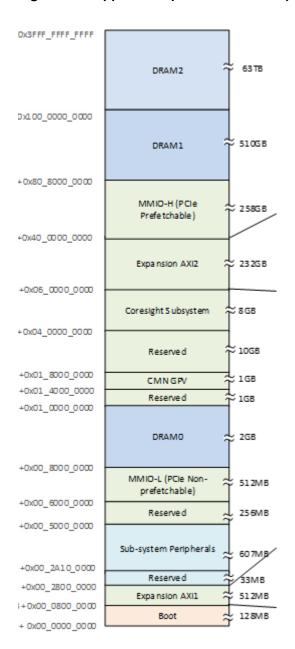

| Cluster ROM                 | AP debug<br>domain  | CoreO ROM table. For information about components in the core DBG ROM, see the Arm <sup>®</sup> Neoverse™ N2 Core Technical Reference Manual. |  |  |  |