## Arm<sup>®</sup> Architecture Reference Manual Supplement Morello for A-profile Architecture

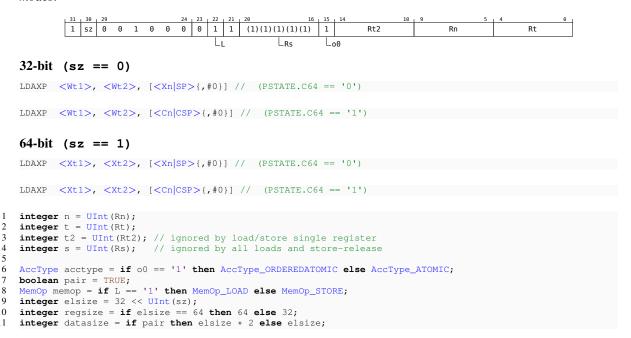

Document number DDI0606

Document version A.k

Document confidentiality Non-confidential

Copyright © 2019-2022 Arm Limited or its affiliates. All rights reserved.

#### Important message

Morello is a prototype architecture, which has a particular meaning to Arm of which the recipient must be aware as follows:

Subject to change without consent of all parties, and it is not committed for product development.

Includes the majority of expected features.

Includes detail on the majority of expected features.

Includes some necessary information from documentation relating to earlier architectures, but some cross-referencing might be necessary.

See the architecture release notes for more detail.

No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

## **Release information**

| Date        | Version  | Changes                                                                                                               |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------|

| 2022/Jan/17 | A.k      | <ul><li>PROTO_REL 04</li><li>PROTO_REL 04 external release</li></ul>                                                  |

| 2021/Jun/25 | A.j      | <ul><li>PROTO_REL 03</li><li>PROTO_REL 03 external release</li></ul>                                                  |

| 2021/Mar/19 | A.i      | <ul><li>PROTO_REL 02</li><li>PROTO_REL 02 external release</li></ul>                                                  |

| 2020/Dec/18 | A.h      | <ul><li>PROTO_REL 01</li><li>PROTO_REL 01 external release</li></ul>                                                  |

| 2020/Oct/28 | A.g      | <ul> <li>PROTO_REL 00</li> <li>PROTO_REL 00 external release</li> <li>CHERI reference updated to version 8</li> </ul> |

| 2020/Sep/30 | A.f      | <ul><li>PROTO_REL 00</li><li>PROTO_REL 00 external release</li></ul>                                                  |

| 2020/Aug/13 | A.e      | <ul><li>PROTO_EAC 01</li><li>PROTO_EAC 01 release, limited circulation</li></ul>                                      |

| 2020/Jul/02 | A.d      | <ul><li>PROTO_EAC 00</li><li>PROTO_EAC release, limited circulation</li></ul>                                         |

| 2020/May/29 | A.c      | <ul><li>Beta 02</li><li>Beta release, limited circulation</li></ul>                                                   |

| 2020/Apr/09 | A.b      | <ul><li>Beta 01</li><li>Beta release, limited circulation</li></ul>                                                   |

| 2020/Mar/25 | A.b      | <ul> <li>Beta 01 RC</li> <li>Beta release candidate, limited circulation</li> </ul>                                   |

| 2020/Jan/20 | Beta 00  | Beta draft, limited circulation                                                                                       |

| 2019/Dec/09 | Alpha 01 | • First draft for review                                                                                              |

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or TM are registered trademarks or trademarks of Arm Limited (or its affiliates) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at http://www.arm.com/company/policies/trademarks

Copyright © 2019-2022 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349 version 21.0

#### **Product Status**

The information in this document is for a prototype extension to the Armv8-A architecture.

#### Changes in PROTO\_REL\_04

[1633]

The Embedded Trace Macrocell Architecture Specification expects instructions to be classified in to direct branches, indirect branches, and not a branch. The Morello specification did not contain enough information to make this classification. This has been corrected by adding a new rule KHQMC.

[1623]

The ASL of the registers CDBGDTR\_EL0 and CDLR\_EL0 is corrected with respect to the trapping due to CPTR\_EL2.CEN at EL2 and EL3.

[1618]

Rule R KDDZF step 10 references to B ie[4] and T ie[4] have been corrected to B ie[3] and T ie[3].

[1616]

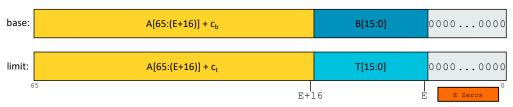

In section 2.5.1 (Morello Bounds format), sub-section "Setting and encoding Bounds", the syntax used for SignExtend() when oE < 48 was incorrect, making it difficult to read. This has been corrected.

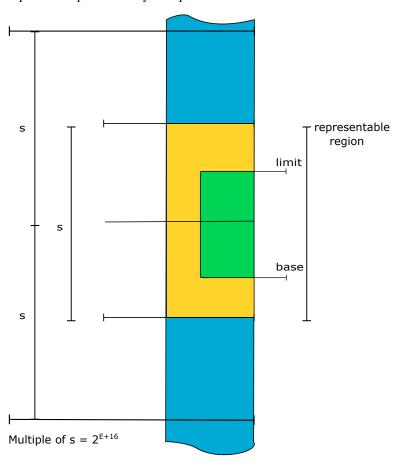

In section 2.5.2 (Representability checks), rule R LMXSB is clarified to describe the guaranteed range of the Capability Value, with respect to the base and the limit.

In section 2.8 (Capability memory relocation), rule R GFXBJ is clarified to apply the CCTLR\_ELx.DDCBO field when executing in ELx.

[1594]

AArch64.SecondStageTranslate() is corrected for the case where the first stage of translation results in a Capability fault due to a store of a valid capability (CDBM == 0 && SC == 1). The second stage translation should not perform the hardware update if the second stage entry has CDBM == 1.

[1593]

The CheckLoadTagsPermission() function is corrected to use the Exception level for the translation regime, instead of the current Exception level.

[1592]

The code in MemAttrDefaults() that initialized fields related to the handling of the LC and SC bits has been removed, because generally these fields have been initialized before this function is called. The initialization code was missing in AArch64.TranslateAddressS1Off(), and so it has been added there.

[1590]

The ASL for MSR (immediate) is corrected to show that writes of SPSel are ignored when the PE is in Restricted.

[1589]

In R KDDZF, step 5 for bounds setting contains a wrong variable E, which has been corrected to E'.

[1585]

The pseudocode functions AArch64.SysInstrInputIsCapability() was incorrectly checking for DC IVAC using op1 == 3 and crm == 6, and has been corrected to check for op1 == 0 and crm == 6.

[1584]

The ASL functions AArch64.MemSingle(), AArch64.CapabilityTag(), MemAtomicCompareAndSwapC(), and MemAtomicC() are updated to correctly handle faulting due to the LC bit on Device memory.

[1582]

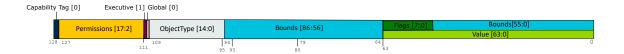

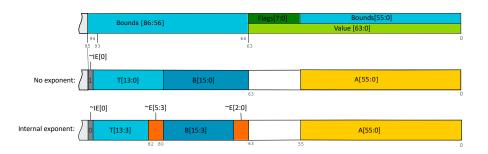

The text in section 2.5.1 describing how the Capability Bounds are decoded was corrected in order to match the related pseudocode in section 5. The specific correction is in the decoding of T[15:14].

[1580]

The description for BLRS (pair of capabilities) is corrected in removing the suggestion that this instruction would perform a switch to Restricted.

[1156]

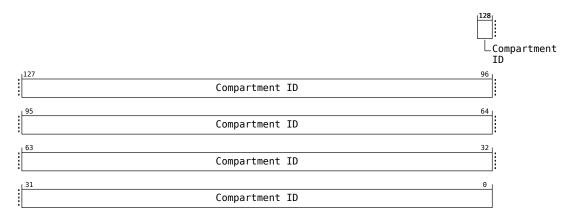

In section 2.9, Compartment ID, the informational text state BYCZR is clarified to explain the intention with respect to how an implementation might use this information.

#### **Known issues**

[635]

The pseudo-instruction "MOV Cn,CZR", which maps to "MOV Xn, XZR", is not described in the instruction set. [626]

The <extend> specifier on the following instructions is shown as a mandatory part of the syntax.

- \* ADD (extended register),

- \* Load/Store with a offset register.

This does not match the syntax for the equivalent instructions in the base architecture

# Arm<sup>®</sup> Architecture Reference Manual Supplement Morello for A-profile Architecture

| About this book                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           | Release information                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------|

| Conventions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Preface   | About this hoot                       |

| Numbers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |                                       |

| Pseudocode descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |                                       |

| Assembler syntax descriptions xxxx Rules-based writing xxxxi leteral l |           |                                       |

| Rules-based writing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           | ·                                     |

| Identifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           | · · · · · · · · · · · · · · · · · · · |

| Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           | •                                     |

| Additional reading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |                                       |

| Arm publications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           | ·                                     |

| Feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           | <del>-</del>                          |

| Feedback on this book                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           | Other publications                    |

| Chapter 1         Introduction           1.1         About the Morello architecture         36           1.2         The CHERI protection model         38           1.3         The Morello architecture in the Armv8-A profile         39           1.3.1         Capability registers and memory         39           1.3.2         Capability tagged memory         39           1.3.3         ISA         39           1.3.4         Controlled non-monotonicity         39           1.3.5         Capability memory protection         40           1.3.6         Capability memory protection for System registers and instructions         40           1.3.7         Capability memory relocation         40           1.3.8         Recursive immutability         41           1.3.9         The Virtual Memory System Architecture         41           1.3.10         Debug and trace         41           1.4         The Morello architecture features         42           Chapter 2         Capability architecture rules           2.1         Capabilities         43           2.2         Capability registers         45           2.3         Chapter Villes         45           2.5 <t< td=""><td></td><td>Feedback</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           | Feedback                              |

| Chapter 1         Introduction           1.1         About the Morello architecture         36           1.2         The CHERI protection model         38           1.3         The Morello architecture in the Armv8-A profile         39           1.3.1         Capability registers and memory         39           1.3.2         Capability tagged memory         39           1.3.3         ISA         39           1.3.4         Controlled non-monotonicity         39           1.3.5         Capability memory protection         40           1.3.6         Capability memory protection         40           1.3.7         Capability memory relocation         40           1.3.8         Recursive immutability         41           1.3.9         The Virtual Memory System Architecture         41           1.3.10         Debug and trace         41           1.4         The Morello architecture features         42           Chapability architecture rules           2.1         Capability registers         45           2.2         Capability registers         45           2.3         Changes to Armv8 terminology         47           2.4         Capability encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           | Feedback on this book                 |

| 1.1       About the Morello architecture       36         1.2       The CHERI protection model       38         1.3       The Morello architecture in the Armv8-A profile       39         1.3.1       Capability registers and memory       39         1.3.2       Capability tagged memory       39         1.3.3       ISA       39         1.3.4       Controlled non-monotonicity       39         1.3.5       Capability memory protection       40         1.3.6       Capability protection for System registers and instructions       40         1.3.7       Capability memory relocation       40         1.3.8       Recursive immutability       41         1.3.9       The Virtual Memory System Architecture       41         1.3.10       Debug and trace       41         1.4       The Morello architecture features       42         Chaptility architecture rules         2.1       Capabilitites       43         2.2       Capability registers       45         2.3       Changes to Armv8 terminology       47         2.4       Capability encoding       49         2.5.1       Morello Bounds format       50         2.5.2       Representabilit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           | Progressive terminology commitment    |

| 1.1       About the Morello architecture       36         1.2       The CHERI protection model       38         1.3       The Morello architecture in the Armv8-A profile       39         1.3.1       Capability registers and memory       39         1.3.2       Capability tagged memory       39         1.3.3       ISA       39         1.3.4       Controlled non-monotonicity       39         1.3.5       Capability memory protection       40         1.3.6       Capability protection for System registers and instructions       40         1.3.7       Capability memory relocation       40         1.3.8       Recursive immutability       41         1.3.9       The Virtual Memory System Architecture       41         1.3.10       Debug and trace       41         1.4       The Morello architecture features       42         Chaptility architecture rules         2.1       Capabilitites       43         2.2       Capability registers       45         2.3       Changes to Armv8 terminology       47         2.4       Capability encoding       49         2.5.1       Morello Bounds format       50         2.5.2       Representabilit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Chanter 1 | Introduction                          |

| 1.2       The CHERI protection model       38         1.3       The Morello architecture in the Armv8-A profile       39         1.3.1       Capability registers and memory       39         1.3.2       Capability tagged memory       39         1.3.3       ISA       39         1.3.4       Controlled non-monotonicity       39         1.3.5       Capability memory protection       40         1.3.6       Capability protection for System registers and instructions       40         1.3.7       Capability memory relocation       40         1.3.8       Recursive immutability       41         1.3.9       The Virtual Memory System Architecture       41         1.3.10       Debug and trace       41         1.4       The Morello architecture features       42         Chaptility architecture rules         2.1       Capability architecture rules         2.2       Capability registers       45         2.3       Changes to Armv8 terminology       47         2.4       Capability encoding       49         2.5.1       Morello Bounds format       50         2.5.2       Representability checks       55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Onapier i |                                       |

| 1.3       The Morello architecture in the Armv8-A profile       39         1.3.1       Capability registers and memory       39         1.3.2       Capability tagged memory       39         1.3.3       ISA       39         1.3.4       Controlled non-monotonicity       39         1.3.5       Capability memory protection       40         1.3.6       Capability protection for System registers and instructions       40         1.3.7       Capability memory relocation       40         1.3.8       Recursive immutability       41         1.3.9       The Virtual Memory System Architecture       41         1.4       The Morello architecture features       42         Chapter 2       Capability architecture rules         2.1       Capability registers       43         2.2       Capability registers       43         2.2       Capability registers       43         2.3       Changes to Armv8 terminology       47         2.4       Capabilities in memory       48         2.5       Capability encoding       49         2.5.1       Morello Bounds format       50         2.5.2       Representability checks       55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |                                       |

| 1.3.1       Capability registers and memory       39         1.3.2       Capability tagged memory       39         1.3.3       ISA       39         1.3.4       Controlled non-monotonicity       39         1.3.5       Capability memory protection       40         1.3.6       Capability protection for System registers and instructions       40         1.3.7       Capability memory relocation       40         1.3.8       Recursive immutability       41         1.3.9       The Virtual Memory System Architecture       41         1.3.10       Debug and trace       41         1.4       The Morello architecture features       42         Chapter 2       Capability architecture rules         2.1       Capability registers       42         2.2       Capability registers       43         2.2       Capability registers       43         2.2       Capabilities in memory       48         2.3       Changes to Armv8 terminology       47         2.4       Capabilities in memory       48         2.5       Capability encoding       49         2.5.1       Morello Bounds format       50         2.5.2       Representability checks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |                                       |

| 1.3.2       Capability tagged memory       39         1.3.3       ISA       39         1.3.4       Controlled non-monotonicity       39         1.3.5       Capability memory protection       40         1.3.6       Capability protection for System registers and instructions       40         1.3.7       Capability memory relocation       40         1.3.8       Recursive immutability       41         1.3.9       The Virtual Memory System Architecture       41         1.3.10       Debug and trace       41         1.4       The Morello architecture features       42         Chapter 2       Capability architecture rules         2.1       Capabilities       43         2.2       Capability registers       45         2.3       Changes to Armv8 terminology       47         2.4       Capability encoding       49         2.5.1       Morello Bounds format       50         2.5.2       Representability checks       55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           | ·                                     |

| 1.3.4   Controlled non-monotonicity   39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           | · · · · · · · · · · · · · · · · · · · |

| 1.3.5       Capability memory protection       40         1.3.6       Capability protection for System registers and instructions       40         1.3.7       Capability memory relocation       40         1.3.8       Recursive immutability       41         1.3.9       The Virtual Memory System Architecture       41         1.4       The Morello architecture features       42         Chapter 2       Capability architecture rules         2.1       Capabilities       43         2.2       Capability registers       45         2.3       Changes to Armv8 terminology       47         2.4       Capabilities in memory       48         2.5       Capability encoding       49         2.5.1       Morello Bounds format       50         2.5.2       Representability checks       55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           | 1.3.3 ISA                             |

| 1.3.6   Capability protection for System registers and instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           | 1.3.4 Controlled non-monotonicity     |

| 1.3.7       Capability memory relocation       40         1.3.8       Recursive immutability       41         1.3.9       The Virtual Memory System Architecture       41         1.3.10       Debug and trace       41         1.4       The Morello architecture features       42         Chapter 2         Capability architecture rules         2.1       Capabilities       43         2.2       Capability registers       45         2.3       Changes to Armv8 terminology       47         2.4       Capabilities in memory       48         2.5       Capability encoding       49         2.5.1       Morello Bounds format       50         2.5.2       Representability checks       55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           | ' ' '                                 |

| 1.3.8       Recursive immutability       41         1.3.9       The Virtual Memory System Architecture       41         1.3.10       Debug and trace       41         1.4       The Morello architecture features       42         Chapter 2         Capability architecture rules         2.1       Capabilities       43         2.2       Capability registers       45         2.3       Changes to Armv8 terminology       47         2.4       Capabilities in memory       48         2.5       Capability encoding       49         2.5.1       Morello Bounds format       50         2.5.2       Representability checks       55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           | , ,,                                  |

| 1.3.9       The Virtual Memory System Architecture       41         1.3.10       Debug and trace       41         1.4       The Morello architecture features       42         Chapter 2         Capability architecture rules       2.1       Capabilities       43         2.2       Capability registers       45         2.3       Changes to Armv8 terminology       47         2.4       Capabilities in memory       48         2.5       Capability encoding       49         2.5.1       Morello Bounds format       50         2.5.2       Representability checks       55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           | · · · · · · · · · · · · · · · · · · · |

| 1.3.10       Debug and trace       41         1.4       The Morello architecture features       42         Chapter 2         Capability architecture rules       2.1       Capabilities       43         2.2       Capability registers       45         2.3       Changes to Armv8 terminology       47         2.4       Capabilities in memory       48         2.5       Capability encoding       49         2.5.1       Morello Bounds format       50         2.5.2       Representability checks       55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           | · · · · · · · · · · · · · · · · · · · |

| 1.4       The Morello architecture features       42         Chapter 2       Capability architecture rules       3         2.1       Capabilities       43         2.2       Capability registers       45         2.3       Changes to Armv8 terminology       47         2.4       Capabilities in memory       48         2.5       Capability encoding       49         2.5.1       Morello Bounds format       50         2.5.2       Representability checks       55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           | • •                                   |

| Chapter 2         Capability architecture rules           2.1         Capabilities         43           2.2         Capability registers         45           2.3         Changes to Armv8 terminology         47           2.4         Capabilities in memory         48           2.5         Capability encoding         49           2.5.1         Morello Bounds format         50           2.5.2         Representability checks         55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           | · · · · · · · · · · · · · · · · · · · |

| 2.1       Capabilities       43         2.2       Capability registers       45         2.3       Changes to Armv8 terminology       47         2.4       Capabilities in memory       48         2.5       Capability encoding       49         2.5.1       Morello Bounds format       50         2.5.2       Representability checks       55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           | 1.4 The Morello architecture features |

| 2.1       Capabilities       43         2.2       Capability registers       45         2.3       Changes to Armv8 terminology       47         2.4       Capabilities in memory       48         2.5       Capability encoding       49         2.5.1       Morello Bounds format       50         2.5.2       Representability checks       55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Chapter 2 | Capability architecture rules         |

| 2.2       Capability registers       45         2.3       Changes to Armv8 terminology       47         2.4       Capabilities in memory       48         2.5       Capability encoding       49         2.5.1       Morello Bounds format       50         2.5.2       Representability checks       55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           | •                                     |

| 2.3       Changes to Armv8 terminology       47         2.4       Capabilities in memory       48         2.5       Capability encoding       49         2.5.1       Morello Bounds format       50         2.5.2       Representability checks       55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           | ·                                     |