# Morello Platform Model

Version 2.0

# Reference Guide

Non-Confidential

Issue 00

Copyright © 2020–2021 Arm Limited (or its affiliates).  $102225\_0200\_00\_en$ All rights reserved.

### Morello Platform Model

#### Reference Guide

Copyright © 2020–2021 Arm Limited (or its affiliates). All rights reserved.

#### Release Information

#### **Document history**

| Issue   | Date             | Confidentiality  | Change                                        |

|---------|------------------|------------------|-----------------------------------------------|

| 0100-00 | 29 October 2020  | Non-Confidential | First release                                 |

| 0101-00 | 11 December 2020 | Non-Confidential | Update for Morello Platform Model version 1.1 |

| 0102-00 | 26 February 2021 | Non-Confidential | Update for Morello Platform Model version 1.2 |

| 0103-00 | 14 May 2021      | Non-Confidential | Update for Morello Platform Model version 1.3 |

| 0200-00 | 6 October 2021   | Non-Confidential | Update for Morello Platform Model version 2.0 |

### **Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND

# REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or ™ are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at https://www.arm.com/company/policies/trademarks.

Copyright © 2020–2021 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

(LES-PRE-20349)

# **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

#### **Product Status**

The information in this document is Final, that is for a developed product.

### Web Address

developer.arm.com

# Inclusive language commitment

Arm values inclusive communities. Arm recognizes that we and our industry have used language that can be offensive. Arm strives to lead the industry and create change.

We believe that this document contains no offensive language. To report offensive language in this document, email terms@arm.com.

# **Contents**

| 1 Introduction                                               | 6  |

|--------------------------------------------------------------|----|

| 1.1 Conventions                                              | 6  |

| 1.2 Feedback                                                 | 7  |

| 1.3 Other information                                        | 7  |

| 2 Introduction to the Morello Platform Model                 | 8  |

| 2.1 About the Morello Platform Model                         | 8  |

| 2.2 High-level block diagram                                 | 9  |

| 2.3 Host prerequisites                                       | 10 |

| 2.4 Additional reading                                       | 10 |

| 3 Get started                                                | 12 |

| 3.1 Install the package                                      | 12 |

| 3.2 What is in the package?                                  | 12 |

| 3.3 Verify the installation                                  | 15 |

| 3.4 What software is available?                              | 15 |

| 4 Reference information                                      | 16 |

| 4.1 Morello Platform Model notes and limitations             | 16 |

| 4.2 Command-line options                                     | 17 |

| 4.3 CMN-Skeena topology configuration and connection diagram | 22 |

| 4.4 Morello-specific changes to tarmac trace                 | 23 |

| 4.4.1 File format changes                                    | 23 |

| 4.4.2 Instruction trace changes                              | 23 |

| 4.4.3 Register trace changes                                 | 24 |

| 4.4.4 Processor memory access trace changes                  | 24 |

| 4.5 ToggleMTIPlugin                                          | 25 |

| 4.6 Morello Platform Model instances                         | 26 |

# 1 Introduction

# 1.1 Conventions

The following subsections describe conventions used in Arm documents.

### Glossary

The Arm® Glossary is a list of terms used in Arm documentation, together with definitions for those terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

See the Arm Glossary for more information: developer.arm.com/glossary.

### Typographic conventions

| Convention                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Use                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| italic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Introduces citations.                                                                                                                                                                                        |

| bold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.                                                                        |

| monospace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.                                                                                                  |

| monospace bold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Denotes language keywords when used outside example code.                                                                                                                                                    |

| monospace <u>underline</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.                                                                      |

| <and></and>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example:                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MRC p15, 0, <rd>, <crn>, <opcode_2></opcode_2></crn></rd>                                                                                                                                                    |

| SMALL CAPITALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Used in body text for a few terms that have specific technical meanings, that are defined in the<br>Arm® Glossary. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE. |

| Caution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | This represents a recommendation which, if not followed, might lead to system failure or damage.                                                                                                             |

| Warning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | This represents a requirement for the system that, if not followed, might result in system failure or damage.                                                                                                |

| Danger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | This represents a requirement for the system that, if not followed, will result in system failure or damage.                                                                                                 |

| Note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | This represents an important piece of information that needs your attention.                                                                                                                                 |

| - Control of the cont | This represents a useful tip that might make it easier, better or faster to perform a task.                                                                                                                  |

| Convention | Use                                                                                        |

|------------|--------------------------------------------------------------------------------------------|

| Remember   | This is a reminder of something important that relates to the information you are reading. |

### 1.2 Feedback

Arm welcomes feedback on this product and its documentation.

### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

#### Feedback on content

Information about how to give feedback on the content.

If you have comments on content then send an e-mail to errata@arm.com. Give:

- The title Morello Platform Model Reference Guide.

- The number 102225 0200 00 en.

- If applicable, the page number(s) to which your comments refer.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

Arm tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader.

# 1.3 Other information

See the Arm® website for other relevant information.

- Arm<sup>®</sup> Developer.

- Arm® Documentation.

- Technical Support.

- Arm<sup>®</sup> Glossary.

# 2 Introduction to the Morello Platform Model

This chapter contains a high-level description of the Morello Platform Model, and gives links to further information.

# 2.1 About the Morello Platform Model

The Morello Platform Model is a software model of the Morello System on Chip (SoC) hardware platform.

It is freely available for download from the Arm® Developer website, does not require a license, and runs on Linux host machines only.

The Morello Platform Model is a Fixed Virtual Platform (FVP). An FVP is a pre-built model that consists of a hierarchy of model components connected together to form a system. Although the composition of an FVP is fixed, you can configure its behavior using parameters. You can also load plug-in libraries to provide extra functionality.

FVPs enable applications and operating systems to be written and debugged without the need for real hardware. They work by translating Arm® instructions into the instruction set of the host dynamically and use optimization techniques to improve performance. So, while they are functionally accurate, they do not provide accurate timing information or cycle counts.

FVPs have several benefits over the hardware they model:

#### Early availability

FVPs are available much earlier than hardware, which enables software development ahead of hardware availability.

#### Software compatibility

As the same software stack runs on both the model and the hardware, you can use the same toolchain to build for both targets.

#### Configurable

FVPs can be easily customized by using parameters to test different configurations. To see the available parameters, run the FVP with the --list-params option.

#### Debuggable

The Morello Platform Model supports the CADI interface which enables debuggers to connect to it and debug it. You can use Arm Debugger in the Arm® Development Studio Morello Edition to work with the Morello Platform Model.

#### **Trace support**

The Morello Platform Model supports Model Trace Interface (MTI), which enables you to use plug-ins to output trace information from the FVP. The Morello Platform Model package includes several pre-built trace plug-ins.

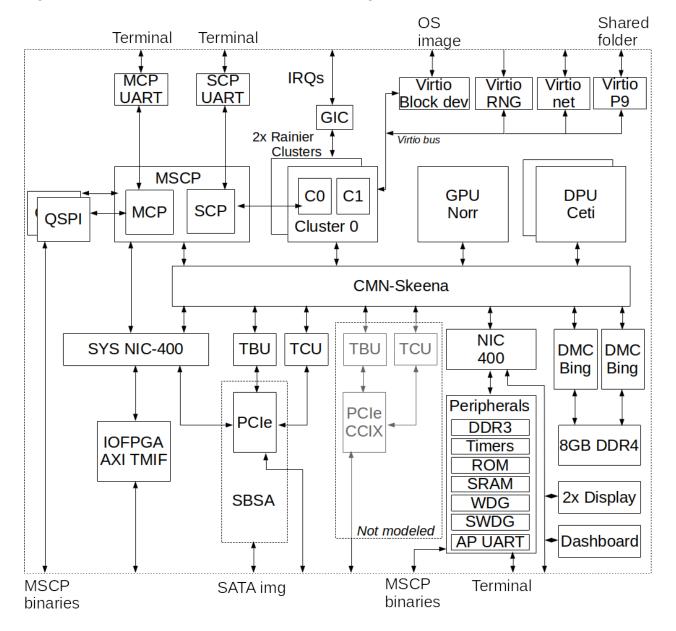

# 2.2 High-level block diagram

This simplified block diagram shows the SoC and board peripherals.

Figure 2-1: Morello Platform Model system block diagram

# 2.3 Host prerequisites

The Morello Platform Model supports the following host operating systems and compilers.

#### Operating system

The FVP requires a Linux x86-64 host. It has been tested with Ubuntu 18.04 but should also work with later versions.

The following GCC-6.4 compatible libraries must be installed on the host:

- /lib64/ld-linux-x86-64.so.2

- libatomic.so.1

- libc.so.6

- libdbus-1.so.3

- libdl.so.2

- libgcc s.so.1

- libgcrypt.so.20

- libgpg-error.so.0

- liblz4.so.1

- liblzma.so.5

- libm.so.6

- libpthread.so.0

- librt.so.1

- libstdc++.so.6

- libsystemd.so.0

- linux-vdso.so.1

#### Other requirements

- A shell compatible with sh, such as bash or tesh. If you want to change terminals use the terminal command parameter to select a different console program.

- If you want to use the host GPU for rendering pixels, you must install the Mali™ OpenGL ES emulator from OpenGL ES Emulator Downloads. Follow the steps described in the documentation included in the download package.

# 2.4 Additional reading

This section lists other publications and websites from Arm that are relevant to the Morello Platform Model.

• To learn more about the Morello program and architecture, see Arm Morello Program.

- To learn more about the Open Source Software targeting this FVP, see Morello Project.

- A preliminary Technical Reference Manual (TRM) for this FVP is available at Arm® Morello System Development Platform (SDP) Preliminary Technical Reference Manual.

- To learn about software development for Morello using Arm Development Studio, read Arm Development Studio Morello Edition Getting Started Guide and Arm Development Studio Morello Edition User Guide.

- To learn more about Fast Models, see Fast Models on Arm Developer.

# 3 Get started

This chapter describes how to download and install the Morello Platform Model package, and verify the installation.

# 3.1 Install the package

The Morello Platform Model package is installed using a command-line installer.

#### About this task

Follow these steps to download and install the package:

#### **Procedure**

- 1. Download the package from the Arm Ecosystem FVPs page.

- 2. Uncompress the tarball:

```

tar -xzf FVP_Morello_x.xx_xxx.tgz

```

where x indicates the model version number. For example, FVP Morello 0.10 310.tgz.

3. Run the installation shell script:

```

./FVP_Morello.sh

```

- 4. Read and agree to the terms and conditions and select the directory to install to.

- 5. When installation has finished, the model, called FVP\_Morello, can be found in <install\_directory</pre>/FVP\_Morello/models/Linux64\_GCC-x.x/.

where x indicates the GCC version number. For example, /Linux64\_GCC-6.4.

#### Results

To uninstall the package, remove the installation folder.

# 3.2 What is in the package?

The package contains the FVP binary, libraries that it uses, documentation, and some plug-in libraries.

The contents of the Morello Platform Model installation are:

```

FVP_Morello/

doc

Morello_FVP_ReleaseNotes.txt

morello_platform_model_rg_102225_0200_00_en.pdf

fmtplib

libstdc++.so.6

libstdc++.so.6-gdb.py

LICENSE

install_history

```

```

license terms

license agreement.txt

redistributables.txt

supplementary_terms.txt

third_party_licenses.txt

models

Linux64 GCC-6.4

- checkerrcode.ini

cmn600 morello skeena topology.yml

- FVP_Morello

- FVP Morello.so

libarmctmodel.so

- libMAXCOREInitSimulationEngine.3.so

libnomali.so

libReconciler.so

- libSDL2-2.0.so.0.10.0

settings.ini

- Sidechannel.so

plugins

Linux64 GCC-6.4

ArchMsqTrace.so

GDBRemoteConnection.so

- GenericCounter.so

GenericTrace.so

ListTraceSources.so

MTS.so

TarmacText.so

TarmacTrace.so

- ToggleMTIPlugin.so

ARM Fast Models FVP Morello

rev

9 directories, 31 files

```

#### doc

Contains release notes and a PDF version of the Morello Platform Model Reference Guide (this document).

#### fmtplib

Contains GCC runtime libraries to allow you to run the FVP on older Linux distributions.

The runtime.sh script that installed these libraries in previous releases is no longer required. The model now searches for the libraries in the fmtplib directory.

#### license-terms

Contains the copyright and license information for third-party software, and the standard FVP end-user license agreement.

#### models

Contains the GCC build of the Morello Platform Model, FVP\_Morello, and the libraries that it requires.

#### plugins

Plug-ins are libraries that provide extra functionality for the FVP, for instance trace output. To load a plug-in, specify it when launching the FVP using the --plugin command-line option, or use the FM TRACE PLUGINS environment variable.

The following plug-ins are included in the Morello Platform Model package. Most of them are documented in the Fast Models Reference Manual, see Plug-ins for Fast Models for details.

### ArchMsgTrace

Prints warnings and error messages to stdout or to a file when the core executes code that is unsafe or not recommended.

#### **GDBRemoteConnection**

Allows the model to be debugged using GDB.

#### GenericCounter

At the end of the simulation prints to stdout the number of occurrences of a specific trace source.

#### GenericTrace

Prints trace information, specified using a comma-separated list of trace sources, to stdout or to a file.

#### ListTraceSources

Displays a list of the trace sources that the model provides, without running the model.

#### **MTS**

Used by Arm® Debugger in Arm® Development Studio Morello Edition to report instructions and exceptions that were captured during the simulation.

#### **TarmacText**

Extracts the architectural execution trace, known as Tarmac trace, of the processor. This might include instructions, program flow, or memory accesses. TarmacText extracts the trace in a textual form and saves it in a file.

#### **TarmacTrace**

Prints Tarmac trace information to stdout or to a file. Parameters control the amount and type of information that is traced. The Tarmac trace file format is documented in the Fast Models Reference Manual, see TarmacTrace file format. Some changes to the file format have been made for Morello. For details, see 4.4 Morello-specific changes to tarmac trace on page 22.

#### **ToggleMTIPlugin**

Toggles trace generation on or off during the simulation. See 4.5 ToggleMTIPlugin on page 24 for details.

# 3.3 Verify the installation

Run the FVP manually from the command line to verify that it has installed correctly on the host machine.

#### About this task

You would not typically launch the Morello Platform Model in this way. For most expected use cases, the FVP requires the Open Source Software stack and is launched using a script to simplify the process, see 3.4 What software is available? on page 15 for details.

#### **Procedure**

- 1. In the terminal, change to the directory where you installed the Morello Platform Model. For example: cd ~/FVP Morello/models/Linux64\_GCC-6.4

- 2. Launch the Morello Platform Model with the --list-params option, for example: ./ FVP Morello --list-params.

The --list-params option prints a list of model parameters to the terminal. For a description of all the available command-line options, see 4.2 Command-line options on page 17.

### 3.4 What software is available?

The Morello Platform Model is typically used with a compatible Open Source Software (OSS) stack.

- Arm provides an integrated OSS stack for the Morello platform with scripts to build and run it.

- Arm Development Studio Morello Edition provides comprehensive support for all software development projects on the Morello platform. It also provides a selection of examples to help you get started with the Morello platform.

- An LLVM compiler with Morello support is available, with Morello code examples included.

To find out more about the OSS stack configurations supported on the model and the Morello-aware LLVM toolchain, see the Morello software page.

For technical support, see the Morello forum on Arm Community.

# 4 Reference information

This chapter provides reference information for the Morello Platform Model including differences between the model implementation and the Morello specification, command-line options, and a list of model component instances.

For more information about the Morello program see the Arm Morello Program page.

- For the Morello Platform memory maps and interrupt maps, see Chapter 4

Programmers model, in the Arm® Morello System Development Platform (SDP)

Preliminary Technical Reference Manual.

- For information about additional devices available in the Morello Platform Model, see 4.1 Morello Platform Model notes and limitations on page 16.

# 4.1 Morello Platform Model notes and limitations

The model is implemented according to the Morello TRM with some exceptions.

- Dual DPU Ceti has been integrated into the model.

- PCIe CCIX has not been integrated into the model.

#### Trace

- Several Morello-specific trace sources have been added, and some extra fields have been added to existing trace sources. To display the list of available trace sources and their fields, use the ListTraceSources plug-in as described in the Fast Models Reference Manual.

- Some changes have been made to the TarmacTrace format to represent Morello-specific state and events. These are documented in 4.4 Morello-specific changes to tarmac trace on page 22.

- Some Morello-specific states are not fully captured in the trace:

- The clearing of capability tags performed by non-capability stores is not reflected in the trace.

- Executive/Restricted (both transitions and the current state) are not directly reflected in the trace, although can be deduced from the traced value of PCC.

- Writes to x registers are sometimes inconsistently traced as writes to the corresponding c register. When they are traced as writes to the x register, zero-extension into the upper bits of the capability is implicit. The OLD\_VALUE field might be incorrect between writes to the same x and c register.

- The squashing of mutable permissions and the tag of a capability loaded from memory using a capability without Loadcap Or MutableLoad permissions is not reflected in the trace. Instead, the traced value can

either include or exclude the squashing, controlled by the cluster parameter trace\_squashed\_mutable\_perms\_and\_tag\_in\_loads.

These issues are expected to be addressed in a future release of the model.

#### **Performance**

The performance of model version 1.x when using Morello features, in particular memory accesses, was reduced. Model version 2.0 is 2x faster than previous versions by implementing Direct Memory Interface (DMI) in the Rainier CPU model.

#### Rainier IMPLEMENTATION DEFINED registers and behavior

The Rainier CPU model supports the Morello-specific IMPLEMENTATION DEFINED Performance Monitor Unit (PMU) events. For details about these events, see the Morello prototype architecture specifications.

#### Additional devices

The following devices are present in the Morello Platform Model but are not present in the hardware:

Table 4-1: Additional devices in the model

| Device            | Memory range               | IRQ |

|-------------------|----------------------------|-----|

| virtioblockdevice | 0x1C17_0000 to 0x1C17_FFFF | 96  |

| virtio_net        | 0x1C18_0000 to 0x1C18_FFFF | 102 |

| virtio_rng        | 0x1C19_0000 to 0x1C19_FFFF | 101 |

| virtio_p9 1       | 0x1C1A_0000 to 0x1C1A_FFFF | 103 |

# 4.2 Command-line options

Use these options to configure the FVP when launching it from the command line. Each table groups together related options. For a listing of these options with brief descriptions, run the model with --help.

Table 4-2: CADI-related options

| Short form | Long form   | Description                                                                                                                                                                                                               |

|------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>-</b> S | cadi-server | Start a CADI server. This option allows a CADI-enabled debugger to connect to targets in the simulation. To shut down the server, return to the command window that you used to start the model and press <b>Ctrl+C</b> . |

| -R         | run         | Run the simulation immediately after the CADI server is started.  Use this option withcadi-server.  The default is to wait until the debugger has connected before running the simulation.                                |

<sup>&</sup>lt;sup>1</sup> The virtio\_p9 device allows you to share a folder between the host and the FVP. See the Morello Platform Model release notes for instructions on building a guest OS that enables the virtio\_p9 device. For further instructions on how to configure and use it, see VirtioP9Device in the Fast Models Reference Manual.

| Short<br>form | Long form         | Description                                                                                                                 |

|---------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------|

| -L            | cadi-log          | Log all CADI function calls made during the simulation into XML files.                                                      |

|               |                   | One log file is created for each CADI target. The log files are created in the current working directory.                   |

|               |                   | The filename format is:                                                                                                     |

|               |                   | CADIlog- <targetinstancename>-<processid>.xml</processid></targetinstancename>                                              |

| -p            | print-port-number | Print the port number on which the CADI server is listening.                                                                |

|               |                   | <b>Tip:</b> This option can be useful if you need to specify the port number when you connect a client to the debug server. |

### Table 4-3: Output-related options

| Short<br>form | Long form           | Description                                                                                                                                |

|---------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

|               | list-instances      | Print a list of model instances to standard output, then exit the simulation.                                                              |

|               |                     | Use this option to help identify the correct syntax for configuration files, and to find out what instances the target supplies.           |

| -1            | list-params         | Print a list of model parameters to standard output, then exit the simulation.                                                             |

|               |                     | <b>Tip:</b> If you load a plug-in, this option also lists the plug-in parameters.                                                          |

|               | list-regs           | Print model register information to standard output, then exit the simulation.                                                             |

|               | check-regs          | Same aslist-regs but with extra consistency checks on the CADI register API.                                                               |

|               | list-memory         | Print memory information to standard output, then exit the simulation.                                                                     |

| -0            | output filename     | Redirect output from thelist-instances,list-memory,list-params, andlist-regs options to a file.                                            |

|               |                     | If this option is used withlist-params, the contents of the output file are formatted correctly for use as input by theconfig-file option. |

|               | dump file@addr,size | Dump a section of memory to a file at model shutdown. This option can be specified multiple times. The full syntax is:                     |

|               |                     | dump [instance=]file@[memspace:]address,size                                                                                               |

|               |                     | Tip: To see the list of instances and memory spaces, use thelist-memory option.                                                            |

|               | data file@addr      | Write raw data contained in $file$ to the specified address. This option can be specified multiple times. The full syntax is:              |

|               |                     | data [instance=]file@[memspace:]address                                                                                                    |

|               | log filename        | Log all SystemC reports into filename.                                                                                                     |

| Short<br>form | Long form | Description                                                                                                   |

|---------------|-----------|---------------------------------------------------------------------------------------------------------------|

|               | stat      | Print the following performance statistics on simulation exit:                                                |

|               |           | Simulated time                                                                                                |

|               |           | An estimate of the time that the workload would have taken on the modeled hardware.                           |

|               |           | User time                                                                                                     |

|               |           | Time in wall clock seconds that the host CPU spent running in user mode.                                      |

|               |           | System time                                                                                                   |

|               |           | Time in wall clock seconds that the host CPU spent running in system mode.                                    |

|               |           | Wall time                                                                                                     |

|               |           | Time in wall clock seconds between the simulation starting and stopping.                                      |

|               |           | Performance index                                                                                             |

|               |           | An estimate of the accuracy of the simulation performance. This value is Simulated time divided by Wall time. |

| -P            | prefix    | Prefix each line of semihosting output with the name of the target instance.                                  |

| -h            | help      | Print the help message and exit.                                                                              |

|               | version   | Print version information.                                                                                    |

| -q            | quiet     | Suppress informational output.                                                                                |

### Table 4-4: Run control options

| Short form | Long form    | Description                                                                                                                                                                  |

|------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | cpulimit n   | Maximum number of wall-clock seconds for the simulation process to be active. This value excludes simulation startup and shutdown.                                           |

|            |              | This option is ignored if a debug server is started.                                                                                                                         |

|            |              | The default is unlimited.                                                                                                                                                    |

|            | cyclelimit n | Maximum number of cycles to run.                                                                                                                                             |

|            |              | This option is ignored if a debug server is started.                                                                                                                         |

|            |              | The default is unlimited.                                                                                                                                                    |

| -T         | timelimit n  | Maximum number of wall-clock seconds for the simulation to run, excluding startup and shutdown. To terminate the model immediately after initialization, specifytimelimit 0. |

|            | simlimit n   | Maximum number of seconds to simulate.                                                                                                                                       |

|            |              | This option is ignored if a debug server is started.                                                                                                                         |

|            |              | The default is unlimited.                                                                                                                                                    |

|            |              | Like the Simulated time value output bystat, this value is measured in simulation seconds, not wall-clock seconds.                                                           |

| Short<br>form | Long form              | Description                                                                                                                                                                                            |

|---------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -b            | break [instance=] addr | Set a program breakpoint on the address of an instruction.                                                                                                                                             |

|               |                        | This option can be specified multiple times.                                                                                                                                                           |

|               |                        | For an FVP with multiple cores, you must specify an instance, for example:                                                                                                                             |

|               |                        | -b FVP_Morello.cluster0.cpu0=0x80000278                                                                                                                                                                |

|               | start [instance=] addr | Set the initial PC value to this address, overriding the <code>.axf</code> start address.                                                                                                              |

|               |                        | Note:                                                                                                                                                                                                  |

|               |                        | <ul> <li>Use this option if you do not want the CPU to start executing at the default reset address. You do not normally need to do this if you are loading an ELF file usingap\ plication.</li> </ul> |

|               |                        | This option can be used withdata to load binary data that is not in an ELF file.                                                                                                                       |

### Table 4-5: Timing and performance options

| Short<br>form | Long form          | Description                                                                                                                               |

|---------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

|               | cpi-file filename  | Use filename to set the Cycles Per Instruction (CPI) class.                                                                               |

|               |                    | For more information, see CPI files in Fast Models User Guide.                                                                            |

| -Q            | quantum <i>n</i>   | Number of ticks to simulate for each quantum. The default is 10000.                                                                       |

| -м            | min-sync-latency n | Number of ticks to simulate before synchronizing. Events that occur at a higher frequency than this value are missed. The default is 100. |

### **Table 4-6: Configuration options**

| Short<br>form | Long form          | Description                                                                                                                                                             |

|---------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | stance.param=value | Set a parameter. This option can be specified multiple times. Specify the full hierarchical name of the parameter.  This option is also used to set plug-in parameters. |

| -f            |                    | Load parameters from a configuration file.                                                                                                                              |

### Table 4-7: Options for loading a plug-in or application

| Short form | Long form | Description                                                                                                                             |

|------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| -a         |           | Load an application.  Specify the core instance to load the application image onto, or use * to load it on multiple cores, for example: |

|            |           | -a cluster0.cpu*=file                                                                                                                   |

| Short<br>form | Long form             | Description                                                                                                                                                 |

|---------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | plugin filename       | Load the plug-in <i>filename</i> . This option can be specified multiple times. You can also load plug-ins using the FM_TRACE_PLUGINS environment variable. |

|               |                       | For more information, see Plug-ins for Fast Models in Fast Models Reference Manual.                                                                         |

|               | trace-plugin filename | Load a trace plug-in.  Note: This option is deprecated. Useplugin instead.                                                                                  |

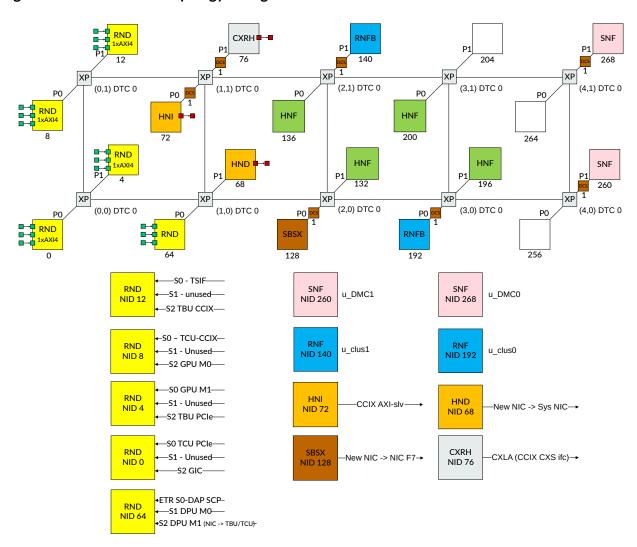

# 4.3 CMN-Skeena topology configuration and connection diagram

This figure shows the CMN-Skeena topology configuration diagram and a list of external connections.

Figure 4-1: CMN-Skeena topology configuration and connection overview

# 4.4 Morello-specific changes to tarmac trace

Tarmac trace is a format for tracing code executing on an Arm® core, for example branches, memory accesses, or cache hits or misses. Examining tarmac trace is a useful technique in debugging software.

To generate tarmac trace on the FVP, you must load the TarmacTrace. so plug-in at simulation startup. The plug-in attaches to the model and registers for specific trace events that might occur during the simulation.

The TarmacTrace plug-in file format is documented in TarmacTrace in the Fast Models Reference Manual. The following topics describe the changes that have been made to TarmacTrace for Morello.

#### Related information

TarmacTrace

### 4.4.1 File format changes

New syntax has been added for 129-bit addresses derived from a capability in Morello.

As stated in the Fast Models Reference Manual, 64-bit addresses are written as either:

- 8 hex digits, if the value can be represented in 32 bits.

- 16 hex digits otherwise.

When Morello is enabled, for 129-bit addresses derived from a capability, the value is written as up to 33 hex digits representing the 129 bits of the capability. The tag and the bottom 64 bits are separated using a vertical bar ( $_{\rm I}$ ). The bottom 64 bits are written as described for a 64-bit address. When a physical address is present, the virtual address is surrounded by parentheses.

(1|ffffc0000010005|80000000):90000000

Refer to TarmacTrace file format in the Fast Models Reference Manual.

# 4.4.2 Instruction trace changes

An extra instruction set specifier, c, for C64 has been added for Morello.

The new syntax is:

[A|T|X|O|C]

Refer to Instruction trace in the Fast Models Reference Manual.

### 4.4.3 Register trace changes

New syntax has been added for 129-bit capability registers in Morello.

The following example output shows how these registers are traced when the value changes:

These registers have the same format as 64-bit registers, with the addition of a vertical bar ( $_{\rm I}$ ) separating the capability tag, bits [127:64], and bits [63:0].

Refer to Register trace in the Fast Models Reference Manual.

### 4.4.4 Processor memory access trace changes

New syntax has been added for capability tag transfers in Morello.

The new syntax is:

```

<time> <scale> {<cpu>} [M|C]<rw><sz><attrib> <addr> <data>

```

The changes for Morello are:

#### [M|C]

**M** Data transfer.

**C** Capability tag transfer, when Morello is enabled.

#### <sz>

For data transfers, the size of the data transfer in bytes, 1, 2, 4, or 8.

For capability tag transfers, the size of the capability tag transfer in bits. That is, the number of capability tags transferred.

#### <data>

Hexadecimal value of the data transferred. The data padding is according to the size of the transfer. Data of 64 bits or more contains an underscore (\_) separator every eight characters (32 bits).

For capability tag transfers, each digit represents a single tag. For example, 1111 represents four tags, each with a value of 1.

Refer to Processor memory access trace in the Fast Models Reference Manual.

# 4.5 ToggleMTIPlugin

Generating trace throughout the simulation can result in very large trace files and slow down the simulation. To help avoid these problems, ToggleMTIPlugin enables you to turn trace generation on or off during the simulation.

ToggleMTIPlugin is enabled, like other plug-ins, using the --plugin parameter. If you are enabling multiple plug-ins on the command line, ToggleMTIPlugin must be specified last.

There are two alternative ways to use the plug-in:

You cannot use both of these methods in the same simulation session.

• Using the plug-in parameters use\_hlt = 1 and hlt\_imm16 = #imm16.

This pair of plug-in parameters is used in combination with the application using HLT #imm16 for toggling Model Trace Interface (MTI) callbacks. For these parameters to take effect, you must also set the corresponding parameters on the core model that is running the application:

#### enable\_trace\_special\_hlt\_imm16

If true, enables the parameter trace\_special\_hlt\_imm16.

#### trace\_special\_hlt\_imm16

Specifies an integer which, when used as the operand to an HLT instruction, causes the usual HLT execution to be skipped. If the integer matches the value specified in hlt\_imm16, tracing is turned on or off.

Using the plug-in parameter disable mti runtime = true.

You can set or unset this parameter at runtime using a CADI client, for instance Model Debugger. When set to true, trace is disabled.

Each parameter is prefixed with TRACE. ToggleMTIPlugin, for example:

TRACE.ToggleMTIPlugin.disable mti runtime

**Table 4-8: ToggleMTIPlugin parameters**

| Parameter              | Туре | Allowed values | Default value | Runtime | Description                                                           |

|------------------------|------|----------------|---------------|---------|-----------------------------------------------------------------------|

| diagnostics            | bool | true, false    | false         | false   | Print diagnostics.                                                    |

| disable_mti_from_start | bool | -              | false         | false   | Enable or disable MTI callbacks from start of simulation.             |