# Arm<sup>®</sup> CoreSight<sup>™</sup> ETM-M55 Revision: r1p0

**Technical Reference Manual**

### Arm<sup>®</sup> CoreSight<sup>™</sup> ETM-M55

### **Technical Reference Manual**

Copyright © 2019-2021 Arm Limited or its affiliates. All rights reserved.

#### **Release Information**

### **Document History**

| Issue   | Date             | Confidentiality  | Change                                |

|---------|------------------|------------------|---------------------------------------|

| 0000-02 | 07 June 2019     | Confidential     | First beta release for r0p0           |

| 0000-04 | 20 December 2019 | Confidential     | First limited access release for r0p0 |

| 0001-05 | 31 March 2020    | Non-Confidential | First early access release for r0p1   |

| 0002-01 | 17 July 2020     | Non-Confidential | First release for r0p2                |

| 0002-02 | 30 October 2020  | Non-Confidential | Second documentation release for r0p2 |

| 0100-01 | 21 April 2021    | Non-Confidential | First early access release for r1p0   |

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. **No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.**

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or ™ are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at *http://www.arm.com/company/policies/trademarks*.

Copyright © 2019-2021 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

(LES-PRE-20349)

### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

#### **Product Status**

The information in this document is Final, that is for a developed product.

#### Web Address

developer.arm.com

#### Progressive terminology commitment

Arm values inclusive communities. Arm recognizes that we and our industry have used terms that can be offensive. Arm strives to lead the industry and create change.

This document includes terms that can be offensive. We will replace these terms in a future issue of this document.

If you find offensive terms in this document, please contact terms@arm.com.

# Contents Arm<sup>®</sup> CoreSight<sup>™</sup> ETM-M55 Technical Reference Manual

|           | Pref  | face                                    |      |

|-----------|-------|-----------------------------------------|------|

|           |       | About this book                         |      |

|           |       | Feedback                                |      |

| Chapter 1 | Intro | oduction                                |      |

|           | 1.1   | CoreSight <sup>™</sup> ETM-M55 features | 1-12 |

|           | 1.2   | Compliance                              |      |

|           | 1.3   | Features                                |      |

|           | 1.4   | Interfaces and configurable options     |      |

|           | 1.5   | Design process                          |      |

|           | 1.6   | Documentation                           |      |

|           | 1.7   | Product revisions                       | 1-21 |

| Chapter 2 | Fund  | ctional Description                     |      |

|           | 2.1   | ETM-M55 functional blocks               | 2-23 |

|           | 2.2   | External input and output connections   |      |

|           | 2.3   | Operation                               |      |

| Chapter 3 | Prog  | grammers model                          |      |

|           | 3.1   | Modes of operation and execution        |      |

| Chapter 4  | ETM  | -M55 register descriptions                                               |             |

|------------|------|--------------------------------------------------------------------------|-------------|

|            | 4.1  | Register summary                                                         | 4-37        |

|            | 4.2  | TRCPRGCTLR, Programming Control Register                                 | 4-40        |

|            | 4.3  | TRCSTATR, Status Register                                                | 4-41        |

|            | 4.4  | TRCCONFIGR, Trace Configuration Register                                 | 4-42        |

|            | 4.5  | TRCEVENTCTL0R, Event Control 0 Register                                  | 4-44        |

|            | 4.6  | TRCEVENTCTL1R, Event Control 1 Register                                  | 4-45        |

|            | 4.7  | TRCSTALLCTLR, Stall Control Register                                     | 4-46        |

|            | 4.8  | TRCTSCTLR, Global Timestamp Control Register                             | 4-47        |

|            | 4.9  | TRCSYNCPR, Synchronization Period Register                               | 4-48        |

|            | 4.10 | TRCCCCTLR, Cycle Count Control Register                                  | 4-49        |

|            | 4.11 | TRCTRACEIDR, Trace ID Register                                           | 4-50        |

|            | 4.12 | TRCVICTLR, ViewInst Main Control Register                                | 4-51        |

|            | 4.13 | TRCVIPCSSCTLR, ViewInst Start/Stop Processor Comparator Control Register | 4-53        |

|            | 4.14 | TRCEXTINSELR, External Input Select Register                             | 4-56        |

|            | 4.15 | TRCCNTRLDVR0, Counter Reload Value Register 0                            | 4-57        |

|            | 4.16 | TRCIDR0-13, ID Registers                                                 | 4-58        |

|            | 4.17 | TRCRSCTLRn, Resource Selection Registers 2-3                             | 4-69        |

|            | 4.18 | TRCSSCCR0, Single-shot Comparator Control Register 0                     | 4-71        |

|            | 4.19 | TRCSSCSR0, Single-shot Comparator Status Register 0                      | 4-72        |

|            | 4.20 | TRCSSPCICR0, Single-shot Processor Comparator Input Control Register 0   | 4-74        |

|            | 4.21 | TRCPDCR, Power Down Control Register                                     | 4-75        |

|            | 4.22 | TRCPDSR, Power Down Status Register                                      | 4-76        |

|            | 4.23 | Integration test registers                                               | 4-77        |

|            | 4.24 | TRCCLAIMSET, Claim Tag Set Register                                      | 4-82        |

|            | 4.25 | TRCCLAIMCLR, Claim Tag Clear Register                                    | 4-83        |

|            | 4.26 | TRCAUTHSTATUS, Authentication Status Register                            | 4-84        |

|            | 4.27 | TRCDEVARCH, Device Architecture Register                                 | 4-85        |

|            | 4.28 | TRCDEVID, Device ID Register                                             | <b>4-86</b> |

|            | 4.29 | TRCDEVTYPE, Device Type Register                                         | 4-87        |

|            | 4.30 | TRCPIDR0-7, Peripheral Identification Registers                          | 4-88        |

|            | 4.31 | TRCCIDR0-3, Component Identification Registers                           | 4-90        |

| Appendix A | Revi | sions                                                                    |             |

|            | A 1  | Revisions Ann                                                            | x-A-92      |

| A.1 | Revisions | Appx-A-92 |

|-----|-----------|-----------|

|-----|-----------|-----------|

# Preface

This preface introduces the Arm<sup>®</sup> CoreSight<sup>™</sup> ETM-M55 Technical Reference Manual.

It contains the following:

- *About this book* on page 7.

- Feedback on page 10.

### About this book

This book is for the CoreSight Embedded Trace Macrocell<sup>™</sup> for the Cortex<sup>®</sup>-M55 processor. You implement ETM-M55 with the Cortex-M55 processor. In this manual, in general, any reference to the processor applies to the Cortex-M55 processor, as appropriate.

### **Product revision status**

The rxpy identifier indicates the revision status of the product described in this book, for example, r1p2, where:

- rx Identifies the major revision of the product, for example, r1.

- py Identifies the minor revision or modification status of the product, for example, p2.

### Intended audience

This book is written for designers of development tools providing support for ETM functionality and hardware and software engineers integrating the macrocell into an ASIC that includes the Cortex<sup>®</sup>-M55 processor. Implementation-specific behavior is described in this document. You can find complementary information in the *Arm*<sup>®</sup> *Embedded Trace Macrocell Architecture Specification ETMv4* and *Arm*<sup>®</sup> *Cortex*<sup>®</sup>-M55 *Processor Integration and Implementation Manual.*

### Using this book

This book is organized into the following chapters:

### **Chapter 1 Introduction**

This chapter describes ETM-M55.

### **Chapter 2 Functional Description**

This chapter describes the ETM-M55 functional features and operation.

### Chapter 3 Programmers model

This chapter describes the mechanisms for programming the registers used to set up the trace and triggering facilities of the macrocell. The programmers model enables you to use the ETM-M55 registers to control the macrocell.

### Chapter 4 ETM-M55 register descriptions

This chapter describes the ETM-M55 registers.

### Appendix A Revisions

This appendix describes the technical changes between released issues of this book.

### Glossary

The Arm Glossary is a list of terms used in Arm documentation, together with definitions for those terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

See the Arm<sup>®</sup> Glossary for more information.

### **Typographic conventions**

italic

Introduces special terminology, denotes cross-references, and citations.

### bold

Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.

### monospace

Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.

monospace

Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.

monospace italic

Denotes arguments to monospace text where the argument is to be replaced by a specific value.

### monospace bold

Denotes language keywords when used outside example code.

<and>

Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example:

MRC p15, 0, <Rd>, <CRn>, <CRm>, <Opcode\_2>

### SMALL CAPITALS

Used in body text for a few terms that have specific technical meanings, that are defined in the *Arm*<sup>®</sup> *Glossary*. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE.

### **Timing diagrams**

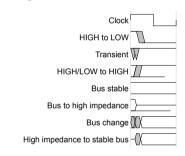

The following figure explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

### Figure 1 Key to timing diagram conventions

### Signals

The signal conventions are:

### Signal level

The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

- HIGH for active-HIGH signals.

- LOW for active-LOW signals.

### Lowercase n

At the start or end of a signal name, n denotes an active-LOW signal.

### Additional reading

This book contains information that is specific to this product. See the following documents for other relevant information.

### Arm publications

- Arm<sup>®</sup> CoreSight<sup>™</sup> DAP-Lite Technical Reference Manual (DDI 0316)

- Arm<sup>®</sup> CoreSight<sup>™</sup> Architecture Specification v3.0 (IHI 0029)

- AMBA® APB Protocol Version 2.0 Specification (IHI 0033)

- AMBA® 4 ATB Protocol Specification (IHI 0032)

- Arm<sup>®</sup> Embedded Trace Macrocell Architecture Specification ETMv4 (ARM IHI 0064)

- Arm<sup>®</sup>v8-M Architecture Reference Manual (DDI 0553)

- Arm<sup>®</sup> Cortex<sup>®</sup>-M55 Processor Technical Reference Manual (101051)

- Arm<sup>®</sup> PMC-100 Technical Reference Manual (101528)

The following confidential book is only available to licensees:

• Arm<sup>®</sup> Cortex<sup>®</sup>-M55 Processor Integration and Implementation Manual (101052)

### Other publications

None.

# Feedback

### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

### Feedback on content

If you have comments on content then send an e-mail to *errata@arm.com*. Give:

- The title Arm CoreSight ETM-M55 Technical Reference Manual.

- The number 101053 0100 01 en.

- If applicable, the page number(s) to which your comments refer.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

\_\_\_\_\_ Note \_\_\_\_\_

Arm tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader.

# Chapter 1 Introduction

This chapter describes ETM-M55.

It contains the following sections:

- 1.1 CoreSight<sup>™</sup> ETM-M55 features on page 1-12.

- *1.2 Compliance* on page 1-14.

- *1.3 Features* on page 1-15.

- 1.4 Interfaces and configurable options on page 1-18.

- 1.5 Design process on page 1-19.

- *1.6 Documentation* on page 1-20.

- *1.7 Product revisions* on page 1-21.

# 1.1 CoreSight<sup>™</sup> ETM-M55 features

ETM-M55 can provide non-intrusive program-flow trace for the Cortex-M55 processor. ETM-M55 generates information that trace software tools use to reconstruct the execution of an entire program or part of a program.

ETM-M55 implements instruction trace only. ETM-M55 is able to trace:

- All instructions, including condition code pass or fail

- Target addresses of indirect branch operations that have been taken

- Target addresses of direct branch operations that have been taken when TRCCONFIGR.BB is set to 1

- Exceptions

- Entry to debug state when Halting debug mode is enabled

- Cycle counts relating to instruction execution

ETM-M55 contains resource logic that enables you to control instruction trace. This resource logic includes one reduced function counter. For more information on the provision of a reduced function counter, see the *Arm*\* *Embedded Trace Macrocell Architecture Specification ETMv4*. Other resources available for ETM-M55 include *Data Watchpoint and Trace*(DWT) processor comparators and external inputs. You can specify the exact set of trigger and filter conditions that are required for a particular application.

For more information about CoreSight, see:

- Arm<sup>®</sup> CoreSight<sup>™</sup> Architecture Specification v3.0

- Arm<sup>®</sup> CoreSight<sup>™</sup> System-on-Chip SoC-600 Technical Reference Manual

For more information about the ETM architecture, see the *Arm*<sup>®</sup> *Embedded Trace Macrocell Architecture Specification ETMv4*.

### 1.1.1 The CoreSight<sup>™</sup> debug environment

The CoreSight debug environment contains a software debugger that provides a user interface to ETM-M55. ETM-M55 is designed for instruction trace and it has a single 8-bit AMBA 4 ATB interface.

### Software debugger

A software debugger provides a user interface to ETM-M55. You can use this interface to:

- Configure ETM-M55 facilities such as filtering.

- Configure optional trace features such as cycle counting.

- Configure the other CoreSight components such as the Trace Port Interface Unit (TPIU).

- Access the processor debug registers and Performance Monitoring Units (PMUs).

ETM-M55 outputs its trace to the AMBA 4 ATB interface.

You can use the CoreSight infrastructure to design systems that provide the option to:

- Export the trace information through a trace port. An external *Trace Port Analyzer* (TPA) captures the trace information as shown in *Figure 1-1 Example CoreSight system with ETM-M55* on page 1-13.

- Write the trace information to a trace-capable device that can access local or system memory. You can read out the trace at low speed using a *Joint Test Action Group* (JTAG) or *Serial Wire* (SW) interface.

The software debugger has a copy of the executed image from memory and the captured trace information from the TPA or on-chip trace buffer. It decompresses the image to provide full disassembly with symbols of the code that was executed. ETM-M55 generates trace information that gives the software debugger the capability to link this data back to the original high-level source code. This information provides a visualization of how the code was executed on the Cortex-M55 processor.

### Example CoreSight<sup>™</sup> system with ETM-M55

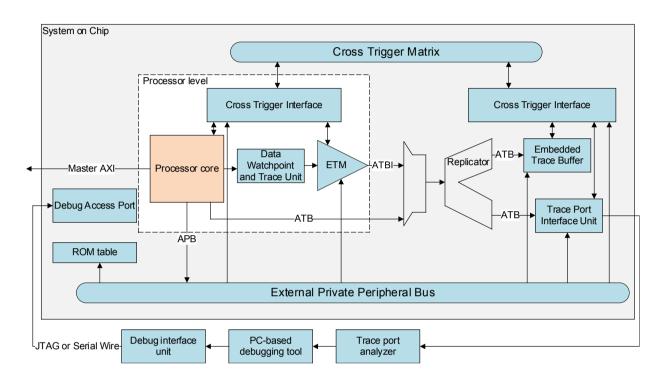

The following figure shows an example of how ETM-M55 fits into a CoreSight debug environment to provide instruction trace capabilities in a single processor system.

In this example, the external debug software configures the trace and debug components through the *Debug Access Port* (DAP). The top-level ROM table contains:

- A unique identification code for the SoC.

- The base addresses of the components that are connected to the *External Private Peripheral Bus* (EPPB) on the Cortex-M55 processor.

The ETM-M55 trace interfaces are replicated to provide on-chip storage using the CoreSight ETB and output off-chip using the TPIU. Cross-triggering operates through the *Cross Trigger Interface* (CTI) and *Cross Trigger Matrix* (CTM) components.

### Figure 1-1 Example CoreSight system with ETM-M55

As an alternative to using an external computer to run a software debugger, the Cortex-M55 processor (or another processor on the *System-on-Chip* (SoC) can access ETM-M55 and an on-chip trace buffer to provide self-hosted debug and trace functionality.

# 1.2 Compliance

ETM-M55 is compatible with the CoreSight architecture.

This manual complements architecture reference manuals, architecture specifications, protocol specifications, and relevant external standards. It does not duplicate information from these sources.

The ETM-M55 implements the architecture specification and protocols shown in the following table.

### Table 1-1 Architecture specifications and protocols

| Component                    | Specification                                                                                                                                                                                                                          |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ETM architecture             | ETM-M55 implements the ETM architecture version 4.5. For more information, see <i>Arm</i> * <i>Embedded Trace Macrocell Architecture Specification ETMv4</i> .                                                                         |

| Interconnect<br>architecture | ETM-M55 complies with the AMBA 4 APB and AMBA 4 ATB protocols. For more information, see the <i>AMBA</i> <sup>®</sup> <i>APB Protocol Version 2.0 Specification</i> and <i>AMBA</i> <sup>®</sup> <i>4 ATB Protocol Specification</i> . |

## 1.3 Features

The ETM-M55 consists of a range of IMPLEMENTATION DEFINED features and also implements several optional features from the ETM architecture.

See the Arm® Embedded Trace Macrocell Architecture Specification ETMv4 for information about:

- The trace protocol

- The ETM version 4.5 features

- Controlling tracing using triggering and filtering resources

The following table shows the ETM-M55 features that are IMPLEMENTATION DEFINED, in terms of either:

- The number of times the feature is implemented

- The size of the feature

### Table 1-2 ETM-M55 features with IMPLEMENTATION DEFINED number of instances or size

| Feature                                                            | ETM-M55 configuration                                       | Description                                                                                                                                                    |

|--------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address comparators                                                | 0 pairs                                                     | See bits[3:0] of the 4.16.5 TRCIDR4, ID<br>Register 4 on page 4-62.                                                                                            |

| Instruction trace cycle counting minimum allowable threshold value | 4                                                           | -                                                                                                                                                              |

| Data value comparators                                             | 0                                                           | See bits[7:4] of the 4.16.5 TRCIDR4, ID<br>Register 4 on page 4-62.                                                                                            |

| Context ID comparators                                             | 0                                                           | See bits[27:24] <i>4.16.5 TRCIDR4, ID</i><br><i>Register 4</i> on page 4-62.                                                                                   |

| Single-Shot comparator controls                                    | 1                                                           | The single-shot comparators are only<br>sensitive to the processor comparator<br>inputs. See bits [23:20] in<br>4.16.5 TRCIDR4, ID Register 4<br>on page 4-62. |

| Counters                                                           | 1                                                           | This indicates reduced function counter<br>implementation. See bits[30:28] of the<br>4.16.6 TRCIDR5, ID Register 5<br>on page 4-63.                            |

| Trace events supported                                             | 2                                                           | See bits[11:10] of the 4.16.1 TRCIDR0, ID<br>Register 0 on page 4-58.                                                                                          |

| Cycle counter size                                                 | 12 bits                                                     | See bits[28:25] of the 4.16.3 TRCIDR2, ID<br>Register 2 on page 4-60.                                                                                          |

| Sequencer                                                          | 0                                                           | See bits[27:25] of the 4.16.6 TRCIDR5, ID<br>Register 5 on page 4-63.                                                                                          |

| Processor comparator inputs                                        | 2, 4 or 8                                                   | See bits[15:12] of the 4.16.5 TRCIDR4, ID<br>Register 4 on page 4-62.                                                                                          |

| External inputs                                                    | 4+number of <i>Performance Monitor Unit</i><br>(PMU) events | See bits[8:0] of the 4.16.6 TRCIDR5, ID<br>Register 5 on page 4-63.                                                                                            |

| External outputs                                                   | 2                                                           | -                                                                                                                                                              |

| External input selectors                                           | 4                                                           | See bits[11:9] of the 4.16.6 TRCIDR5, ID<br>Register 5 on page 4-63.                                                                                           |

| Feature                     | ETM-M55 configuration      | Description                                                           |

|-----------------------------|----------------------------|-----------------------------------------------------------------------|

| Resource selection pairs    | 2                          | See bits[19:16] of the 4.16.5 TRCIDR4, ID<br>Register 4 on page 4-62. |

| Instruction trace port size | 8-bit                      | -                                                                     |

| Instruction FIFO            | 64 bytes with 8-bit output | Uses Advanced Trace Bus (ATB).                                        |

| Claim tag bits              | 4                          | -                                                                     |

### Table 1-2 ETM-M55 features with IMPLEMENTATION DEFINED number of instances or size (continued)

The following table shows the optional features of the ETM architecture that ETM-M55 implements.

### Table 1-3 ETM-M55 implementation of optional features

| Feature                                        | Implemented | Description                                                                                                                                                              |  |

|------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Commit mode                                    | No          | -                                                                                                                                                                        |  |

| Configurable FIFO                              | No          | -                                                                                                                                                                        |  |

| Trace Start/Stop block                         | Yes         | -                                                                                                                                                                        |  |

| Branch broadcast tracing support               | Yes         | See bit[5] of the 4.16.1 TRCIDR0, ID Register 0 on page 4-58.                                                                                                            |  |

| Trace of conditional instructions              | Yes         | See bits[13:12] and bit[6] of the 4.16.1 TRCIDR0, ID Register 0 on page 4-58.                                                                                            |  |

| Data trace                                     | No          | -                                                                                                                                                                        |  |

| System error trace                             | Yes         | -                                                                                                                                                                        |  |

| Load and store instruction data trace          | No          | -                                                                                                                                                                        |  |

| Low-power override                             | Yes         | See bit[23] of the 4.16.6 TRCIDR5, ID Register 5 on page 4-63.                                                                                                           |  |

| Support for overflow avoidance                 | Yes         | -                                                                                                                                                                        |  |

| Cycle counting in instruction trace            | Yes         | See bit[7] of the 4.16.1 TRCIDR0, ID Register 0 on page 4-58.                                                                                                            |  |

| Data address comparison                        | No          | ETM-M55 does not implement data address comparison.                                                                                                                      |  |

| OS Lock mechanism                              | No          | The Cortex-M55 processor does not implement OS Lock.                                                                                                                     |  |

| Secure non-invasive debug                      | Yes         | The Cortex-M55 processor implements optional Security Extensions.                                                                                                        |  |

| Context ID tracing                             | No          | See bits[9:5] of the 4.16.3 TRCIDR2, ID Register 2 on page 4-60.                                                                                                         |  |

| Trace output                                   | Yes         | Uses ATB.                                                                                                                                                                |  |

| Timestamp size                                 | 64-bit      | See bits[28:24] of the 4.16.1 TRCIDR0, ID Register 0 on page 4-58.                                                                                                       |  |

| Memory mapped access to ETM-M55 registers      | Yes         | See the <i>Arm</i> <sup>®</sup> <i>Embedded Trace Macrocell Architecture Specification</i><br><i>ETMv4</i> for more information about the access permissions behavior on |  |

| External debugger access to ETM-M55 registers  | Yes         | register accesses for different states of ETM-Cortex-M55.                                                                                                                |  |

| System instruction access to ETM-M55 registers | No          |                                                                                                                                                                          |  |

| Virtual Machine ID (VMID) comparator support   | No          | See bits[31:28] of the 4.16.5 TRCIDR4, ID Register 4 on page 4-62.                                                                                                       |  |

| Q-element filtering support                    | No          | -                                                                                                                                                                        |  |

### Table 1-3 ETM-M55 implementation of optional features (continued)

| Feature                        | Implemented | Description                                                    |

|--------------------------------|-------------|----------------------------------------------------------------|

| Q-element support              | No          | -                                                              |

| Reduced function counter       | Yes         | See bit [31] in 4.16.6 TRCIDR5, ID Register 5 on page 4-63.    |

| Return stack support           | Yes         | -                                                              |

| Stall control support          | Yes         | -                                                              |

| Software lock                  | No          | -                                                              |

| Synchronization period support | Yes         | Read-only support is provided                                  |

| ATB trigger support            | Yes         | See bit[22] of the 4.16.6 TRCIDR5, ID Register 5 on page 4-63. |

# 1.4 Interfaces and configurable options

ETM-M55 has four main interfaces.

### **ETM-M55** interfaces

The following table shows the main interfaces in ETM-M55.

### Table 1-4 ETM-M55 interfaces

| Interface                 | Description                                                                                                                                                                                                                                                                          |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processor interface       | <ul> <li>This interface connects the M55 processor to ETM-M55. It has the following functions:</li> <li>Tracking execution information from the processor.</li> <li>Decoding the control signals.</li> <li>Passing on the decoded information to the internal interfaces.</li> </ul> |

| AMBA 4 ATB interface      | This interface is the instruction ATB interface. This interface reads single bytes of packet information from the instruction FIFO and the information is sent over the interface.                                                                                                   |

| AMBA 4 APB interface      | This interface is an interface to the APB that provides access to the programmable registers.                                                                                                                                                                                        |

| Production test interface | This interface contains the scan enable signal that is used in ETM-M55 production testing.                                                                                                                                                                                           |

### **Configurable options**

ETM-M55 has no configurable options.

## 1.5 Design process

ETM-M55 is delivered as synthesizable RTL.

Before it can be used in a product, ETM-M55 must go through the design process described in the following table.

### Table 1-5 ETM-M55 design process

| Stage          | Description                                                                                                                                                                                                                                                                                                                                                    |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Implementation | For <i>Microcontroller Units</i> (MCUs), often a single design team integrates the processor and ETM-M55 before synthesizing the complete design. Alternatively, the team can synthesize the processor on its own or partially integrated, to produce a hard macrocell. Then, the same team or a separate team, integrates the hard macrocell into the design. |

| Integration    | The integrator connects the implemented design into a <i>System on Chip</i> (SoC). This includes connecting it to a memory system and peripherals.                                                                                                                                                                                                             |

| Programming    | This is the last stage in the process. The system programmer develops the software required to configure and initialize ETM-M55, and tests the required application software.                                                                                                                                                                                  |

The operation of the final device depends on:

### **Build configuration**

The implementer chooses the options that affect how the RTL source files are pre-processed. These options usually include or exclude logic that affects one or more of the following:

- Area.

- Maximum frequency.

- Features of the resulting design.

### **Configuration inputs**

The integrator configures some of the ETM-M55 features by tying inputs to specific values. These configurations affect the start-up behavior before any software configuration is made. They can also limit the options available to the software.

### Software configuration

The programmer configures ETM-M55 by programming particular values into registers. These register values affect the ETM-M55 behavior.

— Note —

- This manual refers to IMPLEMENTATION DEFINED features that are applicable to build configuration options. Any reference to:

- An included feature means that the appropriate build and pin configuration options are selected.

- An enabled feature means one that has also been configured by software.

- Each stage of the process:

- Can be performed by a different party.

- Can include implementation and integration choices that affect the ETM-M55 behavior and features.

## 1.6 Documentation

ETM-M55 documentation is as follows:

### **Technical Reference Manual**

The *Technical Reference Manual* (TRM) describes the functionality and the effects of functional options on the ETM-M55 behavior. It is required at all stages of the design flow. Some behavior described in the TRM might not be relevant because of the way that ETM-M55 is implemented and integrated.

### **Integration and Implementation Manual**

For both the processor and ETM-M55, the *Arm*<sup>®</sup> *Cortex*<sup>®</sup>-*M55 Processor Integration and Implementation Manual* (IIM) describes:

- The available build configuration options and related issues in selecting them.

- How to configure the Register Transfer Level (RTL) with the build configuration options.

- How to integrate the processor into a *System on Chip* (SoC). This includes a description of the pins that the integrator must tie off to configure the macrocell for the required integration.

- The processes to sign off the integration and implementation of the design.

The Arm product deliverables include reference scripts and information about using them to implement your design.

Reference methodology documentation from your EDA tools vendor complements the IIM.

The IIM is a confidential document that is only available to licensees.

## 1.7 Product revisions

The following product revisions have been released.

- **r0p0** First beta release for r0p0

- First limited access release for r0p0

- **r0p1** First early access release for r0p1

- **r0p2** First release for r0p2 Second documentation release for r0p2

- r1p0 First early access release for r1p0Addition of Arm Custom Instructions (ACIs), Dual Core Lock-Step (DCLS), and Flop Parity

# Chapter 2 Functional Description

This chapter describes the ETM-M55 functional features and operation.

It contains the following sections:

- 2.1 ETM-M55 functional blocks on page 2-23.

- 2.2 External input and output connections on page 2-24.

- 2.3 Operation on page 2-30.

## 2.1 ETM-M55 functional blocks

ETM-M55 is a CoreSight component and an integral part of the Arm real-time debug solution, Arm Development Studio. ETM-M55 performs real-time instruction tracing based on the ETM version 4.5 architecture.

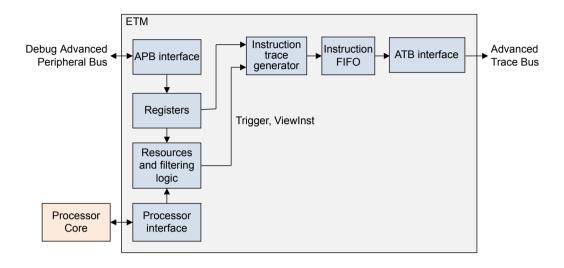

The following figure shows the main functional blocks of ETM-M55.

### Figure 2-1 ETM-M55 block diagram

The following table describes the ETM-M55 functional blocks.

### Table 2-1 ETM-M55 functional blocks

| Functional block               | Description                                                                                                                                                                                                                                                                                               |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processor interface            | <ul> <li>The processor interface from ETM-M55 connects to the Cortex-M55 processor. It has the following functions:</li> <li>Tracking execution information from the processor.</li> <li>Decoding the control signals.</li> <li>Passing on the decoded information to the internal interfaces.</li> </ul> |

| Resources and filtering logic  | These blocks contain resources which are programmed by trace software to trigger and filter the trace information. They start and stop trace generation, depending on the conditions that have been set.                                                                                                  |

| AMBA 4 APB interface           | This is an interface to the APB that provides access to the programmable registers.                                                                                                                                                                                                                       |

| Instruction trace<br>generator | This block generates the trace packets that are a compressed form of the instruction execution information provided by the Cortex-M55 processor. The trace packets are then passed to the instruction FIFO.                                                                                               |

| Instruction FIFO               | This block buffers bursts of trace packets. There is one FIFO provided for the instruction trace stream.                                                                                                                                                                                                  |

| AMBA 4 ATB interface           | This is the instruction ATB interface. This interface reads single bytes of packet information from the instruction FIFO and the information is sent over the interface.                                                                                                                                  |

| Global timestamping            | ETM-M55 supports connection to a global timestamp source. This provides a 64-bit timestamp that a debugger can use for coarse-grained profiling and correlation of the trace source. Arm recommends that the timestamp counter is no slower than 10% of the maximum processor clock frequency.            |

## 2.2 External input and output connections

The following table shows the external input connections. These inputs can be selected using the external input selectors controlled by TRCEXTINSELR.

For more information, see 4.14 TRCEXTINSELR, External Input Select Register on page 4-56.

### Table 2-2 External input connections

| External input bits                         | Description |

|---------------------------------------------|-------------|

| [3:0]                                       | CTI         |

| [3+N:4] where N is the number of PMU events | PMU events  |

The following table shows the ETM-M55 external input and output bit connections to the *Cross Trigger Interface* (CTI).

### Table 2-3 CTI connections

| ETM-M55 external input and output bits | CTI input             |

|----------------------------------------|-----------------------|

| ETM external input bits [3:0]          | CTI output bits [7:4] |

| ETM external output bits [1:0]         | CTI input bits [5:4]  |

The following table shows the ETM-M55 external input and output bit connections to the *Performance Monitoring Unit* (PMU).

### Table 2-4 PMU events

| Event<br>number | Event mnemonic   | External input bit | Event name                                                                                  |  |

|-----------------|------------------|--------------------|---------------------------------------------------------------------------------------------|--|

| 0x0000          | SW_INCR          | 4                  | Instruction architecturally executed, condition code check pass, software increment         |  |

| 0x0001          | L1I_CACHE_REFILL | 5                  | L1 instruction cache linefill                                                               |  |

| 0x0003          | L1D_CACHE_REFILL | 6                  | L1 data cache linefill                                                                      |  |

| 0x0004          | L1D_CACHE        | 7                  | L1 data cache access                                                                        |  |

| 0x0006          | LD_RETIRED       | 8                  | Instruction architecturally executed, condition code check pass, load                       |  |

| 0x0007          | ST_RETIRED       | 9                  | Instruction architecturally executed, condition code check pass, store                      |  |

| 0x0008          | INST_RETIRED     | 10                 | Instruction architecturally executed.                                                       |  |

| 0x0009          | EXC_TAKEN        | 11                 | Exception taken.                                                                            |  |

| 0x000A          | EXC_RETURN       | 12                 | Instruction architecturally executed, condition code check pass, exception return.          |  |

| 0x000C          | PC_WRITE_RETIRED | 13                 | Instruction architecturally executed, condition code check pass, software change of the PC. |  |

| 0x000D          | BR_IMMED_RETIRED | 14                 | Instruction architecturally executed, immediate branch.                                     |  |

| Event<br>number | Event mnemonic                                                                    | External<br>input bit                                                                             | Event name                                                                                                                                                                                                                                      |  |

|-----------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0x000E          | BR_RETURN_RETIRED                                                                 | 15                                                                                                | Instruction architecturally executed, condition code check pass, procedure return.                                                                                                                                                              |  |

| 0x000F          | UNALIGNED_LDST_RETIRED                                                            | 16                                                                                                | Instruction architecturally executed, condition code check pass, unaligned load or store.                                                                                                                                                       |  |

| 0x0011          | CPU_CYCLES                                                                        | 17                                                                                                | Cycle.                                                                                                                                                                                                                                          |  |

| 0x0013          | MEM_ACCESS                                                                        | 18                                                                                                | Data memory access.                                                                                                                                                                                                                             |  |

| 0x0014          | L11_CACHE                                                                         | 19                                                                                                | L1 instruction cache access.                                                                                                                                                                                                                    |  |

| 0x0015          | L1D_CACHE_WB                                                                      | 20                                                                                                | L1 data cache write-back                                                                                                                                                                                                                        |  |

| 0x0019          | BUS_ACCESS                                                                        | 21                                                                                                | Any beat access to the M-AXI read interface,<br>M-AXI write interface and any access to P-<br>AHB interface                                                                                                                                     |  |

| 0x001A          | MEMORY_ERROR                                                                      | 22                                                                                                | ECC error for TCMs and caches.                                                                                                                                                                                                                  |  |

| 0x001D          | BUS_CYCLES                                                                        | 23                                                                                                | Counts the number of cycles on which the M-<br>AXI interface is clocked.                                                                                                                                                                        |  |

| 0x001E          | CHAIN                                                                             | 24                                                                                                | For an odd-numbered counter, increments<br>when an overflow occurs on the preceding<br>even-numbered counter on the same PE.                                                                                                                    |  |

| 0x0021          | BR_RETIRED                                                                        | 25                                                                                                | Instruction architecturally executed, branch.                                                                                                                                                                                                   |  |

| 0x0022          | BR_MIS_PRED_RETIRED                                                               | 26                                                                                                | Instruction architecturally executed, mispredicted branch.                                                                                                                                                                                      |  |

| 0x0023          | STALL_FRONTEND                                                                    | 27                                                                                                | If there are no instructions available from the fetch stage of the processor pipeline, the processor considers the front-end of the processor pipeline as being stalled.                                                                        |  |

| 0x0024          | fetch stage of the pipelin<br>accepted by the decode<br>pipeline, the processor c |                                                                                                   | If there is an instruction available from the<br>fetch stage of the pipeline but it cannot be<br>accepted by the decode stage of the processor<br>pipeline, the processor considers the back-end<br>of the processor pipeline as being stalled. |  |

| 0x0036          | LL_CACHE_RD                                                                       | HE_RD 29 L1 data cache read. For the Cortex-M55 processor, this event is the same as L1_CACHE_RD. |                                                                                                                                                                                                                                                 |  |

| 0x0037          | LL_CACHE_MISS_RD                                                                  | 30                                                                                                | L1 data cache read miss. For the Cortex-M55 processor, this event is the same as L1D_CACHE_MISS_RD.                                                                                                                                             |  |

| 0x0039          | L1D_CACHE_MISS_RD                                                                 | 31                                                                                                | L1 data cache read miss. For the Cortex-M55 processor, this event is the same as LL_CACHE_MISS_RD.                                                                                                                                              |  |

| 0x003C          | C STALL 32 No operation sent for exec                                             |                                                                                                   |                                                                                                                                                                                                                                                 |  |

| Event<br>number | Event mnemonic                                | External<br>input bit<br>33 | Event name         L1 data cache read. For the Cortex-M55         processor, this event is the same as         LL_CACHE_RD. |  |

|-----------------|-----------------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| 0x0040          | L1D_CACHE_RD                                  |                             |                                                                                                                             |  |

| 0x0100          | LE_RETIRED                                    | 34                          | Loop end instruction architecturally executed,<br>entry registered in the LO_BRANCH_INFO<br>cache.                          |  |

| 0x0104          | BF_RETIRED                                    | 35                          | Tied LOW.                                                                                                                   |  |

| 0x0108          | LE_CANCEL                                     | 36                          | LO_BRANCH_INFO cache containing a valid<br>loop entry cleared while not in the last<br>iteration of the loop.               |  |

| 0x0109          | BF_CANCEL                                     | 37                          | Tied LOW.                                                                                                                   |  |

| 0x0114          | SE_CALL_S                                     | 38                          | Call to secure function, resulting in security state change.                                                                |  |

| 0x0115          | SE_CALL_NS                                    | 39                          | Call to Non-secure function, resulting in security state change                                                             |  |

| 0x0200          | MVE_INST_RETIRED                              | 40                          | <i>M-profile Vector Extension</i> (MVE) instruction architecturally executed                                                |  |

| 0x0204          | MVE_FP_RETIRED                                | 41                          | MVE floating-point instruction architecturally executed.                                                                    |  |

| 0x0208          | MVE_FP_HP_RETIRED                             | 42                          | MVE half-precision floating-point instruction architecturally executed                                                      |  |

| 0x020C          | MVE_FP_SP_RETIRED                             | 43                          | MVE single-precision floating-point instruction architecturally executed                                                    |  |

| 0x0214          | MVE_FP_MAC_RETIRED                            | 44                          | MVE floating-point multiply or multiply<br>accumulate instruction architecturally<br>executed                               |  |

| 0x0224          | MVE_INT_RETIRED                               | 45                          | MVE integer instruction architecturally executed                                                                            |  |

| 0x0228          | MVE_INT_MAC_RETIRED                           | 46                          | MVE integer multiply or multiply-accumulate instruction architecturally executed                                            |  |

| 0x0238          | MVE_LDST_RETIRED                              | 47                          | MVE load or store instruction architecturally executed                                                                      |  |

| 0x023C          | C MVE_LD_RETIRED 48 MVE load instruction arch |                             | MVE load instruction architecturally executed                                                                               |  |

| 0x0240          | MVE_ST_RETIRED                                | 49                          | MVE store instruction architecturally execute                                                                               |  |

| 0x0244          | MVE_LDST_CONTIG_RETIRED                       | 50                          | MVE contiguous load or store instruction architecturally executed                                                           |  |

| 0x0248          | MVE_LD_CONTIG_RETIRED                         | 51                          | MVE contiguous load instruction<br>architecturally executed                                                                 |  |

| Event<br>number | Event mnemonic                       | External input bit | Event name                                                                             |

|-----------------|--------------------------------------|--------------------|----------------------------------------------------------------------------------------|

| 0x024C          | MVE_ST_CONTIG_RETIRED                | 52                 | MVE contiguous store instruction<br>architecturally executed                           |

| 0x0250          | MVE_LDST_NONCONTIG_RETIRED           | 53                 | MVE non-contiguous load or store instruction architecturally executed                  |

| 0x0254          | MVE_LD_NONCONTIG_RETIRED             | 54                 | MVE non-contiguous load instruction<br>architecturally executed                        |

| 0x0258          | MVE_ST_NONCONTIG_RETIRED             | 55                 | MVE non-contiguous store instruction<br>architecturally executed                       |

| 0x025C          | MVE_LDST_MULTI_RETIRED               | 56                 | MVE memory instruction targeting multiple registers architecturally executed           |

| 0x0260          | MVE_LD_MULTI_RETIRED                 | 57                 | MVE memory load instruction targeting<br>multiple registers architecturally executed   |

| 0x0264          | MVE_ST_MULTI_RETIRED                 | 58                 | MVE memory store instruction targeting<br>multiple registers architecturally executed  |

| 0x028C          | MVE_LDST_UNALIGNED_RETIRED           | 59                 | MVE unaligned memory load or store instruction architecturally executed                |

| 0x0290          | MVE_LD_UNALIGNED_RETIRED             | 60                 | MVE unaligned load instruction<br>architecturally executed                             |

| 0x0294          | MVE_ST_UNALIGNED_RETIRED             | 61                 | MVE unaligned store instruction<br>architecturally executed                            |

| 0x0298          | MVE_LDST_UNALIGNED_NONCONTIG_RETIRED | 62                 | MVE unaligned non-contiguous load or store instruction architecturally executed        |

| 0x02A0          | MVE_VREDUCE_RETIRED                  | 63                 | MVE vector reduction instruction<br>architecturally executed                           |

| 0x02A4          | MVE_VREDUCE_FP_RETIRED               | 64                 | MVE floating-point vector reduction<br>instruction architecturally executed            |

| 0x02A8          | MVE_VREDUCE_INT_RETIRED              | 65                 | MVE integer vector reduction instruction architecturally executed                      |

| 0x02B8          | MVE_PRED                             | 66                 | Cycles where one or more predicated beats architecturally executed                     |

| 0x02CC          | MVE_STALL                            | 67                 | Stall cycles caused by an MVE instruction                                              |

| 0x02CD          | MVE_STALL_RESOURCE                   | 68                 | Stall cycles caused by an MVE instruction because of resource conflicts                |

| 0x02CE          | MVE_STALL_RESOURCE_MEM               | 69                 | resource conflicts                                                                     |

| 0x02CF          | MVE_STALL_RESOURCE_FP                | 70                 | Stall cycles caused by an MVE instruction because of floating-point resource conflicts |

| 0x02D0          | MVE_STALL_RESOURCE_INT               | 71                 | Stall cycles caused by an MVE instruction because of integer resource conflicts        |

| 0x02D3          | MVE_STALL_BREAK                      | 72                 | Stall cycles caused by an MVE chain break                                              |

| Event<br>number | Event mnemonic                                      | External<br>input bit<br>73          | Event name<br>Stall cycles caused by MVE register<br>dependency                         |  |

|-----------------|-----------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------|--|

| 0x02D4          | MVE_STALL_DEPENDENCY                                |                                      |                                                                                         |  |

| 0x4007          | ITCM_ACCESS                                         | 74                                   | Instruction Tightly Coupled Memory (ITCM)<br>access                                     |  |

| 0x4008          | DTCM_ACCESS                                         | 75                                   | Data Tightly Coupled Memory (ITCM) access                                               |  |

| 0x4010          | TRCEXTOUT0                                          | 76                                   | <i>Embedded Trace Macrocell</i> (ETM) external output 0                                 |  |

| 0x4011          | TRCEXTOUT1                                          | 77                                   | ETM external output 1                                                                   |  |

| 0x4012          | TRCEXTOUT2                                          | 78                                   | ETM external output 2                                                                   |  |

| 0x4013          | TRCEXTOUT3                                          | 79                                   | ETM external output 3                                                                   |  |

| 0x4018          | CTI_TRIGOUT4                                        | 80                                   | Cross Trigger Interface (CTI) output trigger 4                                          |  |

| 0x4019          | CTI_TRIGOUT5                                        | 81                                   | CTI output trigger 5                                                                    |  |

| 0x401A          | CTI_TRIGOUT6                                        | 82                                   | CTI output trigger 6                                                                    |  |

| 0x401B          | CTI_TRIGOUT7                                        | 83                                   | CTI output trigger 7                                                                    |  |

| 0xC000          | ECC_ERR                                             | 84                                   | One or more <i>Error Correcting Code</i> (ECC) errors detected                          |  |

| 0xC001          | ECC_ERR_MBIT                                        | 85                                   | One or more multi-bit ECC errors detected                                               |  |

| 0xC010          | ECC_ERR_DCACHE                                      | 86                                   | One or more ECC errors in the data cache                                                |  |

| 0xC011          | ECC_ERR_ICACHE                                      | 87                                   | One or more ECC errors in the instruction cache                                         |  |

| 0xC012          | ECC_ERR_MBIT_DCACHE                                 | 88                                   | One or more multi-bit ECC errors in the data cache                                      |  |

| 0xC013          | ECC_ERR_MBIT_ICACHE                                 | 89                                   | One or more multi-bit ECC errors in the instruction cache                               |  |

| 0xC020          | ECC_ERR_DTCM                                        | 90                                   | One or more ECC errors in the DTCM                                                      |  |

| 0xC021          | ECC_ERR_ITCM                                        | 91                                   | One or more ECC errors in the ITCM                                                      |  |

| 0xC022          | ECC_ERR_MBIT_DTCM 92 One or more r<br>DTCM          |                                      | One or more multi-bit ECC errors in the DTCM                                            |  |

| 0xC023          | ECC_ERR_MBIT_ITCM                                   | 93                                   | One or more multi-bit ECC errors in the ITCM                                            |  |

| 0xC100          | PF_LINEFILL     94     The prefetcher starts a line |                                      | The prefetcher starts a linefill.                                                       |  |

| 0xC101          | PF_CANCEL                                           | 95 The prefetcher stops prefetching. |                                                                                         |  |

| 0xC102          | PF_DROP_LINEFILL                                    | 96                                   | A linefill triggered by the prefetcher has been dropped because of lack of buffering.   |  |

| 0xC200          | NWAMODE_ENTER                                       | 97                                   | No-write allocate mode entry                                                            |  |

| 0xC201          |                                                     |                                      | Write-Allocate store is not allocated into the data cache due to no-write-allocate mode |  |

| Event<br>number | Event mnemonic    | External<br>input bit<br>99 | Event name                                                                                            |  |

|-----------------|-------------------|-----------------------------|-------------------------------------------------------------------------------------------------------|--|

| 0xC300          | SAHB_ACCESS       |                             | Read or write access on the S-AHB interface<br>to the TCM                                             |  |

| 0xC301          | PAHB_ACCESS       | 100                         | Read or write access to the P-AHB write interface                                                     |  |

| 0xC302          | AXI_WRITE_ACCESS  | 101                         | Any beat access to M-AXI write interface.                                                             |  |

| 0xC303          | AXI_READ_ACCESS   | 102                         | Any beat access to M-AXI read interface.                                                              |  |

| 0xC400          | DOSTIMEOUT_DOUBLE | 103                         | Denial of Service timeout has fired twice and<br>caused buffers to drain to allow forward<br>progress |  |

| 0xC401          | DOSTIMEOUT_TRIPLE | 104                         | Denial of Service timeout has fired three times<br>and blocked the LSU to force forward<br>progress   |  |

## 2.3 Operation

The ETM-M55 has IMPLEMENTATION DEFINED operations.

For information on the operation, see the Arm<sup>®</sup> Embedded Trace Macrocell Architecture Specification ETMv4.

### 2.3.1 ETM-M55 registers

There are two groups of ETM-M55 registers:

- Registers that are completely defined by the *Arm*<sup>®</sup> *Embedded Trace Macrocell Architecture Specification ETMv4*.

- Registers that are partly IMPLEMENTATION DEFINED.

### 2.3.2 Precise ViewInst events

The only condition that ensures **ViewInst** is precise is that the enabling event condition is TRUE.

For more information, see the Arm® Embedded Trace Macrocell Architecture Specification ETMv4.

### 2.3.3 Parallel instruction execution

The Cortex-M55 processor supports parallel instruction execution. This means that ETM-M55 is capable of tracing two instructions per cycle.

If ViewInst is active in a cycle when two instructions are executed, then both instructions are traced.

### 2.3.4 Trace features

The ETM-M55 implements the following optional ETMv4.5 trace features:

- Cycle-counting

- Timestamping

- · Branch broadcasting

- Conditional instruction tracing

See the *Arm*<sup>®</sup> *Embedded Trace Macrocell Architecture Specification ETMv4* for descriptions of these features.

### 2.3.5 Packet formats

This section describes the packet formats that the ETM-M55 instruction trace interface supports.

The ETM-M55 instruction trace interface does not support the following trace packet types:

- Speculation resolution packets are not supported.

- Q instruction trace packets are not supported.

ETM-M55 supports conditional tracing, but does not trace APSR condition flag values. See the *Arm*<sup>®</sup> *Embedded Trace Macrocell Architecture Specification ETMv4* for the trace packet format descriptions.

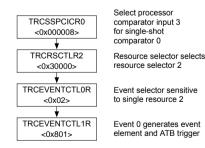

### 2.3.6 Resource selection

The ETM-M55 uses event selectors to control resources.

The ETM-M55 has the following resources:

- Reduced function counter

- Data Watchpoint and Trace (DWT) processor comparators

- Single shot comparator

- External inputs

The ETM-M55 generates the following events:

- Trace events, triggers, and markers in the trace stream

- Timestamp event

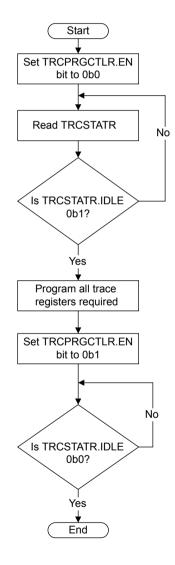

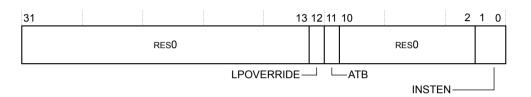

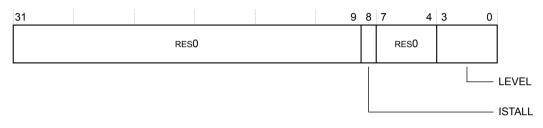

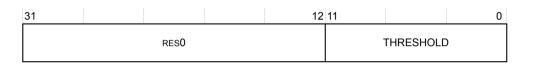

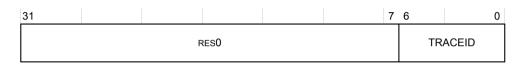

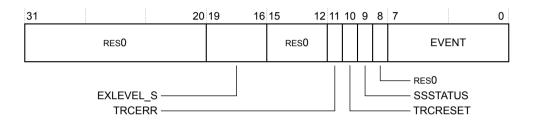

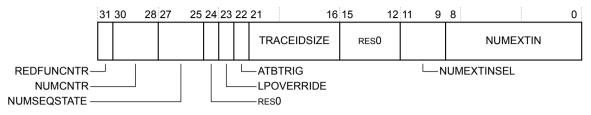

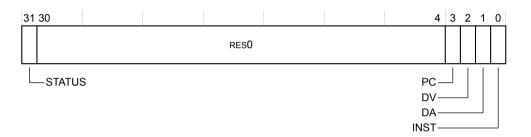

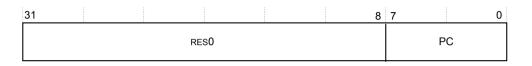

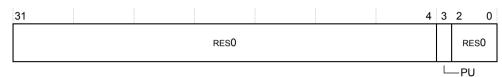

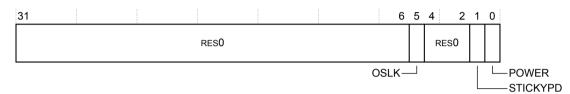

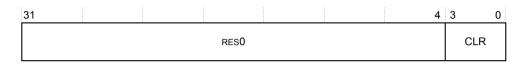

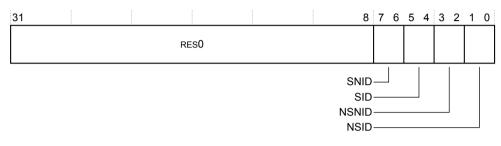

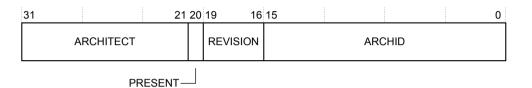

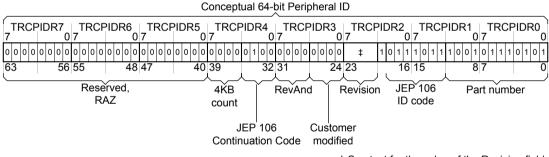

- ViewInst event