# Arm<sup>®</sup> CoreSight<sup>™</sup> TPIU-M

Revision: r0p0

**Technical Reference Manual**

### Arm<sup>®</sup> CoreSight<sup>™</sup> TPIU-M

#### **Technical Reference Manual**

Copyright © 2021 Arm Limited or its affiliates. All rights reserved.

#### **Release Information**

#### **Document History**

| Issue   | Date        | Confidentiality  | Change                     |  |

|---------|-------------|------------------|----------------------------|--|

| 0000-01 | 18 May 2021 | Non-Confidential | First release for r0p0 EAC |  |

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. **No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.**

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with <sup>®</sup> or <sup>™</sup> are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at *https://www.arm.com/company/policies/trademarks*.

Copyright © 2021 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

(LES-PRE-20349)

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

#### **Product Status**

The information in this document is Final, that is for a developed product.

#### Web Address

developer.arm.com

#### Progressive terminology commitment

Arm values inclusive communities. Arm recognizes that we and our industry have used terms that can be offensive. Arm strives to lead the industry and create change.

This document includes terms that can be offensive. We will replace these terms in a future issue of this document.

If you find offensive terms in this document, please contact terms@arm.com.

# Contents Arm<sup>®</sup> CoreSight<sup>™</sup> TPIU-M Technical Reference Manual

### Introduction

|           |      | Feedback                            |      |

|-----------|------|-------------------------------------|------|

| Chapter 1 | Abo  | ut the CoreSight™ TPIU-M            |      |

|           | 1.1  | About this product                  |      |

|           | 1.2  | Features                            | 1-13 |

|           | 1.3  | Supported standards                 | 1-14 |

|           | 1.4  | Documentation                       |      |

|           | 1.5  | Design process                      | 1-16 |

|           | 1.6  | TPIU-M component                    | 1-17 |

|           | 1.7  | Product revisions                   | 1-18 |

| Chapter 2 | TPIL |                                     |      |

|           | 2.1  | Functional interfaces               |      |

|           | 2.2  | Clocks and resets                   |      |

|           | 2.3  | Trace output modes                  |      |

|           | 2.4  | Effect of the trace clock prescaler |      |

|           | 2.5  | Parallel trace output mode          |      |

|           | 2.6  | SWO modes                           |      |

|           | 2.7  | Output interfaces                   |      |

|           | 2.8  | traceclk alignment                  |      |

|            | A.1          | Revisions                                                                                                      | Аррх-А-79 |  |  |  |  |  |

|------------|--------------|----------------------------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|

| Appendix A |              | sions                                                                                                          |           |  |  |  |  |  |

|            |              |                                                                                                                |           |  |  |  |  |  |

|            | 3.37         | TPIU Component Identification Register 3, TPIU_CIDR3                                                           |           |  |  |  |  |  |

|            | 3.36         | TPIU Component Identification Register 2, TPIU_CIDR2                                                           |           |  |  |  |  |  |

|            | 3.34         | TPIU Component Identification Register 1, TPIU_CIDR1                                                           |           |  |  |  |  |  |

|            | 3.33<br>3.34 | TPIU Component Identification Register 0, TPIU_CIDR0                                                           |           |  |  |  |  |  |

|            | 3.32<br>3.33 | TPIU Peripheral Identification Register 2, TPIU_PIDR2<br>TPIU Peripheral Identification Register 3, TPIU_PIDR3 |           |  |  |  |  |  |

|            | 3.31<br>3.32 | TPIU Peripheral Identification Register 1, TPIU_PIDR1<br>TPIU Peripheral Identification Register 2, TPIU_PIDR2 |           |  |  |  |  |  |

|            | 3.30         | TPIU Peripheral Identification Register 0, TPIU_PIDR0                                                          |           |  |  |  |  |  |

|            | 3.29         | TPIU Peripheral Identification Register 7, TPIU_PIDR7                                                          |           |  |  |  |  |  |

|            | 3.28         | TPIU Peripheral Identification Register 6, TPIU_PIDR6                                                          |           |  |  |  |  |  |

|            | 3.27         | TPIU Peripheral Identification Register 5, TPIU_PIDR5                                                          |           |  |  |  |  |  |

|            | 3.26         |                                                                                                                |           |  |  |  |  |  |

|            |              | TPIU Device Type Register, TPIU_DEVTYPE<br>TPIU Peripheral Identification Register 4, TPIU_PIDR4               |           |  |  |  |  |  |

|            | 3.24<br>3.25 | TPIU Device Identifier Register, TPIU_DEVID                                                                    |           |  |  |  |  |  |

|            |              | TPIU Device Configuration Register 1, TPIU_DEVID1                                                              |           |  |  |  |  |  |

|            | 3.22<br>3.23 | TPIU Device Configuration Register 2, TPIU_DEVID2                                                              |           |  |  |  |  |  |

|            | 3.21         | TPIU Device Architecture Register, TPIU_DEVARCH                                                                |           |  |  |  |  |  |

|            | 3.20         | TPIU Device Affinity register 1, TPIU_DEVAFF1                                                                  |           |  |  |  |  |  |

|            | 3.19         | TPIU Device Affinity register 0, TPIU_DEVAFF0                                                                  |           |  |  |  |  |  |

|            | 3.18         | TPIU Claim Tag Clear Register, TPIU_CLAIMCLR                                                                   |           |  |  |  |  |  |

|            | 3.17         | TPIU Claim Tag Set Register, TPIU_CLAIMSET                                                                     |           |  |  |  |  |  |

|            | 3.16         | TPIU Integration Mode Control Register, TPIU_ITCTRL                                                            |           |  |  |  |  |  |

|            | 3.15         | TPIU Integration Test FIFO Test Data Register 1, TPIU_ITFTTD1                                                  |           |  |  |  |  |  |

|            | 3.14         | Integration Test ATB Control Register 0, TPIU_ITATBCTR0                                                        |           |  |  |  |  |  |

|            | 3.13         | Integration Test ATB Control Register 1, TPIU_ITATBCTR1                                                        |           |  |  |  |  |  |

|            | 3.12         | TPIU Integration Test ATB Control Register 2, TPIU_ITATBCTR2                                                   |           |  |  |  |  |  |

|            | 3.11         | TPIU Integration Test FIFO Test Data Register 0, TPIU_ITFTTD0                                                  |           |  |  |  |  |  |

|            | 3.10         | TPIU Integration Test Trigger Register, TPIU_ITTRIGGER                                                         |           |  |  |  |  |  |

|            | 3.9          | TPIU Integration Test DSYNC Register, TPIU_ITDSYNC                                                             |           |  |  |  |  |  |

|            | 3.8          | TPIU Periodic Synchronization Control Register, TPIU_PSCR                                                      |           |  |  |  |  |  |

|            | 3.7          | TPIU Formatter and Flush Control Register, TPIU_FFCR                                                           |           |  |  |  |  |  |

|            | 3.6          | TPIU Formatter and Flush Status Register, TPIU_FFSR                                                            |           |  |  |  |  |  |

|            | 3.5          | TPIU Selected Pin Protocol Register, TPIU_SPPR                                                                 | 3-39      |  |  |  |  |  |

|            | 3.4          | TPIU Asynchronous Clock Prescaler Register, TPIU_ACPR                                                          | 3-37      |  |  |  |  |  |

|            | 3.3          | TPIU Current Parallel Port Size Register, TPIU_CSPSR                                                           | 3-36      |  |  |  |  |  |

|            | 3.2          | TPIU Supported Parallel Port Sizes Register, TPIU_SSPSR                                                        | 3-35      |  |  |  |  |  |

|            | 3.1          | TPIU-M register summary                                                                                        | 3-33      |  |  |  |  |  |

| Chapter 3  | Prog         | irammers model                                                                                                 |           |  |  |  |  |  |

|            | 2.11         |                                                                                                                |           |  |  |  |  |  |

|            | 2.10         | Example configuration scenarios                                                                                |           |  |  |  |  |  |

|            | 2.10         | Programming the TPIU-M for trace capture                                                                       |           |  |  |  |  |  |

|            | 2.9          | Trace port triggers                                                                                            | 2-28      |  |  |  |  |  |

# Introduction

This preface introduces the Arm<sup>®</sup> CoreSight<sup>™</sup> TPIU-M Technical Reference Manual.

It contains the following:

- *About this book* on page 7.

- Feedback on page 10.

### About this book

This book describes the interfaces, configuration options, functionality, and programmer's model of the CoreSight<sup>™</sup> Trace Port Interface Unit for Cortex<sup>®</sup>-M processors.

#### **Product revision status**

The rxpy identifier indicates the revision status of the product described in this book, for example, r1p2, where:

- rx Identifies the major revision of the product, for example, r1.

- py Identifies the minor revision or modification status of the product, for example, p2.

#### Intended audience

This book is written for the following audiences:

- Hardware and software engineers who want to incorporate CoreSight<sup>™</sup> TPIU-M into their design and produce real-time instruction and data trace information from a SoC.

- Software engineers writing tools to use CoreSight TPIU-M.

This book assumes that readers are familiar with AMBA® bus design and JTAG methodology.

#### Using this book

This book is organized into the following chapters:

#### Chapter 1 About the CoreSight<sup>™</sup> TPIU-M

This chapter introduces the CoreSight TPIU-M.

#### Chapter 2 TPIU-M functional description

This chapter describes the functionality of the CoreSight TPIU-M.

#### **Chapter 3 Programmers model**

This chapter describes the programmers model for the CoreSight TPIU-M.

#### Appendix A Revisions

This appendix describes the technical changes between released issues of this book.

#### Glossary

The Arm<sup>®</sup> Glossary is a list of terms used in Arm documentation, together with definitions for those terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

See the Arm® Glossary for more information.

#### **Typographic conventions**

#### italic

Introduces special terminology, denotes cross-references, and citations.

#### bold

Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.

monospace

Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.

#### <u>mono</u>space

Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.

#### monospace italic

Denotes arguments to monospace text where the argument is to be replaced by a specific value.

#### monospace bold

Denotes language keywords when used outside example code.

<and>

Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example:

MRC p15, 0, <Rd>, <CRn>, <CRm>, <Opcode\_2>

SMALL CAPITALS

Used in body text for a few terms that have specific technical meanings, that are defined in the *Arm*<sup>®</sup> *Glossary*. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE.

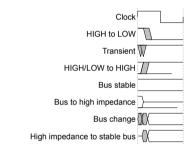

#### **Timing diagrams**

The following figure explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

#### Figure 1 Key to timing diagram conventions

#### Signals

The signal conventions are:

#### Signal level

The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

- HIGH for active-HIGH signals.

- LOW for active-LOW signals.

#### Lowercase n

At the start or end of a signal name, n denotes an active-LOW signal.

#### Additional reading

This book contains information that is specific to this product. See the following documents for other relevant information.

#### Arm publications

This book contains information that is specific to this product. See the following documents for other relevant information:

- Arm<sup>®</sup> CoreSight<sup>™</sup> Architecture Specification v3.0 (IHI 0029E)

- Arm<sup>®</sup> CoreSight<sup>™</sup> DAP-Lite2 Technical Reference Manual (100572)

- AMBA® APB Protocol Specification Version 2.0 (IHI 0024C)

- AMBA® 4 ATB Protocol Specification ATBv1.0 and ATBv1.1 (IHI 0032B)

- AMBA<sup>®</sup> Low Power Interface Specification, Arm<sup>®</sup> Q-Channel and P-Channel Interfaces (IHI 0068C)

- Arm<sup>®</sup> v8-M Architecture Reference Manual (DDI 0553B.0)

- The Technical Reference Manual for your Cortex-M processor

The following confidential books are only available to licensees:

- Arm<sup>®</sup> CoreSight<sup>™</sup> TPIU-M Configuration and Integration Manual (102428)

- Arm<sup>®</sup> CoreSight<sup>™</sup> DAP-Lite2 Configuration and Integration Manual (100589)

- The Configuration and Integration Manual for your Cortex-M processor

#### **Other publications**

- Verilog-2001 Standard (IEEE Std 1364-2001)

- Accellera, *IP-XACT version 1685-2009*

# Feedback

#### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

#### Feedback on content

If you have comments on content then send an e-mail to *errata@arm.com*. Give:

- The title Arm CoreSight TPIU-M Technical Reference Manual.

- The number 102427\_0000\_01\_en.

- If applicable, the page number(s) to which your comments refer.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

\_\_\_\_\_ Note \_\_\_\_\_

Arm tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader.

# Chapter 1 About the CoreSight<sup>™</sup> TPIU-M

This chapter introduces the CoreSight TPIU-M.

It contains the following sections:

- *1.1 About this product* on page 1-12.

- 1.2 Features on page 1-13.

- 1.3 Supported standards on page 1-14.

- *1.4 Documentation* on page 1-15.

- *1.5 Design process* on page 1-16.

- *1.6 TPIU-M component* on page 1-17.

- *1.7 Product revisions* on page 1-18.

# 1.1 About this product

CoreSight TPIU-M is a *Trace Port Interface Unit* (TPIU) that is designed for use in single-processor systems based on Arm Cortex-M processors. Using TPIU-M, you can export instrumentation trace data and processor execution trace data off-chip to a *Trace Port Analyzer* (TPA) for use in a software debugging environment, for example Arm Development Studio or Keil<sup>®</sup> *Microcontroller Development Kit* (MDK).

You can build a full CoreSight debug and trace system for a single Arm Cortex-M processor using:

- DAP-Lite2 to provide debug connectivity and control

- TPIU-M to export trace data off chip

Other CoreSight products are available to support designs with multiple processors. Contact Arm for further details.

# 1.2 Features

TPIU-M supports the following features:

- 8-bit ATB interface that supports *Instrumentation Trace Macrocell* (ITM) trace from a Cortex-M processor

- Optional second 8-bit ATB interface that supports *Embedded Trace Macrocell* (ETM) trace from a Cortex-M processor

- Configurable width parallel trace port interface for connection to an off-chip *Trace Port Analyzer* (TPA)

- Serial Wire Output support for connection to low-cost TPAs using a single pin

- Programmable clock prescaler for both parallel and serial trace output modes

- Two asynchronous clock domains: APB/ATB and trace port

- Q-Channel Low-Power Interfaces (LPIs) to support low-power implementation

- Low gate count

#### — Note —

TPIU-M supports only one trace source per ATB interface. You must connect the TPIU-M ATB interfaces directly to the Cortex-M ITM and ETM. TPIU-M is optimised for direct connection only. You must not instantiate bridges, replicators, funnels, or other components on the ATB paths between the trace sources and the TPIU-M.

# 1.3 Supported standards

CoreSight TPIU-M is compliant with the following standards:

- Arm<sup>®</sup> CoreSight<sup>™</sup> Architecture Specification v3.0

- AMBA® APB Protocol Specification Version 2.0

- AMBA<sup>®</sup> 4 ATB Protocol Specification ATBv1.0 and ATBv1.1

- AMBA® Low Power Interface Specification, Arm® Q-Channel and P-Channel Interfaces

- Verilog-2001 Standard

- Accellera, IP-XACT version 1685-2009

# 1.4 Documentation

The TPIU-M documentation includes a *Technical Reference Manual* (TRM) and a *Configuration and Integration Manual* (CIM). These books relate to the TPIU-M design flow.

#### Technical Reference Manual

The TRM describes the functionality and the effects of functional options on the behavior of the TPIU-M. It is required at all stages of the design flow. The choices that you make in the design flow can mean that some behaviors that are described in the TRM are not relevant. If you are programming a device that is based on TPIU-M components, then contact:

- The implementer to determine:

- The build configuration of the implementation

- The integration, if any, that was performed before implementing the TPIU-M

- The integrator to determine the pin configuration of your device.

#### **Configuration and Integration Manual**

The CIM describes:

- How to configure the TPIU-M

- · How to integrate the TPIU-M into your Cortex-M processor-based system

- How to implement the TPIU-M components to produce a hard macrocell of the design. This description includes custom cell replacement, a description of the power domains, and a description of the design synthesis.

The CIM is a confidential book that is only available to licensees.

# 1.5 Design process

The TPIU-M is delivered as synthesizable Verilog RTL.

Before the TPIU-M can be used in a product, it must go through the following processes:

#### System design

Determining the necessary structure and interconnections of the TPIU-M components that form the CoreSight debug and trace subsystem.

#### Configuration

Defining the memory map of the system and the functional configuration of the TPIU-M components.

#### Integration

Connecting the TPIU-M components together, and to the SoC memory system and peripherals.

#### Verification

Verifying that the CoreSight debug and trace subsystem has been correctly integrated to the processor or processors in your SoC.

#### Implementation

Using the Verilog RTL in an implementation flow to produce a hard macrocell.

The operation of the final device depends on:

#### Configuration

The implementer chooses the options that affect how the RTL source files are pre-processed. These options usually include, or exclude, logic that affects one or more of the area, maximum frequency, and features of the resulting macrocell.

#### Software configuration

The programmer configures the CoreSight debug and trace subsystem by programming specific values into registers that affect the behavior of the TPIU-M components.

# 1.6 TPIU-M component

The following table shows the component and its version.

#### Table 1-1 TPIU-M component list

| Name  | Description                            | Version | Revision | IP-XACT version |

|-------|----------------------------------------|---------|----------|-----------------|

| tpium | Trace Port Interface Unit for Cortex-M | r0p0    | 0        | r0p0_0          |

\_\_\_\_\_ Note \_\_\_\_\_

The Revision column shows the value of the PIDR2.REVISION field.

# 1.7 Product revisions

This section describes the differences in functionality between product revisions of the CoreSight TPIU-M.

r0p0

First release of CoreSight TPIU-M.

# Chapter 2 TPIU-M functional description

This chapter describes the functionality of the CoreSight TPIU-M.

It contains the following sections:

- 2.1 Functional interfaces on page 2-20.

- 2.2 Clocks and resets on page 2-21.

- 2.3 Trace output modes on page 2-22.

- 2.4 Effect of the trace clock prescaler on page 2-23.

- 2.5 Parallel trace output mode on page 2-24.

- 2.6 SWO modes on page 2-25.

- 2.7 Output interfaces on page 2-26.

- 2.8 traceclk alignment on page 2-27.

- 2.9 Trace port triggers on page 2-28.

- 2.10 Programming the TPIU-M for trace capture on page 2-29.

- 2.11 Example configuration scenarios on page 2-30.

# 2.1 Functional interfaces

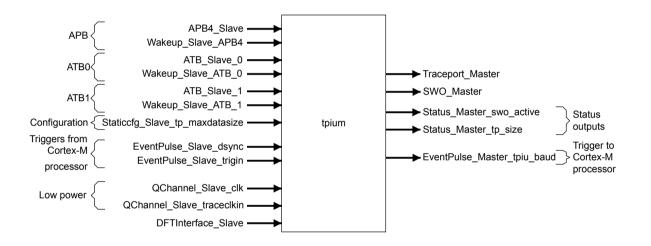

This section describes the functional interfaces of the TPIU-M.

The functional interfaces are:

#### **ATB** slave interfaces

Receive trace data

#### APB slave interface

Accesses the TPIU-M registers

#### Trace out port

Connects to the external trace port pins

#### Serial Wire Output

Connects to the external SWO pin

#### **Triggers from Cortex-M processor**

Permit interaction with the processor ITM and DWT counters and ETM events

The following figure shows the external connections of the TPIU-M.

Figure 2-1 TPIU-M block diagram

# 2.2 Clocks and resets

The clock and reset signals of the TPIU-M are clk, traceclkin, reset\_n, and treset\_n.

The TPIU-M includes an asynchronous bridge between the **traceclkin** clock domain and the rest of the design.

### 2.3 Trace output modes

TPIU-M supports three trace output modes:

- Parallel trace mode

- Serial Wire Output (SWO) using UART (NRZ) encoding

- SWO using Manchester encoding

To select the trace output modes, set TPIU\_SPPR.TXMODE.

The Parallel trace is synchronously clocked. TPIU-M supports 16, 12, 8, 4, 2, and 1-bit data widths, set by the system integrator. TPIU\_SSPSR register describes the supported widths.

To set the active parallel trace width, program the TPIU\_CSPSR register. This enables debug tools to select a value that is supported by their *Trace Port Analyzer* (TPA).

For all three trace output modes, the data rate is a function of **traceclkin** and the clock prescaler TPIU\_ACPR.

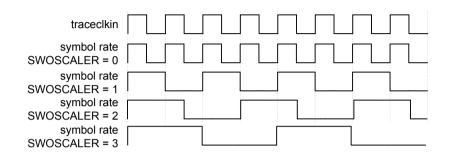

# 2.4 Effect of the trace clock prescaler

The TPIU-M includes a 13-bit prescaler register TPIU\_ACPR that you can program to slow the rate of generated trace compared to the reference clock **traceclkin**.

The prescaler affects both Serial Wire Output and Parallel trace modes. It determines the symbol rate of the TPIU-M output interfaces as follows:

symbol rate = **traceclkin** \* 1/(TPIU\_ACPR.SWOSCALER + 1)

The following figure shows the prescaler timing.

Figure 2-2 TPIU-M prescaler timing

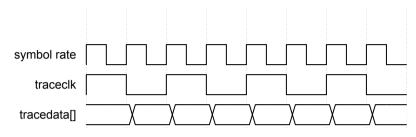

# 2.5 Parallel trace output mode

When the TPIU-M is programmed to generate parallel trace, when TPIU\_SPPR.TXMODE = 0b00:

- tracedata can change at a maximum rate of the symbol rate

- traceclk changes at the symbol rate

The frequency of **traceclk** is therefore half of the symbol rate.

Trace data is sampled on both edges of traceclk.

The gross bit rate of the parallel interface is  $N \times$  symbol rate, where N is the number of parallel bits.

The following figure shows the parallel trace timing.

Figure 2-3 TPIU-M parallel trace timing

# 2.6 SWO modes

In SWO modes the traceclk signal remains static.

#### UART (NRZ) mode

When the TPIU-M is programmed to generate UART *Non Return to Zero* (NRZ) format SWO, when TPIU\_SPPR.TXMODE = 0b10, swo can change at the symbol rate.

The gross bit rate of the interface is equal to 1 \* symbol rate.

UART (NRZ) encoding has an overhead of two symbols that represent the start bit and stop bit for every 8 data bits.

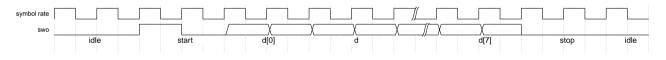

The following figure shows the SWO UART timing.

Figure 2-4 TPIU-M SWO UART timing

#### Manchester mode

When the TPIU-M is programmed to generate Manchester format SWO, when TPIU\_SPPR.TXMODE = 0b01, swo may change at the symbol rate.

The gross bit rate of the interface is equal to symbol rate / 2, because each data bit is represented by two symbols.

Manchester encoding has an overhead of four symbols that represent the start and stop bit for each block of 8-64 data bits. The data is sent LSB first.

The following figure shows the SWO Manchester timing.

Figure 2-5 TPIU-M SWO Manchester timing

# 2.7 Output interfaces

This section contains the following subsections:

- 2.7.1 Parallel trace out port on page 2-26.

- 2.7.2 Serial Wire Output on page 2-26.

#### 2.7.1 Parallel trace out port

This section describes the parallel trace out port signals.

To select parallel trace mode you must program TPIU\_SPPR. TPIU\_SSPSR indicates the supported parallel trace port widths. To select the active parallel trace port width, program TPIU\_CSPSR. You can vary the data rate of the interface by programming TPIU\_ACPR.

The following table summarizes the trace out port signals.

#### Table 2-1 Trace out port signals

| Signal                              | Туре   | Description                                                                                                                                                                                                                                                                         |

|-------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| traceclk                            | Output | Output clock, that the TPA uses to sample the other pins of the trace out<br>port. This signal is <b>traceclkin</b> divided by 2*(TPIU_ACPR.SWOSCALER<br>+1) when parallel trace is enabled (TPIU_SPPR=0x0) and otherwise<br>static, and data is valid on both edges of this clock. |

| tracedata[TRACEPORT_DATA_WIDTH-1:0] | Output | Output data. A system might not connect all the bits of this signal to the trace port pins. The connection depends on the number of pins available and the bandwidth that is required to output trace.                                                                              |

#### 2.7.2 Serial Wire Output

This section describes the Serial Wire Output signals.

To select Serial Wire Output mode you must program TPIU\_SPPR. You can vary the data rate of the interface by pogramming TPIU\_ACPR.

The following table summarizes the Serial Wire output signals.

#### Table 2-2 Trace out port signals

| Signal Type D |        | Description                                                                                                    |

|---------------|--------|----------------------------------------------------------------------------------------------------------------|

| swo           | Output | Serial Wire Output data. Connect this signal to a pin on your device, for connection to a Trace Port Analyser. |

# 2.8 traceclk alignment

The TPIU-M does not offset the edges of traceclk from the edges of the trace data signals tracedata.

Arm recommends that, to support the widest range of targets at the maximum speed, TPAs support systems with a variety of alignments of **traceclk** relative to the data signals, including systems where edges of **traceclk** occur at the same time as transitions of the data signals.

# 2.9 Trace port triggers

TPIU-M supports Continuous mode and Bypass mode only.

See TPIU Formatter and Flush Control Register, TPIU FFCR.

Triggers received by the TPIU-M on the **trigin** input cause trigger packets to be inserted into the formatted trace data in Continuous mode. Triggers are ignored in Bypass mode.

# 2.10 Programming the TPIU-M for trace capture

Arm recommends that debug tools perform a flush by writing TPIU\_FFCR.FOnMan = 1 whenever the TPIU-M is reprogrammed. This causes a Full Sync Packet to be generated in the formatted trace stream, which enables the connected *Trace Port Analyzer* (TPA) to detect the start the frame and decode the subsequent data.

# 2.11 Example configuration scenarios

You can choose from the following modes, controlled with TPIU\_SPPR:

- Asynchronous trace via swo, Manchester encoded: rate is set with TPIU\_ACPR

- Asynchronous trace via swo, NRZ encoded: rate is set with TPIU\_ACPR

- Parallel Trace via tracedata: width is set with TPIU\_CSPSR, rate is set with TPIU\_ACPR

# Chapter 3 Programmers model

This chapter describes the programmers model for the CoreSight TPIU-M.

It contains the following sections:

- 3.1 TPIU-M register summary on page 3-33.

- 3.2 TPIU Supported Parallel Port Sizes Register, TPIU SSPSR on page 3-35.

- 3.3 TPIU Current Parallel Port Size Register, TPIU CSPSR on page 3-36.

- 3.4 TPIU Asynchronous Clock Prescaler Register, TPIU ACPR on page 3-37.

- 3.5 TPIU Selected Pin Protocol Register, TPIU SPPR on page 3-39.

- 3.6 TPIU Formatter and Flush Status Register, TPIU FFSR on page 3-40.

- 3.7 TPIU Formatter and Flush Control Register, TPIU FFCR on page 3-41.

- 3.8 TPIU Periodic Synchronization Control Register, TPIU PSCR on page 3-43.

- 3.9 TPIU Integration Test DSYNC Register, TPIU ITDSYNC on page 3-45.

- 3.10 TPIU Integration Test Trigger Register, TPIU ITTRIGGER on page 3-46.

- 3.11 TPIU Integration Test FIFO Test Data Register 0, TPIU ITFTTD0 on page 3-47.

- 3.12 TPIU Integration Test ATB Control Register 2, TPIU ITATBCTR2 on page 3-49.

- 3.13 Integration Test ATB Control Register 1, TPIU ITATBCTR1 on page 3-50.

- 3.14 Integration Test ATB Control Register 0, TPIU ITATBCTR0 on page 3-51.

- 3.15 TPIU Integration Test FIFO Test Data Register 1, TPIU ITFTTD1 on page 3-52.

- 3.16 TPIU Integration Mode Control Register, TPIU ITCTRL on page 3-54.

- 3.17 TPIU Claim Tag Set Register, TPIU CLAIMSET on page 3-56.

- 3.18 TPIU Claim Tag Clear Register, TPIU CLAIMCLR on page 3-57.

- 3.19 TPIU Device Affinity register 0, TPIU DEVAFF0 on page 3-58.

- 3.20 TPIU Device Affinity register 1, TPIU DEVAFF1 on page 3-59.

- 3.21 TPIU Device Architecture Register, TPIU DEVARCH on page 3-60.

- 3.22 TPIU Device Configuration Register 2, TPIU DEVID2 on page 3-61.

- 3.23 TPIU Device Configuration Register 1, TPIU DEVID1 on page 3-62.

- 3.24 TPIU Device Identifier Register, TPIU DEVID on page 3-63.

- 3.25 TPIU Device Type Register, TPIU DEVTYPE on page 3-65.

- 3.26 TPIU Peripheral Identification Register 4, TPIU PIDR4 on page 3-66.

- 3.27 TPIU Peripheral Identification Register 5, TPIU PIDR5 on page 3-67.

- 3.28 TPIU Peripheral Identification Register 6, TPIU PIDR6 on page 3-68.

- 3.29 TPIU Peripheral Identification Register 7, TPIU PIDR7 on page 3-69.

- 3.30 TPIU Peripheral Identification Register 0, TPIU PIDR0 on page 3-70.

- 3.31 TPIU Peripheral Identification Register 1, TPIU PIDR1 on page 3-71.

- 3.32 TPIU Peripheral Identification Register 2, TPIU\_PIDR2 on page 3-72.

- 3.33 TPIU Peripheral Identification Register 3, TPIU PIDR3 on page 3-73.

- 3.34 TPIU Component Identification Register 0, TPIU CIDR0 on page 3-74.

- 3.35 TPIU Component Identification Register 1, TPIU CIDR1 on page 3-75.

- 3.36 TPIU Component Identification Register 2, TPIU CIDR2 on page 3-76.

- 3.37 TPIU Component Identification Register 3, TPIU CIDR3 on page 3-77.

# 3.1 TPIU-M register summary

The register summary lists all the TPIU-M registers and their key characteristics.

#### Table 3-1 tpium register summary

| Offset | Name           | Туре | Reset      | Width | Description                                                                            |

|--------|----------------|------|------------|-------|----------------------------------------------------------------------------------------|

| 0x000  | TPIU_SSPSR     | RO   | 0x0000     | 32    | 3.2 TPIU Supported Parallel Port Sizes Register, TPIU_SSPSR<br>on page 3-35            |

| 0x004  | TPIU_CSPSR     | RW   | 0x00000001 | 32    | <i>3.3 TPIU Current Parallel Port Size Register, TPIU_CSPSR</i> on page 3-36           |

| 0x010  | TPIU_ACPR      | RW   | 0x00000000 | 32    | <i>3.4 TPIU Asynchronous Clock Prescaler Register, TPIU_ACPR</i> on page 3-37          |

| 0x0F0  | TPIU_SPPR      | RW   | 0x00000001 | 32    | 3.5 TPIU Selected Pin Protocol Register, TPIU_SPPR on page 3-39                        |

| 0x300  | TPIU_FFSR      | RO   | 0x00000008 | 32    | 3.6 TPIU Formatter and Flush Status Register, TPIU_FFSR<br>on page 3-40                |

| 0x304  | TPIU_FFCR      | RW   | 0x00000100 | 32    | 3.7 TPIU Formatter and Flush Control Register, TPIU_FFCR<br>on page 3-41               |

| 0x308  | TPIU_PSCR      | RW   | 0x0000000A | 32    | <i>3.8 TPIU Periodic Synchronization Control Register, TPIU_PSCR</i> on page 3-43      |

| 0xEE4  | TPIU_ITDSYNC   | RO   | 0x00000000 | 32    | 3.9 TPIU Integration Test DSYNC Register, TPIU_ITDSYNC on page 3-45                    |

| 0xEE8  | TPIU_ITTRIGGER | RO   | 0x00000000 | 32    | 3.10 TPIU Integration Test Trigger Register; TPIU_ITTRIGGER<br>on page 3-46            |

| 0xEEC  | TPIU_ITFTTD0   | RO   | 0x00000000 | 32    | <i>3.11 TPIU Integration Test FIFO Test Data Register 0, TPIU_ITFTTD0</i> on page 3-47 |

| 0xEF0  | TPIU_ITATBCTR2 | WO   | 0x00000000 | 32    | 3.12 TPIU Integration Test ATB Control Register 2, TPIU_ITATBCTR2<br>on page 3-49      |

| 0xEF4  | TPIU_ITATBCTR1 | RO   | 0x00000000 | 32    | 3.13 Integration Test ATB Control Register 1, TPIU_ITATBCTR1<br>on page 3-50           |

| 0xEF8  | TPIU_ITATBCTR0 | RO   | 0x00000000 | 32    | 3.14 Integration Test ATB Control Register 0, TPIU_ITATBCTR0<br>on page 3-51           |

| 0xEFC  | TPIU_ITFTTD1   | RW   | 0x00000000 | 32    | 3.15 TPIU Integration Test FIFO Test Data Register 1, TPIU_ITFTTD1<br>on page 3-52     |

| 0xF00  | TPIU_ITCTRL    | RW   | 0x00000000 | 32    | 3.16 TPIU Integration Mode Control Register, TPIU_ITCTRL<br>on page 3-54               |

| 0xFA0  | TPIU_CLAIMSET  | RW   | 0x000000F  | 32    | 3.17 TPIU Claim Tag Set Register, TPIU_CLAIMSET on page 3-56                           |

| 0xFA4  | TPIU_CLAIMCLR  | RW   | 0x00000000 | 32    | 3.18 TPIU Claim Tag Clear Register, TPIU_CLAIMCLR on page 3-57                         |

| 0xFA8  | TPIU_DEVAFF0   | RO   | 0x00000000 | 32    | 3.19 TPIU Device Affinity register 0, TPIU_DEVAFF0 on page 3-58                        |

| 0xFAC  | TPIU_DEVAFF1   | RO   | 0x00000000 | 32    | 3.20 TPIU Device Affinity register 1, TPIU_DEVAFF1 on page 3-59                        |

| 0xFBC  | TPIU_DEVARCH   | RO   | 0x00000000 | 32    | <i>3.21 TPIU Device Architecture Register, TPIU_DEVARCH</i> on page 3-60               |

| 0xFC0  | TPIU_DEVID2    | RO   | 0x00000000 | 32    | <i>3.22 TPIU Device Configuration Register 2, TPIU_DEVID2</i> on page 3-61             |

#### Table 3-1 tpium register summary (continued)

| Offset | Name         | Туре | Reset      | Width | Description                                                                    |

|--------|--------------|------|------------|-------|--------------------------------------------------------------------------------|

| 0xFC4  | TPIU_DEVID1  | RO   | 0x00000000 | 32    | 3.23 TPIU Device Configuration Register 1, TPIU_DEVID1<br>on page 3-62         |

| 0xFC8  | TPIU_DEVID   | RO   | 0x00020C2- | 32    | 3.24 TPIU Device Identifier Register, TPIU_DEVID on page 3-63                  |

| 0xFCC  | TPIU_DEVTYPE | RO   | 0x00000011 | 32    | 3.25 TPIU Device Type Register, TPIU_DEVTYPE on page 3-65                      |

| 0xFD0  | TPIU_PIDR4   | RO   | 0x00000004 | 32    | <i>3.26 TPIU Peripheral Identification Register 4, TPIU_PIDR4</i> on page 3-66 |

| 0xFD4  | TPIU_PIDR5   | RO   | 0x00000000 | 32    | <i>3.27 TPIU Peripheral Identification Register 5, TPIU_PIDR5</i> on page 3-67 |

| 0xFD8  | TPIU_PIDR6   | RO   | 0x00000000 | 32    | <i>3.28 TPIU Peripheral Identification Register 6, TPIU_PIDR6</i> on page 3-68 |

| 0xFDC  | TPIU_PIDR7   | RO   | 0x00000000 | 32    | <i>3.29 TPIU Peripheral Identification Register 7, TPIU_PIDR7</i> on page 3-69 |

| 0xFE0  | TPIU_PIDR0   | RO   | 0x000000F1 | 32    | 3.30 TPIU Peripheral Identification Register 0, TPIU_PIDR0<br>on page 3-70     |

| 0xFE4  | TPIU_PIDR1   | RO   | 0x000000B9 | 32    | 3.31 TPIU Peripheral Identification Register 1, TPIU_PIDR1<br>on page 3-71     |

| 0xFE8  | TPIU_PIDR2   | RO   | 0x0000000B | 32    | <i>3.32 TPIU Peripheral Identification Register 2, TPIU_PIDR2</i> on page 3-72 |

| 0xFEC  | TPIU_PIDR3   | RO   | 0x00000000 | 32    | <i>3.33 TPIU Peripheral Identification Register 3, TPIU_PIDR3</i> on page 3-73 |

| 0xFF0  | TPIU_CIDR0   | RO   | 0x0000000D | 32    | 3.34 TPIU Component Identification Register 0, TPIU_CIDR0<br>on page 3-74      |

| 0xFF4  | TPIU_CIDR1   | RO   | 0x00000090 | 32    | 3.35 TPIU Component Identification Register 1, TPIU_CIDR1<br>on page 3-75      |

| 0xFF8  | TPIU_CIDR2   | RO   | 0x00000005 | 32    | 3.36 TPIU Component Identification Register 2, TPIU_CIDR2<br>on page 3-76      |

| 0xFFC  | TPIU_CIDR3   | RO   | 0x000000B1 | 32    | 3.37 TPIU Component Identification Register 3, TPIU_CIDR3<br>on page 3-77      |

# 3.2 TPIU Supported Parallel Port Sizes Register, TPIU\_SSPSR

Indicates the supported parallel trace port sizes.

The possible values of each bit are:

0

Parallel trace port width (m+1) not supported.

1

Parallel trace port width (m+1) supported.

Attributes Offset

0x000

Type

Read-only

Reset

0x0000---Width

32

Bit descriptions

The following image shows the register bit assignments.

SWIDTH

#### Figure 3-1 TPIU\_SSPSR

The following table shows the register bit assignments.

#### Table 3-2 TPIU\_SSPSR attributes

| Bits   | Reset value               | Name   | Туре          | Function                                                                                                                                  |  |

|--------|---------------------------|--------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| [31:0] | IMPLEMENTATION<br>DEFINED | SWIDTH | Read-<br>only | Supported width. SwiDTTI[III] indicates whether a parametrize port width of                                                               |  |

|        |                           |        |               | The supported port sizes depend on the configuration parameter TRACEPORT_DATA_WIDTH and the configuration tie-off <b>tp_maxdatasize</b> . |  |

|        |                           |        |               | <b>0x0001</b> 1 bit Parallel Trace is supported.                                                                                          |  |

|        |                           |        |               | <b>0x0003</b> 1 and 2 bit Parallel Trace is supported.                                                                                    |  |

|        |                           |        |               | <b>0x000B</b> 1, 2 and 4 bit Parallel Trace is supported.                                                                                 |  |

|        |                           |        |               | <b>0x008B</b> 1, 2, 4 and 8 bit Parallel Trace is supported.                                                                              |  |

|        |                           |        |               | <b>0x088B</b> 1, 2, 4, 8 and 12 bit Parallel Trace is supported.                                                                          |  |

|        |                           |        |               | <b>0x888B</b> 1, 2, 4, 8, 12 and 16 bit Parallel Trace is supported.                                                                      |  |

# 3.3 TPIU Current Parallel Port Size Register, TPIU\_CSPSR

Controls the width of the parallel trace port.

The possible values of each bit are:

0

Width (m+1) is not the current parallel trace port width.

1

Width (m+1) is the current parallel trace port width.

A debugger must set only one bit to 1, and all others must be zero.

The effect of writing a value with more than one bit set to 1 is architecurally UNPREDICTABLE.

The effect of a write to an unsupported bit is UNPREDICTABLE.

This register resets to the value for the smallest supported parallel trace port size.

#### Attributes

#### Offset

0x004

Туре

Read-write

Reset

0x00000001

#### Width

31

32

#### **Bit descriptions**

The following image shows the register bit assignments.

CWIDTH

#### Figure 3-2 TPIU\_CSPSR

0

The following table shows the register bit assignments.

#### Table 3-3 TPIU\_CSPSR attributes

| Bits   | Reset value | Name   | Туре       | Function                                                                        |

|--------|-------------|--------|------------|---------------------------------------------------------------------------------|

| [31:0] | 0x1         | CWIDTH | Read-write | Current width. CWIDTH $[m]$ represents a parallel trace port width of $(m+1)$ . |

# 3.4 TPIU Asynchronous Clock Prescaler Register, TPIU\_ACPR

Defines a prescaler value for the baud rate of the Serial Wire Output (SWO).

Writing to the register automatically updates the prescale counter, immediately affecting the baud rate of the serial data output.

If a debugger changes the register value while the TPIU is transmitting data, the effect on the output stream is UNPREDICTABLE and the required recovery process is IMPLEMENTATION DEFINED.

SWO or Parallel trace port output clock = Asynchronous\_Reference\_Clock/(\$n + 1)

When TPIU\_SPPR.TXMODE=0b00, the parallel trace clock traceclk is traceclkin / 2\*(TPIU\_ACPR.SWOSCALER + 1).

When TPIU\_SPPR.TXMODE=0b01 or TPIU\_SPPR.TXMODE=0b10 the Serial Wire Output trace is generated at a rate of traceclkin / (TPIU\_ACPR.SWOSCALER + 1), and the parallel trace clock traceclk remains static.

#### Attributes

#### Offset

0x010

Туре

Read-write

Reset

0x00000000

#### Width

32

#### **Bit descriptions**

The following image shows the register bit assignments.

| 31 15  | 14 0      |

|--------|-----------|

| RES0_0 | SWOSCALER |

Figure 3-3 TPIU\_ACPR

The following table shows the register bit assignments.

# Table 3-4 TPIU\_ACPR attributes

| Bits    | Reset<br>value | Name      | Туре           | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|----------------|-----------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:15] | 0x0            | RES0_0    | Read-<br>write | Reserved bit or field with SBZP behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| [14:0]  | 0x0            | SWOSCALER | Read-<br>write | SWO and Parallel trace port baud rate prescaler.<br>Sets the ratio between an IMPLEMENTATION DEFINED reference clock and the TPIU<br>output clock rates.<br>The prescaler always sets the ratio for the SWO output clock. When<br>TPIU_DEVID.CPPT is one, the prescaler also sets the ratio for the Parallel trace<br>port clock.<br>The supported scaler value range is IMPLEMENTATION DEFINED, to a maximum scaler<br>value of ØxFFFF.<br>Unused bits of this field are RAZ/WI.<br>TPIU-M implements bits [12:0] only, supporting a maximum scaler value of<br>Øx1FFF. |

# 3.5 TPIU Selected Pin Protocol Register, TPIU\_SPPR

Selects the protocol used for trace output.

The effect of selecting a reserved value, or a mode that the implementation does not support, is UNPREDICTABLE.

If a debugger changes the register value while the TPIU is transmitting data, the effect on the output stream is UNPREDICTABLE and the required recovery process is IMPLEMENTATION DEFINED.

#### Attributes

| Offset   |            |

|----------|------------|

|          | 0x0F0      |

| Туре     |            |

| -, , , , | Read-write |

| Reset    |            |

|          | 0x00000001 |

| Width    |            |

|          | 32         |

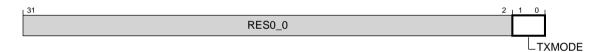

#### **Bit descriptions**

The following image shows the register bit assignments.

#### Figure 3-4 TPIU\_SPPR

The following table shows the register bit assignments.

#### Table 3-5 TPIU\_SPPR attributes

| Bits   | Reset value | Name   | Туре       | Function                                                                                              |                                                                                                               |  |  |  |

|--------|-------------|--------|------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|

| [31:2] | 0x0         | RES0_0 | Read-write | Reserved b                                                                                            | oit or field with SBZP behavior                                                                               |  |  |  |

| [1:0]  | 0b01        | TXMODE | Read-write | Transmit n                                                                                            | Fransmit mode. Specifies the protocol for trace output from the TPIU.                                         |  |  |  |

|        |             |        |            | 0Ь00                                                                                                  | Parallel trace port mode. This value is reserved if TPIU_DEVID.PTINVALID == 1.                                |  |  |  |

|        |             |        |            | 0b01                                                                                                  | <b>0b01</b> Asynchronous SWO, using Manchester encoding. This value is reserved if TPIU_DEVID.MANCVALID == 0. |  |  |  |

|        |             |        |            | <b>0b10</b> Asynchronous SWO, using NRZ encoding. This value is reserved if TPIU_DEVID.NRZVALID == 0. |                                                                                                               |  |  |  |

|        |             |        |            | 0b11                                                                                                  | RESERVED.                                                                                                     |  |  |  |

# 3.6 TPIU Formatter and Flush Status Register, TPIU\_FFSR

Shows the status and capabilities of the TPIU formatter.

| Attributes       |                                       |  |  |  |  |  |  |  |  |

|------------------|---------------------------------------|--|--|--|--|--|--|--|--|

| Offset           |                                       |  |  |  |  |  |  |  |  |

|                  | 0x300                                 |  |  |  |  |  |  |  |  |

| Туре             |                                       |  |  |  |  |  |  |  |  |

|                  | Read-only                             |  |  |  |  |  |  |  |  |

| Reset            |                                       |  |  |  |  |  |  |  |  |

|                  | 0x0000008                             |  |  |  |  |  |  |  |  |

| Width            |                                       |  |  |  |  |  |  |  |  |

|                  | 32                                    |  |  |  |  |  |  |  |  |

| Bit descriptions |                                       |  |  |  |  |  |  |  |  |

| TT1 0 11         | · · · · · · · · · · · · · · · · · · · |  |  |  |  |  |  |  |  |

The following image shows the register bit assignments.

| _ 31 4              | 3 | 12 | 1 | 0   | L                  |

|---------------------|---|----|---|-----|--------------------|

| RES0_0              |   |    |   |     |                    |

| FtNonStop<br>TCPres |   | t⊥ |   | FtS | FIInProg<br>topped |

#### Figure 3-5 TPIU\_FFSR

The following table shows the register bit assignments.

#### Table 3-6 TPIU\_FFSR attributes

| Bits   | Reset<br>value | Name      | Туре      | Function                                                                                                                                                                                                                                                                                                                                |  |  |  |

|--------|----------------|-----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| [31:4] | 0x0            | RES0_0    | Read-only | Reserved bit or field with SBZP behavior                                                                                                                                                                                                                                                                                                |  |  |  |

| [3]    | 1              | FtNonStop | Read-only | Non-stop formatter. The value cannot be changed.<br>The fixed value of 1 indicates that the formatter cannot be stopped.                                                                                                                                                                                                                |  |  |  |

| [2]    | 0              | TCPresent | Read-only | TRACECTL present. The value cannot be changed.<br>The fixed value of 0 indicates that the TRACECTL pin is not present.                                                                                                                                                                                                                  |  |  |  |

| [1]    | 0              | FtStopped | Read-only | Formatter stopped. The value cannot be changed.<br>The fixed value of 0 indicates that the formatter has not stopped.                                                                                                                                                                                                                   |  |  |  |

| [0]    | 0              | FlInProg  | Read-only | <ul> <li>Flush in progress. Set to 1 when a flush is initiated and clears to zero when all data received before the flush is acknowledged has been output on the trace port. That is, t trace has been received at the sink, formatted, and output on the trace port.</li> <li>No ongoing flush.</li> <li>Flush in progress.</li> </ul> |  |  |  |

# 3.7 TPIU Formatter and Flush Control Register, TPIU\_FFCR

Controls the TPIU formatter.

| Attributes |            |  |  |  |  |  |  |  |

|------------|------------|--|--|--|--|--|--|--|

| Offset     |            |  |  |  |  |  |  |  |

|            | 0x304      |  |  |  |  |  |  |  |

| Туре       | Read-write |  |  |  |  |  |  |  |

| Reset      | 0x00000100 |  |  |  |  |  |  |  |

| Width      | 32         |  |  |  |  |  |  |  |

# **Bit descriptions**

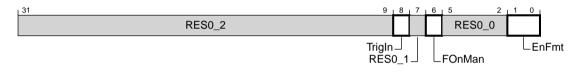

The following image shows the register bit assignments.

#### Figure 3-6 TPIU\_FFCR

The following table shows the register bit assignments.

#### Table 3-7 TPIU\_FFCR attributes

| Bits   | Reset<br>value | Name   | Туре       | Function                                                                                                                                                                                                                                                            |

|--------|----------------|--------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:9] | 0x0            | RES0_2 | Read-write | Reserved bit or field with SBZP behavior                                                                                                                                                                                                                            |

| [8]    | 1              | TrigIn | Read-only  | <ul> <li>Trigger input asserted. Indicate a trigger on the trace port when an IMPLEMENTATION DEFINED TRIGIN signal is asserted.</li> <li>Disable trigger indication when trigin is asserted.</li> <li>Enable trigger indication when trigin is asserted.</li> </ul> |

| [7]    | 0              | RES0_1 | Read-write | Reserved bit or field with SBZP behavior                                                                                                                                                                                                                            |

| [6]    | 0              | FOnMan | Read-write | Flush On Manual. Setting this bit to 1 generates a flush. The TPIU clears the bit to 0 when the flush completes.                                                                                                                                                    |

# Table 3-7 TPIU\_FFCR attributes (continued)

| Bits  | Reset<br>value | Name   | Туре       | Function                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|-------|----------------|--------|------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| [5:2] | 0Ь0000         | RES0_0 | Read-write | Reserved bi                                                               | t or field with SBZP behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| [1:0] | 0600           | EnFmt  | Read-write | This field m<br>multiple trac<br>Changing th<br>Arm recomm<br><b>0b00</b> | ontrol. Selects the output formatting mode.<br>nust be set to 0b10 when the parallel trace port is selected, or when using<br>ce sources.<br>ne value of this field when TPIU_FFSR.FtStopped is 0 is UNPREDICTABLE.<br>mends that you change this field only when the ATB interfaces are idle.<br>Bypass. Disable formatting. Only supported when SWO mode is selected.<br>Only a single trace source is supported in bypass mode: If only a single<br>trace source is connected to this TPIU, it is selected. If multiple sources<br>(including the ITM) are implemented and connected to this TPIU, then all<br>other trace sources, except for the ITM, must be disabled. Otherwise, the<br>trace output is UNPREDICTABLE. All other trace sources are discarded. |  |

|       |                |        |            | 0b01                                                                      | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|       |                |        |            |                                                                           | <b>b10</b> Continuous. Enable formatting and embed triggers and null cycles in the formatted output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|       |                |        |            | 0b11                                                                      | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

# 3.8 TPIU Periodic Synchronization Control Register, TPIU\_PSCR

Defines the reload value for the Periodic Synchronization Counter register.

The Periodic Synchronization Counter decrements for each byte that is output by the TPIU. If the formatter is implemented and enabled, the TPIU forces completion of the current frame when the counter reaches zero. The TPIU forces all trace sources to generate synchronization packets with the implemented **syncreqx\_s** signals when the counter reaches zero. Bytes generated by the TPIU as part of a Halfword synchronization packet or a Full frame synchronization packet are not counted.

#### Attributes

| Offset | 0x308      |

|--------|------------|

| Туре   | Read-write |

| Reset  | 0x000000A  |

| Width  | 32         |

| Reset  | 0x000000A  |

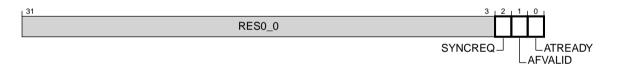

#### **Bit descriptions**

The following image shows the register bit assignments.

| L 31 5 | 4 | 0       |

|--------|---|---------|

| RES0_0 |   | PSCount |

|        |   |         |

Figure 3-7 TPIU\_PSCR

The following table shows the register bit assignments.

# Table 3-8 TPIU\_PSCR attributes

| Bits   | Reset<br>value | Name    | Туре           | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------|----------------|---------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:5] | 0x0            | RES0_0  | Read-<br>write | Reserved bit or field with SBZP behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| [4:0]  | 0Ь01010        | PSCount | Read-<br>write | <ul> <li>Periodic Synchronization Count.</li> <li>Determines the reload value of the Periodic Synchronization Counter.</li> <li>The reload value takes effect the next time the counter reaches zero. Reads from this register return the reload value programmed into this register. The possible values of this field are:</li> <li><b>0b00000</b> Synchronization disabled.</li> <li><b>0b00111</b> 128 bytes.</li> <li><b>0b01000</b> 256 bytes.</li> <li></li> <li><b>0b11111</b> 2^31 bytes.</li> <li>All other values are reserved.</li> <li>The Periodic Synchronization Counter might have a maximum value smaller than 2^31. In this case, if the programmed reload value is greater than the maximum value, then the Periodic Synchronization Counter is reloaded with its maximum value and the TPIU will generate synchronization requests at this interval.</li> <li>TPIU-M supports a maximum value of <b>0b100000</b>.</li> </ul> |

# 3.9 TPIU Integration Test DSYNC Register, TPIU\_ITDSYNC

This register indicates the integration status of the dsync input in integration mode.

Reads are allowed even in functional mode, but the register itself is disabled and does not get updated even if the inputs change.

| Attribu                                                 | Attributes |  |  |  |  |  |

|---------------------------------------------------------|------------|--|--|--|--|--|

| Offset                                                  |            |  |  |  |  |  |

| _                                                       | 0xEE4      |  |  |  |  |  |

| Туре                                                    | Read-only  |  |  |  |  |  |

| Reset                                                   |            |  |  |  |  |  |

| ****                                                    | 0×0000000  |  |  |  |  |  |

| Width                                                   | 32         |  |  |  |  |  |

| Bit descriptions                                        |            |  |  |  |  |  |

| The following image shows the register bit assignments. |            |  |  |  |  |  |

RES0\_0

#### Figure 3-8 TPIU\_ITDSYNC

The following table shows the register bit assignments.

#### Table 3-9 TPIU\_ITDSYNC attributes

| Bits   | Reset value | Name    | Туре      | Function                                                                                                                                  |

|--------|-------------|---------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| [31:2] | 0x0         | RES0_0  | Read-only | Reserved bit or field with SBZP behavior                                                                                                  |

| [1]    | 0           | DSYNCED | Read-only | This bit indicates that dsync was observed HIGH since integration mode was enabled. Reading this register clears the bit if dsync is LOW. |

| [0]    | 0           | DSYNC   | Read-only | This bit returns the value of the dsync input.                                                                                            |

# 3.10 TPIU Integration Test Trigger Register, TPIU\_ITTRIGGER

This register indicates the integration status of the trigger input in integration mode.

Reads are allowed even in functional mode, but the register itself is disabled and does not get updated even if the inputs change.

| Attribu          | Attributes                                      |  |  |  |  |  |

|------------------|-------------------------------------------------|--|--|--|--|--|

| Offset           | 0xEE8                                           |  |  |  |  |  |

| Туре             | Read-only                                       |  |  |  |  |  |

| Reset            | 0x0000000                                       |  |  |  |  |  |

| Width            | 32                                              |  |  |  |  |  |

| Bit descriptions |                                                 |  |  |  |  |  |

| The foll         | owing image shows the register bit assignments. |  |  |  |  |  |

<sup>31</sup>

RES0\_0

#### Figure 3-9 TPIU\_ITTRIGGER

The following table shows the register bit assignments.

#### Table 3-10 TPIU\_ITTRIGGER attributes

| Bits   | Reset value | Name      | Туре      | Function                                                                                                                                    |

|--------|-------------|-----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------|

| [31:2] | 0x0         | RES0_0    | Read-only | Reserved bit or field with SBZP behavior                                                                                                    |

| [1]    | 0           | TRIGGERED | Read-only | This bit indicates that trigin was observed HIGH since integration mode was enabled. Reading this register clears the bit if trigin is LOW. |

| [0]    | 0           | TRIGGER   | Read-only | This bit returns the value of the trigin input.                                                                                             |

# 3.11 TPIU Integration Test FIFO Test Data Register 0, TPIU\_ITFTTD0

This register indicates the integration status of the ATB data interfaces.

To read this register the integration data test mode must be enabled with TPIU ITCTRL.Mode=0b10.

Reads are allowed otherwise but the register itself is disabled and doesn't get updated even if the inputs change.

#### Attributes

#### Offset

0xEEC

Туре

Reset

0x00000000

Read-only

#### Width

32

#### **Bit descriptions**

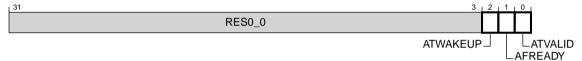

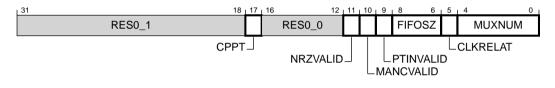

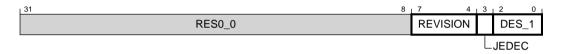

The following image shows the register bit assignments.