# Platform Security Guide for A-Profile

Document number:ARM DEN 0123Release Quality:AlphaIssue Number:0Confidentiality:Non-confidentialDate of Issue:26/06/21

© Copyright Arm Limited 2019-2021. All rights reserved.

### Contents

| Abo | ut this d | ocument                     | v    |

|-----|-----------|-----------------------------|------|

|     | Releas    | se Information              | V    |

|     | Platfo    | rm Security Guide           | vi   |

|     | Confic    | lential Proprietary Notice  | vi   |

|     | Refer     | ences                       | viii |

|     | Terms     | and abbreviations           | viii |

|     | Poten     | tial for change             | ix   |

|     | Conve     | entions                     | ix   |

|     | Status    | and anticipated changes     | х    |

|     | Feedb     | back                        | х    |

| 1   |           | Introduction                | 11   |

|     | 1.1       | How to read this document   | 11   |

| 2   |           | Lifecycle                   | 13   |

|     | 2.1       | Fuses                       | 14   |

|     |           | 2.1.1 Fuse locking          | 15   |

|     |           | 2.1.2 Confidential fuses    | 15   |

|     |           | 2.1.3 Public fuses          | 16   |

|     | 2.2       | Authorization               | 16   |

| 3   |           | Boot ROM and reset          | 18   |

|     | 3.1       | Secure boot keys            | 18   |

|     | 3.2       | Warm boot                   | 19   |

|     | 3.3       | Boot parameters             | 19   |

|     | 3.4       | Boot robustness             | 20   |

|     | 3.5       | Temporal isolation          | 20   |

|     | 3.6       | Reset                       | 22   |

| 4   |           | Clock and power             | 23   |

|     | 4.1       | Power management operations | 23   |

|     | 4.2       | Glitch resistance           | 23   |

|     |           |                             |      |

| 4.3 | Suspend or hibernate                                                                                                                                                                             | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Memory system                                                                                                                                                                                    | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | 5.1.1 TrustZone technology overview                                                                                                                                                              | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.2 | Physical memory mapping                                                                                                                                                                          | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.3 | Transaction routing and cache control                                                                                                                                                            | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.4 | Instruction fetches                                                                                                                                                                              | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | Processing elements                                                                                                                                                                              | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.1 | Isolation of execution contexts                                                                                                                                                                  | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.2 | Non-executable memory                                                                                                                                                                            | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.3 | Speculation control                                                                                                                                                                              | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.4 | Control flow integrity                                                                                                                                                                           | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.5 | Memory safety                                                                                                                                                                                    | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | Interrupts                                                                                                                                                                                       | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | Debug                                                                                                                                                                                            | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 8.1 | Debug ports                                                                                                                                                                                      | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 8.2 | Authentication methods                                                                                                                                                                           | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | 8.2.1 Secret-based authentication                                                                                                                                                                | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | 8.2.2 PKI-based authentication                                                                                                                                                                   | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 8.3 | Interoperable authentication                                                                                                                                                                     | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 8.4 | Processor signals and control registers                                                                                                                                                          | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 8.5 | Other signals                                                                                                                                                                                    | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 8.6 | Unlock operations                                                                                                                                                                                | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | Peripherals and subsystems                                                                                                                                                                       | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 9.1 | Inter-world DMA protection                                                                                                                                                                       | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 9.2 | Intra-world DMA protection                                                                                                                                                                       | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0.2 | External security subsystem pairing                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9.3 | External security subsystem pairing                                                                                                                                                              | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 9.5 | Platform identity                                                                                                                                                                                | 49<br><b>51</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | <ul> <li>5.3</li> <li>5.4</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> <li>8.6</li> <li>9.1</li> </ul> | 5.1.1       TrustZone technology overview         5.2       Physical memory mapping         5.3       Transaction routing and cache control         5.4       Instruction fetches         Processing elements         6.1       Isolation of execution contexts         6.2       Non-executable memory         6.3       Speculation control         6.4       Control flow integrity         6.5       Memory safety         Interrupts         Bebug         8.1       Debug ports         8.2       Authentication methods         8.2.1       Secret-based authentication         8.2.2       PKI-based authentication         8.3       Interoperable authentication         8.4       Processor signals and control registers         8.5       Other signals         8.6       Unlock operations         Peripherals and subsystems         9.1       Inter-world DMA protection |

| 12 |      | Timers                  | 54 |

|----|------|-------------------------|----|

| 13 |      | Cryptography            | 55 |

|    | 13.1 | Algorithms              | 55 |

|    | 13.2 | Side channel resilience | 55 |

|    | 13.3 | Key operations          | 56 |

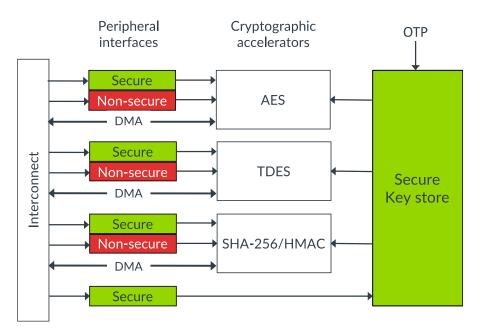

|    | 13.4 | Hardware acceleration   | 56 |

|    | 13.5 | Hardware key stores     | 56 |

| 14 |      | Secure storage          | 58 |

|    | 14.1 | Confidentiality         | 58 |

|    | 14.2 | Integrity               | 59 |

|    | 14.3 | Freshness               | 59 |

| 15 |      | Main memory             | 61 |

|    | 15.1 | Isolation               | 61 |

|    | 15.2 | Confidentiality         | 62 |

|    | 15.3 | Integrity               | 63 |

|    | 15.4 | Freshness               | 63 |

# About this document

This document is one of a set of resources provided by Arm that can help organizations develop products that meet the security requirements of PSA Certified on Arm-based platforms. The PSA Certified scheme provides a framework and methodology that helps silicon manufacturers, system software providers and OEMs to develop more secure products. Arm resources that support PSA Certified range from threat models, standard architectures that simplify development and increase portability, and open-source partnerships that provide ready-to-use software. You can read more about PSA Certified find more Arm resources here:

https://www.psacertified.org/ developer.arm.com/platform-security-resources

This Platform Security Guide for A-profile provides guidance on building a secure platform using Arm technology.

### **Release Information**

The change history table lists the changes that have been made to this document.

| Date      | Version | Confidentiality  | Change               |

|-----------|---------|------------------|----------------------|

| June 2021 | Alpha 0 | Non-confidential | First alpha version. |

# **Platform Security Guide**

Copyright ©2018-2021 Arm Limited or its affiliates. All rights reserved. The copyright statement reflects the fact that some draft issues of this document have been released, to a limited circulation.

### **Confidential Proprietary Notice**

This Licence is a legal agreement between you and Arm Limited ("**Arm**") for the use of Arm's intellectual property (including, without limitation, any copyright) embodied in the document accompanying this Licence ("**Document**"). Arm licenses its intellectual property in the Document to you on condition that you agree to the terms of this Licence. By using or copying the Document you indicate that you agree to be bound by the terms of this Licence.

"**Subsidiary**" means any company the majority of whose voting shares is now or hereafter owner or controlled, directly or indirectly, by you. A company shall be a Subsidiary only for the period during which such control exists.

This Document is **NON-CONFIDENTIAL** and any use by you and your Subsidiaries ("Licensee") is subject to the terms of this Licence between you and Arm.

Subject to the terms and conditions of this Licence, Arm hereby grants to Licensee under the intellectual property in the Document owned or controlled by Arm, a non-exclusive, non-transferable, non-sub-licensable, royalty-free, worldwide licence to:

- (i) use and copy the Document for the purpose of designing and having designed products that comply with the Document;

- (ii) manufacture and have manufactured products which have been created under the license granted in (i) above; and

- (iii) sell, supply and distribute products which have been created under the license granted in (i) above.

### Licensee hereby agrees that the licences granted above shall not extend to any portion or function of a product that is not itself compliant with part of the Document.

Except as expressly licensed above, Licensee acquires no right, title or interest in any Arm technology or any intellectual property embodied therein.

THE DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. Arm may make changes to the Document at any time and without notice. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

NOTWITHSTANING ANYTHING TO THE CONTRARY CONTAINED IN THIS LICENCE, TO THE FULLEST EXTENT PETMITTED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, IN CONTRACT, TORT OR OTHERWISE, IN CONNECTION WITH THE SUBJECT MATTER OF THIS LICENCE (INCLUDING WITHOUT LIMITATION) (I) LICENSEE'S USE OF THE DOCUMENT; AND (II) THE IMPLEMENTATION OF THE DOCUMENT IN ANY PRODUCT CREATED BY LICENSEE UNDER THIS LICENCE). THE EXISTENCE OF MORE THAN ONE CLAIM OR SUIT WILL NOT ENLARGE OR EXTEND THE LIMIT. LICENSEE RELEASES ARM FROM ALL OBLIGATIONS, LIABILITY, CLAIMS OR DEMANDS IN EXCESS OF THIS LIMITATION.

This Licence shall remain in force until terminated by Licensee or by Arm. Without prejudice to any of its other rights, if Licensee is in breach of any of the terms and conditions of this Licence then Arm may terminate this Licence immediately upon giving written notice to Licensee. Licensee may terminate this Licence at any time. Upon termination of this Licence by Licensee or by Arm, Licensee shall stop using the Document and destroy all copies of the Document in its possession. Upon termination of this Licence, all terms shall survive except for the licence grants.

Any breach of this Licence by a Subsidiary shall entitle Arm to terminate this Licence as if you were the party in breach. Any termination of this Licence shall be effective in respect of all Subsidiaries. Any rights granted to any Subsidiary hereunder shall automatically terminate upon such Subsidiary ceasing to be a Subsidiary.

The Document consists solely of commercial items. Licensee shall be responsible for ensuring that any use, duplication or disclosure of the Document complies fully with any relevant export laws and regulations to assure that the Document or any portion thereof is not exported, directly or indirectly, in violation of such export laws.

This Licence may be translated into other languages for convenience, and Licensee agrees that if there is any conflict between the English version of this Licence and any translation, the terms of the English version of this Licence shall prevail.

The Arm corporate logo and words marked with ® or <sup>™</sup> are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. No licence, express, implied or otherwise, is granted to Licensee under this Licence, to use the Arm trade marks in connection with the Document or any products based thereon. Visit Arm's website at https://www.arm.com/company/policies/trademarks for more information about Arm's trademarks.

The validity, construction and performance of this Licence shall be governed by English Law. Copyright © [2021] Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

Arm document reference: LES-PRE-21585 version 4.0

# References

This document refers to the following Arm documents.

| Ref | Document Number | Title                                    |

|-----|-----------------|------------------------------------------|

| [1] | DEN 0112        | Platform Threat Model and Security Goals |

| [2] | DEN 0128        | Platform Security Model                  |

| [3] | DEN 0106        | Platform Security Requirements           |

| [4] | DEN 0072        | Platform Security Boot Guide             |

### Terms and abbreviations

This document uses the following terms and abbreviations.

| Term               | Meaning                                                                                                            |

|--------------------|--------------------------------------------------------------------------------------------------------------------|

| Completer          | A component that responds to requests made by a Requester.                                                         |

| CoreSight          | Debug technology from Arm                                                                                          |

| Cryptographic hash | A one-way function which maps data of arbitrary size to a bit string of fixed size.                                |

| DPM                | Debug Protection Mechanism                                                                                         |

| Glue logic         | Custom circuitry used to interface to off-the-shelf IP blocks.                                                     |

| НИК                | Hardware Unique Key                                                                                                |

| IP                 | A reusable unit of logic, cell, or integrated circuit layout design that is the Intellectual Property of a vendor. |

| MAC                | Message Authentication Code                                                                                        |

| MMU                | Memory Management Unit within a PE                                                                                 |

| MTP                | Multi-time programmable                                                                                            |

| NSAID              | Non-secure Access Identifier                                                                                       |

| NVM                | Non-volatile memory                                                                                                |

| OTP                | One-time programmable                                                                                              |

| PE                 | Processing Element                                                                                                 |

| Requester          | A component capable making a request to a Completer.                                                               |

| ROTPK              | Root of Trust Public Key; also known as a Boot Validation Key.                                                     |

| Term      | Meaning                                                                                                  |

|-----------|----------------------------------------------------------------------------------------------------------|

| SMMU      | System Memory Management Unit used to control access to memory by peripherals with Requester capability. |

| SoC       | System on Chip                                                                                           |

| TLB       | Translation Lookaside Buffer                                                                             |

| TRTC      | Trusted Real Time Clock                                                                                  |

| TrustZone | Security technology from Arm                                                                             |

### Potential for change

The contents of this specification are subject to change.

### Conventions

#### The typographical conventions are:

italic

Introduces special terminology, and denotes citations.

#### bold

Denotes signal names, and is used for terms in descriptive lists, where appropriate.

monospace

Used for assembler syntax descriptions, pseudocode, and source code examples.

Also used in the main text for instruction mnemonics and for references to other items appearing in assembler syntax descriptions, pseudocode, and source code examples.

#### SMALL CAPITALS

Used for some common terms like IMPLEMENTATION DEFINED.

Also used for a few terms that have specific technical meanings, and are included in the Glossary.

#### Red text

Indicates an open issue.

#### Blue text

Indicates a link, which can be:

- A cross-reference to another location within the document.

- A URL, for example http://infocenter.arm.com.

Numbers are normally written in decimal. Binary numbers are preceded by 0b, and hexadecimal numbers by 0x.

In both cases, the prefix and the associated value are written in a monospace font, for example **0xFFFF0000**. To improve readability, long numbers can be written with an underscore separator between every four characters, for example **0xFFFF\_0000\_0000\_0000**. Ignore any underscores when interpreting the value of a number.

### Status and anticipated changes

First draft, major changes, and revisions to be expected.

Requirement identifiers will be introduced in a later version of this document.

### Feedback

Arm welcomes feedback on its documentation. If you have comments on the content of this book, send an email to errata@arm.com. Give:

- The title (Platform Security Guide for A-Profile)

- The number and issue (ARM DEN 0123 1.0 Alpha 0)

- The page numbers to which your comments apply

- The rule identifiers to which your comments apply, if applicable

- A concise explanation of your comments

Arm also welcomes general suggestions for additions and improvements.

# 1 Introduction

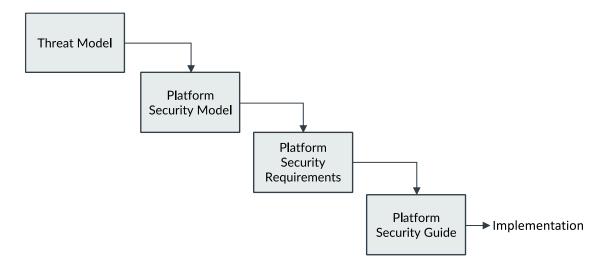

This Platform Security Guide for A-profile forms part of the process for secure by design systems, as illustrated in Figure 1. The Platform Security Model (PSM) describes the essential goals and defines the terminology in a way that is agnostic of any implementation. PSM is motivated by the generic Threat Model for compute centric devices. The Platform Security Requirements (PSR) provides requirements to guide a system designer which are agnostic of any specific implementation.

This document, Platform Security Guide for A-profile, contains system recommendations that meet the security requirements described in PSR. It covers the use of the A-profile system architecture and the Armv8-A instruction set, and various trade-offs between functionality, cost, complexity, and time to market. The rationale and threat model for each requirement are described in PSR and are not described here.

These recommendations are not required for any compliance program. However, these recommendations may be useful in informing the design choices that are made by different silicon vendors for various market requirements.

Figure 1: Document Relationship

### 1.1 How to read this document

Each section summarizes the security requirements from Platform Security Requirements for a particular topic, and then describes the Arm recommendations on how to meet those requirements. Other methods not mentioned in this document might also meet the requirements. Arm welcomes such feedback, see Feedback on page x.

In this version of Platform Security Guide, the Platform Security Requirements are not yet numbered. The requirements will be numbered in a future update to this document.

# 2 Lifecycle

The PSR requires a lifecycle control mechanism for all security functionalities. The lifecycle contains a number of irreversible states and must be captured in some on-chip non-volatile storage. Table 1 lists the requirements.

### Table 1: Lifecycle requirements

| PSR requirement | Description                                                                                                 |  |

|-----------------|-------------------------------------------------------------------------------------------------------------|--|

|                 | The security lifecycle must have a designated initial state.                                                |  |

|                 | The security lifecycle must have a designated secured state which enforces the security requirements.       |  |

|                 | The security lifecycle must have a designated terminal state from which no further transitions are allowed. |  |

|                 | A transition into the terminal state must put secrets and private cryptographic keys beyond use.            |  |

The number of lifecycle states depends on the supply chain of the SoC. For example, there may be several provisioning stages before reaching a designated secure state. It is typical for at least the following states to be available:

- Chip manufacturing state

- Device manufacturing state

- Secured and operational state

- Debug state

- Return-to-manufacturer, or decommissioned, state

Additional lifecycle states might be added that are specific to a market, application, or supply chain. Examples include more specific return-to-manufacturer states or diagnostic states. These lifecycle states are often orthogonal or complementary to the security lifecycle states that are described in this document.

On-chip non-volatile storage can use a variety of technologies, for example floating gate memories or oxide-breakdown anti-fuse cells. These technologies vary with respect to certain properties, including whether they are one-time-programmable (OTP) or many-time-programmable (MTP). Not all non-volatile storage technologies are available in all semiconductor processes. Where needed, off-chip non-volatile memory can be used to augment the available on-chip non-volatile storage.

Non-volatile storage technologies generally require error correction mechanisms to ensure the correct storage of data over the lifespan of the device. Because anyone with physical access can tamper with

off-chip non-volatile memory, the product threat model must indicate whether this threat must be mitigated. For mitigations, see Section 14 Secure storage.

The lifecycle state may also need to be available for attestation purposes. This implies a certain availability of the lifecycle information.

### 2.1 Fuses

Following the industry norm, this document uses the term fuse to refer to on-chip OTP non-volatile storage. Fuses can be implemented using anti-fuses, which are inherently one-time-programmable, or an MTP technology with controlling logic to make it one-time-programmable.

A fuse can transition in one direction only, from its un-programmed state to its programmed state. The reverse operation shall be prevented. The following guidance is provided:

- A fuse shall be programmed only once. This is because multiple programming operations might degrade the programmed cell and introduce a fault, for example, the fuse appears as unprogrammed. Hardware mechanisms for OTP may be available to enforce programming restrictions that prevent operations that could lead to failure.

- All fuse values shall be stable before any parts of the SoC that depend on the value are released from reset.

- Fuses that configure the security features of the device shall be configured so that the programmed state of the fuse enables the feature. The programming of a security configuration fuse will always increase security within the SoC.

Lifetime guarantee mechanisms to correct for in-field failures shall not indicate which fuses have had errors detected or corrected, only that an error has been detected or corrected. This indicator must only be available after all fuses have been checked.

The full error information will be available to the lifetime guarantee mechanism. The security of the mechanism implementation must be considered. Arm recommends implementing the mechanism in hardware, but this might not always be practical.

Fuses can be programmed in one of two known ways:

- Bitwise fuses can be programmed one logical fuse bit at a time.

- Bulk fuses store multi-bit values that must be programmed at the same time and are treated as an atomic unit.

Both types of fuse need to comply with the following properties:

- Depending on system requirements it must be possible to lock any bitwise or bulk fuse in its current state, regardless of whether it is programmed or un-programmed.

- The locking mechanism for a lockable fuse can be shared with other lockable fuses, depending on the system requirements. For example, there can be one locking mechanism for all fuses that are related to a particular feature, or the set of fuses that are programmed by the silicon vendor.

• Additional fuses that are used to implement lifetime guarantee mechanisms shall have the same confidentiality and write lock characteristics as the logical fuse itself.

Assets stored in fuses have a variety of characteristics that determine the way that the fuses are accessed. These assets are classified as confidential or public fuses.

### 2.1.1 Fuse locking

Some fuses are programmed and locked in the factory, either by the Silicon Vendor or OEM. Other fuses may be programmed at a later point in time, depending on customer requirements.

To ensure that fuses safely retain their value, one of the following hardware approaches is recommended:

- Prevent re-writing of a locked value. A mechanism that prevents the programming of a fuse bit or group of fuse bits can be implemented by reserving an additional fuse bit to act as a lock bit. This is often called a write-lock.

- Writing the value is followed by its lock bit being set. Glue logic ensures that no further programming is possible:

- Writing zero, which corresponds to the un-programmed fuse state, causes no value to be written, only the lock bit to be set.

- Use tamper detection to detect that the value has been modified. A tamper detection mechanism can be implemented by storing a code in additional fuses. The code must be sufficient to detect any modification to the value. The behavior upon detection will be system specific, but in general should result in a higher security state.

- Writing the value is followed by storing the detection code.

- When the value is read by the system, a mechanism must recalculate the code from the value and compare it with the stored code. If the codes do not match, the value shall not be returned to the system.

- Prevent reading of a fuse by un-authorized system specific components. This is often called a read-lock. See section 2.1.2.

### 2.1.2 Confidential fuses

Confidential fuses must only be read by the intended recipients. Examples of intended recipients include a particular hardware module or software process.

A confidential fuse whose recipient is only a hardware IP should not be readable by any software process. Typically, this type of confidential fuse is connected to the IP using a hardware data path that is not visible to software or any other hardware IP. It may be necessary to read back a bitwise or bulk fuse as part of the programming process. In such cases, a read-lock fuse can be deployed to disable such a read path once correct programming has been confirmed.

A confidential fuse whose recipient is a software process should be readable by that process. This type of confidential fuse may need to be readable by higher privileged software. This is necessary where that higher privilege software implements the process access controls. For example, a kernel level driver could provide fuse access control for user space processes. The confidentiality relies on the kernel level driver only passing fuse values to the correct user space process.

A confidential fuse whose recipient is a Trusted world software process shall be protected by a hardware filtering mechanism that can only be configured by Trusted software, for example an MPU, an MMU, or an TrustZone NS-bit filter.

### 2.1.3 Public fuses

Public fuses can be accessed by any piece of software or hardware. The SoC designer must consider the implications of making a fuse public on a case-by-case basis.

# 2.2 Authorization

A transition to a final lifecycle state, like Return Merchandise Authorization (RMA), must be part of a process involving the owner of the security lifecycle. Authorization is required to prevent unintended loss of service or loss of important data. Table 2 lists the requirements.

### Table 2: Terminal state authorization requirement

| PSR requirement | Description                                                                                     |

|-----------------|-------------------------------------------------------------------------------------------------|

|                 | A transition into the terminal state must be authorized by the owner of the security lifecycle. |

The owner of the security lifecycle can vary depending on the type of product that is being made. For example, an OEM may choose to restrict access to certain functionality, like full debug, until the terminal state is reached. Another example is that an OEM might allow secure boot to be disabled only after all device secrets have been put beyond use.

The method of authorization can vary according to the operational processes of the product. For example:

- If the product is registered within an ecosystem, then the ecosystem may need to add the product credentials to a deny list before permitting the transition. This ensures that any credentials leaked from the device can no longer be used to access important services.

- The product might seek approval from the owner by means of a password, pin code, or other authentication mechanism. This ensures that an unauthorized user cannot revoke secrets that are used to secure data. Also, the owner can be made aware of any data loss, like secrets, that might occur after the transition has finished. We recommend the use of multiple factors of authentication. For example, physical presence can be used as a secondary factor to counter

remote attacks. An example of physical presence is a physical button, key combination, or other form of physical user input.

# 3 Boot ROM and reset

# 3.1 Secure boot keys

The requirements listed in Table 3 indicate that the Boot ROM must be able to securely boot the next stage of the boot process. This implies that the Boot ROM has a cryptographic key to authenticate the first firmware component.

#### Table 3: Secure boot keys requirements

| PSR requirement | Description                                                                                                                      |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------|

|                 | The SoC must have an on-chip Boot ROM with the initial code that is needed to perform a secure boot.                             |

|                 | The SoC must either contain an on-chip public key for secure boot, or the information that is needed to securely identify it.    |

|                 | If a cryptographic hash of the ROTPK is stored in on chip non-volatile memory, rather than the key itself, it must be immutable. |

On-chip OTP NVM memory can be used to store a cryptographic hash of the key that is used to authenticate the firmware. A hash is typically smaller in size than the full key, especially in the case of the RSA algorithm. The Boot ROM uses the stored hash to check the integrity of the full key, which may be stored on external flash. Use of a hash is the most economical use of OTP NVM. The use of a hash may be more flexible with supply chains because the key hash can be programmed at a later stage of manufacturing if there is not enough OTP to program the key.

For information about appropriate cryptographic algorithms, see section 13 Cryptography.

The secure boot flow is normally divided into two phases:

- The Trusted world secure boot flow that executes Trusted world components.

- The Non-Trusted world secure boot flow that executes normal world component, for example UEFI or U-Boot.

DEN 0072 Platform Security Boot Guide provides the security requirements for the boot process. The open-source Trusted Firmware-A project demonstrates an implementation of a boot flow that meets the requirements of this document.

Boot code is highly critical to overall system security. Some markets will want to encrypt the firmware images to make it more difficult for attackers to identify vulnerabilities within the boot code. This encryption would require an extra on-chip key for decryption, typically held in fuses or equivalent on-

chip NVM. To simplify firmware provisioning, the same decryption key is often used across a class of devices.

# 3.2 Warm boot

When a system boots from a powerless state, it is known as a cold boot. Some systems support a type of reset where the system boots from a powered state. This type of boot is called a warm boot. Because a warm reset only resets a subset of system components, it allows the boot process to skip certain reinitialization routines and potentially reuse RAM contents from the previous boot session. This allows for fast reboots but also raises security concerns. Table 4 lists the requirements. Recommendations will be included in a future update to this document.

### Table 4: Warm boot requirements

| PSR requirement | Description                                                                                                                                                                                                             |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | If the system supports warm boot, a flag or register that survives warm boot must exist to distinguish between warm boots and cold boots.                                                                               |

|                 | Where a flag or register that survives warm boot exists to distinguish between cold and warm boot, the flag or register must be programmable only by the Trusted world and must be reset during a cold and a warm boot. |

|                 | Where a flag or register is used to distinguish between cold and warm boots,<br>the default should be for cold boot, and should use a value that any<br>unauthorized perturbation will result in a cold boot.           |

|                 | If a boot status register is implemented, it must be accessible only by the Trusted world.                                                                                                                              |

### 3.3 Boot parameters

Table 5 lists the boot parameter requirements. Recommendations will be included in a future update to this document.

#### Table 5: Boot parameter requirements

| PSR requirement | Description                                                                                                      |

|-----------------|------------------------------------------------------------------------------------------------------------------|

|                 | The Boot ROM must be aware of the current security lifecycle state.                                              |

|                 | It must not be possible to bypass secure boot unless a Trusted Debug mode permits this.                          |

|                 | Any Boot ROM configuration data outside of on-chip OTP memory must be authenticated using an on-chip public key. |

## 3.4 Boot robustness

It is desirable to minimize the amount of code that is embedded in the Boot ROM. This is because of the possibility of code issues or vulnerabilities. For example, a cryptographic library or USB stack could contain a non-trivial amount of code. Because the Boot ROM is the first stage of a secure boot process, any exploitable vulnerability could be used to either bypass secure boot, or to create system instability.

A simplified Boot ROM implementation should contain only the necessary initialization code, and a hash algorithm that is used to verify a loadable code module with a stored cryptographic hash in OTP NVM. The loadable code can include more complicated code, like asymmetric cryptographic algorithms and additional device drivers. This allows a greater portion of Boot ROM code to be updated without a metal mask change and permits later delivery of that code during SoC development.

When the Boot ROM is invoked, it typically sets up an execution stack and may temporarily use other parts of memory for large objects.

To prevent DMA transactions changing the execution state, Arm recommends disabling DMA for all requesters on reset. This is a simple way to ensure compliance with Table 6. However, this might be too restrictive for some system designs. Alternatively, the SoC designer can use a memory access filter that prevents unauthorized writes to the Boot ROM execution environment and other relevant places.

**Table 6: Boot robustness requirements**

| PSR requirement | Description                                                               |  |

|-----------------|---------------------------------------------------------------------------|--|

|                 | The Boot ROM execution state must be protected from DMA reads and writes. |  |

# 3.5 Temporal isolation

The Boot ROM, or an early boot stage component, might have immutable secrets that should not be accessible to runtime software. If the secrets are left accessible, a runtime attack might leak them. Because these secrets are not needed by runtime software, they should be hidden by the boot software using a hardware mechanism. An example of a hardware mechanism would be an SoC register that hides portions of the address map once it is written to. That register should ideally be write-once, or writeable only by trusted software.

Examples of such immutable secrets may include:

- Boot ROM code

- Hardware unique key

- Root parameters, like SoC or IP parameters

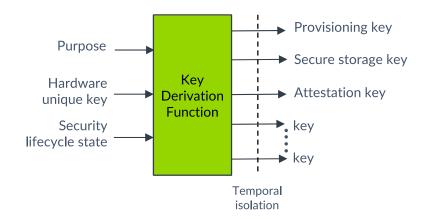

A typical usage scenario for temporal isolation is to hide a single hardware unique secret. Key Derivation Functions (KDF) can then be used to derive multiple hardware unique keys. Each derived key can be given to a specific runtime component and used only for a specific purpose. With only the output of a

good key derivation function, it is technically infeasible to determine the secret used to derive a key. Arm recommends reading NIST 800-56C for examples of good KDF algorithms and usage.

An example of the various keys that can be derived is shown in Figure 2, where the Boot ROM or equivalent passes the following into a key derivation function:

- The hardware unique key

- The current security lifecycle state

- The purpose of the derived key

#### Figure 2 Key derivation with temporal isolation

The Boot ROM uses the KDF to generate all the required keys. The derived keys can be used for specific purposes, like provisioning, secure storage, attestation, and potentially other types of keys. Before the derived keys are given to their respective components, the Boot ROM activates the temporal isolation to hide the hardware unique key from access. Typically, the temporal isolation is achieved by implementing a sticky bit in a hardware register, which when set, causes the location of the hardware unique key to be inaccessible until the next system reset.

Because the security lifecycle state can be included as a parameter in the derivation process, a change in the security lifecycle state will change the derived keys. There are a few useful scenarios for this property:

- A valid provisioning key can only be derived during a factory provisioning state.

- A valid attestation key can only be derived when the system is not in a debug state.

- A valid secure storage key can only be derived when the system is not in a debug or decommissioned state.

More keys and detailed policies can be created using the same mechanism.

# 3.6 Reset

During normal operation, all external interfaces to the SoC should be disabled. They may be selectively enabled by the Boot ROM or secure boot firmware when they are needed. Table 7 lists the requirements.

#### **Table 7: External Interface reset requirements**

| PSR requirement                                          | Description |  |

|----------------------------------------------------------|-------------|--|

| External interfaces must be disabled on each cold reset. |             |  |

If the SoC implements multiple processing elements (PEs), the designated boot processor core is called the primary PE. After the de-assertion of a reset, the primary PE usually executes first, while the secondary PEs are held in reset, or a safe platform-specific state, until the primary PE initializes and boots them. A more complex SoC might have a dedicated security co-processor. This co-processor would control the reset logic holding PEs in a halted or safe state, load and validate firmware, and then allow the Primary PE to execute. Table 8 lists the requirements.

#### **Table 8: Secondary PE reset requirements**

| PSR requirement | Description                                                                       |  |

|-----------------|-----------------------------------------------------------------------------------|--|

|                 | All secondary PEs must remain inactive until permitted to boot by the primary PE. |  |

# 4 Clock and power

This section lists the clock and power related security requirements and some design options that can meet the requirements.

## 4.1 Power management operations

Power management is a sensitive operation that can affect the execution of the Trusted world and its operations. Table 9 lists the requirements. Therefore, it is important that sensitive power management operations are not handled by the Non-trusted world:

- The basic core management operations, like turning CPUs on or off, is typically implemented in the Trusted world, typically at EL3. The Non-trusted world software communicates with the Trusted world power management code using the Power State Coordination Interface (PSCI) defined by Arm.

- Dynamic Voltage and Frequency Scaling (DVFS) controls is typically implemented by a separate on-chip System Control Processor (SCP). The Non-trusted world software communicates with this processor using the System Control Management Interface (SCMI) defined by Arm.

In both cases, the parameters must be checked by the trusted entity to ensure they remain within safe limits.

Where possible, non-critical or non-sensitive power management code should run in the Non-trusted world in order to minimize the attack surface of the Trusted world and System Control Processor.

#### **Table 9: Power management requirements**

| PSR requirement | Description                                                                                                                                                                                                                |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                 | The power control mechanism must integrate a Trusted management function to control clocks and power. It must not be possible to directly access reset, clock, and power management mechanisms from the Non-Trusted world. |  |

### 4.2 Glitch resistance

A non-invasive physical attacker can perturbate the clock or power lines to cause malfunction. These injected faults can sometimes be exploited by an attacker to elevate privileges or leak secrets. The required training and equipment cost to perform this type of attack is becoming increasingly affordable to adversaries. The need to protect against these attacks will depend upon the Protection Profile of any applicable certification scheme or industry segment. To counteract these types of attack it is necessary to employ counter measures, for example:

- Ensuring that Trusted software always fails in a secure and safe way when a glitch occurs. This may be impractical depending on the amount of software that needs protection. A more comprehensive description of the topic is described the paper Secure Application Programming in the presence of Side Channel Attacks, published by Riscure.

- Including a monitoring unit within the SoC that detects if the clock, temperature or voltage vary beyond safe limits.

Arm recommends a mixture of techniques to obtain good coverage against these attacks.

# 4.3 Suspend or hibernate

A system may need to support hibernate or suspend operations. These operations put the SoC into a very low power state, while the main memory may be copied to some non-volatile storage device like flash or a hard disc drive or the DRAM may be placed in a self-refresh mode. Table 10 lists the requirements. Recommendations on suspend-to-DRAM scenarios will be included in a future update to this document.

| PSR requirement | Description                                                                                                                                                                                    |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                 | If suspend to RAM is implemented and the main die is powered down so that<br>any DRAM protection keys need to be saved and restored, these operations<br>must be handled by the Trusted world. |  |

|                 | The keys must be stored in either on-chip Trusted storage or wrapped using a key derived from an on-chip hardware unique key.                                                                  |  |

|                 | Security critical suspend state information that is stored off-chip must be encrypted and authenticated using an on-chip key.                                                                  |  |

#### Table 10: Suspend or hibernate requirements

# 5 Memory system

The Security Model [1] requires as a minimum hardware-based isolation between the security sensitive processing and the remainder of the software. This is reflected in Table 11. For isolation of memory, we describe Arm TrustZone technology in this section.

#### **Table 11: Memory isolation requirements**

| PSR requirement | Description                                                                                                                 |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------|--|

|                 | The SoC must provide a hardware-based mechanism for isolating the memories of the Trusted world from the Non-trusted world. |  |

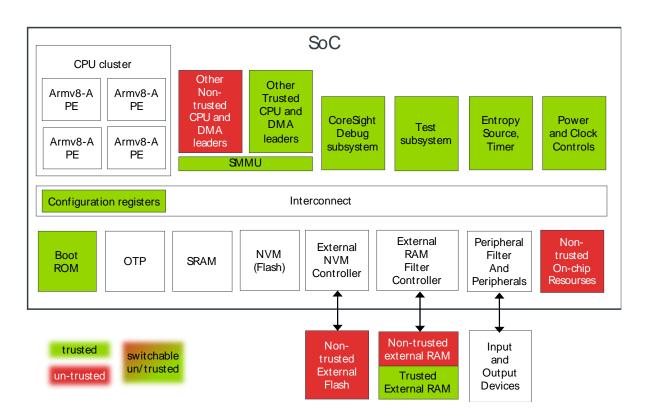

### 5.1.1 TrustZone technology overview

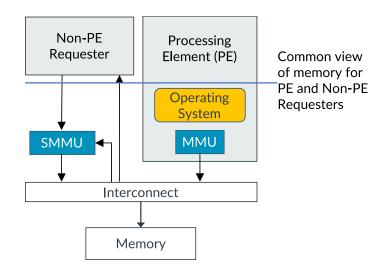

TrustZone technology lies at the heart of an Arm processor element. While it is executing code, the processor element can operate in one of two possible states that correspond to the Trusted and Non-trusted worlds. These are known as the Secure and Non-secure states, respectively. Context switches between Security states can only be made using dedicated instructions and code to ensure that strict isolation is maintained. The context switch mechanism enforces fixed code entry points and ensures that code running in the Non-secure state cannot access registers that belong to the Secure state. Conceptually, the Secure and Non-secure states can be regarded as two virtual processor elements.

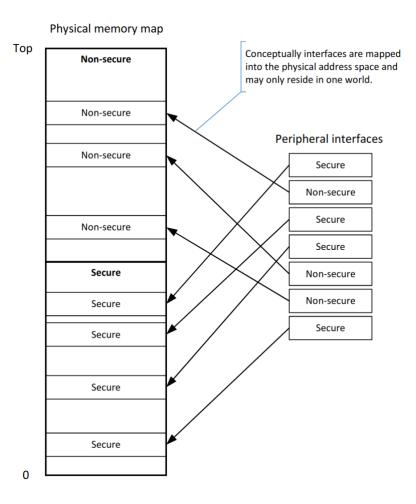

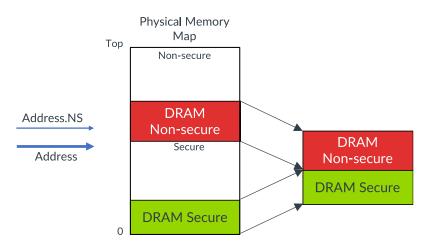

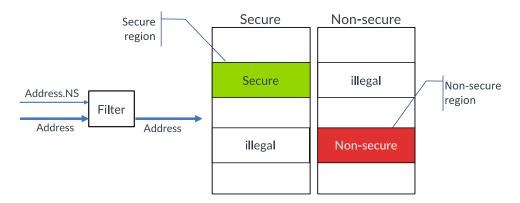

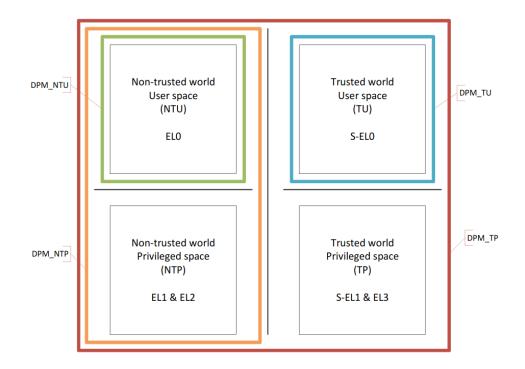

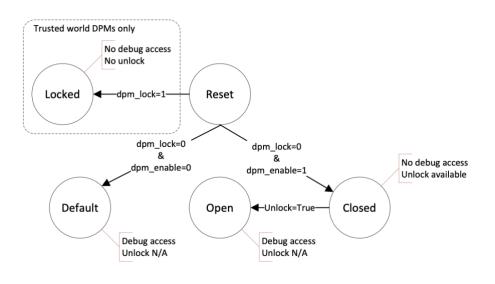

When the Arm processor performs a memory access, the MMU translation provides an extra bit that indicates the security state that is associated with the transaction. When this bit is set, it indicates a Non-secure (NS) transaction. The mechanism is tightly coupled to the cache and consequently an NS bit is stored in every cache line. The NS bit can be considered as an extra address bit that is used to access the Trusted and Non-trusted worlds as completely independent address spaces.