# Arm<sup>®</sup> Ethos<sup>™</sup>-U65 NPU

Revision: r0p0

**Technical reference manual**

#### Arm<sup>®</sup> Ethos™-U65 NPU

#### **Technical reference manual**

Copyright © 2020, 2021 Arm Limited or its affiliates. All rights reserved.

#### **Release Information**

#### **Document History**

| Issue   | Date             | Confidentiality  | Change                              |

|---------|------------------|------------------|-------------------------------------|

| 0000-01 | 31 March 2020    | Confidential     | First development release for r0p0. |

| 0000-02 | 24 June 2020     | Confidential     | First beta release for r0p0.        |

| 0000-03 | 20 August 2020   | Confidential     | First EAC release for r0p0.         |

| 0000-04 | 19 November 2020 | Non-Confidential | Second EAC release for r0p0.        |

| 0000-05 | 12 May 2021      | Non-Confidential | Third EAC release for r0p0.         |

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or TM are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at <a href="https://www.arm.com/company/policies/trademarks">https://www.arm.com/company/policies/trademarks</a>.

Copyright  $\ensuremath{\mathbb{C}}$  2020, 2021 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

(LES-PRE-20349)

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

#### **Product Status**

The information in this document is Final, that is for a developed product.

#### Web Address

developer.arm.com

#### Progressive terminology commitment

Arm values inclusive communities. Arm recognizes that we and our industry have used terms that can be offensive. Arm strives to lead the industry and create change.

This document includes terms that can be offensive. We will replace these terms in a future issue of this document.

If you find offensive terms in this document, please contact terms@arm.com.

# Contents

# **Arm® Ethos™-U65 NPU Technical reference manual**

|           | Pret  | race                                      |                  |

|-----------|-------|-------------------------------------------|------------------|

|           |       | About this book                           |                  |

|           |       | Feedback                                  | 9                |

| Chapter 1 | Intro | oduction                                  |                  |

|           | 1.1   | Description of the neural processing unit | 1-1              |

|           | 1.2   | Interfaces                                | 1-14             |

|           | 1.3   | Documentation                             | 1-1              |

|           | 1.4   | Design process                            | 1-16             |

|           | 1.5   | Product revisions                         | 1-1              |

| Chapter 2 | Fun   | ctional description                       |                  |

|           | 2.1   | Control and data flow                     | 2-19             |

|           | 2.2   | Security and boot flow                    | 2-2 <sup>-</sup> |

|           | 2.3   | Functional blocks                         | 2-22             |

| Chapter 3 | Prog  | grammers model                            |                  |

|           | 3.1   | Register characteristics                  | 3-29             |

|           | 3.2   | Register page BASE                        | 3-30             |

|           | 3.3   | Register page BASE_POINTERS               | 3-48             |

|           | 3.4   | Register page ID                          | 3-54             |

|           | 3.5   | Register page PMU                         | 3-59             |

|           | 3.6   | Command stream                            | 3-76             |

|           | 3.7   | Weight stream format                      | 3-87             |

|           |       |                                           |                  |

|            | 3.8  | Operators and performance       | 3-97       |

|------------|------|---------------------------------|------------|

|            | 3.9  | Block based operation           | 3-107      |

| Appendix A | Sign | nal descriptions                |            |

|            | A.1  | Clock and reset signals         | Appx-A-113 |

|            | A.2  | Interrupt signals               | Appx-A-114 |

|            | A.3  | Power management signals        | Appx-A-115 |

|            | A.4  | AMBA® 5 AXI master signals      | Appx-A-116 |

|            | A.5  | AMBA® 4 APB slave signals       | Appx-A-122 |

|            | A.6  | DFT and MBIST signals           | Appx-A-123 |

| Appendix B | Gen  | eral neural network concepts    |            |

|            | B.1  | General neural network concepts | Appx-B-125 |

| Appendix C | Boo  | t flow information              |            |

|            | C.1  | Boot flow information           | Appx-C-127 |

| Appendix D | Revi | isions                          |            |

|            | D.1  | Revisions                       | Appx-D-130 |

# **Preface**

This preface introduces the  $Arm^*$   $Ethos^{\mathsf{TM}}$ -U65 NPU Technical reference manual.

It contains the following:

- About this book on page 7.

- Feedback on page 9.

#### About this book

This manual is for the Arm<sup>®</sup> Ethos<sup>™</sup>-U65 neural processing unit.

#### **Product revision status**

The rxpy identifier indicates the revision status of the product described in this book, for example, r1p2, where:

- rx Identifies the major revision of the product, for example, r1.

- py Identifies the minor revision or modification status of the product, for example, p2.

#### Intended audience

This manual is for system designers, system integrators, and verification engineers who are designing a *System-on-Chip* (SoC) device that uses an Arm® Ethos™-U65 NPU.

#### Using this book

This book is organized into the following chapters:

#### **Chapter 1 Introduction**

This chapter introduces the processor.

#### **Chapter 2 Functional description**

This chapter describes the function and structure of the processor.

#### Chapter 3 Programmers model

This chapter describes a register and register map of the NPU.

## Appendix A Signal descriptions

This appendix describes the signals for the processor.

#### Appendix B General neural network concepts

This appendix describes the various concepts Arm uses to describe the NPU.

#### Appendix C Boot flow information

This appendix describes the various boot flows for the NPU.

#### Appendix D Revisions

This appendix describes the technical changes between releases of this book.

#### Glossary

The Arm Glossary is a list of terms used in Arm documentation, together with definitions for those terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

See the Arm® Glossary for more information.

# Typographic conventions

italic

Introduces special terminology, denotes cross-references, and citations.

#### bold

Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.

#### monospace

Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.

#### monospace

Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.

#### monospace italic

Denotes arguments to monospace text where the argument is to be replaced by a specific value.

#### monospace bold

Denotes language keywords when used outside example code.

<and>

Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example:

#### SMALL CAPITALS

Used in body text for a few terms that have specific technical meanings, that are defined in the *Arm*® *Glossary*. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE.

#### **Signals**

The signal conventions are:

#### Signal level

The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

- HIGH for active-HIGH signals.

- LOW for active-LOW signals.

#### Lowercase n

At the start or end of a signal name, n denotes an active-LOW signal.

#### Additional reading

This book contains information that is specific to this product. See the following documents for other relevant information.

#### **Arm publications**

Non-confidential documents:

- AMBA® AXI and ACE Protocol Specification AXI3, AXI4, AXI5, ACE and ACE5 (Arm IHI 0022).

- AMBA® Low Power Interface Specification Arm® Q-Channel and P-Channel Interfaces (IHI 0068).

- Arm<sup>®</sup> Ethos<sup>™</sup>-U65 NPU Technical overview (102024).

- Arm<sup>®</sup> Ethos<sup>™</sup>-U NPU Application development overview (101888).

Confidential documents that are only available to licensees:

- Arm<sup>®</sup> Ethos<sup>™</sup>-U65 NPU Configuration and integration manual (102025).

- Arm<sup>®</sup> Ethos<sup>™</sup>-U NPU Functional model integration guide (101889).

#### Developer resources:

• https://developer.arm.com/solutions/machine-learning-on-arm.

# Other publications

None.

#### **Feedback**

#### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

#### Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- The title *Arm Ethos-U65 NPU Technical reference manual*.

- The number 102023 0000 05 en.

- If applicable, the page number(s) to which your comments refer.

- A concise explanation of your comments.

| Arm also welcomes general suggestions for additions and improvements.                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note                                                                                                                                                          |

| Arm tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader. |

# Chapter 1 **Introduction**

This chapter introduces the processor.

It contains the following sections:

- 1.1 Description of the neural processing unit on page 1-11.

- 1.2 Interfaces on page 1-14.

- 1.3 Documentation on page 1-15.

- 1.4 Design process on page 1-16.

- 1.5 Product revisions on page 1-17.

# 1.1 Description of the neural processing unit

The *Neural Processing Unit* (NPU) improves the inference performance of neural networks. The NPU targets quantized *Convolutional Neural Networks* (CNN) and 8-bit and 16-bit integer *Recurrent Neural Networks* (RNN). The NPU supports 8-bit weights.

Arm delivers the hardware *Register Transfer Level* (RTL) of the NPU with an open-source driver and compiler. A neural network must be compiled offline using the open-source compiler to produce a command stream. The application invokes the driver, which communicates with the NPU to tell it where the command stream is and initiates the network traversal. The command stream describes the steps necessary for the NPU to execute the operators compiled into the command stream autonomously. When complete, the NPU raises an IRQ to the driver.

The driver programs the memory location of the command stream and other payloads into registers in the NPU. The *Central Control* (CC) processes the command stream.

The NPU includes a *Direct Memory Access* (DMA) controller that can read and write to external memory. When the NPU performs inferences, the DMA controller reads the neural network description. This description contains:

- The command stream

- Network weights

- · Bias information

- Scale information

The DMA controller also transfers the *Input Feature Maps* (IFMs) and the *Output Feature Maps* (OFMs) and NPU-private intermediate data that is also held in system memory.

The external interfaces that the NPU implements are:

Two Arm AMBA 5 AXI master interfaces that provide the DMA controller with access to external

memory. Two read/write masters, M0 and M1. This means that the NPU can present two sets of

transactions at the same time. The command, weight, bias, and scale channels can be mapped to

either AXI master.

| either AXI master.                                    |  |

|-------------------------------------------------------|--|

| Note                                                  |  |

| The master interfaces are also AMBA 4 AXI compatible. |  |

• An Arm AMBA 4 APB slave interface with wake up signaling that allows the application processor to program the NPU.

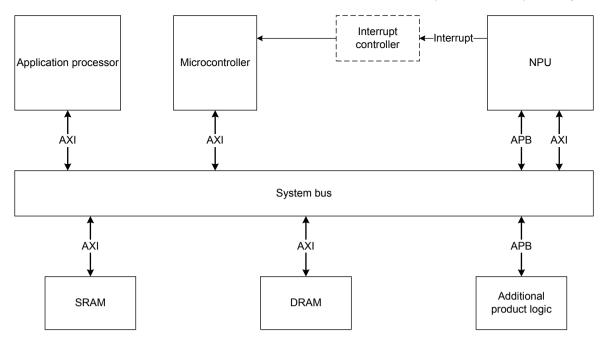

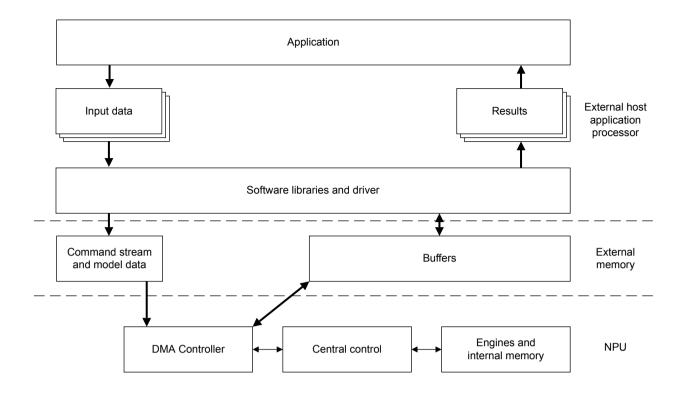

The following figure shows a typical system configuration block diagram for the NPU.

Figure 1-1 Typical system configuration block diagram

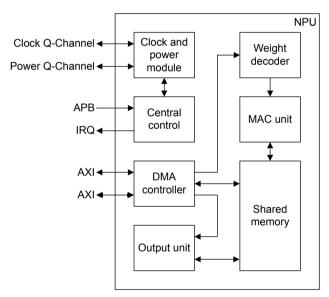

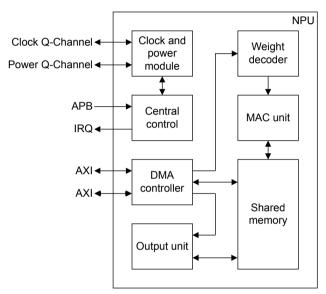

The following figure shows the main components of the NPU.

Figure 1-2 Functional blocks diagram

This section contains the following subsection:

• 1.1.1 Supported application programming interfaces on page 1-12.

# 1.1.1 Supported application programming interfaces

To program, test, and monitor the NPU, Arm deploys the open-source *TensorFlow Lite for Microcontrollers* (TFL $\mu$ ) tool, which runs on an external host application processor. It uses the compiler offline to compile and optimize the neural network graph for the NPU. Its API generates a command stream for the NPU to process.

The compiler decides which parts of a network graph can be optimized and executed on the NPU. The NPU drivers manage the workloads that execute inferences on the NPU.

If the network maps exclusively to the NPU, then the power required by the external host application processor is negligible. If there is a requirement to process layers on the Cortex\*-M core, then more performance is required.

# 1.2 Interfaces

The NPU has several external interfaces.

The external interfaces are:

- Arm AMBA 4 APB slave with wake-up signaling.

- Two Arm AMBA 5 AXI masters:

- A read/write master, M0.

- A read/write master, M1.

- An interrupt.

- Two Q-channels:

- A Q-Channel for clock.

- A Q-Channel for power.

- System configuration signals that determine the security level after boot.

- Clock.

- Reset.

## 1.3 Documentation

Arm Limited publishes documentation that describes the NPU, including this document.

#### **Technical overview**

The Technical overview (TO) describes the functionality of the NPU.

#### Technical reference manual

The *Technical reference manual* (TRM) describes the functionality and the effects of functional options on the behavior of the processor. It is required at all stages of the design flow. Design flow choices can mean that some behavior that the TRM describes is not relevant. If you are programming the processor, obtain additional information from:

- The implementer to determine the build configuration of the implementation.

- The integrator to determine the pin configuration of the device that you are using.

#### **Application development overview**

The Application development overview (ADO) describes the flow of data between an application and the NPU.

#### Configuration and integration manual

The Configuration and integration manual (CIM) describes the configuration and implementation of the NPU.

# Functional model integration guide

The Functional model integration guide (FMIG) describes how to integrate the NPU functional model.

The CIM and FMIG are confidential books only available to licensees.

# 1.4 Design process

The NPU is delivered as synthesizable RTL. Before it can be used in a product, it must go through the design process.

#### **Implementation**

The implementer configures and synthesizes the RTL to produce a hard macrocell.

# Integration

The integrator connects the configured design into an SoC, including a memory system and peripherals.

# **Programming**

The system programmer uses the following to develop the SoC:

- The software to configure and initialize the NPU.

- The application software and the SoC tests.

# 1.5 Product revisions

Successive product revisions have differences in functionality.

r0p0

First release.

# **Chapter 2 Functional description**

This chapter describes the function and structure of the processor.

It contains the following sections:

- 2.1 Control and data flow on page 2-19.

- 2.2 Security and boot flow on page 2-21.

- 2.3 Functional blocks on page 2-22.

## 2.1 Control and data flow

The software stack manages the control and data flows between the application software running on an external host application processor and individual subcomponents of the NPU.

The components of the software stack communicate with each other to handle the control and data flow between the neural network application and the NPU.

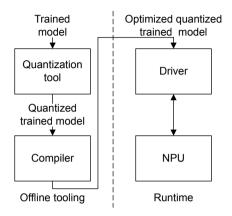

The following figure shows the software stack for the NPU.

Figure 2-1 The software stack of the NPU

The NPU uses offline tools to optimize the code. At runtime, the application processor passes this optimized trained model to the NPU.

The following steps describe the offline tooling flow:

- 1. Pass your trained model through the quantization tool. This tool quantizes weights to 8-bit and activations to 8-bit or 16-bit values.

- 2. Pass the quantized model to the compiler. This tool optimizes the model for this NPU and outputs an optimized model that contains a command stream for the NPU.

The following steps describe the runtime control and data flow:

- 1. The optimized model is placed in system memory, which is accessible by the NPU.

- 2. At runtime, the TFLµ tool reads the model and dispatches the operators.

- 3. The NPU reads the optimized model and runs the command stream that is included in it. The application processor runs any parts that the NPU cannot execute.

- 4. When the inference is complete, the result is placed in the memory location that the driver specifies.

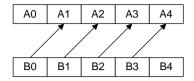

The following figure shows the control and data flow.

Figure 2-2 Control and data flow

This section contains the following subsection:

• 2.1.1 Supported memory formats for feature maps on page 2-20.

#### 2.1.1 Supported memory formats for feature maps

The NPU supports the industry-standard NHWC format of feature-map data.

NHWC is used as an input and output format by the NPU for communication with TensorFlow light.

When the NPU processes multiple layers, it reformats NHWC-formatted feature maps into an internal NHCWB16 format when reading in data. The NPU also performs the reverse transformation on the final output layer.

#### **NHWC format**

The NHWC format has the following properties:

- H (height), W (width), and C (channels) data.

- The size of each element (ElemSize) is 1-byte or 2-bytes.

- Only a single batch is supported (N=1).

- The address of an element y, x, c is (BASE+y\*STRIDE\_Y+x\*STRIDE\_X+c\*ElemSize).

- The values BASE, STRIDE\_Y, and STRIDE\_X must be aligned in element size.

- Only tile 0 can be used, the address of tile 0 is BASE.

#### **NHCWB16 format**

The NHCWB16 format has the following properties:

- A block format consisting of 16 channels per block.

- Only a single batch is supported (N=1).

- The address of an element y, x, c is (BASE+y\*STRIDE\_Y+(c/16)\*STRIDE\_C + (x\*16 + (c %16))\*ElemSize).

- The values BASE, STRIDE\_Y, and STRIDE\_C must be 16-byte aligned.

- Tiles can be used.

# 2.2 Security and boot flow

The NPU can be set to different security and privilege modes during a reset. The host application processor cannot reset the NPU to a higher security level than its current level.

At any reset, all registers and memories in the NPU are cleared to prevent leakage between states.

When a soft reset is requested, the NPU ensures that all AMBA 5 AXI transactions are complete before issuing the reset.

When the NPU is powered up after a hard reset, it reads the **PORPL** signal to set its privilege level:

- LOW indicates user mode.

- · HIGH indicates privileged mode.

When the NPU is powered up after a hard reset, it reads the **PORSL** signal to set its security level:

- LOW indicates Secure mode.

- HIGH indicates Non-secure mode.

When the NPU is accessed, it uses the **PPROT** signal to check if the access is permitted. The NPU security and privilege level that is used on the AXI ports are the **ARPROT/AWPROT** signals. The **ARPROT/AWPROT** signals may be used for memory protection at system-level.

| ART ROT/AVI ROT signals may be used for memory protection at system-level.                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note                                                                                                                                                                                                                  |

| The NPU assumes that the software on the host that has permission to access it is trusted. You must ensure that the system provides suitable protection from memory tampering (for example, by protecting the flash). |

#### 2.3 Functional blocks

The NPU consists of the *Central Control* (CC), a DMA controller, a MAC unit, an Output unit, and the interconnect fabric.

The following are descriptions of the units of the NPU:

- The CC receives tasks from the external host application processor. The CC queues and dispatches units of work to the DMA and engines.

- The DMA controller uses its two Arm AMBA 5 AXI master interfaces to move data between external memory and internal shared memory.

- The MAC unit has various internal units for reading IFMs, performing dot products and accumulations.

The following figure shows the main components of the NPU.

Figure 2-3 Functional blocks diagram

This section contains the following subsections:

- 2.3.1 External interfaces on page 2-22.

- 2.3.2 Central control on page 2-23.

- 2.3.3 DMA controller on page 2-23.

- 2.3.4 Clock and power module on page 2-25.

- 2.3.5 Weight decoder on page 2-26.

- 2.3.6 MAC unit on page 2-26.

- 2.3.7 Output unit on page 2-26.

#### 2.3.1 External interfaces

The NPU uses two AMBA 5 AXI master interfaces, an AMBA 4 APB slave interface with wake-up signaling, an interrupt interface, two Q-Channel interfaces, clock, and reset to enable access to and from external components.

#### Two AMBA 5 AXI master interfaces

These interfaces enable read-access and write-access to external memory for the DMA controller.

The NPU has two read/write masters, M0 and M1.

#### AMBA 4 APB slave interface with wake-up signaling

Enables the device driver that runs on the external host application processor to access the control registers of the NPU.

#### Interrupt interface

Sends interrupt requests to the external host application processor, usually to signal a completed job.

#### Two Q-Channel interfaces

These interfaces enable communication with an external clock controller and power controller. This communication enables the system to automatically disable the clock of the NPU or disable the power to it. The clock is otherwise free-running. The NPU does not quiesce while executing a task, and usually does not quiesce if there are any tasks in a job queue.

The NPU software stack partly manages the activity the Q-Channel reports on.

You can configure the NPU to request downclocking or powering down when it is idle. This downclocking can be when the command queue is empty or when the NPU is waiting to be restarted after being stopped.

# Clock and reset

The NPU has one clock and one reset signal.

Arm recommends that the AXI and NPU clock be the same; however, a different clock ratio can be supported using the **CLKEN** signals.

#### 2.3.2 Central control

The *Central Control* (CC) is the main control unit inside the NPU. The CC controls how the NPU processes neural networks, maintains synchronization, and handles data dependencies.

The CC receives tasks from the external host application processor. The CC queues and dispatches units of work to the DMA controller, weight decoder, MAC unit, and Output unit. The DMA controller and MAC unit send events to the CC to signal the completion of work.

The CC contains multiple sets of operation settings to increase efficiency. This enables the CC to set up the next piece of work while the current one is being processed.

After completing scheduling, dispatching, or processing work, the CC checks for any events that have been triggered. If there are no new events, the CC requests underclocking or powerdown, depending on the configuration.

The CC comprises a Traversal unit. The CC instructs this unit to handle commands that require traversal. This unit breaks commands down into smaller commands, performs synchronization as they execute, and implements the different data flows the NPU requires.

The CC comprises a Command unit. This unit receives commands and parses them. Traversal tasks are passed to the traversal unit. Data dependencies can be coded into the NPU command stream by the Offline Compiler, so that data dependencies between commands are not broken. Measuring the data dependency is an NPU internal process.

Other commands can:

- Trigger interrupts.

- Cause the NPU to wait for a data dependency to be cleared.

- Set up internal registers with information relating to the next execution step.

The CC implements an Arm AMBA 4 APB slave interface. This interface enables the application processor to control the NPU. This interface also enables performance measurements.

#### 2.3.3 DMA controller

The DMA controller manages all transactions that use the Arm AMBA 5 AXI interfaces.

The channels that the DMA controller uses are:

#### **Command channel**

The NPU uses this channel to read the command stream, normally from external flash. The NPU moves the commands into CC. The application processor activates the command channel when it sets up the location and size of the Command queue. It sets up the Command queue by using the registers that are mapped to the AMBA 4 APB.

#### IFM channel

The NPU uses the IFM channel to read input feature maps and stores them in its shared RAM. Because the shared buffer must store activations from different x,y coordinates in different words, the DMA controller unpacks data which is stored in NHWC format. This might require extra internal buffering, but only for the initial layer of a job. Internal layers can use a more efficient format.

The DMA controller considers the kernel stride, because this affects which bank or address the DMA controller requires to store activations.

When the DMA controller is in vector-product mode, it supports fetching multiple batches.

The IFM channel is triggered once per block for blocks that require input feature maps.

#### **OFM** channel

The NPU uses the OFM channel to write output feature maps from shared RAM to external RAM. Because the output is double-buffered in the shared RAM, the DMA requires an interface to synchronize with the output module to notify the DMA which buffer is empty or full.

For the last layer of a job, the output must be written out in NHWC format. This may require the DMA to pack the data, depending on the depth of the layer. Since this process reduces the bandwidth, this process is possible in a small register bank inside the DMA.

The traversal unit triggers the OFM channel once per output block for blocks that require transfer to external memory.

## Weight channel

The weight channel transfers compressed weights from external memory to the weight decoder. The DMA controller uses a read buffer to hide bus latency from the weight decoder and to enable the DMA to handle data arriving out of order.

The traversal unit triggers the weight channel for blocks that require the transfer of weights.

The weight stream must be quantized to 8 bits or less by an offline tool. When passed through the offline compiler, weights are compressed losslessly and reordered into an NPU-specific weight stream. This process is effective, if the quantizer uses less than 8 bits or if it uses clustering and pruning techniques, it may also employ all three methods. Using lossless compression, an average of  $\sim$ 2 bits is possible in the final weight stream, especially if the weight stream has many zeros.

#### mem2mem channel

The NPU uses this channel to stream general data from memory to memory. The main purpose of this channel is to read weights from slow, non-volatile memory and store them in the SRAM. This might be performed in preparation for a layer which reads the weights multiple times. Having the weights in SRAM saves power and improves performance compared to reads to non-volatile memory.

The traversal unit triggers mem2mem operations on specific API commands.

#### Bias and scale channel

This channel streams data to the Output unit. The data that it transmits is the scale and bias necessary for the block that the NPU is processing. Layers that pass through the Output unit are written to the external SRAM. As the layers pass through the Output unit, activation functions can be fused.

| Note |

|------|

|------|

Only the mem2mem DMA channel is controllable directly by the command stream. The other channels are used to load or store data required by NPU operations. Write DMA channels must always use AXI port 0. Read DMA channels can use AXI port 0 or 1 according to which region is configured for the memory.

# 2.3.4 Clock and power module

The *Clock and Power Module* (CPM) handles hard and soft resets, contains registers for the current security settings, the main clock gate, and the QLPI interface.

#### Clock and power module controlling reset

The **nRESET** input signal triggers a hard reset. When the APB RESET register is written to, a soft reset is triggered, as long as Write-Access is permitted. The APB-PPROT and CPL, CSL register values determine whether a write is permitted.

Register access to APB RESET is permitted, if (PPROT[0]>=CPL && PPROT[1]<=CNS). Otherwise the register access is not permitted.

At any reset, all registers and memories in the NPU are cleared to prevent leakage between Security states. The CPM triggers all soft resets. Hard resets must come from an external reset controller.

Both hard and soft resets use a similar procedure, which is:

- 1. If the reset is a soft reset:

- a. With the DMA controller clock on, signal to the DMA that a soft reset is initiated.

- b. Wait for the DMA to acknowledge the reset request.

- 2. With the internal NPU clock off, activate the system reset within two clock cycles.

- 3. Deactivate the system reset.

- 4. With the shared buffer and DMA controller clock on, the CPM signals to the shared buffer and the DMA that the RAMs must be cleared.

- 5. Update the setting in the CPL, CSL register.

#### QLPI for clock

To enable high-level clock gating, the NPU exposes a Q-Channel slave port. This slave port enables the system to automatically disable the clock of the NPU, that is free-running except during reset.

If the entire NPU is in stopped state, it indicates when the clock can be turned off. You can configure the NPU registers using the AMBA 4 APB, so that it keeps requesting a clock in stopped state.

#### QLPI for power

For high-level power gating, the NPU exposes a Q-Channel slave port. This slave port permits the system to automatically disable the power of the NPU.

If the entire NPU is in stopped state, it indicates when power can be turned off. You can configure the NPU using the AMBA 4 APB, so that it keeps requesting power in stopped state.

#### Clock and power module clock gates

The CPM contains one main clock gate. Other clock gating is performed inside each of the blocks, which the CPM can override. These clock gates are explicitly instantiated, with the CPM clock gate preceding the block level clock gates.

#### 2.3.5 Weight decoder

The Weight Decoder (WD) reads the weight stream from the DMA controller. The decoder decompresses and stores this stream in a double-buffered register, ready for the MAC unit to consume it.

#### 2.3.6 MAC unit

The MAC unit performs multiply-accumulate operations that are required for convolution, depth-wise pooling, vector products, and the max operation required for max pooling.

The MAC unit comprises:

- · An IFM unit

- · Dot product units

- An adder array.

#### IFM unit

The IFM unit inside the MAC unit reads the input feature maps from the shared SRAM and stores them in register slices. These slices are fed into the multipliers in the dot product units. The IFM unit also performs some extra services as part of other operations.

The IFM unit handles zero-padding around the outside edge of feature maps and the upscaling that deconvolution requires. Deconvolution upscaling uses nearest neighbor or zero insertion.

#### Dot product units

The MAC unit contains several dot product units. These dot product units perform the multiply-accumulate operations that are required for convolutions.

The dot product units contain a max operator that they use for max pooling.

## Adder array

The adder array reads a set of accumulators from the shared RAM buffer and updates them with partial accumulations from the dot product units. The adder array then writes the result back.

Accuracy is maintained throughout this process. The internal accumulators retain precision so that the output is bit-exact to the software reference, in this case TFL.

The compiler selects the accumulator format in the shared buffer. This format can be:

- 32-bit two's complement

- 40-bit two's complement

You can also configure the compiler to use 16-bit floating-point format, which improves performance but impacts accuracy.

These formats are only used internally.

# 2.3.7 Output unit

The Output unit reads finished accumulators from the shared RAM and converts them into output activations. This process includes performing scaling for each OFM, adding the bias to values, and applying the activation function to each point.

Every layer is written to external SRAM, but the activation function and scaling are normally fused. There is no forwarding path from output to input inside the NPU. Although layers can be split into horizontal stripes and run in "cascade" to minimize the SRAM footprint. This means that the external SRAM footprint can be smaller than the largest layer.

The activation functions that the Output unit supports are:

- ReLU, ReLU1, ReLU6, and Leaky ReLU

- tanh

- sigmoid

- Configurable Lookup Table (LUT)

- · None or bypass

The elementwise operations that the Output unit supports are:

- Elementwise ADD and SUB

- Elementwise Multiplication (MUL)

- Elementwise Min and Max

- Elementwise ABS

- Elementwise Shift Left (SHL) and Elementwise Shift Right (SHR)

- Elementwise Count-leading Zero (CLZ)

When the Output unit has computed output activations, it writes them back into the shared RAM. The output activations are buffered in the shared RAM where they wait for the DMA controller to send them to external memory.

#### Scaling unit

The Scaling unit in the Output unit performs scaling in convolutions and division in average pooling.

The number of scaling operations that are performed per clock depends on the configuration. The number of outputs per clock varies, depending on the operation.

# **ReLU and Leaky ReLU**

Rectified Linear Unit (ReLU) operations are typically performed after scaling and bias addition.

The number of ReLU operations that are done in parallel is the same as the number of parallel operations that the Scaling unit performs.

Leaky ReLU (LReLU) is a variant, a nonzero ReLU with a small positive gradient that targets negative values, unlike standard ReLU functions. Leaky ReLU implements Leaky ReLU as long as the input and output quantization scale are the same. The most recent TensorFlow Lite allows the quantization scale to differ. In that case, we recommend using the LUT for 8-bit activations and element wise operators for 16-bit activations.

#### tanh, sigmoid, and LUT

The Output unit supports tanh and sigmoid functions using a hardwired table combined with bilinear interpolation. The same table is used for both functions, because they are mathematically related.

The Output unit can perform one tanh or sigmoid function per cycle.

There is also a *Configurable Lookup Table* (LUT) that can be used for any point-wise activation or function. For 8-bit activations, the LUT holds up to 256 8-bit values that are directly mapped from IFM to OFM. The LUT size increases to 512 for 16-bit values; however, the outputs are interpolated, bilinear values.

The LUT can be configured by setting up a mem2mem transfer. For more information, refer to 2.3.3 DMA controller on page 2-23.

# Chapter 3 **Programmers model**

This chapter describes a register and register map of the NPU.

It contains the following sections:

- 3.1 Register characteristics on page 3-29.

- 3.2 Register page BASE on page 3-30.

- 3.3 Register page BASE POINTERS on page 3-48.

- 3.4 Register page ID on page 3-54.

- 3.5 Register page PMU on page 3-59.

- 3.6 Command stream on page 3-76.

- 3.7 Weight stream format on page 3-87.

- 3.8 Operators and performance on page 3-97.

- 3.9 Block based operation on page 3-107.

# 3.1 Register characteristics

The registers in the NPU have common characteristics.

The following are the characteristics of the registers in the NPU:

- Register addresses are shown as offsets from the base address.

- Registers are 32-bit wide words.

- Register reads and writes use word accesses only.

- Register halfword and byte reads are UNDEFINED.

- Register halfword and byte writes are UNPREDICTABLE.

- Every access to the registers is compared with the *Current active Privilege Level* (CPL) and the active *Current Non-Secure level* (CNS) of the PROT register:

- Register access is permitted if (PPROT[0]>=CPL && PPROT[1]<=CNS). Otherwise the register access is not permitted.</li>

- A read access that is not permitted, either due to privilege or being a write-only register, returns the value zero.

- A write-access that is not permitted, either due to privilege or being a read-only register, is ignored.

# 3.2 Register page BASE

The NPU control registers bank.

Table 3-1 BASE registers

| Address    | Link                                       | Usage                                                                                         | Access     | Default                                                                                     |

|------------|--------------------------------------------|-----------------------------------------------------------------------------------------------|------------|---------------------------------------------------------------------------------------------|

| 0x00000000 | 3.2.1 Register ID on page 3-31             | ID register                                                                                   | Read-only  | 0x10066001                                                                                  |

| 0x00000004 | 3.2.2 Register STATUS on page 3-32         | Register describing the current operating status of the NPU                                   | Read-only  | 0x00000008                                                                                  |

| 0x00000008 | 3.2.3 Register CMD on page 3-34            | Command register, reads as last written command                                               | Read/write | 0x0000000C                                                                                  |

| 0x0000000C | 3.2.4 Register RESET on page 3-35          | Request Reset and new security mode                                                           | Read/write | 0x00000000                                                                                  |

| 0x00000010 | 3.2.5 Register QBASE0 on page 3-36         | Base address of Command queue bits[31:0]. The address is 4-byte-aligned                       | Read/write | 0x00000000                                                                                  |

| 0x00000014 | 3.2.6 Register QBASE1 on page 3-37         | Address extension bits[39:32] bits for queue base                                             | Read/write | 0x00000000                                                                                  |

| 0x00000018 | 3.2.7 Register QREAD on page 3-37          | Read offset in the command stream in bytes. Multiples of 4 in the range 0-16 MB               | Read-only  | 0x00000000                                                                                  |

| 0x0000001C | 3.2.8 Register QCONFIG<br>on page 3-37     | AXI configuration for the command stream in the range 0-3. Same encoding as for REGIONCFG     | Read/write | 0x00000000                                                                                  |

| 0x00000020 | 3.2.9 Register QSIZE on page 3-37          | Size of the command stream in bytes. Multiples of 4 in the range 0-16 MB                      | Read/write | 0x00000000                                                                                  |

| 0x00000024 | 3.2.10 Register PROT on page 3-38          | Protection level configured for the NPU when acting as an AXI master                          | Read-only  | 0x00000000                                                                                  |

| 0x00000028 | 3.2.11 Register CONFIG on page 3-39        | RTL configuration                                                                             | Read-only  | 0x10003008 for the<br>256 configuration,<br>and 0x10006009 for<br>the 512<br>configuration. |

| 0x0000002C | 3.2.12 Register LOCK on page 3-40          | Lock register. This register is designed for driver use and does not affect NPU functionality | Read/write | 0x00000000                                                                                  |

| 0x0000003C | 3.2.13 Register REGIONCFG on page 3-40     | Base pointer configuration. Bits[2*k +1:2*k] give the memory type for REGION[k]               | Read/write | 0x00000000                                                                                  |

| 0x00000040 | 3.2.14 Register AXI_LIMITO on page 3-43    | AXI limits for port 0 counter 0                                                               | Read/write | 0x00000000                                                                                  |

| 0x00000044 | 3.2.15 Register AXI_LIMIT1 on page 3-44    | AXI limits for port 0 counter 1                                                               | Read/write | 0x00000000                                                                                  |

| 0x00000048 | 3.2.16 Register AXI_LIMIT2<br>on page 3-45 | AXI limits for port 1 counter 2                                                               | Read/write | 0x00000000                                                                                  |

| 0x0000004C | 3.2.17 Register AXI_LIMIT3<br>on page 3-46 | AXI limits for port 1 counter 3                                                               | Read/write | 0x00000000                                                                                  |

This section contains the following subsections:

- *3.2.1 Register ID* on page 3-31.

- 3.2.2 Register STATUS on page 3-32.

- *3.2.3 Register CMD* on page 3-34.

- 3.2.4 Register RESET on page 3-35.

- 3.2.5 Register OBASE0 on page 3-36.

- 3.2.6 Register QBASE1 on page 3-37.

- 3.2.7 Register QREAD on page 3-37.

- 3.2.8 Register QCONFIG on page 3-37.

- 3.2.9 Register QSIZE on page 3-37.

- 3.2.10 Register PROT on page 3-38.

- 3.2.11 Register CONFIG on page 3-39.

- 3.2.12 Register LOCK on page 3-40.

- 3.2.13 Register REGIONCFG on page 3-40.

- 3.2.14 Register AXI\_LIMIT0 on page 3-43.

- 3.2.15 Register AXI\_LIMIT1 on page 3-44.

- 3.2.16 Register AXI\_LIMIT2 on page 3-45.

- 3.2.17 Register AXI LIMIT3 on page 3-46.

#### 3.2.1 Register ID

ID register.

The default value of this RO register describes the product version. Please refer to the individual fields for information

Table 3-2 Register BASE.ID layout

| Bits    | Link                        | Name           | Usage                                                                            | Default                    |

|---------|-----------------------------|----------------|----------------------------------------------------------------------------------|----------------------------|

| [31:28] | arch_major_rev on page 3-31 | arch_major_rev | This is the major architecture version number, a in the architecture version a.b | 1                          |

| [27:20] | arch_minor_rev on page 3-31 | arch_minor_rev | This is the minor architecture version number, b in the architecture version a.b | 0                          |

| [19:16] | arch_patch_rev on page 3-32 | arch_patch_rev | This is the patch number of the architecture version a.b                         | 6 (implementation defined) |

| [15:12] | product_major on page 3-32  | product_major  | This is the X-part of the ML00X product number                                   | 6 (implementation defined) |

| [11:8]  | version_major on page 3-32  | version_major  | This is the <i>n</i> for the R-part of an R <i>n</i> P <i>n</i> release number   | 0x0                        |

| [7:4]   | version_minor on page 3-32  | version_minor  | This is the <i>n</i> for the P-part of an R <i>n</i> P <i>n</i> release number   | 0x0                        |

| [3:0]   | version_status on page 3-32 | version_status | This is the version of the product                                               | 1 (implementation defined) |

#### Field arch\_major\_rev

This is the major architecture version number, a in the architecture version a.b.

arch\_major\_rev is stored in bits[31:28] and is a 4-bit unsigned integer. Its default value is 1 (implementation defined).

### Field arch\_minor\_rev

This is the minor architecture version number, b in the architecture version a.b.

arch\_minor\_rev is stored in bits[27:20] and is a 8-bit unsigned integer. Its default value is 0 (implementation defined).

#### Field arch\_patch\_rev

This is the patch number of the architecture version a.b.

arch\_patch\_rev is stored in bits[19:16] and is a 4-bit unsigned integer. Its default value is 6 (implementation defined).

### Field product\_major

This is the X-part of the ML00X product number.

product\_major is stored in bits[15:12] and is a 4-bit unsigned integer. Its default value is 6 (implementation defined).

#### Field version\_major

This is the n for the R-part of an RnPn release number.

version\_major is stored in bits[11:8] and is a 4-bit unsigned integer. Its default value is 0x0.

#### Field version\_minor

This is the n for the P-part of an RnPn release number.

version minor is stored in bits[7:4] and is a 4-bit unsigned integer. Its default value is 0x0.

#### Field version\_status

This is the version of the product.

version\_status is stored in bits[3:0] and is a 4-bit unsigned integer. Its default value is 1 (implementation defined).

#### 3.2.2 Register STATUS

Register describes the current operating status of the NPU.

Table 3-3 Register BASE.STATUS layout

| Bits    | Link                            | Name               | Usage                                                                                                            | Default |

|---------|---------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------|---------|

| [31:16] | irq_history_mask on page 3-33   | irq_history_mask   | IRQ History mask                                                                                                 | 0x0     |

| [15:12] | faulting_channel on page 3-33   | faulting_channel   | Faulting channel on a bus abort. Read: 0=Cmd, 1=IFM, 2=Weights, 3=Scale+Bias, 4=Mem2Mem; Write: 8=OFM, 9=Mem2Mem | 0x0     |

| [11]    | faulting_interface on page 3-33 | faulting_interface | Faulting interface on bus abort. 0=AXI-M0, 1=AXI-M1                                                              | 0x0     |

| [10:9]  | Reserved                        | -                  | -                                                                                                                | -       |

| [8]     | ecc_fault on page 3-33          | ecc_fault          | ECC state for internal RAMs: 0=no fault, 1=ECC fault signalled. Can only be cleared by reset.                    | 0x0     |

| [7]     | wd_fault on page 3-33           | wd_fault           | This bit will never be set in this product.                                                                      | -       |

| [6]     | pmu_irq_raised on page 3-33     | pmu_irq_raised     | 0=No PMU IRQ, 1=PMU IRQ raised. Cleared by using command register bit 1                                          | 0x0     |

| [5]     | cmd_end_reached on page 3-34    | cmd_end_reached    | 0=Not reached, 1=Reached. Cleared by writing QBASE or QSIZE when NPU is in stopped state                         | 0x0     |

Table 3-3 Register BASE.STATUS layout (continued)

| Bits | Link                         | Name            | Usage                                                                                                                                                                               | Default                                               |

|------|------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| [4]  | cmd_parse_error on page 3-34 | cmd_parse_error | 0=No error, 1=Command-stream parsing error detected. Can only be cleared by a reset                                                                                                 | 0x0                                                   |

| [3]  | reset_status on page 3-34    | reset_status    | Reset is ongoing and only this register can be read (other registers read as 0 and writes are ignored). A value of 0 means the NPU is not being reset and can be accessed as normal | 0x1 if the reset operation is ongoing, otherwise 0x0. |

| [2]  | bus_status on page 3-34      | bus_status      | 0=OK, 1=Bus abort detected and processing halted (the NPU has reached IDLE state and does not start to process any more commands/AXI transactions). Can only be cleared by a reset  | 0x0                                                   |

| [1]  | irq_raised on page 3-34      | irq_raised      | Raw IRQ status, 0 = IRQ not raised, 1 = IRQ raised. IRQ is cleared using command register bit 1                                                                                     | 0x0                                                   |

| [0]  | state on page 3-34           | state           | NPU state, 0 = Stopped, 1 = Running                                                                                                                                                 | stopped                                               |

#### Field irq\_history\_mask

IRQ History mask.

irq history mask is stored in bits[31:16] and is a 16-bit unsigned integer. Its default value is 0x0.

This is used for debug purposes. Each IRQ or Event operation provides a 16-bit mask, which is logically ORed into these bits. The bits can be cleared using the command register.

#### Field faulting\_channel

Faulting channel on a bus abort. Read: 0=Cmd, 1=IFM, 2=Weights, 3=Scale+Bias, 4=Mem2Mem; Write: 8=OFM, 9=Mem2Mem.

faulting channel is stored in bits[15:12] and is a 4-bit unsigned integer. Its default value is 0x0.

#### Field faulting\_interface

Faulting interface on bus abort. 0=AXI-M0, 1=AXI-M1.

faulting interface is stored in bit[11] and is a 1-bit unsigned integer. Its default value is 0x0.

#### Field ecc fault

ECC state for internal RAMs: 0=no fault, 1=ECC fault signalled. Can only be cleared by reset. ecc\_fault is stored in bit[8] and is a 1-bit unsigned integer. Its default value is 0x0.

#### Field wd\_fault

This bit will never be set in this product.

#### Field pmu\_irq\_raised

0=No PMU, IRQ, 1=PMU IRQ raised. Cleared by using command register bit 1.

pmu\_irq\_raised is stored in bit[6] and is a 1-bit unsigned integer. Its default value is 0x0.

#### Field cmd\_end\_reached

0=Not reached, 1=Reached. Cleared by writing QBASE or QSIZE when the NPU is in stopped state. cmd\_end\_reached is stored in bit[5] and is a 1-bit unsigned integer. Its default value is 0x0.

#### Field cmd\_parse\_error

0=No error, 1=Command stream parsing error detected. Can only be cleared by a reset. cmd parse error is stored in bit[4] and is a 1-bit unsigned integer. Its default value is 0x0.

#### Field reset status

Reset is ongoing and only this register can be read (other registers read as 0 and writes are ignored). A value of 0 means the NPU is not being reset and can be accessed as normal.

reset\_status is stored in bit[3] and is a 1-bit unsigned integer. Its default value is 0x1 if the reset operation is ongoing, otherwise its default value is 0x0.

#### Field bus\_status

0=OK, 1=Bus abort detected and processing halted (the NPU has reached IDLE state and does not start to process any more commands/AXI transactions). Can only be cleared by a reset.

bus\_status is stored in bit[2] and is a 1-bit unsigned integer. Its default value is 0x0.

### Field irq\_raised

Raw IRQ status, 0 = IRQ not raised, 1 = IRQ raised. IRQ is cleared using command register bit 1. irq raised is stored in bit[1] and is a 1-bit unsigned integer. Its default value is 0x0.

#### Field state

NPU state, 0 = Stopped, 1 = Running.

state is stored in bit[0] and is a 1-bit enumeration. Its default value is stopped.

The field can contain the following values:

Table 3-4 Field state values

| Value       | Name    | Meaning                      |

|-------------|---------|------------------------------|

| 0 (default) | stopped | The NPU is in stopped state. |

| 1           | running | The NPU is in Running state. |

#### 3.2.3 Register CMD

The Command register, reads as last written command.

Table 3-5 Register BASE.CMD layout

| Bits    | Link                           | Name              | Usage                                                           | Default |

|---------|--------------------------------|-------------------|-----------------------------------------------------------------|---------|

| [31:16] | clear_irq_history on page 3-35 | clear_irq_history | Clears the IRQ history mask                                     | 0x0     |

| [15:4]  | Reserved                       | -                 | -                                                               | -       |

| [3]     | power_q_enable on page 3-35    | power_q_enable    | Write 1 to this bit to enable power off using Power Q-interface | 0x1     |

#### Table 3-5 Register BASE.CMD layout (continued)

| Bits | Link                                     | Name                        | Usage                                                                                          | Default |

|------|------------------------------------------|-----------------------------|------------------------------------------------------------------------------------------------|---------|

| [2]  | clock_q_enable on page 3-35              | clock_q_enable              | Write 1 to this bit to enable clock off using Clock Q-interface and enable the main clock gate | 0x1     |

| [1]  | clear_irq on page 3-35                   | clear_irq                   | Write 1 to clear the IRQ status in the STATUS register. Writing 0 has no effect                | 0x0     |

| [0]  | transition_to_running_state on page 3-35 | transition_to_running_state | Write 1 to transition the NPU to running state. Writing 0 has no effect                        | 0x0     |

#### Field clear\_irq\_history

Clears the IRQ history mask.

clear irq history is stored in bits[31:16] and is a 16-bit unsigned integer. Its default value is 0x0.

When bit k is set then corresponding bit k of the status register (IRQ history) is cleared.

#### Field power q enable

Write 1 to this bit to enable power off using Power Q-interface.

power q enable is stored in bit[3] and is a 1-bit unsigned integer. Its default value is 0x1.

#### Field clock\_q\_enable

Write 1 to this bit to enable clock off using Clock Q-interface and enable the main clock gate.

clock q enable is stored in bit[2] and is a 1-bit unsigned integer. Its default value is 0x1.

#### Field clear\_irq

Write 1 to clear the IRQ status in the STATUS register. Writing 0 has no effect.

clear irq is stored in bit[1] and is a 1-bit unsigned integer. Its default value is 0x0.

#### Field transition\_to\_running\_state

Write 1 to transition the NPU to running state. Writing 0 has no effect.

transition\_to\_running\_state is stored in bit[0] and is a 1-bit unsigned integer. Its default value is 0x0.

# 3.2.4 Register RESET

Request Reset and new security mode.

If this register is written to by a permitted master, then the NPU is reset (clearing all internal RAMs) and the reset register value is updated. (Otherwise the write to this register is ignored and the NPU is not reset.)

The value written to this register sets the privilege level used by the NPU when the NPU acts as an AXI master. The host is permitted to set any level of privilege less than or equal to the host privilege level.

Table 3-6 Register BASE.RESET layout

| Bits   | Link                     | Name        | Usage                                         | Default |

|--------|--------------------------|-------------|-----------------------------------------------|---------|

| [31:2] | Reserved                 | -           | -                                             | -       |

| [1]    | pending_CSL on page 3-36 | pending_CSL | Current security level 0=Secure, 1=Non-secure | secure  |

| [0]    | pending_CPL on page 3-36 | pending_CPL | Current privilege level 0=User, 1=Privileged  | user    |

# Field pending\_CSL

Current security level 0=Secure, 1=Non-secure.

pending\_CSL is stored in bit[1] and is a 1-bit enumeration. Its default value is secure.

The field can contain the following values:

Table 3-7 Field pending\_CSL values

| Value       | Name       | Meaning                                               |

|-------------|------------|-------------------------------------------------------|

| 0 (default) | secure     | The NPU's security level is configured as Secure.     |

| 1           | non_secure | The NPU's security level is configured as Non-Secure. |

# Field pending\_CPL

Current privilege level 0=User, 1=Privileged.

pending\_CPL is stored in bit[0] and is a 1-bit enumeration. Its default value is user.

The field can contain the following values:

Table 3-8 Field pending\_CPL values

| Value       | Name       | Meaning                                            |

|-------------|------------|----------------------------------------------------|

| 0 (default) | user       | The NPU is configured for User-level access.       |

| 1           | privileged | The NPU is configured for Privileged-level access. |

# 3.2.5 Register QBASE0

The base address of the Command-queue bits[31:0]. The address is 4-byte-aligned.

Table 3-9 Register BASE.QBASE0 layout

| Bits   | Link                | Name   | Usage                                                                    | Default    |

|--------|---------------------|--------|--------------------------------------------------------------------------|------------|

| [31:0] | QBASE0 on page 3-36 | QBASE0 | The 4-byte-aligned lower bytes of the base address value for the command | 0x00000000 |

|        |                     |        | stream                                                                   |            |

#### Field QBASE0

The 4-byte-aligned lower bytes of the base address value for the command stream.

QBASE0 is stored in bits[31:0] and is a 32-bit unsigned integer. Its default value is 0x000000000.

### 3.2.6 Register QBASE1

Address extension bits[39:32] bits for queue base.

Table 3-10 Register BASE.QBASE1 layout

| Bits   | Link                | Name   | Usage                                                                        | Default |

|--------|---------------------|--------|------------------------------------------------------------------------------|---------|

| [31:0] | QBASE1 on page 3-37 | QBASE1 | SE1 The 4-byte-aligned upper bytes of the base address value for the command |         |

|        |                     |        | stream                                                                       |         |

#### Field QBASE1

The 4-byte-aligned upper bytes of the base address value for the command stream.

QBASE1 is stored in bits[31:0] and is a 32-bit unsigned integer. Its default value is 0x00000000.

### 3.2.7 Register QREAD

The Read offset in the command stream in bytes. Multiples of 4 in the range 0-16 MB.

Table 3-11 Register BASE.QREAD layout

| Bits   | Link               | Name  | Usage                                                  | Default    |

|--------|--------------------|-------|--------------------------------------------------------|------------|

| [31:0] | QREAD on page 3-37 | QREAD | The read offset of the current command under execution | 0x00000000 |

#### Field QREAD

The read offset of the current command under execution.

QREAD is stored in bits[31:0] and is a 32-bit unsigned integer. Its default value is 0x000000000.

#### 3.2.8 Register QCONFIG

The AXI configuration for the command stream in the range 0-3. Same encoding as for REGIONCFG.

Table 3-12 Register BASE.QCONFIG layout

| Bits   | Link                 | Name    | Usage                                                     | Default    |

|--------|----------------------|---------|-----------------------------------------------------------|------------|

| [31:0] | QCONFIG on page 3-37 | QCONFIG | AXI configuration for the command stream in the range 0-3 | 0x00000000 |

#### Field QCONFIG

The AXI configuration for the command stream in the range 0-3.

QCONFIG is stored in bits[31:0] and is a 32-bit unsigned integer. Its default value is 0x00000000.

### 3.2.9 Register QSIZE

Size of the command stream in bytes. Multiples of 4 in the range 0-16 MB.

Table 3-13 Register BASE.QSIZE layout

| Bits   | Link               | Name  | Usage                                                     | Default    |

|--------|--------------------|-------|-----------------------------------------------------------|------------|

| [31:0] | QSIZE on page 3-38 | QSIZE | Size of the next command stream to be executed by the NPU | 0x00000000 |

#### Field QSIZE

Size of the next command stream to be executed by the NPU.

QSIZE is stored in bits[31:0] and is a 32-bit unsigned integer. Its default value is 0x00000000.

### 3.2.10 Register PROT

The protection level configured for the NPU when acting as an AXI master.

Table 3-14 Register BASE.PROT layout

| Bits   | Link                    | Name       | Usage                                         | Default            |

|--------|-------------------------|------------|-----------------------------------------------|--------------------|

| [31:2] | Reserved                | -          |                                               |                    |

| [1]    | active_CSL on page 3-38 | active_CSL | Current security level 0=Secure, 1=Non-secure | Dependent on PORSL |

| [0]    | active_CPL on page 3-38 | active_CPL | Current privilege level 0=User, 1=Privileged  | Dependent on PORPL |

#### Field active\_CSL

Current security level 0=Secure, 1=Non-secure.

active\_CSL is stored in bit[1] and is a 1-bit enumeration. Its default value is dependent on PORSL.

This is used as AxPROT[1] when the NPU is a master and set from Pending CSL after the reset is complete.

- After a hard reset, this is set to Power-on-reset security level (PORSL), which allows for CPUs that

do not support TrustZone.

- After a soft reset, this is set to pending\_CSL, if PPROT[1]==0, otherwise it is set to 1. For this to be effective, there must be a memory-protection controller included in the system.

The field can contain the following values:

Table 3-15 Field active\_CSL values

| Value       | Name       | Meaning                                               |  |

|-------------|------------|-------------------------------------------------------|--|

| 0 (default) | secure     | The NPU's security level is configured as Secure.     |  |

| 1           | non_secure | The NPU's security level is configured as Non-Secure. |  |

#### Field active CPL

Current privilege level 0=User, 1=Privileged.

active CPL is stored in bit[0] and is a 1-bit enumeration. Its default value is dependent on PORPL.

This is used as AxPROT[0] when the NPU is a master.

- After a hard reset, this is set to Power-on-reset privilege level (PORPL).

- After a soft reset, this is set to pending\_CPL, if PPROT[0]==1, otherwise it is set to 0. For this to be effective, there must be system-level memory protection built for the system.

The field can contain the following values:

Table 3-16 Field active\_CPL values

| Value       | Name       | Meaning                                            |  |

|-------------|------------|----------------------------------------------------|--|

| 0 (default) | user       | The NPU is configured for User-level access.       |  |

| 1           | privileged | The NPU is configured for Privileged-level access. |  |

## 3.2.11 Register CONFIG

The RTL configuration register.

The default value of this RO register describes the NPU configuration. Please refer to the individual fields for information.

Table 3-17 Register BASE.CONFIG layout

| Bits    | Link                            | Name               | Usage                                                                                                                  | Default                    |

|---------|---------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------|

| [31:28] | product on page 3-39            | product            | Product configuration                                                                                                  | 1 (implementation defined) |

| [27:16] | Reserved                        | -                  | -                                                                                                                      | -                          |

| [15:8]  | shram_size on page 3-39         | shram_size         | The size of SHRAM is 48KB for the 256 configuration, and 96KB for the 512 configuration.                               | -                          |

| [7:4]   | cmd_stream_version on page 3-39 | cmd_stream_version | Command-stream version accepted by this NPU                                                                            | 0x0                        |

| [3:0]   | macs_per_cc on page 3-39        | macs_per_cc        | The log2 (macs/clock cycle). The valid encoding range is 8 for the 256 configuration, and 9 for the 512 configuration. | -                          |

#### Field product

Product configuration.

product is stored in bits[31:28] and is a 4-bit unsigned integer. Its default value is 1 (implementation defined).

#### Field shram\_size

Size in KB of SHRAM in the range 48-96.

shram size is stored in bits[15:8] and is an 8-bit enumeration.

The field can contain the following values:

Table 3-18 Field shram\_size values

| Value | Name       | Meaning                     |

|-------|------------|-----------------------------|

| 0x30  | SHRAM_48kB | The available SHRAM is 48KB |

| 0x60  | SHRAM_96kB | The available SHRAM is 96KB |

#### Field cmd\_stream\_version

The command-stream version accepted by this NPU.

cmd stream version is stored in bits[7:4] and is a 4-bit unsigned integer. Its default value is 0x0.

#### Field macs\_per\_cc

The log2(macs/clock cycle). Valid encoding range is 8 and 9 for 256 and 512 MACs/clock cycle, respectively (each MAC is an 8-bit x 8-bit MAC).

macs per cc is stored in bits[3:0] and is a 4-bit enumeration.

The field can contain the following values:

Table 3-19 Field macs\_per\_cc values

| Value | Name             | Meaning                                       |

|-------|------------------|-----------------------------------------------|

| 0x8   | Macs_per_cc_is_8 | The number of MACs per clock cycle is 28.     |

| 0x9   | Macs_per_cc_is_9 | The number of MACs per clock cycle is $2^9$ . |

## 3.2.12 Register LOCK

The Lock register. This register is designed for driver use and does not affect NPU functionality.

The register holds a 32-bit value which is cleared to 0 on a reset. The register has special write semantics. Suppose the current register value is "c" and the newly written register value is "w":

If (c==0 or w==0), then the register is updated to the newly written value "w".

Otherwise the write is ignored and the value remains unchanged.

- To try to claim the lock, write a nonzero ID value and read it back to see if the value was accepted.

- To release the lock (that contains your nonzero ID value), write the value 0 to the lock register.

Table 3-20 Register BASE.LOCK layout

| Bits   | Link              | Name | Usage                                   | Default     |

|--------|-------------------|------|-----------------------------------------|-------------|

| [31:0] | LOCK on page 3-40 | LOCK | 32-bit value for the LOCK configuration | 0x000000000 |

#### Field LOCK

32-bit value for the LOCK configuration.

LOCK is stored in bits[31:0] and is a 32-bit unsigned integer. Its default value is 0x000000000.

# 3.2.13 Register REGIONCFG

Region memory type configuration. Bits[2\*k+1:2\*k] give the memory type for REGION[k].

Table 3-21 Register BASE.REGIONCFG layout

| Bits    | Link                 | Name    | Usage                              | Default                   |

|---------|----------------------|---------|------------------------------------|---------------------------|

| [31:16] | Reserved             | -       | -                                  | -                         |

| [15:14] | region7 on page 3-41 | region7 | Bits for the Region7 configuration | axi0_outstanding_counter0 |

| [13:12] | region6 on page 3-41 | region6 | Bits for the Region6 configuration | axi0_outstanding_counter0 |

| [11:10] | region5 on page 3-41 | region5 | Bits for the Region5 configuration | axi0_outstanding_counter0 |

| [9:8]   | region4 on page 3-42 | region4 | Bits for the Region4 configuration | axi0_outstanding_counter0 |

| [7:6]   | region3 on page 3-42 | region3 | Bits for the Region3 configuration | axi0_outstanding_counter0 |

| [5:4]   | region2 on page 3-42 | region2 | Bits for the Region2 configuration | axi0_outstanding_counter0 |

| [3:2]   | region1 on page 3-42 | region1 | Bits for the Region1 configuration | axi0_outstanding_counter0 |

| [1:0]   | region0 on page 3-43 | region0 | Bits for the Region0 configuration | axi0_outstanding_counter0 |

# Field region7

Bits for the Region7 configuration.

region7 is stored in bits[15:14] and is a 2-bit enumeration. Its default value is axi0 outstanding counter0.

The field can contain the following values:

Table 3-22 Field region7 values

| Value       | Name                      | Meaning                                                                      |  |