# Arm® Musca-B1 Test Chip and Board

**Technical Overview**

# Arm® Musca-B1 Test Chip and Board

### **Technical Overview**

Copyright © 2018-2020 Arm Limited or its affiliates. All rights reserved.

#### **Release Information**

### **Document History**

| Issue   | Date             | Confidentiality  | Change       |

|---------|------------------|------------------|--------------|

| 0000-00 | 03 December 2018 | Non-Confidential | First issue  |

| 0000-01 | 01 August 2019   | Non-Confidential | Second issue |

| 0000-02 | 29 March 2020    | Non-Confidential | Third issue  |

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. **No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.**

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with <sup>®</sup> or <sup>™</sup> are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at *http://www.arm.com/company/policies/trademarks*.

Copyright © 2018-2020 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

#### **Product Status**

The information in this document is Final, that is for a developed product.

#### Web Address

www.arm.com

#### **Conformance Notices**

This section contains conformance notices.

### **Federal Communications Commission Notice**

This device is test equipment and consequently is exempt from part 15 of the FCC Rules under section 15.103 (c).

### **CE Conformity**

The *Waste Electrical and Electronic Equipment* (WEEE) marking, that is, the crossed out wheelie-bin figure, indicates that this product must not be disposed of with general waste within the European Union. To prevent possible harm to the environment from uncontrolled waste disposal, the user is required to recycle the product responsibly to promote reuse of material resources. To comply with EU law, you must dispose of the product in one of the following ways:

- Return it to the distributer where it was purchased. The distributer is required to arrange free collection when requested.

- Recycle it using local WEEE recycling facilities. These facilities are now very common and might provide free collection.

- If purchased directly from Arm, Arm provides free collection. Please e-mail weee@arm.com for instructions.

The CE Declaration of Conformity for this product is available on request.

The system should be powered down when not in use.

It is recommended that ESD precautions be taken when handling this product.

The product generates, uses, and can radiate radio frequency energy and may cause harmful interference to radio communications. There is no guarantee that interference will not occur in a particular installation. If this equipment causes harmful interference to radio or television reception, which can be determined by turning the equipment off or on, you are encouraged to try to correct the interference by one or more of the following measures:

- · Ensure attached cables do not lie across any sensitive equipment.

- Reorient the receiving antenna.

- Increase the distance between the equipment and the receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/TV technician for help.

------ Note -

It is recommended that wherever possible shielded interface cables be used.

# Contents Arm<sup>®</sup> Musca-B1 Test Chip and Board Technical Overview

|            | Pref                  | ace                                        |           |  |

|------------|-----------------------|--------------------------------------------|-----------|--|

|            |                       | About this book                            |           |  |

|            |                       | Feedback                                   |           |  |

| Chapter 1  | Introduction          |                                            |           |  |

|            | 1.1                   | Precautions                                | 1-11      |  |

|            | 1.2                   | About the Musca-B1 test chip and board     | 1-12      |  |

|            | 1.3                   | Location of components                     |           |  |

| Chapter 2  | Hardware and software |                                            |           |  |

|            | 2.1                   | Board hardware                             | 2-16      |  |

|            | 2.2                   | Musca-B1 test chip                         |           |  |

|            | 2.3                   | Software, firmware, board, and tools setup | 2-22      |  |

| Appendix A | Spe                   | cifications                                |           |  |

| Appendix B | Revi                  | isions                                     |           |  |

|            | B.1                   | Revisions                                  | Аррх-В-26 |  |

# Preface

This preface introduces the Arm® Musca-B1 Test Chip and Board Technical Overview.

It contains the following:

- *About this book* on page 6.

- *Feedback* on page 9.

# About this book

This book gives an overview of the Arm® Musca-B1 test chip and board.

### Intended audience

This book is written for experienced hardware and software developers to enable low-power, secure *Internet of Things* (IoT) endpoint development using the Musca-B1 test chip and board.

### Using this book

This book is organized into the following chapters:

### **Chapter 1 Introduction**

This chapter introduces the Musca-B1 test chip and Musca-B1 board.

### Chapter 2 Hardware and software

This chapter gives an overview of the Musca-B1 test chip and Musca-B1 board hardware and software.

### Appendix A Specifications

See the *Arm<sup>®</sup> Musca-B1 Test Chip and Board Technical Reference Manual* for information on the Musca-B1 board power supply rails and maximum current loads.

### Appendix B Revisions

This appendix describes the technical changes between released issues of this book.

### Glossary

The Arm<sup>®</sup> Glossary is a list of terms used in Arm documentation, together with definitions for those terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

See the Arm® Glossary for more information.

### **Typographic conventions**

### italic

Introduces special terminology, denotes cross-references, and citations.

### bold

Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.

### monospace

Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.

### <u>mono</u>space

Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.

### monospace italic

Denotes arguments to monospace text where the argument is to be replaced by a specific value.

### monospace bold

Denotes language keywords when used outside example code.

### <and>

Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example:

MRC p15, 0, <Rd>, <CRn>, <CRm>, <Opcode\_2>

### SMALL CAPITALS

Used in body text for a few terms that have specific technical meanings, that are defined in the *Arm*<sup>®</sup> *Glossary*. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE.

### **Timing diagrams**

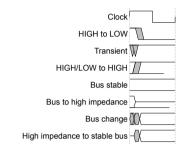

The following figure explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

### Figure 1 Key to timing diagram conventions

# Signals

The signal conventions are:

### Signal level

The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

- HIGH for active-HIGH signals.

- LOW for active-LOW signals.

### Lowercase n

At the start or end of a signal name, n denotes an active-LOW signal.

# Additional reading

This book contains information that is specific to this product. See the following documents for other relevant information.

### Arm publications

- Arm<sup>®</sup> Musca-B1 Test Chip and Board Technical Reference Manual (101312).

- Arm<sup>®</sup> CoreLink<sup>™</sup> SSE-200 Subsystem for Embedded Technical Overview (101123).

- Arm<sup>®</sup> CoreLink<sup>™</sup> SSE-200 Subsystem for Embedded Technical Reference Manual (101104).

- Arm<sup>®</sup> CoreLink<sup>™</sup> SIE-200 System IP for Embedded Technical Reference Manual (DDI 0571).

- Arm<sup>®</sup> Cortex<sup>®</sup>-M System Design Kit Technical Reference Manual (DDI 0479).

- Arm<sup>®</sup> Cortex<sup>®</sup>-M33 Processor Technical Reference Manual (100230).

- PrimeCell UART (PL011) Technical Reference Manual (DDI 0183).

- Arm<sup>®</sup> PrimeCell Real Time Clock (PL031) Technical Reference Manual (DDI 0224).

- CoreSight<sup>™</sup> Components Technical Reference Manual (DDI 0314).

- Arm<sup>®</sup> DS-5 Arm DSTREAM User Guide (DUI 0481).

- Arm<sup>®</sup> DS-5 Using the Debug Hardware Configuration Utilities (DUI 0498).

The following confidential books are only available to licensees or require registration with Arm.

- Arm<sup>®</sup> CryptoCell-312 Technical Reference Manual (100774).

- Arm<sup>®</sup> CryptoIsland-300 Technical Reference Manual (101119).

- Arm<sup>®</sup> v7-M Architecture Reference Manual (DDI 0403).

- Arm<sup>®</sup> AMBA<sup>®</sup> 5 AHB Protocol Specification (IHI 0033).

- Arm<sup>®</sup> AMBA<sup>®</sup> APB Protocol Specification Version 2.0 (IHI 0024).

# Feedback

# Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

# Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- The title Arm Musca-B1 Test Chip and Board Technical Overview.

- The number 101311 0000 02 en.

- If applicable, the page number(s) to which your comments refer.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

\_\_\_\_\_ Note \_\_\_\_\_

Arm tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader.

# Chapter 1 Introduction

This chapter introduces the Musca-B1 test chip and Musca-B1 board.

It contains the following sections:

- *1.1 Precautions* on page 1-11.

- 1.2 About the Musca-B1 test chip and board on page 1-12.

- 1.3 Location of components on page 1-13.

# 1.1 Precautions

This section describes precautions that ensure safety and prevent damage to your Musca-B1 board.

This section contains the following subsections:

- 1.1.1 Ensuring safety on page 1-11.

- *1.1.2 Operating temperature* on page 1-11.

- 1.1.3 Preventing damage on page 1-11.

# 1.1.1 Ensuring safety

The Musca-B1 board operates at 5V supplied through the DAPLink 5V USB connector.

—— Warning ——

Do not use the Musca-B1 board near equipment that is sensitive to electromagnetic emissions, for example, medical equipment.

# 1.1.2 Operating temperature

The Musca-B1 board has been tested in the temperature range 15°C-30°C.

# 1.1.3 Preventing damage

The Musca-B1 board is intended for use within a laboratory or engineering development environment.

### ——— Caution —

To avoid damage to the Musca-B1 board, observe the following precautions:

- Never subject the board to high electrostatic potentials. Observe *ElectroStatic Discharge* (ESD) precautions when handling any board.

- Always wear a grounding strap when handling the board.

- Only hold the board by the edges.

- Avoid touching the component pins or any other metallic element.

- Do not fit an Arduino Expansion Shield while the Musca-B1 board is powered up.

# 1.2 About the Musca-B1 test chip and board

The Musca-B1 board is a development system that demonstrates the foundation of single-chip secure *Internet of Things* (IoT) endpoints.

# Purposes of the Musca-B1 test chip and board

The Arm Musca-B1 board provides access to the Arm Musca-B1 test chip that implements the Arm CoreLink SSE-200 Subsystem for Embedded product.

# Major components and systems

The system enables development and evaluation of custom software on the Musca-B1 test chip. The board and Musca-B1 test chip provide the following main features:

- Musca-B1 test chip that includes, but is not limited to, the following:

- CoreLink SSE-200 subsystem that contains two Arm Cortex-M33 processors.

- Peripheral and Arduino Expansion Shield interfaces.

- On-board DAPLink that provides the following access:

- Serial Wire Debug (SWD).

- USB Mass Storage Device (USBMSD) for uploading new firmware.

- USB serial port. The UART on the Musca-B1 test chip does not support hardware flow control.

- Remote reset.

- On-board:

- 3-axis orientation and motion sensor (gyro sensor).

- Temperature sensor/ADC/DAC.

- Quad Serial Peripheral Interface (QSPI) 8MB boot flash.

- Secure Digital I/O (SDIO) microSD card.

- P-JTAG processor debug and SWD header.

- User RGB LED, status LEDs, user reset, and ON/OFF push buttons.

- The board is powered from USB 5V power or Li-ion rechargeable battery backup, battery not supplied, selectable by a slider switch.

- Headers for Arduino Expansion Shield to support development of custom designs:

- 16 3V3 GPIO.

- UART. No hardware flow control.

- SPI, master only.

- I<sup>2</sup>C, master only.

- I<sup>2</sup>S three-channel, master only.

- 3-channel Pulse Width Modulation (PWM).

- 6-channel analog interface from the on-board combined ADC, DAC, and GPIO.

# **Electrical specifications**

See the *Arm*<sup>®</sup> *Musca-B1 Test Chip and Board Technical Reference Manual* for information on the Musca-B1 board power supply rails and maximum current loads.

# 1.3 Location of components

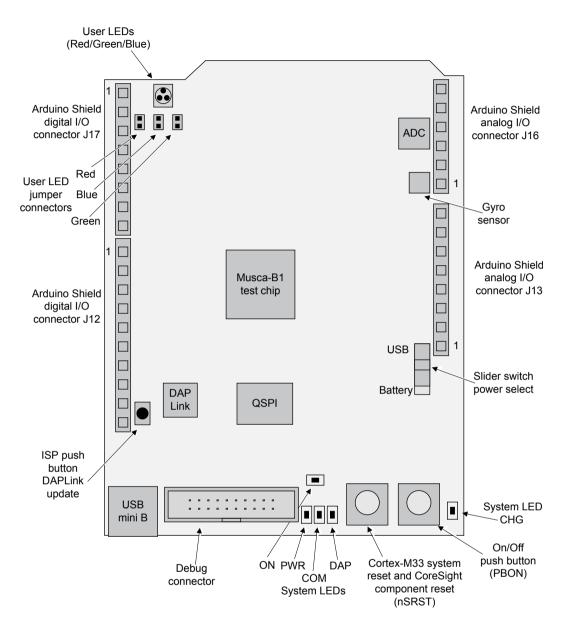

The following figure shows the physical layout of the upper face of the Musca-B1 board.

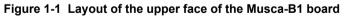

The following figure shows the physical layout of the lower face of the Musca-B1 board.

Figure 1-2 Layout of the lower face of the Musca-B1 board

# Chapter 2 Hardware and software

This chapter gives an overview of the Musca-B1 test chip and Musca-B1 board hardware and software.

It contains the following sections:

- 2.1 Board hardware on page 2-16.

- 2.2 Musca-B1 test chip on page 2-18.

- 2.3 Software, firmware, board, and tools setup on page 2-22.

# 2.1 Board hardware

The hardware infrastructure of the Musca-B1 board provides access to the Musca-B1 test chip and supports Shield expansion.

# Overview of the Musca-B1 board hardware

The Musca-B1 test chip interfaces connect directly between the test chip and the peripheral devices on the board, and between test chip and the Shield header.

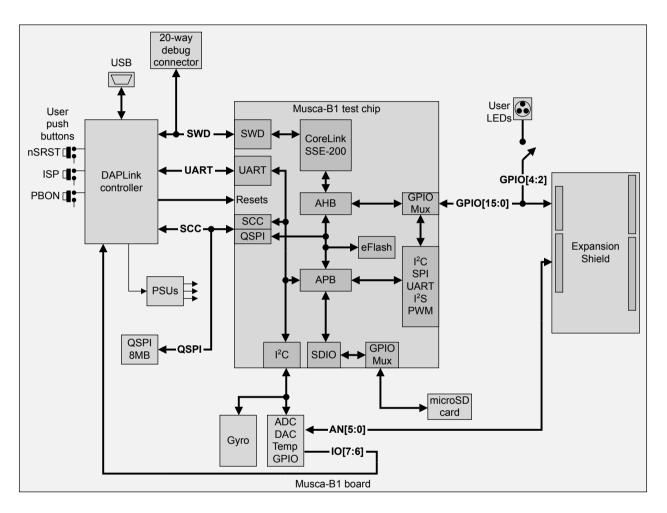

The following figure shows the hardware infrastructure of the Musca-B1 board.

### Figure 2-1 Hardware infrastructure of the Musca-B1 board

# Musca-B1 board components and systems

The Musca-B1 board contains the following components and systems:

- One Musca-B1 test chip that contains a CoreLink SSE-200 Subsystem for Embedded. The SSE-200 subsystem includes, but is not limited to, the following:

- CPU0: One Cortex-M33 processor. Floating Point Unit (FPU), DSP, no coprocessor.

- CPU1: One Cortex-M33 processor. FPU, DSP, no coprocessor.

- Two 2KB instruction caches, one for each processor.

- 4 × 128KB SRAM. One bank of SRAM functions as *Tightly-Coupled Memory* (TCM), Tightly-Coupled to CPU1.

- CryptoCell-312.

- Timer, Watchdog peripherals, and system control.

- Arduino Shield expansion to enable custom designs by providing the following interfaces:

- UART. The UART on the Musca-B1 test chip does not support hardware flow control.

- I<sup>2</sup>S, three-channel, master only.

- SPI, master only.

- I<sup>2</sup>C, master only.

- PWM.

- 6-channel analog interface from the on-board combined ADC, DAC, and GPIO.

- 16 3V3 GPIO.

- On-board DAPLink that enables the following functionality over USB:

- Serial Wire Debug (SWD).

- USB Mass Storage Device (USBMSD) for uploading new firmware.

- USB serial port. The UART on the Musca-B1 test chip does not support hardware flow control.

- Remote reset.

- On-board gyro sensor:

- MMA7660FC 3-axis orientation and motion detection sensor.

- I<sup>2</sup>C interface to Musca-B1 test chip.

- On-board combined ADC/DAC/temperature sensor:

- AD5593.

- 6-channel 3V3 ADC/DAC/GPIO interface to Arduino Shield.

- Temperature indicator.

- Programmable boot select:

- 512KB on-chip system memory SRAM.

- 8MB On-board QSPI boot flash.

- Two 2MB on-chip boot eFlash.

- Both Secure and Non-secure access.

- Debug connector that provides access to:

- P-JTAG processor debug.

- Serial Wire Debug (SWD).

- User push-button:

- PBON On/Off push-button.

- nSRST: Cortex-M33 system reset and CoreSight component reset.

- ISP: Updates DAPLink firmware.

- RGB LED. Jumper connectors provide optional connections between the Arduino Expansion header and the Musca-B1 test chip:

- Red LED connected to GPIO[2] pin, optional PWM0.

- Green LED connected to GPIO[3] pin, optional PWM1.

- Blue LED connected to GPIO[4] pin, optional PWM2.

- Status LEDs.

- 5V USB or battery power, selectable by slider switch:

- DAPLink 5V USB connector.

- CLN 523450, Lithium Ion, 3.7V, 950mAh (not supplied).

See Arm<sup>®</sup> Musca-B1 Test Chip and Board Technical Reference Manual for more information on the Musca-B1 board components and systems.

# 2.2 Musca-B1 test chip

The Musca-B1 test chip is based on the SSE-200 subsystem which features two Cortex-M33 processors.

# Overview of the Musca-B1 test chip

The Musca-B1 test chip features a memory system, integrated connectivity, sensor interfaces, a clock generator, and *Serial Configuration Control* (SCC) registers for setting default powerup values.

See the following documentation for more information on the SSE-200 subsystem:

- Arm<sup>®</sup> CoreLink<sup>™</sup> SSE-200 Subsystem for Embedded Technical Overview.

- Arm<sup>®</sup> CoreLink<sup>™</sup> SSE-200 Subsystem for Embedded Technical Reference Manual.

See the Arm® Musca-B1 Test Chip and Board Technical Reference Manual for more information.

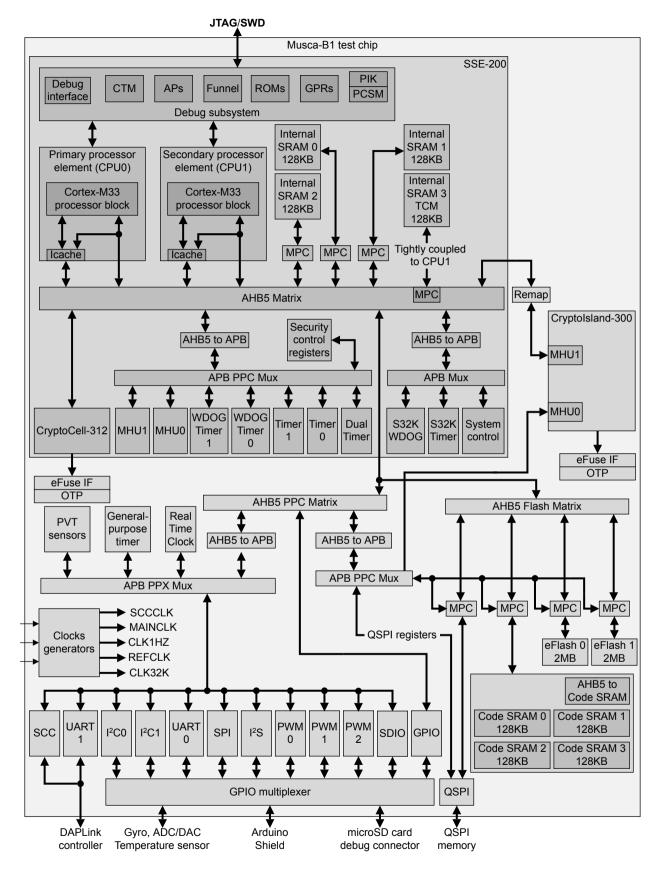

The following figure shows a high-level view of the architecture of the Musca-B1 test chip.

### Figure 2-2 Musca-B1 test chip

# Major components and systems of the Musca-B1 test chip

# SSE-200 subsystem

- Two processors:

- Two Cortex-M33 processors with FPU and DSP, and with no coprocessor:

- CPU0: 40.96MHz maximum. Used as main processor.

- CPU1: 163.84MHz maximum.

- Memory system:

- One 2KB instruction cache for each Cortex-M33 processor.

- 4 × 128KB SRAM. One bank of SRAM functions as *Tightly-Coupled Memory* (TCM), Tightly-Coupled to CPU1.

- CoreSight components, Cross Trigger Interface (CTI), and Serial Wire Debug (SWD).

- Secure AMBA interconnect:

- AHB5 Bus matrix.

- AHB5 Exclusive Access Monitors (EAMs).

- AHB5 Access Control Gates (ACGs).

- AHB5 to APB bridges.

- Expansion AHB5 master and slave buses two of each.

- Security components:

- AHB5 TrustZone® Memory Protection Controllers (MPCs).

- AHB5 TrustZone Peripheral Protection Controllers (PPCs).

- CryptoCell-312.

- Implementation defined Attribution Unit (IDAU).

- Secure and Non-secure configurable peripherals and memory access.

- Secure APB peripherals:

- One general-purpose timer with configurable security in the S32KCLK domain.

- Two general-purpose timers, Timer0 and Timer1 with configurable security, in the SYSCLK domain.

- One Cortex<sup>®</sup>-M System Design Kit (CMSDK) dual timer with configurable security.

- One secure watchdog in the S32KCLK domain.

- One secure watchdog in the SYSCLK domain.

- One Non-secure watchdog in the SYSCLK domain.

### Musca-B1 test chip outside the SSE-200 subsystem

- One CryptoIsland-300 subsystem, a security enclave module used for Secure access control.

64KB RAM.

- Two 2MB Embedded Flash (eFlash) memories.

- 512KB Code SRAM: 4 × 128KB independently power-enabled.

- Two 8KB true One-Time Programmable (OTP) memories:

- One used for CryptoCell-312.

- One used for CryptoIsland-300 secure enclave.

- One Real Time Clock (RTC) in the Always ON domain.

- One 32-bit general-purpose timer running at 32.768kHz with programmable interrupts.

- 16 external GPIO interrupts.

- 16 GPIO.

- Nine Process, Voltage, and Temperature (PVT) sensors:

- 501-stage ring oscillators that perform boot time process measurements. Software can read data from the sensors in the sensor peripheral and group registers.

- Three-channel I<sup>2</sup>S:

- Two master transmitters.

- One master receiver.

- Three independent Pulse Width Modulation (PWM) outputs.

- Two UARTs, UART0 user, UART1 debug. The UART on the Musca-B1 test chip does not support hardware flow control.

- Two  $I^2C$ :

- I<sup>2</sup>C0. Master only.

- I<sup>2</sup>C1. Master only to on-board interfaces.

- One SPI master interface.

- One microSD card I/O (SDIO 3.0):

- Interface width of 4.

- Up to SDR50.

- No DMA support.

- One alternate function I/O multiplexer.

- One QSPI for external flash control with Execute in Place (XIP) capability.

- Programmable boot select:

- eFlash 0 or eFlash 1.

- Code SRAM.

- External QSPI Flash.

- External powerup reset.

- Three system clock sources:

- External **REFCLK**, 32.768kHz.

- External FASTCLK, 24MHz.

- On-chip PLL. Input 32.768kHz. Output up to 40.96MHz to primary processor, CPU0, and 163.84MHz to secondary processor, CPU1.

- One JTAG/SWD debug port.

- One Serial Configuration Controller (SCC) with dual access port:

- SCC serial during reset.

- APB after reset.

# 2.3 Software, firmware, board, and tools setup

Arm supplies software and firmware for the Musca-B1 board.

You can access software and firmware at the Arm Community pages which are accessible from *https://www.arm.com/musca*.

### Setting up a project

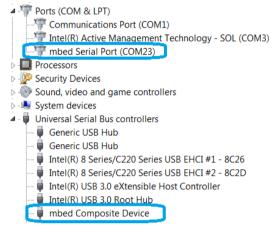

To power the board, connect the USB port to your computer and press the PBON user push button. The DAPLink interface appears in the Windows device manager as an Mbed<sup>™</sup> composite device, part of which is the Mbed serial port, UART. The following figure shows an example configuration that contains the Mbed composite device and the Mbed serial port.

Figure 2-3 DAPLink interface

\_\_\_\_\_ Note \_\_\_\_\_

Other components of the Mbed composite device are not visible in the Windows device manager. See *2.1 Board hardware* on page 2-16 for the other components of the Mbed composite device.

The UART on the Musca-B1 test chip does not support hardware flow control.

# Updating DAPLink firmware

You can update the DAPLink firmware for either QSPI or eFlash. To update the DAPLink firmware, you can use the DAPLink drag and drop update method:

- 1. Press and hold the ISP button while powering up the board using the USB lead.

- 2. Delete the firmware.bin file that appears in the CRP DISABLD USB drive.

- 3. Copy DAPLink\_QSPI\_XTAL\_vxx.bin or DAPLink\_eFLASH\_XTAL\_vxx.bin to the CRP DISABLD drive.

- From a Windows system, you can simply Drag and Drop the file.

- On Linux/Mac OS, use the following command:

dd if={new\_firmware.bin} of=/Volumes/CRP\ DISABLD/firmware.bin conv=notrunc

4. Power cycle the board using the USB lead. Do not press the ISP button during the power cycle.

# Updating the application software image

To update the application image, perform the following steps:

- 1. Power up the board by connecting the USB lead and pressing the PBON button.

- 2. Drop a .bin format software image onto the MBED drive, for example blinky.bin.

- 3. Power cycle the board or press the nSRST button to reset the system and boot from the new QSPI or eFlash software image.

### — Note –

The file blinky.bin is available at the Arm Community pages which are accessible from *https://www.arm.com/musca*.

# DAPLink UART setting

The default DAPLink UART setting is 115,200 baud (8N1).

# Appendix A **Specifications**

See the *Arm<sup>®</sup> Musca-B1 Test Chip and Board Technical Reference Manual* for information on the Musca-B1 board power supply rails and maximum current loads.

# Appendix B **Revisions**

This appendix describes the technical changes between released issues of this book.

It contains the following section:

• *B.1 Revisions* on page Appx-B-26.

# B.1 Revisions

The following table lists the technical changes between released issues of this book.

### Table B-1 Issue 101311\_0000\_00

| Change                     | Location | Affects |

|----------------------------|----------|---------|

| No changes, first release. | -        | -       |

# Table B-2 Differences between issue 101311\_0000\_00 and issue 101311\_0000\_01

| Change                                                                   | Location                                                    | Affects            |

|--------------------------------------------------------------------------|-------------------------------------------------------------|--------------------|

| Added CryptoIsland-300 RAM size.                                         | 2.2 Musca-B1 test chip on page 2-18                         | All board versions |

| Corrected CPU0 and CPU1 maximum operating frequencies.                   | 2.2 Musca-B1 test chip on page 2-18                         | All board versions |

| Added information on how to update DAPLink firmware from a Linux/Mac OS. | 2.3 Software, firmware, board, and tools setup on page 2-22 | All board versions |

# Table B-3 Differences between issue 101311\_0000\_01 and issue 101311\_0000\_02

| Change                            | Location                      | Affects            |

|-----------------------------------|-------------------------------|--------------------|

| Updated CE Conformance Notice.    | Conformance Notices on page 3 | All board versions |

| Removed trace debug from document | Throughout document           | All board versions |