# TRUSTED BASE SYSTEM ARCHITECTURE, CLIENT (4TH EDITION)

# System Hardware on ARM®

Document number: ARM DEN 0021D

Copyright © 2012, 2016, 2018, ARM Limited or its affiliates

# Trusted Base System Architecture, Client (4th Edition) System Hardware on ARM

Copyright © 2012, 2016, 2018, ARM Limited or its affiliates. All rights reserved.

#### Release information

Table 1 lists the changes made to this document.

**Table 1 Change history**

| Date              | Issue | Confidentiality  | Change                                                                  |

|-------------------|-------|------------------|-------------------------------------------------------------------------|

| 20 January 2012   | Α     | Confidential     | First release                                                           |

| 21 March 2012     | В     | Confidential     | Second release                                                          |

| 26 September 2016 | С     | Confidential     | 3 <sup>rd</sup> Edition. Update and restructure document. Draft release |

| 15 October 2018   | D     | Non-Confidential | 4 <sup>th</sup> Edition. Non-confidential release.                      |

Intermediate releases, numbered A-3 to A-9, were issued to a restricted circulation

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there

is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or ™ are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at <a href="http://www.arm.com/company/policies/trademarks">http://www.arm.com/company/policies/trademarks</a>.

Copyright ©2018 Arm Limited (or its affiliates). All rights reserved. Arm Limited. Company 02557590 registered in England. 110 Fulbourn Road, Cambridge, England CB1 9NJ. LES-PRE-20349

# **Table of contents**

| 1    | Intro                           | duction                                                | 6            |

|------|---------------------------------|--------------------------------------------------------|--------------|

|      | 1.1<br>1.2                      | Additional reading  Target platform                    |              |

| 2    | Use                             | cases                                                  | 8            |

|      | 2.1<br>2.2<br>2.3<br>2.4<br>2.5 | User privacy                                           | 9<br>9<br>10 |

| 3    | _                               | ırity threats                                          |              |

| •    | 3.1<br>3.2                      | ThreatsAttackers                                       | 12           |

| 4    | Trus                            | tZone® technology                                      | 16           |

|      | 4.1<br>4.2                      | Execution model                                        | 17           |

| 5    | TBS                             | A architecture variants                                | 20           |

|      | 5.1<br>5.2                      | Baseline architecture                                  |              |

| 6    | TBS                             | A security requirements                                | 23           |

|      | 6.1<br>6.2<br>6.3               | System viewInfrastructure                              | 23           |

|      | 6.4                             | Cryptographic keys                                     | 33           |

|      | 6.5<br>6.6                      | Trusted boot  Trusted timers                           | 39           |

|      | 6.7<br>6.8                      | Version counters Entropy source                        |              |

|      | 6.9                             | Cryptographic acceleration                             |              |

|      | 6.11                            | Debug  External interface peripherals  DRAM protection | 51           |

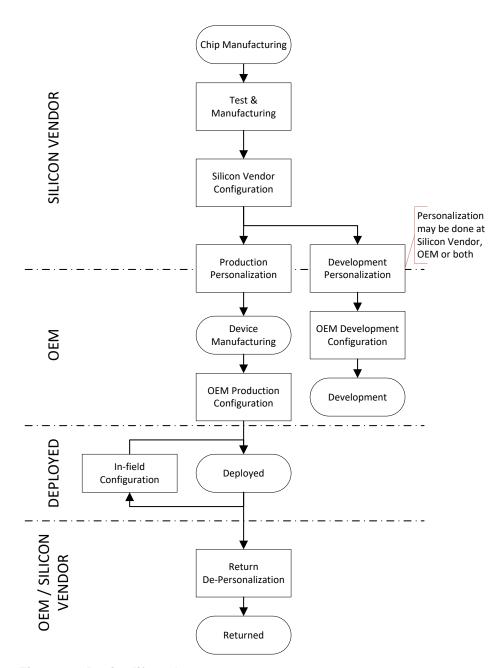

| 7    | Devi                            | ce lifecycle                                           | 57           |

| 8    |                                 | roved algorithms                                       |              |

| Glos | ssarv                           |                                                        | 60           |

|      | ,                               |                                                        |              |

#### 1 Introduction

This document presents a *System-on-Chip* (SoC) architecture that incorporates a trusted hardware base suitable for the implementation of systems compliant with key industry security standards and specifications, in particular those dealing with third party content protection, personal data, and second factor authentication. The architecture is founded on ARM TrustZone® technology, which provides isolation between the Trusted and Non-trusted worlds. This document includes an overview of TrustZone technology to give the necessary context.

The goal of the TBSA is to create a platform that supports Trusted Services. Trusted Services are defined as collections of operations and assets that require protection from the wider system, and each other, to ensure their confidentiality, authenticity, and integrity.

A description of each target use case is provided together with a list of the assets to be protected and protection mechanisms needed. Threats and the capabilities of attackers are then discussed before presenting suitable security architectures and detailed implementation requirements.

This document aims to provide information that is useful to the designers and implementers of such platforms. However, this document does not replace the need for thorough security analysis during the system design.

### 1.1 Additional reading

This section lists publications by ARM and by third parties.

See the ARM Infocenter, <a href="http://infocenter.arm.com/">http://infocenter.arm.com/</a>, for access to ARM documentation.

#### 1.1.1 ARM publications

The following documents contain information relevant to this document:

- [1.] ARM® Security Technology Building a Secure System using TrustZone® Technology (PRD29-GENC-009492)

- [2.] ARMv8-A Architecture Reference Manual (ARM DDI 0487)

- [3.] ARM® Trusted Board Boot Requirements (ARM DEN 0006)

- [4.] ARM® Trusted Firmware https://github.com/ARM-Software/arm-trusted-firmware

#### 1.1.2 Other publications

The following documents list relevant documents published by third parties:

- [5.] NIST Draft Special Publication 800-90b http://csrc.nist.gov/publications/drafts/800-90/draft-sp800-90b.pdf

- [6.] NIST Special Publication 800-22rev1a: A Statistical Test Suite for the Validation of Random Number Generators and Pseudo Random Number Generators for Cryptographic Applications http://csrc.nist.gov/groups/ST/toolkit/rng/documents/SP800-22rev1a.pdf

- [7.] Commercial National Security Algorithm Suite (superseding NSA Suite B Cryptography)

https://apps.nsa.gov/iaarchive/programs/iad-initiatives/cnsa-suite.cfm

- [8.] SEC Recommended Elliptic Curve Domain Parameters http://www.secq.org/sec2-v2.pdf

- [9.] GlobalPlatform TEE Protection Profile Specification v1.2 http://www.globalplatform.org/specificationsdevice.asp

#### 1.2 Target platform

The target platforms addressed by this document are primarily, but not limited to, portable cellular handsets, mobile internet devices and PayTV systems. These platforms have the following features:

- They implement a feature-rich operating system (ROS) that is capable of executing user downloaded third party applications. The environment in which the ROS executes is referred to as the rich execution environment (REE).

- They support online and over-the-air firmware updates.

- They might support audio and video playback and, in the case of third party premium content, they will be required to support and comply with digital rights management (DRM) technology.

- They might act as security tokens that support strong second factor authentication.

It is expected that suitable platforms will utilize the following SoC technology:

- The ARMv8-A architecture or higher with Security Extensions (aka TrustZone).

- On chip peripherals supporting data entry, for example keyboard, touch pad, finger print sensor.

- Video display and audio output.

- One or more integrated DRAM controllers and interfaces to support a large shared memory pool.

- A controller and interface supporting external non-volatile bulk storage, for example flash memory.

- Wired or wireless internet connectivity.

In addition, a SoC that targets mobile applications will require a high degree of power control and is therefore likely to embed an advanced power control subsystem to meet its power targets.

There is a wide diversity of platforms and products that are within the scope of this document. The resulting collection of use cases, assets, threats, and necessary security measures cannot be reduced to a single, simple checklist of security requirements. Each platform and product requires specific analysis to determine the appropriate use of security features, and will need to consider the specification and certification requirements of the target market.

Attacks on systems always get better, with the effect that old security defenses need to be strengthened and new security defenses need to be implemented to maintain the required level of security. The requirements described in this document represent best practice at this point in time. Some requirements significantly raise the bar in comparison with previous versions of this document and the *ARM® Trusted Board Boot Requirements* (TBBR) [3.]. In all cases, the differences are in the degree of security provided, or demanded by other market specifications: the newer requirements described here are more resilient to certain types of attack.

#### 2 Use cases

The use cases that follow are implemented within and therefore rely on *Trusted Services*, which typically run on top of a trusted kernel, for example a *Trusted Execution Environment* (TEE). A Trusted Service must be securely loaded by the trusted kernel while the kernel must first be securely loaded itself. The resulting architecture therefore chains together a series of software modules, each verifying the next in a chain of trust, starting from the secure boot of the SoC.

The secure boot of the device, which forms the beginning of the chain of trust, is rooted in the SoC hardware and based on an embedded ROM. Following a system reset, the processor core boots into Secure state and executes the ROM code. The ROM contains code that verifies that the next stage boot code is permitted to execute. The next stage boot code is responsible for verifying that the boot code for the following stage is permitted to execute, and so forth. Code verification is performed using public key cryptography and requires a root certificate that is embedded in the SoC, either in the ROM, or in on-chip non-volatile storage. For further information, see the TBBR specification [3.].

A further core component of the following use cases is the functionality that is required to securely install a system update delivered over the network to the device. Such an update must be checked for integrity and authenticity before it is applied, which also relies on a root of trust.

The following subsections outline the use cases targeted by this specification. For each use case, the following information is provided:

- An overview of the use case.

- A list of primary assets.

- The protection mechanisms that are required.

**Note:** A root key that is needed to protect an asset is an asset in itself. It is, however, an implied asset, not a primary asset, and therefore not listed in the asset table.

#### 2.1 User privacy

A common requirement of modern devices is the protection of user and application data against malicious access. This requires one or more Trusted Services to be available on the device to provide isolation from other applications and guarantee confidentiality, authenticity, and integrity of the assets.

The end solution demands a robust secure platform and often incorporates features such as a password or biometrically protected screen lock, disk encryption, and remote wipe.

To protect data against malicious access, devices must protect the following assets:

| Assets                | Authenticity | Integrity | Confidentiality |

|-----------------------|--------------|-----------|-----------------|

| Generic user data     |              | ✓         | ✓               |

| Biometric sensor data |              | ✓         | ✓               |

| Application data      | <b>✓</b>     | ✓         | ✓               |

Protection of these assets relies on an underlying root of trust that supports:

- Secure provisioning.

- Secure persistent storage.

- A persistent counter or counters.

- A secure application environment that provides memory protection to isolate code and data from the REE and other applications.

A secure application loading mechanism.

### 2.2 Digital Rights Management

Digital rights management (DRM) systems are responsible for ensuring the legitimate playback of stored or streamed media, primarily video and audio content. The right to play the content is determined by referring to an associated certificate that is purchased by the end user, and issued by a trusted authority. The certificate contains rights information concerning factors such as: legitimate decoder devices, legitimate display devices, the display resolution, legitimate users, the number of views, and the content lifetime.

DRM implementations differ from traditional PayTV systems in that they do not use an external smart card to generate content decryption keys. Instead, they rely on a secure software stack running in a protected computing environment which is responsible for generating the content decryption key. This environment constitutes a trusted service environment, and one particular embodiment would be a suitable TEE implementation which maps the DRM stack onto a TA.

DRM systems must protect the following assets:

| Assets                                            | Authenticity | Integrity | Confidentiality |

|---------------------------------------------------|--------------|-----------|-----------------|

| License keys, intermediate keys, and certificates | <b>✓</b>     | <b>√</b>  | ✓               |

| Content keys                                      |              | ✓         | ✓               |

| Secure time                                       | ✓            | ✓         |                 |

| Identification credentials                        | ✓            | ✓         |                 |

| Secure version                                    | ✓            | ✓         |                 |

| The DRM stack                                     | <b>✓</b>     | ✓         | ✓               |

| The content                                       |              |           | ✓               |

Protection of these assets relies on an underlying root of trust that supports:

- Secure provisioning.

- Secure persistent storage, accessible only by the DRM stack.

- A persistent counter or counters.

- A secure timer.

- A secure application environment that provides memory protection to isolate code and data from the REE and other applications.

- A secure application loading mechanism.

#### 2.3 FIDO

The Fast IDentity Online (FIDO) Alliance is an industry consortium that was formed to accelerate the adoption of strong online authentication via standardization. The consortium has developed the following:

Universal 2nd Factor (U2F) Authentication - A system that augments current webbased password security with a second factor in the form of a token. Universal Authentication Framework (UAF) - A password-less authentication system

that unlocks a key held in a token based on biometric input such as a fingerprints,

pictures, etc.

In both cases, the token holds a secret key and offers the associated cryptographic services that are required by the online authentication protocol. One of the most commonly available form factors is a USB key with an embedded secure microprocessor. However, the FIDO token technology can also be embedded into portable consumer devices, such as mobile phones.

A FIDO implementation must protect the following assets:

| Assets                | Authenticity | Integrity | Confidentiality |

|-----------------------|--------------|-----------|-----------------|

| The secret key(s)     |              | ✓         | ✓               |

| Token counter(s)      | ✓            | ✓         |                 |

| A unique identifier   |              | ✓         |                 |

| Biometric sensor data |              |           | ✓               |

| The software stack    | ✓            | ✓         | ✓               |

Protection of these assets relies on an underlying root of trust that supports:

- Secure provisioning.

- Secure persistent storage to hold a secret key or keys, accessible only by the software stack.

- Dedicated access to biometric inputs.

- A persistent token counter or counters.

- A secure application environment that provides memory protection to isolate code and data from the REE and other applications.

- A secure application loading mechanism.

## 2.4 Enterprise system support

Mobile devices that operate in a corporate environment are expected to support the following security features:

- Authentication of the device and user, based on provisioned keys.

- Disk and/or file encryption, using a unique device secret.

- Malware protection, using verified runtime software.

- Remote wipe, which is activated if the device is stolen.

Traditionally, these devices would be owned by a corporation and they would be dedicated to corporate use. However, a use case that has become increasingly popular is "bring your own device" (BYOD), where corporate services are installed on a device owned by the employee. This use case adds additional complexity because it mixes user data and apps with corporate data and apps and therefore demands a method to provide isolation between the two, which can be achieved by one of the following methods:

- Implementing specific kernel functionality.

- A second OS that uses, for example, an underlying hypervisor.

A trusted services environment that uses, for example, a TEE.

Implementations that isolate user data from corporate data must protect the following assets:

| Assets                                                        | Authenticity | Integrity | Confidentiality |

|---------------------------------------------------------------|--------------|-----------|-----------------|

| Provisioned keys for authentication and encryption/decryption |              | ✓         | ✓               |

| Device and user identity                                      |              | ✓         |                 |

| Corporate code and data                                       | ✓            | ✓         | ✓               |

Protection of these assets relies on an underlying root of trust that supports:

- Secure provisioning.

- · Secure persistent storage.

- A persistent counter or counters.

- A secure timer.

- A secure application environment that provides memory protection to isolate code and data from the REE and other applications.

- A secure application loading mechanism.

# 2.5 Mobile Network Operators

Devices that interact with mobile networks establish secure connections using protocols that rely on embedded keys.

To be able to use embedded keys, an implementation must protect the following assets:

| Assets                         | Authenticity | Integrity | Confidentiality |

|--------------------------------|--------------|-----------|-----------------|

| Embedded Keys                  |              | ✓         | ✓               |

| A unique identifier, e.g. IMEI |              | <b>√</b>  |                 |

| The software stack             | ✓            | ✓         | ✓               |

Protection of these assets relies on an underlying root of trust that requires:

- Secure persistent storage, accessible only by the software stack.

- A secure application environment that provides memory protection to isolate code and data from the REE and other applications.

- A secure application loading mechanism.

# 3 Security threats

The goal of this specification is to protect the Trusted Services that run on the device from attackers who would benefit from their compromise. The chapter on use cases outlined examples of the Trusted Services, their assets and the type of protection they require: authenticity, integrity and confidentiality.

No security implementation can be perfect and so the goal must be to make attacks too costly with respect to time and money to be feasible in the real world. This chapter outlines the main threats that TBSA aims to protect against and the capabilities of the attackers performing the attacks. TBSA does not aim to protect against all types of attack and a TBSA device might need to meet stricter security requirements depending on its target market.

TBSA cannot prevent the non-trusted world from being compromised, nor can it prevent phishing attacks. For example, it is possible for malware, executing in the REE, to attempt to acquire sensitive user information by pretending to be a trustworthy entity.

#### 3.1 Threats

It must be assumed that every interaction from outside of a Trusted Service might be malicious and a threat. This section draws out the primary threats to aid the rationale of the security requirements later in the document.

#### 3.1.1 T.FUNC ABUSE - Functional abuse

Abusing the functionality of the Trusted Service by providing ill-formed interactions, through APIs or physical interfaces, can compromise the integrity of the Trusted Service. By compromising the integrity of the Trusted Service any assets directly accessed by the Trusted Service are also compromised.

This is a very broad threat surface as the interfaces to a Trusted Service can be quite complex. Examples of potential attack routes are:

- · Buffer overflow attacks

- Invalid command sequences

- Hidden commands

- Undefined commands

- Incorrect commands

- System resets during commands

- Exploitation of context switching, for example a poor implementation might not clear all previous state.

#### 3.1.2 T.CLONE - Trusted Service cloning

Most Trusted Services must be device specific as they are working on behalf of a single user. If a Trusted Service can be cloned to run on multiple devices, the Trusted Service cannot be guaranteed to be linked with the user.

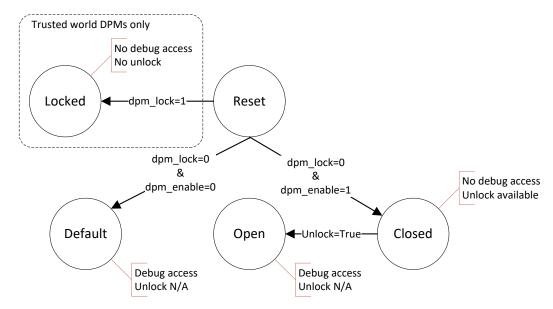

#### 3.1.3 T.DEBUG ABUSE - Debug feature abuse

Devices contain many debug and test features that can be misused to compromise the assets of a Trusted Service when the service is running or dormant. Depending on the access and features of the debug functionality, the integrity and confidentiality of the assets might be compromised.

#### 3.1.4 T.NVS.READ - Reading of non-volatile storage (Flash/HDD)

If the plaintext code or data for a Trusted Service can be retrieved from NVS then its confidentiality has been breached. Often the data would contain assets of value but an analysis of the code can reveal further, more serious, vulnerabilities to the Attacker.

#### 3.1.5 T.NVS.WRITE - Writing to non-volatile storage (Flash/HDD)

It is expected that the REE, or an external attacker, will be able to write to the system non-volatile storage and so the threats resulting from this must be considered. Any assets stored in NVS related to the Trusted Service can be tampered with by the REE. The assets might be corrupted to attempt to produce undesired behavior in the Trusted Service or the assets might be replaced with valid assets from another device (or from a previous image for the same device). In either case the authenticity of the Trusted Service is compromised if these images are accepted.

#### 3.1.6 T.RAM.READ - Reading of Trusted Service RAM

If the Trusted Service RAM contents can be read, the confidentiality of any assets within that space will be compromised. The breach does not have to cover the entire Trusted Service RAM space for the threat to be serious; if the code region is breached, the cleartext version of the encrypted flash image is readable and any security vulnerabilities can be detected using code analysis.

#### 3.1.7 T.RAM.WRITE - Writing to Trusted Service RAM

If the Trusted Service RAM can be modified, the integrity of any assets in that space will be compromised, even if they cannot be read. The operation of the Trusted Service could be modified through code or data regions to leak other assets. An advanced form of this attack could introduce faults into cryptographic operations to enable the attacker to perform Differential Fault Analysis, permitting the asset to be extracted.

#### 3.1.8 T.COVERT\_PATH - Covert leakage paths

The Trusted Service can leak information via unconventional paths during its operation; e.g. timing of operations might reveal information on the assets that are used. If the memory is not cleared after the Trusted Service is shutdown, assets can be accessible to the REE. Undocumented error codes can reveal operational information, this can be particularly powerful when combined with fault-injection techniques such as T.RAM.WRITE.

#### 3.1.9 T.ROLLBACK - Rollback to previous versions of code/data

Trusted Services require that when a new firmware containing a security fix is issued, the previous version cannot be used. If the image can be rolled back, the vulnerability can still be exploited. In a similar manner, if the data assets of a Trusted Service can be rolled back to an earlier version, the integrity of the Trusted Service has been compromised.

Secure Time required by some Trusted Services might also be vulnerable to a roll back attack that enables a user to perform actions beyond a specified expiry time.

#### 3.2 Attackers

When considering the threats and attacks on a system, it is widely recognized that these must be divided into two phases: identification and exploitation.

The identification phase requires an attacker to discover a vulnerability and create an exploit to gain access to an asset, which can take the form of access to a higher-privilege execution level, access to protected content, or access to a cryptographic key.

In the exploitation phase, the exploit is executed on one or more devices by the same or different attackers. If different attackers are performing the exploit, it is expected that the identification phase attacker has prepared the exploit as either a set of detailed instructions or a piece of software.

A security implementation must consider both phases. Due to the complexity of modern devices, there is a high probability that functional bugs will exist and these can give rise to vulnerabilities. The system should be designed to resist widespread exploitation because this form of attack is often the most damaging to the asset owners.

Assuming that the identification phase attacker has full access to the device, they can use all of the normal interfaces, for example touch screen, keyboard, buttons, non-volatile storage port, and audio and video ports. They might also perform partial disassembly of the

device to access any engineering interfaces that are covered by the casing, for example jumpers and JTAG connectors. The attacker might also use any wireless connections to breach the device, for example Wi-Fi, Bluetooth, RF, and IR.

Attacks that require probing, modifying the PCB itself, or breaching the package of the SoC are out-of-scope of TBSA.

#### 3.2.1 Identification phase

Attackers that are capable of identifying a vulnerability are generally considered to have more expertise than those that use the exploitation phase as they might have software and hardware skills along with access to equipment such as JTAG debuggers, oscilloscopes and logic analyzers.

| Attacker         | Description                                                                                                                                                                   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Basic User       | The device user could find and implement the attack using the standard user interface.                                                                                        |

| Adept            | The attacker is capable of writing custom software, connecting to PCB connectors inside the device packaging, and applying knowledge of the security functions of the device. |

| Expert           | The attacker is familiar with numerous attack methods and the underlying cryptographic principles and methods employed by the device.                                         |

| Multiple Experts | The exploit requires experts from different fields of expertise.                                                                                                              |

#### 3.2.2 Exploitation phase

If the exploit discovered in the identification phase reveals a class-breaking asset, for example a content master key, then often no further actions are required. However, in most cases the exploit must be repeated on each device. Because the 'hard' work of discovering the vulnerability and creating the exploit has already been done, the skills of the attacker in the exploitation phase are often lower.

| Attacker     | Description                                                                                                                                                                                               |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Remote       | An attacker can perform the exploit remotely. The skill to do this might be "Expert" but the ability to perform the exploit remotely ranks it before "Basic User".                                        |

| Basic User   | The exploit can be simply performed by the device user using software that was either downloaded to the device, or downloaded to a PC connected to the device using a standard user-accessible interface. |

| Adept        | The exploit requires an attacker who can dismantle the device and utilize connectors and settings within the device.                                                                                      |

| Professional | The exploit requires an attacker with the skills and resources of a backstreet shop. The device might be dismantled and the PCB modified.                                                                 |

| Expert       | The exploit requires an attacker with capabilities of an Identification Phase Expert or above and laboratory-like equipment.                                                                              |

#### 3.2.3 Access to devices

During the identification phase, the attacker might need access to more than one device, either to compare the operations of the devices, or because a device might be damaged by the attack. How easy it is for an attacker to acquire multiple devices must be considered.

The properties of the devices must be considered too. For example, if the identification phase requires development parts that do not have all the security protections activated, the difficulty of acquisition is increased accordingly.

#### 3.2.4 Equipment

Many consumer devices include a method of linking with a PC, for example a USB connection. This is an example of simple equipment that any attacker who is local to the device would have.

Beyond this, an attacker might utilize more specialized equipment that can be acquired easily and relatively inexpensively acquired. Examples of these are JTAG interface controllers, soldering irons and oscilloscopes.

To perform the most sophisticated attacks an attacker might require expensive laboratory-like equipment or software that must be specifically developed.

#### 3.2.5 Scoring

The difficulty of an attack is evaluated based on the profiles outlined above and gives a numeric score. A detailed scoring scheme is outside the scope of this document, but a well-known example of this type of scoring system is the Attack potential rating derived from the Common Criteria, which is applied in the *GlobalPlatform TEE Protection Profile* [9.].

# 4 TrustZone® technology

Over recent years, driven by consumer demand, the complexity of embedded devices has increased dramatically and this trend is set to continue. While in the past it was common to implement closed software running on a bespoke operating system, this approach is no longer economically scalable and is now the exception rather than the rule. Today most devices demand an operating system with a rich feature set and this has driven the adoption of solutions such as Linux and Android. However, these rich operating systems (ROS) have a far larger footprint than their predecessors, and, given that the number of potential security bugs increases with the number of lines of code, the threat surface is also increased. Moreover, with the widespread deployment of app stores and third party app support the threat surface is extended significantly, as such malware is now a real threat to mobile devices. In addition, when premium content is delivered to a device, which is increasingly common, the user himself is a potential threat as he might attempt to circumvent protection mechanisms to receive free content or services.

To combat these new threats, a robust platform architecture is needed. The architecture must be able to provide a trusted environment that is isolated and protected from the ROS. TrustZone technology supports this requirement by providing a binary partition that divides the system into two isolated worlds.

- Trusted world: This partition is intended to encapsulate and protect all high value

assets including code, data and any hardware assets (such as peripherals) that

need to be protected against malicious attack. Access to these assets is restricted

to Trusted world software and hardware. However, software running in the Trusted

world has the right to access assets in the Non-trusted world.

- Non-trusted world: This partition is intended to support the execution of the ROS, the assets contained are deemed to have a security value that is lower than those placed in the Trusted world. Access to these assets is permitted for both Trusted and Non-trusted software and hardware.

TrustZone technology lies at the heart of the ARM processor core. While it is executing code, the processor core can operate in one of two possible states, which correspond to the Trusted and Non-trusted worlds and are known as the Secure and Non-secure states, respectively. Context switches between Security states can only be made using dedicated instructions and code that ensures that strict isolation is maintained. The context switch mechanism enforces fixed code entry points and ensures that code running in the Non-secure state cannot access registers that belong to the Secure state. Conceptually, the Secure and Non-secure states can be regarded as two virtual processor cores.

When the ARM processor performs a memory access, the MMU translation provides an extra bit that indicates the security state that is associated with the transaction. When this bit is high, it indicates a *Non-secure* (NS) transaction. The mechanism is tightly coupled to the cache and consequently an NS bit is stored in every cache line.

When a memory access reaches the external bus, the NS bit from the cache is translated into two transaction bits: one NS bit for reads and one NS bit for writes. The on-chip interconnect must guarantee that these bits are propagated to the target of the access, and the target must determine from the address and NS bits if the access is to be granted or denied. The NS bit is considered to be an extra address bit that is used to access the Secure and Non-secure worlds as completely independent address spaces.

By propagating the security state of the processor core through the on-chip interconnect to target based transaction filters, the TrustZone technology is extended into the SoC architecture, creating a robust platform supporting fully isolated Trusted and Non-trusted worlds.

TrustZone technology is also implemented in many other ARM IP components, for example debug subsystems and memory transaction filters.

Later sections describe the architecture of the SoC hardware that provides such a trusted system.

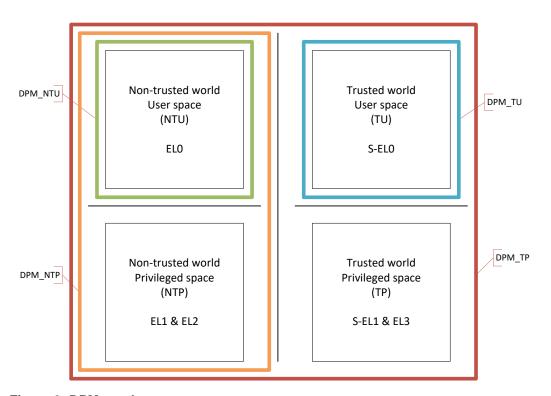

#### 4.1 Execution model

The overview of the TrustZone technology presented a binary division of the processor core state and the resources into two worlds, a Trusted and a Non-trusted world. However, in the in the ARMv8-A architecture, additional privilege levels provide support for the traditional user/supervisor (unprivileged/privileged) separation that a modern ROS expects, as well as support for the virtualization layer introduced in the ARMv7-A architecture.

These distinct levels of separation are referred to as Exception levels in the ARMv8-A architecture and are denoted EL0 to EL3, EL0 being the lowest privilege level and EL3 the highest. Execution can move between Exception levels only on taking an exception, or on returning from an exception:

- On taking an exception, the Exception level either increases or remains the same. The Exception level cannot decrease on taking an exception.

- On returning from an exception, the Exception level either decreases or remains the same. The Exception level cannot increase on returning from an exception.

The resulting Exception level, is called the target Exception level of the exception:

- Every exception type has a target Exception level that is either implicit in the nature of the exception, or defined by configuration bits in the System registers.

- An exception cannot target the EL0 Exception level.

As previously described, the ARM processor core also executes in one of two Security states, called Secure and Non-secure. As a result, exception levels and privilege levels are defined within a particular Security state. The following table summarizes the situation:

| EL\Security-state | Non-secure                                                                     | Secure                                                                 |

|-------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------|

| 0                 | Name: ELO (unprivileged) Runs: User space (ROS) World: Non-Trusted             | Name: S-EL0 Runs: Trusted Application World: Trusted                   |

| 1                 | Name: EL1 Runs: Kernel space (ROS) World: Non-Trusted                          | Name: S-EL1 Runs: TEE World: Trusted                                   |

| 2                 | Name: EL2 Runs: Hypervisor space for virtualization support World: Non-Trusted | NA                                                                     |

| 3                 | NA                                                                             | Name: EL3 Runs: Monitor code for security state control World: Trusted |

- EL0 and EL1 provide the traditional user/supervisor separation for a ROS executing in the Non-trusted world.

- In order to support a Trusted world kernel implementation having a traditional user/supervisor separation, for example a TEE and associated TAs, both EL0 and EL1 are supported within the Secure state. These levels are referred to as S-EL0 and S-EL1, respectively.

- EL2 provides support for virtualization and is the level at which the associated hypervisor executes. It exists within the Non-secure state and consequently the Nontrusted world.

EL3 has the highest privilege level and exists within the Secure state and consequently the Trusted world. It provides support for a monitor mode. Monitor code executing in EL3 is responsible for managing the security state transitions at lower privilege levels.

#### 4.2 Memory access

An important property of a TrustZone system is that a Trusted service can access both Secure and Non-secure memory. To achieve this, two possible approaches are evident:

- A Trusted service can issue either Secure or Non-secure memory transactions, and the transaction filters only permit a Secure transaction to access Secure memory. A Secure transaction cannot access Non-secure memory. This is the recommended approach.

- A Trusted service always issues Secure memory transactions and the transaction filters permit a Secure transaction to access any memory, Secure or Non-secure. This approach has been implemented in legacy systems but is no longer recommended by ARM.

**Note:** In both cases a Non-secure memory transaction is only permitted to access Non-secure memory, it is never possible for a Non-secure transaction to access Secure memory.

Approach (2) leads to aliased entries in the cache and TLBs, and can cause coherency and security problems, and ARM recommends using approach (1) instead of approach (2).

When using approach (1), software executing in a Secure state that wants to access Non-secure memory must issue Non-secure memory transactions, by means of translation table control flags.

The security state of each memory transaction is propagated with each access, and used to tag cache lines. It exists at all stages of the memory hierarchy up to the final access control filter. At the SoC interconnect level, it is propagated in the form of the tag bits previously described, which effectively creates two address spaces, one for Trusted and one for Nontrusted.

When the processor is in the Non-secure state (EL2, EL1, or EL0), all memory transactions are Non-secure.

When the processor is in the Secure state (EL3, S-EL1, or S-EL0), the security state of memory transactions is determined as follows:

- If the MMU is enabled, the security state of memory transactions can be determined

by attributes in the translation table. Consequently, a Trusted kernel in S-EL1 can

provide mappings that send Secure or Non-secure memory accesses into the

memory system.

- If the MMU is disabled, Translation tables are not utilized, and all Secure state accesses default to Secure transactions on the bus.

The processor core integrates an internal configuration bit that is held in the *Security Configuration Register* (SCR), which determines the security state of levels below EL3. This bit can only be updated in EL3. In the 64-bit architecture (AArch64), it is referred to as SCR\_EL3.NS, when high a Non-secure state is indicated.

Transitions between the two Security states are managed by a dedicated software module called the Secure Monitor, which runs in EL3. The Secure Monitor is responsible for providing a clean context switch and must therefore support the safe save and restore of processor state, including the content of registers, while maintaining isolation between the two worlds.

A Secure Monitor Call (SMC) instruction is used to enter EL3 and safely invoke the Secure monitor code. Because this instruction can only be executed in privileged mode, a user process that requests a change from one world to the other must do so using an SVC instruction, which is usually done via an underlying OS kernel. Furthermore, an SMC can optionally be trapped by EL2, and prevent even the OS kernel (EL1) from directly invoking the Secure Monitor (EL3).

Interrupts and exceptions can also be configured to cause the processor core to switch into EL3. Independent exception and vector tables support this functionality.

#### 5 TBSA architecture variants

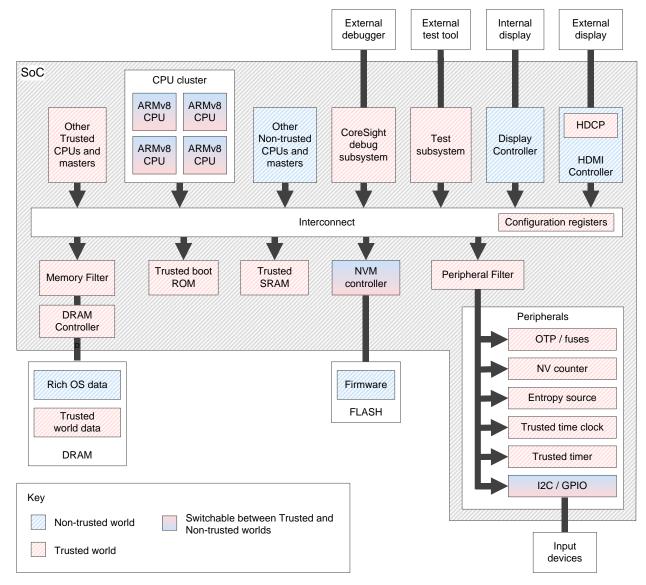

A typical SoC architecture based on TrustZone technology is shown in Figure 1. The processor cluster is supported by a number of security hardware IPs that utilize TrustZone technology, such as the NS-bit, to work within the Trusted world.

Figure 1 TBSA SoC architecture

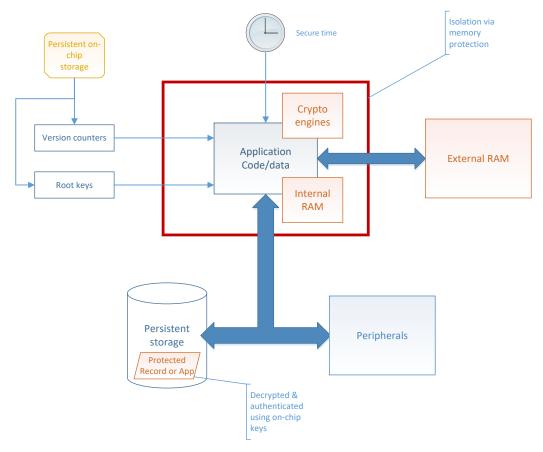

The Trusted world software and security hardware together implement the protection mechanisms required for the use cases in section 2. Figure 2 shows an example implementation.

Figure 2 Example protection mechanisms

Memory protection is used to isolate the target application from other applications at runtime by providing a partitioning of internal and external memory into the Trusted and Non-trusted worlds. The partitioning is achieved using NS bit target based filtering. The configuration must be performed by a trusted agent where the trusted agent itself forms part of the chain of trust that begins with the Secure boot of the device using an on-chip key.

**Note:** Further partitioning of the Non-trusted world can be achieved using NSAID filtering or through a hypervisor and associated MMUs. These techniques are outside the scope of TBSA; For more information, see the relevant ARM documentation.

The critical resources of the protected application are its code and associated data, which includes cryptographic certificates and keys, but which can also include physical interfaces. Resources can be loaded into internal or external memory, or can be stored in Secure persistent external memory, for example flash memory. In the latter case the data must be encrypted and saved along with an authentication tag or signature so that it can be verified when read back.

Decryption and authentication of persistent external data (including code) must be dependent on chip root keys, which are typically stored in non-volatile OTP memory that is programmed during manufacture. In addition, to prevent replay or roll back attacks, each application needs a non-volatile version counter. .

A common requirement of many applications is secure time, which requires a permanently powered hardware timer that is securely loaded with a time stamp that is provided by the network.

This specification considers two architectures for a TrustZone based system: "Baseline" and "Assisted". These architecture variants might impose different requirements on the security features that are described later in this document.

#### 5.1 Baseline architecture

The Baseline Architecture performs the majority of the security functions within Trusted world software on the Processor cluster. It is supported by a minimum set of required security hardware, for example:

- Trusted Boot ROM.

- Trusted RAM and/or Trusted External Memory Partitioning.

- Trusted peripherals.

- OTP Fuses.

- Entropy Source.

- Timer.

- Watchdog.

The Baseline architecture focuses on ensuring that the Trusted world software has access to all the assets it requires, and has the underlying mechanisms to protect the integrity, confidentiality, and authenticity of the Trusted world. The Trusted world software exports crypto services to the Non-trusted world, and supports the execution of trusted services, for example by implementing a TEE capable of running trusted applications.

In a TEE architecture, the API that is exposed to the trusted applications by the TEE will be responsible for providing secure time, secure version counters, and cryptographic services that utilize the device root keys. A Trusted application in turn, can expose further services to the Non-trusted world through its API.

The exact requirements for the Trusted Hardware depend on the use cases that the device must support.

#### 5.2 Assisted architecture

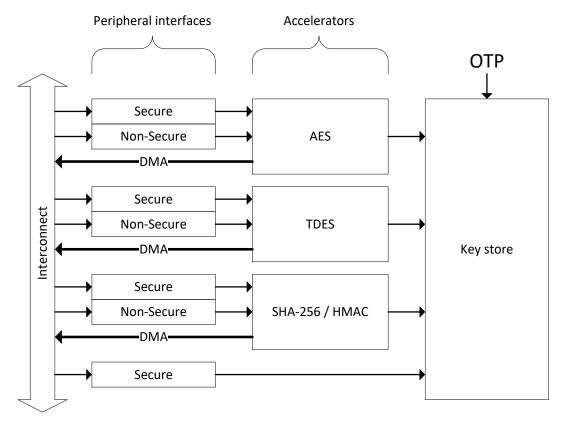

The Assisted Architecture builds on the Baseline Architecture by adding hardware to accelerate and offload some of the cryptographic operations from the Trusted world software, and to provide increased protection to high value assets, such as root keys.

The cryptographic accelerators are expected to support the most commonly used algorithms for encryption, decryption, and authentication. These are likely to include AES, TDES, SHA, RSA, and ECC.

ARM recommends increasing protection for the keys in the system by implementing a hardware Key Store that enables use of the keys by the cryptographic accelerators while preventing the keys from being read by both Non-trusted and Trusted software.

# 6 TBSA security requirements

#### 6.1 System view

At an abstract level, the TBSA can be viewed as a system that comprises a collection of assets, together with operations that act on those assets.

In this context, an asset is defined as a data set that has an owner and a particular intrinsic value, for example a monetary value. All data sets are assets that are associated with a value, even if that value is zero. A data set can be any stored or processed information; this includes executable code as well as the data it operates on.

High value assets that require protection belong to the Trusted world, while lower value assets that do not require protection belong to the Non-trusted world. The actual classification, ranking, and mapping of assets to worlds depends on the target specifications, and is therefore beyond the scope of this document.

Similarly, an operation belongs to a world and is therefore classified as either Trusted or Non-trusted.

R010\_TBSA\_BASE R020 TBSA BASE A Non-trusted world operation shall only access Non-trusted world assets.

A Trusted world operation can access both Trusted and Non-trusted world assets.

In the ARM architecture, code executing on an ARM TZ processor core exists in one of two Security states, Secure or Non-secure, where the Secure state corresponds to Trusted world operations, and the Non-secure state corresponds to Non-trusted world operations.

R030\_TBSA\_BASE

The SoC shall be based on version 8-A of the ARM architecture. See [2.] for details.

ARM recognizes that the security features of a TBSA device will not be entirely implemented in hardware, and that the hardware might be configurable by software.

R040 TBSA BASE

The hardware and software of a TBSA device shall work together to ensure all the security requirements are met.

#### 6.2 Infrastructure

The TBSA is underpinned by a hardware infrastructure that provides strong isolation between the operations and assets of the Trusted and non-Trusted worlds.

The ARM TZ processor core is a key component of a larger SoC design that performs operations on stored assets within the wider system, where storage comprises registers, random access memory, and non-volatile memory. To provide the required protection for assets, the storage is divided into two types: Secure and Non-secure, which correspond to the Trusted and Non-trusted worlds, respectively.

Which world an operation belongs to is determined by its security state. A Secure operation belongs to the Trusted world, while a Non-secure operation belongs to the Non-trusted world. The ARMv8 processor core and some complex hardware IPs can support operations in both worlds.

#### 6.2.1 Memory system

Operations and assets are connected by transactions, where a transaction represents a read or write access to storage containing the asset. Each transaction has a security state that is defined by the originating operation, and can be Secure or Non-secure.

As described in section 4.2, the memory map as seen by the TZ processor core is divided into two spaces: Secure and Non-secure storage, where Trusted world assets are held in Secure storage and Non-trusted world assets are held in Non-secure storage.

The security state of the transaction is interpreted as an additional address bit, which is referred to as ADDRESS.NS for clarity. ADDRESS.NS is high in a Non-secure state, and low in a Secure state.

To build a useful system, it is necessary to facilitate communication between worlds through shared memory. In the TBSA this is achieved by permitting a Trusted operation to issue both

Secure and Non-secure transactions. The opposite, however, is not true: a Non-trusted operation can only issue Non-secure transactions.

R010\_TBSA\_INFRA R020\_TBSA\_INFRA A Trusted operation can issue Secure or Non-secure transactions.

A Non-trusted operation shall only issue Non-secure transactions.

As described in section 4.2, ARM recommends that a consistent system-wide approach is adopted, such that Secure transactions only access Secure storage, and Non-secure transactions only access Non-secure storage. Moreover, this approach is mandatory where data is cached, to guarantee coherency.

R030\_TBSA\_INFRA R040\_TBSA\_INFRA A Secure transaction shall only access Secure storage.

A Non-secure Transaction shall only access Non-secure storage.

The following rules summaries the link between operations, transactions and storage:

- A Non-trusted operation is said to operate in a Non-secure state and shall only issue Non-secure transactions targeting Non-secure storage locations. It shall not issue Secure transactions and therefore cannot access Trusted assets.

- A Trusted operation is said to operate in a Secure state and can issue either Secure

or Non-secure transactions. As such it is capable of accessing both Secure and Nonsecure storage. However, ARM recommends that a Secure transaction only access

Trusted assets and a Non-secure transaction only access Non-trusted assets.

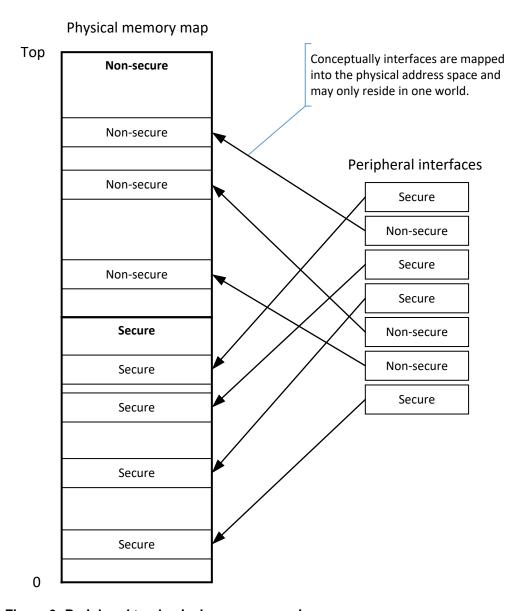

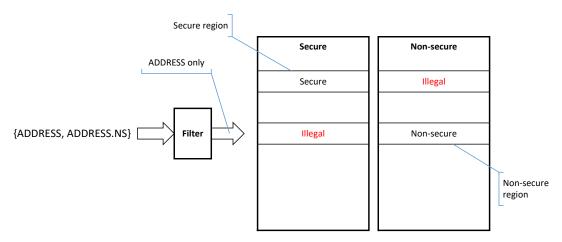

Given these definitions, Figure 3 shows how resources, for example a set of memory mapped peripheral interfaces, are placed into the physical memory map that is based on the world they belong to.

Figure 3: Peripheral to physical memory mapping

If the peripherals are grouped together on a local interconnect node, the required mapping can be achieved through memory translation.

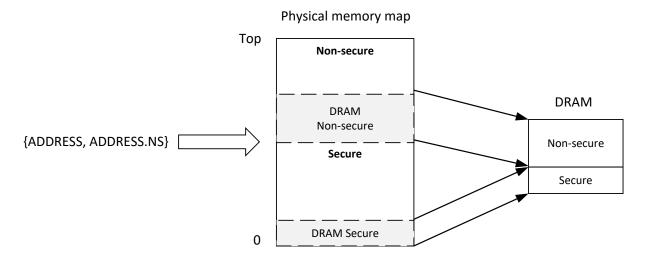

Figure 4 shows the incorporation of a DRAM that is divided into Trusted and Non-trusted regions, using remapping logic.

Figure 4: DRAM to physical memory mapping

In this example, and in many real word cases, the DRAM is simply split into only two regions, Secure and Non-secure. to map the two DRAM regions correctly into the larger physical address map, remapping logic must be implemented. In simple implementations, this can be fixed logic, but it is more likely to be programmable logic, as this offers greater flexibility if software is updated. In the latter case, the relevant configuration registers must only be accessible to Secure transactions, and belong to the Trusted world.

R050 TBSA INFRA

If programmable address remapping logic is implemented in the interconnect then its configuration shall only be possible from the Trusted world.

In general, the mapping of resources into Secure or Non-secure memory can be achieved using either fixed or programmable logic, for example TLB-based translations of the physical address, but a more optimal solution uses a target-based filter. Such a filter enables the definition of Secure and Non-secure memory regions using ranges that are based on all address bits except ADDRESS.NS, causing incoming transactions to be permitted only if the following conditions are true:

- Region is Secure and ADDRESS.NS = 0

- Region is Non-secure and ADDRESS.NS = 1

The physical address space after the filter, which does not consider ADDRESS.NS, is consequently halved in size. Figure 5 shows the resulting address map.

Figure 5: Filter aliasing

The aliasing in the address map that results after filtering places constraints on the memory layout from the point of view of a bus master, for example an ARM processor.

R060 TBSA INFRA

A unified address map that uses target side filtering to disambiguate Non-secure and Secure transactions must only permit all Secure or all Non-secure transactions to any one region. Secure and Non-secure aliased accesses to the same address region are not permitted.

R070\_TBSA\_INFRA

The target transaction filters configuration space shall only be accessed from the Trusted world.

At the interconnect level, and before filtering, ADDRESS.NS forms an additional address bit, and each memory transaction must transport this bit together with all other address bits to the point where the filter constraints are applied.

**Note:** In the legacy case of the APB v4 or earlier, the peripheral bus does not support an ADDRESS.NS bit, which makes it necessary to perform filtering before a transaction reaches the bus, for example at a bus bridge joining AXI and APB.

The ARM TrustZone Address Space Controller (TZC) is one embodiment of such a target-based filter.

In the specific case of the TZC filter, aliasing enables a region to be configured as accessible by any combination of accesses. For example, it is possible to configure a region to be accessible to both Secure and Non-secure transactions. As previously discussed, this violates TBSA requirements, which demand that a region belongs to only one world, and a Secure transaction must only access Secure regions, and a Non-secure transaction must only access Non-secure regions.

Note: This configuration is referred to as "security inversion mode" in the TZC-380 product and must be explicitly enabled by setting a control bit. Later versions of TZC enable such configurations by default.

The TZC filter can be configured to silently block illegal transactions or to block and signal a security exception through a bus error or an interrupt. If an interrupt is generated, it is classified as a Trusted interrupt, as described in the next section.

R080\_TBSA\_INFRA

Security exception Interrupts shall be wired or configured as Secure interrupt sources.

For the ARM processor core, the security state of the transaction is made available at the boundary of the processor core so that it can be propagated through the on-chip interconnect. For example, in an AXI bus implementation, the security state of the transaction, ADDRESS.NS, is mapped to the ARPROT[1] and AWPROT[1] signals, where:

- ARPROT[1] indicates a Trusted write when low.

- AWPROT[1] indicates a Trusted read when low.

Similarly, a hardware IP that is an AXI bus master will generate the same signals to indicate the security state of each transaction.

In architectures that use a network-on-chip interconnect approach, it might be possible to reconfigure the routing of packets so that they arrive at a different interface. Even though the access address remains unchanged, this is dangerous and can lead to an exploit. Any such configuration shall only be possible from the Trusted world using Secure transactions.

R090\_TBSA\_INFRA

Configuration of the on-chip interconnect that modifies routing or the memory map shall only be possible from the Trusted world.

The different techniques for address remapping and filtering are both methods of constraint that bind storage locations to worlds. Whatever the method of constraint, it must not be possible for a memory transaction to bypass it.

A particular example is the case where multiple caches that are up-stream from a target filter are synchronized via a coherency mechanism. If such a mechanism, for example bus snooping, is implemented, the mechanism must force a coherency transaction to pass through the target filter.

R100 TBSA INFRA

All transactions must be constrained; it must not be possible for a transaction to bypass a constraining mechanism.

#### 6.2.1.1 Shared volatile storage

When assets from different worlds can occupy the same physical volatile storage location, the underlying storage, for example internal RAM, external RAM, or peripheral space, is referred to as shared volatile storage.

A shared volatile storage implementation therefore enables a storage location or region that previously held a Trusted asset to hold a Non-trusted asset. Before such a storage location or region can be reallocated from Trusted to Non-trusted, the Trusted asset must be securely removed. This can be achieved using scrubbing.

Scrubbing is defined as the atomic process of overwriting a Trusted asset with an unrelated value, which is either a constant, a Non-trusted asset value, or a randomly generated number of the same size. Atomic means that the process must not be interrupted by the Non-trusted world.

R110\_TBSA\_INFRA

If shared volatile storage is implemented, then the associated location or region must be scrubbed, before it can be reallocated from Trusted to Non-trusted.

Note:

When a copy of Trusted data is held in a cache, it is important that the implementation does not permit any mechanism that provides the Non-Trusted world with access to that data, as required by R030\_TBSA\_INFRA and R040\_TBSA\_INFRA. If a hardware engine is used for scrubbing, careful attention must be given to the sequence to make sure that the relevant cached data is flushed and invalidated before the scrubbing operation.

#### 6.2.2 Interrupts

In most cases a Trusted interrupt, which is an interrupt that is generated by a Trusted operation, must not be visible to a Non-trusted operation to prevent information leaks that might be useful to an attacker. Consequently, the on-chip interrupt network must be capable of routing any interrupt to any world with the caveat that the routing of Trusted interrupts shall only be configured from the Trusted world.

The number of interrupts that must be supported in each world depends on the target requirements and is therefore not specified in this document.

R120 TBSA INFRA

An interrupt originating from a Trusted operation must by default be mapped only to a Trusted target. By default, we mean that this must be the case following a system reset.

R130 TBSA INFRA

Any configuration to mask or route a Trusted interrupt shall only be carried out from the Trusted world.

R140 TBSA INFRA

The interrupt network might be configured to route an interrupt originating from a Trusted operation to a Non-trusted target.

R150 TBSA\_INFRA

Any status flags recording Trusted interrupt events shall only be read from the Trusted world, unless specifically configured by the Trusted world, to be readable by the Nontrusted world.

For example, these rules permit a Non-trusted world request to a Trusted operation to result, after passing the policy check, in a Trusted Interrupt being delivered to a non-trusted target to signal the end of the operation. Configuration of the interrupt in this way must be done by the Trusted world before or during the Trusted operation.

In the ARM architecture, these requirements can be supported using the GIC interrupt controller block.

#### 6.2.3 Secure RAM

In a TBSA system, Trusted code is expected to execute from Secure RAM. The Trusted code will also store high value assets within the Secure RAM. In the context of this document, Secure RAM refers to one or more dedicated regions that are mapped onto one or more physical RAMs. When a physical RAM is not entirely dedicated to Secure storage, it is shared between worlds. However, the underlying locations are not classified as shared volatile

storage unless they are re-allocated from Secure to Non-secure. The mapping of Secure regions can be static and fixed by design, or programmable at runtime.

ARM recommends the use of on-chip RAM, but it is acceptable to use SRAM on a separate die if it is within the same package as the main SoC.

Example Secure RAM use cases are:

- Secure boot code and data.

- Monitor code.

- A Secure OS.

- Cryptographic services.

- Trusted services, for example Global Platform TEE and TAs.

The Secure RAM size depends on the target requirements and is therefore not specified in this document. As an example, a quad core system typically integrates 256 KB of SRAM.

R160\_TBSA\_INFRA R170\_TBSA\_INFRA R180\_TBSA\_INFRA A TBSA system must integrate a Secure RAM.

Secure RAM must be mapped into the Trusted world only.

If the mapping of Secure RAM into regions is programmable, then configuration of the regions must only be possible from the Trusted world.

Note, if Secure RAM is re-mapped from the Trusted world to the Non-trusted world, it is classified as shared volatile storage, and it must meet the requirements of a shared volatile storage.

For a description of the use of external DRAM for Secure RAM see 6.12

#### 6.2.4 Power and clock management

Modern battery powered mobile platforms have a high degree of power control and might integrate an advanced power management subsystem using dedicated hardware, and execute a small software stack from local RAM. In such cases, the management subsystem has control over a number of Trusted assets, for example:

- Clock generation and selection. Examples include:

- Phase-Locked Loops (PLL).

- o Clock dividers.

- Glitch-less clock switching.

- High-level clock gating.

- Reset generation. Examples include:

- o Registers to enable or disable clocks.

- State machines to sequence the assertion and de-assertion of resets in relation to clocks and power states.

- Re-synchronization of resets.

- Power control. Examples include:

- Access to an off-chip power controller/switch/regulator.

- State machine for sequencing when changing power states.

- Logic or processing to intelligently apply power states either on request, or dynamically.

- State saving and restoration. To dynamically apply power states, some subsystems

can also perform saving and restoration of system states without the involvement of

the main application processor.

Unrestricted access to this functionality is dangerous, because it could be used by an attacker to induce a fault that targets a Trusted service, for example by perturbing a system clock. To mitigate this threat, the advanced power mechanism must integrate a Trusted

management function, which performs policy checks on any requests from the Non-trusted word, before they can be applied.

This approach still permits most of the Non-trusted complex peripheral wake up code, which is usually created by the OEM and subject to frequent updates, to be executed from the Non-trusted world.

R190 TBSA INFRA

The advanced power mechanism must integrate a Trusted management function to control clocks and power. It must not be possible to directly access clock and power functionality from the Non-trusted world.

R200 TBSA INFRA

The power and clock status must be available to the Non-trusted world.

**Note:** All system clocks are classified as Trusted because they can only be configured via the Trusted manager.

#### 6.2.5 Peripherals

A peripheral is a hardware block that is not a processor core and which implements one or more operations that act on assets. It has an interface to receive commands and data from one or more processor cores and might be capable of direct memory access.

A simple peripheral can have its operations mapped into one world or the other by the wider system depending on its role in the current use case.

R210\_TBSA\_INFRA

If access to a peripheral, or a subset of its operations, can be dynamically switched between Trusted world and Non-trusted world, then this shall only be done under the control of the Trusted world.

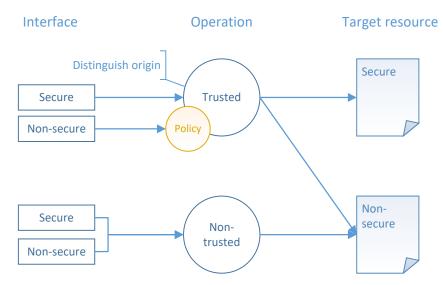

A Non-Trusted peripheral acts only on Non-Trusted assets, while a Trusted peripheral can act on assets in both worlds. Complex peripherals might therefore act in both worlds, supporting both Trusted and Non-trusted operations, as illustrated in Figure 6.

Figure 6: Peripheral operations

A Trusted peripheral is viewed as hardware block that implements at least one Trusted operation. In turn, each operation has an interface that is mapped into the Trusted or non-trusted world, or into both worlds.

The implementation of the operations is a design choice. They can be built using fully separate hardware, or utilize multiplexing of shared functions and resources.

A Trusted peripheral must meet the following requirements, which are framed in terms of its operations:

R220\_TBSA\_INFRA

If the peripheral stores assets in local embedded storage, a Non-trusted operation must not be able to access the local assets of a Trusted operation.

R230 TBSA INFRA

A Trusted operation must be able to distinguish the originating world of commands and data arriving at its interface, by using the address.

R240 TBSA INFRA

A Trusted operation that exposes a Non-secure interface must apply a policy check to the Non-trusted commands and data before acting on them. The policy check must be atomic and, following the check, it must not be possible to modify the checked commands or data.

An example policy for a cryptographic accelerator peripheral would cover at least:

- Which world the input data is permitted to be read from.

- Which world the output data is permitted to be written to.

- Whether encryption is permitted.

- Whether decryption is permitted.

A specific example is a DMA engine that is shared between worlds. When configured from the Trusted world, the DMA can operate on Trusted and Non-Trusted memory, by appropriate use of the NS bit. However, when configured from the Non-Trusted world, the DMA shall only operate on Non-Trusted memory, using an NS value of 1.

#### 6.3 Fuses

A modern SoC requires non-volatile storage to store a range of data across power cycles. These vary from the device firmware to cryptographic keys and system configuration parameters. Non-volatile storage can use a variety of technologies, for example floating gate memories or oxide-breakdown antifuse cells. These technologies vary with respect to certain properties, most notably whether they are one-time-programmable (OTP) or many-time-programmable (MTP).

Not all non-volatile storage technologies are available in all semiconductor processes. Floating gate memories, for example, are not economic in modern bulk CMOS processes. Where needed, off-chip non-volatile memory can be used to augment the available on-chip non-volatile storage.

Non-Volatile storage technologies generally require error correction mechanisms to ensure the correct storage of data over the lifespan of the device.

R010\_TBSA\_FUSE

A non-volatile storage technology shall meet the lifetime requirements of the device, either through its intrinsic characteristics, or through the use of error correction mechanisms.

The majority of security assets and settings that need to be stored on-chip require OTP non-volatile storage to ensure that the values cannot be changed. Following the industry norm, the rest of this document will use the term fuse to refer to on-chip OTP non-volatile storage. Fuses can be implemented using antifuses or an MTP technology with controlling logic to make it OTP.

The fundamental requirements for implementing fuses in a TBSA device are:

R020\_TBSA\_FUSE

A fuse is permitted to transition in one direction only, from its un-programmed state to its programmed state. The reverse operation shall be prevented.

R030\_TBSA\_FUSE

A fuse shall be programmed only once as multiple programming operations might degrade the programmed cell(s) and introduce a fault.

R040\_TBSA\_FUSE

It shall be possible to blow at least a subset of the fuses when the device has left the silicon manufacturing facility.

R050\_TBSA\_FUSE

All fuse values shall be stable before any parts of the SoC that depend on them are released from reset.

R060 TBSA FUSE

Fuses that configure the security features of the device shall be configured so that the programmed state of the fuse enables the feature. i.e. the programming of a security configuration fuse will always increase security within the SoC.

This ensures that after a security feature is enabled, it cannot be deactivated.

R070\_TBSA\_FUSE

Lifetime guarantee mechanisms to correct for in-field failures shall not indicate which fuses have had errors detected or corrected, just that an error has been detected or corrected. This indicator shall only be available after all fuses have been checked.

The full error information will be available to the lifetime guarantee mechanism and the security of the mechanism implementation must be considered. ARM recommends to implement the mechanism in hardware, but this might not always be practical.

Assets stored in fuses have a variety of characteristics that in turn determine the way that the fuses are accessed. The characteristics of fuses can be summarized as follows:

**Confidential/Public** - "Confidential" fuses must only be read by the intended recipient, or a particular hardware module or software process. "Public" fuses can be accessed by any piece of software or hardware.

#### Lockable/Open -

"Lockable" fuses shall comply with one of the following requirements:

Prevent re-writing of a locked value.

A mechanism that prevents the programming of a fuse bit or group of fuse bits can be implemented by reserving an additional fuse bit to act as a lock bit:

- Writing the value is followed by its lock bit being set. Glue logic ensures that no further programming is possible.

- Writing zero, which corresponds to the un-programmed fuse state, causes no value to be written, only the lock bit to be set.

- Use tamper detection to detect that the value has been modified.

A tamper protection mechanism can be implemented by storing a code in additional fuses that is sufficient to detect any modification to the value:

- Writing the value is followed by storing the detection code.

- When the value is read by the system, a mechanism must recalculate the code from the value and compare it with the stored code.

- o If the codes do not match, the value shall not be returned to the system.

By definition, "Open" fuse bits might be programmed only once, at any point in the device lifetime.

**Bitwise/Bulk** - "Bitwise" fuses can be programmed one logical fuse at a time, regardless of the number of fuses required to store the value. "Bulk" fuses store multi-bit values that must be programmed at the same time and are treated as an atomic unit.

Bitwise and bulk fuses must comply with the following requirements:

R080\_TBSA\_FUSE

A confidential fuse whose recipient is a hardware IP shall not be readable by any software process.

R090\_TBSA\_FUSE

A confidential fuse whose recipient is a hardware IP shall be connected to the IP using a path that is not visible to software or any other hardware IP.

Usually, this is implemented as a direct wire connection.

R100\_TBSA\_FUSE