# ACPI for Arm Components 1.0 Platform Design Document

Non-confidential

# Contents

| Re                               | lease inf              | ormation                                                                                                               |                              | 3                                                                                                                 |

|----------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Arm N                            | Ion-Con                | fidential D                                                                                                            | Document Licence ("Licence") | 4                                                                                                                 |

| 1 Ab<br>1.1<br>1.2<br>1.3        | Terms<br>Refere        |                                                                                                                        |                              | <b>6</b><br>6<br>6<br>7                                                                                           |

| 2 Int                            | roductio               | n                                                                                                                      |                              | 8                                                                                                                 |

| 3 AC<br>3.1<br>3.2<br>3.3<br>3.4 | ACPI<br>Reser<br>Reser | ved ACPI<br>omponent<br>Arm DM<br>3.4.1.1<br>3.4.1.2<br>Arm Dyn<br>3.4.2.1<br>3.4.2.2<br>3.4.2.3<br>Arm Cor<br>3.4.3.1 |                              | <b>9</b><br>9<br>9<br>9<br>10<br>10<br>10<br>11<br>11<br>11<br>11<br>11<br>11<br>11<br>11<br>13<br>14<br>15<br>15 |

Copyright © 2020 Arm Limited. All rights reserved.

# **Release information**

| Date        | Version | Changes                              |  |

|-------------|---------|--------------------------------------|--|

| 2020/Jul/30 | 1.0     | <ul> <li>External release</li> </ul> |  |

# **Arm Non-Confidential Document Licence ("Licence")**

This Licence is a legal agreement between you and Arm Limited ("**Arm**") for the use of Arm's intellectual property (including, without limitation, any copyright) embodied in the document accompanying this Licence ("**Document**"). Arm licenses its intellectual property in the Document to you on condition that you agree to the terms of this Licence. By using or copying the Document you indicate that you agree to be bound by the terms of this Licence.

"Subsidiary" means any company the majority of whose voting shares is now or hereafter owner or controlled, directly or indirectly, by you. A company shall be a Subsidiary only for the period during which such control exists.

This Document is **NON-CONFIDENTIAL** and any use by you and your Subsidiaries ("Licensee") is subject to the terms of this Licence between you and Arm.

Subject to the terms and conditions of this Licence, Arm hereby grants to Licensee under the intellectual property in the Document owned or controlled by Arm, a non-exclusive, non-transferable, non-sub-licensable, royalty-free, worldwide licence to:

- (i) use and copy the Document for the purpose of designing and having designed products that comply with the Document;

- (ii) manufacture and have manufactured products which have been created under the licence granted in (i) above; and

- (iii) sell, supply and distribute products which have been created under the licence granted in (i) above.

# Licensee hereby agrees that the licences granted above shall not extend to any portion or function of a product that is not itself compliant with part of the Document.

Except as expressly licensed above, Licensee acquires no right, title or interest in any Arm technology or any intellectual property embodied therein.

THE DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. Arm may make changes to the Document at any time and without notice. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

NOTWITHSTANING ANYTHING TO THE CONTRARY CONTAINED IN THIS LICENCE, TO THE FULLEST EXTENT PETMITTED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, IN CONTRACT, TORT OR OTHERWISE, IN CONNECTION WITH THE SUBJECT MATTER OF THIS LICENCE (INCLUDING WITHOUT LIMITATION) (I) LICENSEE'S USE OF THE DOCUMENT; AND (II) THE IMPLEMENTATION OF THE DOCUMENT IN ANY PRODUCT CREATED BY LICENSEE UNDER THIS LICENCE). THE EXISTENCE OF MORE THAN ONE CLAIM OR SUIT WILL NOT ENLARGE OR EXTEND THE LIMIT. LICENSEE RELEASES ARM FROM ALL OBLIGATIONS, LIABILITY, CLAIMS OR DEMANDS IN EXCESS OF THIS LIMITATION.

This Licence shall remain in force until terminated by Licensee or by Arm. Without prejudice to any of its other rights, if Licensee is in breach of any of the terms and conditions of this Licence then Arm may terminate this Licence immediately upon giving written notice to Licensee. Licensee may terminate this Licence at any time. Upon termination of this Licence by Licensee or by Arm, Licensee shall stop using the Document and destroy all copies of the Document in its possession. Upon termination of this Licence, all terms shall survive except for the licence grants.

Any breach of this Licence by a Subsidiary shall entitle Arm to terminate this Licence as if you were the party in breach. Any termination of this Licence shall be effective in respect of all Subsidiaries. Any rights

granted to any Subsidiary hereunder shall automatically terminate upon such Subsidiary ceasing to be a Subsidiary.

The Document consists solely of commercial items. Licensee shall be responsible for ensuring that any use, duplication or disclosure of the Document complies fully with any relevant export laws and regulations to assure that the Document or any portion thereof is not exported, directly or indirectly, in violation of such export laws.

This Licence may be translated into other languages for convenience, and Licensee agrees that if there is any conflict between the English version of this Licence and any translation, the terms of the English version of this Licence shall prevail.

The Arm corporate logo and words marked with ® or ™ are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. No licence, express, implied or otherwise, is granted to Licensee under this Licence, to use the Arm trade marks in connection with the Document or any products based thereon. Visit Arm's website at https://www.arm.com/company/policies/trademarks for more information about Arm's trademarks.

The validity, construction and performance of this Licence shall be governed by English Law.

Copyright © [2020] Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England. 110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-21585 version 4.0

# **1** About this document

### **1.1 Terms and abbreviations**

| Term | Meaning                                    |  |

|------|--------------------------------------------|--|

| ACPI | Advanced Configuration and Power Interface |  |

| ASL  | ACPI Source Language                       |  |

| CMN  | Arm CoreLink Mesh Network                  |  |

| DSU  | DynamicIQ Shared Unit                      |  |

| DTC  | Debug and Trace Controller                 |  |

| GIC  | Arm Generic Interrupt Controller           |  |

| GSIV | Global System Interrupt Vector             |  |

| HN   | Home Node                                  |  |

| PMU  | Performance Monitoring Unit                |  |

| RN   | Requester Node                             |  |

| SPE  | Statistical Profiling Extension            |  |

| XP   | Cross-point                                |  |

### 1.2 References

This section lists publications by Arm and by third parties.

See Arm Developer (http://developer.arm.com) for access to Arm documentation.

[1] Advanced Configuration and Power Interface Specification 6.3. UEFI Forum, https://uefi.org/specifications.

[2] Arm® Architecture Reference Manual Armv8, for Armv8-A architecture profile: ARM DDI 0487F.b (ID040120). Arm Limited.

[3] Arm® Generic Interrupt Controller Architecture Specification, GIC architecture version 3 and version 4: Arm IHI 0069E (ID012119). Arm Limited.

[4] Arm® System Memory Management Unit Architecture Specification SMMU architecture versions 3.0, 3.1 and 3.2: Arm IHI 0070C.a..

[5] Arm<sup>®</sup> CoreSight<sup>™</sup> Architecture Specification v3.0: Arm IHI 0029E (ID022717). Arm Ltd.

[6] Arm® Server Base System Architecture 6.0 Platform Design Document: DEN0029. Arm Limited.

[7] Arm IO Remapping Table: DEN0049E. Arm Limited.

[8] ACPI for CoreSight<sup>™</sup> 1.1: DEN0067. Arm Ltd.

[9] Arm® Functional Fixed Hardware Specification Document number: Arm DEN 0048A. Arm Limited, https://uefi.org/acpi.

[10] \_DSD (Device Specific Data) Implementation Guide v1.2. UEFI Forum, https://uefi.org/specifications.

[11] ACPI for Arm v8-A Memory System Resource Partitioning and Monitoring: DEN0065. Arm Limited.

[12] Arm Architecture Reference Manual Supplement Memory System Resource Partitioning and Monitoring (MPAM), for Armv8-A: ARM DDI 0598B.a. Arm Limited.

[13] ACPI for the Armv8-A RAS Extensions 1.0: DEN0085. Arm Limited.

[14] Arm® Reliability, Availability, and Serviceability (RAS) Specification: Arm DDI 0587C.b. Arm Limited.

[15] Serial Port Console Redirection Table. Microsoft Corporation, https://uefi.org/acpi.

[16] Debug Port Table 2. Microsoft Corporation, https://uefi.org/acpi.

[17] Arm® DynamIQ<sup>™</sup> Shared Unit, Revision r0p2, Technical Reference Manual: Arm 100453\_0002\_00\_en. Arm Limited.

[18] Arm® CoreLink™ CMN-600 Coherent Mesh Network Revision: r1p3, Technical Reference Manual: 100180\_0103\_00\_en. Arm Limited.

[19] Arm® Power State Coordination Interface Platform Design Document: DEN0022D. Arm Limited.

# 1.3 Feedback

Arm welcomes feedback on its documentation.

If you have comments on the content of this manual, send an email to errata@arm.com. Give:

- The title (ACPI for Arm Components).

- The document ID and version (DEN0093 1.0).

- The page numbers to which your comments apply.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

## **2** Introduction

This document provides guidance for describing system components implemented or licensed by Arm, and their properties, in ACPI [1].

This specification does not cover ACPI description of the Arm Architecture [2] or related architectures, for example the Generic Interrupt Controller Architecture [3], the System Memory Management Unit Architecture [4], the CoreSight Architecture [5], or architected components that are described in the Server Base System Architecture [6]. The ACPI descriptions of these architectural components are covered in the following specifications instead:

| Specification                                                                                                                          | Table or<br>object                                      | Arm Architecture Covered                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| ACPI [1]<br>ACPI [1]<br>I/O Remapping Table [7]<br>ACPI For CoreSight [8]<br>FFH for Arm [9]<br>ACPI _DSD Implementation<br>Guide [10] | MADT<br>MADT<br>IORT<br>ACPI graph<br>FFH<br>ACPI graph | Arm Architecture [2]<br>GIC [3], SPE<br>SMMU [4]<br>CoreSight Architecture [5]<br>Armv8 Activity Monitors Extension<br>CoreSight Architecture [5] |

| ACPI for MPAM [11]<br>ACPI for Arm RAS Extensions<br>[13]                                                                              | MPAM<br>AEST                                            | Armv8 MPAM Architecture [12]<br>Armv8 RAS Extensions Architecture [14]                                                                            |

#### Table 3: Arm Architectures that are covered by ACPI Tables

The following table details coverage of specific Arm components in ACPI:

#### Table 4: Arm Components that are covered by specific ACPI Tables

| ACPI Tables          | Arm Components Covered  |

|----------------------|-------------------------|

| GTDT                 | SBSA Watchdog timer [6] |

| PPTT                 | Caches, cores, clusters |

| SPCR [15], DBG2 [16] | SBSA UART, PL011        |

This specification recommends that components that are not covered in standard or Arm-specific ACPI tables are described as ACPI device objects in ASL. Because a component might have multiple internal interfaces, Arm recommends that a separate ACPI device object is created to cover each of these interfaces to allow device drivers in OS to unequivocally bind to those specific interfaces. Interfaces like RAS Extensions and MPAM are not covered, and instead are described in appropriate tables, as indicated in Table 3 above.

The device objects should define the generic and specific properties of the component interface to aid software discovery from the OS, where:

- Generic properties include an ACPI namespace identifier for the component or its interface, the memory-mapped base address of the component or its interface, and the interrupts that the component can generate.

- · Specific properties are component specific or vendor specific or both.

# 3 ACPI for Arm Components

# 3.1 ACPI Identifiers

ACPI Identifiers of Arm components follow the conventions that are described in [1]. The ACPI Hardware ID object, \_HID, is used as the primary identifier. For Arm components, the format is ARMH###.

For some Arm components, existing standard ACPI or PNP identifiers may also be used as \_HID values. In such cases, Arm recommends setting the \_CID of the device object as ARMH#### where relevant.

## 3.2 Reserved ACPI IDs for legacy Arm components

This section lists reserved ACPI IDs for components from Arm that are managed as a complete unit by a single device driver, or are required for cross-referencing from other Arm ACPI tables like the AEST [13] and the MPAM [12]. These components are listed in Table 5.

| Component                      | HID      |

|--------------------------------|----------|

| Prime cell UART (PL011         | ARMH0011 |

| Prime cell General Purpose I/O | ARMH0061 |

### 3.3 Reserved ACPI IDs for SBSA-defined Arm components

The following types of Arm components require a unique ACPI ID for identification:

- Specifically defined by the SBSA specification [6]

- Not described in any standard ACPI table listed in Table 3 or Table 4

- · Are described in ACPI namespace by virtue of the above two properties

#### Table 6: Reserved ACPI IDs for SBSA components

| SBSA Component | HID      |

|----------------|----------|

| SBSA UART      | ARMHB000 |

An SBSA component can be described in both ACPI namespace and the standard ACPI tables in a given system. For example, a system might have two instances of SBSA UARTs: a primary UART that is used by the OS and a secondary, general-purpose, UART for application usage. In this example system, the primary UART must be declared in the ACPI SPCR table. The secondary UART might be declared as a device object in ACPI namespace and assigned the HID that is defined in Table 6.

# 3.4 Arm components requiring ACPI description

This section describes Arm components that have at least one interface that is not covered by standard or Arm-specific ACPI tables, and that must be described in ACPI namespace.

### 3.4.1 Arm DMC620 Memory Controller

Table 7 describes interfaces within the DMC620 that require ACPI description to support software discovery.

#### 3.4.1.1 Interface identification

#### Table 7: Arm DMC620 Memory Controller HID values

| Value    | Description                                  |

|----------|----------------------------------------------|

| ARMHD620 | ACPI Hardware Identifier for the DMC620 PMU. |

#### 3.4.1.2 The DMC620 PMU

The DMC620 PMU is assigned the HID value of ARMHD620, as specified in Table 7.

#### Device configuration objects for the DMC620 PMU

#### Table 8: Configuration objects for the DMC620 PMU

| Object | Values       | Туре        | Description                                       |

|--------|--------------|-------------|---------------------------------------------------|

| _CRS   | Base address | QWordMemory | Base address of the PMU in the system address map |

|        | GSIV         | Interrupt   | GSIV of the PMU overflow interrupt                |

#### ASL reference code for the DMC620 PMU

The DMC620 PMU register space is mapped at a 512-byte range that begins at offset 0x80000A00 in the system address space. In this reference code, it is assumed that the PMU overflow interrupt from the DMC620 is mapped to GSIV 312.

```

Device (MCOO) { // PMU interface on the example DMC620 memory controller

// instance in the system.

Name (_HID, "ARMHD620")

Name (_CID, "ARMHD620")

Name (_UID, 0)

Name (_CCA, 1)

Name (_STR, Unicode ("Socket0:MCU0"))

Name(_STA, 0, NotSerialized) {

Return (0x0f)

Name (_CRS, ResourceTemplate () {

// Descriptor for 64-bit memory-mapped register space

// of the DMC620 \,

QWord Memory (

// ResourceUsage

ResourceProducer,

// Decode

PosDecode,

MinFixed,

// Min range is fixed

// Max range is fixed

MaxFixed,

// Cacheable

NonCacheable,

// ReadAndWrite

ReadWrite,

0x00000000000000, // Address Granularity - GRA

0x0000100080000A00, // Address Minimum - MIN

```

```

0x0000100080000BFF, // Address Maximum - MAX

0x00000000000000, // Address Translation - TRA

0x000000000000000, // Range Length - LEN

, // ResourceSourceIndex

, // ResourceSource

CFGS // Descriptor Name

)

// PMU overflow Interrupt, with GSIV = 312

Interrupt (ResourceConsumer, Level, ActiveHigh, Exclusive) {312}

})

}

```

#### 3.4.2 Arm DynamIQ Shared Unit (DSU)

The Arm DynamIQ Shared Unit (DSU) provides circuitry, logic, interfaces, and an optional shared cache to support a DynamIQ cluster. The DSU is described in detail in [17]. Interfaces within the DSU that require ACPI description to support software discovery are described here.

The DSU is shared by a set of cores organized as a cluster. The ACPI description of interfaces within the DSU is therefore expressed as a device object that is a child of the ACPI processor container object that describes the cluster.

The OS must parse the CPU topology in ACPI namespace to discover the DSU interface objects and to understand the associativity between those DSU instances and cores.

#### 3.4.2.1 Interface Identification

Table 9: Arm DSU HID values

| Value    | Description                                           |

|----------|-------------------------------------------------------|

| ARMHD500 | ACPI Hardware Identifier for the DSU PMU.             |

| ARMHD501 | ACPI Hardware Identifier for the common DSU elements. |

#### 3.4.2.2 Common DSU elements

Common DSU elements are collectively described by a single device object with a HID of ARMHD501. This device object allows cross-referencing the DSU object from other ACPI objects and tables.

#### 3.4.2.3 DSU PMU

The DSU provides a PMU for monitoring and recording miscellaneous events. DSU PMU registers are presented as System Registers to allow for native software discovery. Therefore, no ACPI description is required to locate them. When a PMU counter overflows, the PMU asserts an interrupt signal that can be routed to an interrupt controller such as the GIC.

The DSU PMU is assigned the HID value of ARMHD500, as specified in Table 9.

#### DSU PMU device configuration objects

| Object | Value | Туре      | Description                            |

|--------|-------|-----------|----------------------------------------|

| _CRS   | GSIV  | Interrupt | GSIV of the DSU PMU overflow interrupt |

#### Table 10: Arm DSU PMU device configuration objects

#### ASL reference code

This reference code illustrates how the CPU topology that is associated with the DSU is described in ACPI namspace by including the DSU device objects in the CPU hierarchy description. The code showcases an example system that has two clusters, each with a single DSU. Each cluster includes two CPU cores that share the associated DSU.

The code also illustrates how the global DSU device object may be also included within the CPU topology description. The placement of the global DSU object allows generic references to the DSU from the OSPM.

```

Device

(SYSM) { // System level states

Name (_HID, "ACPI0010")

Name (_UID , 0)

Name (_LPI ,

Package () {...}

)

Device ( CLU0 ) { // Cluster 0

Name (_HID, "ACPI0010")

Name (_UID , 1)

Name (_LPI ,

Package () {...}

Device ( DSU0 ) { // Common DSU Instance 0 associated with cluster 0

Name (_HID, "ARMHD501")

Name (_UID , 0)

} // DSU descriptor ends here

Device ( DSP0 ) { // PMU interface on DSU 0 associated with cluster 0

Name (_HID, "ARMHD500")

Name (_UID , 0)

Name (_CRS, ResourceTemplate () {

// PMU overflow Interrupt, with GSIV = 302

Interrupt (ResourceConsumer, Level, ActiveHigh, Exclusive) {302}

})

} // DSUO PMU interface descriptor ends here

Device (CPU0) { // Core0

Name (HID, "ACPI0007")

Name (UID, 0)

Method (_LPI, 0, NotSerialized) {

. . .

}

} // CPUO description ends here

Device ( CPU1 ) { // Core1

Name (_HID, "ACPI0007")

Name (UID, 1)

Method (_LPI, 0, NotSerialized) \{

}

} // CPU1 description ends here

```

```

} // Cluster 0 descriptor ends here

Device ( CLU1 ) { // Cluster 1

Name (_HID, "ACPI0010")

Name (_UID , 2)

Method (_LPI, 0, NotSerialized) {

}

Device (DSU1) { // Common DSU Instance 1 associated with cluster 1

Name (_HID, "ARMHD501")

Name (_UID , 1)

} // DSU descriptor ends here

Device (DSP1) { // PMU interface on DSU 1 associated with cluster 1

Name (_HID, "ARMHD500")

Name (_UID , 1)

Name (_CRS, ResourceTemplate () {

// PMU overflow Interrupt , with GSIV = 402

Interrupt (ResourceConsumer, Level, ActiveHigh, Exclusive) \{402\}

})

} // DSU1 PMU interface descriptor ends here

Device ( CPU2 ) { // Core2

Name (_HID, "ACPI0007")

Name (_UID , 2)

Method (_LPI, 0, NotSerialized) {

. . .

}

} // CPU2 description ends here

Device (CPU3) { // Core3

Name (_HID, "ACPI0007")

Name (_UID , 3)

Method (_LPI, 0, NotSerialized) {

. . .

}

} // CPU3 description ends here

} // Cluster 1 descriptor ends here

} // End of system description

```

### 3.4.3 Arm CoreLink CMN-600 Coherent Mesh Network

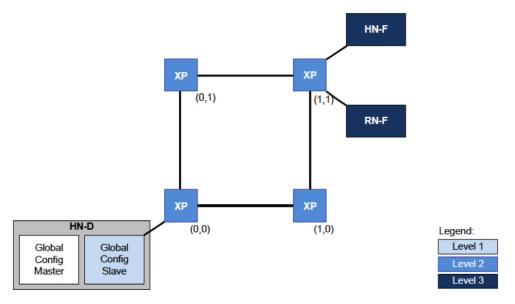

The Arm CoreLink CMN-600 Coherent Mesh Network is described in [18]. The CMN-600 network consists of Cross-points (XPs), Home Nodes (HNs) and Request Nodes (RNs). A special Home Node, HN-D, houses the global configuration registers. In this network, PMU logic is integrated into Debug and Trace Logic Controllers (DTCs). HN-D also houses the primary DTC, which is labelled DTC0. Other DTCs, DTC1 to DTC3, are housed in special Home Nodes called HN-T. The CMN-600 layout is illustrated in the following diagram:

Figure 1: High-level layout of the CMN-600

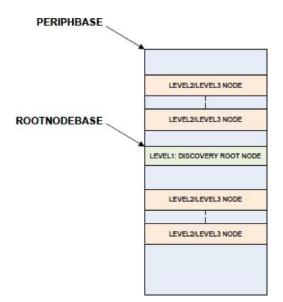

All configuration registers that belong to the CMN-600 network are mapped into System Address Map (SAM) at a pre-determined, 64MB aligned address range at offset PERIPHBASE. Within this address range, the configuration space of the root node of the network is mapped to an address range at offset ROOTNODEBASE. These offsets are illustrated in the following diagram:

Figure 2: Memory-mapped configuration region of the CMN-600

All registers are organized into one or more register blocks. Each register block is 16KB in size, and there is one register block for each logical block in the network. Each register block is called a node. The nodes are laid out in a tree hierarchy. The root of the tree hierarchy is the root node, as illustrated in the preceding diagram.

#### 3.4.3.1 Interface Identification

#### Table 11: Arm CMN-600 HID values

| Value    | Description                                                    |

|----------|----------------------------------------------------------------|

| ARMHC600 | ACPI Hardware Identifier for the<br>CMN-600 PMU                |

| ARMHC601 | ACPI Hardware Identifier for common<br>elements of the CMN-600 |

#### 3.4.3.2 Common CMN-600 elements

Common CMN-600 elements are collectively described by a single device object with a HID of ARMHC601. The common device object facilitates cross-referencing the CMN-600 object from other ACPI objects and tables.

#### 3.4.3.3 CMN-600 PMU

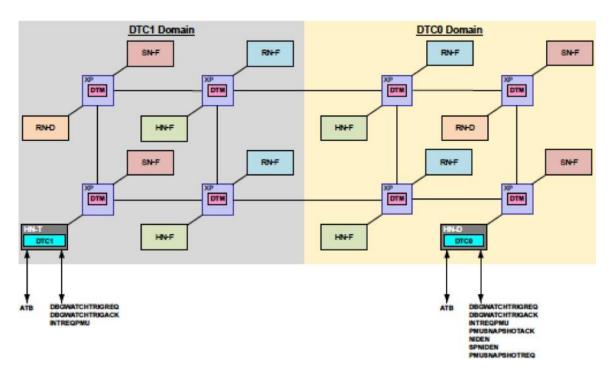

CMN-600 PMU logic is integrated into Debug and Trace Logic Controllers (DTCs). Thus, discovery of the PMU interface in a CMN-600 network relies on the topology in which the DTCs are organized within the network.

The HN-D houses the primary DTC, which is labelled DTC0. Each DTC is associated with multiple DTMs. The parent DTC and its children DTMs form a DTC domain. The following diagram shows an example system with two DTC domains:

#### Figure 3: CMN-600-based topology with 2 DTCs

Each PMU asserts its own dedicated interrupt signal on overflow, called INTREQPMU. The interrupts from the PMUs are routed to the GIC and appear as one or more GSIVs to software.

This means that, to support software discovery of CMN PMUs, the primary sources of required information are:

| Information                                                                                                             | Information source         |

|-------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Discovery of PMUs in CMN-600 network. This is based on discovery of DTC <i>n</i> for PMU <i>n</i> .                     | ROOTNODEBASE               |

| Identity of PMU overflow interrupt for all PMU logic within the network, where PMU <i>n</i> is housed in DTC <i>n</i> . | INTREQPMU <i>n</i> routing |

#### Table 12: Information sources for CMN-600 PMU discovery

#### PMU overflow interrupt description ordering and Logical ID

The CMN-600 network specification allows for up to four DTCs in the system. DTC0 is the primary DTC, and it must always exist in a system. Additional DTCs may be installed on various cross-points, based on system design and topology. The CMN-600 provides logical numbering of DTCs to allow for their unique identification in hardware. The Logical ID is the only way for software to identify a unique DTC. However, the Logical IDs is not guaranteed to be the same as the DTC number. For example, DTC 1 is not guaranteed to obtain a Logical ID of 1.

Here is an example mapping for a CMN-600 system with 4 DTCs is as follows:

| DTC Name | DTC Domain<br>Number (Value) | DTC Logical ID<br>(Notation) | DTC Logical ID<br>(Value) | Description                                                                        |

|----------|------------------------------|------------------------------|---------------------------|------------------------------------------------------------------------------------|

| DTC0     | 0                            | DTC[0]                       | 0                         | DTC0 is always assigned<br>Logical ID of 0.                                        |

| DTC1     | 1                            | DTC[1]                       | j                         | DTC1 is assigned Logical ID <i>j</i> , where <i>j</i> != 0.                        |

| DTC2     | 2                            | DTC[2]                       | k                         | DTC2 is assigned Logical ID <i>k</i> , where <i>j</i> != 0 && <i>k</i> != <i>j</i> |

| DTC3     | 3                            | DTC[3]                       | т                         | DTC1 is assigned Logical<br>ID $m$ , where $m \ge 0 \&\& m \ge j \ge k$ .          |

#### Table 13: DTC domain number to Logical ID mapping in an example system

To address the lack of an explicit relation between the Logic ID and Domain Number as shown in Table 13, the PMU overflow interrupt descriptors are organized in increasing order of the hardware assigned Logical IDs of the related DTCs, respectively. This allows OS software to map interrupt descriptors to their parent DTCs. This means that INTDESC[1] corresponds to DTC0, INTDESC[2] corresponds to the DTC that is assigned the next smallest Logical ID, and so on.

#### Device Identification for CMN-600 PMU

The CMN-600 PMU interface is assigned an ACPI ID of ARMHC600 as indicated in Table 11.

#### Device configuration objects

| Object | Values       | Туре        | Description                                                                                                |

|--------|--------------|-------------|------------------------------------------------------------------------------------------------------------|

| _CRS   | PERIPHBASE   | QWordMemory | Base address of the memory-mapped region in the system address map where the CMN-600 registers are mapped. |

|        | ROOTNODEBASE | QWordMemory | Base address of the root node.                                                                             |

#### Table 14: Arm CMN-600 Coherent Mesh Network configuration objects

| Object | Values           | Туре      | Description                                                                                                                               |  |

|--------|------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

|        | GSIV[ <i>n</i> ] | Interrupt | List of GSIVs of <i>n</i> distinct interrupts<br>that can be generated by the <i>n</i><br>PMUs located in this instance of the<br>CMN-600 |  |

The list must always begin with PERIPHBASE, followed by ROOTNODEBASE, and finally the interrupt resource descriptors. Similarly, the interrupt resource descriptors for the PMUs, for example GSIV[*n*], must appear in numerically increasing order of the corresponding DTC[*n*]. So the first interrupt resource descriptor relates to DTC[0], the second interrupt resource descriptor relates to DTC[1] and so on. The *m*th interrupt resource descriptor in the list corresponds to DTC[*m*-1].

#### ASL code example

This code example pertains to a CMN-600 based network with a dimension larger than 4x4 and that has two DTCs. Like the example illustrated in Figure 3 in Section 3.4.3.3, the first DTC is always DTC0 and is attached to HN-D. However, the second DTC could be assigned any Logical ID that will be non-zero. The term DTC[n] is used to represent the Logical ID of DTCn. In this example, PERIPHBASE of the CMN-600 is set as 0xAFE0000000, and the root node is at an offset of 0x4000 from PERIPHBASE.

```

Device (CMN6) { // CMN-600 device object for an X * Y mesh where X, Y > 4

Name (HID, "ARMHC600")

Name( CRS, ResourceTemplate () {

// Descriptor for 256 MB of the CFG region at offset PERIPHBASE

QWord Memory (

ResourceConsumer,

// bit 0 of general flags is 0

PosDecode,

MinFixed,

// Range is fixed

MaxFixed,

// Range is Fixed

NonCacheable,

ReadWrite,

0x00000000,

// Granularity

0xAFE0000000,

// Min, set to PERIPHBASE

OxAFEFFFFFFF,

// Max

0x00000000,

// Translation

// Range Length = 256 MB

// ResourceSourceIndex

// Resource Source

CFGR

// Descriptor Name

)

// Descriptor for the root node. This is a 16 KB region at

// offset ROOTNODEBASE. In this example, ROOTNODEBASE starts

// at the 16 KB aligned offset of PERIPHBASE+0xC000

QWord Memory (

ResourceConsumer,

// bit 0 of general flags is 0

PosDecode,

MinFixed,

// Range is fixed

// Range is Fixed

MaxFixed.

NonCacheable,

ReadWrite,

// Granularity

0 \times 000000000.

// Min, set to ROOTNODEBASE

0xAFE000C000.

// Max

OxAFE000FFFF.

0x00000000,

// Translation

// Range Length = 16 KB

// ResourceSourceIndex

// Resource Source

```

```

ROOT // Descriptor Name

)

// Interrupt on PMUO overflow, attached to DTC [0], with GSIV=<gsiv0>

Interrupt (ResourceConsumer, Level, ActiveHigh, Exclusive) {<gsiv0>}

// Interrupt on PMU1 overflow, attached to DTC [1], with GSIV=<gsiv1>

Interrupt (ResourceConsumer, Level, ActiveHigh, Exclusive) {<gsiv1>}

})

}

```

The following ASL code example shows pertains to a CMN-600 based network that has a dimension less than 4x4 and that has four DTCs, DTC0-DTC3. The logical numbers of these DTCs are DTC[0] to DTC[3].

```

Device (CMN6) { // CMN-600 device object for an X * Y mesh where X, Y <= 4

Name (_HID, "ARMHC600")

Name(_CRS, ResourceTemplate () {

// Descriptor for 256 MB of the CFG region at offset PERIPHBASE

QWord Memory (

ResourceConsumer,

// bit 0 of general flags is 0

PosDecode,

MinFixed,

// Range is fixed

MaxFixed,

// Range is Fixed

NonCacheable,

ReadWrite,

// Granularity

0xAFE0000000,

// Min

// Max

OxAFEOFFFFFF,

// Translation

0x001000000,

// Range Length

// ResourceSourceIndex

// Resource Source

// Descriptor Name

CFGR

)

// 16KB memory - mapped address space of the Root Node within CFG

Memory32Fixed (ReadWrite, ROOTNODEBASE, 0x4000, ROOT)

// Interrupt on PMUO overflow, attached to DTC[0], with GSIV = \langle gsiv 0 \rangle

Interrupt (ResourceConsumer, Level, ActiveHigh, Exclusive) {<gsiv0>}

// Interrupt on PMU1 overflow, attached to DTC[1], with GSIV=<gsiv1>

Interrupt (ResourceConsumer, Level, ActiveHigh, Exclusive) {<gsiv1>}

// Interrupt on PMU2 overflow, attached to DTC [2], with GSIV = \langle gsiv 2 \rangle

Interrupt (ResourceConsumer, Level, ActiveHigh, Exclusive) {<gsiv2>}

// Interrupt on PMU3 overflow, attached to DTC [3], with GSIV = \langle gsiv 3 \rangle

Interrupt (ResourceConsumer, Level, ActiveHigh, Exclusive) {<gsiv3>}

})

}

```