# ARM<sup>®</sup> Embedded Trace Macrocell Architecture Specification

#### **ARM Embedded Trace Macrocell Architecture Specification** ETMv4

Copyright © 2012-2014 ARM Limited. All rights reserved.

#### **Release Information**

The Change history table lists the changes made to this document.

|               |         |                   | Change history             |

|---------------|---------|-------------------|----------------------------|

| Date          | Issue   | Confidentiality   | Change                     |

| 28 March 2012 | А       | Confidential Beta | First Beta Release         |

| 22 May 2013   | B (B.a) | Non-Confidential  | Final Release              |

| 21 March 2014 | B.b     | Non-Confidential  | Minor updates to Issue B.a |

#### **Proprietary Notice**

This document is protected by copyright and the practice or implementation of the information herein may be protected by one or more patents or pending applications. No part of this document may be reproduced in any form by any means without the express prior written permission of ARM. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

Unless otherwise stated in the terms of the Agreement, this document is provided "as is". ARM makes no representations or warranties, either express or implied, included but not limited to, warranties of merchantability, fitness for a particular purpose, or non-infringement, that the content of this document is suitable for any particular purpose or that any practice or implementation of the contents of the document will not infringe any third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

To the extent not prohibited by law, in no event will ARM be liable for any damages, including without limitation any direct loss, lost revenue, lost profits or data, special, indirect, consequential, incidental or punitive damages, however caused and regardless of the theory of liability, arising out of or related to any furnishing, practicing, modifying or any use of this document, even if ARM has been advised of the possibility of such damages.

Words and logos marked with <sup>®</sup> or <sup>™</sup> are registered trademarks or trademarks, respectively, of ARM Limited. Other brands and names mentioned herein may be the trademarks of their respective owners. Unless otherwise stated in the terms of the Agreement, you will not use or permit others to use any trademark of ARM Limited.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws.

In this document, where the term ARM is used to refer to the company it means "ARM or any of its subsidiaries as appropriate".

Copyright © 2012-2014 ARM Limited.

110 Fulbourn Road, Cambridge, England CB1 9NJ. All rights reserved.

#### — Note –

The term ARM is also used to refer to versions of the ARM architecture, for example ARMv7 refers to version 7 of the ARM architecture. The context makes it clear when the term is used in this way.

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

# Contents ARM Embedded Trace Macrocell Architecture Specification ETMv4

#### Preface

|           |     | About this document                                  |      |

|-----------|-----|------------------------------------------------------|------|

|           |     | Using this document                                  |      |

|           |     | Conventions                                          | xi   |

|           |     | Additional reading                                   | xii  |

|           |     | Feedback                                             | xiii |

| Chapter 1 |     | Introduction                                         |      |

| -         | 1.1 | Introduction to processing element tracing           | 1-16 |

|           | 1.2 | Introduction to trace units                          | 1-19 |

|           | 1.3 | Introduction to the ETMv4 architecture               | 1-22 |

|           | 1.4 | Terminology used in this document                    |      |

| Chapter 2 |     | About the Trace Streams                              |      |

| -         | 2.1 | The tracing flow                                     | 2-30 |

|           | 2.2 | Separate instruction and data trace streams          |      |

|           | 2.3 | Handling the trace streams                           |      |

|           | 2.4 | Synchronizing the instruction and data trace streams |      |

|           | 2.5 | Synchronization with a trace analyzer                |      |

|           | 2.6 | Trace behavior                                       |      |

|           | 2.7 | Optional features                                    |      |

| Chapter 3 |     | About the Trace Unit                                 |      |

| • • • •   | 3.1 | Functions of the trace unit                          |      |

|           | 3.2 | Trace unit block diagram                             |      |

|           | 3.3 | Trace unit power domains                             |      |

|           |     |                                                      |      |

|             | 3.4        | Trace unit powerdown support                                               | 3-89   |

|-------------|------------|----------------------------------------------------------------------------|--------|

|             | 3.5        | Trace unit behavior                                                        | 3-93   |

|             |            |                                                                            |        |

| Chapter 4   |            | Configuring the Trace Unit                                                 |        |

| enapter     | 4.1        | Filtering models                                                           | 1-106  |

|             | 4.2        | Trace unit resources                                                       |        |

|             | 4.3        | Accessing the trace unit                                                   |        |

|             | 4.3<br>4.4 | Selecting trace unit resources                                             |        |

|             | 4.4<br>4.5 | •                                                                          |        |

|             | 4.5        | Program examples                                                           | 4-171  |

|             |            | Descriptions of Trace Flowents                                             |        |

| Chapter 5   |            | Descriptions of Trace Elements                                             |        |

|             | 5.1        | Elements summary tables                                                    |        |

|             | 5.2        | Descriptions of instruction trace elements                                 |        |

|             | 5.3        | Return stack                                                               |        |

|             | 5.4        | Descriptions of data trace elements                                        | 5-200  |

|             |            |                                                                            |        |

| Chapter 6   |            | Descriptions of Trace Protocols                                            |        |

| -           | 6.1        | About the instruction trace and data trace protocol                        | 6-208  |

|             | 6.2        | Trace analyzer state between receiving packets                             | 6-213  |

|             | 6.3        | Packet header encodings summary tables                                     |        |

|             | 6.4        | Descriptions of instruction trace packets                                  |        |

|             | 6.5        | Descriptions of data trace packets                                         |        |

|             |            |                                                                            |        |

| Chapter 7   |            | Register Descriptions                                                      |        |

|             | 7.1        | Register summary                                                           | 7 200  |

|             | 7.1        | <b>o i</b>                                                                 |        |

|             |            | Access permissions                                                         |        |

|             | 7.3        | ETMv4 registers descriptions, in register name order                       | 1-317  |

| A           |            | Evenueles of Turner                                                        |        |

| Appendix A  |            | Examples of Trace                                                          |        |

|             | A.1        | An example of basic program trace                                          |        |

|             | A.2        | Examples of basic program trace when exceptions occur                      |        |

|             | A.3        | Examples of basic program trace when execution is mispredicted             |        |

|             | A.4        | Examples of basic program trace with cycle counting enabled                | A-398  |

|             | A.5        | Examples of basic program trace with filtering applied                     |        |

|             | A.6        | An example of the use of the trace unit return stack                       |        |

|             | A.7        | Examples of operations that change the execution context                   | A-408  |

|             |            |                                                                            |        |

| Appendix B  |            | Recommended Configurations                                                 |        |

|             | B.1        | Configuration overview                                                     | B-412  |

|             | B.2        | Configuration parameters                                                   | B-413  |

|             |            |                                                                            |        |

| Appendix C  |            | Filtering Examples                                                         |        |

| , ppendix e | C.1        | About the filtering examples                                               | C-416  |

|             | 0.1        |                                                                            | 0 4 10 |

| Appendix D  |            | Posource Selection Examples                                                |        |

| Appendix D  |            | Resource Selection Examples                                                | D 400  |

|             | D.1        | Configuring the ETMv4 to assert an external output on SAC0 or SAC1         |        |

|             | D.2        | Configuring the ETMv4 to set the ViewInst filter on SAC5 or Counter 1 at 0 | D-421  |

|             |            |                                                                            |        |

| Appendix E  |            | Instruction Categories                                                     |        |

|             | E.1        | Branch instructions                                                        |        |

|             | E.2        | Load and store instructions                                                |        |

|             | E.3        | Conditional instructions                                                   |        |

|             | E.4        | Flag setting instructions                                                  | E-431  |

|             | E.5        | 32-bit T32 instructions                                                    | E-432  |

|             |            |                                                                            |        |

| Appendix F  |            | Standard Layout of the External Inputs                                     |        |

| ••          | F.1        | Recommended connection layout                                              | F-434  |

|             |            | ,                                                                          | -      |

# Appendix GPseudocode DefinitionG.1About ARM pseudocodeG-436G.2Data typesG-437G.3ExpressionsG-441G.4Operators and built-in functionsG-443G.5Statements and program structureG-448

#### Appendix H Revisions

Glossary

### Preface

This preface introduces the *Embedded Trace Macrocell (ETM) Architecture Specification*. It contains the following sections:

- About this document on page viii.

- Using this document on page ix.

- Conventions on page xi.

- Additional reading on page xii.

- *Feedback* on page xiii.

#### About this document

This document describes version four of the architecture for the ARM Embedded Trace Macrocell (ETM).

Some features of the ETMv4 architecture are IMPLEMENTATION DEFINED. For more information, see the relevant ETM *Technical Reference Manual* (TRM).

#### Intended audience

This document is written for the following target audiences:

- Designers of development tools providing support for ETMv4 functionality.

- Advanced users of development tools providing support for ETMv4 functionality.

- Designers of trace analyzers for use with ETMv4 trace units.

- Designers of an ARM based product that includes an ETMv4 trace unit.

- Engineers who want to specify, design, or implement an ETM that conforms to the ARM ETMv4 architecture.

Hardware engineers who want to incorporate an ARM ETM into their design must consult the relevant ETM *Technical Reference Manual*. ARM recommends that all users of this specification also have experience of the ARM architecture.

#### Using this document

This document is organized into the following chapters:

#### **Chapter 1** Introduction

Read this for a brief introduction to tracing, and to version four of the ARM ETM architecture.

#### Chapter 2 About the Trace Streams

Read this for a description of the trace streams that are generated by the trace unit. Includes information about the instruction and data trace streams, as well as how they can be synchronized with each other and with a trace analyzer. Also contains a list of optional features that can be implemented in an ETMv4 trace unit architecture.

#### Chapter 3 About the Trace Unit

Read this for an overview of the trace unit and its behavior. Includes information about possible trace unit power domain implementations and power-down support.

#### Chapter 4 Configuring the Trace Unit

Read this for a description of internal structure of the ETMv4 trace unit architecture, and a guide to how it can be programmed. Includes information about the filtering and resource selection logic, and information about how an ETMv4 trace unit can be accessed, either from an external debugger or from the core that it is attached to.

#### **Chapter 5** Descriptions of Trace Elements

Read this for a description of the elements that are generated by the trace unit to indicate the flow of the program being traced. The elements that comprise the instruction and data trace streams are described.

#### **Chapter 6** Descriptions of Trace Protocols

Read this for a description of the packets that are output to indicate the elements in the instruction and data trace streams, as well as the necessary state information that must be retained between packets in order to correctly interpret the trace stream.

#### **Chapter 7** Register Descriptions

Read this for a description of the registers in the ETMv4 trace unit architecture.

#### Appendix A Examples of Trace

Read this for a set of examples of trace obtained by using an ETMv4 trace unit.

#### Appendix B Recommended Configurations

Read this for a set of recommended configurations for trace unit implementations.

#### Appendix C Filtering Examples

Read this for examples of instruction address range filtering, and a listing of the typical trace output for each example.

#### Appendix D Resource Selection Examples

Read this for example configurations for the ETMv4 resource selectors.

#### Appendix E Instruction Categories

Read this for a list of instructions that are classified as branch, load and store, conditional, or flag setting instructions for the purposes of trace generation and analysis.

#### Appendix F Standard Layout of the External Inputs

Read this for recommendations on the number and type of inputs that are available to a trace unit.

#### Appendix G Pseudocode Definition

Read this for a guide to the pseudocode used elsewhere in this document.

#### Appendix H Revisions

Read this for information on the changes between issue A and issue B of this document.

#### Conventions

The following sections describe conventions that this document can use:

- Typographic conventions.

- Signals.

- Numbers.

- Pseudocode descriptions.

#### Typographic conventions

The typographical conventions are:

- *italic* Introduces special terminology, denotes internal cross-references and citations, or highlights an important note.

- **bold** Denotes signal names, and is used for terms in descriptive lists, where appropriate.

- monospace Used for assembler syntax descriptions, pseudocode, and source code examples.

Also used in the main text for instruction mnemonics and for references to other items appearing in assembler syntax descriptions, pseudocode, and source code examples.

#### SMALL CAPITALS

Used for a few terms that have specific technical meanings, and are included in the Glossary.

Colored text Indicates a link. This can be:

- A URL, for example http://infocenter.arm.com.

- A cross-reference, that includes the page number of the referenced information if it is not on the current page, for example, *Pseudocode descriptions*.

- A link, to a chapter or appendix, or to a glossary entry, or to the section of the document that defines the colored term, for example *Trace unit behavior* on page 3-93 or TRCTSCTLR.

#### Signals

In general this document does not define signals but it does include some signal examples and recommendations. The signal conventions are:

| Signal level | The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means: |

|--------------|-------------------------------------------------------------------------------------------------------------|

|              | • HIGH for active-HIGH signals.                                                                             |

|              | • LOW for active-LOW signals.                                                                               |

| Lower-case n | At the start or end of a signal name denotes an active-LOW signal.                                          |

#### Numbers

Numbers are normally written in decimal. Binary numbers are preceded by 0b, and hexadecimal numbers by 0x. In both cases, the prefix and the associated value are written in a monospace font, for example 0xFFFF0000.

#### **Pseudocode descriptions**

This document uses a form of pseudocode to provide precise descriptions of the specified functionality. This pseudocode is written in a monospace font, and is described in Appendix G *Pseudocode Definition*.

#### Additional reading

This section lists relevant publications from ARM and third parties.

See the Infocenter http://infocenter.arm.com, for access to ARM documentation.

#### **ARM** publications

This document contains information that is specific to this specification. See the following documents for other relevant information:

- AMBA® APB Protocol Specification (ARM IHI 0024).

- AMBA® 3 ATB Protocol Specification (ARM IHI 0032).

- ARM<sup>®</sup> CoreSight<sup>™</sup> Architecture Specification (ARM IHI 0029).

- ARM<sup>®</sup> Debug Interface v5 Architecture Specification (ARM IHI 0031).

- ARM® Architecture Reference Manual ARMv7-A and ARMv7-R edition (ARM DDI 0406).

- ARM®v7-M Architecture Reference Manual (ARM DDI 0403).

- ARM<sup>®</sup>v6-M Architecture Reference Manual (ARM DDI 0419).

- ARM<sup>®</sup>v8 Architecture Reference Manual (ARM DDI 0487).

#### Other publications

This section lists relevant documents published by third parties:

• JEDEC, Standard Manufacturers Identification Code, JEP106 http://www.jedec.org.

#### Feedback

ARM welcomes feedback on its documentation.

#### Feedback on this document

If you have comments on the content of this document, send an e-mail to errata@arm.com. Give:

- The title.

- The number, ARM IHI 0064B.b.

- The page numbers to which your comments apply.

- A concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

#### — Note –

ARM tests PDFs only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the appearance or behavior of this document when viewed with any other PDF reader.

Preface Feedback

# Chapter 1 Introduction

This chapter contains a brief introduction to tracing, and to version four of the architecture for ARM's *Embedded Trace Macrocell* (ETM). It contains the following sections:

- Introduction to processing element tracing on page 1-16.

- Introduction to trace units on page 1-19.

- Introduction to the ETMv4 architecture on page 1-22.

- Terminology used in this document on page 1-25.

#### 1.1 Introduction to processing element tracing

In the context of the ETMv4 architecture, the term *tracing*, refers to the tracing of instruction execution, the tracing of data movements, and the tracing of events in a PE.

— Note –

This document describes a *Processing Element (PE)* and trace elements. Trace elements describe the execution of a PE. A *Processing Element* is not a trace element.

A trace unit performs these functions. It is the hardware implementation of a particular functional configuration of an ARM trace architecture. A trace unit might be implemented as part of a full debug solution inside a *System-on-Chip* (SoC), where it traces instructions and data by monitoring the instruction and data buses. A trace unit has the following interfaces:

- A PE interface, that provides visibility of instruction execution and data movements within a PE.

- A programming interface, that is usually connected to a debug port on the chip, such as a *JTAG Access Port* (JTAG-AP) or a *Serial Wire Debug Port* (SW-DP).

- A trace output interface, that is usually a parallel data interface.

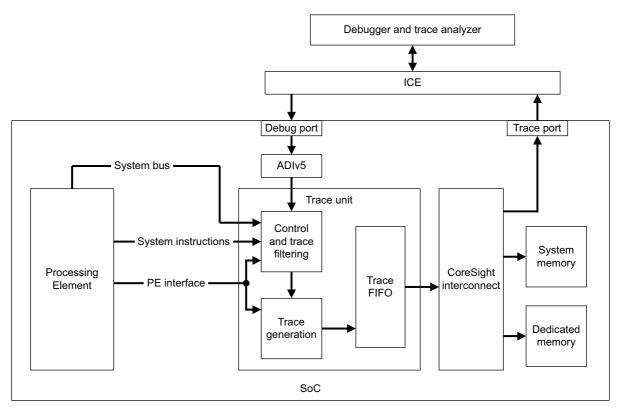

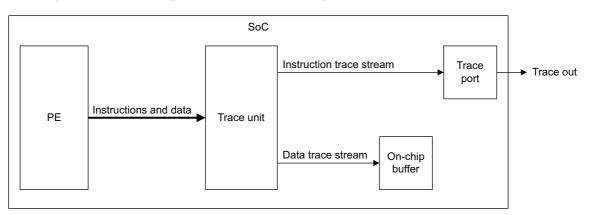

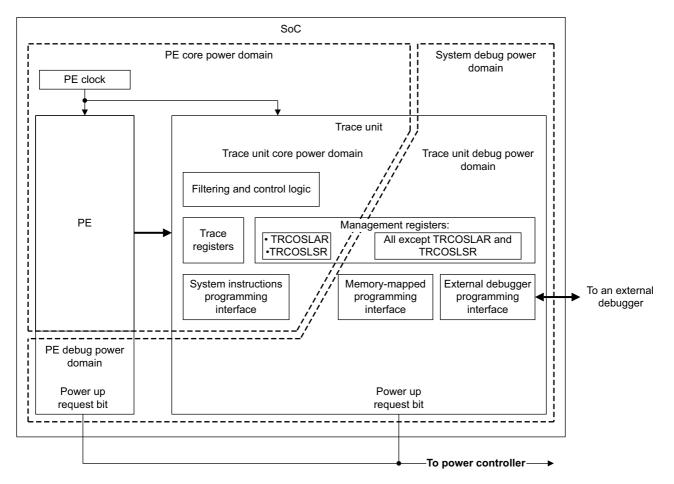

Figure 1-1 shows an example of a trace unit implemented in an SoC.

Figure 1-1 Example SoC with a trace unit

The trace output from a trace unit has several uses. It can be analyzed for:

- System development purposes, such as examining timing issues.

- Diagnosing and fixing bugs.

- PE profiling or performance analysis.

The following sections describe:

- The attributes of PE tracing on page 1-17.

- External debug and self-hosted debug on page 1-17.

#### 1.1.1 The attributes of PE tracing

The attributes of PE tracing are:

- It is done in real-time. This means that the operation of the PE can be observed while it is running. For diagnostic purposes, this is useful because some types of bug and some instances of erroneous behavior can only be solved by observing the system during runtime. In addition, because the PE trace can include cycle counts, it can be used for PE profiling purposes.

- It provides a method of debugging PEs that are deeply embedded within an SoC.

- In most cases, it has no effect on the functional performance of the PE, although this attribute does depend on the market use of the PE being debugged, and on the trace requirements for the PE and the trace solution adopted to meet those requirements. For some markets, some impact on PE performance might be acceptable but for others, most notably in real-time systems, an impact on PE performance might be unacceptable.

#### 1.1.2 External debug and self-hosted debug

Figure 1-1 on page 1-16 shows a system that supports both external debug and self-hosted debug. Either methodology can be adopted.

#### **External debug**

External debug is commonly used in trace applications that require long term logging of behavior. In addition, external debug is more likely to be used when the impact of PE tracing on system performance must be kept to a minimum. For example, external debug might be used:

- For debugging real-time systems.

- When analyzing programs that do not vary their behavior very often.

- For debugging software, where a history of execution is required up to the point of failure.

Exporting the trace off-chip usually involves one of the following methodologies:

#### **Real-time continuous export**

This can be done using either:

- A dedicated trace port that is capable of sustaining the bandwidth of the trace, as shown in Figure 1-1 on page 1-16.

- An existing interface on the SoC, such as a USB or other high speed port.

Use of a dedicated trace port means that the trace can be exported off-chip with zero or minimum effect on system behavior. An existing interface is usually used when system constraints, such as cost or package size, mean that a dedicated trace port is not possible. However, use of an existing interface might impact on system behavior, because it means that the normal interface traffic has to contend with the trace for the use of the port.

#### Short term on-chip capture with subsequent low speed export

This is used when a low cost method of exporting the trace is required, or when system constraints mean that real-time continuous export is not possible. The trace output from the trace unit is stored temporarily on-chip, and then exported using either:

- An existing debug port on the SoC, such as a JTAG-DP or SW-DP.

- Another existing interface on the SoC, such as USB.

Typically, the temporary storage is a circular buffer where, if the buffer is full, newer trace overwrites older trace, so that the buffer always contains the most recent trace. In SoCs that employ ARM CoreSight<sup>™</sup> technology, a dedicated *Embedded Trace Buffer* (ETB) is provided for the on-chip capture of trace.

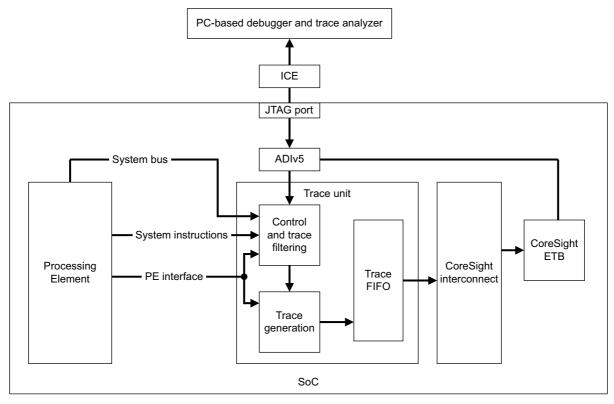

Figure 1-2 on page 1-18 shows an example of short term on-chip capture with subsequent low speed export in a system that uses an ARM CoreSight ETB and a JTAG-DP.

Figure 1-2 Example SoC with a trace unit and a dedicated trace buffer

#### Self-hosted debug

Self-hosted debug is used for a variety of purposes, including:

- Non-invasive single stepping. The trace provides a history of execution similar to that obtained by single-stepping through code.

- Failure logging. This is similar to a stack trace dump when a failure occurs.

- Performance analysis. The trace might be used in conjunction with other trace sources or performance analysis units to analyze program performance.

Capturing the trace on-chip usually involves either:

- Use of a dedicated on-chip buffer, such as the ETB offered by ARM CoreSight technology. If dedicated memory is used, a dedicated bus is also usually implemented between the trace unit and the dedicated memory. This means that PE tracing can be performed with zero or minimal effect on system behavior.

- Use of existing shared system memory, where some main system memory is reserved for trace capture. The trace output from the trace unit is directed to the reserved memory over the main system bus. This means that tracing might affect system behavior, because the trace contends for system bus bandwidth with the normal bus traffic.

#### 1.2 Introduction to trace units

The descriptions given in this section are on different aspects of trace unit operation, that include:

- Trace stream generation and compression techniques.

- Configuring a trace unit before a trace run.

- Filtering of the trace on page 1-20.

- Tracing a PE on page 1-20.

- Trace unit resources on page 1-21.

- Trace unit powerdown support and low power state on page 1-21.

- Sharing a trace unit between multiple PEs on page 1-21.

#### 1.2.1 Trace stream generation and compression techniques

A trace unit compresses the information it obtains at its PE interface and outputs it as one or more trace streams that comprise multiple packets of encoded data.

A trace stream might be output from a trace unit over either a parallel data interface or a serial data interface, depending on the implementation of the trace unit.

Compression techniques that are used include:

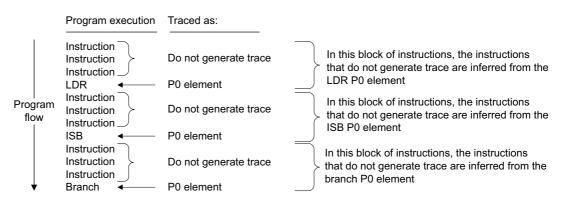

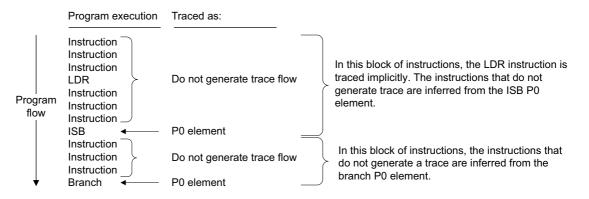

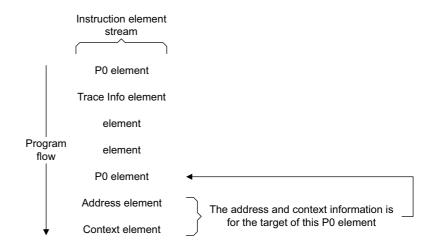

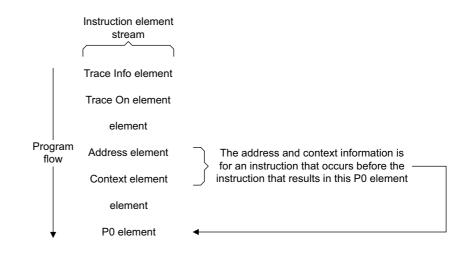

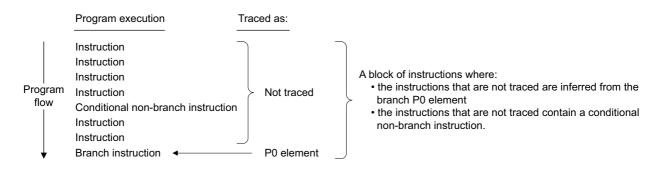

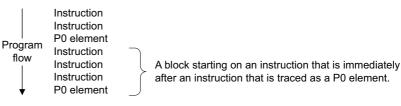

- The instruction trace stream does not contain an element for every instruction that is executed. Instead, the trace unit generates P0 elements in the instruction trace stream when certain types of instruction are executed. A P0 element acts as a sign-post in the program flow, indicating that execution is proceeding along a given branch. As a result, the stream of P0 elements implies the execution of a greater number of instructions, and a trace analyzer can reconstruct the stream of instructions executed between P0 elements by using the P0 element stream and the program image.

- Multiple P0 elements can be encoded into a single P0 packet. See *Atom instruction trace packets on page 6-269*.

- The trace unit can remove program addresses from the trace stream that can be inferred by the trace analyzer from the program image and the previous history of the program. This includes the targets of direct branch instructions, where the target address is encoded in the instruction itself.

- The trace unit can include a return stack, that contains information about the return address for particular instances of certain types of branch instruction. The trace analyzer maintains an independent copy of the return stack, based on the branch instructions it observes in the instruction trace stream. As a result, a trace analyzer can infer some return addresses, and it is possible for the trace unit to avoid generating some Address packets. See *Use of the return stack on page 5-197*

#### 1.2.2 Configuring a trace unit before a trace run

A trace unit includes facilities that can be configured before a trace run, including:

- Filtering of the trace. See *Filtering of the trace on page 1-20*.

- Selecting and configuring any *trace unit resources* that are required for the trace run, such as counters, comparators and external inputs that might be implemented as part of the trace unit. See *Trace unit resources* on page 1-21. These resources can be selected and used to trigger filtering of the trace, or to signal to a trace analyzer that a particular event has occurred in the program the PE is executing.

- Turning on data tracing. Some trace applications require only the tracing of instructions, termed *instruction tracing*, whereas others require the tracing of both instructions and data transfers, such as data loads and stores. The tracing of data transfers is termed *data tracing*. If a trace unit implementation provides support for data tracing, it can be turned on if required.

- Selecting which types of instructions are traced explicitly. All trace unit implementations trace certain instruction types explicitly, such as branch instructions and ISBs, and the execution of other instruction types can be inferred from these instructions. However, if required, an implementation can include support for the explicit tracing of other instruction types, such as data load and store instructions.

If the external debug model is adopted, the PC-based debugger provides the user interface to the trace unit, and can be used to configure the trace unit facilities before each trace run. The debugger also decodes, analyzes, and post-merges the trace data with the program source code, to display the captured trace information.

If the self-hosted debug model is adopted, then depending on the trace unit implementation, either a memory-mapped interface or system instructions, also known as *coprocessor access*, can be used to configure the trace unit.

#### 1.2.3 Filtering of the trace

A trace unit can be configured to filter the trace, so that not everything about program execution is traced. When filtering is applied, only those functions that are of interest, those data transfers that are of interest, or those sequences of code that are of interest, are traced. This can help to manage the bandwidth of the trace that is output from the trace unit.

#### 1.2.4 Tracing a PE

A trace unit traces a PE by generating *trace elements*. These are then encoded into trace packets and output from the trace unit.

Some elements carry information that a trace analyzer requires to enable it to analyze the trace successfully, such as:

- Elements that contain information about which instructions, data or events the trace unit is configured to trace.

- Elements that show the context in which instructions are being executed.

- Elements that signal to a trace analyzer when there is a gap in the trace, and other elements that indicate why the gap has occurred. These enable the trace analyzer to take the appropriate action to maintain the integrity of the trace.

- Elements that enable a trace analyzer to synchronize trace streams if more than one trace stream is output.

Other elements either directly indicate program execution, or carry information about program execution, such as:

- Elements that indicate which branches are executed.

- Elements that indicate the execution of other instruction types, for example, if data tracing is implemented and enabled, elements that indicate load or store instructions.

- Elements that indicate exceptions, and returns from exceptions.

- Elements that indicate the addresses of instructions, and if data tracing is implemented and enabled, elements that contain data values, and elements that indicate addresses that data is transferred to or from.

- Speculation resolution elements, that show whether traced instructions are:

- Canceled because they were executed speculatively and the speculation was incorrect.

- Committed for execution. A trace analyzer must only infer execution when a traced instruction has been committed for execution.

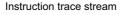

- Elements that show the results of condition code checks, to show whether traced conditional non-branch instructions have been executed, if tracing of conditional non-branch instructions is implemented and enabled.

- Elements that signal to a trace analyzer that a particular event has occurred in the program that the PE is executing.

*Program events* are represented by *trace unit events*, that are activated by *trace unit resources*. For example, a trace unit might be configured to signal when one of its address comparators becomes active as a result of the PE accessing a particular instruction address. In this case:

- The address comparator is the trace unit resource.

- The access performed is the program event.

- The address comparator matching is the trace unit event.

In addition, there are elements that contain timing information, such as:

- Timestamp elements, that contain global timestamp values.

- Cycle Count elements, that show counts of PE clock cycles.

#### 1.2.5 Trace unit resources

A trace unit provides a range of resources that can be implemented and used to trigger the trace unit to begin tracing, or that can be used to program the trace unit to signal to a trace analyzer when particular program events occur. A trace unit implementation might contain any, or all, of the following:

- Counters.

- A sequencer.

- External inputs.

- External outputs.

- Single instruction or data address comparators.

- Instruction or data address range comparators.

- Data value comparators.

- Context identifier (Context ID) comparators.

- Virtual machine identifier (VMID) comparators.

- PE comparator inputs.

- Single-shot comparator controls.

The architecture provides the option to implement a certain number of each resource type. For example, a simple design of a trace unit implementation might contain one counter, four PE comparator inputs, and two external outputs.

#### 1.2.6 Trace unit powerdown support and low power state

A trace unit might include powerdown support, where the trace unit state, that is held in the trace unit registers, can be saved before powering down the trace unit. In addition, a trace unit implementation might include support for entering a low power state. If a trace unit does support low power state, then the low power state is usually invoked whenever the PE being traced enters a low power state.

#### 1.2.7 Sharing a trace unit between multiple PEs

A trace unit might be shared between multiple PEs, to reduce the cost of a system. One PE can be selected to be traced and the trace unit must be disabled when changing the selected PE.

.

#### 1.3 Introduction to the ETMv4 architecture

The ETMv4 architecture introduces the following changes from previous trace architectures from ARM:

- It provides support for addresses that are up to 64 bits wide.

- It provides support for the ARMv8 architecture.

- In addition to instruction tracing, it provides optional support for:

- Data tracing.

- Event tracing.

- Tracing of conditional non-branch instructions.

- It provides better compression than previous trace architectures from ARM.

#### The following sections describe:

- Supported instruction sets.

- *Impact on PE behavior.*

- Trace unit resources.

- Possible functional configurations of an ETMv4 trace unit on page 1-23.

#### 1.3.1 Supported instruction sets

The ETMv4 architecture supports the following instruction sets:

- A64 in AArch64 state.

- A32 and T32 in AArch32 state.

#### — Note —

A32 and T32 are new names for what were the ARM and Thumb instruction sets in ARMv7-A, ARMv7-R, ARMv7-M, and ARMv6-M.

#### 1.3.2 Impact on PE behavior

The ETMv4 architecture places no requirements on the impact that trace generation has on the functional performance of a PE. ARM expects that trace unit implementations are designed according to the market requirements of the PEs being traced, and according to the trace requirements for those PEs. For some markets and trace requirements, the trace solution might always have some performance impact on the PE and the ETMv4 architecture does not prohibit this.

#### 1.3.3 Trace unit resources

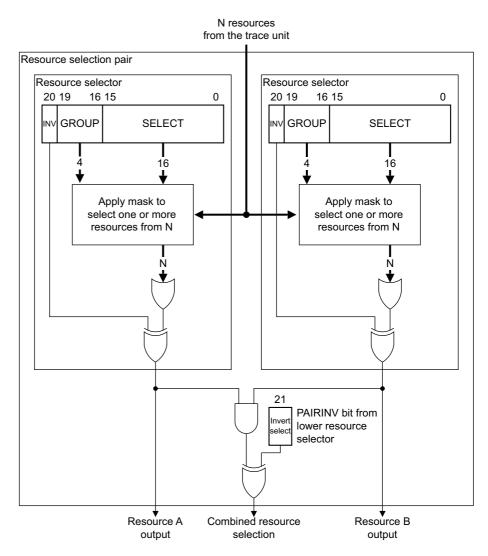

A trace unit provides resource selectors that are used to choose one or more of the trace unit resources. Up to 32 resource selectors are implemented, see *Selecting trace unit resources on page 4-161*.

The ETMv4 architecture provides the resources shown in Table 1-1.

#### Table 1-1 Resources provided by the ETMv4 architecture

| Resource type            | Number available | Notes                                                                                                                                                                                                                     |

|--------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Counters                 | 0-4              | -                                                                                                                                                                                                                         |

| Sequencer state machine  | 0-1              | -                                                                                                                                                                                                                         |

| External input selectors | 0-4              | Each of these can select from up to 256 external inputs to be a trace unit resource.                                                                                                                                      |

| External outputs         | 1-4              | These are used for event tracing and for signaling to a trace analyzer that a particular trace unit event has occurred. As mentioned in <i>Tracing a PE on page 1-20</i> , a trace unit event represents a program event. |

| Resource type                   | Number available | Notes                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Single address comparators      | 0-16             | Single address comparators are implemented in pairs. One pair of single address comparators can be configured to comprise one <i>address range comparator</i> .<br>A single address comparator can be programmed to match on an instruction                                                                                                                                                          |

| Address range comparators       | 0-8              | address or, if data tracing is implemented, on a data address. <sup>a</sup><br>See <i>single address comparators</i> in this table.<br>An address range comparator is programmed with an address range, so that it<br>matches on any address within that range. The address range might be an<br>instruction address range or, if data tracing is implemented, a data address<br>range. <sup>a</sup> |

| Data value comparators          | 0-8              | These are used in conjunction with data address comparators.                                                                                                                                                                                                                                                                                                                                         |

| Context ID comparators          | 0-8              | <ul> <li>Each comparator can be one of the following:</li> <li>Associated with one or more single address comparators.</li> <li>Associated with one or more address range comparators.</li> <li>Used on its own as a trace unit resource.</li> </ul>                                                                                                                                                 |

| VMID comparators                | 0-8              | <ul> <li>Each comparator can be one of the following:</li> <li>Associated with one or more address comparators.</li> <li>Associated with one or more address range comparators.</li> <li>Used on its own as a trace unit resource.</li> </ul>                                                                                                                                                        |

| PE comparator inputs            | 0-8              | -                                                                                                                                                                                                                                                                                                                                                                                                    |

| Single-shot comparator controls | 0-8              | Each control can be used in conjunction with one or more address comparators to signal to a trace analyzer when an accessed instruction or data transfer is nonspeculative.                                                                                                                                                                                                                          |

#### Table 1-1 Resources provided by the ETMv4 architecture (continued)

a. Single address comparators and address range comparators that are programmed to match on instruction addresses are called *instruction address comparators*. Single address comparators and address range comparators that are programmed to match on data addresses are called *data address comparators*.

#### 1.3.4 Possible functional configurations of an ETMv4 trace unit

An ETMv4 *trace unit* is the hardware implementation of a particular functional configuration of the ETMv4 architecture.

An ETMv4 trace unit might support one of several different functional configurations that the ETMv4 architecture permits, giving a trade-off between trace unit functionality and trace unit cost. An implementation might contain all available options that the ETMv4 architecture offers, so that it can provide full instruction and data trace and includes all resources and support for a trace unit low power state. Alternatively, a trace unit might be implemented with only the minimum of functionality, so that it gives only basic program flow trace. Between these two extremes, several intermediate functional configurations are possible. Appendix B *Recommended Configurations* contains some example functional configurations. All implementations support certain features but support for other features is optional. Table 1-2 on page 1-24 summarizes this.

| Function                                 | Always implemented                                                                                                                                                                                                                        | Optional                                                                                                                                      | For more information:                                                                                                                                                                                                             |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Trace stream generation                  | The instruction trace stream.                                                                                                                                                                                                             | For ARM R and M<br>profile PEs, the data<br>trace stream is optional.<br>For ARM A profile PEs,<br>the data trace stream is<br>not permitted. | See Separate instruction and data trace streams on page 2-31.                                                                                                                                                                     |

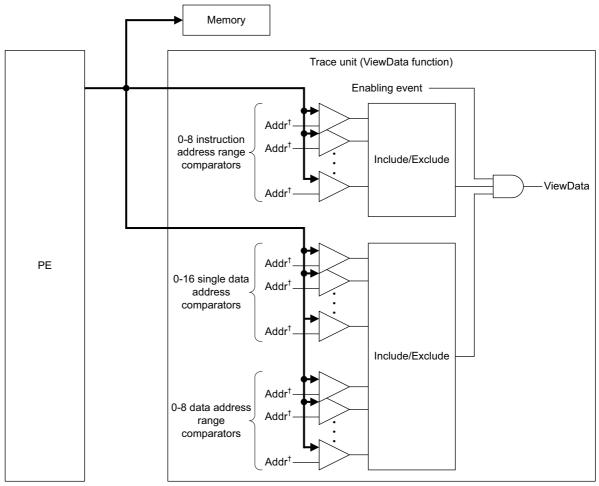

| Filtering                                | The ViewInst function, that is used<br>to filter the instruction trace stream.<br>If data tracing is implemented, the<br>ViewData function is also<br>implemented. The ViewData<br>function is used to filter the data<br>trace stream.   | -                                                                                                                                             | <ul> <li>See:</li> <li>The instruction-based filtering model on page 4-110.</li> <li>The data-based filtering model on page 4-122.</li> </ul>                                                                                     |

| Event tracing<br>and external<br>outputs | At least one external output is<br>always implemented for the purpose<br>of indicating a trace unit event to a<br>trace analyzer. As mentioned on<br>page 1-20, a trace unit event<br>represents a program event.                         | Up to three additional external outputs.                                                                                                      | <ul> <li>See:</li> <li>External outputs on page 4-137.</li> <li>Selecting trace unit resources on page 4-161.</li> <li>Event instruction trace element on page 5-193.</li> <li>Event data trace element on page 5-205.</li> </ul> |

| Powerdown<br>support                     | <ul> <li>The TRCPDCR.</li> <li>The TRCPDSR.</li> <li>In addition, the trace unit state can<br/>be saved before the trace unit is<br/>powered down, so that it can be<br/>restored when the trace unit is<br/>powered up again.</li> </ul> | -                                                                                                                                             | <ul> <li>See:</li> <li>Trace unit powerdown support on page 3-89.</li> <li>TRCPDCR, PowerDown Control Register on page 7-360.</li> <li>TRCPDSR, PowerDown Status Register on page 7-361.</li> </ul>                               |

| Trace unit low power state               | -                                                                                                                                                                                                                                         | Whether the trace unit supports low power state.                                                                                              | See Trace unit behavior on a PE low power state on page 3-98.                                                                                                                                                                     |

#### Table 1-2 A summary of the features of an ETMv4 trace unit

#### 1.4 Terminology used in this document

This section contains:

- General terms used in this document.

- Terms used to describe ETMv4 architectural features on page 1-26.

- Terms used to describe resets on page 1-28.

#### 1.4.1 General terms used in this document

Table 1-3 lists the general terminology this document uses.

#### Table 1-3 General terms used in this document

| Term              | Meaning                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Trace unit        | The hardware implementation used to generate the trace.                                                                                                                                                                                                                                                                                                                        |

| Instruction trace | PE trace that indicates program execution, such as branches taken, the execution of instructions, and exceptions and exception returns.                                                                                                                                                                                                                                        |

|                   | Instruction trace might also contain timing information.                                                                                                                                                                                                                                                                                                                       |

|                   | Instruction trace contains information that a trace analyzer requires to enable it to analyze the trace.                                                                                                                                                                                                                                                                       |

| Data trace        | PE trace that carries information about data transfers that are performed by the PE.                                                                                                                                                                                                                                                                                           |

|                   | Data trace might also contain timing information.                                                                                                                                                                                                                                                                                                                              |

|                   | Data trace contains information that a trace analyzer requires to enable it to analyze the trace.                                                                                                                                                                                                                                                                              |

| Event trace       | PE trace that indicates certain events in the program that the PE is executing. The program events indicated are configured before a trace run.                                                                                                                                                                                                                                |

| ViewInst active   | Both of the following are true:                                                                                                                                                                                                                                                                                                                                                |

|                   | • The trace unit has been configured and is enabled.                                                                                                                                                                                                                                                                                                                           |

|                   | • The ViewInst instruction trace filtering function is permitting instruction tracing, therefore the trace unit i generating instruction trace. The trace unit might also be generating data trace if data tracing is implemented and enabled. In addition, the trace unit might also be generating event trace.                                                               |

| ViewInst inactive | Both of the following are true:                                                                                                                                                                                                                                                                                                                                                |

|                   | • The trace unit has been configured and is enabled.                                                                                                                                                                                                                                                                                                                           |

|                   | • The trace unit is not generating any instruction trace, because the ViewInst filtering function is prohibiting instruction tracing. However, the trace unit might be generating event trace in the instruction trace stream In addition, if data tracing is implemented and enabled, the trace unit might be generating data trace and event trace in the data trace stream. |

|                   | Note                                                                                                                                                                                                                                                                                                                                                                           |

|                   | A trace unit can only generate data trace for instructions that are traced.                                                                                                                                                                                                                                                                                                    |

| ViewData active   | All of the following are true:                                                                                                                                                                                                                                                                                                                                                 |

|                   | • The trace unit implementation supports data tracing.                                                                                                                                                                                                                                                                                                                         |

|                   | • The trace unit has been configured and is enabled. As part of this process, data tracing has been enabled.                                                                                                                                                                                                                                                                   |

|                   | • The ViewData data trace filtering function is permitting data tracing, therefore the trace unit is generating data trace. If ViewInst is active, the trace unit is also generating instruction trace and in addition, the trace unit might also be generating event trace in both trace streams.                                                                             |

|                   | Note                                                                                                                                                                                                                                                                                                                                                                           |

|                   | A trace unit can only generate data trace for instructions that are traced.                                                                                                                                                                                                                                                                                                    |

|                   |                                                                                                                                                                                                                                                                                                                                                                                |

| Term                                | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ViewData inactive                   | <ul><li>All of the following are true:</li><li>The trace unit implementation supports data tracing.</li></ul>                                                                                                                                                                                                                                                                                                                                                                         |

|                                     | <ul> <li>The trace unit has been configured and is enabled. As part of this process, data tracing has been enabled.</li> <li>The trace unit is not generating any data trace because the ViewData filtering function is prohibiting data tracing. The trace unit might be generating instruction trace if ViewInst is active. In addition, the trace unit might be generating event trace in both trace streams.</li> </ul>                                                           |

| Trace buffer<br>overflow            | Buffering inside the trace unit is unable to capture more trace data.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Trace analyzer                      | A tool that takes the trace streams and analyzes them to determine PE execution. This tool can be part of a self-hosted debug environment, or an external debug tool.                                                                                                                                                                                                                                                                                                                 |

| Trace run                           | When the trace unit is enabled, it starts a trace run.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Element stream                      | A stream of trace elements generated by a trace unit. Trace elements are encoded into trace packets.                                                                                                                                                                                                                                                                                                                                                                                  |

| Packet stream                       | A stream of trace packets output by a trace unit.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Analysis of the trace stream        | <ul> <li>This term refers to the process of:</li> <li>Tracing elements that carry information that a trace analyzer requires to enable it to analyze the trace successfully.</li> <li>Tracing elements that either directly indicate program execution, or carry information about program execution.</li> <li>A trace stream might also contain trace elements that contain timing information.</li> <li>This term is distinct from <i>analysis of program execution</i>.</li> </ul> |

| Analysis of<br>program<br>execution | A trace analyzer contains a program image for the program that the PE is executing. When a trace analyzer analyzes trace elements that directly indicate program execution, and elements that carry information about program execution, it uses the program image to ascertain the instructions being executed. This term refers to that process.                                                                                                                                    |

| Speculation depth                   | The number of traced P0 elements that are uncommitted. When a P0 element is traced, it remains speculative until it is either canceled or committed for execution. For more information, see <i>About instruction trace P0 elements on page 2-33</i> .                                                                                                                                                                                                                                |

| Program image                       | A copy of the compiled executable that is being executed on the PE being traced.                                                                                                                                                                                                                                                                                                                                                                                                      |

#### Table 1-3 General terms used in this document (continued)

#### 1.4.2 Terms used to describe ETMv4 architectural features

Table 1-4 lists the architectural terminology this document uses.

#### Table 1-4 Terms used to describe ETMv4 architectural features

| Term            | Meaning                                                                                                                                                     |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Implemented     | The feature is included in the implementation.                                                                                                              |

| Not implemented | The feature is not included in the implementation.                                                                                                          |

| Enabled         | The feature is implemented and has been configured to operate at runtime. However, because of other trace unit conditions, the feature might not be active. |

#### Table 1-4 Terms used to describe ETMv4 architectural features (continued)

| Term     | Meaning                                                                                                                                 |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Disabled | The feature is either not implemented, or is implemented but has been configured to be disabled during the trace run.                   |

| Active   | The feature is implemented and enabled, and the trace unit is in a state that the feature is configured to operate in.                  |

| Inactive | The feature is either not implemented or is disabled, or the trace unit is in a state that the feature is configured not to operate in. |

Some usage examples of these terms are:

#### Implemented and not implemented

For example, the ETMv4 architecture supports the implementation of up to eight pairs of single address comparators, pairs 0-7. If an implementation contains only four pairs of single address comparators, then pairs 0-3 are implemented and pairs 4-7 are not implemented.

#### Implemented but disabled

For example, cycle-counting might be included in an implementation but it might not be required for a particular trace run. Therefore, if the trace unit is configured not to use cycle counting during that trace run, the feature is implemented but disabled.

#### Implemented and enabled, and active or inactive

For example, branch broadcasting might be included in an implementation and might be required for a particular trace run, but only when the PE executes instructions from a particular memory region. In this case, if the trace unit is configured to use branch broadcasting for these memory regions during a trace run, then:

- When the program is executing from inside the memory region, branch broadcasting is implemented, enabled and active.

- When the program is executing from outside the memory region, branch broadcasting is implemented and enabled, but inactive.

#### 1.4.3 Terms used to describe resets

Table 1-5 lists the reset terminology this document uses.

Table 1-5 Terms used to describe resets

| Term           | Meaning                                                                                                                                                                  |  |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PE reset       | The PE has been through a reset procedure and has restarted execution from its reset state.                                                                              |  |  |

|                | This does not reset any trace unit registers, unless one of the following occurs at the same time:                                                                       |  |  |

|                | • A trace unit reset.                                                                                                                                                    |  |  |

|                | An external trace reset.                                                                                                                                                 |  |  |

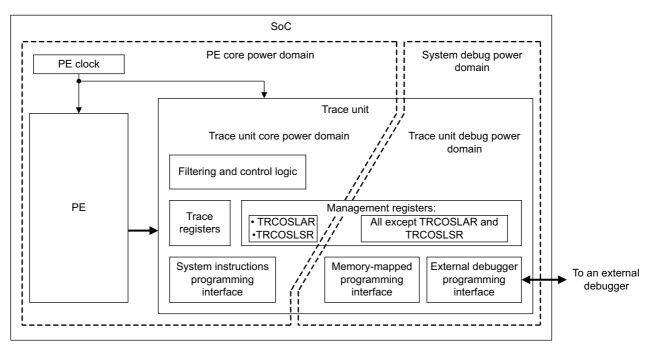

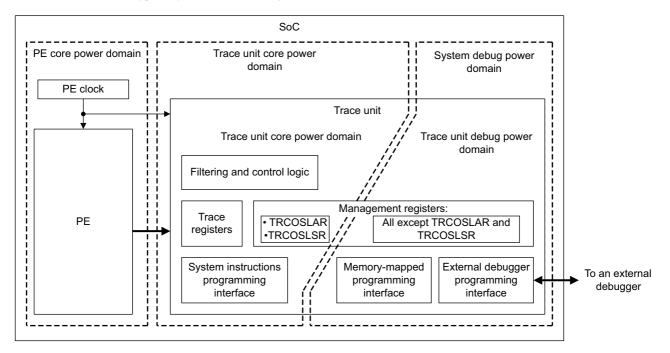

| Trace unit     | This resets all trace unit registers that are located in the trace unit core power domain. These include:                                                                |  |  |

| reset          | • All trace unit <i>trace registers</i> .                                                                                                                                |  |  |

|                | • Some trace unit <i>management registers</i> , that is, TRCOSLAR and TRCOSLSR.                                                                                          |  |  |

|                | Register map overview on page 4-153 shows which registers are trace registers and which are management registers.                                                        |  |  |

|                | This reset is usually only applied on a trace unit core power domain powerup. For more information, see <i>Trace unit behavior on a trace unit reset on page 3-93</i> .  |  |  |

| External trace | This resets all trace unit registers that are located in the trace unit debug power domain. These include:                                                               |  |  |

| reset          | All trace unit management registers except TRCOSLAR and TRCOSLSR.                                                                                                        |  |  |

|                | Register map overview on page 4-153 shows which registers are trace registers and which are management registers.                                                        |  |  |

|                | This reset is usually only applied on a trace unit debug power domain powerup. For more information, see <i>Trace unit behavior on a trace unit reset on page 3-93</i> . |  |  |

## Chapter 2 About the Trace Streams

This chapter describes the trace streams that are generated by the trace unit. It contains the following sections:

- The tracing flow on page 2-30.

- Separate instruction and data trace streams on page 2-31.

- *Handling the trace streams on page 2-38.*

- Synchronizing the instruction and data trace streams on page 2-39.

- Synchronization with a trace analyzer on page 2-61.

- Trace behavior on page 2-66.

- Optional features on page 2-76.

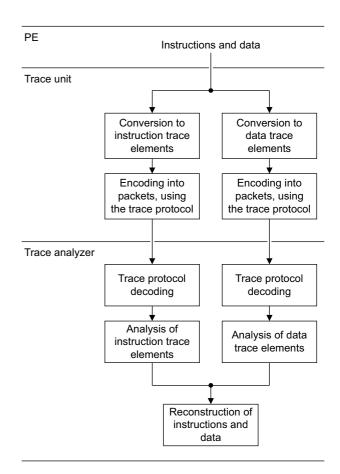

#### 2.1 The tracing flow

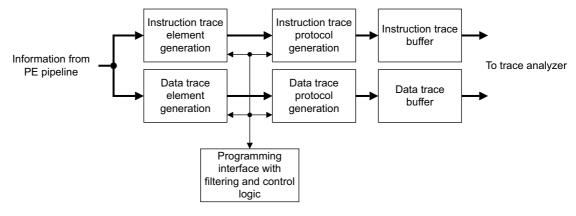

A ETMv4 trace unit traces *processing element*, or PE, execution by generating *trace elements*. The ETMv4 architecture defines the generation of these trace elements from the execution of the PE.

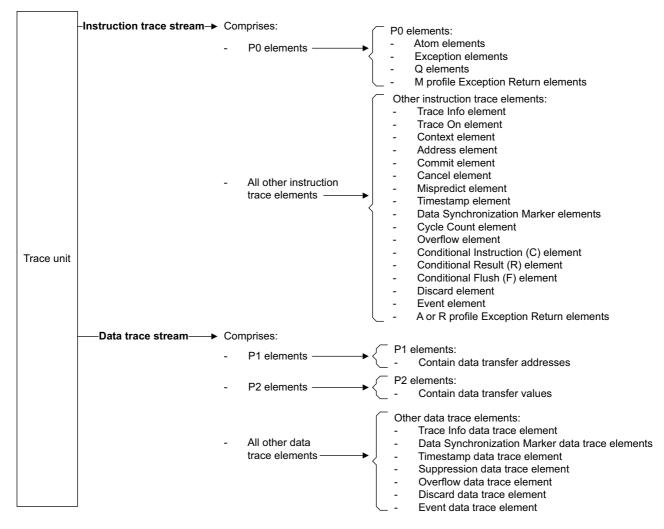

An ETMv4 trace unit can generate two trace element streams:

- An instruction trace element stream.

- A data trace element stream, if data tracing is implemented and enabled.

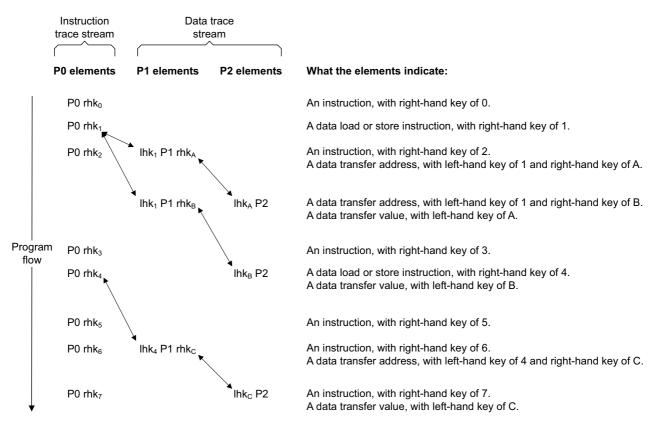

These are then encoded into two streams of trace packets:

- A stream of instruction trace packets.

- A stream of data trace packets.

The encoding process uses compression techniques to reduce the amount of trace generated, thereby improving transmission efficiency and reducing the trace storage requirement. For more information, see *Trace stream generation and compression techniques on page 1-19*.

On receiving a trace stream, an analyzer decodes the data and then analyzes each trace element to infer program execution.

Figure 2-1 shows the tracing flow.

#### Figure 2-1 The tracing flow

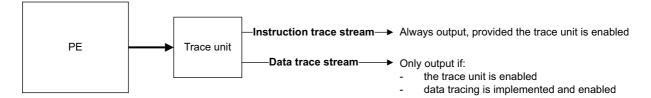

#### 2.2 Separate instruction and data trace streams

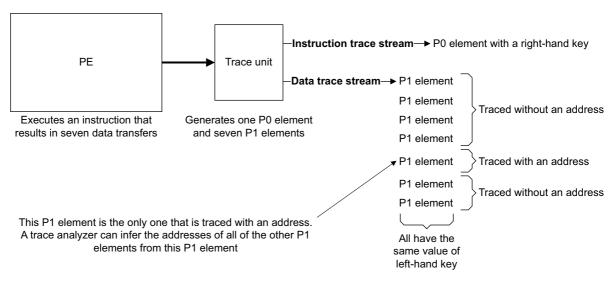

As mentioned in *The tracing flow on page 2-30*, an ETMv4 trace unit outputs an instruction trace stream and in addition, if data tracing is implemented and if configured to do so, a data trace stream, as shown in Figure 2-2.

#### Figure 2-2 Separate instruction and data trace streams

Each trace stream can be filtered:

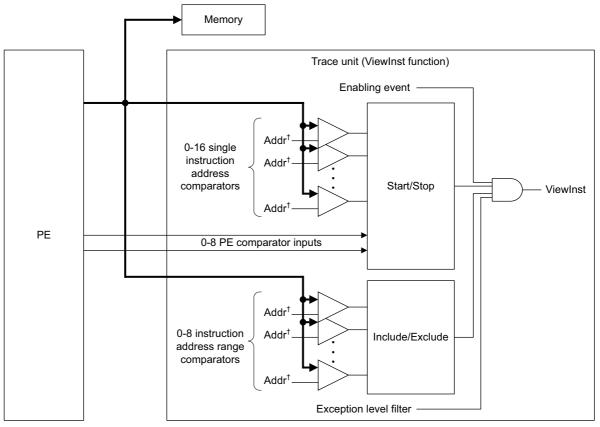

- The trace unit includes a ViewInst function that can be used to filter the instruction trace stream.

- If data tracing is implemented, the trace unit includes a ViewData function that can be used to filter the data trace stream.

If data tracing is implemented, the data trace stream is enabled by setting either or both of the following to 1:

- TRCCONFIGR.DA. When this bit is set to 1, whenever the PE initiates a data load or store transfer and if ViewData permits it to be traced, the address of that data transfer is output in the data trace stream:

- If the transfer is a data load, the address that is output is the address that the data is loaded from.

- If the transfer is a data store, the address that is output is the address that the data is stored to.

- TRCCONFIGR.DV. When this bit is set to 1, whenever the PE initiates a data load or store transfer and if ViewData permits it to be traced, the data value of that data transfer is output in the data trace stream.

```

——Note —

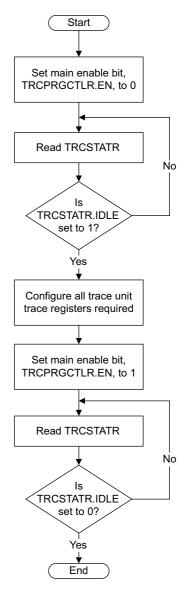

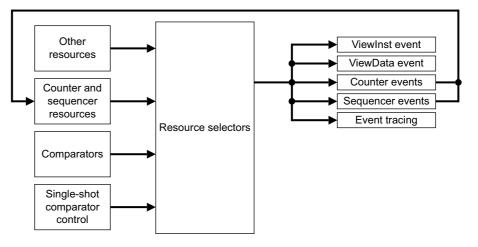

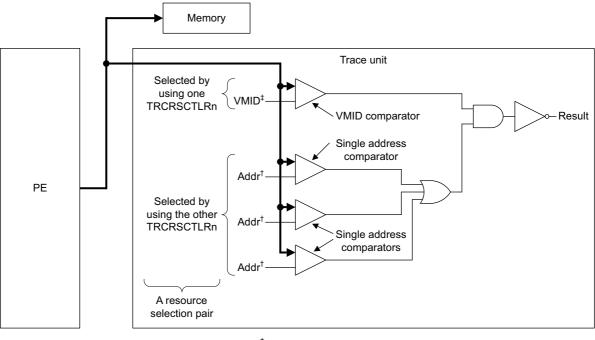

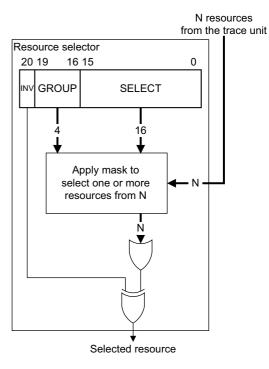

```