# Arm® Architecture Reference Manual Supplement Armv8, for Armv8-R AArch64 architecture profile

## Arm Architecture Reference Manual Supplement Army8. for Army8-R AArch64 architecture profile

Copyright © 2019-2020 Arm Limited or its affiliates. All rights reserved.

#### **Release Information**

The following changes have been made to this document.

#### Release history

| Date             | Issue | Confidentiality  | Change                                                                                    |

|------------------|-------|------------------|-------------------------------------------------------------------------------------------|

| 14 January 2020  | A.a   | Confidential     | Beta release                                                                              |

| 19 June 2020     | A.b   | Confidential     | Second beta release                                                                       |

| 7 September 2020 | A.c   | Non-Confidential | Initial EAC release of the PMSA architecture, first Beta release of the VMSA architecture |

#### **Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with \* or ™ are registered trademarks or trademarks of Arm Limited (or its affiliates) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. You must follow the Arm's trademark usage guidelines http://www.arm.com/company/policies/trademarks.

Copyright © 2019-2020 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England. 110 Fulbourn Road, Cambridge, England CB1 9NJ.

(LES-PRE-20349 version 21.0)

In this document, where the term Arm is used to refer to the company it means "Arm or any of its affiliates as appropriate".

- The term Arm can refer to versions of the Arm architecture, for example Armv8 refers to version 8 of the Arm architecture.

The context makes it clear when the term is used in this way.

- This document describes only the Armv8-R AArch64 architecture profile. For the behaviors required by the Armv8-A architecture, see the Arm<sup>®</sup> Architecture Reference Manual Armv8, for Armv8-A architecture profile.

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

#### **Product Status**

This manual covers two memory system architectures, Protected Memory System Architecture (PMSAv8-64) and Virtual Memory System Architecture (VMSAv8-64). The information related to PMSAv8-64 as described in Chapter C1 *Protected Memory System Architecture* is at EAC quality. EAC quality means that all features of the specification are described in the manual.

The information related to VMSAv8-64 as described in Chapter D1 Virtual Memory System Architecture is at Beta quality. Beta quality means that:

- All major features of the specification are described in the manual, some details might be missing.

- Information can be used for software development at risk.

- Information should not be used for hardware development.

#### Web Address

http://www.arm.com

#### Limitations of this issue

This issue of the Arm® Architecture Reference Manual Supplement Armv8, for Armv8-R AArch64 architecture profile contains many improvements and corrections. Validation of this document has identified the following issues that Arm will address in future issues:

- The references to LDLAR, LDLARH, and SMC instructions are present in register descriptions.

- In Part I Architectural Pseudocode:

- The functions that address both AArch32 and AArch64 functionality might contain cases, comments, or references that apply to only AArch32 state, EL3 Exception level, Monitor mode, Non-secure state, or other features that are not supported in Armv8-R AArch64, and are therefore not applicable to the Armv8-R AArch64 architecture.

- Some functions and comments might contain information that is related to the short-descriptor format that is not applicable to the Armv8-R AArch64 architecture.

- Assertions that are not applicable to Armv8-R AArch64 might be present.

- Enumerations might contain values that are not applicable to Armv8-R AArch64.

- Tests might contain clauses that always return TRUE or FALSE in AArch64 state and there could be potentially redundant tests in the Armv8-R AArch64 architecture. For example, in Armv8-R AArch64:

- UsingAArch32() always returns FALSE.

- IsSecure always returns TRUE.

### Contents

## Arm Architecture Reference Manual Supplement Armv8, for Armv8-R AArch64 architecture profile

|            |      | Preface                                                             |             |

|------------|------|---------------------------------------------------------------------|-------------|

|            |      | About this supplement                                               | x           |

|            |      | Using this book                                                     |             |

|            |      | Conventions                                                         |             |

|            |      | Additional reading                                                  |             |

|            |      | Feedback                                                            |             |

| Part A     |      | Introduction and Architecture Overview                              |             |

| Chapter A1 |      | Architecture Overview                                               |             |

|            | A1.1 | About the Armv8 architecture                                        | A1-20       |

|            | A1.2 | Architecture profiles                                               | A1-21       |

|            | A1.3 | The Armv8-R AArch64 architecture profile                            | A1-22       |

|            | A1.4 | Architecture extensions                                             | A1-23       |

|            | A1.5 | Supported extensions in Armv8-R AArch64                             | A1-26       |

| Part B     |      | Differences between the Armv8-A AArch64 a Armv8-R AArch64 Profiles  | nd the      |

| Chapter B1 |      | Differences between the Armv8-A AArch64 and the Armv                | 8-R AArch64 |

|            | B1.1 | Differences from the Armv8-A AArch64 application level architecture | B1-30       |

|            | B1.2 | Differences from the Armv8-A AArch64 system level architecture      |             |

| Part C     |       | Armv8-R AArch64 Protected Memory Systeture          | m Architec-  |

|------------|-------|-----------------------------------------------------|--------------|

| Chapter C1 |       | Protected Memory System Architecture                |              |

| •          | C1.1  | About the Protected Memory System Architecture      | C1-36        |

|            | C1.2  | Memory Protection Unit                              |              |

|            | C1.3  | Address translation regimes                         |              |

|            | C1.4  | Default memory map                                  | C1-39        |

|            | C1.5  | Armv8-A memory view                                 | C1-40        |

|            | C1.6  | MPU memory translations and faults                  | C1-41        |

|            | C1.7  | Protection region attributes and access permissions | C1-49        |

|            | C1.8  | MPU fault encodings                                 | C1-53        |

|            | C1.9  | PMSAv8-64 implications for caches                   | C1-54        |

|            | C1.10 | Address tagging and pointer authentication support  |              |

|            | C1.11 | Security model                                      | C1-56        |

|            | C1.12 | Virtualization                                      | C1-59        |

| Part D     |       | Armv8-R AArch64 Virtual Memory System               | Architecture |

| Chapter D1 |       | Virtual Memory System Architecture                  |              |

|            | D1.1  | About the Virtual Memory System Architecture        | D1-64        |

|            | D1.2  | Architecture extensions in VMSAv8-64                |              |

|            | D1.3  | Support for VMSAv8-64 in Armv8-R AArch64            |              |

|            | D1.4  | System registers access control                     |              |

|            | D1.5  | Virtualization                                      |              |

|            | D1.6  | System operations                                   |              |

| Part E     |       | A64 Instruction Set for Armv8-R AArch64             |              |

| Chapter E1 |       | A64 Instruction Set for Armv8-R AArch64             |              |

| Onapter E1 | E1.1  | Instruction encodings                               | E1 71        |

|            | E1.1  | A64 instructions in Armv8-R AArch64                 |              |

| Part F     |       | The A64 System Instructions                         |              |

| Chapter F1 |       | The A64 System Instructions                         |              |

|            | F1.1  | System instructions                                 | F1-84        |

| Part G     |       | Armv8-R AArch64 System Registers                    |              |

| Chapter G1 |       | System Registers in a PMSA Implementation           |              |

|            | G1.1  | System register groups                              | G1-88        |

|            | G1.2  | Accessing MPU memory region registers               |              |

|            | G1.3  | General system control registers                    |              |

|            | G1.4  | Debug registers                                     |              |

|            | G1.5  | Performance Monitors registers                      |              |

| Chapter G2 |       | System Registers in a VMSA Implementation           |              |

|            | G2.1  | General system control registers                    | G2-258       |

| Part H Armv8-R AArch64 External Debug Registers |              |                                                                                | isters |

|-------------------------------------------------|--------------|--------------------------------------------------------------------------------|--------|

| Chapter H1                                      | H1.1<br>H1.2 | External Debug Registers Descriptions About the external debug registers       |        |

| Part I                                          |              | Architectural Pseudocode                                                       |        |

| Chapter I1                                      | I1.1<br>I1.2 | Armv8-R AArch64 Pseudocode Pseudocode for AArch64 operations Shared pseudocode |        |

|                                                 |              | Glossary                                                                       |        |

### **Preface**

This preface introduces the Arm® Architecture Reference Manual Supplement Armv8, for Armv8-R AArch64 architecture profile. It contains the following sections:

- *About this supplement* on page x.

- Using this book on page xi.

- Conventions on page xiii.

- Additional reading on page xiv.

- Feedback on page xv.

#### About this supplement

This supplement describes the changes that are introduced by the Armv8-R AArch64 architecture. For a summary of these changes, see *The Armv8-R AArch64 architecture profile* on page A1-22.

The supplement must be read with the most recent issue of the *Arm*\* *Architecture Reference Manual Armv8, for Armv8-A architecture profile*. Together, that manual and this supplement provide a full description of the Armv8-R AArch64 architecture.

This manual is organized into parts as described in *Using this book* on page xi.

#### Using this book

The purpose of this book is to describe the changes that are introduced by the Armv8-R AArch64 architecture. It describes the Armv8-R AArch64 profile in terms of how it differs from the Armv8-A AArch64 profile.

This book is a supplement to the Arm® Architecture Reference Manual Armv8, for Armv8-A architecture profile, (ARM DDI 0487), and is intended to be used with it. There might be inconsistencies between this supplement and the Armv8-A Architecture Reference Manual due to some late-breaking changes. Therefore, the Armv8-A Architecture Reference Manual is the definitive source of information about Armv8-A.

It is assumed that the reader is familiar with the Army8-A and Army8-R architectures.

The information in this book is organized into parts, as described in this section:

#### Part A, Introduction and Architecture Overview

#### Chapter A1 Architecture Overview

Provides an introduction to the Armv8 architecture, the Armv8-R AArch64 architecture profile, and the architecture extensions supported in Armv8-R AArch64.

#### Part B, Differences between the Armv8-A AArch64 and the Armv8-R AArch64 Profiles

#### Chapter B1 Differences between the Armv8-A AArch64 and the Armv8-R AArch64 Profiles

Describes the system level and application level architectural differences between the Armv8-A AArch64 and the Armv8-R AArch64 profiles.

#### Part C, Protected Memory System Architecture

#### Chapter C1 Protected Memory System Architecture

Read this for a system level view of the Army8-R AArch64 Protected Memory System Architecture.

#### Part D, Virtual Memory System Architecture

#### Chapter D1 Virtual Memory System Architecture

Read this for a system level view of the Armv8-R AArch64 Virtual Memory System Architecture.

#### Part E, A64 Instruction Set for Armv8-R AArch64

#### Chapter E1 A64 Instruction Set for Armv8-R AArch64

Read this for descriptions of the A64 instructions that are added or affected by the Armv8-R AArch64 architecture profile.

#### Part F, The A64 System Instructions

#### Chapter F1 The A64 System Instructions

Read this for the descriptions of A64 System instructions.

#### Part G, Armv8-R AArch64 System Registers

Part G describes the System registers for Armv8-R AArch64. It contains the following chapters:

#### Chapter G1 System Registers in a PMSA Implementation

Read this for descriptions of Armv8-R AArch64 System registers in a Protected Memory System Architecture (PMSAv8-64) implementation.

#### Chapter G2 System Registers in a VMSA Implementation

Read this for descriptions of Armv8-R AArch64 System registers in a Virtual Memory System Architecture (VMSAv8-64) implementation.

#### Part H, Armv8-R AArch64 External Debug Registers

#### Chapter H1 External Debug Registers Descriptions

Read this for descriptions of the External debug registers that are added or affected by the Armv8-R AArch64 architecture profile.

#### Part I, Architectural Pseudocode

#### Chapter I1 Armv8-R AArch64 Pseudocode

Contains pseudocode that describes various features of the Armv8-R AArch64 architecture profile.

#### Glossary

| Defines terms used in this document that have a specialized meaning.                                              |

|-------------------------------------------------------------------------------------------------------------------|

| Note  Terms that are generally well understood in the microelectronics industry are not included in the Glossary. |

#### Conventions

The following sections describe conventions that this book can use:

- Typographic conventions.

- Signals.

- Numbers.

- Pseudocode descriptions.

#### Typographic conventions

The following table describes the typographic conventions:

#### Typographic conventions

| Style          | Purpose                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| italic         | Introduces special terminology, and denotes citations.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| bold           | Denotes signal names, and is used for terms in descriptive lists, where appropriate.                                                                                                                                                                                                                                                                                                                                                         |  |  |

| monospace      | Used for assembler syntax descriptions, pseudocode, and source code examples.  Also used in the main text for instruction mnemonics and for references to other items appearing in assembler syntax descriptions, pseudocode, and source code examples.                                                                                                                                                                                      |  |  |

| SMALL CAPITALS | Used in body text for a few terms that have specific technical meanings, and are included in the <i>Glossary</i> in the <i>Arm</i> * <i>Architecture Reference Manual Armv8, for Armv8-A architecture profile.</i>                                                                                                                                                                                                                           |  |  |

| Colored text   | <ul> <li>Indicates a link. This can be:</li> <li>A URL, for example https://developer.arm.com.</li> <li>A cross-reference, that includes the page number of the referenced information if it is not on the current page, for example, <i>Pseudocode descriptions</i>.</li> <li>A link, to a chapter or appendix, or to a glossary entry, or to the section of the document that defines the colored term, for example Chapter A1.</li> </ul> |  |  |

#### **Signals**

In general this specification does not define processor signals, but it does include some signal examples and recommendations.

The signal conventions are:

#### Signal level

The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

- HIGH for active-HIGH signals.

- LOW for active-LOW signals.

#### Lowercase n

At the start or end of a signal name denotes an active-LOW signal.

#### **Numbers**

Numbers are normally written in decimal. Binary numbers are preceded by 0b, and hexadecimal numbers by 0x. In both cases, the prefix and the associated value are written in a monospace font, for example 0xFFFF0000.

#### Pseudocode descriptions

This book uses a form of pseudocode to provide precise descriptions of the specified functionality.

#### **Additional reading**

This section lists relevant publications from Arm and third parties.

See Developer, https://developer.arm.com, for access to Arm documentation.

#### **Arm publications**

- Arm® Architecture Reference Manual, Armv7-A and Armv7-R edition (ARM DDI 0406).

- Arm® Architecture Reference Manual Armv8, for Armv8-A architecture profile (ARM DDI 0487).

- *Arm® CoreSight™ Architecture Specification v3.0* (ARM IHI 0029).

- Arm® Embedded Trace Macrocell Architecture Specification, ETMv4.0 to ETMv4.5 (ARM IHI 0064).

- Arm® Generic Interrupt Controller Architecture Specification, GIC architecture version 3 and version 4 (ARM IHI 0069).

#### Other publications

JEDEC Solid State Technology Association, Standard Manufacturer's Identification Code, JEP106.

#### **Feedback**

Arm welcomes feedback on its documentation.

#### Feedback on this book

If you have comments on the content of this book, send an e-mail to errata@arm.com. Give:

- The title, Arm® Architecture Reference Manual Supplement Armv8, for Armv8-R AArch64 architecture profile.

- The number, ARM DDI 0600A.c.

- The page numbers to which your comments apply.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

| ——— Note ———                                                                                                |

|-------------------------------------------------------------------------------------------------------------|

| Arm tests PDFs only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the appearance or behavior of |

| any document when viewed with any other PDF reader.                                                         |

Preface Feedback

## Part A Introduction and Architecture Overview

## Chapter A1 **Architecture Overview**

This chapter introduces the Armv8 architecture, the architecture profiles it defines, and the Armv8-R AArch64 profile that this manual defines. It contains the following sections:

- About the Armv8 architecture on page A1-20.

- *Architecture profiles* on page A1-21.

- The Armv8-R AArch64 architecture profile on page A1-22.

- *Architecture extensions* on page A1-23.

- Supported extensions in Armv8-R AArch64 on page A1-26.

#### A1.1 About the Armv8 architecture

The Arm architecture that this Architecture Reference Manual describes, defines the behavior of an abstract machine, referred to as a *processing element* (PE). The implementations that are compliant with the Arm architecture must conform to the described behavior of the PE. This manual does not describe how to build an implementation of the PE, nor does it limit the scope of such implementations beyond the defined behaviors.

Except where the architecture specifies differently, the programmer-visible behavior of an implementation that is compliant with the Arm architecture must be the same as a simple sequential execution of the program on the PE. This programmer-visible behavior does not include the execution time of the program.

The Arm Architecture Reference Manual also describes rules for software to use the PE.

The Arm architecture includes definitions of:

- An associated debug architecture.

- Associated trace architectures, which define trace macrocells that implementers can implement with the associated processor hardware.

The Arm architecture is a *Reduced Instruction Set Computer* (RISC) architecture with the following RISC architecture features:

- A large uniform register file.

- A load/store architecture, where data-processing operations only operate on register contents, not directly on memory contents.

- Simple addressing modes, with all *load/store* addresses determined from register contents and instruction fields only.

The architecture defines the interaction of the PE with memory, including caches, and includes a memory translation system. It also describes how multiple PEs interact with each other and with other observers in a system. This document defines the Armv8-R AArch64 architecture profile. See *The Armv8-R AArch64 architecture profile* on page A1-22 for more information.

The Arm architecture supports implementations across a wide range of performance points. Implementation size, performance, and low power consumption are key attributes of the Arm architecture.

See *Conventions* on page xiii for information about conventions used in this manual, including the use of SMALL CAPS for particular terms that have Arm-specific meanings that are defined in the *Glossary*.

#### A1.1.1 See also

- Introduction to the Armv8 Architecture.

- Armv8 architectural concepts.

#### A1.2 Architecture profiles

The Arm architecture has evolved significantly since its introduction, and Arm continues to develop it. Eight major versions of the architecture have been defined to date, denoted by the version numbers 1 to 8. Of these, the first three versions are now obsolete.

Armv8 defines three architecture profiles:

#### **A** Application profile:

- Supports a Virtual Memory System Architecture (VMSA) based on a Memory Management Unit (MMU).

- Supports the A32, T32, and A64 instruction sets.

#### R Real-time profile:

- Supports the AArch64 or AArch32 Execution states.

- Supports A64, or A32 and T32 instruction sets.

- Supports a Protected Memory System Architecture (PMSA) based on a Memory Protection Unit (MPU).

- Supports a VMSA based on an MMU.

#### M Microcontroller profile:

- Implements a programmers' model that is designed for low-latency interrupt processing, with hardware stacking of registers and support for writing interrupt handlers in high-level languages.

- Supports a PMSA based on an MPU.

- Supports a variant of the T32 instruction set.

For more information, see *Introduction to the Armv8 Architecture* chapter of the *Armv8 Architecture Reference Manual Armv8*, for *Armv8-A architecture profile*.

#### A1.3 The Armv8-R AArch64 architecture profile

The Armv8-R AArch64 architecture profile is described in terms of Armv8-A Exception levels. Armv8-R AArch64 implementations support EL0, EL1, and EL2 Exception levels.

The main features of the Armv8-R AArch64 profile are:

- Support for one Execution state, AArch64.

- No EL3 Exception level. Secure monitor is not supported in the Armv8-R AArch64 profile.

- A PMSA that defines memory ordering and memory management in 64-bit address space and provides:

- A model for defining protection regions at EL1 and EL2 using two 64-bit registers to specify a base address and a limit address.

- A minimum protection region size of 64 bytes.

- No support for overlapping protection regions.

- The PE is always in Secure state.

- A programmers' model and its interfaces to AArch64 registers with EL1 and EL2 PMSA registers that control most PE and memory system features, and provide status information.

- Support for Advanced SIMD and floating-point instructions.

- The Armv8-R AArch64 virtualization model, which provides:

- Support for the EL2 Exception level.

- A second MPU that provides stage 1 memory protection for memory accesses from EL2 and provides stage 2 memory protection for accesses from EL1 and EL0. These protection stages act as address translation regimes in the Armv8-R AArch64 profile.

- ETMv4.5 with Armv8-R AArch64 extension.

- The Arm architecture includes definitions of associated trace architectures, which define trace macrocells that implementers can implement with the associated processor hardware. For more information, see *Arm*<sup>®</sup> *Embedded Trace Macrocell Architecture Specification, ETMv4.0 to ETMv4.5* (ARM IHI 0064).

- Support for GICv3 or GICv4. For more information, see *Arm*\* *Generic Interrupt Controller Architecture Specification, GIC architecture version 3 and version 4* (ARM IHI 0069).

- The Armv8 AArch64 Debug architecture that provides software access to debug features.

- Optional support for Virtual Memory System Architecture (VMSAv8-64) extension. VMSAv8-64 provides virtual memory addressing support.

#### A1.3.1 See also

- The AArch64 Application Level Programmers' Model.

- The AArch64 Application Level Memory Model.

- The AArch64 System Level Programmers' Model.

- AArch64 Self-hosted Debug.

- AArch64 Self-hosted Trace.

- The AArch64 System Level Memory Model.

- The AArch64 Virtual Memory System Architecture.

#### A1.4 Architecture extensions

An implementation of the Armv8-R AArch64 architecture is based on the Armv8.4-A architecture. Table A1-1 lists the features supported by the Armv8-R AArch64 architecture.

Table A1-1 Armv8-A features supported in Armv8-R AArch64

| Feature        | Description                                                       |  |  |

|----------------|-------------------------------------------------------------------|--|--|

| FEAT_SSBS      | Speculative Store Bypass Safe                                     |  |  |

| FEAT_CSV2      | Cache Speculation Variant 2                                       |  |  |

| FEAT_CSV3      | Cache Speculation Variant 3                                       |  |  |

| FEAT_SB        | Speculation Barrier                                               |  |  |

| FEAT_SPECRES   | Speculation restriction instructions                              |  |  |

| FEAT_SHA1      | Advanced SIMD SHA1 instructions                                   |  |  |

| FEAT_SHA256    | Advanced SIMD SHA256 instructions                                 |  |  |

| FEAT_AES       | Advanced SIMD AES instructions                                    |  |  |

| FEAT_PMULL     | Advanced SIMD PMULL instructions                                  |  |  |

| FEAT_PCSRv8    | PC Sample-based Profiling Extension                               |  |  |

| FEAT_DGH       | Data Gathering Hint                                               |  |  |

| FEAT_LSE       | Large System Extensions                                           |  |  |

| FEAT_RDM       | Advanced SIMD rounding double multiply accumulate instructions    |  |  |

| FEAT_PAN       | Privileged access never                                           |  |  |

| FEAT_VMID16    | 16-bit VMID                                                       |  |  |

| FEAT_PMUv3p1   | PMU Extensions v3.1                                               |  |  |

| FEAT_XNX       | Translation table stage 2 Unprivileged Execute-never              |  |  |

| FEAT_UAO       | Unprivileged Access Override control                              |  |  |

| FEAT_PAN2      | AT S1E1R and AT S1E1W instruction variants affected by PSTATE.PAN |  |  |

| FEAT_DPB       | DC CVAP instruction                                               |  |  |

| FEAT_Debugv8p2 | Debug v8.2                                                        |  |  |

| FEAT_ASMv8p2   | Armv8.2 changes to the A64 ISA                                    |  |  |

| FEAT_IESB      | Implicit Error Synchronization event                              |  |  |

| FEAT_DPB2      | DC CVADP instruction                                              |  |  |

| FEAT_FP16      | Half-precision floating-point data processing                     |  |  |

| FEAT_LVA       | Large VA support                                                  |  |  |

| FEAT_LPA       | Large PA and IPA support                                          |  |  |

| FEAT_VPIPT     | VMID-aware PIPT instruction cache                                 |  |  |

Table A1-1 Armv8-A features supported in Armv8-R AArch64 (continued)

| Feature        | Description                                               |

|----------------|-----------------------------------------------------------|

| FEAT_PCSRv8p2  | PC Sample-based profiling                                 |

| FEAT_DotProd   | Advanced SIMD dot product instructions                    |

| FEAT_SHA3      | Advanced SIMD SHA3 instructions                           |

| FEAT_SHA512    | Advanced SIMD SHA512 instructions                         |

| FEAT_SM3       | Advanced SIMD SM3 instructions                            |

| FEAT_SM4       | Advanced SIMD SM4 instructions                            |

| FEAT_FHM       | Floating-point half-precision multiplication instructions |

| FEAT_PAuth     | Pointer authentication                                    |

| FEAT_JSCVT     | JavaScript conversion instructions                        |

| FEAT_LRCPC     | Load-acquire RCpc instructions                            |

| FEAT_FCMA      | Floating-point complex number instructions                |

| FEAT_DoPD      | Debug over Powerdown                                      |

| FEAT_CCIDX     | Extended cache index                                      |

| FEAT_PAuth2    | Enhancements to pointer authentication                    |

| FEAT_FPAC      | Faulting on AUT* instructions                             |

| FEAT_SEL2      | Secure EL2                                                |

| FEAT_S2FWB     | Stage 2 forced Write-Back                                 |

| FEAT_DIT       | Data Independent Timing instructions                      |

| FEAT_IDST      | ID space trap handling                                    |

| FEAT_FlagM     | Flag Manipulation instructions v2                         |

| FEAT_LSE2      | Large System Extensions v2                                |

| FEAT_LRCPC2    | Load-acquire RCpc instructions v2                         |

| FEAT_TLBIOS    | TLB invalidate instructions in Outer Shareable domain     |

| FEAT_TLBIRANGE | TLB invalidate range instructions                         |

| FEAT_CNTSC     | Generic Counter Scaling                                   |

| FEAT_RASv1p1   | RAS Extension v1.1                                        |

| FEAT_Debugv8p4 | Debug v8.4                                                |

| FEAT_PMUv3p4   | PMU Extensions v3.4                                       |

| FEAT_TRF       | Self-hosted Trace Extensions                              |

The Armv8-R AArch64 architecture supports concurrent modification and execution of instructions as defined by the Armv8-A architecture. FEAT\_IDST feature is extended to include MPUIR\_EL1 register.

For the architectural features supported by Armv8-R AArch64, whether a feature is mandatory or optional depends on whether the feature is mandatory or optional in the Armv8.4-A architecture.

In a PMSAv8-64 only implementation, the FEAT\_TLBIOS and FEAT\_TLBIRANGE features are optional.

#### A1.4.1 See also

- Armv8-A Architecture Extensions.

- The Armv8.1 architecture extension.

- The Armv8.2 architecture extension.

- The Armv8.3 architecture extension.

- The Armv8.4 architecture extension.

#### A1.5 Supported extensions in Armv8-R AArch64

#### A1.5.1 Advanced SIMD and Floating-point extensions

The support for Advanced SIMD and floating-point instructions must conform to the Armv8-A AArch64 specifications.

#### A1.5.2 See also

- Advanced SIMD and floating-point support.

- A64 Advanced SIMD and Floating-point Instruction Descriptions.

## Part B

Differences between the Armv8-A AArch64 and the Armv8-R AArch64 Profiles

### Chapter B1

## Differences between the Armv8-A AArch64 and the Armv8-R AArch64 Profiles

This chapter describes the system level and application level architectural differences between Armv8-R AArch64 and Armv8-A AArch64. It contains the following sections:

- Differences from the Armv8-A AArch64 application level architecture on page B1-30.

- Differences from the Armv8-A AArch64 system level architecture on page B1-31.

#### B1.1 Differences from the Armv8-A AArch64 application level architecture

#### B1.1.1 Differences from the Armv8-A AArch64 application level programmers' model

The Armv8-R AArch64 application level programmers' model differs from the Armv8-A AArch64 profile in the following ways:

- Armv8-R AArch64 supports only a single Security state, Secure.

- EL2 is mandatory.

- EL3 is not supported.

- Armv8-R AArch64 supports the A64 ISA instruction set with some modifications.

See The AArch64 Application Level Programmers' Model chapter of the Arm® Architecture Reference Manual Armv8, for Armv8-A architecture profile.

#### B1.1.2 Differences from the Armv8-A AArch64 application level memory model

Armv8-R AArch64 redefines Data Memory Barrier and Data Synchronization Barrier, and adds an instruction, Data Full Barrier.

#### B1.1.3 See also

- Memory barriers.

- Data Memory Barrier (DMB).

- Data Synchronization Barrier (DSB).

- Use of ASIDs and VMIDs to reduce TLB maintenance requirements.

#### B1.2 Differences from the Armv8-A AArch64 system level architecture

#### B1.2.1 Differences from the Armv8-A AArch64 system level programmers' model

#### Virtualization

Armv8-R AArch64 provides a PMSA-based virtualization model.

#### **Generic Interrupt Controller**

Armv8-R AArch64 supports GICv3 or GICv4. The GIC architecture is defined by the *Arm*\* *Generic Interrupt Controller Architecture Specification, GIC architecture version 3 and version 4* (ARM IHI 0069).

#### B1.2.2 Differences from the Armv8-A AArch64 system level memory model

#### **Address space**

Armv8-R AArch64 uses flat mapping from the *virtual address* (VA), used by the PE, to the *physical address* (PA), and can support address bits up to 52 if FEAT LPA is enabled, otherwise 48 bits.

#### Address translation

In PMSAv8-64 address translation flat-maps the VA to the PA, and determines the access permissions and memory attributes of the target PA.

#### System register support for IMPLEMENTATION DEFINED memory features

The type, presence, and accessibility of *Tightly Coupled Memory* to EL1 and EL0, or to EL2, is IMPLEMENTATION DEFINED.

#### B1.2.3 Protected Memory System Architecture, PMSAv8-64

The Armv8-R AArch64 implementation supports the Protected Memory System Architecture (PMSAv8-64) at EL1 and EL2. See Chapter C1 *Protected Memory System Architecture*.

#### B1.2.4 See also

- The Arm Generic Interrupt Controller System registers.

- About the GIC System registers.

- Address generation.

- Address space.

- Address size configuration.

- Address translation instructions.

- A64 System instructions for address translation.

Differences between the Armv8-A AArch64 and the Armv8-R AArch64 Profiles B1.2 Differences from the Armv8-A AArch64 system level architecture

# Part C Armv8-R AArch64 Protected Memory System Architecture

### Chapter C1

## **Protected Memory System Architecture**

This chapter provides a system-level view of the Protected Memory System Architecture for any implementation that is compliant with the Armv8-R AArch64 architecture. It contains the following sections:

- About the Protected Memory System Architecture on page C1-36.

- *Memory Protection Unit* on page C1-37.

- *Address translation regimes* on page C1-38.

- *Default memory map* on page C1-39.

- *Armv8-A memory view* on page C1-40.

- *MPU memory translations and faults* on page C1-41.

- Protection region attributes and access permissions on page C1-49.

- *MPU fault encodings* on page C1-53.

- *PMSAv8-64 implications for caches* on page C1-54.

- Address tagging and pointer authentication support on page C1-55.

- Security model on page C1-56.

- *Virtualization* on page C1-59.

#### C1.1 About the Protected Memory System Architecture

The Armv8-R AArch64 implementation supports the Protected Memory System Architecture (PMSAv8-64) at EL1 and EL2. The PMSAv8-64 is based on MPUs that provide a memory protection scheme by defining protection regions in the address space.

#### The PMSAv8-64:

- Supports a unified memory protection scheme where an MPU manages instruction and data access. It does not provide separate instruction protection regions and data protection regions in the address map.

- Defines MPU faults that are consistent with VMSAv8-64 fault definitions and reuses IFSC and DFSC fault encodings.

- Does not support virtual addressing and flat maps input address to output address.

For general information about the Arm memory model, see *The AArch64 Application Level Memory Model* and *The AArch64 System Level Memory Model* chapters of the *Arm® Architecture Reference Manual Armv8, for Armv8-A architecture profile*.

#### C1.1.1 Protection regions

An MPU defines protection regions in the address map. A protection region is a contiguous memory region for which the MPU defines the memory attributes and the access permissions.

#### Protection regions:

- Are defined by a pair of registers, a Base Address Register, and a Limit Address Register, see *Memory Protection Unit* on page C1-37.

- Have a minimum size of 64 bytes.

- Have a maximum size of the entire address map.

- Must not overlap.

The definition of a protection region specifies the start and the end of the region, the access permissions, and the memory attributes for the region.

#### C1.1.2 Address range

The maximum supported address bit size is 48, or 52 if FEAT\_LPA is enabled. A PE can choose to implement a smaller PA range and the actual implemented physical address range is provided by the ID\_AA64MMFR0\_EL1.PARange field. Any access to physical memory address outside the address range results in a memory fault.

## C1.2 Memory Protection Unit

An MPU checks whether the address used by a memory access matches a defined protection region. The MPU uses a Base Address Register and a Limit Address Register to define a protection region and its associated access permissions and memory attributes. The minimum supported size of a protection region is 64-bytes.

The PMSAv8-64 defines two MPUs:

#### EL1 MPU

The EL1 MPU can be configured from EL1 or EL2. The EL1 MPU controls the stage 1 of the Secure EL1&0 translation regime that defines the protection regions for accesses from EL1 and EL0. The PMSAv8-64 uses SCTLR\_EL1.M to enable and disable the EL1 MPU. The EL1 MPU also supports a Background region, controlled by SCTLR\_EL1.BR.

#### EL2 MPU

The EL2 MPU can be configured only from EL2. The EL2 MPU controls:

- Stage 1 of the Secure EL2 translation regime that defines the protection regions for accesses from EL2.

- Stage 2 of the Secure EL1 &0 translation regime that defines the protection regions for accesses from EL1 and EL0.

The PMSAv8-64 uses SCTLR\_EL2.M to enable and disable the EL2 MPU. The EL2 MPU also supports a Background region, controlled by SCTLR EL2.BR.

See *Protection region attributes and access permissions* on page C1-49. PMSAv8-64 supports a default memory map as a Background region for memory region checks at both EL1 and EL2. See *Default memory map* on page C1-39.

### C1.2.1 MPU Default Cacheability

The PMSAv8-64 supports Default Cacheability for the stage 1 of the Secure EL1&0 translation regime access and follows the same rule as Armv8-A.

For more information, see chapter AArch64 System Register Descriptions of the Arm® Architecture Reference Manual Armv8, for Armv8-A architecture profile.

## C1.3 Address translation regimes

In PMSAv8-64:

- Address translation describes the process of flat mapping the VA used by the PE, to the PA accessed in the memory system, and determining the access permissions and memory attributes of the target PA.

- A translation regime maps a VA to a PA using one or two stages of address translation to assign the access permissions and memory attributes of the target PA. When two translation stages are used, the intermediate address is treated as an *intermediate physical address* (IPA).

The Armv8-R AArch64 architecture supports two translation regimes:

- Secure EL1&0 translation regime.

- Secure EL2 translation regime.

#### Secure EL1&0 translation regime

The Secure EL1&0 translation regime assigns the access permissions and memory attributes for any access from EL1 or EL0.

This translation regime has one or two stages of translation:

- All accesses from EL1 or EL0 are translated by the EL1 MPU. This translation is a stage 1 translation

- When the value of HCR\_EL2.VM is 1 and SCTLR\_EL2.M is 1, the accesses are further translated by the EL2 MPU. This translation is a stage 2 translation, and can modify the access permissions and memory attributes that are assigned by the stage 1 translation.

For the EL1&0 stage 1 translation, an ADDRESS is in the protection region n if and only if:

PRBAR<n> EL1.BASE:'000000' <= ADDRESS <= PRLAR<n> EL1.LIMIT:'1111111'.

#### Secure EL2 translation regime

The Secure EL2 translation regime assigns the access permissions and memory attributes for any access from EL2.

This translation regime has a single stage of translation, stage 1, that is performed by the EL2 MPU.

For the EL2 stage 1 translation, an ADDRESS is in the protection region n if and only if:

PRBAR<n> EL2.BASE:'000000' <= ADDRESS <= PRLAR<n> EL2.LIMIT:'111111'.

The attributes for a protection region are defined by the combination of:

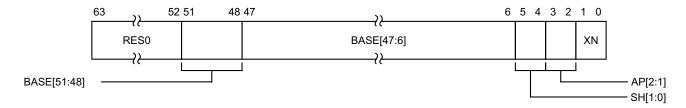

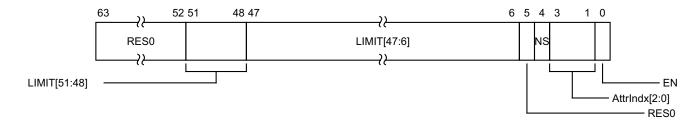

- The values that are programmed into the Base Address Registers and Limit Address Registers. The registers are PRBAR\_EL1, PRLAR\_EL1, PRBAR\_EL2, and PRLAR\_EL2.

- A Memory Attributes Indirection register that is indexed by the values MAIR\_EL1 and MAIR\_EL2.

## C1.4 Default memory map

For PMSAv8-64, the Background region is enabled and disabled using SCTLR\_ELx.BR. If the Background region is enabled, then the MPU uses the default memory map as the Background region for generating the memory attributes when MPU is disabled.

The default memory map of the Armv8-R AArch64 architecture is IMPLEMENTATION DEFINED. Therefore, the Armv8-R AArch64 architecture defines only the condition to access the default memory map, but not the memory map itself. The memory attributes, access permissions, and Security state of the memory regions in the default memory map are also IMPLEMENTATION DEFINED.

Any access outside the implemented physical address range in the default memory map results in a fault.

If the IMPLEMENTATION DEFINED default memory map is discontinuous, then the implementation must also define a generic permission and attribute to be used for memory access to all memory regions that are not covered by the default memory map. However, an implementation can also select a default memory map so that the accesses to these discontinuous memory regions, where no memory attributes are allocated, always result in memory faults.

| these discontinuous memory regions, where no memory authories are anocated, always result in memory fault |

|-----------------------------------------------------------------------------------------------------------|

| Note                                                                                                      |

| The default memory map is same for EL1 and EL2 MPUs.                                                      |

| 1,000                                                                                                     |

## C1.5 Armv8-A memory view

The PMSAv8-64 uses same controls as VMSAv8-64 to enable and disable translation stages.

If the MPU and the Background region are not enabled for stage 1 translation stage, then PMSAv8-64 uses the same memory attributes as defined by VMSAv8-64 when stage 1 translation is disabled.

## C1.6 MPU memory translations and faults

This section provides information on memory attributes and the MPU faults for the stage 1 Secure EL1&0, stage 1 Secure EL2, and the stage 2 Secure EL1&0 translation regimes.

For the EL1 MPU memory translations, this section describes the following:

- Stage 1 EL1&0 memory attributes.

- Stage 1 MPU faults for EL1 access.

- Stage 1 MPU faults for EL0 access.

- EL1 MPU fault types.

- MPU fault check sequence for the stage 1 Secure EL1&0 translation.

For the EL2 MPU memory translations, this section describes the following:

- Stage 1 EL2 memory attributes.

- Stage 1 MPU faults for EL2 access.

- Stage 2 EL1&0 memory attributes.

- Stage 2 EL1&0 MPU faults.

- EL2 MPU fault types.

- MPU fault check sequence for the stage 1 Secure EL2 translation.

- MPU fault check sequence for the stage 2 Secure EL1&0 translation.

## C1.6.1 EL1 MPU memory translations

The EL1 MPU controls the stage 1 of the Secure EL1&0 translation regime. Based on the values of HCR\_EL2.DC and SCTLR\_EL1.{M, BR}, the stage 1 of the Secure EL1&0 translation regime can have the following configurations for memory attributes, as described in Table C1-1.

Table C1-1 Stage 1 EL1&0 memory attributes

| HCR_EL2 | SCTLR_EL1 |    | - MPU hit   | Mamany attribute            |

|---------|-----------|----|-------------|-----------------------------|

| DC      | М         | BR | - WIFO IIIL | Memory attribute            |

| 1       | X         | X  | -           | Default Cacheability        |

| 0       | 0         | 0  | -           | Armv8-A AArch64 memory view |

| 0       | 0         | 1  | -           | Default memory map          |

| 0       | 1         | 0  | No          | Not applicable, MPU Fault   |

| 0       | 1         | 0  | Yes         | MPU memory map              |

| 0       | 1         | 1  | No          | Default memory map          |

| 0       | 1         | 1  | Yes         | MPU memory map              |

Armv8-A AArch64 memory view is the stage 1 memory attribute defined by the Armv8-A architecture for accessing a memory location when stage 1 address translation is disabled (SCTLR\_ELx.M = 0).

Table C1-2 lists the configurations for the stage 1 MPU faults for EL1 access.

Table C1-2 Stage 1 MPU faults for EL1 access

| HCR_EL2 | SCTLR_EL1 |    | MDII 1:4  | MBU C. II                                                                                  |  |

|---------|-----------|----|-----------|--------------------------------------------------------------------------------------------|--|

| DC      | М         | BR | - MPU hit | MPU faults                                                                                 |  |

| 1       | X         | Х  | -         | No Fault or Address size fault                                                             |  |

| 0       | 0         | 0  | -         | No Fault or Address size fault                                                             |  |

| 0       | 0         | 1  | -         | No Fault, or Background region Translation fault, or Background region<br>Permission fault |  |

| 0       | 1         | 0  | No        | Translation fault                                                                          |  |

| 0       | 1         | 0  | Yes       | No Fault or Permission fault                                                               |  |

| 0       | 1         | 1  | No        | No Fault, or Background region Translation fault, or Background region Permission fault    |  |

| 0       | 1         | 1  | Yes       | No Fault or Permission fault                                                               |  |

Table C1-3 lists the configurations for the stage 1 MPU faults for EL0 access.

Table C1-3 Stage 1 MPU faults for EL0 access

| HCR_EL2 | SCT | LR_EL1 | - MPU hit  | MPU faults                                                                              |

|---------|-----|--------|------------|-----------------------------------------------------------------------------------------|

| DC      | М   | BR     | - WPO IIIL |                                                                                         |

| 1       | X   | Х      | -          | No Fault or Address size fault                                                          |

| 0       | 0   | 0      | -          | No Fault or Address size fault                                                          |

| 0       | 0   | 1      | -          | No Fault, or Background region Translation fault, or Background region Permission fault |

| 0       | 1   | X      | No         | Translation fault                                                                       |

| 0       | 1   | X      | Yes        | No Fault or Permission fault                                                            |

\_\_\_\_\_ Note \_\_\_\_\_

If HCR\_EL2. {DC, TGE} is not  $\{0,0\}$ , then the PE behaves as if the value of the SCTLR\_EL1.BR is 0 for all purposes other than returning the value of a direct read of the field.

## C1.6.2 EL1 MPU faults

Each EL1 MPU protection region is defined using the PRBAR\_EL1 and PRLAR\_EL1 registers. The MPU checks the input address with each protection region, and an address is considered to match a region if:

Address >= PRBAR\_EL1.BASE:'000000' && Address <= PRLAR\_EL1.LIMIT:'111111'

Based on MPU protection region checks, the EL1 MPU can raise the following responses as described in Table C1-4.

Table C1-4 EL1 MPU fault types

| Protection region match | Permission | MPU response      |

|-------------------------|------------|-------------------|

| No match                | -          | Translation fault |

| Multiple                | -          | Translation fault |

| Single                  | Denied     | Permission fault  |

|                         | Allowed    | Valid             |

If the EL1 MPU is disabled and the input address is larger than the implemented PA size, then a level 0 address size fault is generated. If the EL1 MPU is enabled and the input address is larger than the implemented PA size, then a level 0 translation fault is generated. Permitted transactions are then presented to stage 2 permission checks by the EL2 MPU.

Depending on the configuration in the PMSAv8-64 registers, the memory attributes of an address can be defined by an MPU protection region, a Background region, or it may have Armv8-A AArch64 memory view.

## C1.6.3 MPU fault check for the stage 1 Secure EL1&0 translation

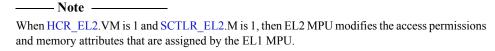

Figure C1-1 shows the MPU fault check sequence for the stage 1 of the Secure EL1&0 translation regime.

Figure C1-1 MPU fault check sequence for the stage 1 Secure EL1&0 translation

## C1.6.4 EL2 MPU memory translations

Based on the values of SCTLR\_EL2.{M, BR}, the stage 1 of the Secure EL2 translation regime can have the following configurations for memory attributes, as described in Table C1-5.

Table C1-5 Stage 1 EL2 memory attributes

| SCTLR_EL2 |    | - MPU hit | Mamanyattuibutaa            |  |

|-----------|----|-----------|-----------------------------|--|

| М         | BR | - WPU nit | Memory attributes           |  |

| 0         | 0  | -         | Armv8-A AArch64 memory view |  |

| 0         | 1  | -         | Default memory map          |  |

| 1         | 0  | No        | Not applicable. MPU Fault.  |  |

| 1         | 0  | Yes       | MPU memory map              |  |

| 1         | 1  | No        | Default memory map          |  |

| 1         | 1  | Yes       | MPU memory map              |  |

Table C1-6 lists the configurations for stage 1 MPU faults for EL2 access.

Table C1-6 Stage 1 MPU faults for EL2 access

| SCT | SCTLR_EL2 |         | MPU faults                                                                              |  |  |

|-----|-----------|---------|-----------------------------------------------------------------------------------------|--|--|

| М   | BR        | MPU hit | WIFO laults                                                                             |  |  |

| 0   | 0         | -       | No Fault or Address size fault                                                          |  |  |

| 0   | 1         | -       | No Fault, or Background region Translation fault, or Background region Permission fault |  |  |

| 1   | 0         | No      | Translation fault                                                                       |  |  |

| 1   | 0         | Yes     | No Fault or Permission fault                                                            |  |  |

| 1   | 1         | No      | No Fault, or Background region Translation fault, or Background region Permission fault |  |  |

| 1   | 1         | Yes     | No Fault or Permission fault                                                            |  |  |

Based on HCR\_EL2.VM and SCTLR\_EL2.{M, BR}, the stage 2 of the Secure EL1&0 translation regime can have the following configurations for memory attributes, as described in Table C1-7.

Table C1-7 Stage 2 EL1&0 memory attributes

| HCR_EL2 | SCTLR_EL2 |    | MPU hit | Memory attribute             |

|---------|-----------|----|---------|------------------------------|

| VM      | M         | BR | WIFOIII | Memory attribute             |

| 0       | X         | X  | -       | Stage 2 translation disabled |

| 1       | 0         | 0  | -       | CONSTRAINED UNPREDICTABLE    |

| 1       | 0         | 1  | -       | Default memory map           |

| 1       | 1         | X  | No      | Not applicable. MPU Fault.   |

| 1       | 1         | X  | Yes     | MPU memory map               |

|         |           |    |         |                              |

Table C1-8 lists the configurations for MPU faults for the stage 2 of the Secure EL1&0 translation regime.

Table C1-8 Stage 2 EL1&0 MPU faults

| HCR_EL2 | SCT | LR_EL2 | MDII bit | nit MPU faults                                                                                                                                 |

|---------|-----|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------------|

| VM      | М   | BR     | MPU hit  |                                                                                                                                                |

| 0       | X   | X      | -        | No Fault                                                                                                                                       |

| 1       | 0   | 0      | -        | CONSTRAINED UNPREDICTABLE                                                                                                                      |

| 1       | 0   | 1      | -        | No Fault, or Background region Translation fault, or Background region Permission fault, or Translation fault due to Secure Check, if enabled. |

| 1       | 1   | X      | No       | Translation fault                                                                                                                              |

| 1       | 1   | X      | Yes      | No Fault, or Permission fault, or Translation fault due to Secure Check, if enabled.                                                           |

There are no separate configurations for the protection regions for the stage 1 of the Secure EL2 and the stage 2 of the Secure EL1&0 translations. Memory accesses for both translations are controlled by the same MPU configuration registers, PRBAR\_EL2 and PRLAR\_EL2.

\_\_\_\_\_Note \_\_\_\_\_

In Armv8-A, there are separate translation table base registers for the stage 1 of the Secure EL2 and the stage 2 of the Secure EL1&0 translation regimes.

#### C1.6.5 EL2 MPU faults

Each EL2 MPU protection region is defined using PRBAR\_EL2 and PRLAR\_EL2. The MPU checks the input address with each protection region and an address is considered to match a region if:

Address >= PRBAR\_EL2.BASE:'000000' && Address <= PRLAR\_EL2.LIMIT:'111111'

Based on MPU protection region checks, the EL2 MPU can raise the following responses as described in Table C1-9.

Table C1-9 EL2 MPU fault types

| Protection region match | Permission | MPU response      |

|-------------------------|------------|-------------------|

| No match                | -          | Translation fault |

| Multiple                | -          | Translation fault |

| Single                  | Denied     | Permission fault  |

| Single                  | Allowed    | Valid             |

If the EL2 MPU is disabled for the stage 1 of the Secure EL2 translation regime, then any access to an address outside the implemented PA range raises a level 0 address size fault. If the EL2 MPU is enabled for the stage 1 of the Secure EL2 translation regime, and the input address is larger than the implemented PA range, then a level 0 translation fault is generated.

## C1.6.6 MPU fault check for the stage 1 Secure EL2 translation

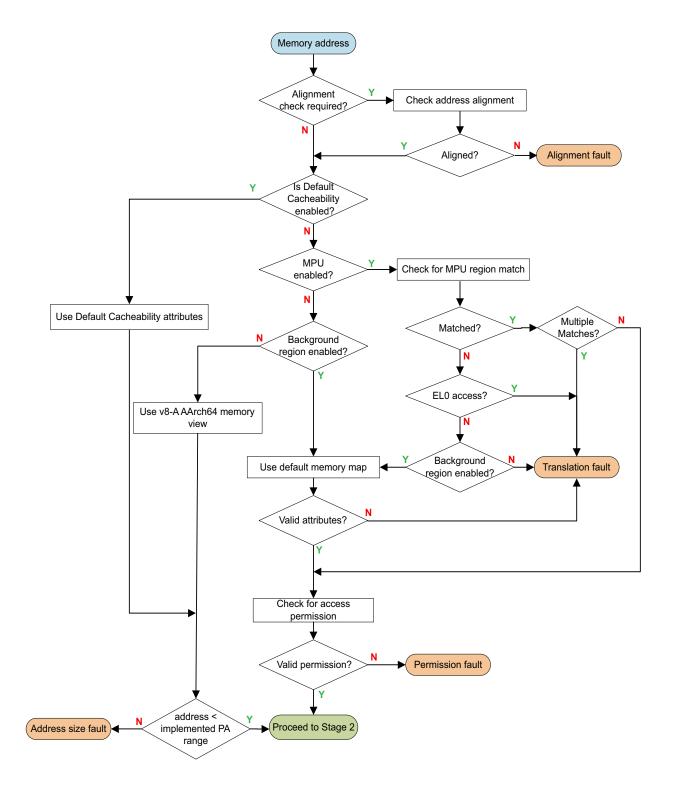

Figure C1-2 shows the MPU fault check sequence for the stage 1 of the Secure EL2 translation regime.

Figure C1-2 MPU fault check sequence for the stage 1 Secure EL2 translation

## C1.6.7 MPU fault check for the stage 2 Secure EL1&0 translation

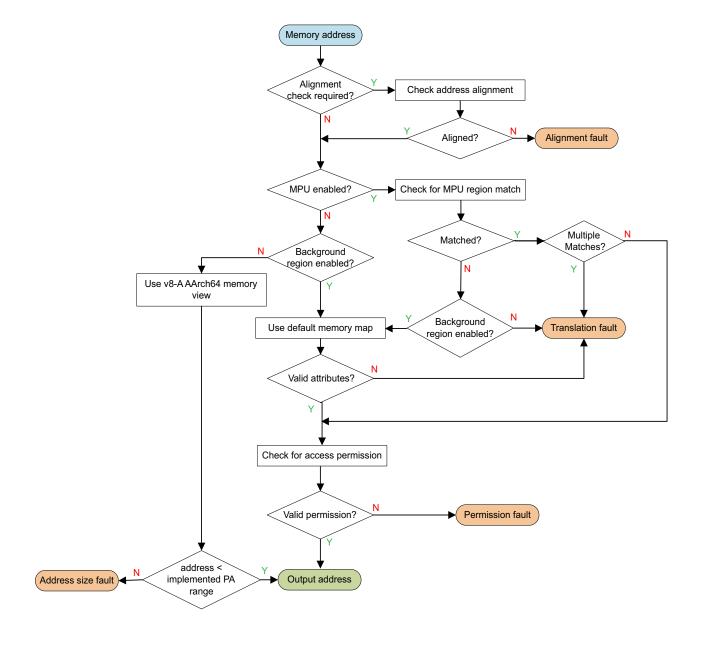

Figure C1-3 shows the MPU fault check sequence for the stage 2 of the Secure EL1&0 translation regime.

Figure C1-3 MPU fault check sequence for the stage 2 Secure EL1&0 translation

## C1.7 Protection region attributes and access permissions

The protection region attribute fields control the Memory type, Cacheability, and Shareability attributes of the region. PMSAv8-64 uses the same memory types and memory attributes as VMSAv8-64 in Armv8-A.

The memory attributes and access permissions for a protection region are defined by:

- The PRBAR\_EL1 and PRLAR\_EL1 registers, or the PRBAR\_EL2 and PRLAR\_EL2 registers that define

the protection region.

- The MAIR\_EL1.Attr<n> or MAIR\_EL2.Attr<n> field that is indexed by PRLAR\_EL1.AttrIndx or PRLAR\_EL2.AttrIndx, respectively.

See also Memory attributes and access permission mappings on page C1-51.

For the Secure EL1&0 translation regime, when HCR\_EL2.VM is 1, the stage 1 memory attribute and access permission assignments are combined with the stage 2 assignments, as described in *Combining memory attributes* and access permissions on page C1-51.

### C1.7.1 Protection region attributes

The PMSAv8-64 uses the same memory attributes defined by the VMSAv8-64, and the MPU enables configuration of the attributes for each protection region using MAIR\_EL1 and MAIR\_EL2. The PMSAv8-64 also enables configuration of each protection region to map to Secure or Non-secure address space using the NS bit in the EL1 and EL2 MPU configuration registers.

| Note                                                                                                |         |

|-----------------------------------------------------------------------------------------------------|---------|

| Writes to MPU registers are only guaranteed to be visible following a Context synchronization event | and DSB |

| operation.                                                                                          |         |

If there are multiple protection regions allocated to the same coherency granule, then Armv8-R AArch64 follows the Armv8-A mismatched memory attributes rules to access any byte within that coherency granule. If the Security states of protection regions are different, then implementation must ensure that these regions are not allocated to the same coherency granule.

The PMSAv8-64 uses the same memory attributes defined by the VMSAv8-64 using MAIR\_EL1 and MAIR\_EL2 for the stage 1 EL1&0 and EL2 translations. For the stage 2 EL1&0 translations, memory attributes encoding in the MAIR\_EL2 register is defined in Table C1-10.

Table C1-10 Meaning of Attr[7:4]

| Attr [7:6] | Attr [5:4] | Memory type   | Outer cache policy  |

|------------|------------|---------------|---------------------|

| 00         | 00         | Device memory | Not Applicable (NA) |

| 00         | !=00       | Normal memory | Write-Through (WT)  |

| 01         | 00         | Normal memory | Non Cacheable (NC)  |

| 01         | !=00       | Normal memory | Write-Back (WB)     |

| 10         | xx         | Normal memory | Write-Through (WT)  |

| 11         | xx         | Normal memory | Write-Back (WB)     |

When Attr[7:4] is 0b0000, Attr[3:0] defines the type of Device memory. In this case, Attr[1:0] != 0b00 gives UNPREDICTABLE behavior as defined by Armv8-A. Table C1-11 describes the meaning of Attr<3.0> when Attr[7:4] is 0b0000.

Table C1-11 Attr<3.0> Meaning when Attr[7:4] is 0b0000

| Attr [3:2] | Attr [1:0] | Memory type   |

|------------|------------|---------------|

| 00         | 00         | Device-nGnRnE |

| 01         | 00         | Device-nGnRE  |

| 10         | 00         | Device-nGRE   |

| 11         | 00         | Device-GRE    |

When Attr[7:4] is not 0b0000, Attr[3:0] defines the Inner Cache Policy, and Attr[3:0] = 0b0000 gives UNPREDICTABLE behavior as defined by Armv8-A. Table C1-12 describes the meaning of Attr<3.0> when Attr[7:4] is not 0b0000.

Table C1-12 Attr<3.0> Meaning when Attr[7:4] is not 0b0000

| Attr [3:2] | Attr [1:0] | Memory type   | Inner Cache Policy |

|------------|------------|---------------|--------------------|

| 00         | !=00       | Normal memory | Write-Through (WT) |

| 01         | 00         | Normal memory | Non Cacheable (NC) |

| 01         | !=00       | Normal memory | Write-Back (WB)    |

| 10         | xx         | Normal memory | Write-Through (WT) |

| 11         | xx         | Normal memory | Write-Back (WB)    |

For more information, see chapter *The AArch64 Virtual Memory System Architecture* of the *Arm*<sup>®</sup> *Architecture Reference Manual Armv8, for Armv8-A architecture profile.*

## C1.7.2 Access control

The access permission and security configuration bits, such as AP, XN, and NS in the VMSAv8-64 translation table descriptors are present in the MPU configuration registers in PMSAv8-64.

Access granted in the stage 1 of the Secure EL1&0 translation regime by the EL1 MPU is subject to further qualification by the EL2 MPU in the stage 2 of the Secure EL1&0 translation regime.

The AP, XN, and NS bits in PMSAv8-64 are interpreted in the same way as defined by VMSAv8-64. For selecting memory attributes and defining access permissions, PMSAv8-64 follows the same prioritization rules defined by VMSAv8-64 in Armv8-A.

PMSAv8-64 does not support hierarchical control bits defined in the VMSAv8-64 table descriptors. PMSAv8-64 also does not support Privileged execute-never (PXN) and Unprivileged execute-never (UXN) bits. PMSAv8-64 behaves as PXN = XN and UXN = XN, and follows the same rule defined by VMSAv8-64 in combining permission attributes.

If the value of SCTLR\_ELx. {M, BR} is {0, 1}, where ELx is the highest Exception level of the translation regime, then PE behaves as if the value of SCTLR\_ELx. WXN is 0 for all purposes other than returning the value of a direct read of the field.

If the value of SCTLR\_EL1.{M, BR} is {0, 1}, then for the Secure EL1&0 translation regime, any memory region that is writable at EL0, is also executable from EL1 if that address is marked as executable by the Background region.

Armv8-R AArch64 supports FEAT\_PAN as defined by the Armv8-A architecture. If the value of SCTLR\_EL1.M is 1, FEAT\_PAN is applied to the stage 1 of the Secure EL1&0 translation regime.

#### C1.7.3 Memory attributes and access permission mappings

Memory attributes, Security states, and access permission information present in the translation table descriptors of VMSAv8-64 are mapped to MPU configuration registers in PMSAv8-64, as described in Table C1-13.

Table C1-13 Memory attributes and access permission mappings

| Attributes and permissions | MPU register fields                      | Description                                                                                                                                                   |

|----------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Non-secure (NS)            | PRLAR_EL1.NS<br>PRLAR_EL2.NS             | Specifies whether the translated address is in the Secure or Non-secure address space.                                                                        |

| Access Permission (AP)     | PRBAR_EL1.AP<br>PRBAR_EL2.AP             | Defines the Access permissions for the protection region.                                                                                                     |

| Execute Never (XN)         | PRBAR_EL1.XN<br>PRBAR_EL2.XN             | Defines the Execute-never attribute for the protection region.                                                                                                |

| Shareability (SH)          | PRBAR_EL1.SH<br>PRBAR_EL2.SH             | Defines the Shareability for a Normal memory region. For any type of Device memory or Normal Non-cacheable memory, the value of the SH[1:0] field is IGNORED. |

| Attribute Index (AttrIndx) | PRLAR_EL1.AttrIndx<br>PRLAR_EL2.AttrIndx | Indexes an Attr <n> field in the MAIR_EL1 or MAIR_EL2 register, which gives the memory type and memory attributes.</n>                                        |

## C1.7.4 Combining memory attributes and access permissions

Armv8-R AArch64 uses the same architecture rules as Armv8-A for combining stage 1 and stage 2 memory attributes and the access permissions for the Secure EL1&0 translation regime.

#### Stage 2 forced Write-Back Feature

the 0b11 encoding in Armv8-R AArch64.

If FEAT\_S2FWB is enabled (HCR\_EL2.FWB=1), the Inner and Outer Memory attributes for the stage 2 of the Secure EL1&0 translation regime must be the same with the same encoding, otherwise the combined attribute is UNKNOWN.

- If FEAT\_S2FWB is enabled and the memory attributes for the stage 2 of the Secure EL1&0 translation regime are Write-Back (WB) with Attr[7:6] = 0b11, then the combined attribute is WB. If the memory attribute is assigned by the MPU, the attribute encoding is derived from MAIR\_EL2.Attr[7:6]. If the memory attribute is assigned from Background region, then the encoding is derived from the memory region configuration in the Background region.

- If FEAT\_S2FWB is not enabled, then stage 1 and stage 2 memory attributes of the Secure EL1&0 translation

regime are combined using Armv8-A rule for combining memory attributes when FEAT\_S2FWB is not

enabled.

| —— Note ———                                                                                                   |

|---------------------------------------------------------------------------------------------------------------|

| In Armv8-A, the memory attribute encoding that enables FEAT_S2FWB is MemAttr[4:2] = 0b110 in stage 2 block    |

| or page descriptor of the Secure EL1&0 translation regime, while in Armv8-R AArch64, it is MAIR_EL2.Attr[7:6] |

| = 0b11. Therefore, FEAT S2FWB architecture rules defined for the 0b110 encoding in Armv8-A must be applied to |

For more information, see the Stage 2 memory region type and Cacheability attributes when Armv8.4-S2FWB is implemented section of the Arm® Architecture Reference Manual Armv8, for Armv8-A architecture profile.

#### C1.7.5 Enabling and disabling the caching of memory accesses

The Armv8-R AArch64 architecture follows the same rule as the Armv8-A AArch64 architecture for enabling and disabling cache, and can force all memory locations with the Normal memory type to be treated as Non-cacheable regardless of their assigned Cacheability attribute using SCTLR\_ELx.{I,C} and HCR\_EL2.{ID,CD}. For a PMSAv8-64 based address translation, Armv8-R AArch64 extends the functionality of SCTLR\_ELx.{I,C} and HCR\_EL2.{ID,CD} for accesses to Background region also.

## C1.7.6 Enabling and disabling stages in translation regimes

The EL1 MPU controls the stage 1 of the Secure EL1&0 translation regime. The EL2 MPU controls the stage 2 of the Secure EL1&0 translation regime and the stage 1 of the Secure EL2 translation regime.

For the Secure EL1&0 translation regime:

- If SCTLR\_EL1. {M, BR} is {0, 0}, then stage 1 translation is disabled.

- If HCR EL2.VM is 0, then stage 2 translation is disabled.

- If HCR\_EL2.VM is 1 and SCTLR\_EL2.{M, BR} is {0, 0}, then the behavior is CONSTRAINED UNPREDICTABLE with the following permitted values:

- The stage 2 memory attribute becomes UNKNOWN.

- Raise stage 2 level 0 translation fault.

For the Secure EL2 translation regime if SCTLR\_EL2. {M, BR} is {0, 0}, then translation is disabled.

## C1.8 MPU fault encodings

PMSAv8-64 defines MPU faults that are consistent with the VMSAv8-64 fault definitions and reuses IFSC and DFSC fault encodings. Each MPU raises faults on invalid memory accesses, including accesses to memory regions outside address ranges and the accesses without sufficient permissions. Table C1-14 describes the MPU fault encodings mapped from VMSAv8-64.

Table C1-14 PMSAv8-64 fault encodings

| Memory faults                              | MPU fault encodings mapped from VMSAv8-64 | Description                                                                                        |

|--------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------|

| Alignment fault                            | Alignment fault                           | Unaligned memory access.                                                                           |

| Translation fault                          | Translation fault, level 0                | Invalid input address. There is no valid mapping or valid memory attributes for the input address. |

| Permission fault                           | Permission fault, level 0 (0b001100)      | Insufficient access permissions.                                                                   |

| Address size fault                         | Address size fault, level 0               | Generated output address is out of range of the implemented physical address.                      |

| Access flag fault                          |                                           | Not applicable for PMSAv8-64.                                                                      |

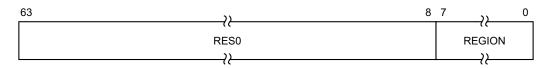

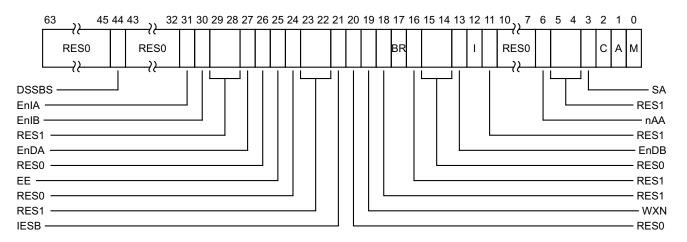

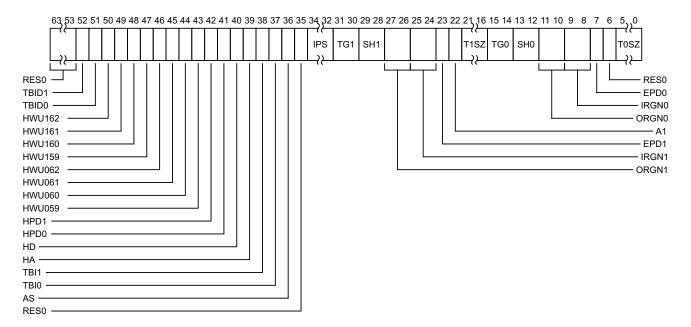

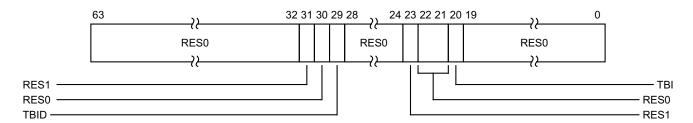

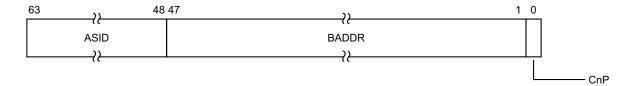

| TLB conflict abort                         |                                           | Not applicable for PMSAv8-64.                                                                      |