# ARM<sup>®</sup> IoT Subsystem for Cortex<sup>®</sup>-M

Revision: r0p0

**Technical Reference Manual**

Copyright © 2015. All rights reserved. ARM DDI 0551A (ID120415)

### ARM IoT Subsystem for Cortex-M Technical Reference Manual

Copyright © 2015. All rights reserved.

#### **Release Information**

The following changes have been made to this book.

|                  |       |                  |                             | Change history |

|------------------|-------|------------------|-----------------------------|----------------|

| Date             | Issue | Confidentiality  | Change                      |                |

| 13 November 2015 | А     | Non-Confidential | First release for r0p0 EAC. |                |

#### **Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of ARM. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information: (i) for the purposes of determining whether implementations infringe any third party patents; (ii) for developing technology or products which avoid any of ARM's intellectual property; or (iii) as a reference for modifying existing patents or patent applications or creating any continuation, continuation in part, or extension of existing patents or patent applications; or (iv) for generating data for publication or disclosure to third parties, which compares the performance or functionality of the ARM technology described in this document with any other products created by you or a third party, without obtaining ARM's prior written consent.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, ARM makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to ARM's customers is not intended to create or refer to any partnership relationship with any other company. ARM may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any signed written agreement covering this document with ARM, then the signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

Words and logos marked with <sup>®</sup> or <sup>™</sup> are registered trademarks or trademarks of ARM<sup>®</sup> in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners. Please follow ARM's trademark usage guidelines at http://www.arm.com/about/trademarks/guidelines/index.php.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

Copyright © 2015, ARM Limited or its affiliates. All rights reserved.

ARM Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20348

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

## Contents ARM IoT Subsystem for Cortex-M Technical Reference Manual

|           | Prefa | ace                            |     |

|-----------|-------|--------------------------------|-----|

|           |       | About this book                | vii |

|           |       | Feedback                       | x   |

| Chapter 1 | Intro | duction                        |     |

| •         | 1.1   | About IoT endpoints            | 1-2 |

|           | 1.2   | Features of the IoT Subsystem  |     |

|           | 1.3   | Compliance                     |     |

|           | 1.4   | Product revisions              |     |

| Chapter 2 | Fund  | ctional Description            |     |

| -         | 2.1   | System top-level partitioning  | 2-2 |

|           | 2.2   | Cortex-M3 processor block      |     |

|           | 2.3   | Power management               |     |

|           | 2.4   | Clocks                         |     |

|           | 2.5   | Resets                         | 2-7 |

|           | 2.6   | Timer                          |     |

|           | 2.7   | eFlash memory subsystem        |     |

|           | 2.8   | Banked SRAM subsystem          |     |

|           | 2.9   | AHB and APB expansion          |     |

|           | 2.10  | Debug and Trace                |     |

| Chapter 3 | Prog  | rammers Model                  |     |

| •         | 3.1   | , About this programmers model |     |

|           | 3.2   | Memory map                     |     |

|           | 3.3   | eFlash controller              |     |

|           |       |                                |     |

#### Contents

|            | 3.4   | eFlash cache                                      | 3-21 |

|------------|-------|---------------------------------------------------|------|

|            | 3.5   | Interrupts                                        |      |

|            | 3.6   | Wakeup Interrupt Controller (WIC)                 |      |

|            | 3.7   | Timer                                             |      |

|            | 3.8   | System registers                                  |      |

|            | 3.9   | Debug and Trace                                   |      |

| Appendix A | Signa | al Descriptions                                   |      |

|            | A.1   | Clock and reset signals                           | A-2  |

|            | A.2   | Interrupt signals                                 | A-4  |

|            | A.3   | eFlash signals                                    | A-5  |

|            | A.4   | SRAM signals                                      | A-9  |

|            | A.5   | Timer signals                                     | A-10 |

|            | A.6   | Bus signals                                       | A-11 |

|            | A.7   | Debug and Trace signals                           | A-14 |

|            | A.8   | CPU control, status, and power management signals | A-20 |

|            | A.9   | Memory remap signals                              | A-23 |

|            | A.10  | DFT signals                                       |      |

| Appendix B | Revis | sions                                             |      |

## Preface

This preface introduces the *IoT Subsystem for Cortex-M Technical Reference Manual*. It contains the following sections:

- *About this book* on page vii.

- *Feedback* on page x.

### About this book

| This book is for the IoT Subsystem for Cortex-M (IoT Subsystem). It provides a high-level       |

|-------------------------------------------------------------------------------------------------|

| overview of the IoT Subsystem. It describes architectural information, and as such, facilitates |

| the creation of IoT Subsystem software or an SoC targeted at an Internet of Things (IoT)        |

| application.                                                                                    |

### **Product revision status**

The *rmpn* identifier indicates the revision status of the product described in this book, for example, r0p0, where:

rm Identifies the major revision of the product, for example, r0.pn Identifies the minor revision or modification status of the product, for example, p0.

### Intended audience

This book is written for software engineers who want to work with an ARM reference platform. The manual describes the functionality of the IoT Subsystem.

#### Using this book

This book is organized into the following chapters:

### **Chapter 1** Introduction

Read this for a high-level view of the IoT Subsystem and a description of its features.

#### **Chapter 2** Functional Description

Read this for a description of the major interfaces and components of the IoT Subsystem. This chapter also describes how the components operate.

#### **Chapter 3** Programmers Model

Read this for a description of the address map and registers of the IoT Subsystem.

### **Appendix A Signal Descriptions**

Read this for an overview of the signals present in the IoT Subsystem.

#### Appendix B Revisions

Read this for a description of the technical changes between released issues of this book.

#### Glossary

The *ARM Glossary* is a list of terms used in ARM documentation, together with definitions for those terms. The *ARM Glossary* does not contain terms that are industry standard unless the ARM meaning differs from the generally accepted meaning.

The *ARM Glossary* is available on the ARM Infocenter at http://infocenter.arm.com/help/topic/com.arm.doc.aeg0014-/index.html.

### Conventions

Conventions that this book can use are described in:

Typographical conventions on page viii.

- Timing diagrams.

- *Signals* on page ix.

### **Typographical conventions**

The following table describes the typographical conventions:

| Style                                                                    | Purpose                                                                                                                                                                                                 |  |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| italic                                                                   | Introduces special terminology, denotes cross-references, and citations.                                                                                                                                |  |

| bold                                                                     | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.                                                                   |  |

| monospace                                                                | Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code                                                                                              |  |

| <u>mono</u> space                                                        | Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.                                                                 |  |

| monospace italic                                                         | Denotes arguments to monospace text where the argument is to be replaced by a specific value.                                                                                                           |  |

| monospace bold Denotes language keywords when used outside example code. |                                                                                                                                                                                                         |  |

| <and></and>                                                              | Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example: MRC p15, 0 <rd>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></rd>                         |  |

| SMALL CAPITALS                                                           | IALL CAPITALS       Used in body text for a few terms that have specific technical meanings, that are defined in the ARM gloss         For example, IMPLEMENTATION DEFINED, UNKNOWN, and UNPREDICTABLE. |  |

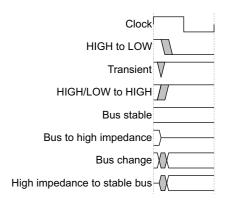

### **Timing diagrams**

The figure named *Key to timing diagram conventions* explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

### Key to timing diagram conventions

Timing diagrams sometimes show single-bit signals as HIGH and LOW at the same time and they look similar to the bus change shown in *Key to timing diagram conventions*. If a timing diagram shows a single-bit signal in this way then its value does not affect the accompanying description.

### Signals

The signal conventions are:

| Signal level | The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means: |

|--------------|-------------------------------------------------------------------------------------------------------------|

|              | • HIGH for active-HIGH signals.                                                                             |

|              | • LOW for active-LOW signals.                                                                               |

| Lower-case n | At the start or end of a signal name denotes an active-LOW signal.                                          |

### Additional reading

This section lists publications by ARM and by third parties.

See Infocenter, http://infocenter.arm.com for access to ARM documentation.

See www.arm.com/cmsis for embedded software development resources including the *Cortex*<sup>®</sup> *Microcontroller Software Interface Standard* (CMSIS).

See mbed, https://mbed.org/ for information on the mbed tools including mbed OS and online tools.

### **ARM** publications

This book contains information that is specific to this product. See the following documents for other relevant information:

- *Cortex®-M System Design Kit Technical Reference Manual* (ARM DDI 0479). http://infocenter.arm.com/help/topic/com.arm.doc.ddi0479c/index.html

- Cortex<sup>®</sup>-M3 Devices Generic User Manual (ARM DUI 0552).

http://infocenter.arm.com/help/topic/com.arm.doc.dui0552a/index.html

- ARM<sup>®</sup> Cortex<sup>®</sup>-M3 Technical Reference Manual (ARM 100165\_0201\_00\_en). http://infocenter.arm.com/help/topic/com.arm.doc.100165\_0201\_00\_en/index.html

The following confidential books are only available to licensees or require registration with ARM:

- ARM<sup>®</sup> IoT for Cortex-M Implementation and Integration Manual (ARM DII0300).

- AMBA<sup>®</sup> 3 APB Protocol Specification (ARM IHI 0024). http://infocenter.arm.com/help/topic/com.arm.doc.ihi0024c

- AMBA® 3 AHB-Lite Protocol Specification (ARM IHI 0033). http://infocenter.arm.com/help/topic/com.arm.doc.ihi0033a

- ARM<sup>®</sup> ARMv7M Architecture Reference Manual (ARM DDI 0403). http://infocenter.arm.com/help/topic/com.arm.doc.ddi0403e.b/index.html

### Feedback

ARM welcomes feedback on this product and its documentation.

### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

### Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- The title.

- The number, ARM DDI 0551A.

- The page numbers to which your comments apply.

- A concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

### — Note —

ARM tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader.

## Chapter 1 Introduction

This chapter introduces the *IoT Subsystem for Cortex-M* (IoT Subsystem). It contains the following sections:

- *About IoT endpoints* on page 1-2.

- *Features of the IoT Subsystem* on page 1-4.

- *Compliance* on page 1-6.

- *Product revisions* on page 1-7.

### 1.1 About IoT endpoints

The IoT Subsystem delivers a reference pre-integrated, validated, hardware and software subsystem that can be extended to provide an IoT endpoint system.

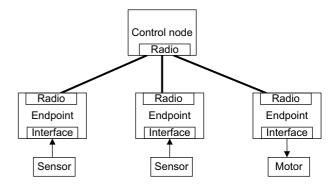

Figure 1-1 shows an IoT system consisting of several endpoints and a shared control node:

### Figure 1-1 An IoT endpoint as part of a larger control system

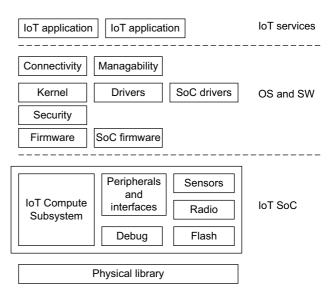

Figure 1-2 shows a block diagram of the hardware and software in an endpoint solution:

### Figure 1-2 IoT endpoint HW and SW solution

A complete endpoint system typically contains the following components:

### **Compute Subsystem**

The IoT Subsystem consists of the Cortex-M3 processor and associated bus, debug, controller, and interface logic supplied by ARM.

### Reference system memory and peripherals

Additional memory, control, and peripheral components beyond the minimum IoT Subsystem components.

Licensees of the IoT Subsystem are provided with an example integration layer which includes implementations of eFlash and SRAM. The example integration layer provides a starting point for customizing an SoC.

### **Communication interface**

The endpoint will have some way of communicating with other nodes or masters in the system. This could be WiFi, Bluetooth, or a wired connection.

The ARM Cordio<sup>®</sup> BT4 radio IP is available as an option for the IoT Subsystem. The example integration layer expansion ports are however technology independent and other radio devices could be used instead of the Cordio radio IP. Radio-specific interfaces such as clock, reset, and power control must be implemented at the SoC level.

### Sensor or control component

To be useful as an endpoint, the reference design is typically extended by adding sensors or control logic such as, for example, temperature input or motor speed control output.

### Software development environment

ARM provides a complete software development environment which includes the mbed operating system, ARM or GCC compilers and debuggers, and firmware.

Any custom peripherals typically require corresponding third-party firmware that can be integrated into the software stack.

### 1.2 Features of the IoT Subsystem

The IoT Subsystem contains the following components:

- A Cortex-M3 processor:

- Bit-banding enables using standard instructions to read or modify of individual bits.

The default implementation does not include bit banding.

- Eight MPU regions (optional)

- NVIC providing deterministic, high-performance interrupt handling with a configurable number of interrupts.

- Wakeup Interrupt Controller (WIC) with configurable number of WIC lines (optional). This is a latch-based WIC implementation, and not the standard Cortex-M3 WIC.

- Little-endian memory addressing only (for compatibility with eFlash controller and Flash cache).

For more information see the ARM Cortex-M3 Technical Reference Manual.

*The Cortex-M3 has a Processor Integration Layer* (PIL) to simplify integration of the IoT Subsystem into a multiprocessor system with a SoC-level CoreSight subsystem.

- Configurable Debug and Trace as either:

- Stand-alone system with a TPIU and a SWJDAP.

- Full CoreSight integration over a DAP and the ATB buses.

- Multilayer AMBA AHB-Lite interconnect:

- Low-latency interconnect bus matrix.

- Two AHB-Lite initiator expansion ports for external AHB masters.

- Two AHB-Lite target expansion ports for external AHB slaves.

- Eleven APB4 target expansion ports (each with 4KB address space) to connect APB peripherals.

- Memory system, consisting of:

- Integrated eFlash cache with configurable cache size from 512 bytes to 8kB. (The cache is two-way set associative instruction cache with a four-word cache line.)

- Integrated eFlash controller for TSMC 55 ULP-TV2 eFlash.

### — Note -

The IoT Subsystem can be easily modified to replace the supplied eFlash controller if a different eFlash technology is used in the SoC, but the warranty is void if the IoT Subsystem is changed.

- Static memory (configurable as one to four 32KB banks) is provided in the example integration layer.

- eFlash memory (banked as 2x128KB or 2x256KB) provided in the example integration layer.

- Two APB timers:

- Interrupt generation when the counter reaches 0.

- Each timer has an TIMERnEXTIN signal that can be used as an enable or external clock.

- Configurable privileged access mode.

- Cordio BT4 Radio component (optional).

- Fully integrated Bluetooth Smart controller sub-system IP block.

- Radio transceiver, baseband, integrated link layer (LL) controller.

- LL firmware up to the Host Controller Interface (HCI).

- Delivered as a hard macro (55nm TSMC) with a synthesizable integration wrapper.

- The Cordio BT4 IP is not provided with the IoT Subsystem, and must be separately licensed from ARM.

A third-party BlueTooth solution can be connected to the AHB expansion ports, but that will require customized software and firmware to support the product.

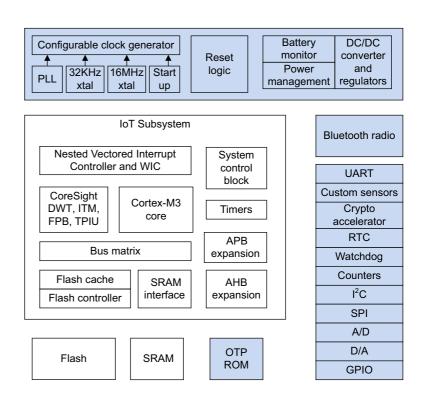

The reference system contains the peripherals required to support a rich OS. The components highlighted in Figure 1-3 are not provided by the IoT Subsystem. Other peripherals not included in the IoT Subsystem might be required for specific application areas.

Figure 1-3 Example of an IoT endpoint SoC

### 1.3 Compliance

The IoT Subsystem complies with, or includes components that comply with, the following specifications:

- ARM Architecture.

- Interrupt controller architecture.

- Advanced Microcontroller Bus Architecture.

This TRM complements the TRMs for included components, architecture reference manuals, architecture specifications, protocol specifications, and relevant external standards. It does not duplicate information from these sources.

### 1.3.1 ARM Architecture

The IoT Subsystem implements the ARMv7-M architecture which executes the ARM-v7M Thumb instruction set.

See the ARMv7-M Architecture Reference Manual for more information.

### 1.3.2 Interrupt controller architecture

The IoT Subsystem implements the ARM Nested Vectored Interrupt Controller (NVIC).

See the ARM Cortex-M3 Technical Reference Manual for more information.

### 1.3.3 Advanced Microcontroller Bus Architecture

The IoT Subsystem complies with the:

- *Advanced High Performance Bus* (AHB-Lite) protocol. See the *AMBA*<sup>®</sup> *3 AHB-Lite Protocol Specification*.

- *Advanced Peripheral Bus* (APB) protocol. See the *AMBA*<sup>®</sup> *APB Protocol Specification* (Rev 2.0).

### 1.4 **Product revisions**

This section describes the differences in functionality between product revisions:

**1.0** First release.

## Chapter 2 Functional Description

This chapter describes the functionality of the IoT Subsystem for Cortex-M (IoT Subsystem).

It contains the following sections:

- *System top-level partitioning* on page 2-2.

- *Cortex-M3 processor block* on page 2-3.

- *Power management* on page 2-5.

- *Clocks* on page 2-6.

- *Resets* on page 2-7.

- *Timer* on page 2-9.

- *eFlash memory subsystem* on page 2-10.

- Banked SRAM subsystem on page 2-12.

- *AHB and APB expansion* on page 2-14.

- *Debug and Trace* on page 2-16.

### 2.1 System top-level partitioning

The IoT Subsystem consists of partitions of smaller sub-blocks.? The IoT Subsystem is extended by additional components in the SoC integration layer.

— Note –

The provided example system is for information only and ARM expects that the system designers will customize it for their application requirements.

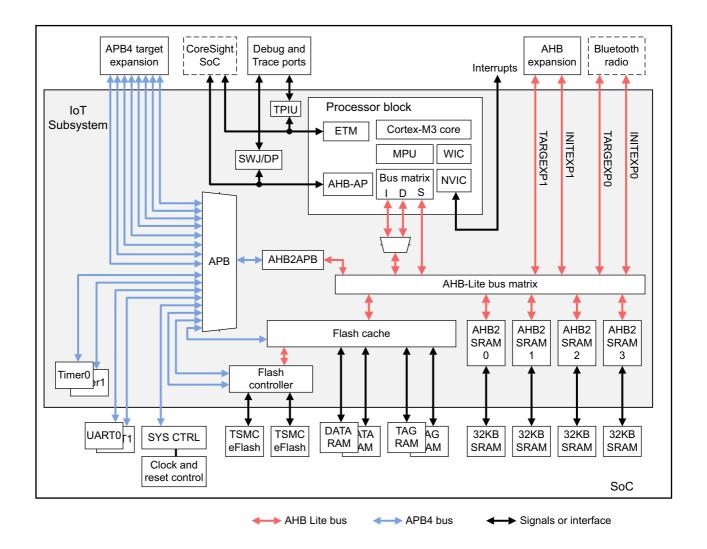

The figure below shows the top-level block diagram with the AHB-Lite and APB bus interconnections.

Figure 2-1 Bus interconnections

### 2.2 Cortex-M3 processor block

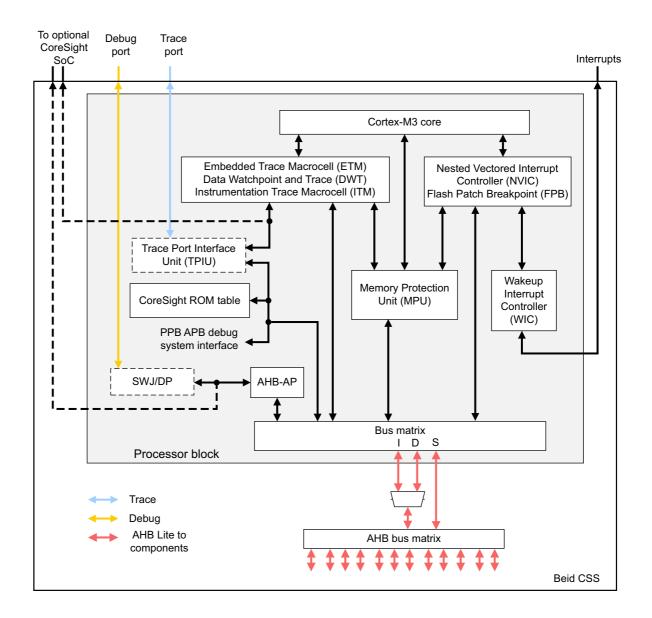

The block diagram for the Cortex-M3 processor logic and CoreSight SoC interface is shown in the figure below:

### Figure 2-2 Cortex-M3 component

The default implementation reuses the TPIU and SWJDP from Cortex-M3 package and connects the SWJ-DP and TPIU to the Processor Integration layer. For basic usage, there is no requirement to license the CoreSight SoC IP.

The system designer can however choose to design a system with the separately licensed CoreSight SoC debug interface connected to the AHB-AP. In this case the SWJ/DP and TPIU blocks and their corresponding signals are not present.

– Note –

For more information on the Cortex-M3 and the debug and trace logic, see the following documents:

- ARMv7-M Architecture Reference Manual (ARM DDI 0403).

- ARM Cortex-M3 Processor Technical Reference Manual (ARM 100165\_0201\_00\_en).

- ARM CoreSight Components Technical Reference Manual (ARM DDI 0314).

- ARM Debug Interface v5 Architecture Specification (ARM IHI 0031).

- ARM Embedded Trace Macrocell Architecture Specification (ARM IHI 0014).

### 2.3 Power management

Low-power operation is essential for most IoT endpoint devices which typically rely on a battery or on harvested energy.

The IoT Subsystem is single power domain system and it does not support control of different power domains within the SoC. It does however define the necessary HW handshake signals that can be connected to a Power Management Unit (PMU) at the SoC level.

SRAM power management is not present in the IoT Subsystem because SRAM models are outside of the IoT Subsystem block. Memory power mode support can be implemented at SoC level.

For power-management signals, see *CPU control, status, and power management signals* on page A-20.

### 2.4 Clocks

The IoT Subsystem does not implement a clock control infrastructure. The IoT Subsystem is a single clock domain system that provides inputs for the clocks. Therefore all input clocks (except for the debug clocks) are identical in frequency and phase.

The target frequencies for the IoT Subsystem and associated components are:

- The typical configuration is 50MHz when using the TSMC 55 ULP process.

- The minimum operating frequency is 1MHz because of restrictions from the eFlash controller and the eFlash memory.

- 20MHz for the JTAG and Trace components.

- 32kHZ low-power mode (optional). If present, this clock is sampled by FLSHCLK and the rising edge is used as an enable signal for the eFlash erase timing counters. This reduces the toggle rate and allows RTL gating of the erase timer.

### 2.4.1 Component clocks

The subsystem does not implement architectural clock gating other than the Cortex-M3 and ETM internal gating. The IoT Subsystem is a single clock domain. The component clocks can however be gated by a custom implementation at SoC level.

For a full list of component clocks, see Clock and reset signals on page A-2.

For a list of power-management related signals, see Power management on page 2-5.

### 2.5 Resets

The IoT Subsystem has no internal reset generation implemented (except that Cortex-M3 CPU can be reset by the internal AIRCR.VECTRESET MMR bit of the NVIC).

All component resets in the IoT Subsystem are connected to the IoT Subsystem boundary and can therefore be reset using reset input signals.

— Note —

The IoT Subsystem is not designed to handle arbitrary reset patterns. The SoC integration and software must ensure that all resets are cleanly released before functional operation and no software reset is triggered to functioning components.

All resets are active low and asynchronous. External reset synchronization is required to guarantee the clean de-assertion of the resets in sync with the corresponding clocks.

### 2.5.1 Reset inputs

For a full list of component reset signals, see *Clock and reset signals* on page A-2.

### 2.5.2 About boot after reset

There is one Cortex M3 CPU integrated into the IoT Subsystem. After CPU reset de-assertion the CPU starts fetching the addresses as follows:

- 1. 0x00000000: Fetch the stack pointer to initialize the SP register

- 2. 0x00000004: Fetch the reset vector and jump to the reset vector value

- 3. Reset vector: Start boot code execution

Address 0x0000000 of the IoT Subsystem is mapped to the eFlash controller statically. It is therefore not possible to directly boot from ROM attached to the AHB expansion port.

eFlash reference cell erase is performed during wafer testing. If the flash is not empty, the factory reset must be applied before first use. Because the eFlash main array will be then be empty, the initial reset vector, SP and boot code must be written to eFlash through the debugger.

— Note —

An alternative way to load the Flash content after wafer testing is to preload it with the Flash DFT controller.

### 2.5.3 Events

The following table lists events that can be used for multiprocessor systems:

### Table 2-1 Cortex-M3 events

| Name     | Description                                                                                                                                                                                                                                                                                                                   |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU0RXEV | RX event input of the Cortex-M3. Causes a wake-up from a WFE instruction.                                                                                                                                                                                                                                                     |

|          | Connect to TXEVs from other processors in a multi-processor system. Input from OR'ing TXEV signals from other processors in the system. If different processors run at different frequencies then synchronizers must be used to guarantee that TXEV is synchronous to this processor. TXEV must also be a single-cycle pulse. |

|          | Tie to 0 if not used.                                                                                                                                                                                                                                                                                                         |

| CPU0TXEV | TX event output of the Cortex-M3 Event transmitted as a result of SEV instruction. This is a single-cycle pulse. You can use it to implement a more power efficient spin-lock in a multi-processo system.                                                                                                                     |

|          | In a multi-processor system, TXEV from each processor can be broadcast to the RXEV input of the other processors.                                                                                                                                                                                                             |

The system designer can configure the IoT Subsystem with or without support for CoreSight SoC.

If CoreSight SoC is enabled, the Processor Integration Layer is exposed to the top of the IoT Subsystem and can be connected to existing systems to form a multi core system. Event ports are used as described in the table.

If CoreSight SoC is disabled, the Cortex-M3 is expected to be a standalone (single) core. The system designer might chose to connect the RX event port to DMA done signals.

### 2.6 Timer

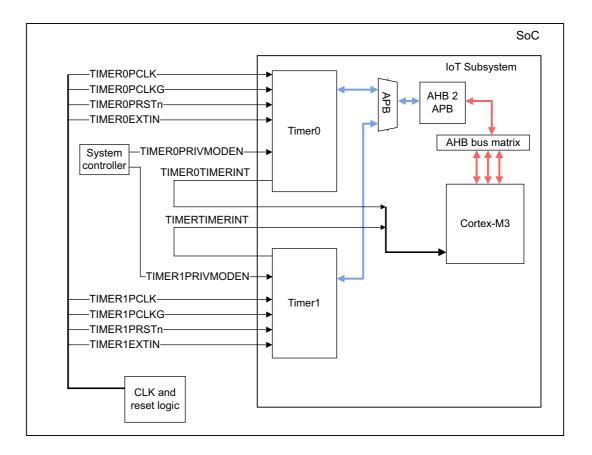

The IoT Subsystem includes two instances of APB timers. These are required to satisfy the mbed OS requirements.

### Figure 2-3 Timer interfaces

See also *Timer signals* on page A-10.

### 2.6.1 Security extension

Privilege mode enable signals determine whether only privileged accesses or both privileged and non-privileged accesses can write to the timer MMRs.

### Table 2-2 Privilege mode enable input signals

| Signal          | Clock      | Description                                                                                                                                                                                                   |

|-----------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TIMER0PRIVMODEN | TMER0PCLK  | <ul> <li>Defines if the timer memory mapped registers are writeable only by privileged access:</li> <li>0: Non privileged access can write MMRs</li> <li>1: Only Privileged access can write MMRs</li> </ul>  |

| TIMER1PRIVMODEN | TIMER1PCLK | <ul> <li>Defines if the timer memory mapped registers are writeable only by privileged access:</li> <li>0: Non privileged access can write MMRs.</li> <li>1: Only Privileged access can write MMRs</li> </ul> |

### 2.7 eFlash memory subsystem

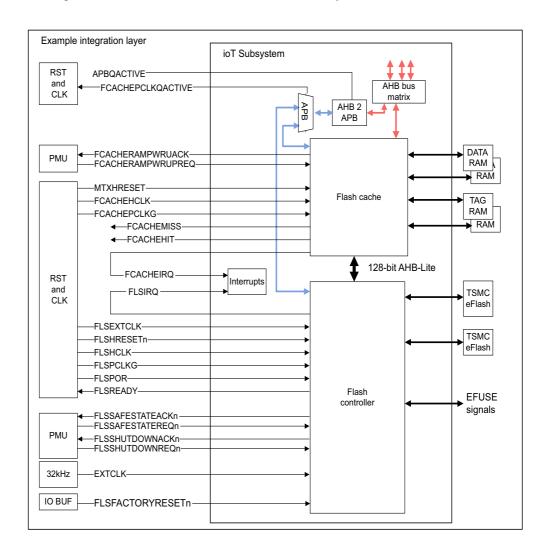

The figure below shows the connections to the flash subsystem.

### Figure 2-4 eFlash interface

The system designer can select generation of status registers that register cache hits and misses. If more detailed statistics are required, the designer can use the **FCACHEHIT** and **FCACHEMISS** signals and implement custom statistics collection logic. See also *eFlash signals* on page A-5.

### 2.7.1 eFlash cache

The IoT Subsystem includes an AHB instruction cache connected to the eFlash Controller to reduce eFlash accesses due to *execute in place* instructions fetches. This reduces the power consumption of the IoT Subsystem.

#### — Note —

Because the cache is only for instructions, AHB writes are bypassed and ignored. If a write changes program memory, software must invalidate the cache region.

The eFlash cache has the following features:

- Configurable cache size (minimum 512 bytes).

- Two way set associative.

- Configurable address bus size (based on flash memory size) so that tag memory size can be minimized.

- 128-bit AHB master to the AHB-Lite slave in the eFlash controller.

- 32 bit APB interface for configuration/status and write access

- Automatic/Manual power up.

- If the cache is powered down, the RAMs might be in retention. During power up the software can avoid invalidation of the cache RAMs and therefore save energy.

- Automatic/Manual invalidate cache RAM.

- Optional run-time configurable pre-fetcher.

- Compile time configurable performance counters accessible by SW.

- PMU interface supporting SRAM power-down or retention modes.

### 2.7.2 TSMC eFlash controller

The features of the eFlash controller include:

- 128-bit AHB slave interface to connect with eFlash cache master for read accesses.

- 32 bit APB interface for configuration/status and write access

- One IRQ line to notify status changes to the CPU and optionally let the CPU sleep or wake up while the eFlash is being programmed/erased.

- Supports two banks of flash memory as 2x128KB or 2x256KB.

- Supports eFlash Info page and Trim page with automatic self-repair function, and emulated security fuses.

- Factory reset request can perform an autonomous mass erase.

- Compatible with TSMC ULP55-TV2 embedded flash macros.

- Can be implemented with support for external low-power 32KHz clock to sequence program and erase operations.

### 2.8 Banked SRAM subsystem

The IoT Subsystem infrastructure supports up to four 32KB SRAMs. At least one 32KB SRAM must be implemented (SRAM bank 0).

If a SRAM bank is not implemented and the corresponding MTXREMAP bits are 1, then the corresponding address space is mapped to the AHB Slave expansion port of the interconnect.

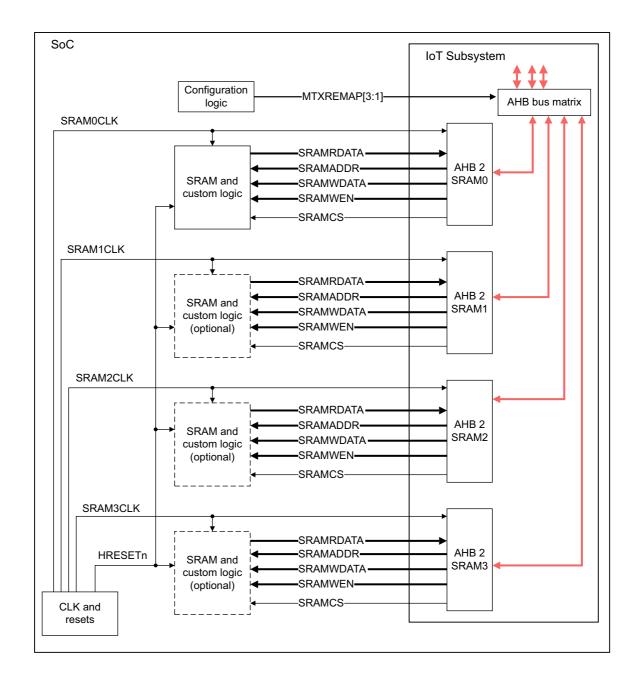

In Figure 2-5 on page 2-13, the MTXREMAP signals from the configuration logic are static during functional operation.

The SRAM modules are outside of the IoT Subsystem. The IoT Subsystem does not implement retention or power-down supports for the SRAMs. It is the responsibility of the SoC integration to implement power domains for the SRAM, control the power modes of the SRAM banks with a SoC level PMU.

The AHB2SRAM bridge always responds with OKAY to all AHB accesses, even if the connected SRAM is not functional because for example it is powered-down or in retention mode.

It is the responsibility of the software to not read or write the SRAMs when they are not functional. If the SW tries to access non-accessible SRAM, the AHB2SRAM bridge implementation ensures that system will not go to deadlock state because of a non-responsive SRAM. Read data is implementation specific.

#### Figure 2-5 SRAM interface

See also SRAM signals on page A-9.

### 2.9 AHB and APB expansion

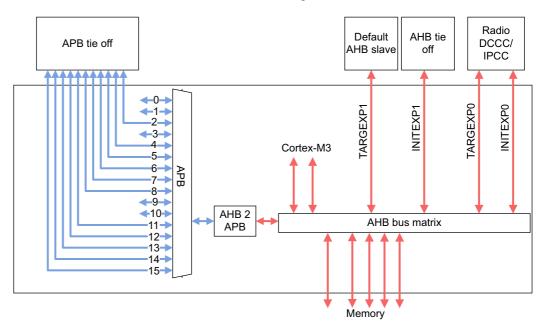

The AHB and APB bus structure is shown in the figure below:

### Figure 2-6 AHB and APB expansion buses

The APB and AHB tie off connections are for unused ports, and it is expected that these will be removed during synthesis.

See also Bus signals on page A-11.

### 2.9.1 APB slave multiplexer

The APB slave multiplexer, supports sixteen APB slaves in the IoT Subsystem. All ports are synchronous to the AHB expansion ports. Five APB ports are used for internal usage and eleven APB ports are hooked-up to the IoT Subsystem boundary and can be connected to external peripherals. The table below shows the usage of the APB ports in the IoT Subsystem:

### Table 2-3 APB ports

| APB port | Connection   |

|----------|--------------|

| PORT0    | TIMER0       |

| PORT1    | TIMER1       |

| PORT2    | APBTARGEXP2  |

| PORT3    | eFlash cache |

| PORT4    | APBTARGEXP4  |

| PORT5    | APBTARGEXP5  |

| PORT6    | APBTARGEXP6  |

| PORT7    | APBTARGEXP7  |

| PORT8    | APBTARGEXP8  |

### Table 2-3 APB ports (continued)

| APB port | Connection        |

|----------|-------------------|

| PORT9    | eFlash controller |

| PORT10   | eFlash controller |

| PORT11   | APBTARGEXP11      |

| PORT12   | APBTARGEXP12      |

| PORT13   | APBTARGEXP13      |

| PORT14   | APBTARGEXP14      |

| PORT15   | APBTARGEXP15      |

If an APB expansion interface is not used to connect a peripheral, the port must be tied off properly at SoC integration level.

### 2.9.2 AHB expansion

This section describes the AHB expansion features of the IoT Subsystem.

### AHB initiator ports

Two AHB INITIATOR ports permit external AHB masters to be connected to the IoT Subsystem. These ports are prefixed with INITEXP<0..1>:

- INITEXP0 port is reserved for the AHB DMA master port of the BlueTooth Radio.

- INITEXP1 port can be used to connect any additional AHB master to the system.

— Note —

If one of the initiator ports is not used, then it must be tied off properly at SoC integration level.

### AHB target ports

— Note —

Two AHB TARGET ports permit external AHB masters to be connected to the IoT Subsystem. These ports are prefixed with TARGETEXP<0..1>:

- TARGETEXP0 port is reserved for the AHB DMA slave port of the BlueTooth Radio.

- TARGETEXP1 port can be used to connect any additional AHB slave to the system.

If one of the target ports is not used, then the default slave must be connected to the port.

### 2.10 Debug and Trace

The SWJ-DP is a combined JTAG-DP and SW-DP that enables you to connect either an SWD or JTAG probe to a target. It is the standard CoreSight debug port.

To make efficient use of package pins, the JTAG pins use an auto-detect mechanism that switches between JTAG-DP and SW-DP depending on which probe is connected.

The Cortex-M3 TPIU is an optional component that acts as a bridge between the on-chip trace data from the *Embedded Trace Macrocell* (ETM) and the *Instrumentation Trace Macrocell* (ITM), with separate IDs, to a data stream. The TPIU encapsulates IDs where required, and the data stream is then captured by a *Trace Port Analyzer* (TPA). The Cortex-M3 TPIU is specially designed for low-cost debug.

— Note — \_\_\_\_

The default implementation reuses the TPIU and SWJ/DP from the Cortex-M3 package. This configuration is sufficient for basic use.

For more sophisticated multi-processor debug solution, a full CoreSight SoC IP solution can be licensed and implemented. If the CoreSight SoC option is selected, the TPIU and SWJ/DP blocks and corresponding interface signals are not present.

See also Debug and Trace signals on page A-14.

## Chapter 3 Programmers Model

This chapter describes the *IoT Subsystem* memory regions and registers, and provides information on how to program a SoC that contains an implementation of the IoT Subsystem.

It contains the following sections:

- *About this programmers model* on page 3-2.

- *Memory map* on page 3-3.

- *eFlash controller* on page 3-7.

- *eFlash cache* on page 3-21.

- *Interrupts* on page 3-30.

- *Wakeup Interrupt Controller (WIC)* on page 3-32.

- *Timer* on page 3-33.

- System registers on page 3-34.

- *Debug and Trace* on page 3-35.

### 3.1 About this programmers model

The following information applies to all registers:

- Do not attempt to access reserved or unused address locations. Attempting to access these locations can result in unpredictable behavior.

- Unless otherwise stated in the accompanying text:

- Do not modify undefined register bits.

- Ignore undefined register bits on reads.

- All register bits are reset to a logic 0 by a system or power up reset.

- The following describes the access type:

- **RW** Read and write.

- **RO** Read-only.

- WO Write-only.

### 3.2 Memory map

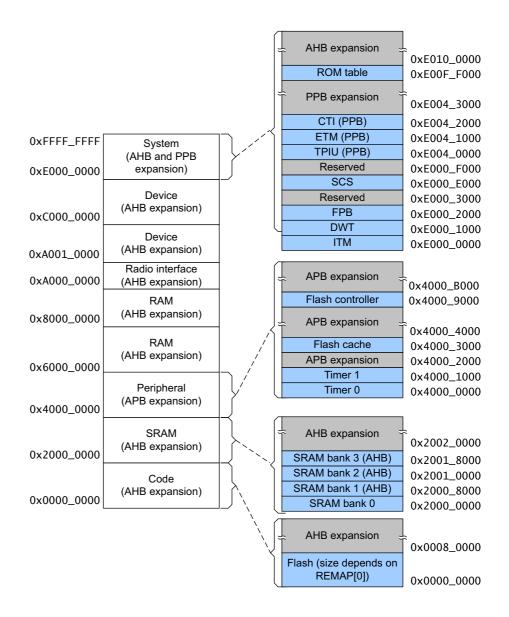

The memory map for the IoT Subsystem is shown in the figure below:

#### Figure 3-1 IoT Subsystem top-level memory map

### 3.2.1 Remap

The remapping feature of the bus matrix provides the following remapping options:

- **REMAP[0]** The Embedded flash memory region represents the maximum supported eFlash size: 512KB. If the size of the actual eFlash banks is 256kB, the upper 256kB can be remapped to the AHB expansion port as follows:

- 0: 512KB eFlash

- 1: 256KB eFlash upper 256kbytes mapped to AHB expansion port

- **REMAP[1]** If SRAM1 is not present the corresponding memory range can be mapped to AHB expansion port as follows:

- 0: SRAM1 present

- 1: SRAM1 not available, mapped to AHB expansion port

- **REMAP[2]** If SRAM2 is not present the corresponding memory range can be mapped to AHB expansion port as follows:

- 0: SRAM2 present

- 1: SRAM2 not available, mapped to AHB expansion port

- **REMAP[3]** If SRAM3 is not present the corresponding memory range can be mapped to AHB expansion port as follows:

- 0: SRAM3 present

- 1: SRAM3 not available, mapped to AHB expansion port

The PPB address region of the Cortex-M3 memory map is assigned to the default slave of the MTX thus returns SLVERR response.

# Table 3-1 Code and SRAM regions

| Region | Start      | End        | Peripheral    | Size   | AHB bus matrix | Re | ema | р |   | Comment                                        |

|--------|------------|------------|---------------|--------|----------------|----|-----|---|---|------------------------------------------------|

|        | Address    | Address    | name          |        | port           | 3  | 2   | 1 | 0 |                                                |

| Code   | 0x0        | 0x0003FFFF | eFlash 2x128K | 256K   | TARG_FLASH0    | -  | -   | - | - | Actual size is implementation defined          |

|        | 0x00040000 | 0x0007FFFF | eFlash 2x256K | 256K   | TARG_FLASH0    | -  | -   | - | 0 | Implementation defined                         |

|        |            |            | AHB Expansion | 2x128K | TARG_EXP1      | -  | -   | - | 1 | -                                              |

|        | 0x00080000 | 0x01FFFFFF | AHB Expansion | 511M   | TARG_EXP1      | -  | -   | - | - | -                                              |

| SRAM   | 0x20000000 | 0x20007FFF | SRAM0         | 32K    | TARG_SRAM0     | -  | -   | - | - | Bit band region                                |

|        | 0x20008000 | 0x2000FFFF | SRAM1         | 32K    | TARG_SRAM1     | -  | -   | 0 | - | Bit band region                                |

|        |            |            | AHB Expansion | 32K    | TARG_EXP1      | -  | -   | 1 | - | Bit band region                                |

|        | 0x20010000 | 0x20017FFF | SRAM2         | 32K    | TARG_SRAM2     | -  | 0   | - | - | Bit band region                                |

|        |            |            | AHB Expansion | 32K    | TARG_EXP1      | -  | 1   | - | - | Bit band region                                |

|        | 0x20018000 | 0x2001FFFF | SRAM          | 32K    | TARG_SRAM3     | 0  | -   | - |   | Bit band region                                |

|        |            |            | AHB Expansion | 32K    | TARG_EXP1      | 1  | -   | - |   | Bit band region                                |

|        | 0x20020000 | 0x3FFFFFFF | AHB Expansion | 511M   | TARG_EXP1      | -  | -   | - | - | Bit band region<br>0x20020000 to<br>0x200FFFFF |

|        |            |            |               |        |                |    |     |   |   | Bit band alias<br>0x22000000 to<br>0x23FFFFFF  |

# 3.2.2 Peripheral, expansion, and system regions

### Table 3-2 Expansion and system map

| Туре   | Start      | End        | Peripheral                 | Size  | AHB bus<br>matrix | Bus fabric  | Comment                           |

|--------|------------|------------|----------------------------|-------|-------------------|-------------|-----------------------------------|

| Periph | 0x40000000 | 0x40000FFF | Timer0                     | 4KB   | TARG_APB0         | APB port 0  | Bit band region                   |

| Periph | 0x40001000 | 0x40001FFF | Timer1                     | 4KB   | TARG_APB0         | APB port 1  | Bit band region                   |

| Periph | 0x40002000 | 0x40002FFF | APB expansion              | 4KB   | TARG_APB0         | APB port 2  | Bit band region                   |

| Periph | 0x40003000 | 0x40003FFF | eFlash cache               | 4KB   | TARG_APB0         | APB port 3  | Bit band region                   |

| Periph | 0x40004000 | 0x40004FFF | APB expansion              | 4KB   | TARG_APB0         | APB port 4  | Bit band region<br>Optional UART0 |

| Periph | 0x40005000 | 0x40005FFF | APB expansion              | 4KB   | TARG_APB0         | APB port 5  | Bit band region<br>Optional UART1 |

| Periph | 0x40006000 | 0x40006FFF | APB expansion              | 4KB   | TARG_APB0         | APB port 6  | Bit band region                   |

| Periph | 0x40007000 | 0x40007FFF | APB expansion              | 4KB   | TARG_APB0         | APB port 7  | Bit band region                   |

| Periph | 0x40008000 | 0x40008FFF | APB expansion              | 4KB   | TARG_APB0         | APB port 8  | Bit band region                   |

| Periph | 0x40009000 | 0x40009FFF | eFlash controller<br>MMRs  | 4KB   | TARG_APB0         | APB port 9  | Bit band region                   |

| Periph | 0x4000A000 | 0x4000A7FF | eFlash Ctrl Info<br>page 0 | 4KB   | TARG_APB0         | APB port 10 | Bit band region                   |

| Periph | 0x4000A800 | 0x4000AFFF | eFlash Ctrl Info<br>page 1 | 4KB   | TARG_APB0         | APB port 10 | Bit band region                   |

| Periph | 0x4000B000 | 0x4000BFFF | APB expansion              | 4KB   | TARG_APB0         | APB port 11 | Bit band region                   |

| Periph | 0x4000C000 | 0x4000CFFF | APB expansion              | 4KB   | TARG_APB0         | APB port 12 | Bit band region                   |

| Periph | 0x4000D000 | 0x4000EFFF | APB expansion              | 4KB   | TARG_APB0         | APB port 13 | Bit band region                   |

| Periph | 0x4000E000 | 0x4000EFFF | APB expansion              | 4KB   | TARG_APB0         | APB port 14 | Bit band region                   |

| Periph | 0x4000F000 | 0x4000FFFF | APB expansion              | 4KB   | TARG_EXP1         | APB port 15 | Bit band region                   |

| Periph | 0x40010000 | 0x5FFFFFFF | AHB expansion              | 511MB | TARG_APB0         | APB port 15 | Bit band region                   |

| RAM    | 0x60000000 | 0x7FFFFFFF | AHB Expansion              | 512MB | TARG_EXP1         | -           | -                                 |

| RAM    | 0x80000000 | 0x9FFFFFFF | AHB Expansion              | 512MB | TARG_EXP1         | -           | -                                 |

| Device | 0xA0000000 | 0xA000FFFF | AHB Expansion              | 64KB  | TARG_EXP0         | -           | Radio ICCC                        |

| Device | 0xA0010000 | 0xBFFFFFFF | AHB Expansion              | 511MB | TARG_EXP1         | -           | -                                 |

| Device | 0xC0000000 | 0xDFFFFFFF | AHB Expansion              | 512MB | TARG_EXP1         | -           | -                                 |

# Table 3-2 Expansion and system map (continued)

| Туре   | Start      | End        | Peripheral              | Size | AHB bus<br>matrix | Bus fabric   | Comment                |

|--------|------------|------------|-------------------------|------|-------------------|--------------|------------------------|

| System | 0xE0000000 | 0xE0000FFF | ITM (or<br>reserved)    | 4K   | Default slave     | PPB-Internal | Implementation defined |

|        | 0xE0001000 | 0xE0001FFF | DWT (or<br>reserved)    | 4K   | Default slave     | PPB-Internal | Implementation defined |

|        | 0xE0002000 | 0xE0002FFF | FPB (or reserved)       | 4K   | Default slave     | PPB-Internal | Implementation defined |

|        | 0xE0003000 | 0xE000DFFF | Reserved                | 44K  | Default slave     | PPB-Internal | -                      |

|        | 0xE000E000 | 0xE000EFFF | SCS (or reserved)       | 4K   | Default slave     | PPB-Internal | Implementation defined |

|        | 0xE000F000 | 0xE003FFFF | Reserved                | 196K | Default slave     | PPB-Internal | -                      |

|        | 0xE0040000 | 0xE0040FFF | TPIU (or PPB expansion) | 4K   | Default slave     | PPB-External | Implementation defined |

|        | 0xE0041000 | 0xE0041FFF | ETM (or PPB expansion)  | 4K   | Default slave     | PPB-External | Implementation defined |

|        | 0xE0042000 | 0xE0042FFF | CTI (or PPB expansion)  | 4K   | Default slave     | PPB-External | Implementation defined |

|        | 0xE0043000 | 0xE0043FFF | PPB expansion           | 4K   | Default slave     | PPB-External | -                      |

|        | 0xE0044000 | 0xE0044FFF | PPB expansion           | 4K   | Default slave     | PPB-External | -                      |

|        | 0xE0045000 | 0xE00FEFFF | PPB expansion           | 754K | Default slave     | PPB-External | -                      |

|        | 0xE00FF000 | 0xE00FFFFF | ROM table               | 4K   | Default slave     | PPB-External | -                      |

|        | 0xE0100000 | 0xFFFFFFFF | AHB expansion           | 511K | TARG_EXP1         | -            | -                      |

# 3.3 eFlash controller

This section defines all the memory mapped registers that are present in the eFlash controller. These registers are used for control, status, configuration, write data to the flash banks, and read-emulated fuse values.

# 3.3.1 eFlash interrupts

The eFlash Controller provides a HW interrupt signal (IRQ) that can be connected to the CPU. Interrupt status register can be used to identify the exact source of the interrupt.

The IRQ output is synchronous to HCLK. The type of interrupt is level interrupt. The active level is high.

The interrupt output will be high if at least one bit of IRQ\_MASKED\_STATUS register value is 1.

To clear an interrupt, software writes 1 to the corresponding bit of the IRQ\_CLR\_STATUS register.

eFlash Controller has the following interrupt sources:

**READY** Any write or erase operation finished normally.

TIMEOUT Row-write operation aborted by time out.

**NEXT** Row write operation ready to accept the next word.

There is a corresponding bit for each interrupt source in the IRQ\_SET\_STATUS, IRQ\_CLR\_STATUS, IRQ\_SET\_ENA, IRQ\_CLR\_ENA and IRQ\_MASKED\_STATUS registers.

# 3.3.2 APB memory map

### Table 3-3 APB memory map for eFlash controller

| Memory Name | Туре | Width | Number of<br>words | Striped | Address offset within eFlash controller |

|-------------|------|-------|--------------------|---------|-----------------------------------------|

| FLASH0_INFO | RO   | 32    | 512                | false   | 0x1000                                  |

| FLASH1_INFO | RO   | 32    | 512                | false   | 0x1800                                  |

# 3.3.3 Register summary

# Table 3-4 APB register map for eFlash controller

|                   |    | Width | Reset<br>value | Address<br>offset | Description                             |

|-------------------|----|-------|----------------|-------------------|-----------------------------------------|

| IRQ_SET_ENA       | RW | 32    | 0x00000000     | 0x0000            | IRQ_SET_ENA register on page 3-9        |

| IRQ_CLR_ENA       | RW | 32    | 0x00000000     | 0x0004            | IRQ_CLR_ENA register on page 3-9        |

| IRQ_SET_STATUS    | RW | 32    | 0x00000000     | 0x0008            | IRQ_SET_STATUS register on page 3-10    |

| IRQ_CLR_STATUS    | RW | 32    | 0x00000000     | 0x000C            | IRQ_CLR_STATUS register on page 3-10    |

| IRQ_MASKED_STATUS | RO | 32    | 0x00000000     | 0x0010            | IRQ_MASKED_STATUS register on page 3-11 |

| CTRL              | RW | 32    | 0x00000000     | 0x0014            | CTRL register on page 3-12              |

| STATUS            | RO | 32    | 0x00000000     | 0x0018            | STATUS register on page 3-12            |

| CONFIG0           | RW | 32    | 0x0008003F     | 0x001C            | CONFIG0 register on page 3-12           |

| CONFIG1           | RW | 32    | 0x00080000     | 0x0020            | CONFIG1 register on page 3-13           |

| CONFIG2           | RW | 32    | 0x00080000     | 0x0024            | CONFIG2 register on page 3-14           |

| WADDR             | RW | 32    | 0x00000000     | 0x0028            | WADDR register on page 3-14             |

| WDATA             | RW | 32    | 0x00000000     | 0x002C            | WDATA register on page 3-15             |

| EFUSE             | RO | 32    | 0x00000000     | 0x0030            | EFUSE register on page 3-15             |

| HWPARAMS0         | RO | 32    | 0x00002011     | 0x0034            | HWPARAMS0 register on page 3-15         |

| HWPARAMS1         | RO | 32    | 0x0000003F     | 0x0038            | HWPARAMS1 register on page 3-16         |

| HWPARAMS2         | RO | 32    | 0x00000000     | 0x003C            | HWPARAMS2 register on page 3-16         |

| HWPARAMS3         | RO | 32    | 0x00000000     | 0x0040            | HWPARAMS3 register on page 3-16         |

| PIDR4             | RO | 32    | 0x00000014     | 0x0FD0            | Product ID Register; PIDR4 on page 3-17 |

| PIDR5             | RO | 32    | 0x00000000     | 0x0FD4            | Product ID Register; PIDR5 on page 3-17 |

| PIDR6             | RO | 32    | 0x00000000     | 0x0FD8            | Product ID Register; PIDR6 on page 3-17 |

| PIDR7             | RO | 32    | 0x00000000     | 0x0FDC            | Product ID Register; PIDR7 on page 3-17 |

| PIDR0             | RO | 32    | 0x00000030     | 0x0FE0            | Product ID Register; PIDR0 on page 3-18 |

| PIDR1             | RO | 32    | 0x000000B8     | 0x0FE4            | Product ID Register; PIDR1 on page 3-18 |

| PIDR2             | RO | 32    | 0x0000000B     | 0x0FE8            | Product ID Register; PIDR2 on page 3-18 |

| Register name | Туре | Width | Reset<br>value | Address<br>offset | Description                               |

|---------------|------|-------|----------------|-------------------|-------------------------------------------|

| PIDR3         | RO   | 32    | 0×00000000     | 0x0FEC            | Product ID Register; PIDR3 on page 3-19   |

| CIDR0         | RO   | 32    | 0x0000000D     | 0x0FF0            | Component ID Register; CIDR0 on page 3-19 |

| CIDR1         | RO   | 32    | 0x000000F0     | 0x0FF4            | Component ID Register; CIDR1 on page 3-19 |

| CIDR2         | RO   | 32    | 0x00000005     | 0x0FF8            | Component ID Register; CIDR2 on page 3-20 |

| CIDR3         | RO   | 32    | 0x000000B1     | 0x0FFC            | Component ID Register; CIDR3 on page 3-20 |

#### Table 3-4 APB register map for eFlash controller (continued)

# IRQ\_SET\_ENA register

Enables, or reads the enable state of interrupts.

RW register at offset 0x0000.

For the non-reserved bits:

- On reads:

- 0: interrupt disabled.

- 1: interrupt enabled.

If not masked, a HW interrupt generated if the corresponding bit of the IRQ\_STATUS register is set.

- On writes:

- 0: no effect.

- 1: enable interrupt.

### Table 3-5 IRQ\_SET\_ENA register

| Bits   | Name     | Description | Access     | Reset |

|--------|----------|-------------|------------|-------|

| [31:3] | Reserved | -           | RO,<br>RAZ | 0     |

| [2]    | NEXT     | -           | RW         | 0     |

| [1]    | TIMEOUT  | -           | RW         | 0     |

| [0]    | READY    | -           | RW         | 0     |

# IRQ\_CLR\_ENA register

Disables, or reads, the enable state of interrupts.

RW register at offset 0x0004.

For the non-reserved bits:

- On reads:

- 0: interrupt disabled.

- 1: interrupt enabled.

If not masked, a HW interrupt generated if the corresponding bit of the IRQ\_STATUS register is set.

- On writes:

- 0: no effect.

— 1: disable interrupt.

| Bits   | Name     | Description | Access     | Reset |

|--------|----------|-------------|------------|-------|

| [31:3] | Reserved | -           | RO,<br>RAZ | 0     |

| [2]    | NEXT     | -           | RW         | 0     |

| [1]    | TIMEOUT  | -           | RW         | 0     |

| [0]    | READY    | -           | RW         | 0     |

# Table 3-6 IRQ\_SET\_ENA register

### IRQ\_SET\_STATUS register

Shows the current raw status of interrupts or sets the status of interrupts.

RW register at offset 0x0008.

For the non-reserved bits:

- On reads:

- 0: interrupt not pending.

- 1: interrupt pending.

- On writes:

- 0: no effect.

- 1: sets the state of the interrupt to pending.

#### Table 3-7 IRQ\_SET\_STATUS register

| Bits   | Name     | Description                                                                                                                                                | Access     | Reset |

|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|

| [31:3] | Reserved | -                                                                                                                                                          | RO,<br>RAZ | 0     |

| [2]    | NEXT     | This interrupt is set by HW during word-write operation whenever HW is ready to accept the next word.                                                      | RW         | 0     |

| [1]    | TIMEOUT  | This interrupt is set by HW when any row-write operation<br>finished by HW as a result of SW not clearing the NEXT<br>interrupt within the specified time. | RW         | 0     |

| [0]    | READY    | This interrupt set by HW when any word-write, row-write, page-erase, mass-erase operation finishes.                                                        | RW         | 0     |

### IRQ\_CLR\_STATUS register

Shows the current raw status of interrupts or clears the status of interrupts.

RW register at offset 0x000C.

For the non-reserved bits:

- On reads:

- 0: interrupt not pending.

- 1: interrupt pending.

- On writes:

٠

- 0: no effect.

- 1: clears the pending state of the interrupt.

### Table 3-8 IRQ\_CLR\_STATUS register

| Bits   | Name     | Description                                                                                                                                                | Access     | Reset |

|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|

| [31:3] | Reserved | -                                                                                                                                                          | RO,<br>RAZ | 0     |

| [2]    | NEXT     | This interrupt is set by HW during word-write operation<br>whenever HW is ready to accept the next word.                                                   | RW         | 0     |

| [1]    | TIMEOUT  | This interrupt is set by HW when any row-write operation<br>finished by HW as a result of SW not clearing the NEXT<br>interrupt within the specified time. | RW         | 0     |

|        |          | On reads:                                                                                                                                                  |            |       |

|        |          | 0 = Interrupt is not pending.                                                                                                                              |            |       |

|        |          | 1 = Interrupt is pending.                                                                                                                                  |            |       |

|        |          | On writes:                                                                                                                                                 |            |       |

|        |          | 0 = No effect.                                                                                                                                             |            |       |

|        |          | 1 = Clears the pending state of the interrupt.                                                                                                             |            |       |

| [0]    | READY    | This interrupt is set by HW when any word-write, row-write, page-erase, or mass-erase operation finishes.                                                  | RW         | 0     |

|        |          | On reads:                                                                                                                                                  |            |       |

|        |          | 0 = Interrupt is not pending.                                                                                                                              |            |       |

|        |          | 1 = Interrupt is pending.                                                                                                                                  |            |       |

|        |          | On writes:                                                                                                                                                 |            |       |

|        |          | 0 = No effect.                                                                                                                                             |            |       |

|        |          | 1 = Clears the pending state of the interrupt.                                                                                                             |            |       |

# IRQ\_MASKED\_STATUS register

Shows for each interrupt if it is pending and the cause of the interrupt line being asserted.

RO register at offset 0x0010.

- On reads:

- 0: interrupt is not causing IRQ line assertion.

- 1: interrupt is cause of IRQ line assertion. Interrupt is pending and enabled.

# Table 3-9 IRQ\_MASKED\_STATUS register

| Bits   | Name     | Description | Access     | Reset |

|--------|----------|-------------|------------|-------|

| [31:3] | Reserved | -           | RO,<br>RAZ | 0     |

| [2]    | NEXT     | -           | RO         | 0     |

| [1]    | TIMEOUT  | -           | RO         | 0     |

| [0]    | READY    | -           | RO         | 0     |

# **CTRL** register

eFlash control register.

If **SAFESTATEREQn** or **SHUTDOWNREQn** is asserted, the eFlash controller will reject any write attempt to this register and respond with an **APB ERROR** response.

RW register at offset 0x0014.

#### Table 3-10 CTRL register

| Bits   | Name        | Description                                                                                                   | Access     | Reset |

|--------|-------------|---------------------------------------------------------------------------------------------------------------|------------|-------|

| [31:5] | Reserved    | -                                                                                                             | RO,<br>RAZ | 0     |

| [4]    | STOP        | Stop any write or erase operation. High voltage discharge is taken care of by eFlash Controller.              | RW         | 0     |

| [3]    | MASS_ERRASE | Erase all pages of eFlash.                                                                                    | RW         | 0     |

| [2]    | ERASE       | Erase one page of eFlash.                                                                                     | RW         | 0     |

| [1]    | ROW_WRITE   | Write one or more words (32 bit) to a row of eFlash (to sequential addresses) during one high voltage period. | RW         | 0     |

| [0]    | WRITE       | Write one word (32 bit) of data to eFlash.                                                                    | RW         | 0     |

### STATUS register

Status or read or erase operation.

RO register at offset 0x0018.

### Table 3-11 STATUS register

| Bits   | Name     | Description                                                                                                       | Access     | Reset |

|--------|----------|-------------------------------------------------------------------------------------------------------------------|------------|-------|

| [31:2] | Reserved | -                                                                                                                 | RO,<br>RAZ | 0     |

| [1]    | LOCK     | Write/Erase lock. Lock conditions are<br>SAFESTATEREQn asserted or<br>SHUTDOWNREQn asserted.                      | RO         | 1     |

|        |          | 0: Write and Erase operations can be executed by the eFlash controller.                                           |            |       |

|        |          | 1: The eFlash controller will reject any write or erase with an APB <b>ERROR</b> response.                        |            |       |

| [0]    | BUSY     | eFlash Controller is executing any write or erase<br>operation. Indicates that any eFlash bank is in HV<br>state. | RO         | 0     |

# **CONFIG0** register

Configuration register.

# RW register at offset 0x001C.

### Table 3-12 CONFIG0 register

| Bits    | Name         | Description                                                                                                                                                                                                                                                                                                                                                                                                       | Access     | Reset         |

|---------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------|

| [31:26] | Reserved     | -                                                                                                                                                                                                                                                                                                                                                                                                                 | RO,<br>RAZ | 0             |

| [25:16] | ER_CLK_COUNT | Erase clock configuration register.<br>Set the number of clock cells in 1ms period.<br>(ER_CLK_COUNT+1) * Clock_period > 1ms<br>Minimum value is the nearest integer that results in a<br>period > 1ms.<br>The clock source is always EXTCLK. The valid<br>EXTCLK frequency range is 1kHz - 1MHz.<br>This register is not implemented if EXTCLKEN<br>parameter set to 0 (RAZ).                                    | RW         | ERCLKCOUNTRST |

| [15:8]  | WR_CLK_COUNT | Write clock configuration register.<br>Set the number of clock cells in 1us period.<br>If EXT_CLK_CONF is 0x0 or 0x1<br>then(WR_CLK_COUNT * HCLK-period) >= 1us.<br>If EXT_CLK_CONF is 0x2 then(WR_CLK_COUNT *<br>EXTCLK-period) >= 1us.                                                                                                                                                                          | RW         | WRCLKCOUNTRST |

| [7:6]   | ETC_CLK_CONF | <ul> <li>Write/erase timers source clock configuration.</li> <li>If EXTCLKEN parameter is set to 0, then this register is tied to 0x0.</li> <li>0x0 [Internal] External clock not used.</li> <li>0x1 [Erase] External clock used for erase counters (&gt;1ms). HCLK used for write counters.</li> <li>0x2 [Write] External clock used for write and erase counters (&gt;1us).</li> <li>0x3 [Reserved].</li> </ul> | RW         | 0x0           |

| [5:0]   | RD_CLK_CONF  | <ul> <li>Read clock configuration register.</li> <li>0x0 Reserved.</li> <li>0x1 1_cycle_read_mode. This value is allowed only if HALFCLKREAD parameter is set to 1.</li> <li>Read from flash in 1 clock cycle over AHB interface, Read from flash in 2 clock cycles over APB interface.</li> <li>0x2-03F normal_read_mode. eFlash read operation requires RD_CLK_COUNT number of HCLK cycles.</li> </ul>          | RW         | RDCLKCOUNTRST |

# **CONFIG1** register

Configuration register.

#### RW register at offset 0x0020.

#### Table 3-13 CONFIG1 register

| Bits    | Name         | Description                                                                 | Access | Reset     |

|---------|--------------|-----------------------------------------------------------------------------|--------|-----------|

| [31:26] | TNVH         | eFlash timing parameter. NVSTR hold time in microseconds.                   | RW     | TNVH_RST  |

| [23:16] | TPROG        | eFlash timing parameter. Programming time in microseconds.                  | RW     | TPROG_RST |

| [15:8]  | TPGS         | eFlash timing parameter. NVSTR to program setup time in microseconds.       | RW     | TPGS_RST  |

| [7:0]   | ETC_CLK_CONF | eFlash timing parameter. PROG or ERASE to NVSTR setup time in microseconds. | RW     | TNVS_RST  |

### **CONFIG2** register

Configuration register.

RW register at offset 0x0024.

#### Table 3-14 CONFIG2 register

| Bits    | Name   | Description                                                | Access | Reset      |

|---------|--------|------------------------------------------------------------|--------|------------|

| [31:24] | TME    | eFlash timing parameter. Mass erase time in ms.            | RW     | TME_RST    |

| [23:16] | TERASE | eFlash timing parameter. Erase time in ms.                 | RW     | TERASE_RST |

| [15:8]  | TRCV   | eFlash timing parameter. Recovery time in microseconds.    | RW     | TRCV_RST   |

| [7:0]   | TNVH1  | eFlash timing parameter. NVSTR1 hold time in microseconds. | RW     | TNVH1_RST  |

# WADDR register

Write/Erase address register.

Only word addressing is allowed. Bits [1:0] are tied to 0.

Attempting to write an unmapped address into this register results in an APB ERROR response and the register value is not modified.

It is responsibility of software to ensure that the addressed word of eFlash is in erased state.

The bits have special addressing for information pages:

- [31]: Select Bank-1 information page.

- [30]: Select Bank-0 information page.

- [10:2]: Info page word address offset.

RW register at offset 0x0028.

#### Table 3-15 WADDR register

| Bits   | Name     | Description | Access | Reset |

|--------|----------|-------------|--------|-------|

| [31:2] | WADDR1   | -           | RW     | 0     |

| [1:0]  | Reserved | -           | RO     | 0     |

### WDATA register

Write data register.

RW register at offset 0x002C.

### Table 3-16 WDATA register

| Bits   | Name  | Description | Access | Reset |

|--------|-------|-------------|--------|-------|

| [31:0] | WDATA | -           | RW     | 0     |

### **EFUSE register**

Each bit of this register corresponds to an emulated fuse value.

RO register at offset 0x0030.

### Table 3-17 EFUSE register

| Bits   | Name  | Description          | Access | Reset |

|--------|-------|----------------------|--------|-------|

| [31:0] | EFUSE | EFUSE[0] is efuse 0. | RO     | 0     |

### HWPARAMS0 register

Timeout and clock control register. The value of this register is defined by the system designer. RO register at offset 0x0034.

### Table 3-18 HWPARAMS0 register

| Bits    | Name      | Description                                     | Access     | Reset |

|---------|-----------|-------------------------------------------------|------------|-------|

| [31:16] | Reserved  | -                                               | RO,<br>RAZ | 0     |

| [15:8]  | TIMEOUT   | Row-write timeout parameter                     | RO         | 0x20  |

| [7]     | Reserved  | -                                               | RO,<br>RAZ | 0     |

| [6]     | EXTCLKEN  | Enable EXTCLK input                             | RO         | 0     |

| [5]     | HALFCLKRD | Allow setting RD_CLK_COUNT to 0                 | RO         | 0     |

| [4:0]   | FLASHSIZE | FLASHSIZE parameter = log2(flash size in bytes) | RO         | 0x11  |

# HWPARAMS1 register