# ARM<sup>®</sup> Cortex<sup>®</sup>-R7 MPCore

Revision: r0p1

**Technical Reference Manual**

### ARM Cortex-R7 MPCore Technical Reference Manual

Copyright © 2012, 2014 ARM. All rights reserved.

#### **Release Information**

The following changes have been made to this book.

|                   |       |                  | enange metery           |

|-------------------|-------|------------------|-------------------------|

| Date              | Issue | Confidentiality  | Change                  |

| 21 March 2012     | А     | Non-Confidential | First release for r0p0  |

| 28 September 2012 | В     | Non-Confidential | First release for r0p1  |

| 28 November 2014  | С     | Non-Confidential | Second release for r0p1 |

Change history

#### **Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of ARM. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, ARM makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to ARM's customers is not intended to create or refer to any partnership relationship with any other company. ARM may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any signed written agreement covering this document with ARM, then the signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

Words and logos marked with ® or ™ are registered trademarks or trademarks of ARM Limited or its affiliates in the EU and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow ARM's trademark usage guidelines at http://www.arm.com/about/trademark-usage-guidelines.php

Copyright ©, ARM Limited or its affiliates. All rights reserved.

ARM Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

## Contents ARM Cortex-R7 MPCore Technical Reference Manual

Preface

|           |       | About this book viii                       |

|-----------|-------|--------------------------------------------|

|           |       | Feedback xii                               |

| Chapter 1 | Intro | oduction                                   |

| •         | 1.1   | About the Cortex-R7 MPCore processor 1-2   |

|           | 1.2   | Compliance 1-3                             |

|           | 1.3   | Features 1-4                               |

|           | 1.4   | Interfaces 1-5                             |

|           | 1.5   | Configurable options 1-6                   |

|           | 1.6   | Redundant processor comparison 1-8         |

|           | 1.7   | Test features 1-9                          |

|           | 1.8   | Product documentation and design flow 1-10 |

|           | 1.9   | Product revisions 1-12                     |

| -         |       |                                            |

| Chapter 2 | Fund  | ctional Description                        |

|           | 2.1   | About the functions                        |

|           | 2.2   | Interfaces 2-4                             |

|           | 2.3   | Clocking, resets, and initialization 2-5   |

|           | 2.4   | Power management 2-13                      |

|           |       |                                            |

|           | 2.5   | Processor pons 2-19                        |

| Chapter 3 |       | Processor ports 2-19                       |

| Chapter 3 |       | grammers Model                             |

| Chapter 3 | Prog  |                                            |

|            | 3.4   | Memory formats                                             |            |

|------------|-------|------------------------------------------------------------|------------|

|            | 3.5   | Addresses in the Cortex-R7 MPCore processor                |            |

|            |       |                                                            |            |

| Chapter 4  | -     | em Control                                                 |            |

|            | 4.1   | About system control                                       |            |

|            | 4.2   | Register summary                                           |            |

|            | 4.3   | Register descriptions                                      | 4-17       |

| Chapter 5  | Float | ting Point Unit Programmers Model                          |            |

| •          | 5.1   | About the FPU programmers model                            | 5-2        |

|            | 5.2   | IEEE 754 standard compliance                               |            |

|            | 5.3   | Instruction throughput and latency                         |            |

|            | 5.4   | Register summary                                           |            |

|            | 5.5   | Register descriptions                                      |            |

| Ohantan C  | Lava  |                                                            |            |

| Chapter 6  |       | I One Memory System                                        | <b>C D</b> |

|            | 6.1   | About the L1 memory system                                 |            |

|            | 6.2   | Fault handling                                             |            |

|            | 6.3   | About the TCMs                                             |            |

|            | 6.4   | About the caches                                           |            |

|            | 6.5   | Local exclusive monitor                                    |            |

|            | 6.6   | Memory types and L1 memory system behavior                 | 6-18       |

|            | 6.7   | Error detection events                                     | 6-19       |

| Chapter 7  | Fault | t Detection                                                |            |

| onaptor    | 7.1   | About fault detection                                      | 7_2        |

|            | 7.2   | RAM protection                                             |            |

|            | 7.2   | Logic protection                                           |            |

|            | -     | - ·                                                        |            |

|            | 7.4   | External memory and bus protection                         |            |

|            | 7.5   | Programmers view                                           |            |

|            | 7.6   | Lock-step                                                  |            |

|            | 7.7   | Static split/lock                                          |            |

| Chapter 8  | Dete  | rminism Support                                            |            |

| •          | 8.1   | About determinism support                                  |            |

|            | 8.2   | Memory Protection Unit                                     |            |

|            | 8.3   | Branch prediction                                          |            |

|            | 8.4   | Low latency interrupt mode                                 |            |

|            | 8.5   |                                                            |            |

|            |       | System configurability and QoS<br>Instruction and data TCM |            |

|            | 8.6   |                                                            |            |

| Chapter 9  | Multi | iprocessing                                                |            |

|            | 9.1   | About multiprocessing and the SCU                          | 9-2        |

|            | 9.2   | Multiprocessing programmers view                           |            |

|            | 9.3   | SCU registers                                              |            |

|            | 9.4   | Interrupt controller                                       |            |

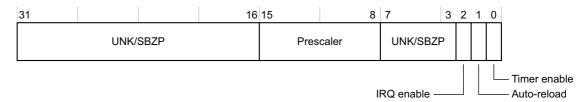

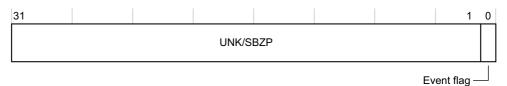

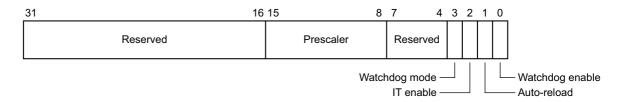

|            | 9.5   | Private timer and watchdog                                 |            |

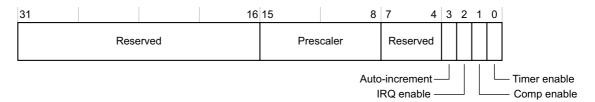

|            | 9.6   | Global timer                                               |            |

|            | 9.7   | Accelerator Coherency Port                                 |            |

| Chanten 40 | Man   | itarian Trees and Debug                                    |            |

| Chapter 10 |       | About monitoring, trace, and debug                         | 10.0       |

|            | 10.1  | About monitoring, trace, and debug                         |            |

|            | 10.2  | Performance Monitoring Unit                                |            |

|            | 10.3  | Memory Reconstruction Port                                 |            |

|            | 10.4  | Embedded Trace Macrocell                                   |            |

|            | 10.5  | Debug                                                      | 10-12      |

|            |       |                                                            |            |

| Chapter 11 | Level | Two Interface                                            |       |

|------------|-------|----------------------------------------------------------|-------|

| •          | 11.1  | About the L2 interface                                   | 11-2  |

|            | 11.2  | Optimized accesses to the L2 memory interface            | 11-8  |

|            | 11.3  | Accessing RAMs using the AXI3 interface                  |       |

|            | 11.4  | STRT instructions                                        |       |

|            | 11.5  | Event communication with an external agent using WFE/SEV | 11-11 |

|            | 11.6  | Accelerator Coherency Port interface                     |       |

| Appendix A | Signa | I Descriptions                                           |       |

| ••         | A.1   | About the signal descriptions                            | A-2   |

|            | A.2   | Clock and control signals                                | A-3   |

|            | A.3   | Reset signals                                            | A-5   |

|            | A.4   | Interrupt controller signals                             |       |

|            | A.5   | Configuration signals                                    |       |

|            | A.6   | Standby signals                                          | A-9   |

|            | A.7   | Power management signals                                 | A-10  |

|            | A.8   | AXI3 interfaces                                          | A-11  |

|            | A.9   | Performance monitoring signals                           | A-23  |

|            | A.10  | Exception flag signals                                   |       |

|            | A.11  | Error detection notification signals                     | A-25  |

|            | A.12  | Test interface                                           | A-31  |

|            | A.13  | MBIST interface                                          | A-32  |

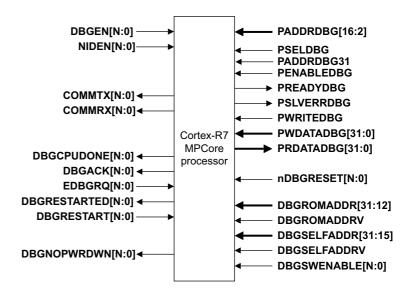

|            | A.14  | External debug signals                                   | A-34  |

|            | A.15  | ETM/ATB interface signals                                | A-37  |

|            | A.16  | Memory reconstruction port signals                       | A-39  |

|            | A.17  | Power gating interface signals                           | A-40  |

| Appendix B | Cycle | Timings and Interlock Behavior                           |       |

|            | B.1   | About instruction cycle timing                           | B-2   |

|            | B.2   | Data-processing instructions                             | B-3   |

|            | B.3   | Load and store instructions                              | B-4   |

|            | B.4   | Multiplication instructions                              | B-7   |

|            | B.5   | Branch instructions                                      | B-8   |

|            | B.6   | Serializing instructions                                 | B-9   |

|            |       |                                                          |       |

Appendix C

Revisions

## Preface

This preface introduces the *ARM*<sup>®</sup> *Cortex*<sup>®</sup>-*R7 MPCore Technical Reference Manual*. It contains the following sections:

- *About this book* on page viii.

- *Feedback* on page xii.

## About this book

This book is for the Cortex-R7 MPCore processor.

| Product revision status | ;                                                                                                                                                                               |             |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|                         | The $rnpn$ identifier indicates the revision status of the product described in this book <b>rn</b> Identifies the major revision of the product.                               | k, where:   |

|                         | <b>p</b> <i>n</i> Identifies the minor revision or modification status of the product.                                                                                          |             |

| Intended audience       |                                                                                                                                                                                 |             |

|                         | This book is written for system designers, system integrators, and programmers whe designing or programming a <i>System-on-Chip</i> (SoC) that uses the Cortex-R7 MPCore        |             |

| Using this book         |                                                                                                                                                                                 |             |

|                         | This book is organized into the following chapters:                                                                                                                             |             |

|                         | Chapter 1 Introduction                                                                                                                                                          |             |

|                         | Read this for an introduction to the Cortex-R7 MPCore processor.                                                                                                                |             |

|                         | Chapter 2 Functional Description                                                                                                                                                |             |

|                         | Read this for descriptions of the major functional blocks.                                                                                                                      |             |

|                         | Chapter 3 Programmers Model                                                                                                                                                     |             |

|                         | Read this for a description of the Cortex-R7 MPCore processor regist programming information.                                                                                   | ers and     |

|                         | Chapter 4 System Control                                                                                                                                                        |             |

|                         | Read this for a description of the system control coprocessor registers programming information.                                                                                | and         |

|                         | Chapter 5 Floating Point Unit Programmers Model                                                                                                                                 |             |

|                         | Read this for a description of the Floating Point Unit (FPU) support.                                                                                                           |             |

|                         | Chapter 6 Level One Memory System                                                                                                                                               |             |

|                         | Read this for a description of the Level One (L1) memory system.                                                                                                                |             |

|                         | Chapter 7 Fault Detection                                                                                                                                                       |             |

|                         | Read this for a description of the fault detection features, including <i>E Correcting Code</i> (ECC), lock-step, and split/lock.                                               | rror        |

|                         | Chapter 8 Determinism Support                                                                                                                                                   |             |

|                         | Read this for a description of the determinism support features, include <i>Memory Protection Unit</i> (MPU) and <i>Quality of Service</i> (QoS).                               | ling the    |

|                         | Chapter 9 Multiprocessing                                                                                                                                                       |             |

|                         | Read this for a description of the multiprocessing features, including <i>Control Unit</i> (SCU), interrupt controller, timers and watchdog, and <i>AcCoherency Port</i> (ACP). |             |

|                         | Chapter 10 Monitoring, Trace, and Debug                                                                                                                                         |             |

|                         | Read this for a description of the monitoring, trace, and debug feature<br>Integration Test Registers.                                                                          | es, and the |

#### Chapter 11 Level Two Interface

Read this for a description of the Level Two (L2) interface.

#### **Appendix A** Signal Descriptions

Read this for a description of the Cortex-R7 MPCore processor signals.

#### Appendix B Cycle Timings and Interlock Behavior

Read this for a description of the Cortex-R7 MPCore instruction cycle timing.

#### Appendix C Revisions

Read this for a description of the technical changes between released issues of this book.

#### Glossary

The *ARM*<sup>®</sup> *Glossary* is a list of terms used in ARM documentation, together with definitions for those terms. The *ARM*<sup>®</sup> *Glossary* does not contain terms that are industry standard unless the ARM meaning differs from the generally accepted meaning.

See ARM<sup>®</sup> Glossary http://infocenter.arm.com/help/topic/com.arm.doc.aeg0014-/index.html.

#### Conventions

Conventions that this book can use are described in:

- *Typographical conventions.*

- *Timing diagrams* on page x.

- Signals on page x.

#### **Typographical conventions**

The following table describes the typographical conventions:

| Style             | Purpose                                                                                                                                                                                                          |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| italic            | Introduces special terminology, denotes cross-references, and citations.                                                                                                                                         |

| bold              | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.                                                                            |

| monospace         | Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.                                                                                                      |

| <u>mono</u> space | Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.                                                                          |

| monospace italic  | Denotes arguments to monospace text where the argument is to be replaced by a specific value.                                                                                                                    |

| monospace bold    | Denotes language keywords when used outside example code.                                                                                                                                                        |

| <and></and>       | Enclose replaceable terms for assembler syntax where they appear in code or code fragments. For example:<br>MRC p15, 0 <rd>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></rd>                                |

| SMALL CAPITALS    | Used in body text for a few terms that have specific technical meanings, that are defined in the <i>ARM Glossary</i> . For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE. |

#### **Timing diagrams**

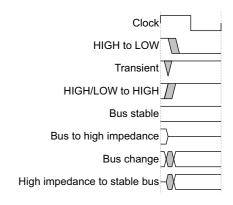

The figure named *Key to timing diagram conventions* explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

#### Key to timing diagram conventions

#### Signals

The signal conventions are:

| Signal level | The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means: |

|--------------|-------------------------------------------------------------------------------------------------------------|

|              | <ul><li>HIGH for active-HIGH signals.</li><li>LOW for active-LOW signals.</li></ul>                         |

| Lower-case n | At the start or end of a signal name denotes an active-LOW signal.                                          |

#### Additional reading

This section lists publications by ARM and by third parties.

See Infocenter http://infocenter.arm.com, for access to ARM documentation.

#### **ARM** publications

This book contains information that is specific to this product. See the following documents for other relevant information:

- ARM<sup>®</sup> Architecture Reference Manual ARMv7-A and ARMv7-R edition (ARM DDI 0406).

- ARM Embedded Trace Macrocell Architecture Specification, ETMv4 (ARM DDI 0406).

- ARM<sup>®</sup> CoreSight<sup>™</sup> ETM-R7 Technical Reference Manual (ARM DDI 0459).

- ARM<sup>®</sup> CoreSight<sup>™</sup> Architecture Specification (ARM IHI 0029).

- ARM<sup>®</sup> CoreSight<sup>™</sup> SoC-400 Technical Reference Manual (ARM DDI 0480).

- *ARM*<sup>®</sup> *AMBA*<sup>®</sup> *AXI and ACE Protocol Specification AXI3, AXI4, and AXI4-Lite, ACE and ACE-Lite* (ARM IHI 0022).

- ARM<sup>®</sup> AMBA<sup>®</sup> 3 AHB-Lite Protocol Specification (ARM IHI 0033).

- ARM<sup>®</sup> AMBA<sup>®</sup> APB Protocol Specification (ARM IHI 0024).

- ARM<sup>®</sup> Generic Interrupt Controller Architecture Specification (ARM IHI 0048).

- *ARM*<sup>®</sup> *CoreLink*<sup>™</sup> *Level 2 Cache Controller L2C-310 Technical Reference Manual* (ARM DDI 0246).

The following confidential books are only available to licensees:

- ARM<sup>®</sup> Cortex<sup>®</sup> -R7 MPCore Configuration and Sign-off Guide (ARM DII 0251).

- ARM<sup>®</sup> Cortex<sup>®</sup>-R7 MPCore Integration Manual (ARM DIT 0030).

- *ARM<sup>®</sup> CoreSight<sup>™</sup> SoC-400 Implementation Guide* (ARM DII 0267).

- ARM<sup>®</sup> CoreSight<sup>™</sup> SoC-400 Integration Manual (ARM DIT 0037).

- *ARM<sup>®</sup> CoreSight<sup>™</sup> SoC-400 System Design Guide* (ARM DGI 0018).

- *ARM<sup>®</sup> CoreSight<sup>™</sup> SoC-400 User Guide* (ARM DUI 0563).

#### Other publications

This section lists relevant documents published by third parties:

- 1149.1-2013 -IEEE Standard for Test Access Port and Boundary-Scan Architecture (JTAG).

- 754-2008 IEEE Standard for Floating-Point Arithmetic.

## Feedback

ARM welcomes feedback on this product and its documentation.

#### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

#### Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- The title.

- The number, ARM DDI 0458C.

- The page numbers to which your comments apply.

- A concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

#### — Note —

ARM tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader.

## Chapter 1 Introduction

This chapter introduces the Cortex-R7 MPCore processor and its features. It contains the following sections:

- *About the Cortex-R7 MPCore processor* on page 1-2.

- *Compliance* on page 1-3.

- *Features* on page 1-4.

- *Interfaces* on page 1-5.

- *Configurable options* on page 1-6.

- *Redundant processor comparison* on page 1-8.

- *Test features* on page 1-9.

- *Product documentation and design flow* on page 1-10.

- *Product revisions* on page 1-12.

## 1.1 About the Cortex-R7 MPCore processor

The Cortex-R7 MPCore processor is a mid-range processor for use in deeply-embedded, real-time systems, and consists of one or two Cortex-R7 processors in a single MPCore device. It implements the ARMv7-R architecture, and includes Thumb-2 technology for optimum code density and processing throughput.

The pipeline has a dual *Arithmetic Logic Unit* (ALU), with dual-issuing of instructions for efficient utilization of other resources such as the register file. The processor has *Level 1* (L1) data cache coherency in a cluster with up to two processors, and an optional hardware *Accelerator Coherency Port* (ACP) is provided to reduce software cache maintenance operations when sharing memory regions with other masters.

Interrupt latency is kept low by interrupting and restarting load-store multiple instructions, and by use of an integrated interrupt controller. The Cortex-R7 MPCore processor provides two specialized memory solutions for low-latency and determinism:

- *Tightly-Coupled Memory* (TCM) offers very low latency and determinism, but has limited memory space.

- Local RAM, cached by L1, offers less low latency than TCM, but latencies are still bounded, so it is deterministic. This solution offers larger memory space than TCM, and is coherent in multiprocessor configurations.

Optional *Error Correcting Code* (ECC) is used on the processor ports and in L1 memories to provide improved reliability and address fault-critical applications.

Many of the features, including the caches, TCM, and ECC are configurable so that a given processor implementation can be tailored to the application for efficient power and area usage.

## 1.2 Compliance

The Cortex-R7 MPCore processor complies with, or implements, the specifications described in:

- ARM architecture.

- Trace macrocell.

- Advanced Microcontroller Bus Architecture.

- *Debug architecture.*

- Generic Interrupt Controller architecture.

This TRM complements architecture reference manuals, architecture specifications, protocol specifications, and relevant external standards. It does not duplicate information from these sources.

#### 1.2.1 ARM architecture

The Cortex-R7 MPCore processor implements the ARMv7-R architecture and ARMv7 debug architecture. The ARMv7-R architecture provides 32-bit ARM and 16-bit and 32-bit Thumb instruction sets, including a range of *Single Instruction, Multiple Data* (SIMD) *Digital Signal Processing* (DSP) instructions that operate on 16-bit or 8-bit data values in 32-bit registers. The optional FPU implements the VFPv3-D16 architecture. This includes the VFPv3 instruction set. See ARM<sup>®</sup> Architecture Reference Manual, ARMv7-A and ARMv7-R edition.

### 1.2.2 Trace macrocell

The Cortex-R7 MPCore can include an optional *Embedded Trace Macrocell* (ETM). This ETM implements ETM architecture version 4. See *ARM*<sup>®</sup> *CoreSight*<sup>™</sup> *Embedded Trace Macrocell v4 Architecture Specification*.

#### 1.2.3 Advanced Microcontroller Bus Architecture

The Cortex-R7 MPCore processor complies with the AMBA 3 protocol. See *ARM*<sup>®</sup> *AMBA*<sup>®</sup> *AXI Protocol Specification* and *ARM*<sup>®</sup> *AMBA*<sup>®</sup> *3 APB Protocol Specification*.

#### 1.2.4 Debug architecture

The Cortex-R7 MPCore processor implements version 7.1 of the ARM Debug architecture that includes support for Security Extensions and CoreSight. See the  $ARM^{\circledast}$  CoreSight<sup>TM</sup> Architecture Specification.

#### 1.2.5 Generic Interrupt Controller architecture

The Cortex-R7 MPCore processor implements the ARM *Generic Interrupt Controller* (GIC) v1.0 architecture. See the *ARM*<sup>®</sup> *Generic Interrupt Controller Architecture Specification*.

## 1.3 Features

The Cortex-R7 MPCore processor includes the following features:

- One or two processors, with the following features:

- Superscalar, variable-length, out-of-order pipeline.

- Static and dynamic branch prediction. The dynamic branch prediction has *PREDictor* (PRED) RAM for the *Global History Buffer* (GHB), and an 8-entry return stack.

- Support for both low interrupt latency mode and normal interrupt latency mode.

- Non-maskable interrupt.

- Optional *Floating Point Unit* (FPU) in each processor. If you choose to instantiate the FPU, there are two possible designs, either an optimized FPU, which is single-precision and half-precision, or a full FPU, which is single-precision, half-precision, and double-precision.

- Each processor has a debug APB interface.

- Optional *Memory Reconstruction Port* (MRP) in each processor for memory reconstruction.

- A Performance Monitoring Unit (PMU) in each processor.

- A Harvard L1 memory system for each processor with:

- An ARMv7-R architecture *Memory Protection Unit* (MPU) with 12 or 16 regions, each region with a minimum resolution of 256 bytes.

- Optional data and instruction TCM, configurable from 0KB to 128KB.

- Optional AXI slave ports to access TCMs from external hardware.

- Optional instruction caches and data caches, with configurable sizes of 0KB, 4KB, 8KB, 16KB, 32KB, or 64KB.

- Optional ECC support on the RAM arrays and external buses.

- A *Snoop Control Unit* (SCU) that connects one or two processors to the memory system through the AXI3 interfaces.

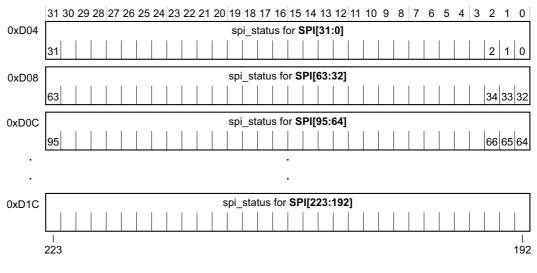

- An integrated *Generic Interrupt Controller* (GIC) supporting a configurable number of external IRQs, from 0 to 480 *Shared Peripheral Interrupts* (SPIs) in increments of 32. There are always 32 internal IRQ lines reserved for inter-processor interrupts, and timer interrupts.

- Integrated private timers, a watchdog timer, and a global timer.

- The ability to implement redundant processor logic, for example, in fault detection.

- High-speed Advanced Microprocessor Bus Architecture (AMBA) Advanced eXtensible Interfaces (AXI3):

- A single 64-bit master AXI3 interface.

- An optional 64-bit AXI slave Accelerator Coherency Port (ACP).

- An optional second AXI3 master interface with address filtering support.

- Memory-mapped 32-bit AXI3 peripheral port in each processor.

Optional ECC protection on data and parity on control bits.

- Optional ETM interface with full instruction and data trace, with either:

- One ETM, statically shared between the processors.

- Two ETMs, one dedicated to each processor.

## 1.4 Interfaces

The Cortex-R7 MPCore processor has the following interfaces for external access:

- *APB Debug interface.*

- *ETM/ATB interface.*

- *PMU interface*.

- *Test interface.*

#### 1.4.1 APB Debug interface

AMBA APBv3 is used for debugging purposes.

#### 1.4.2 ETM/ATB interface

You can implement the Cortex-R7 MPCore processor with an optional ETM. If the ETM is present, there is a dedicated ETM and *AMBA Trace Bus* (ATB) interface, see *ETM/ATB interface signals* on page A-37. The ETM provides instruction and data trace for the processor. For more information on the ETM itself, see the *ARM*<sup>®</sup> *CoreSight*<sup>™</sup> *ETM-R7 Technical Reference Manual*.

The ETM/ATB interface confirms to the AMBA ATB specification. The ETM/ATB interface includes the following signals:

- Instruction trace interface.

- Data trace interface.

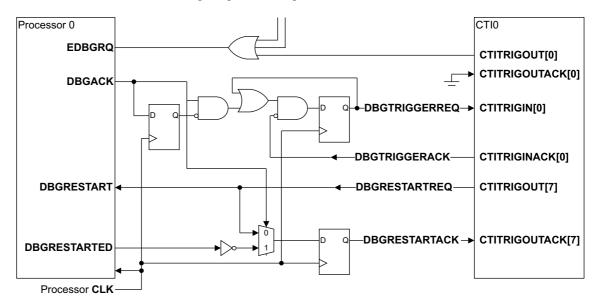

#### 1.4.3 CTM interface

The processor implements a single cross trigger channel interface. This external interface is connected to the CoreSight *Cross Trigger Interface* (CTI) corresponding to each processor through a simplified *Cross Trigger Matrix* (CTM).

#### 1.4.4 PMU interface

See Performance Monitoring Unit on page 10-3 for more information about the event bus.

#### 1.4.5 Test interface

The test interface provides support for test during manufacture of the Cortex-R7 MPCore processor using *Memory Built-In Self Test* (MBIST). For more information on the test interface, see *MBIST interface* on page A-32. See the *ARM*<sup>®</sup> *Cortex*<sup>®</sup>-*R7 MPCore Integration Manual* for information about the timings of these signals.

## 1.5 Configurable options

Table 1-1 shows the features of the Cortex-R7 MPCore processor that can be configured using either build or pin configurations. See *Product documentation and design flow* on page 1-10 for information about configuration of the processor. Many of these features, if included, can also be enabled and disabled during software configuration.

| Feature                                      | Range of options                                         | Sub-options                                        | Build or pin configuration          |

|----------------------------------------------|----------------------------------------------------------|----------------------------------------------------|-------------------------------------|

| Number of processors and optional redundancy | Single processor, no redundancy                          | One processor                                      | Build                               |

|                                              | Single processor, with redundancy                        | One processor built as lock-step                   | Build                               |

|                                              | Dual processor, no redundancy                            | Two processors                                     | Build                               |

|                                              | Dual processor, redundant processor                      | Two processors built as split/lock, lock-step mode | Build and lock-step<br>mode pin = 1 |

|                                              |                                                          | Two processors built as split/lock, normal mode    | Build and lock-step<br>mode pin = 0 |

| Instruction cache                            | No instruction cache <sup>a</sup>                        | -                                                  | Build                               |

|                                              | Instruction cache included                               | No ECC <sup>b</sup><br>64-bit ECC                  | Build                               |

|                                              |                                                          | 4KB, 8KB, 16KB, 32KB, or 64KB                      | Build                               |

| Data cache                                   | No data cache <sup>c</sup>                               | -                                                  | Build                               |

|                                              | Data cache included                                      | No ECC <sup>b</sup><br>32-bit ECC                  | Build                               |

|                                              |                                                          | 4KB, 8KB, 16KB, 32KB, or 64KB                      | Build                               |

| Instruction TCM                              | No Instruction TCM                                       | -                                                  | Build                               |

|                                              | Instruction TCM included                                 | No ECC <sup>b</sup><br>64-bit ECC                  | Build                               |

|                                              |                                                          | 4KB, 8KB, 16KB, 32KB, 64KB, or 128KB               | Build                               |

| Data TCM                                     | No Data TCM                                              | -                                                  | Build                               |

|                                              | Data TCM included                                        | No ECC <sup>b</sup><br>32-bit ECC                  | Build                               |

|                                              |                                                          | 4KB, 8KB, 16KB, 32KB, 64KB, or 128KB               | Build                               |

| Branch Target Address<br>Cache (BTAC) size   | 256, 512, 1024, 2048, or<br>4096 entries, default is 512 | _b                                                 | Build                               |

| PREDictor (PRED) RAM size                    | 1024, 2048, or 4096 entries, default is 4096             | _b                                                 | Build                               |

#### Table 1-1 Configurable options

#### Table 1-1 Configurable options (continued)

| Feature                             | Range of options     | Sub-options                     | Build or pin configuration |  |  |

|-------------------------------------|----------------------|---------------------------------|----------------------------|--|--|

| FPU                                 | Not included         | -                               | Build                      |  |  |

|                                     | FPU included         | Single-precision implementation | Build                      |  |  |

|                                     |                      | Double-precision implementation | Build                      |  |  |

| MPU                                 | Number of regions    | 12 region option                | Build                      |  |  |

|                                     |                      | 16 region option                | Build                      |  |  |

| AXI master ports                    | 1 or 2               | 1                               | Build                      |  |  |

|                                     |                      | 2, with address filtering       | Build and pin              |  |  |

| ETM                                 | Included or not      | -                               | Build                      |  |  |

| Memory Reconstruction<br>Port (MRP) | Included or not      | -                               | Build                      |  |  |

| Support for ECC                     | Used or not          | -                               | Build                      |  |  |

| Number of interrupts                | 0-480 in range of 32 | -                               | Build                      |  |  |

a. If you select no instruction cache, you must also select no data cache.

b. The ECC parameter is global for the instruction and data cache RAMs, and ITCM and DTCM.

BTAC and PRED RAM are protected by parity, initiated using the same ECC parameter.

c. If you select no data cache, you must also select no instruction cache.

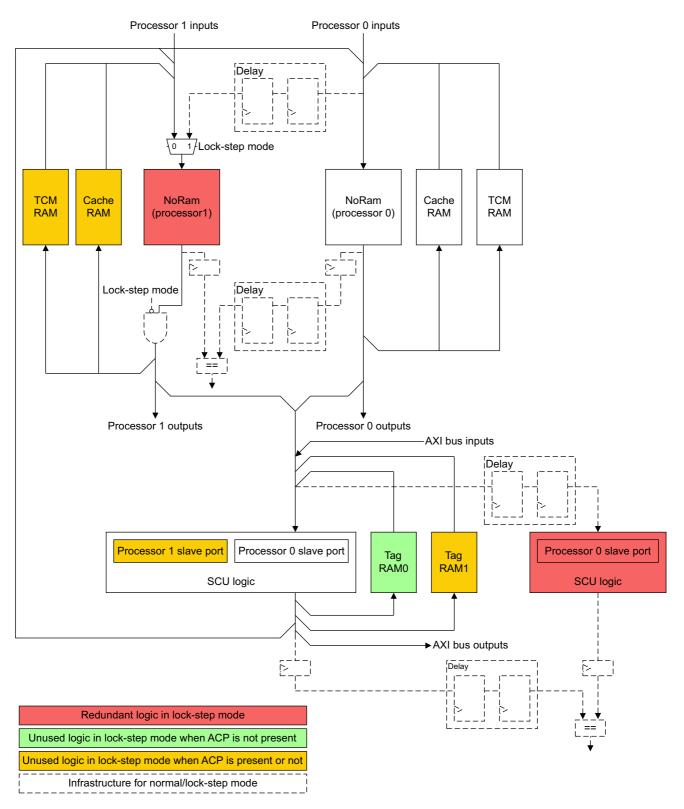

## 1.6 Redundant processor comparison

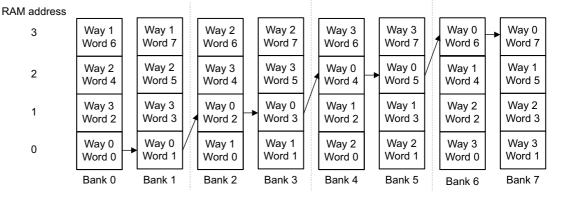

You can implement the Cortex-R7 MPCore processor with a second, redundant copy of most of the logic. The redundant logic includes a second processor that shares the input pins and the cache and TCM of the master processor, so only one set of cache and TCM is required. The redundant logic includes the individual processor logic, but not the ETM logic if the ETM is present. The redundant logic operates in lock-step with the processor, but does not directly affect the processor behavior in any way. The master processor drives the output pins and the RAMs. The redundant logic also includes a copy of

- SCU logic. The SCU Tag RAM is not duplicated.

- AXI TCM slave, if TCM is present.

Comparison logic can be included at build time. This logic compares the outputs of the processor, SCU, and AXI TCM slave with those of their redundant copy. These comparators are enabled through the **COMPENABLE** input signal. If a fault occurs in either the main or redundant logic because of radiation or circuit failure, the comparison logic detects it and the output signal **COMPFAULT** is asserted. Used in conjunction with the RAM error detection schemes, this can help protect the system from faults. **COMPENABLE** can be asserted only after a initialization phase, see the *ARM*<sup>®</sup> *Cortex*<sup>®</sup>-*R7 MPCore Configuration and Sign-Off Guide*. See the *ARM*<sup>®</sup> *Cortex*<sup>®</sup>-*R7 MPCore Integration Manual* for more information about **COMPENABLE** and **COMPFAULT** or contact your system integrator.

ARM provides example comparison logic, but you can change this during implementation. If you are implementing a dual-redundant configuration, contact ARM for more information.

### 1.6.1 Split/lock

If two Cortex-R7 processors are included and the Split/lock infrastructure implemented, the processor group can operate in one of two modes:

Split mode Operates as a multiprocessor configuration, with both processors capable of doing multiprocessing, by maintaining L1 data cache coherency. Each processor uses its dedicated cache RAM. Also known as performance mode.

Locked mode Operates in lock-step mode. The second processor works as redundant logic for the individual processor logic, and the SCU logic, but not the ETM logic if the ETM is present. The processor 1 side cache RAM

You can select the usage mode with the **SAFEMODE** input signal. This input can be changed only while the processor group is held in reset and must remain stable when out of reset.

For more information about how to make a change in processor mode, contact your system integrator.

If you are implementing a Split/lock configuration, contact ARM for more information.

remains implemented but not used.

## 1.7 Test features

The Cortex-R7 MPCore processor is delivered as fully-synthesizable RTL and is a fully-static design. Scan-chains and test wrappers for production test can be inserted into the design by the synthesis tools during implementation.

Production test of the processor cache and TCM RAMs can be done through the dedicated, pipelined MBIST interface. This interface shares some of the multiplexing present in the processor design, to improve the potential frequency compared to adding multiplexers to the RAM modules.

The TCM RAMs can be read and written directly by the program running on the processor. You can also use the dedicated AXI3 slave interface to access the TCMs. See *Accessing RAMs using the AXI3 interface* on page 11-9 for more information about how to access the RAMs using the AXI3 slave interface.

## 1.8 Product documentation and design flow

This section describes the Cortex-R7 MPCore processor books and how they relate to the design flow.

See *Additional reading* on page x for more information about the books described in this section.

#### 1.8.1 Documentation

The Cortex-R7 documentation is as follows:

#### **Technical Reference Manual**

The *Technical Reference Manual* (TRM) describes the functionality and the effects of functional options on the behavior of the Cortex-R7 MPCore processor. It is required at all stages of the design flow. The choices made in the design flow can mean that some behavior described in the TRM is not relevant. If you are programming the Cortex-R7 MPCore processor then contact:

- The implementer to determine:

- The build configuration of the implementation.

- What integration, if any, was performed before implementing the Cortex-R7 MPCore processor.

- The integrator to determine the pin configuration of the Cortex-R7 MPCore processor that you are using.

— Note —

If the ETM is included, see the  $ARM^{\otimes}$  CoreSight<sup>TM</sup> ETM-R7 Technical Reference Manual for more information.

#### **Configuration and Sign-off Guide**

The Configuration and Sign-off Guide (CSG) describes:

- The available build configuration options and related issues in selecting them.

- How to configure the *Register Transfer Level* (RTL) description with the build configuration options.

- The processes to sign off the configured design.

The ARM product deliverables include reference scripts and information about using them to implement your design. Reference methodology flows supplied by ARM are example reference implementations. Contact your EDA vendor for EDA tool support.

The CSG is a confidential book that is only available to licensees.

#### **Integration Manual**

The *Integration Manual* (IM) describes how to integrate the Cortex-R7 MPCore processor into a SoC. It includes describing the pins that the integrator must tie off to configure the macrocell for the required integration. Some of the integration is affected by the configuration options used when implementing the Cortex-R7 MPCore processor.

The IM is a confidential book that is only available to licensees.

#### 1.8.2 Design flow

The Cortex-R7 MPCore processor is delivered as synthesizable RTL. Before it can be used in a product, it must go through the following process:

#### Implementation

The implementer configures and synthesizes the RTL to produce a hard macrocell. This might include integrating RAMs into the design.

**Integration** The integrator connects the implemented design into a SoC. This includes connecting it to a memory system and peripherals.

#### Programming

This is the last process. The system programmer develops the software required to configure and initialize the processor, and tests the required application software.

#### Each process:

- Can be performed by a different party.

- Can include implementation and integration choices that affect the behavior and features of the Cortex-R7 MPCore processor.

The operation of the final device depends on:

#### **Build configuration**

The implementer chooses the options that affect how the RTL source files are pre-processed. These options usually include or exclude logic that affects one or more of the area, maximum frequency, and features of the resulting macrocell.

#### **Configuration inputs**

The integrator configures some features of the processor by tying inputs to specific values. These configurations affect the start-up behavior before any software configuration is made. They can also limit the options available to the software.

#### Software configuration

The programmer configures the processor by programming particular values into registers. This affects the behavior of the processor.

#### — Note ——

This manual refers to implementation-defined features that are applicable to build configuration options. Reference to a feature that is included means that the appropriate build and pin configuration options are selected. Reference to an enabled feature means one that has also been configured by software.

## 1.9 Product revisions

This section describes the differences in functionality between product revisions:

r0p0 First release.

- **r0p0-r0p1** The following changes have been made in this release:

- ID register values changed to reflect product revision status: Main ID Register 0x410FC171.

- Various engineering errata fixes.

## Chapter 2 Functional Description

This chapter describes the functionality of the Cortex-R7 MPCore processor. It contains the following sections:

- *About the functions* on page 2-2.

- *Interfaces* on page 2-4.

- *Clocking, resets, and initialization* on page 2-5.

- *Power management* on page 2-13.

- *Processor ports* on page 2-19.

## 2.1 About the functions

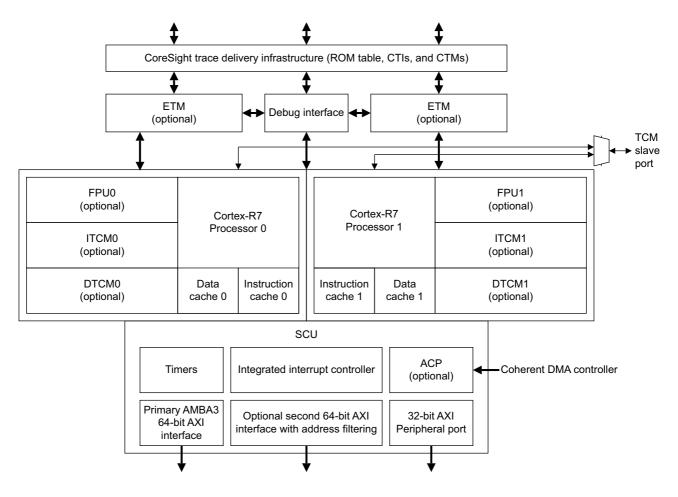

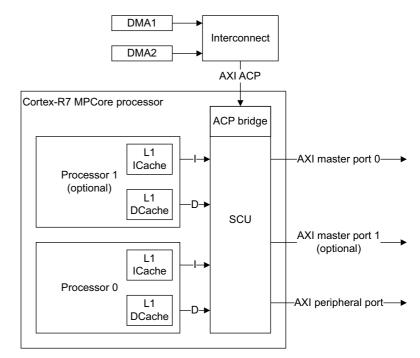

The Cortex-R7 MPCore processor is a highly configurable processor for use in deeply-embedded systems. Figure 2-1 shows a Cortex-R7 MPCore processor design with two processors.

#### Figure 2-1 Cortex-R7 MPCore processor block diagram with two processors

#### 2.1.1 Components of the Cortex-R7 MPCore processor

The main components of the Cortex-R7 MPCore processor are:

- *L1 memory system.*

- Snoop Control Unit on page 2-3.

- *Interrupt controller* on page 2-3.

- *Timers* on page 2-3.

- *Debug and Trace* on page 2-3.

- *Split/lock* on page 2-3.

#### L1 memory system

The L1 memory system has:

- 64-bit data paths throughout the memory system.

- Export of memory attributes for external memory systems.

- Separate optional instruction and data caches each with a fixed line length of 32 bytes.

#### **Snoop Control Unit**

The SCU connects the Cortex-R7 processors to the memory system and peripherals through the AXI3 interfaces. The SCU has an optional AXI3 64-bit slave port, the *Accelerator Coherency Port* (ACP). See *Accelerator Coherency Port* on page 2-23.

See About multiprocessing and the SCU on page 9-2 for more information.

— Note ——

The SCU supports L1 data cache coherency, but does not support hardware management of coherency of the instruction caches.

#### Interrupt controller

The interrupt controller provides support for handling multiple interrupt sources. See *Interrupt controller* on page 9-19 for more information.

#### Timers

The Timers provide the ability to schedule events and trigger interrupts. See *Private timer and watchdog* on page 9-29 and *Global timer* on page 9-35 for more information.

#### **Debug and Trace**

The debug and trace logic includes:

- Support for ARMv7 Debug architecture with an APB slave interface for access to the debug registers.

- Performance Monitor Unit (PMU) based on the PMUv1 architecture.

- *Embedded Trace Macrocell* (ETM) based on the ETMv4 architecture and dedicated ATB interfaces per processor.

- Cross Trigger Interface (CTI) and Cross Trigger Matrix (CTM) for multi-processor debugging.

See the following for more information:

- *Performance Monitoring Unit* on page 10-3.

- *Embedded Trace Macrocell* on page 10-11.

- *Debug* on page 10-12.

#### Split/lock

The Cortex-R7 MPCore processor can be configured so that it can be switched, under reset, between a twin-processor performance mode and a dual-redundant lock-step. This feature imposes extra constraints on the software usage model. ARM provides an init code sequence to guarantee the processor and the redundant processor leave reset in exactly the same state. See *Static split/lock* on page 7-16 for more information.

## 2.2 Interfaces

The Cortex-R7 MPCore processor has the following external interfaces:

- *AXI3 interface.*

- Debug and PMU APB interface.

- *ATB interface*.

- *DFT interface*.

- *MBIST controller interface.*

#### 2.2.1 AXI3 interface

The Cortex-R7 MPCore processor implements the AMBA 3.0 AXI with:

- A primary master port interface.

- An optional secondary master port interface, depending on the build configuration.

- A peripheral master port interface.

- A ACP slave port, depending on the build configuration.

- A TCM slave port, depending on the build configuration.

See Processor ports on page 2-19.

#### 2.2.2 Debug and PMU APB interface

The Cortex-R7 MPCore processor implements an APB slave interface that enables access to the following:

- Debug and PMU registers.

- CoreSight components (local ROM table, CTIs, and CTMs).

- ETM.

See the *ARM*<sup>®</sup> *CoreSight*<sup>™</sup> *Architecture Specification* for more information.

#### 2.2.3 ATB interface

The Cortex-R7 MPCore processor implements two dedicated ATB interfaces for each processor that output trace information for debugging. The ATB interfaces are compatible with the CoreSight architecture. See the *ARM*<sup>®</sup> *CoreSight*<sup>®</sup> *ETM Architecture Specification v4* for more information. See also *ETM/ATB interface signals* on page A-37.

#### 2.2.4 DFT interface

The Cortex-R7 MPCore processor implements a *Design For Test* (DFT) interface that enables an industry standard *Automatic Test Pattern Generation* (ATPG) tool to test logic outside of the embedded memories.

#### 2.2.5 MBIST controller interface

The MBIST controller interface provides support for manufacturing testing of the memories embedded in the Cortex-R7 MPCore processor. MBIST is the industry standard method of testing embedded memories. MBIST works by performing sequences of reads and writes to the memory based on test algorithms. See *MBIST interface* on page A-32 for information on this interface.

## 2.3 Clocking, resets, and initialization

The following sections describe clocking, resets, and initialization:

- Clocking.

- *Resets*.

- Initialization on page 2-9.

#### 2.3.1 Clocking

This section describes the following Cortex-R7 MPCore processor clocks:

- CLK.

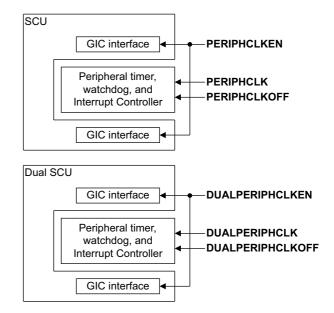

- PERIPHCLK.

- PERIPHCLKEN.

#### CLK

This is the main clock of the Cortex-R7 MPCore processor. All the processors in the device and the SCU are clocked with a distributed version of **CLK**. It is also the main clock for the ETMs and the local CoreSight infrastructure.

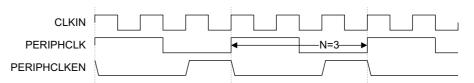

#### PERIPHCLK

The interrupt controller, global timer, private timers, and watchdog are clocked with **PERIPHCLK**. **PERIPHCLK** must be synchronous with **CLK**, and the **PERIPHCLK** clock period, N, must be configured as a multiple of the **CLK** clock period. This multiple N must be equal to, or greater than two.

#### PERIPHCLKEN

This is the clock enable signal for the interrupt controller and timers. The **PERIPHCLKEN** signal is generated at **CLK** clock speed. **PERIPHCLKEN** HIGH on a **CLK** rising edge indicates that there is a corresponding **PERIPHCLK** rising edge.

Figure 2-2 shows an example of clocking the peripherals using these enable signals at a 3:1 ratio.

#### Figure 2-2 Clocking example on MPCore peripherals

#### DUALPERIPHCLK and DUALPERIPHCLKEN

This clock and clock enable signal are present if lock-step or split/lock is implemented. See *Clock and control signals* on page A-3 for more information on how these signals are used.

### 2.3.2 Resets

The Cortex-R7 MPCore processor has the following reset signals, where N is 1 or 2:

- CPUCLKOFF[N-1:0].

- nCPURESET[N-1:0].

- nDBGRESET[N-1:0].

- DBGCLKOFF[N-1:0].

- nPERIPHRESET.

- nSCURESET.

- nCPUHALT[N-1:0].

- nWDRESET[N-1:0].

- WDRESETREQ[N-1:0].

The following reset signals are present for CoreSight debug logic:

- nCTRESET.

- CTCLKOFF.

The following reset signals are present if ETM0 is present:

- nETMORESET.

- ETM0CLKOFF.

The following reset signals are present if ETM1 is present:

- nETM1RESET.

- ETM1CLKOFF.

The following additional reset signals are present if lock-step or split/lock is implemented:

- SCUCLKOFF.

- PERIPHCLKOFF.

- DUALPERIPHCLKOFF.

The reset signals in the Cortex-R7 MPCore processor design enable you to reset different parts of the design independently. Table 2-1 shows the supported reset combinations in a Cortex-R7 system. [n] refers to the processor that receives a reset.

| Reset signals                 | Cortex-R7 | Cortex-R7 MPCore |                | Individual processors |                 | Individual processors |               |

|-------------------------------|-----------|------------------|----------------|-----------------------|-----------------|-----------------------|---------------|

|                               | Powerup   | Software         | Powerup        | Software              | MPCore<br>debug | Debug                 | Watchdog flag |

| nSCURESET and<br>nPERIPHRESET | 0         | 0                | 1              | 1                     | 1               | 1                     | 1             |

| nCPURESET[1:0]                | All 0     | All 0            | [n]=0          | [n]=0                 | All 1           | All 1                 | All 1         |

| nDBGRESET[1:0]                | All 0     | All 1            | [n]=0          | All 1                 | All 0           | [n]=0                 | All 1         |

| nWDRESET[1:0]                 | All 0     | All 0            | [n]=0 or all 1 | [n]=0 or all 1        | All 1           | All 1                 | [n]=0         |

#### Table 2-1 Reset combinations in a Cortex-R7 system

See Clock and control signals on page A-3 and Reset signals on page A-5.

The following sections describe the reset sequences:

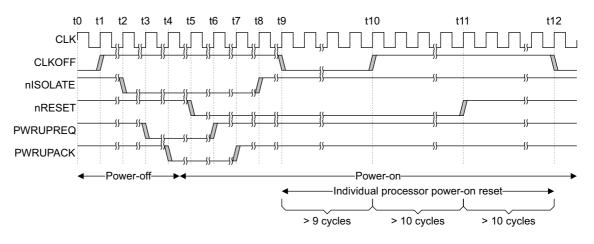

- *Cortex-R7 MPCore powerup reset* on page 2-7.

- Individual processor powerup reset on page 2-8.

- *Individual processor software reset* on page 2-8.

- Cortex-R7 MPCore debug reset on page 2-9.

- *Individual processor debug reset* on page 2-9.

- Individual processor watchdog flag reset on page 2-9.

#### Cortex-R7 MPCore powerup reset

You must apply powerup or cold reset to the Cortex-R7 MPCore processor when power is first applied to the system. In the case of powerup reset, the leading edge, that is the falling edge, of the reset signals do not have to be synchronous to **CLK**, but the rising edge must be. You must assert the reset signals for at least 10 **CLK** cycles to ensure correct reset behavior.

#### You must generate DUALPERIPHCLK, DUALPERIPHCLKEN, and

**DUALPERIPHCLKOFF** as delayed versions of the equivalent primary core signals. Use the same delay as between the primary core and the redundant core.

ARM recommends the following reset sequence:

#### 1. Apply nCPURESET, nDBGRESET, nWDRESET, nSCURESET, nPERIPHRESET, nCTRESET, nETMORESET if ETM0 is present, and nETM1RESET if ETM1 is present.

- 2. Wait for at least 10 CLK cycles, or more if required by other components. There is no harm in applying more clock cycles than this, and maximum redundancy can be achieved by, for example, applying 15 cycles on every clock domain.

- 3. Stop the **CLK** clock input to the Cortex-R7 MPCore processor. You can use an integrated clock gating cell driven by a reset controller to stop the **CLK**.

- 4. Wait for the equivalent of approximately 10 cycles, depending on your implementation. This compensates for clock and reset tree latencies.

- 5. Release all resets.

- 6. Wait for the equivalent of approximately 10 cycles to compensate for clock and reset tree latencies.

- 7. Restart the CLK clock input.

For a lock-step or split/lock implementation, use the following reset sequence:

- 1. Apply nCPURESET, nDBGRESET, nWDRESET, nSCURESET, nPERIPHRESET, nCTRESET, nETMORESET if ETM0 is present, and nETM1RESET if ETM1 is present.

- 2. Wait for at least 10 CLK cycles, or more if required by other components. There is no harm in applying more clock cycles than this, and maximum redundancy can be achieved by, for example, applying 10 cycles on every clock domain.

- 3. Drive DUALPERIPHCLKOFF, SCUCLKOFF, and PERIPHCLKOFF HIGH.

- 4. Stop the **CLK** clock input to the Cortex-R7 MPCore processor.

- 5. Wait for the equivalent of approximately 10 cycles, depending on your implementation. This compensates for clock and reset tree latencies.

- 6. Release all resets.

- 7. Wait for the equivalent of approximately 10 cycles, to compensate for clock and reset tree latencies.

- 8. Restart the CLK clock and maintain DUALPERIPHCLKOFF HIGH.

**SCUCLKOFF** and **PERIPHCLKOFF** are driven LOW. If you want to, you can maintain these two signals HIGH a few more clock cycles but this is not required.

9. After P\* CLK cycles, after PERIPHCLKOFF is driven low, drive **DUALPERIPHCLKOFF** LOW.

— Note —

P\* is defined by the number of delay cycles introduced between the main processor and the dual-redundant processor. It is configurable and implementation defined. The default value used in the Cortex-R7 MPCore processor is 2.

#### Individual processor powerup reset

This reset is for the processor 0 or processor 1 level. It initializes the whole logic in a single processor, including its debug logic. It is expected to be applied when this individual processor exits from powerdown or dormant state. This reset only applies to configurations where each individual processor is implemented in its own power domain.

The reset sequence is as follows:

- 1. Apply **nCPURESET[n]** and **nDBGRESET[n]**. You can apply the **nWDRESET[n]** reset if you want to reset the corresponding watchdog flag.

- 2. Wait for at least 10 CLK cycles, or more if required by other components. There is no harm in applying more clock cycles than this.

- 3. Assert CPUCLKOFF[n] and DBGCLKOFF[n] with a value of 1'b1.

- 4. Wait for the equivalent of approximately 10 cycles, depending on your implementation. This compensates for clock and reset tree latencies.

- 5. Release all resets.

- 6. Wait for the equivalent of approximately 10 cycles, to compensate for clock and reset tree latencies.

- 7. Deassert **CPUCLKOFF**[**n**] and **DBGCLKOFF**[**n**]. This ensures that all registers in the processor see the same **CLK** edge on exit from the reset sequence.

The individual processor powerup reset can be extended to enable its corresponding ETM to be powered down. To wake up from powerdown or dormant mode with ETM, use the **nETM[n]RESET** and **ETM[n]CLKOFF** signals in the same way as **nCPURESET[n]** and **CPUCLKOFF[n]**.

—— Note ———

When resetting a processor from a powerdown state while the ETM is not reset, ARM recommends that you disable the ETM using the APB port before resetting the processor. This avoids the risk of tracing bad data at the point when the processor is reset.

#### Individual processor software reset

This reset is for the processor 0 or processor 1 level, without debug logic. It initializes all functional logic in a single individual processor apart from its debug logic. All breakpoints and watchpoints are retained during this individual warm reset. This reset only applies to configuration where each individual processor is implemented in its own power domain.

ARM recommends that you use the reset sequence described in *Individual processor powerup reset*, except that **nDBGRESET**, **nCTIRESET**, and **nETMxRESET** must not be asserted during the sequence. This ensures that the debug registers of the individual processors retain their values.

#### Cortex-R7 MPCore debug reset

This reset initializes the debug logic in all processors present in the cluster. To perform a Cortex-R7 MPCore debug reset, assert all **nDBGRESET** signals for a number of **CLK** cycles. **CPUCLKOFF**, and **ETM[0/1]CLKOFF** if the ETM is present, must remain deasserted during this reset sequence.

#### Individual processor debug reset

This reset initializes the debug logic in an individual processor in the cluster. To perform an individual processor debug reset, assert the corresponding **nDBGRESET[n]** signal for a number of **CLK** cycles. **CPUCLKOFF**, and **ETM[n]CLKOFF** if the ETM is present, must remain deasserted during this reset sequence.

— Note —

When lock-step or split/lock is implemented, the software must clear the INTdis bit of the *Debug Status and Control Register* (DBGDSCR) before applying a debug reset. This is because if a pending interrupt is masked by the INTdis bit and a debug reset occurs, this bit is cleared by the reset and the interrupt is taken immediately by both processors on the same clock cycle.

#### Individual processor watchdog flag reset

This reset clears the watchdog flag associated with a single individual processor. Watchdog functionality is independent of all other processor functionality, so this reset is independent of the all other resets.

— Note —

When a watchdog reset request occurs and when lock-step or split/lock is implemented, the reset must not be applied immediately to the entire Cortex-R7 MPCore processor. This is because after reset the sticky flag is set in one processor, but not the other and this leads to the assertion of **COMPFAULT**. Therefore, if one processor has its watchdog flag set, the other processor must reach the same state, that is, also having its watchdog flag set. This can be controlled using the **PERIPHCLKOFF** and **DUALPERIPHCLKOFF** signals.

#### 2.3.3 Initialization

Most of the architectural registers in the Cortex-R7 MPCore processor, such as r0-r14, and s0-s31 and d0-d15 when floating-point is included, have an unknown value after reset. Because of this, you must initialize these for all modes before they are used, using an immediate-MOV instruction, or a PC-relative load instruction. The *Current Program Status Register* (CPSR) is given a known value on reset. This is described in the *ARM*<sup>®</sup> *Architecture Reference Manual ARMv7-A and ARMv7-R edition*. The reset values for the CP15 registers are described along with the registers in Chapter 4 *System Control*.

In addition, before you run an application, you might want to:

- Program particular values into various registers, for example, stack pointers.

- Enable various features, for example, error correction.

- Program particular values into memory, for example, the TCMs.

The following sections describe other initialization requirements:

- *MPU* on page 2-10.

- *FPU* on page 2-10.

- *Caches* on page 2-10.

TCM.

#### MPU

Before you can use MPU you must:

- Program and enable at least one of the regions.

- Enable the MPU in the SCTLR. See *System Control Register* on page 4-23.

Do not enable the MPU unless at least one MPU region is programmed and active. If the MPU is enabled, before using the TCM interfaces you must program MPU regions to cover the TCM regions to give access permissions to them.

#### FPU

If the Cortex-R7 MPCore processor has been built with an FPU, you must enable it before *Vector Floating Point* (VFP) instructions can be executed. Enable the FPU as follows:

- Enable access to the FPU in the coprocessor access control register. See *Coprocessor Access Control Register* on page 4-27

- Enable the FPU by setting the EN-bit in the FPEXC register, see *Floating-Point Exception Register* on page 5-10.

#### Caches

If the Cortex-R7 MPCore processor has been built with instruction or data caches, they must be invalidated before they are enabled, otherwise UNPREDICTABLE behavior can occur. See *About the caches* on page 6-8.

An invalidate all operation never reports any ECC errors. See *Auxiliary Control Register* on page 4-25.

#### ТСМ

The Cortex-R7 MPCore processor does not initialize the TCM RAMs, so you must initialize all the TCMs. In addition, you might want to preload instructions or data into the TCM for the main application to use. This section describes various ways that you can perform data preloading. You can also configure the Cortex-R7 MPCore processor to use the TCMs from reset. See *Instruction and data TCM* on page 8-15, *DTCM Region Register* on page 4-33 and *ITCM Region Register* on page 4-34.

#### Preloading TCMs

You can write data to the TCMs using either store instructions or the AXI3 slave interface. Depending on the method you choose, you might require:

- Particular hardware on the SoC that you are using.

- Boot code.

- A debugger connected to the processor.

Methods to preload TCMs include:

#### Memory copy with running boot code

The boot code includes a memory copy routine that reads data from a ROM, and writes it into the appropriate TCM. You must enable the TCM to do this, and it might be necessary to give the TCM one base address while the copy is occurring, and a different base address when the application is being run.

#### Copy data from the debug communications channel

The boot code includes a routine to read data from the *Debug Communications Channel* (DCC) and write it into the TCM. The debug host feeds the data for this operation into the DCC by writing to the appropriate registers on the processor APB debug port.

#### Execute code in debug halt state

The debug host puts the Cortex-R7 MPCore processor into debug halt state and then feeds instructions into it through the *Instruction Transfer Register* (DBGITR). The Cortex-R7 MPCore processor executes these instructions, that replace the boot code in either of the two methods previously described.

#### **DMA into TCM**

The SoC includes a *Direct Memory Access* (DMA) device that reads data from a ROM, and writes it to the TCMs through their AXI slave interfaces.

#### Preloading TCMs with ECC

The error code bits in the TCM RAM, if configured with an error scheme, are not initialized by the Cortex-R7 MPCore processor. Before a RAM location is read with ECC enabled, the error code bits must be initialized. To calculate the error code bits correctly, the logic must have all the data in the data chunk that those bits protect. Therefore, when the TCM is being initialized, the writes must be of the same width and aligned to the data chunk that the error scheme protects.

You can initialize the TCM RAM with error checking turned on or off, according to the following rules. See *Auxiliary Control Register* on page 4-25. You can use the **ITCMECCEN** signal to enable the ITCM when leaving reset.

If the slave port is used, for TCM memory accesses, the transactions must start at a 32-bit aligned address for data or 64-bit aligned address for instructions, and read or write a continuous block of memory, containing a multiple of 4 bytes for data or 8 bytes for instruction. All bytes in the block must be written, that is, have their byte lane strobe asserted.

If initialization is done by running code on the Cortex-R7 MPCore processor, this is best done by a loop of stores that write to the whole of the TCM memory as follows:

- If the scheme is 32-bit ECC, use *Store Word* (STR), *Store Two Words* (STRD), or *Store Multiple Words* (STM) instructions to 32-bit aligned addresses.

- If the scheme is 64-bit ECC, use STRD or STM, that has an even number of registers in the register list with a 64-bit aligned starting address.

You can use the alignment-checking features of the Cortex-R7 MPCore processor to help you ensure that memory accesses are 32-bit aligned, but there is no checking for 64-bit alignment. If you are using STRD or STM, an alignment fault is generated if the address is not 32-bit aligned. For the same behavior with STR instructions, enable strict-alignment-checking by setting the A-bit in the System Control Register. See *System Control Register* on page 4-23.

#### Using TCMs from reset

– Note –

You can pin-configure the Cortex-R7 MPCore processor to enable the TCM interfaces from reset and to select the address at which each TCM appears from reset. This enables you to configure the processor to boot from TCM but, to do this, the TCM must first be preloaded with the boot code. The **nCPUHALT** input can be asserted while the processor is in reset to prevent the processor from fetching and executing instructions after coming out of reset. While the

processor is halted in this way, the TCMs can be preloaded with the appropriate data. When the **nCPUHALT** input is deasserted, the processor starts fetching instructions from the reset vector address in the normal way.

\_\_\_\_\_Note \_\_\_\_\_

When **nCPUHALT** has been deasserted to start the processor fetching, it must not be asserted again except when the processor is under processor or powerup reset. See *Resets* on page 2-5.

## 2.4 Power management

The Cortex-R7 MPCore processor provides mechanisms and support to control both dynamic and static power dissipation. The following sections describe:

- Individual processor power management.

- *Power domains* on page 2-18.

#### 2.4.1 Individual processor power management

•

Placeholders for clamps are inserted around each processor to simplify implementation of different power domains. See the *ARM*<sup>®</sup> *Cortex*<sup>®</sup>-*R7 MPCore Configuration and Sign-off Guide* for implementation information about the different power domains and the signals that require specific clamp values. Software is responsible for signaling to the Snoop Control Unit and the interrupt controller that a processor is shut off so that the processor can be seen as non-existent in the cluster. Table 2-2 shows the power modes and the wake-up mechanisms for each mode: