## AMBA® CXS Protocol Specification

#### **AMBA CXS Protocol Specification**

Copyright © 2017, 2018 Arm Limited or its affiliates. All rights reserved.

#### **Release Information**

The following changes have been made to this specification.

Change history

| Date          | Issue | Confidentiality  | Change        |  |

|---------------|-------|------------------|---------------|--|

| 12 March 2018 | A     | Non-Confidential | First release |  |

|               |       |                  |               |  |

#### **Proprietary Notice**

This document is NON-CONFIDENTIAL and any use by you is subject to the terms of this notice and the Arm AMBA Specification Licence set about below.

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications.

Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or TM are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at <a href="http://www.arm.com/company/policies/trademarks">http://www.arm.com/company/policies/trademarks</a>.

Copyright © 2017, 2018 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

In this document, where the term Arm is used to refer to the company it means "Arm or any of its subsidiaries as appropriate"

#### ARM AMBA SPECIFICATION LICENCE

THIS END USER LICENCE AGREEMENT ("LICENCE") IS A LEGAL AGREEMENT BETWEEN YOU (EITHER ASINGLE INDIVIDUAL, OR SINGLE LEGAL ENTITY) AND ARM LIMITED ("ARM") FOR THE USE OF THE RELEVANT AMBA SPECIFICATION ACCOMPANYING THIS LICENCE. ARM IS ONLY WILLING TO LICENSE THE RELEVANT AMBA SPECIFICATION TO YOU ON CONDITION THAT YOU ACCEPT ALL OF THE TERMS IN THIS LICENCE. BY CLICKING "I AGREE" OR OTHERWISE USING OR COPYING THE RELEVANT AMBA SPECIFICATION YOU INDICATE THAT YOU AGREE TO BE BOUND BY ALL THE TERMS OF THIS LICENCE. IF YOU DO NOT AGREE TO THE TERMS OF THIS LICENCE, ARM IS UNWILLING TO LICENSE THE RELEVANT AMBA SPECIFICATION TO YOU AND YOU MAY NOT USE OR COPY THE RELEVANT AMBA SPECIFICATION AND YOU SHOULD PROMPTLY RETURN THE RELEVANT AMBA SPECIFICATION TO ARM.

"LICENSEE" means You and your Subsidiaries.

"Subsidiary" means, if You are a single entity, any company the majority of whose voting shares is now or hereafter owned or controlled, directly or indirectly, by You. A company shall be a Subsidiary only for the period during which such control exists.

1. Subject to the provisions of Clauses 2, 3 and 4, Arm hereby grants to LICENSEE a perpetual, non-exclusive, non-transferable, royalty free, worldwide licence to:

(i) use and copy the relevant AMBA Specification for the purpose of developing and having developed products that comply with the relevant AMBA Specification;

- (ii) manufacture and have manufactured products which either: (a) have been created by or for LICENSEE under the licence granted in Clause 1(i); or (b) incorporate a product(s) which has been created by a third party(s) under a licence granted by Arm in Clause 1(i) of such third party's Arm AMBA Specification Licence; and

- (iii) offer to sell, sell, supply or otherwise distribute products which have either been (a) created by or for LICENSEE under the licence granted in Clause 1(i); or (b) manufactured by or for LICENSEE under the licence granted in Clause 1(ii).

- 2. LICENSEE hereby agrees that the licence granted in Clause 1 is subject to the following restrictions:

- (i) where a product created under Clause 1(i) is an integrated circuit which includes a CPU then either: (a) such CPU shall only be manufactured under licence from Arm; or (b) such CPU is neither substantially compliant with nor marketed as being compliant with the Arm instruction sets licensed by Arm from time to time;

- (ii) the licences granted in Clause 1(iii) shall not extend to any portion or function of a product that is not itself compliant with part of the relevant AMBA Specification; and

- (iii) no right is granted to LICENSEE to sublicense the rights granted to LICENSEE under this Agreement.

- 3. Except as specifically licensed in accordance with Clause 1, LICENSEE acquires no right, title or interest in any Arm technology or any intellectual property embodied therein. In no event shall the licences granted in accordance with Clause 1 be construed as granting LICENSEE, expressly or by implication, estoppel or otherwise, a licence to use any Arm technology except the relevant AMBA Specification.

- 4. THE RELEVANT AMBA SPECIFICATION IS PROVIDED "AS IS" WITH NO REPRESENTATION OR WARRANTIES EXPRESS, IMPLIED OR STATUTORY, INCLUDING BUT NOT LIMITED TO ANY WARRANTY OF SATISFACTORY QUALITY, MERCHANTABILITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE, OR THAT ANY USE OR IMPLEMENTATION OF SUCH ARM TECHNOLOGY WILL NOT INFRINGE ANY THIRD PARTY PATENTS, COPYRIGHTS, TRADE SECRETS OR OTHER INTELLECTUAL PROPERTY RIGHTS.

- 5. NOTWITHSTANDING ANYTHING TO THE CONTRARY CONTAINED IN THIS AGREEMENT, TO THE FULLEST EXTENT PETMITTED BY LAW, THE MAXIMUM LIABILITY OF ARM IN AGGREGATE FOR ALL CLAIMS MADE AGAINST ARM, IN CONTRACT, TORT OR OTHERWISE, IN CONNECTION WITH THE SUBJECT MATTER OF THIS AGREEMENT (INCLUDING WITHOUT LIMITATION (I) LICENSEE'S USE OF THE ARM TECHNOLOGY; AND (II) THE IMPLEMENTATION OF THE ARM TECHNOLOGY IN ANY PRODUCT CREATED BY LICENSEE UNDER THIS AGREEMENT) SHALL NOT EXCEED THE FEES PAID (IF ANY) BY LICENSEE TO ARM UNDER THIS AGREEMENT. THE EXISTENCE OF MORE THAN ONE CLAIM OR SUIT WILL NOT ENLARGE OR EXTEND THE LIMIT. LICENSEE RELEASES ARM FROM ALL OBLIGATIONS, LIABILITY, CLAIMS OR DEMANDS IN EXCESS OF THIS LIMITATION.

- 6. No licence, express, implied or otherwise, is granted to LICENSEE, under the provisions of Clause 1, to use the Arm tradename, or AMBA trademark in connection with the relevant AMBA Specification or any products based thereon. Nothing in Clause 1 shall be construed as authority for LICENSEE to make any representations on behalf of Arm in respect of the relevant AMBA Specification.

- 7. This Licence shall remain in force until terminated by you or by Arm. Without prejudice to any of its other rights if LICENSEE is in breach of any of the terms and conditions of this Licence then Arm may terminate this Licence immediately upon giving written notice to You. You may terminate this Licence at any time. Upon expiry or termination of this Licence by You or by Arm LICENSEE shall stop using the relevant AMBA Specification and destroy all copies of the relevant AMBA Specification in your possession together with all documentation and related materials. Upon expiry or termination of this Licence, the provisions of clauses 6 and 7 shall survive.

- 8. The validity, construction and performance of this Agreement shall be governed by English Law.

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

## Contents

## **AMBA CXS Protocol Specification**

| Preface                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| About this document                                | vi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Introduction                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.1 About the CXS streaming interface protocol     | 1-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CXS operation                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                    | 2-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Signal descriptions                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.1 Mandatory and optional CXS signals             | 3-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.2 CXS interface checking signals                 | 3-2 <sup>-</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CXS packets                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4.1 Packet position constraints                    | 4-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.2 Packet control signal                          | 4-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.3 Packet size constraints                        | 4-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.4 Packet examples                                | 4-30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CXS interface activation and deactivation          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5.1 Interface control with explicit credit return  | 5-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.2 Request and acknowledgement handshaking        | 5-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.3 Response to a new state                        | 5-30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5.6 Interface activation and deactivation examples | 5-39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                    | Introduction  1.1 About the CXS streaming interface protocol 1.2 Use case  CXS operation 2.1 Protocol operation 2.2 CXS interface properties  Signal descriptions 3.1 Mandatory and optional CXS signals 3.2 CXS interface checking signals  CXS packets 4.1 Packet position constraints 4.2 Packet control signal 4.3 Packet size constraints 4.4 Packet examples  CXS interface activation and deactivation 5.1 Interface control with explicit credit return 5.2 Request and acknowledgement handshaking 5.3 Response to a new state |

| Chapter 6  | CXS packet continuous delivery guarantees |     |

|------------|-------------------------------------------|-----|

| •          | 6.1 Continuous delivery guarantees        | -42 |

| Appendix A | Revisions                                 |     |

## **Preface**

This specification describes the CXS streaming interface protocol. The protocol can be used for any point-to-point packetized communication, but is optimized for the transport of CCIX packets.

This chapter contains the following sections:

- About this document on page viii

- Intended audience on page viii.

- Typographic conventions on page viii.

- Additional reading on page viii.

- Feedback on this specification on page viii.

#### About this document

#### Intended audience

This specification is written for hardware and software engineers who want to design or debug systems and modules that are compatible with the CXS protocol.

#### Typographic conventions

| Convention        | Meaning                                                                                                                                                                                                   |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| italic            | Introduces special terminology, denotes cross-references, and citations.                                                                                                                                  |  |  |

| bold              | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.                                                                     |  |  |

| monospace         | Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.                                                                                               |  |  |

| <u>under</u> line | Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.                                                                   |  |  |

| monospace italic  | Denotes arguments to monospace text where the argument is to be replaced by a specific value.                                                                                                             |  |  |

| monospace bold    | Denotes language keywords when used outside example code.                                                                                                                                                 |  |  |

| <and></and>       | Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example:  MRC p15, 0, <rd>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></rd>                         |  |  |

| SMALL CAPITALS    | Used in body text for a few terms that have specific technical meanings, that are defined in the ARM® Glossary. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE. |  |  |

### **Additional reading**

This section lists relevant documents published by third parties:

PCI Express Base Specification http://www.pcisig.com

CCIX specification https://www.ccixconsortium.com

#### Feedback on this specification

If you have comments on the content of this specification, send e-mail to errata@arm.com. Give:

- The title AMBA CXS Protocol Specification.

- The number, ARM IHI 0079.

- The page number(s) that your comments apply.

- A concise explanation of your comments.

#### **Feedback**

Arm welcomes feedback on its documentation.

# Chapter 1 **Introduction**

This chapter introduces the CXS protocol:

- About the CXS streaming interface protocol on page 1-10.

- *Use case* on page 1-11.

## 1.1 About the CXS streaming interface protocol

This specification describes the CXS streaming interface protocol. The protocol can be used for any point-to-point packetized communication. CXS protocol is optimized for wide interfaces, which allows the protocol to be used to pass packets to a high data rate external interface. The availability of a wide interface permits merging of multiple packets into a single transfer.

### 1.2 Use case

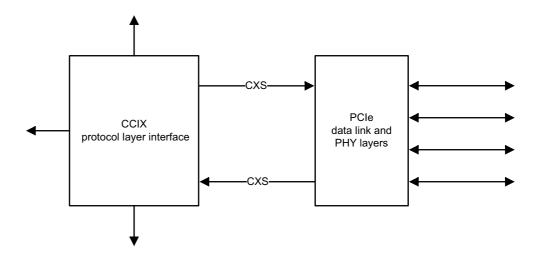

The primary use case for a CXS interface is to transport CCIX packets between an on-chip interconnect and PCIe controller. Data transfer in CXS is unidirectional, so it is typical to have a pair of CXS interfaces between communicating blocks.

Figure 1-1 Typical implementation of CXS

1 Introduction 1.2 Use case

# Chapter 2 CXS operation

This chapter gives an overview of the operation of the CXS protocol and the properties which describe the configuration of a CXS interface. It contains the following sections:

- *Protocol operation* on page 2-14.

- *CXS interface properties* on page 2-16.

## 2.1 Protocol operation

A single instance of the interface has one transmitter (TX) connected to one receiver (RX) and data is sent in one direction.

Table 2-1 shows the mandatory signals of the interface.

Table 2-1 CXS mandatory signals

| Name      | Direction                  | Description                                                                                                                        |

|-----------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| CXSVALID  | Transmitter to receiver    | Indicates that valid information is being passed this cycle.                                                                       |

| CXSDATA   | Transmitter to receiver    | The flit data containing the packet bytes being transmitted. Ignore if <b>CXSVALID</b> is not asserted.                            |

| CXSCNTL   | Transmitter to receiver    | Control information for identifying the start and end of packets within the data field. Ignore if <b>CXSVALID</b> is not asserted. |

| CXSCRDGNT | Receiver to<br>Transmitter | Flow control information indicating that the receiver can accept one flit of data.                                                 |

The transmitter transfers data by driving **CXSDATA**, placing packet control information on **CXSCNTL**, and asserting the **CXSVALID** signal. The data that is transferred in one cycle is known as a flit. A packet can occupy one or more flits. See *Packet examples* on page 4-30 for more details.

Flow control on the interface is implemented through a credit exchange mechanism. The rules of the credit mechanism are:

- Data can only be sent when the transmitter has at least one credit from the receiver.

- When the interface is reset or first activated, the transmitter has no credits and therefore cannot send data across the interface.

- Credits are transferred to the transmitter using the **CXSCRDGNT** signal.

- When CXSCRDGNT is asserted, one credit is transferred to the transmitter every cycle. Each credit permits

one flit of data transfer.

- The receiver must guarantee that it can receive one flit of data for each credit that it grants.

- Each cycle in which CXSVALID is asserted, the transmitter sends one flit of data, which consumes one

credit.

- The maximum number of credits that a receiver grants a transmitter is IMPLEMENTATION DEFINED but must be no more than 15 credits. The transmitter must be able to track up to 15 credits at a time.

- A transmitter cannot use a credit to send a flit until the cycle after the CXSCRDGNT signal is asserted. A

combinational path between CXSCRDGNT and CXSVALID is not recommended.

- Optionally, credits can be returned to the receiver without a flit transfer, using the CXSCRDRTN signal.

When CXSCRDRTN is asserted, one credit is returned to the receiver every cycle. CXSCRDRTN and

CXSVALID must not be asserted in the same cycle. See *Interface control with explicit credit return* on

page 5-34 for more details.

- A receiver cannot reuse a consumed or returned credit until the cycle after CXSVALID or CXSCRDRTN is asserted. . A combinational path between CXSVALID and CXSCRDGNT, and between CXSCRDRTN and CXSCRDGNT is not recommended.

- If the transmitter receives a credit in the same cycle that it returns or uses a credit, the number of available

credits does not change.

This specification expects that most receivers have sufficient storage to issue multiple credits to the transmitter. The number of credits that are required to keep the interface flowing at full bandwidth depends on the credit latency. Credit latency is the number of cycles between the receiver issuing a credit and that credit being reissued after being returned by the transmitter. If the number of credits the receiver can issue is greater than or equal to the credit latency, then the interface can sustain one flit per cycle.

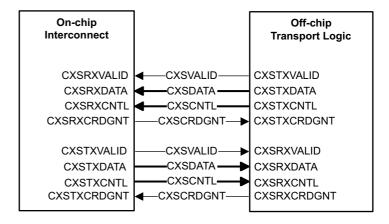

This specification defines signal names for a CXS connection. Port names can be differentiated by adding TX or RX into the name. Figure 2-1 shows an example of a pair of CXS links between two components.

Figure 2-1 CXS connection example

## 2.2 CXS interface properties

A CXS interface is configured for a particular application by setting properties. Table 2-2 describes the properties and their options.

**Table 2-2 Interface properties**

| Property                      | Options                      | Default  | Description                                                                                                          |                                                                                                                                                                                      |  |

|-------------------------------|------------------------------|----------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CXSDATAFLITWIDTH              | 256, 512, 1024               | 256<br>2 | Width of the <b>CXSDATA</b> signal in bits.  Maximum number of packets that can be present in a single flit of data. |                                                                                                                                                                                      |  |

| CXSMAXPKTPERFLIT <sup>a</sup> | 2, 3, 4                      |          |                                                                                                                      |                                                                                                                                                                                      |  |

| CXSCONTINUOUSDATA             | TRUE, FALSE                  | FALSE    | th<br>c                                                                                                              | f set to TRUE, the receiver requires that after a packet is started, it is ompleted in consecutive cycles if nough credits are available.                                            |  |

|                               |                              |          | n<br>tl                                                                                                              | f set to TRUE, the transmitter will<br>ot begin a packet until it can deliver<br>he complete packet in consecutive<br>ycles while credits are available.                             |  |

| CXSERRORFULLPKT <sup>b</sup>  | TRUE, FALSE                  | FALSE    | tl<br>n<br>sj<br>ir                                                                                                  | f set to TRUE, this receiver requires hat the length of every packet natches the packet length that is pecified in the packet header. This necludes packets which end with EndError. |  |

|                               |                              |          | tl<br>p                                                                                                              | f set to TRUE, the transmitter sends<br>he number of bytes specified in the<br>acket header, even if this packet<br>nds with an EndError indication.                                 |  |

| CXSCHECKTYPE                  | None, Odd_Byte_Parity        | None     | Integrity checkin                                                                                                    | g on the CXS interface.                                                                                                                                                              |  |

|                               |                              |          |                                                                                                                      | No signals for integrity checking.                                                                                                                                                   |  |

|                               |                              |          | ir<br>o<br><i>ir</i>                                                                                                 | Odd parity error detection signals included with a nominal granularity of one byte. See section CXS interface checking signals on lage 3-21.                                         |  |

| CXSLINKCONTROL                | None, Explicit_Credit_Return | None     | None: I Explicit Credit                                                                                              | nterface has no link control signals.  Return:                                                                                                                                       |  |

|                               |                              |          | T                                                                                                                    | The interface includes the following                                                                                                                                                 |  |

|                               |                              |          | S1<br>•                                                                                                              | ignals:  CXSACTIVEREQ                                                                                                                                                                |  |

|                               |                              |          | •                                                                                                                    | CXSACTIVEACK                                                                                                                                                                         |  |

|                               |                              |          | •                                                                                                                    | CXSDEACTHINT                                                                                                                                                                         |  |

|                               |                              |          | See <i>Interface com</i> page 5-34 for mo                                                                            | CXSCRDRTN  ntrol with explicit credit return on ore details                                                                                                                          |  |

a. If CXSDATAFLITWIDTH is 256, then CXSMAXPKTPERFLIT must be 2.

b. The encoding of the packet length within the packet is outside of the scope of the CXS document. For use of this interface for CCIX packet transmission, see the CCIX specification for packet length encoding.

Parameters can be set independently for the transmitter and the receiver. When assembling a system, the parameters for connected transmitter and receiver interfaces must be compatible. The compatibility requirements for each of the defined properties are shown in Table 2-3.

**Table 2-3 Property compatibility requirements**

| Parameter         | Compatibility requirement                                                                 |

|-------------------|-------------------------------------------------------------------------------------------|

| CXSDATAFLITWIDTH  | Transmitter and receiver must match.                                                      |

| CXSMAXPKTPERFLIT  | Transmitter must be less than or equal to receiver.                                       |

| CXSCONTINUOUSDATA | If receiver CXSCONTINUOUSDATA = TRUE,<br>then transmitter CXSCONTINUOUSDATA must be TRUE. |

| CXSERRORFULLPKT   | If receiver CXSERRORFULLPKT = TRUE, then transmitter CXSERRORFULLPKT must be TRUE.        |

| CXSCHECKTYPE      | Transmitter and receiver must match.                                                      |

| CXSLINKCONTROL    | Transmitter and receiver must match.                                                      |

2 CXS operation 2.2 CXS interface properties

# Chapter 3 **Signal descriptions**

This chapter describes the signal requirements of the CXS interface. It contains the following sections:

• *Mandatory and optional CXS signals* on page 3-20.

## 3.1 Mandatory and optional CXS signals

Table 3-1 shows the mandatory and optional signals on a CXS interface.

Table 3-1 CXS interface signals

| Signal       | Optional | Property       | Description                                    |

|--------------|----------|----------------|------------------------------------------------|

| CXSDATA      | -        | -              | Data bytes being transmitted.                  |

| CXSCNTL      | -        | -              | Information on packet start, end, and errors.  |

| CXSVALID     | -        | -              | Current cycle has a valid data flit.           |

| CXSCRDGNT    | -        | -              | Grants a single credit to transmitter.         |

| CXSCRDRTN    | Y        | CXSLINKCONTROL | Returns a single credit to receiver.           |

| CXSACTIVEREQ | Y        | CXSLINKCONTROL | Link activation or deactivation request.       |

| CXSACTIVEACK | Y        | CXSLINKCONTROL | Link activation or deactivation acknowledge.   |

| CXSDEACTHINT | Y        | CXSLINKCONTROL | Indicates receiver wants the link deactivated. |

Table 3-2 shows the width of the CXS signals, when present on the interface.

Table 3-2 Signal widths

| Signal       | Width                                                                                                            |

|--------------|------------------------------------------------------------------------------------------------------------------|

| CXSDATA      | CXSDATAFLITWIDTH (256, 512, or 1024 bits)                                                                        |

| CXSCNTL      | 14, 18, 22, 27, 33, 36 or 44 bits. Depends on CXSMAXPKTPERFLIT and CXSDATAFLITWIDTH, See Table 4-2 on page 4-26. |

| CXSVALID     | 1 bit                                                                                                            |

| CXSCRDGNT    | 1 bit                                                                                                            |

| CXSCRDRTN    | 1 bit                                                                                                            |

| CXSACTIVEREQ | 1 bit                                                                                                            |

| CXSACTIVEACK | 1 bit                                                                                                            |

| CXSDEACTHINT | 1 bit                                                                                                            |

### 3.2 CXS interface checking signals

If the CXSCHECKTYPE property is set to Odd\_Byte\_Parity, the interface has additional signals, which can be used to improve the integrity of the interface.

Odd\_Byte\_Parity describes an error detection scheme where check bits are added such that the total count of 1s across the signal and check bits is an odd number. In this scheme, signals wider than 8 bits have one bit added per byte. If the signal width is not divisible by 8, then the most significant parity bit covers less than 8 bits. For example, when CXSCNTL is 27 bits wide, CXSCNTLCHK[3] covers CXSCNTL[26:24].

Single bit control signals have one odd parity bit, so are effectively duplicated with an inverted signal.

Table 3-3 shows the check signals which are included if the CXSCHECKTYPE property is set to Odd\_Byte\_Parity. If the corresponding signal is not present on the interface, then the check signal is not present either.

Table 3-3 Check signal widths (bits)

| Signal       | Check signal    | Signal width | Check signal width |

|--------------|-----------------|--------------|--------------------|

| CXSVALID     | CXSVALIDCHK     | 1            | 1                  |

| CXSDATA      | CXSDATACHK      | 256          | 32                 |

|              |                 | 512          | 64                 |

|              |                 | 1024         | 128                |

| CXSCNTL      | CXSCNTLCHK      | 14           | 2                  |

|              |                 | 18           | 3                  |

|              |                 | 22           | 3                  |

|              |                 | 27           | 4                  |

|              |                 | 33           | 5                  |

|              |                 | 36           | 5                  |

|              |                 | 44           | 6                  |

| CXSCRDRTN    | CXSCRDRTNCHK    | 1            | 1                  |

| CSXACTIVEREQ | CXSACTIVEREQCHK | 1            | 1                  |

| CXSCRDGNT    | CXSCRDGNTCHK    | 1            | 1                  |

| CXSACTIVEACK | CXSACTIVEACKCHK | 1            | 1                  |

| CXSDEACTHINT | N/A             | 1            | -                  |

# Chapter 4 CXS packets

The data that is transmitted on the CXS interface is organized into packets. In CCIX or PCIe terminology, this is a Transaction Layer Packet (TLP). This chapter describes CXS packets:

- Packet position constraints on page 4-24.

- Packet control signal on page 4-25.

- Packet size constraints on page 4-29.

- Packet examples on page 4-30.

### 4.1 Packet position constraints

CXS places restrictions on the placement of packets within each flit of data to simplify data path implementation.

- The first byte of a packet must be placed on an aligned 16-byte boundary.

- Subsequent bytes of the packet occupy subsequent bytes of the flit.

- Packets can end on any four-byte aligned boundary.

- When a packet has been started at a byte position in the current flit, that packet will occupy every subsequent byte in that flit until the packet ends or the flit ends.

- If there are remaining bytes in the packet when the flit ends, that packet will start at byte[0] of the next flit and occupy every subsequent byte position until the packet ends or the flit ends.

- When a packet ends within a flit, the remaining bytes in the flit can be unused.

- Any packet in a flit must begin at the first available 16-byte boundary relative to the start of the flit or the

ending of a previous packet.

CXSMAXPKTPERFLIT specifies the maximum number of packets that can have bytes in a flit. There can be up to CXSMAXPKTPERFLIT new packets starting in a flit, and up to CXSMAXPKTPERFLIT packets ending in a flit.

If a packet started on a previous flit and is continuing in the current flit, that continuing packet will count towards the packet limit. That packet could therefore only have one less than CXSMAXPKTPERFLIT new packets starting.

## 4.2 Packet control signal

The control fields of a CXS packet are signaled using **CXSCNTL**. This section describes the fields and positioning within the **CXSCNTL** signal.

#### 4.2.1 Packet control fields

The **CXSCNTL** signal contains five fields. The widths of each field, and therefore the bit position of each field, vary with the properties of the interface. The fields are described in Table 4-1.

**Table 4-1 Packet control fields**

| Field         | Description                                                                                                                                                                    |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| START         | Each bit in <b>START</b> indicates that a packet is starting in this flit.  The number of bits in <b>START</b> is CXSMAXPKTPERFLIT, which is the number of packets that can be |  |  |

|               | present in a flit of data. For example, when CXSMAXPKTPERFLIT = 4, then:                                                                                                       |  |  |

|               | • START[0] = 1, at least one packet is starting in this flit.                                                                                                                  |  |  |

|               | • START[1] = 1, at least two packets are starting in this flit.                                                                                                                |  |  |

|               | • START[2] = 1, at least three packets are starting in this flit.                                                                                                              |  |  |

|               | • START[3] = 1, at least four packets are starting in this flit.                                                                                                               |  |  |

|               | If any bit of <b>START</b> is 1, all lower bits of <b>START</b> must be 1.                                                                                                     |  |  |

| START[N:0]PTR | This field is an array of pointers to the starting location of each of the packets in this flit.                                                                               |  |  |

|               | • There is one pointer for each bit in the START field, valid if that bit of START is set.                                                                                     |  |  |

|               | • If the corresponding <b>START</b> bit is 0, the pointer can have any value and should be ignored.                                                                            |  |  |

|               | All packet starts are 16-byte aligned.                                                                                                                                         |  |  |

|               | • The width of each pointer is log <sub>2</sub> (CXSDATAFLITWIDTH/128) bits.                                                                                                   |  |  |

|               | • The first byte of the X <sup>th</sup> starting packet is (START[X]PTR << 4).                                                                                                 |  |  |

|               | • Start pointers are defined to be monotonically increasing, for example <b>START1PTR</b> must be greater than <b>START0PTR</b> .                                              |  |  |

Table 4-1 Packet control fields (continued)

| Field       | Description                                                                                                                                                               |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| END         | Each bit in <b>END</b> indicates that a packet is ending in this flit.                                                                                                    |  |  |  |

|             | The number of bits in <b>END</b> is CXSMAXPKTPERFLIT, which is the number of packets that can be present in a flit of data. For example, when CXSMAXPKTPERFLIT = 4, then: |  |  |  |

|             | • <b>END</b> [0] = 1, at least one packet is ending in this flit.                                                                                                         |  |  |  |

|             | • END[1] = 1, at least two packets are ending in this flit.                                                                                                               |  |  |  |

|             | • END[2] = 1, at least three packets are ending in this flit.                                                                                                             |  |  |  |

|             | • END[3] = 1, at least four packets are ending in this flit.                                                                                                              |  |  |  |

|             | If any bit of <b>END</b> is 1, all lower bits of <b>END</b> must be 1.                                                                                                    |  |  |  |

| ENDERROR    | Each bit in ENDERROR indicates that a packet is ending with an error condition in this flit                                                                               |  |  |  |

|             | • <b>ENDERROR</b> [0] = 1, the first packet ending this cycle has an error.                                                                                               |  |  |  |

|             | • <b>ENDERROR</b> [1] = 1, the second packet ending this cycle has an error.                                                                                              |  |  |  |

|             | • <b>ENDERROR</b> [2] = 1, the third packet ending this cycle has an error.                                                                                               |  |  |  |

|             | • <b>ENDERROR</b> [3] = 1, the fourth packet ending this cycle has an error.                                                                                              |  |  |  |

|             | The number of bits in <b>ENDERROR</b> is the number of bits in <b>END</b> .                                                                                               |  |  |  |

|             | If ENDERROR[N] is asserted, END[N] must be asserted.                                                                                                                      |  |  |  |

| END[N:0]PTR | This field is an array of pointers to the last 4 bytes of packets ending in this flit.                                                                                    |  |  |  |

|             | • There is one pointer for each <b>END</b> bit, valid only if that <b>END</b> bit is set.                                                                                 |  |  |  |

|             | • If the corresponding <b>END</b> bit is 0, the pointer can have any value and should be ignored.                                                                         |  |  |  |

|             | All packet ends are 4-byte aligned.                                                                                                                                       |  |  |  |

|             | • The width of each pointer is log <sub>2</sub> (CXSDATAFLITWIDTH/32) bits.                                                                                               |  |  |  |

|             | • Each end pointer points to the first byte of the last aligned 4 bytes of the packet.                                                                                    |  |  |  |

|             | • The last byte of the X <sup>th</sup> ending packet is therefore (( <b>END</b> [X] <b>PTR</b> << 2)+3).                                                                  |  |  |  |

|             | <ul> <li>Valid end pointers are defined to be monotonically increasing, for example if two packets end in this flit then END1PTR must be greater than END0PTR.</li> </ul> |  |  |  |

|             | ——Note ———                                                                                                                                                                |  |  |  |

|             | START[X]PTR and END[X]PTR might not point to the same packet, for example if a packet started in a previous flit.                                                         |  |  |  |

#### 4.2.2 Packet control field structure

Table 4-2 shows Packet control field widths and placement information for all combinations of CXSMAXPKTPERFLIT and CXSDATAFLITWIDTH. See *Packet examples* on page 4-30 for illustrations of how these structures are used.

Table 4-2 Packet control field widths and placement

| CXSMAXPKT | PERFLIT CXSDATAFLITWID | OTH Width of CXSCNTL | Field            | Bit positions in CXSCNTL |

|-----------|------------------------|----------------------|------------------|--------------------------|

| 2         | 256                    | 14                   | START[1:0]       | CXSCNTL[1:0]             |

|           |                        |                      | START0PTR[0]     | CXSCNTL[2]               |

|           |                        |                      | START1PTR[0]     | CXSCNTL[3]               |

|           |                        |                      | <b>END</b> [1:0] | CXSCNTL[5:4]             |

|           |                        |                      | ENDERROR[1:0]    | CXSCNTL[7:6]             |

|           |                        |                      | END0PTR[2:0]     | CXSCNTL[10:8]            |

|           |                        |                      | END1PTR[2:0]     | <b>CXSCNTL</b> [13:11]   |

Table 4-2 Packet control field widths and placement (continued)

| CXSMAXPKTPERFLIT | CXSDATAFLITWIDTH | Width of CXSCNTL | Field                                                        | Bit positions in CXSCNTL |  |  |  |

|------------------|------------------|------------------|--------------------------------------------------------------|--------------------------|--|--|--|

| 2                | 512              | 18               | <b>START</b> [1:0]                                           | CXSCNTL[1:0]             |  |  |  |

|                  |                  |                  | STARTOPTR[1:0]                                               | CXSCNTL[3:2]             |  |  |  |

|                  |                  |                  | START1PTR[1:0]                                               | CXSCNTL[5:4]             |  |  |  |

|                  |                  |                  | END[1:0]                                                     | CXSCNTL[7:6]             |  |  |  |

|                  |                  |                  | ENDERROR[1:0]                                                | CXSCNTL[9:8]             |  |  |  |

|                  |                  |                  | ENDOPTR[3:0]                                                 | CXSCNTL[13:10]           |  |  |  |

|                  |                  |                  | END1PTR[3:0]                                                 | <b>CXSCNTL</b> [17:14]   |  |  |  |

| 2                | 1024             | 22               | <b>START</b> [1:0]                                           | CXSCNTL[1:0]             |  |  |  |

|                  |                  |                  | STARTOPTR[2:0]                                               | CXSCNTL[4:2]             |  |  |  |

|                  |                  |                  | START1PTR[2:0]                                               | CXSCNTL[7:5]             |  |  |  |

|                  |                  |                  | END[1:0]                                                     | CXSCNTL[9:8]             |  |  |  |

|                  |                  |                  | ENDERROR[1:0]                                                | <b>CXSCNTL</b> [11:10]   |  |  |  |

|                  |                  |                  | END0PTR[4:0]                                                 | <b>CXSCNTL</b> [16:12]   |  |  |  |

|                  |                  |                  | END1PTR[4:0]                                                 | CXSCNTL[21:17]           |  |  |  |

| 3                | 256              | -                | Not legal: 256-bit interface has maximum o packets per flit. |                          |  |  |  |

| 3                | 512              |                  | START[2:0]                                                   | CXSCNTL[2:0]             |  |  |  |

|                  |                  |                  | STARTOPTR[1:0]                                               | CXSCNTL[4:3]             |  |  |  |

|                  |                  |                  | START1PTR[1:0]                                               | CXSCNTL[6:5]             |  |  |  |

|                  |                  |                  | START2PTR[1:0]                                               | CXSCNTL[8:7]             |  |  |  |

|                  |                  |                  | END[2:0]                                                     | CXSCNTL[11:9]            |  |  |  |

|                  |                  |                  | ENDERROR[2:0]                                                | CXSCNTL[14:12]           |  |  |  |

|                  |                  |                  | ENDOPTR[3:0]                                                 | CXSCNTL[18:15]           |  |  |  |

|                  |                  |                  | END1PTR[3:0]                                                 | <b>CXSCNTL</b> [22:19]   |  |  |  |

|                  |                  |                  | END2PTR[3:0]                                                 | CXSCNTL[26:23]           |  |  |  |

| 3                | 1024             | 33               | <b>START</b> [2:0]                                           | CXSCNTL[2:0]             |  |  |  |

|                  |                  |                  | STARTOPTR[2:0]                                               | CXSCNTL[5:3]             |  |  |  |

|                  |                  |                  | START1PTR[2:0]                                               | CXSCNTL[8:6]             |  |  |  |

|                  |                  |                  | START2PTR[2:0]                                               | CXSCNTL[11:9]            |  |  |  |

|                  |                  |                  | END[2:0]                                                     | <b>CXSCNTL</b> [14:12]   |  |  |  |

|                  |                  |                  | ENDERROR[2:0]                                                | CXSCNTL[17:15]           |  |  |  |

|                  |                  |                  | END0PTR[4:0]                                                 | CXSCNTL[22:18]           |  |  |  |

|                  |                  |                  | END1PTR[4:0]                                                 | CXSCNTL[27:23]           |  |  |  |

|                  |                  |                  | END2PTR[4:0]                                                 | CXSCNTL[32:28]           |  |  |  |

Table 4-2 Packet control field widths and placement (continued)

| CXSMAXPKTPERFLIT | CXSDATAFLITWIDTH | Width of CXSCNTL | Field              | Bit positions in CXSCNTL |

|------------------|------------------|------------------|--------------------|--------------------------|

| 4                | 512              | 36               | <b>START</b> [3:0] | CXSCNTL[3:0]             |

|                  |                  |                  | STARTOPTR[1:0]     | CXSCNTL[5:4]             |

|                  |                  |                  | START1PTR[1:0]     | CXSCNTL[7:6]             |

|                  |                  |                  | START2PTR[1:0]     | CXSCNTL[9:8]             |

|                  |                  |                  | START3PTR[1:0]     | <b>CXSCNTL</b> [11:10]   |

|                  |                  |                  | END[3:0]           | CXSCNTL[15:12]           |

|                  |                  |                  | ENDERROR[3:0]      | CXSCNTL[19:16]           |

|                  |                  |                  | ENDOPTR[3:0]       | CXSCNTL[23:20]           |

|                  |                  |                  | END1PTR[3:0]       | CXSCNTL[27:24]           |

|                  |                  |                  | END2PTR[3:0]       | CXSCNTL[31:28]           |

|                  |                  |                  | END3PTR[3:0]       | CXSCNTL[35:32]           |

|                  | 1024             | 44               | START[3:0]         | CXSCNTL[3:0]             |

|                  |                  |                  | STARTOPTR[2:0]     | CXSCNTL[6:4]             |

|                  |                  |                  | START1PTR[2:0]     | CXSCNTL[9:7]             |

|                  |                  |                  | START2PTR[2:0]     | CXSCNTL[12:10]           |

|                  |                  |                  | START3PTR[2:0]     | CXSCNTL[15:13]           |

|                  |                  |                  | END[3:0]           | CXSCNTL[19:16]           |

|                  |                  |                  | ENDERROR[3:0]      | CXSCNTL[23:20]           |

|                  |                  |                  | END0PTR[4:0]       | CXSCNTL[28:24]           |

|                  |                  |                  | END1PTR[4:0]       | CXSCNTL[33:29]           |

|                  |                  |                  | END2PTR[4:0]       | CXSCNTL[38:34]           |

|                  |                  |                  | END3PTR[4:0]       | CXSCNTL[43:39]           |

### 4.3 Packet size constraints

A CXS interface transmits packets of data that meet the following requirements:

- At least 4 bytes in size.

- A multiple of 4 bytes in size.

- No upper limit on packet size.

When used to transmit CCIX packets, there may be further constraints on packet size. Refer to the CCIX specification for more details.

## 4.4 Packet examples

The following examples illustrate packet placement rules and the CXSCNTL field usage. Examples that are shown in Table 4-3 and Table 4-4 on page 4-31 both have CXSCONTINUOUSDATA = TRUE and CXSDATACHECK = None. Each data packet in the figures is shaded and has a unique identifier. Unused packet slots have dashes instead of identifiers.

Table 4-3 shows an example with 256-bit data, CXSDATAFLITWIDTH = 256. It has up to two packets per flit, CXSMAXPKTPERFLIT = 2.

Table 4-3 Example 256-bit wide interface with maximum of two packets per flit.

|                  | Cycle            | Э |      |      |   |      |      |      |      |      |      |      |      |

|------------------|------------------|---|------|------|---|------|------|------|------|------|------|------|------|

| Signal           | Field            | 0 | 1    | 2    | 3 | 4    | 5    | 6    | 7    | 8    | 9    | 10   | 11   |

| CXSVALID         |                  | 0 | 1    | 1    | 0 | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| CXSDATA[31:0]    |                  | - | TLPA | TLPB | - | TLPD | TLPD | TLPE | TLPE | TLPF | TLPH | TLPI | TLPK |

| CXSDATA[63:32]   |                  | - | TLPA | TLPB | - | TLPD | -    | TLPE | TLPE | -    | TLPH | TLPI | TLPK |

| CXSDATA[95:64]   |                  | - | TLPA | TLPB | - | TLPD | -    | TLPE | TLPE | -    | TLPH | TLPI | TLPK |

| CXSDATA[127:96]  |                  | - | TLPA | -    | - | TLPD | -    | TLPE | TLPE | -    | TLPH | TLPI | TLPK |

| CXSDATA[159:128] |                  | - | TLPA | TLPC | - | TLPD | TLPE | TLPE | TLPE | TLPG | TLPI | TLPJ | TLPL |

| CXSDATA[191:160] |                  | - | TLPA | TLPC | - | TLPD | TLPE | TLPE | -    | TLPG | TLPI | TLPJ | TLPL |

| CXSDATA[223:192] |                  | - | TLPA | TLPC | - | TLPD | TLPE | TLPE | -    | TLPG | TLPI | TLPJ | TLPL |

| CXSDATA[255:224] |                  | - | -    | TLPC | - | TLPD | TLPE | TLPE | -    | TLPG | TLPI | TLPJ | TLPL |

|                  |                  |   |      |      |   |      |      |      |      |      |      |      |      |

| CXSCNTL[1:0]     | START[1:0]       | - | 0x1  | 0x3  | - | 0x1  | 0x1  | 0x0  | 0x0  | 0x3  | 0x3  | 0x1  | 0x3  |

| CXSCNTL[2]       | START0PTR[0]     | - | 0x0  | 0x0  | - | 0x0  | 0x1  | -    | -    | 0x0  | 0x0  | 0x1  | 0x0  |

| CXSCNTL[3]       | START1PTR[0]     | - | -    | 0x1  | - | -    | -    | -    | -    | 0x1  | 0x1  | -    | 0x1  |

| CXSCNTL[5:4]     | <b>END</b> [1:0] | - | 0x1  | 0x3  | - | 0x0  | 0x1  | 0x0  | 0x1  | 0x3  | 0x1  | 0x3  | 0x3  |

| CXSCNTL[7:6]     | ENDERROR[1:0]    | - | 0x0  | 0x0  | - | 0x0  |

| CXSCNTL[10:8]    | END0PTR[2:0]     | - | 0x6  | 0x2  | - | -    | 0x0  | -    | 0x4  | 0x0  | 0x3  | 0x3  | 0x3  |

| CXSCNTL[13:11]   | END1PTR[2:0]     | - | -    | 0x7  | - | -    | -    | -    | -    | 0x7  | -    | 0x7  | 0x7  |

Table 4-4 shows an example with 512-bit data, CXSDATAFLITWIDTH = 512. It has up to four packets per flit, CXSMAXPKTPERFLIT = 4.

Table 4-4 Example 512-bit wide interface with maximum of four packets per flit.

|                  | Cycle          | е |          |            |   |          |           |      |          |      |      |            |   |

|------------------|----------------|---|----------|------------|---|----------|-----------|------|----------|------|------|------------|---|

| Signal           | Field          | 0 | 1        | 2          | 3 | 4        | 5         | 6    | 7        | 8    | 9    | 10         | 1 |

| CXSVALID         |                | 0 | 1        | 1          | 0 | 1        | 1         | 1    | 1        | 1    | 1    | 1          | ( |

| CXSDATA[31:0]    |                | - | TLPA     | TLPB       | - | TLPD     | TLPD      | TLPE | TLPE     | TLPF | TLPI | TLPM       |   |

| CXSDATA[63:32]   |                | - | TLPA     | TLPB       | - | TLPD     | -         | TLPE | TLPE     | -    | TLPI | TLPM       |   |

| CXSDATA[95:64]   |                | - | TLPA     | TLPB       | - | TLPD     | -         | TLPE | TLPE     | -    | TLPI | TLPM       |   |

| CXSDATA[127:96]  |                | - | TLPA     | TLPB       | - | TLPD     | -         | TLPE | TLPE     | -    | TLPI | TLPM       |   |

| CXSDATA[159128]  |                | - | TLPA     | TLPB       | - | TLPD     | TLPE      | TLPE | TLPE     | TLPG | TLPJ | TLPN       |   |

| CXSDATA[191:160] |                | - | TLPA     | TLPB       | - | TLPD     | TLPE      | TLPE | TLPE     | TLPG | TLPJ | TLPN       |   |

| CXSDATA[223:192] |                | - | TLPA     | -          | - | TLPD     | TLPE      | TLPE | TLPE     | TLPG | TLPJ | TLPN       |   |

| CXSDATA[255:224] |                | - | TLPA     | -          | - | TLPD     | TLPE      | TLPE | TLPE     | TLPG | TLPJ | TLPN       |   |

| CXSDATA[287:256] |                | - | TLPA     | TLPC       | - | TLPD     | TLPE      | TLPE | TLPE     | TLPH | TLPK | TLPO       |   |

| CXSDATA[319:288] |                | - | -        | TLPC       | - | TLPD     | TLPE      | TLPE | TLPE     | TLPH | TLPK | TLPO       |   |

| CXSDATA[351:320] |                | - | -        | TLPC       | - | TLPD     | TLPE      | TLPE | TLPE     | TLPH | TLPK | TLPO       |   |

| CXSDATA[383:352] |                | - | -        | TLPC       | - | TLPD     | TLPE      | TLPE | TLPE     | TLPH | TLPK | TLPO       |   |

| CXSDATA[415:384] |                | - | -        | TLPC       | - | TLPD     | TLPE      | TLPE | TLPE     | TLPI | TLPL | TLPP       |   |

| CXSDATA[447:416] |                | - | -        | TLPC       | - | TLPD     | TLPE      | TLPE | -        | TLPI | TLPL | TLPP       |   |

| CXSDATA[479:448] |                | - | -        | TLPC       | - | TLPD     | TLPE      | TLPE | -        | TLPI | TLPL | TLPP       |   |

| CXSDATA[511:480] |                | - | -        | TLPC       | - | TLPD     | TLPE      | TLPE | -        | TLPI | TLPL | TLPP       |   |

| CXSCNTL[3:0]     | START[3:0]     |   | 0x1      | 0x3        |   | 0x1      | 0x1       | 0x0  | 0x0      | 0xF  | 0x7  | 0xF        |   |

|                  |                |   |          |            | _ |          |           |      |          |      |      |            |   |

| CXSCNTL[5:4]     | START0PTR[1:0] | - | 0x0      | 0x0<br>0x2 |   | 0x0      | 0x1       | -    | -        | 0x0  | 0x1  | 0x0<br>0x1 |   |

| CXSCNTL[7:6]     | START1PTR[1:0] | - |          | 0XZ        | - | <u>-</u> |           | -    |          | 0x1  | 0x2  |            |   |

| CXSCNTL[8:9]     | START2PTR[1:0] | - | -        |            | - |          |           |      |          | 0x2  | 0x3  | 0x2        |   |

| CXSCNTL[11:10]   | START3PTR[1:0] | - | -<br>0v1 |            | - | -<br>0v0 | -<br>0.:1 |      | -<br>0v1 | 0x3  |      | 0x3        |   |

| CXSCNTL[15:12]   | END[3:0]       | - | 0x1      | 0x3        | - | 0x0      | 0x1       | 0x0  | 0x1      | 0x7  | 0xF  | 0xF        | - |

| CXSCNTL[19:16]   | ENDERROR[3:0]  | - | 0x0      | 0x0        | - | 0x0      | 0x0       | 0x0  | 0x0      | 0x0  | 0x0  | 0x0        |   |

| CXSCNTL[23:20]   | ENDOPTR[3:0]   | - | 0x8      | 0x5        | - | -        | 0x0       | -    | 0xC      | 0x0  | 0x3  | 0x3        |   |

| CXSCNTL[27:24]   | END1PTR[3:0]   | - | -        | 0xF        | - | -        | -         | -    | -        | 0x7  | 0x7  | 0x7        |   |

| CXSCNTL[31:28]   | END2PTR[3:0]   | - | -        | -          | - | -        | -         | -    | -        | 0xB  | 0xB  | 0xB        |   |

| CXSCNTL[35:32]   | END3PTR[3:0]   | - |          | -          | - |          | -         | -    | -        | -    | 0xF  | 0xF        |   |

4 CXS packets 4.4 Packet examples

## Chapter 5

## **CXS** interface activation and deactivation

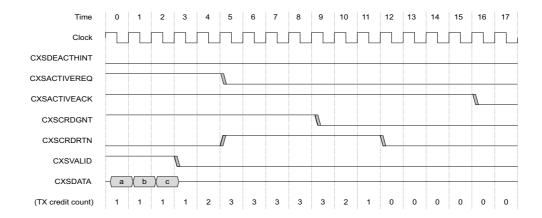

A CXS interface can be optionally configured to include signaling for activation and deactivation, using the CXSLINKCONTROL property. The property can be set to *None* or *Explicit\_Credit\_Return*. When set to *None*, there are no signals for interface activation and deactivation, which requires that the receiver must always send credits when they are available and the transmitter must always be able to receive them. This chapter describes the activation and deactivation mechanisms when the property is set to Explicit\_Credit\_Return, and has the following sections:

- Interface control with explicit credit return on page 5-34.

- Request and acknowledgement handshaking on page 5-35.

- Response to a new state on page 5-36.

- Race conditions on page 5-37.

- Timing relationships between data and link control signals on page 5-38.

- *Interface activation and deactivation examples* on page 5-39.

## 5.1 Interface control with explicit credit return

When the **CXSLINKCONTROL** property is set to *Explicit\_Credit\_Return*, the following specification applies and signals are added to the interface as shown in Table 5-1.

Table 5-1 Signals for link control using explicit credit return

| Name         | Direction               | Description                                                                                                                                                             |

|--------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CXSCRDRTN    | Transmitter to receiver | Flow control information indicating that the sender is returning a previously granted credit without using it. Can only be asserted if <b>CXSVALID</b> is not asserted. |

| CXSACTIVEREQ | Transmitter to receiver | Link activation or deactivation request.                                                                                                                                |

| CXSACTIVEACK | Reciever to transmitter | Link activation or deactivation acknowledge.                                                                                                                            |

| CXSDEACTHINT | Reciever to transmitter | Hint that receiver would like link to be deactivated.                                                                                                                   |

The interface starts in an idle state either on exit from reset or when moving to a full operational state. Transfer of flits can commence when credits have been granted by the receiver side. Credits can be granted when the transmitter side indicates that it is ready to receive them.

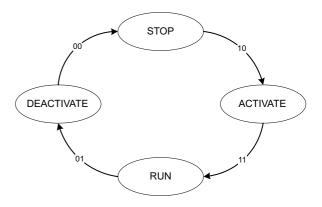

A two-signal, four-phase, handshake mechanism is used. This mechanism synchronizes the state of the link between the transmitter and receiver and is initiated by the transmitter. In addition, a signal is available for the receiver to request that the link be deactivated.

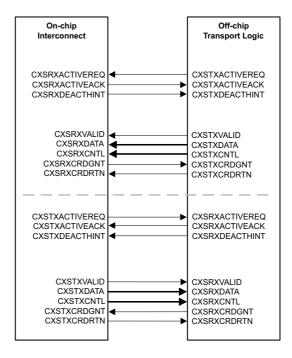

Figure 5-1 shows a typical connection, with one outbound and one inbound CXS interface, each of which has an instance of the credit control signals.

Figure 5-1 Example with two CXS links

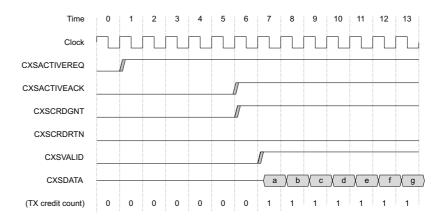

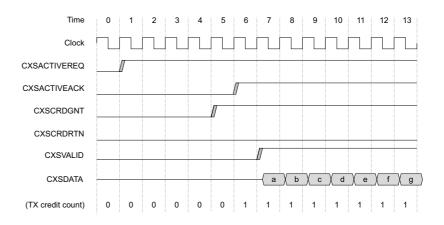

## 5.2 Request and acknowledgement handshaking

Request and acknowledge handshaking uses CXSACTIVEREQ and CXSACTIVEACK as primary signals.

The transmitter requires a credit before it can send a flit. A credit is passed from the receiver when it has resources available to accept a flit.

- On exit from reset, all credits are held by the receiver and at least one must be passed to the transmitter before flit transfer can begin.

- During normal operation, there is an ongoing exchange of flits and credits between the two sides of the interface.

- Before entering a low-power state, the sending of payload flits must be stopped and all credits must be returned to the receiver. This action returns the interface to the same state that it was at immediately after reset