# Arm<sup>®</sup> CoreLink<sup>™</sup> AHB Cache Revision: r0p0

**Technical Reference Manual**

## Arm<sup>®</sup> CoreLink<sup>™</sup> AHB Cache

#### **Technical Reference Manual**

Copyright © 2019, 2020 Arm Limited or its affiliates. All rights reserved.

#### **Release Information**

#### **Document History**

| Issue   | Date             | Confidentiality  | Change                               |

|---------|------------------|------------------|--------------------------------------|

| 0000-01 | 13 December 2019 | Confidential     | First beta release for r0p0.         |

| 0000-02 | 24 April 2020    | Non-Confidential | First early access release for r0p0. |

| 0000-03 | 06 October 2020  | Non-Confidential | First full release for r0p0.         |

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. **No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.**

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with <sup>®</sup> or <sup>TM</sup> are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at *http://www.arm.com/company/policies/trademarks*.

Copyright © 2019, 2020 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

(LES-PRE-20349)

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

#### **Product Status**

The information in this document is Final, that is for a developed product.

#### Web Address

developer.arm.com

# Contents Arm<sup>®</sup> CoreLink<sup>™</sup> AHB Cache Technical Reference Manual

|           | Pref | face                  |  |

|-----------|------|-----------------------|--|

|           |      | About this book       |  |

|           |      | Feedback              |  |

| Chapter 1 | Ove  | erview                |  |

|           | 1.1  | Basic terms           |  |

|           | 1.2  | About the AHB Cache   |  |

|           | 1.3  | Configurable features |  |

|           | 1.4  | Compatibility         |  |

|           | 1.5  | Implementations       |  |

|           | 1.6  | Compliance            |  |

|           | 1.7  | Product documentation |  |

|           | 1.8  | Product revisions     |  |

| Chapter 2 | Inte | rfaces                |  |

|           | 2.1  | Clocking and reset    |  |

|           | 2.2  | AHB interface         |  |

|           | 2.3  | APB interface         |  |

|           | 2.4  | Interrupts            |  |

|           | 2.5  | Low-Power Interface   |  |

|           |      |                       |  |

| Chapter 3  | Ope                 | ration                                                           |            |  |

|------------|---------------------|------------------------------------------------------------------|------------|--|

|            | 3.1                 | Basic operations                                                 | 3-35       |  |

|            | 3.2                 | Performance monitoring                                           | 3-37       |  |

|            | 3.3                 | Maintenance                                                      | 3-38       |  |

| Chapter 4  | Prog                | grammers model                                                   |            |  |

|            | 4.1                 | About the programmers model                                      |            |  |

|            | 4.2                 | Programming considerations                                       | 4-46       |  |

|            | 4.3                 | Register summary                                                 |            |  |

|            | 4.4                 | Register descriptions                                            | 4-51       |  |

| Chapter 5  | Usin                | ng software to program the AHB Cache                             |            |  |

|            | 5.1                 | Enable the AHB Cache by using software                           | 5-96       |  |

|            | 5.2                 | Disable the AHB Cache using software                             | 5-100      |  |

|            | 5.3                 | Use Non-secure software to check cache enable status             | 5-103      |  |

|            | 5.4                 | Configurable cache diagnostics available for Non-secure software | 5-104      |  |

|            | 5.5                 | Use software for manual maintenance on the AHB Cache             | 5-105      |  |

|            | 5.6                 | Use software to access the statistics counters in the AHB Cache  | 5-112      |  |

|            | 5.7                 | Power control                                                    | 5-116      |  |

| Appendix A | Signal descriptions |                                                                  |            |  |

|            | A.1                 | Clock and reset signals                                          | Аррх-А-118 |  |

|            | A.2                 | LPI signals                                                      | Аррх-А-119 |  |

|            | A.3                 | AHB Slave interface signals                                      | Аррх-А-120 |  |

|            | A.4                 | AHB Master interface signals                                     | Аррх-А-122 |  |

|            | A.5                 | APB interface signals                                            | Аррх-А-124 |  |

|            | A.6                 | System interface signals                                         | Аррх-А-125 |  |

|            | A.7                 | Memory interface signals                                         | Аррх-А-126 |  |

|            | A.8                 | Configuration input ports                                        | Аррх-А-128 |  |

| Appendix B | Revi                | isions                                                           |            |  |

|            | B.1                 | Revisions                                                        | Аррх-В-130 |  |

# Preface

This preface introduces the Arm<sup>®</sup> CoreLink<sup>™</sup> AHB Cache Technical Reference Manual.

It contains the following:

- *About this book* on page 7.

- Feedback on page 10.

## About this book

This book describes the functionality of the components in the Arm<sup>®</sup> CoreLink<sup>™</sup> AHB Cache. It also provides the programming information and the signal descriptions.

#### Product revision status

The rxpy identifier indicates the revision status of the product described in this book, for example, r1p2, where:

- rx Identifies the major revision of the product, for example, r1.

- py Identifies the minor revision or modification status of the product, for example, p2.

#### Intended audience

This book is written for system designers and programmers who are designing or programming a *System* on *Chip* (SoC) that uses the AHB Cache.

#### Using this book

This book is organized into the following chapters:

#### **Chapter 1 Overview**

This chapter introduces the AHB Cache.

#### **Chapter 2 Interfaces**

This chapter describes the functional interfaces of the AHB Cache.

#### **Chapter 3 Operation**

This chapter describes the operation of the AHB Cache.

#### Chapter 4 Programmers model

This chapter describes the functionality of the AHB Cache from a programming perspective.

#### Chapter 5 Using software to program the AHB Cache

This chapter provides details on programming the AHB Cache by exploring typical scenarios.

#### Appendix A Signal descriptions

This appendix describes the AHB Cache interface signals.

#### **Appendix B Revisions**

This appendix describes the technical changes between released issues of this book.

#### Glossary

The Arm<sup>®</sup> Glossary is a list of terms used in Arm documentation, together with definitions for those terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

See the Arm® Glossary for more information.

#### **Typographic conventions**

#### italic

Introduces special terminology, denotes cross-references, and citations.

#### bold

Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.

#### monospace

Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.

monospace

Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.

monospace italic

Denotes arguments to monospace text where the argument is to be replaced by a specific value.

#### monospace bold

Denotes language keywords when used outside example code.

<and>

Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example:

MRC p15, 0, <Rd>, <CRn>, <CRm>, <Opcode\_2>

#### SMALL CAPITALS

Used in body text for a few terms that have specific technical meanings, that are defined in the *Arm*<sup>®</sup> *Glossary*. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE.

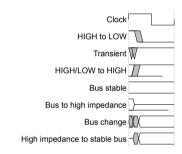

#### **Timing diagrams**

The following figure explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

#### Figure 1 Key to timing diagram conventions

#### Signals

The signal conventions are:

#### Signal level

The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

- HIGH for active-HIGH signals.

- LOW for active-LOW signals.

#### Lowercase n

At the start or end of a signal name, n denotes an active-LOW signal.

#### Additional reading

This book contains information that is specific to this product. See the following documents for other relevant information.

#### **Arm Publications**

| Document name                                                                             | Document ID | Licensee only Y/N |

|-------------------------------------------------------------------------------------------|-------------|-------------------|

| Arm <sup>®</sup> CoreLink <sup>™</sup> AHB Cache Configuration and Integration Manual     | 101808      | Y                 |

| Arm <sup>®</sup> AMBA <sup>®</sup> 5 AHB Protocol Specification, issue B.b                | IHI 0033    | N                 |

| AMBA® APB Protocol Specification Version 2.0, issue C                                     | IHI 0024    | N                 |

| AMBA® Low Power Interface Specification, Arm® Q-Channel and P-Channel Interfaces, Issue C | IHI 0068    | N                 |

# Feedback

#### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

#### Feedback on content

If you have comments on content then send an e-mail to *errata@arm.com*. Give:

- The title Arm CoreLink AHB Cache Technical Reference Manual.

- The number 101807\_0000\_03 en.

- If applicable, the page number(s) to which your comments refer.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

\_\_\_\_\_ Note \_\_\_\_\_

Arm tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader.

# Chapter 1 **Overview**

This chapter introduces the AHB Cache.

It contains the following sections:

- 1.1 Basic terms on page 1-12.

- 1.2 About the AHB Cache on page 1-14.

- 1.3 Configurable features on page 1-17.

- *1.4 Compatibility* on page 1-18.

- 1.5 Implementations on page 1-19.

- 1.6 Compliance on page 1-20.

- 1.7 Product documentation on page 1-21.

- 1.8 Product revisions on page 1-22.

# 1.1 Basic terms

You should be familiar with the terms that are used to describe the AHB Cache and its operation.

This document uses the terms that are defined in the *Arm*<sup>®</sup> *AMBA*<sup>®</sup> *5 AHB Protocol Specification, issue B.b* to describe AHB transfers:

- Bufferable

- Modifiable

- Lookup

- Allocate

The following table describes the complex transfer attributes that are used by AHB Cache.

#### Table 1-1 Complex attributes

| Name              | Signals<br>asserted     | AHB transfer type                                                               | Description                                                                                                                                                                                                                       |

|-------------------|-------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cacheable         | HPROT[4:3]              | A transfer that is both<br>Modifiable and Lookup.                               | A Cacheable transfer is looked up in the cache. If a transfer is not<br>Cacheable, it is passed through.                                                                                                                          |

| Write-Back        | HPROT[4:2]              | A Cacheable Write transfer<br>for which the Bufferable<br>attribute is set.     | A Write-Back transfer updates the data in the cache if the cache<br>line is already allocated (or being allocated due to this transfer).<br>The main memory is only updated when the cache line is evicted.                       |

| Write-<br>Through | HPROT[4:3]              | A Cacheable Write transfer<br>for which the Bufferable<br>attribute is not set. | A Write-Through transfer updates the data in the cache if the cache line is already allocated (or being allocated due to this transfer). A Write-Through transfer forwards the transaction to update the data in the main memory. |

| Early response    | HPROT[2] or<br>HPROT[3] | Writes that are Bufferable or<br>Modifiable.                                    | When a Write-Access is buffered, the AHB Cache can send an<br>early write response to the Write-Access without waiting for the<br>main memory to respond.                                                                         |

The basic operations of the AHB Cache are described in 3.1 Basic operations on page 3-35.

#### Other caching terms

#### Cache line

A cache line is the unit of data transfers between the cache and main memory. The AHB Cache has 32-byte cache lines.

#### Index

A part of the address of a Cacheable access which is used to select between the sets of lines in the cache.

Set

A group of lines with the same index. For a 4-way cache, each set has four lines.

#### Tag

A part of the address of a Cacheable access that is stored in one of the four ways of the tag RAM when allocating a cacheline. This is the part of the address that is compared to a maximum of four valid tags stored in the four ways during a lookup.

#### Streaming

If a cacheable transfer addresses a word that is currently being fetched as part of a linefill, the response and read data is streamed directly to the transfer. In this case, the response and read data does not have to wait for the word to be written to the linefill buffer first.

#### Linefill

See 3.1.4 Linefill on page 3-36.

#### Eviction

See 3.1.5 Eviction on page 3-36.

### Cache hit and cache miss

See 3.1.3 Lookup on page 3-35.

# 1.2 About the AHB Cache

The AHB Cache is a configurable cache which improves performance for IoT devices. The AHB Cache is designed to reduce the effect of high latency or slow memory on system performance.

The AHB Cache can help reduce both system memory bandwidth used and access latency by storing recently accessed memory contents for reuse. Reducing system memory accesses may also help save power at system level.

The AHB Cache can be integrated to connect directly to a processor. It can be implemented as a processor cache (data or generic), or a system cache. It can be used for both code and data.

The cache provides AHB5 data interfaces and an APB configuration interface, both with Arm TrustZone<sup>®</sup> for Armv8-M support. The configuration interface is designed to run at the AHB bus frequency, but it supports running the APB bus on a slower clock by using the **pclken** clock enable input.

The AHB Cache is a non-coherent cache. The AHB5 **HPROT[6]** (Shareable) attribute does not prevent a transfer from being cached or buffered. For more information about how to integrate the AHB Cache into a coherent system, see  $Arm^{\text{\tiny B}}$  CoreLink<sup> $\text{\tiny M}$ </sup> AHB Cache Configuration and Integration Manual.

The AHB Cache has the following features:

- AHB5 data interfaces with 32-bit wide data and address bus

- Zero wait state for cache hit accesses

- 4-way set associativity

- TrustZone for Armv8-M support

- Configurable cache size (2KB-64KB)

- 32-byte cache lines

- Write-Through and Write-Back policy support

- Forceable Write-Through policy

- Pseudo-random replacement policy

- AMBA 4 Low Power Interface (LPI) Q-Channel interfaces for clock and power management.

- Internal buffers for temporarily storing cache lines

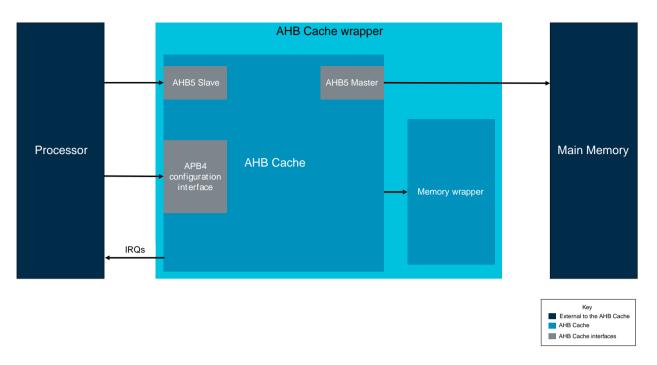

*Figure 1-1 AHB Cache overview* on page 1-15 shows how the AHB Cache connects to the processor and the system memory.

#### Figure 1-1 AHB Cache overview

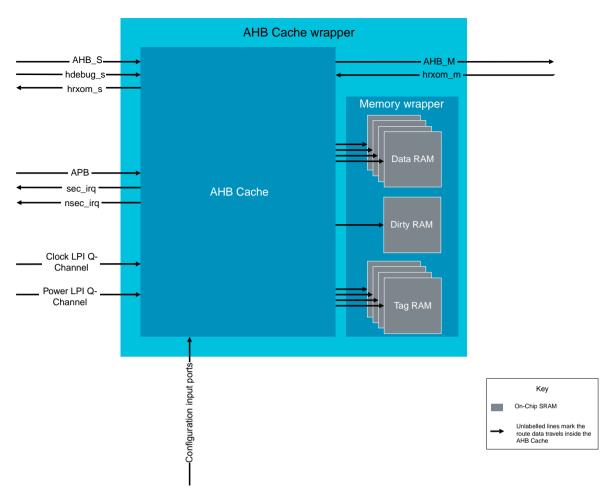

Figure 1-2 AHB Cache wrapper on page 1-16 shows the AHB Cache wrapper.

#### Figure 1-2 AHB Cache wrapper

For the possible configurations of the AHB Cache, see 1.5 Implementations on page 1-19 and the Arm<sup>®</sup> CoreLink<sup>™</sup> AHB Cache Configuration and Integration Manual. The AHB Cache is not designed for safety critical applications.

# 1.3 Configurable features

The AHB Cache provides configurable features.

The AHB Cache configurable features are:

- Write-Through and Write-Back policy support with forceable Write-Through policy. For more information, see *2.3 APB interface* on page 2-29.

- Configurable *eXecute Only Memory* (XOM) support. For more information, see 2.2.6 XOM on page 2-27.

- Configurable automatic maintenance. For more information, see 3.3.7 Automatic maintenance *features* on page 3-39.

- Configurable AHB and APB violation responses. For more information, see 2.2.6 XOM on page 2-27 and 2.3 APB interface on page 2-29.

- Performance monitoring with configurable snapshotting. For more information, see 3.2 Performance monitoring on page 3-37.

- Configurable automatic **power\_on\_enable**. For more information, see 3.3.9 power\_on\_enable on page 3-43.

# 1.4 Compatibility

The AHB Cache is compatible with several other products.

#### **Compatible processors**

The AHB Cache is compatible with the following Arm Cortex<sup>®</sup>-M processors:

- Cortex-M0

- Cortex-M0+

- Cortex-M3

- Cortex-M4

- Cortex-M23

- Cortex-M33

#### Other compatible products

The AHB Cache is compatible with the following products:

- CoreLink SIE-200 System IP for Embedded

- CoreLink PCK-600 Power Control Kit

# 1.5 Implementations

The AHB Cache can be implemented as a processor cache or a system cache.

#### **Processor cache**

The AHB Cache can be implemented as:

- A dedicated data cache

- A dedicated instruction cache

- A generic cache

#### System cache

A system cache implementation of the AHB Cache can be used to:

- Share memory access among several masters

- Reduce latency when connecting an AHB processor to an AXI subsystem

For more details on how to implement the AHB Cache, see Chapter 2 System Design with the *AHB Cache* in the *Arm*<sup>®</sup> CoreLink<sup>™</sup> AHB Cache Configuration and Integration Manual.

# 1.6 Compliance

Arm CoreLink AHB Cache is compliant with Arm specifications and protocols:

- Arm<sup>®</sup> AMBA<sup>®</sup> 5 AHB Protocol Specification, issue B.b

- AMBA® APB Protocol Specification Version 2.0, issue C

- AMBA<sup>®</sup> Low Power Interface Specification, Arm<sup>®</sup> Q-Channel and P-Channel Interfaces, Issue C

\_\_\_\_\_ Note \_\_\_\_\_

The AHB Cache supports the Cortex-M0, M0+, M3, M4 processors even though they are not AHB5 compliant. For more information, see section 8.6.2 *Integration with non-AHB5 compliant processors* in the *Arm*<sup>®</sup> *CoreLink*<sup>™</sup> *AHB Cache Configuration and Integration Manual.*

# 1.7 Product documentation

Documentation that is provided with this product includes a *Technical Reference Manual* (TRM) and a *Configuration and Integration Manual* (CIM), together with architecture and protocol information.

For relevant protocol and architectural information that relates to this product, see *Additional reading* on page 8.

The AHB Cache documentation is as follows:

#### **Technical Reference Manual**

The TRM describes the functionality and the effects of functional options on the behavior of AHB Cache. It is required at all stages of the design flow. The choices that are made in the design flow can mean that some behaviors that the TRM describes are not relevant. If you are programming AHB Cache, contact:

- The implementer to determine:

- The build configuration of the implementation

- What integration, if any, was performed before implementing AHB Cache.

- The integrator to determine the signal configuration of the device that you use.

The TRM complements architecture and protocol specifications and relevant external standards. It does not duplicate information from these sources.

#### **Configuration and Integration Manual**

The CIM describes:

- The available build configuration options

- How to configure the RTL with the build configuration options

- How to integrate AHB Cache into an SoC

- How to implement AHB Cache into your design

- The processes to validate the configured design

The Arm product deliverables include reference scripts and information about using them to implement your design.

The CIM is a confidential book that is only available to licensees.

# 1.8 Product revisions

This section describes the differences in functionality between product revisions.

r0p0 First release.

# Chapter 2 Interfaces

This chapter describes the functional interfaces of the AHB Cache.

It contains the following sections:

- 2.1 Clocking and reset on page 2-24.

- 2.2 AHB interface on page 2-25.

- 2.3 APB interface on page 2-29.

- 2.4 Interrupts on page 2-30.

- 2.5 Low-Power Interface on page 2-31.

# 2.1 Clocking and reset

The AHB Cache uses a single clock and a single reset.

The clock signal, **clk**, drives all the clocked logic, including the interfaces and the SRAM blocks.

The APB configuration interface uses a clock enable signal, **pclken**, to support APB running on a divided frequency. This enable signal must be periodical and synchronous to the clock, **clk**.

The cache uses a single, active-LOW reset, **resetn**. This reset must be deasserted synchronously with **clk** but it can be asserted asynchronously.

For more information, see the Arm<sup>®</sup> CoreLink<sup>™</sup> AHB Cache Configuration and Integration Manual.

#### **Related references**

A.1 Clock and reset signals on page Appx-A-118

# 2.2 AHB interface

The AHB Cache has standard AHB5 data interfaces, which support XOM, locked sequences, and exclusive accesses.

The AHB Cache has an AHB5 Slave interface that receives transfers and serves them from the cache. The AHB Cache is optimized for single cycle hit latency on its AHB5 Slave interface.

The AHB Cache also has an AHB5 Master interface, which:

- Passes through transfers

- Fills data into the cache

- Writes back data from the cache

This section contains the following subsections:

- 2.2.1 Latency and stalling on the AHB interface on page 2-25.

- 2.2.2 Write-Through and Write-Back support on page 2-26.

- 2.2.3 Exclusive access sequences on page 2-26.

- 2.2.4 Locked accesses and locked sequences on page 2-26.

- 2.2.5 Error responses on page 2-27.

- 2.2.6 XOM on page 2-27.

- 2.2.7 Debug accesses on page 2-28.

#### 2.2.1 Latency and stalling on the AHB interface

The AHB Cache operates transparently when disabled, without any latency added. When the cache is enabled, the AHB interface responds with some delay to certain transactions.

#### **Normal latencies**

*Table 2-1 Normal access latencies* on page 2-25 shows the normal access latencies. More latency cycles can occur when:

- Maintenance is ongoing.

- Linefill is ongoing.

#### Table 2-1 Normal access latencies

| Added latency cycles | Cacheable transaction                 | Reason for latency                              |

|----------------------|---------------------------------------|-------------------------------------------------|

| 0                    | Hit or No-Allocate Write-Through miss | Normal operation                                |

| 1                    | No-Allocate Write-Back miss           | Forwarding the transfer after lookup            |

| 3                    | Allocate miss                         | Internal maintenance before linefill is started |

#### AHB interface response to enabling and disabling the cache

When a register access on the APB interface enables or disables the cache, the new setting becomes effective at the next IDLE or NONSEQ transaction on the AHB interface. This operation takes place so that the AHB Cache can avoid changing behavior in the middle of an AHB Burst.

If cache enable maintenance is on when enabling the cache, the AHB interface continues to operate transparently.

If cache disable maintenance is on when disabling the cache, the cache stalls the AHB interface at the next NONSEQ transaction.

The AHB Slave interface remains stalled until the related clean all maintenance is completed. The duration of the maintenance depends on the number of dirty cache lines found in the cache memories.

See *Cache enable maintenance* on page 3-41 and *Cache disable maintenance* on page 3-42 for more information.

#### Write-Allocate

If a Write-Allocate transaction misses the cache, the cache response depends on whether the XOM configuration is enabled:

- If the XOM configuration is enabled, the transaction is stalled. The Write-Allocate transaction is only responded to after the related (critical) word of the triggered linefill has been received from main memory. While the critical word of the triggered linefill is being fetched, the AHB Slave interface remains stalled. Linefill is started with the critical word.

- If the XOM configuration is disabled, the cache buffers the written data and it does not need to wait for the linefill. The cache responds when the internal maintenance is completed.

#### 2.2.2 Write-Through and Write-Back support

The AHB Cache supports both Write-Through and Write-Back policies.

By default, the cache selects the write policy based on the transfer attributes, as defined by the *Arm*<sup>®</sup> *AMBA*<sup>®</sup> *5 AHB Protocol Specification, issue B.b.* For more information about Write-Through and Write-Back transfer attributes, see *1.1 Basic terms* on page 1-12.

Write-Through policy can also be forced if necessary. Forced Write-Through policy makes the cache always select the Write-Through attribute for cacheable transfers. For more information, see *4.4.2 CTRL*, *control register* on page 4-54.

The cache requires that a cache line is always accessed as either Write-Back or Write-Through only. Bursts must not cross between regions of different types. This is normally the case for a *Memory Protection Unit* (MPU) with a 1KB granularity.

#### 2.2.3 Exclusive access sequences

The AHB interface supports exclusive accesses.

Exclusive accesses are triggered by **hexcl\_s** and **hexcl\_m**. Exclusive cacheable accesses are looked up in the cache. If the result is a hit, then the line is cleaned and invalidated before the access proceeds. Then the access continues as an exclusive non-cacheable access and is forwarded to the AHB Master interface. For more information, see the *Exclusive access* section of the  $Arm^{\text{*}}$  *CoreLink*<sup>TM</sup> *AHB Cache Configuration and Integration Manual*.

Exclusive accesses do not trigger a linefill.

#### 2.2.4 Locked accesses and locked sequences

The AHB interface supports locked accesses.

The AHB Cache responds to locked transfers as outlined by the *Arm*<sup>®</sup> *AMBA*<sup>®</sup> *5 AHB Protocol Specification, issue B.b.*

#### **IDLE transfers**

When the cache is enabled, the AHB Cache inserts an unlocked IDLE transfer after the end of a locked sequence, as recommended by the AHB specification. If an unlocked IDLE transfer is already present after the end of the locked sequence, the AHB Cache does not insert another unlocked IDLE transfer.

#### hmastlock

The AHB Cache propagates **hmastlock** when the cache is transparent. While a locked access is being looked up in the cache, **hmastlock** appears on the AHB master interface.

If the lookup results in a hit and the cache line is dirty, the data needs to be written back before the locked access proceeds. Therefore, **hmastlock** is masked. This behavior produces an empty locked sequence. When the Write-Back is completed, **hmastlock** is reasserted.

#### **Eviction Write-Back Burst**

If an AHB locked sequence contains accesses to different addresses, an eviction Write-Back Burst can interrupt it.

\_\_\_\_\_ Note \_\_\_\_\_

Normal use cases of locked transfers in Arm-based systems are:

- Read-modify-write of semaphore data

- Cortex-M3 and Cortex-M4 bit band operations

These use cases are not affected by this limitation because the locked sequence in these cases targets the same address and never crosses a cache line boundary.

When the AHB Cache receives a locked access that hits the cache, the access is stalled until the related cache line is cleaned and invalidated.

It can be the case that a locked sequence crosses a cache line boundary and the subsequent cache line is stored in the cache and dirty. In that situation, the locked sequence is broken at the boundary by the eviction Write-Back Burst and the AHB master interface deasserts **hmastlock**. The sequence is continued with a NONSEQ transaction after the eviction is finished.

**hmastlock** being deasserted can result in the locked sequence progressing further during the eviction Write-Back Burst without completing the previous access.

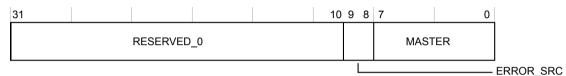

#### 2.2.5 Error responses

The AHB Cache operates transparently when disabled, without any latency added.

The AHB Cache forwards the error response from the master interface to the slave interface for:

- Transfers that must be responded from the endpoint. For example, non-cacheable, non-bufferable, and non-modifiable transfers.

- Streaming hits during a linefill

To learn more about error responses to XOM reads, see 2.2.6 XOM on page 2-27.

#### Linefill error and data loss

If a linefill receives an error response on the AHB Master interface, data from a Write-Back access can be lost.

If a linefill encounters a bus error, the data from the entire linefill Burst is invalidated. Any data written to this cache line before the bus error occurred is lost. The AHB Cache signals the linefill error through an interrupt, TR\_ERR, which is generated by the transfer error.

Further errors are not reported for the given linefill Burst. If a subsequent Burst beat is responded to with an AHB error, it does not trigger the TR\_ERR interrupt again. The AHB error is not captured in the IRQINFO registers, and does not overwrite the information saved earlier for the first error. Therefore regardless of the number of errors received during a linefill Burst, the AHB Cache reports only a single interrupt for the first error.

A linefill error does not affect read data.

## Related concepts

3.1.4 Linefill on page 3-36

#### 2.2.6 XOM

The AHB interface can be configured to support the configurable eXecute Only Memory (XOM) feature.

- Instruction read accesses to a memory location flagged as XOM proceed as normal.

- Data read accesses and writes to XOM regions are not allowed.

The AHB interface supports XOM using hrxom\_s and hrxom\_m sideband signals.

hrxom\_s and hrxom\_m follow the same timing as hruser\_s and hruser\_m.

The downstream AHB slave must assert the hrxom\_m signal when a read access hits an XOM region.

The **hrxom\_m** signal must be consistent throughout a cache line. The AHB Cache can detect that a memory region belongs to an XOM region when the **hrxom\_m** signal is set on its AHB master interface. The XOM attribute is saved for each cache line. On read accesses, the **hrxom\_s** signal is driven according to the previously saved XOM attribute or, for streaming purposes, by the **hrxom\_m** input signal.

If a data access read (**hprot\_s[0]**=1) hits an XOM line already in the cache, the read data is masked and the transfer is responded with an error or an OK response depending on the **ahb\_violation\_resp**. If a Write-Access hits an XOM line already in the cache, the line is invalidated and the transfer is always forwarded. When such XOM violations are detected by the AHB Cache, the AHB Cache sets the XOM error interrupt flag. For more information, see 4.4.9 SECIRQEN, Secure interrupt enable register on page 4-62 and 4.4.14 NSECIRQEN, Non-secure interrupt enable register on page 4-67.

#### 2.2.7 Debug accesses

The AHB Cache supports debug accesses.

Debug accesses must be flagged using the **hdebug\_s** input port. **hdebug\_s** follows the same timing as **hmaster\_s**.

Debug accesses are looked up in the cache, even if they are marked as non-cacheable. The lookup takes place in case the debugger has used the wrong attributes or the MPU overwrote them.

# 2.3 APB interface

The APB interface provides a software control and status interface for the AHB Cache.

It allows software to complete the following actions:

- Enable and disable the cache

- Configure Non-secure permissions

- Configure forceable Write-Through policy

- Read the statistics registers

- Perform manual maintenance operations

- Handle interrupt enables and interrupt statuses

- · Setup and trigger snapshots, when SNAPSHOTTING is configured

#### Access rules

The APB interface only accepts an access that meets all the following conditions:

- The access is privileged.

- The access is a data access.

- The address is aligned.

- Writes have all strobe bits set.

An access that does not meet the preceding conditions is considered a failed APB access. The cache responds to failed APB accesses as follows:

- Read accesses return zero.

- Writes accesses are ignored.

If the **apb\_violation\_resp** is set to HIGH, the AHB Cache responds with errors to failed APB accesses by asserting **pslverr**. For more information, see the *AMBA*<sup>®</sup> *APB Protocol Specification Version 2.0, issue C.*

The APB interface is security aware. Each register and individual bits have security attributes as described in the *Chapter 4 Programmers model* on page 4-44.

#### Table 2-2 Secure and Non-secure accesses

| Access Type                                                                                                            | Permissions                                                                                                                                                                                                                                                         |  |

|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Secure accesses Secure accesses can access all registers and fields, including registers and fields marked as Non-secu |                                                                                                                                                                                                                                                                     |  |

| Non-secure<br>accesses                                                                                                 | Non-secure accesses can only access Non-secure registers and fields. Attempts to access Secure information are ignored: <i>Reads As Zero, Writes Ignored</i> (RAZ/WI) or <b>pslverr</b> HIGH, depending on <b>apb_violation_resp</b> . No interrupts are triggered. |  |

|                                                                                                                        | Note                                                                                                                                                                                                                                                                |  |

|                                                                                                                        | You can configure some Non-secure access permissions using the CTRL register.                                                                                                                                                                                       |  |

|                                                                                                                        |                                                                                                                                                                                                                                                                     |  |

#### **Configuring Non-secure access permissions**

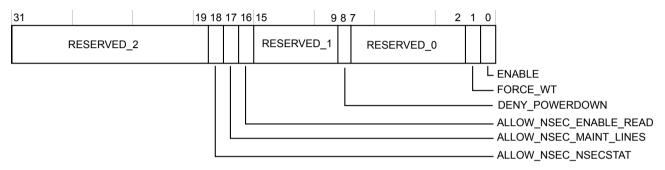

Only Secure accesses can configure the Non-secure access permission registers. You can configure the CTRL register so that Non-secure accesses are allowed to perform the following actions:

- Checking if the cache is enabled

- Reading Non-secure statistics registers

- · Triggering some Non-secure line maintenance features

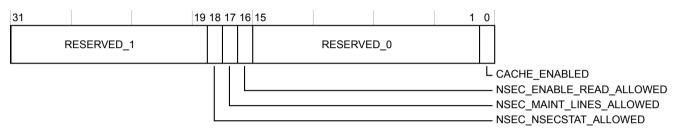

For more information, see 4.4.2 CTRL, control register on page 4-54. Non-secure software can read the NSEC\_ACCESS register to see which information and features it can access. For more information, see 4.4.3 NSEC\_ACCESS, Non-secure access information register on page 4-56.

2 Interfaces 2.4 Interrupts

# 2.4 Interrupts

The AHB Cache has two interrupt signals: one for Secure and one for Non-secure interrupt sources.

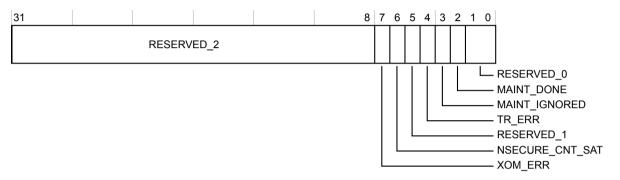

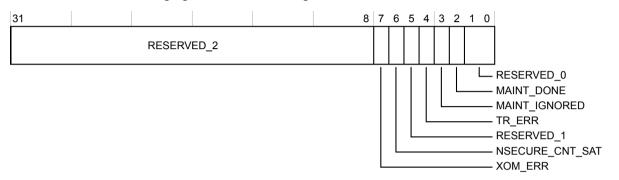

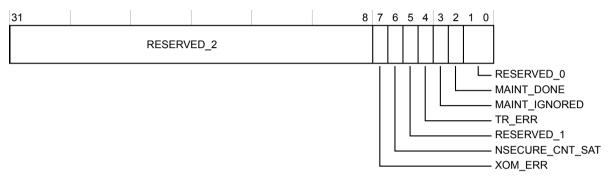

The AHB Cache can generate interrupts for the following events:

- Maintenance finished

- A maintenance request being ignored

- Interface errors on the AHB Master interface

- Saturation of the statistics counters.

- The AHB Cache being either enabled or disabled

- Access violations

----- Note -----

Access violations can be triggered by bus masters that are able to generate speculative accesses.

The following table lists the interrupt signals used by the AHB Cache.

#### Table 2-3 Interrupt signals

| Signal   | Description          |  |

|----------|----------------------|--|

| sec_irq  | Secure interrupt     |  |

| nseq_irq | Non-secure interrupt |  |

Each interrupt has a set of associated registers. If an interrupt source is not enabled, its status register is still set as normal, but it does not contribute to the interrupt signal. Two associated information registers help diagnose the source of the interrupt generated by a transfer error. For interrupt register descriptions, see from section 4.4.7 SECIRQSTAT, Secure interrupt request status register on page 4-60 to section 4.4.16 NSECIRQINFO2, Non-secure transfer error information register 2 on page 4-69 of the Chapter 4 Programmers model on page 4-44.

#### **Related references**

A.6 System interface signals on page Appx-A-125

# 2.5 Low-Power Interface

The AHB Cache has two LPI Q-Channel interfaces to support low-power applications: one for clock and one for power management.

For a description of the signals that are used by the LPI Q-Channel, see *A.2 LPI signals* on page Appx-A-119.

This section contains the following subsections:

- 2.5.1 Dirty status indicator on page 2-31.

- 2.5.2 Clock LPI on page 2-31.

- 2.5.3 Power LPI on page 2-31.

- 2.5.4 Quiescent state on page 2-32.

#### 2.5.1 Dirty status indicator

The AHB Cache uses a simplified model to track the overall dirty status of the cache.

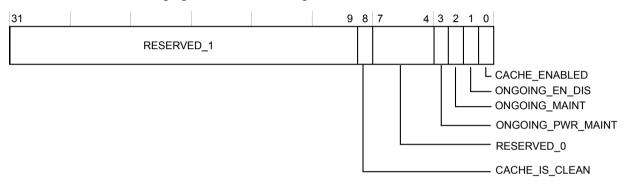

The simplified model does not track the actual dirty status of individual lines. Instead, it reports if there is potentially any dirty data in the cache, using the CACHE\_IS\_CLEAN bit in the MAINT\_STATUS register. For more information, see 4.4.6 MAINT\_STATUS, maintenance status for the cache register on page 4-59.

Any write to an allocated or soon-to-be allocated cache line sets the dirty status indicator. Once set, this bit remains set and is only cleared by a completed clean all, invalidate all, or clean and invalidate all cache maintenance operation (automatic or manual).

Therefore the AHB Cache can report a dirty status, even if all lines are clean. If the AHB Cache reports a clean status, it guarantees that the cache is clean.

#### 2.5.2 Clock LPI

The clock LPI module signals activity on the AHB Cache and responds to incoming quiescence requests.

The clock LPI module is active and denies quiescence requests in the following situations:

- There is activity on the AHB or APB interface.

- An internal operation (for example, maintenance) is ongoing.

- There is activity on the power Q-Channel.

Otherwise the quiescence request is accepted and the response is synchronized with pcklen.

------ Note

When the AHB Cache is in a clock quiescent state, it can asynchronously request clk for itself.

#### **Related references**

A.2 LPI signals on page Appx-A-119

#### 2.5.3 Power LPI

The power LPI module responds to incoming quiescence requests.

The power LPI module is active and denies quiescence requests in the following situations:

- There is activity on the AHB or APB interfaces.

- An internal operation, for example, maintenance is ongoing.

- There is any outstanding interrupt.

- The DENY\_POWERDOWN bit in the CTRL register is set.

Otherwise the request is accepted and the response is synchronized with pcklen.

—— Note —

When the AHB Cache is in power and clock quiescent state, it cannot asynchronously request power for itself.

When the clock LPI module is in a quiescent state, the power LPI module does not respond to requests or update **pwr\_qactive**. Instead, the power LPI module waits for the clock request to be granted.

By default, the AHB Cache runs typical maintenance tasks automatically, see 3.3.7 Automatic maintenance features on page 3-39.

— Note —

By default, the AHB Cache automatically cleans all cache lines before accepting a quiescence request. However, it is possible to disable automatic cache maintenance through the configuration input, **dis\_pwr\_down\_maint**. We recommend that the cache is cleaned before it enters any retention state, unless optimization requirements demand otherwise.

The AHB Cache does not monitor dirty cache lines for activity reporting.

When the AHB Cache receives a quiescence request, it checks the cache activity and status:

- If the cache status is clean and the cache otherwise idle, then it accepts the quiescence request.

- If the cache status is dirty but otherwise idle, it starts a clean all maintenance process. The AHB Cache delays the response and only denies the request if a dirty line is actually found in the cache memory during the maintenance operation. If no dirty line was found and the maintenance operation is completed, the AHB Cache accepts the request.

Quiescence requests are denied until the powerdown maintenance is completed. The AHB Cache aborts the powerdown maintenance process, if it receives new transfer on the AHB Slave interface.

Before requesting quiescence again, the software can check the MAINT\_STATUS register to see if the cache is clean. For more information, see 4.4.6 MAINT\_STATUS, maintenance status for the cache register on page 4-59.

#### **Related references**

A.2 LPI signals on page Appx-A-119

#### 2.5.4 Quiescent state

The quiescent state affects the way that the AHB Cache processes transactions on its AHB slave interface.

The AHB Cache is not intended to be on the power, reset, or clock domain border with its AHB or APB interfaces.

By default, the AHB Cache is not expected to receive a transaction on the AHB slave interface while in quiescent state.

If an access is received while the cache is in a quiescent state, the access is stalled while the AHB Cache is wakened. The AHB address phase cannot be stalled according to the *Arm*<sup>®</sup> *AMBA*<sup>®</sup> *5 AHB Protocol Specification, issue B.b.* However, the Q-Channel handshakes might not have finished yet, while the AHB Cache might already have stable power and clock. Therefore, the AHB slave interface buffers the address phase of the access to avoid data loss if possible.

If the AHB Cache is powered off after the AHB slave interface has buffered the address phase of the access, the buffered address phase is lost. The transfer is completed with the isolation values of the data phase signals.

If the cache is not reset after entering quiescent state, but returned to functional state instead, then the cache enable status remains unchanged. This process takes place in, for example, retention states. The RAM content is still valid and the previously enabled cache continues to function.

# *Related references A.2 LPI signals* on page Appx-A-119

# Chapter 3 **Operation**

This chapter describes the operation of the AHB Cache.

It contains the following sections:

- *3.1 Basic operations* on page 3-35.

- 3.2 Performance monitoring on page 3-37.

- *3.3 Maintenance* on page 3-38.

## 3.1 Basic operations

This section describes some of the basic operations performed by the AHB Cache.

This section contains the following subsections:

- 3.1.1 Cache enable on page 3-35.

- 3.1.2 Cache disable on page 3-35.

- *3.1.3 Lookup* on page 3-35.

- *3.1.4 Linefill* on page 3-36.

- *3.1.5 Eviction* on page 3-36.

#### 3.1.1 Cache enable

The AHB Cache must be enabled to start caching accesses. You can enable the AHB Cache using either software or hardware.

Software can enable the cache by setting the ENABLE field of the CTRL register using the APB configuration interface. For more information about using software to enable the AHB Cache, see *5.1 Enable the AHB Cache by using software* on page 5-96.

Hardware can also enable the cache by setting the configuration port **power\_on\_enable**, which triggers the cache to enable when the LPI interfaces reach the QRUN state for the first time after reset.

If cache enable maintenance is turned on, the AHB Cache runs invalidate all maintenance in the background. When the maintenance is completed, the cache is enabled. For more information about cache enable maintenance, see *Cache enable maintenance* on page 3-41.

If cache enable maintenance is turned off by setting the configuration port **dis\_cache\_en\_maint** and it is unclear whether the cache memory is still valid, the software must invalidate the cache before enabling it. For more information about invalidate all maintenance, see *3.3.4 Invalidate all maintenance* on page 3-39.

#### **Related references**

4.4.2 CTRL, control register on page 4-54

#### 3.1.2 Cache disable

Software can disable the AHB Cache using the APB configuration interface.

For more information, see *5.2 Disable the AHB Cache using software* on page 5-100. If cache disable maintenance is turned on, the AHB Cache starts clean all maintenance. After the maintenance is completed, the AHB Cache is disabled. For more information about cache disable maintenance, see *Cache disable maintenance* on page 3-42.

If cache disable maintenance is turned off by setting the configuration port **dis\_cache\_dis\_maint**, then the software is responsible for cleaning the cache before the cache is disabled to avoid data loss. For more information, see *3.3.2 Clean all maintenance* on page 3-38.

*Related references* 4.4.2 *CTRL, control register* on page 4-54

#### 3.1.3 Lookup

The AHB Cache looks up accesses that are marked as cacheable.

The AHB Cache performs a lookup in the four tag RAMs and in the internal buffers. The result of a lookup can be either hit or miss.

#### Table 3-1 Cache hit and cache miss

| Lookup<br>result | Description                                                                                                                                                                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hit              | A cache hit means that the data is already in the cache or being filled. The AHB Cache responds to the access without added latency, unless the destination cache line is being filled and the given word has not yet been received.                                                                                |

| Miss             | <ul> <li>A cache miss means that the data is not in the cache:</li> <li>Allocate miss accesses trigger a linefill.</li> <li>No-allocate miss accesses are forwarded.</li> <li>Cache miss accesses might affect latency. For more information, see <i>Table 2-1 Normal access latencies</i> on page 2-25.</li> </ul> |

#### 3.1.4 Linefill

A linefill is a read Burst transaction that takes place when a new cache line must be brought into the cache from the external memory.

The linefill results in an entire 32-byte cache line being stored in the internal buffers where it can be looked up. If the target cache set is full, the cache evicts a cache line.

**Related concepts** Linefill error and data loss on page 2-27

#### 3.1.5 Eviction

The eviction process creates space for new data in the AHB Cache.

Cacheable accesses, which have addresses with the same index, can be stored in one of the four lines of the corresponding set.

The eviction process takes place when the corresponding set is full and a new line needs to be cached with the same index.

One of the previously stored cache lines is randomly selected and evicted to make room for a new line. After eviction, the cache line is invalidated in the cache memory. If the evicted cache line was dirty, it is also written back to main memory after eviction.

# 3.2 Performance monitoring

The AHB Cache provides statistical counters to record cache hits and misses. Non-cacheable accesses and debug transactions are not counted.

The statistical counters are available in every configuration. Four counters are available for performance monitoring. Secure and Non-secure hits and misses are counted separately on dedicated counters.

#### Secure software

By default, the counters are only visible to Secure software.

#### Non-secure software

Secure software can enable Non-secure software to access the Non-secure counters. For more information, see *4.4.2 CTRL, control register* on page 4-54. However, Non-secure software cannot access the Secure counters.

#### 3.2.1 Snapshotting

The AHB Cache can support snapshots, which are enabled by a hardware configuration, 'SNAPSHOTTING' in the HWPARAMS register. By using the snapshotting functionality, you can capture all four statistical counters into capture registers at the same time.

When enabled, two triggers are provided:

- A hardware trigger as an input port

- A software trigger as a register bit

- Note

The AHB Cache uses the **pmsnapshotreq** input port, which serves as a hardware trigger, to ensure that gathered statistics are captured at the same time across multiple components.

If there is power and the clock is running, the **pmsnapshotreq** sample port is sampled and snapshots are taken, even when the cache is in clock and power quiescence.

#### Table 3-2 Snapshotting registers

| Name   | Summary                                                                                                                                                                                                                                   | Description                                               |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| PMSSCR | Software can trigger a snapshot by writing 1 to this register.                                                                                                                                                                            | 4.4.28 PMSSCR, PMU snapshot capture register on page 4-81 |

| PMSSSR | The PMSSSR register allows software to check that a capture occurred. The value 1 means no capture has occurred. The value is set to 0 by hardware or software trigger when a snapshot is taken. The value is cleared to 1 by reset only. | 4.4.27 PMSSSR, PMU snapshot status register on page 4-80  |

| PMSSRR | Setting the PMSSRR register makes each snapshot automatically reset the counters on capture, so that the next snapshot does not contain data from an already captured interval.                                                           | 4.4.29 PMSSRR, PMU snapshot reset register on page 4-82   |

For more information, see the Arm<sup>®</sup> CoreLink<sup>™</sup> AHB Cache Configuration and Integration Manual.

# 3.3 Maintenance

The AHB Cache receives requests on the APB interface that can either directly or indirectly trigger a maintenance operation. The APB interface responds to those requests using the APB status registers and interrupts.

Quiescence requests received through the Q-Channel interface can also trigger a maintenance operation. The AHB Cache responds to these requests depending on whether there is any maintenance already ongoing. The AHB Cache also has a dedicated output port, **pwr\_maintenance**, to track the status of powerdown maintenance.

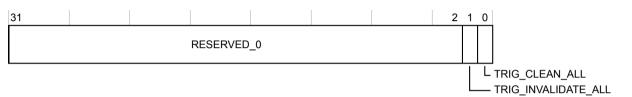

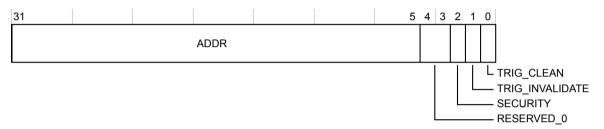

The AHB Cache initiates automatic maintenance activities, see 3.3.7 Automatic maintenance features on page 3-39. Software can initiate manual maintenance, see 3.3.8 Manual maintenance on page 3-43.

All maintenance delays subsequent operations on the cache until the maintenance is complete.

The AHB Cache performs the following maintenance:

- Clean by address

- Clean all

- Invalidate by address

- Invalidate all

- Clean and invalidate by address

- Clean and invalidate all

This section contains the following subsections:

- 3.3.1 Clean by address maintenance on page 3-38.

- 3.3.2 Clean all maintenance on page 3-38.

- 3.3.3 Invalidate by address maintenance on page 3-38.

- 3.3.4 Invalidate all maintenance on page 3-39.

- 3.3.5 Clean and invalidate by address maintenance on page 3-39.

- 3.3.6 Clean and invalidate all maintenance on page 3-39.

- *3.3.7 Automatic maintenance features* on page 3-39.

- *3.3.8 Manual maintenance* on page 3-43.

- 3.3.9 power on enable on page 3-43.

#### 3.3.1 Clean by address maintenance

Clean by address maintenance performs a lookup for a cache line with a selected address.

If the lookup results in a hit and the cache line is dirty, then the AHB Cache writes it back to main memory. The dirty status of the cache line is cleared in the process.

### 3.3.2 Clean all maintenance

Clean all maintenance walks through all cache lines and writes back all dirty cache lines.

The dirty status of each line is cleared during the clean all maintenance process. After clean all maintenance is completed, the cache status is set to clean. For more information, see *4.4.6 MAINT\_STATUS, maintenance status for the cache register* on page 4-59.

#### **Related concepts**

*Powerdown maintenance* on page 3-41 *Cache disable maintenance* on page 3-42

### 3.3.3 Invalidate by address maintenance

Invalidate by address maintenance performs a lookup of a cache line with a specific address. If the lookup results in a hit, then the AHB Cache invalidates the selected cache line.

####

Only Secure software can perform invalidate by address maintenance. Invalidating a dirty cache line can cause data loss.

#### 3.3.4 Invalidate all maintenance

Invalidate all maintenance walks through all cache lines and invalidates them.

#### ——— Caution —

Only Secure software can perform invalidate all maintenance. Invalidating a dirty cache line can cause data loss.

Invalidate all maintenance usually delays subsequent operations on the cache until the maintenance is complete. However, when the cache is being enabled, automatic invalidate all maintenance does not stall the AHB interface.

Invalidate all is the only type of maintenance that is allowed when the AHB Cache is disabled. If invalidate all takes place when the cache is disabled, it also does not stall the AHB interface.

#### **Related concepts**

Cache enable maintenance on page 3-41

#### 3.3.5 Clean and invalidate by address maintenance

The APB interface can initiate clean and invalidate maintenance by address.

Clean and invalidate by address maintenance combines the *3.3.1 Clean by address maintenance* on page 3-38 and *3.3.3 Invalidate by address maintenance* on page 3-38. The address is looked up in the cache. Depending on the result of the lookup, the AHB Cache performs a corresponding action:

- If the lookup results in a hit and the address is dirty, then the address is cleaned, and then invalidated.

- If the lookup results in a hit and the address is clean, the address is invalidated.

- If the lookup results in a miss, the maintenance is complete and no further action is taken.

#### 3.3.6 Clean and invalidate all maintenance

The APB interface can initiate clean and invalidate all maintenance for the entire cache.

\_\_\_\_\_ Note \_\_\_\_

Only Secure software can perform clean and invalidate all maintenance. Invalidating a dirty cache line can cause data loss.

Clean and invalidate all maintenance combines 3.3.2 Clean all maintenance on page 3-38 and 3.3.4 Invalidate all maintenance on page 3-39. The maintenance cycles through all the lines in the cache. Depending on the cache line status, the AHB Cache performs a corresponding action:

- If the line is valid and dirty, then it is cleaned, and then invalidated.

- If the line is valid and clean, it is invalidated.

#### 3.3.7 Automatic maintenance features

Automatic maintenance operations are triggered by default in some situations.

Automatic maintenance operations do not generate a MAINT\_DONE interrupt, but they do generate error interrupts if errors occur.

#### Configurable automatic maintenance

Configurable automatic maintenance is triggered by default, when one of the following conditions is met:

- The AHB Cache is enabled or disabled.

- There is a quiescence request.

The configurable automatic maintenance processes are described in the following table.

#### Table 3-3 Configurable automatic maintenance

| Trigger                                                      | Maintenance    | Condition                                                   |

|--------------------------------------------------------------|----------------|-------------------------------------------------------------|

| Quiescence request (while the AHB Cache is enabled and idle) | Clean all      | When the <b>dis_pwr_down_maint</b> signal is not asserted.  |

| Enabling the cache                                           | Invalidate all | When the <b>dis_cache_en_maint</b> signal is not asserted.  |

| Disabling the cache                                          | Clean all      | When the <b>dis_cache_dis_maint</b> signal is not asserted. |

You can change the default automatic maintenance settings using *Maintenance configuration input ports* on page 3-40.

#### Automatic maintenance to maintain consistency

Automatic maintenance is triggered to maintain consistency in the following situations:

- An AHB locked access hits the cache.

- An AHB Write-Access hits an XOM line in the AHB Cache.

- An AHB exclusive access hits the cache.

The following table describes automatic maintenance triggered for consistency.

#### Table 3-4 Automatic maintenance to maintain consistency

| Trigger                                                | Maintenance                                         | Condition                      |

|--------------------------------------------------------|-----------------------------------------------------|--------------------------------|

| An AHB exclusive access hits the AHB Cache.            | Clean and invalidate by address                     | -                              |

| An AHB Write-Access hits an XOM line in the AHB Cache. | Invalidate by address (an XOM line cannot be dirty) | When XOM support is configured |

| An AHB locked access hits the AHB Cache.               | Clean and invalidate by address                     | -                              |

#### Maintenance configuration input ports

To change the default automatic maintenance settings, use the configuration input ports.

#### Table 3-5 Maintenance configuration input ports

| Input port          | Maintenance process                           | Description                                                                                                                                                                                                                                                                                                                                                    |

|---------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| dis_pwr_down_maint  | Powerdown maintenance<br>on page 3-41         | Configuration input port to disable automatic clean at a power Q-Channel quiescence request. Sampled when the AHB Cache is preparing for powerdown maintenance. This signal must be stable until the cache has finished preparing for powerdown. The cache indicates it has finished preparing for powerdown by deasserting the <b>pwr_maintenance</b> signal. |

| dis_cache_en_maint  | <i>Cache enable maintenance</i> on page 3-41  | Configuration input port to disable automatic maintenance (invalidate all) at<br>enabling the cache. Sampled while the AHB Cache is preparing for cache<br>enable maintenance. This signal must be stable until the AHB Cache is enabled.                                                                                                                      |

| dis_cache_dis_maint | <i>Cache disable maintenance</i> on page 3-42 | Configuration input port to disable automatic maintenance (clean all) at disabling the cache. Sampled when the AHB Cache is preparing for cache disable maintenance. This signal must be stable until the AHB Cache is disabled.                                                                                                                               |

#### — Note —

Software can check whether the automatic maintenance is enabled or disabled by reading the corresponding bits in the HWPARAMS register. For more information, see *4.4.1 HWPARAMS*, *hardware parameter register* on page 4-52.

#### **Powerdown maintenance**

Powerdown maintenance takes place whenever a quiescence request is received through the power Q-Channel interface.

When the **dis\_pwr\_down\_maint** input port is asserted, a power Q-Channel quiescence request does not trigger an automatic clean. You can use this configuration when the cache is not to be powered down or the cache memory contents are preserved through retention.

The **pwr\_maintenance** output status port is asserted while the powerdown maintenance is ongoing. While powerdown maintenance is disabled, this status port might still be asserted for a few clock cycles while preparing internally for powerdown.

#### Powerdown maintenance on

The AHB Cache checks if the cache is clean whenever a quiescence request is received through the power Q-Channel interface. For more information, see 2.5.1 Dirty status indicator on page 2-31.

If the cache status is clean and otherwise idle, then it accepts the quiescence request.

If the cache status is dirty but otherwise idle, it starts a clean all maintenance process.

The AHB Cache delays the response and only denies the request if a dirty line is actually found in the cache memory during the maintenance operation. If no dirty line was found and the maintenance operation is completed, the AHB Cache accepts the request.

While the maintenance is in progress, the cache reports activity on pwr\_qactive signal.

Any activity on the AHB Slave interface aborts this type of maintenance.

When the clean is completed, the module stops reporting activity on the **pwr\_qactive** signal, so a consecutive quiescence request is accepted. If a Write-Back access makes the cache dirty again, then another clean all maintenance starts at the next quiescence request.

#### Powerdown maintenance off

The AHB Cache does not check if the cache is clean but accepts the quiescence request if the cache is idle.

------ Caution --------

If automatic maintenance is turned off, care must be taken to avoid data loss in Write-Back memory regions, when powering down the AHB Cache.

#### **Related concepts**

3.3.2 Clean all maintenance on page 3-38

#### Cache enable maintenance

When cache enable maintenance is on, cache enable maintenance is triggered automatically when the cache is enabled.

For more information, see 3.1.1 Cache enable on page 3-35.

#### Cache enable maintenance on

When an enable command is received, the AHB Cache starts a sequence similar to *3.3.4 Invalidate all maintenance* on page 3-39.

Traffic is not stalled on the AHB Slave interface, since caching is disabled and therefore no lookup would use the RAM interfaces. While the invalidation is in progress, the cache stays disabled and forwards all transactions. This process takes place so that the AHB Cache RAM is initialized to a known empty state. When the invalidation is completed, caching is enabled and the next cacheable nonsequential transaction is looked up.

\_\_\_\_\_ Note \_\_\_\_\_

If the configuration port **power\_on\_enable** is set, cache enable maintenance can also be triggered by hardware. For more information, see *A.8 Configuration input ports* on page Appx-A-128.

#### Cache enable maintenance off

When cache enable maintenance is off and the cache is enabled, the AHB Cache immediately looks up the next nonsequential transaction, without regard for the actual content of the cache memory. If the cache memory contents are not valid, the related data is corrupted.

—— Caution ——

When enabling the AHB Cache with cache enable maintenance turned off, you must take care to avoid memory corruption.

#### **Related concepts**

3.3.4 Invalidate all maintenance on page 3-39

#### Cache disable maintenance

When cache disable maintenance is on, cache disable maintenance is triggered automatically when the cache is disabled.

For more information, see 3.1.2 Cache disable on page 3-35.

#### Cache disable maintenance on

When the AHB Cache is disabled, it starts clean all maintenance when a disable command is received through the APB software programming interface. Before starting the clean maintenance, all traffic to the AHB Slave interface is stalled for the next nonsequential transaction. While the clean is in progress, the AHB Slave interface remains stalled. When the clean is completed, then the cache is disabled, the AHB Slave interface is released and upcoming transactions are forwarded.

#### Cache disable maintenance off

When the cache disable maintenance is off, the cache disable command immediately disables the cache. The AHB Cache does not look up the next nonsequential transaction.

—— Caution ———

When disabling the AHB Cache with cache disable maintenance turned off, you must make sure that there is no dirty data in the cache memory. If the dirty data is not cleaned and the cache is disabled, then the dirty data is no longer visible to the system.

We do not expect the software to send cacheable write transactions while trying to disable the cache with manual maintenance. However, when cache disable automatic maintenance is turned off, we recommend that the cache disable command follows a clean all command. We recommend that the cache disable command is issued without waiting for the maintenance to complete or generate an interrupt. If the cache disable command is received while the clean all maintenance is still running, then the cache executes the disable command before it would service any possible pending transactions.

#### **Related concepts**

3.3.2 Clean all maintenance on page 3-38

#### 3.3.8 Manual maintenance

Software can initiate manual maintenance activities including clean and invalidate.

#### Secure manual maintenance

Secure software can manually start any all-cache or by-address maintenance activities in the AHB Cache. It can also enable Non-secure maintenance.

#### Non-secure manual maintenance

Secure software can enable Non-secure maintenance.

Non-secure maintenance allows Non-secure software to start maintenance on Non-secure addresses. Non-secure software cannot start maintenance on Secure addresses, and it cannot perform any all-cache maintenance. It also cannot start invalidate-only maintenance.

#### 3.3.9 power\_on\_enable

You can use the power\_on\_enable input configuration port to allow hardware to enable the AHB Cache.

The **power\_on\_enable** port is sampled when the cache is directed to running state on its power LPI Q-Channel interface at the first time after reset. When triggered, this feature starts the normal cache enable process. For more information, see *4.4.1 HWPARAMS, hardware parameter register* on page 4-52.

If enable maintenance is disabled through the **dis\_cache\_en\_maint** configuration port, then the related maintenance is not performed and the cache is enabled immediately.

Subsequent interface transitions have no effect on power\_on\_enable until the cache is reset.

Forcing Write-Through can be affected by **power\_on\_enable**. For more information, see 4.4.2 CTRL, control register on page 4-54.

# Chapter 4 Programmers model

This chapter describes the functionality of the AHB Cache from a programming perspective.

It contains the following sections:

- 4.1 About the programmers model on page 4-45.

- 4.2 Programming considerations on page 4-46.

- 4.3 Register summary on page 4-47.

- 4.4 Register descriptions on page 4-51.

# 4.1 About the programmers model

This section describes the functions and programmers model of the AHB Cache.

When using the programmers model, adhere to the following guidelines:

- Do not attempt to access reserved or unused address locations. Attempting to access these locations can result in unpredictable behavior.

- Unless otherwise stated in the accompanying text:

- Do not modify undefined register bits.

- Ignore undefined register bits on reads.

- Unless otherwise specified, all register bits are reset to a logic 0 by a system or power up reset.

The following describes the access type:

# 4.2 **Programming considerations**

To avoid data leaks or corruption when programming the AHB Cache, adhere to the following guidance.

#### ——— Caution ——

When the memory map needs to be changed (for example, the *Security Attribution Unit* (SAU) is reconfigured), adhere to the following guidance:

- If the cache content is dirty, it should be cleaned before the memory map is changed.

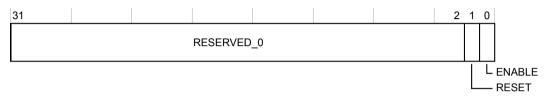

- The cache should stay disabled while the change is in progress.