# ARM® Power State Coordination Interface Platform Design Document

**Non-Confidential**

# **Power State Coordination Interface (PSCI)**

#### System Software on ARM specification

Copyright © 2012, 2013, 2015, 2017 ARM Limited or its affiliates. All rights reserved.

#### Release information

Table 1 below lists the changes made to this document.

#### **Table 1 Change history**

| Date            | Issue | Confidentiality  | Change                                            |

|-----------------|-------|------------------|---------------------------------------------------|

| 13 August 2012  | Α     | Non-Confidential | First release                                     |

| 24 June 2013    | В     | Non-Confidential | Second release, PSCI version 0.2                  |

| 25 Jun 2013     | B.b   | Non-Confidential | Removed inappropriate watermark, PSCI version 0.2 |

| 30 January 2015 | С     | Non-Confidential | PSCI 1.0 release, and errata fix for PSCI 0.2     |

| 21 April 2017   | D     | Non-Confidential | PSCI 1.1. release                                 |

#### **Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of ARM Limited ("ARM"). No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, ARM makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version shall prevail.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to ARM's customers is not intended to create or refer to any partnership relationship with any other company. ARM may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any signed written agreement specifically covering this document with ARM, then the signed written agreement prevails over and supersedes the conflicting provisions of these terms.

Words and logos marked with ® or ™ are registered trademarks or trademarks of ARM Limited or its affiliates in the EU and/or elsewhere. All rights reserved. Other brands and names mentioned in this

document may be the trademarks of their respective owners. You must follow the ARM trademark usage guidelines http://www.arm.com/about/trademarks/guidelines/index.php.

Copyright © 2012, 2013, 2015, 2017 ARM Limited or its affiliates. All rights reserved. ARM Limited. Company 02557590 registered in England. 110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20327

In this document, where the term ARM is used to refer to the company it means "ARM or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### **Web Address**

http://www.arm.com

# Table of Contents

| 1 | Introduction                                                  |    |

|---|---------------------------------------------------------------|----|

|   | 1.1 Additional reading 1.1 Feedback                           |    |

| 2 | Background                                                    | 8  |

| 3 | Assumptions and recommendations                               | 10 |

|   | 3.1 PSCI intended use                                         |    |

|   | 3.2 Exception levels, the ARMv7 privilege levels, and highest |    |

|   | privilegeARM has a deviate as                                 |    |

|   | 3.3 Software stacks on ARM-based systems                      |    |

|   | 3.5 Secure world software and power management                |    |

|   | 3.6 Virtualization and core power policy                      |    |

| 4 | PSCI Use Cases and Use Case Requirements                      | 16 |

|   | 4.1 Idle management                                           |    |

|   | 4.2 Power state system topologies and coordination            |    |

|   | 4.3 CPU hotplug and secondary CPU boot                        | 23 |

|   | 4.4 System shutdown, reset and suspend                        | 24 |

| 5 | Functions                                                     | 26 |

|   | 5.1 Function prototypes                                       | 26 |

|   | 5.2 Arguments and return values in PSCI                       |    |

|   | 5.3 PSCI_VERSION                                              |    |

|   | 5.4 CPU_SUSPEND                                               |    |

|   | 5.6 CPU_ON                                                    |    |

|   | 5.7 AFFINITY_INFO                                             |    |

|   | 5.8 MIGRATE                                                   | 56 |

|   | 5.9 MIGRATE_INFO_TYPE and MIGRATE_INFO_UP_CPU                 |    |

|   | 5.10SYSTEM_OFF                                                |    |

|   | 5.11SYSTEM_RESET<br>5.12SYSTEM RESET2                         |    |

|   | 5.13MEM PROTECT                                               |    |

|   | 5.14MEM_PROTECT_CHECK_RANGE                                   |    |

|   | 5.15PSCI_FEATURES                                             | 64 |

|   | 5.16CPU_FREEZE                                                |    |

|   | 5.17CPU_DEFAULT_SUSPEND                                       |    |

|   | 5.18NODE_HW_STATE<br>5.19SYSTEM_SUSPEND                       |    |

|   | 5.20PSCI_SET_SUSPEND_MODE                                     |    |

|   | 5.21 PSCI_STAT_RESIDENCY/COUNT                                | 72 |

| 6 | Additional Implementation Details                             |    |

| - | 6.1 PSCI call flows                                           |    |

|   | 6.2 OS and Implementation View of Cores State                 |    |

|   | 6.3 Races in OS-initiated mode                                | 79 |

|   | 6.4 Initial state after CPU_ON, CPU_SUSPEND | 84         |

|---|---------------------------------------------|------------|

|   | 6.5 Recommended StateID Encoding            |            |

|   | 6.6 Implementation CPU_ON/CPU_OFF races     | 91         |

|   | 6.7 Discoverability                         |            |

|   | 6.8 Preserving the execution context        |            |

|   | 6.9 Compliance with the PSCI Specification  | 99         |

|   |                                             |            |

| 7 | History                                     | 102        |

| 7 | -                                           |            |

| 7 | 7.1 Changes between PSClv1.1 and PSClv1.0   | 102        |

| 7 | -                                           | 102<br>102 |

#### 1 Introduction

This document defines a standard interface for power management that can be used by OS vendors for supervisory software working at different levels of privilege on an ARM device. Rich operating systems like Linux and Windows, hypervisors, secure firmware, and Trusted OS implementations must interoperate when power is being managed. The aim of this standard is to ease the integration between supervisory software from different vendors working at different privilege levels.

The interface is aimed at the generalization of code in the following power management scenarios:

- Core idle management.

- Dynamic addition and removal of cores, and secondary core boot.

- System shutdown and reset.

The interface does not cover *Dynamic Voltage and Frequency Scaling* (DVFS) or device power management (for example, management of peripherals such as GPUs).

The interface is designed so that it can work in conjunction with hardware discovery technologies such as *Advanced Configuration and Power Interface* (ACPI) and *Flattened Device Tree* (FDT). It is not a replacement for ACPI or FDT.

This document describes PSCI versions 1.1, 1.0, and 0.2. For PSCI 0.2, the document provides an errata fix update. The PSCI 0.2 erratum applies to a single function and is described in section 5.1.7.

The document is arranged into the following sections:

- Section 1 provides this introduction and references.

- Section 2-4 provide background materials, including:

- Intended uses of PSCI.

- Background definitions of power state terms.

- Methods by which PSCI requests are made.

- ARM architecture background.

- Section 5 provides the main description of the PSCI functions.

- Section 6 provides additional implementation details.

- Sections 7 and 8 provide a revision history of the PSCI specification and a glossary.

Readers already familiar with PSCI can skip straight to section 5.

## 1.1 Additional reading

This section lists publications by ARM and by third parties.

See Infocenter, <a href="http://infocenter.arm.com">http://infocenter.arm.com</a>, and <a href="http://developer.arm.com">http://developer.arm.com</a> for access to ARM documentation.

#### 1.1.1 ARM publications

The following documents contain information that is relevant to this document:

- [1] ARM Architecture Reference Manual ARMv7-A and ARMv7-R edition (ARM DDI 0406).

- [2] Embedded Trace Macrocell Architecture Specification (ARM IHI 0014).

- [3] Program Flow Trace Architecture Specification (ARM IHI 0035).

- [4] SMC Calling Conventions (ARM DEN 0028).

- [5] ARM Architecture Reference Manual ARMv8, for ARMv8-A architecture profile (ARM DDI 0487).

- [6] Advanced Configuration and Power Interface Specification.

See http://www.uefi.org/sites/default/files/resources/ACPI 6 1.pdf.

- [7] PSCI device tree definition.

https://www.kernel.org/doc/Documentation/devicetree/bindings/arm/psci

.txt.

- [8] ARM Trusted Firmware.

See https://github.com/ARM-software/arm-trusted-firmware

- [9] Power Control System Architecture Specification (ARM DEN 0050).

#### 1.1 Feedback

ARM welcomes feedback on its documentation.

#### 1.1.1 Feedback on this manual

If you have comments on the content of this manual, send an e-mail to errata@arm.com. Provide:

- The title.

- The number, ARM DEN 0022D.

- The page numbers to which your comments apply.

- A concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

# 2 Background

Power management aware operating systems dynamically change the power states of cores, balancing the available compute capacity to match the current workload, while striving to use the minimum amount of power. Some of these techniques dynamically switch cores on and off or place them in quiescent states, where they no longer perform computation. This means they consume very little power. The main examples of these techniques are:

**Idle Management:** When the kernel in an OS has no threads to schedule on a core, it places that core into a clock-gated, retention, or even fully power-gated state. However, the core remains available to the OS.

**Hotplug:** Cores are physically switched off when compute demand is low, and then brought back online when it increases. The OS migrates all interrupts and threads away from the cores that are taken offline, and rebalances the load when they are brought back online.

Although it would be simpler to consider the software of an embedded system to be provided by a single vendor, in most situations this is not the case, even when the end device is delivered with fixed functionality. The ARM architecture defines a set of Exception levels [5] that support the required partitioning of the software stack used on a device. Table 2 shows this partitioning and indicates the typical vendor of each level of the stack:

Table 2 Typical partitioning of software on a system that complies with the ARM architecture

| AArch32 state           | AArch64 state     | Stack and typical vendor                                                     |

|-------------------------|-------------------|------------------------------------------------------------------------------|

| Non-secure<br>EL0 (PL0) | Non-secure<br>EL0 | Unprivileged applications, such as applications downloaded from an App Store |

| Non-secure<br>EL1 (PL1) | Non-secure<br>EL1 | Rich OS kernels from, for example,<br>Linux, Microsoft Windows, iOS          |

| Non-secure<br>EL2 (PL2) | Non-secure<br>EL2 | Hypervisors, from vendors such as Citrix, VMWare, or OK-Labs                 |

| Secure EL0<br>(PL0)     | Secure EL0        | Trusted OS applications                                                      |

| Secure EL3<br>(PL1)     | Secure EL1        | Trusted OS kernels from Trusted OS vendors such as Trustonic                 |

| Secure EL3<br>(PL1)     | Secure EL3        | Secure Monitor, executing secure platform firmware provided by Silicon       |

# vendors and OEMs ARM Trusted Firmware

**Note**: AArch32 state is the 32-bit ARMv8 Execution state, and the Execution state used by all ARM processors before ARMv8. In an ARMv7 processor, the Exception levels are implicit, and not identified by the processor documentation. The Virtualization Extensions provide the EL2 functionality, and the Security Extensions provide the EL3 functionality, and within a Security state the *Privilege level* (PL) identifies the Exception level hierarchy. For more information, see section 3.2.

As various operating systems from various different vendors can be present in an ARM system, performing power control requires a method of collaboration. Considering operation in Non-secure state, if a supervisory system that is managing power, whether it is executing at the OS level (EL1) or at hypervisor level (EL2), wants to enter an idle state, power up or power down a core, or reset or shut down the system, supervisory systems at other Exception levels will need to react to the power state change request.

Equally, if the power state of a core is changed by a wakeup event, it might be necessary for supervisory systems running at Exception levels to perform actions such as restoring context. PSCI provides a standard interface definition to support this interoperation and integration across the various supervisory systems. This document defines such an interface, the Power State Coordination Interface, and describes its use for idle, hotplug, shutdown, and reset.

# 3 Assumptions and recommendations

This document defines an API that can be used to coordinate power control among supervisory systems concurrently running on a device. As the following sections explain, the API allows a supervisory system to request cores to be powered up or down, and to request context transfer of secure context from one core to another, which might be needed when dealing with trusted OSs. Throughout the description, the document generally assumes that EL2 and EL3 are both implemented, but also covers other cases.

#### 3.1 PSCI intended use

PSCI has the following intended uses:

- Provides a generic interface that supervisory software can use to manage power in the following situations:

- · Core idle management.

- Dynamic addition of cores to and removal of cores from the system, often referred to as hotplug.

- Secondary core boot.

- Moving trusted OS context from one core to another.

- System shutdown and reset.

- Provides an interface that supervisory software can use in conjunction with Firmware Table (FDT and ACPI) descriptions to support the generalization of power management code.

PSCI does not cover:

- Peripheral idle management. PSCI only applies to idle management of the cores used by the central scheduler of supervisory software.

- Dynamic Voltage and Frequency Scaling. PSCI does not provide interfaces for the management of core clock frequencies on a device.

PSCI does not provide power state representations to supervisory software. However, it is designed so that it can also be used with hardware description technologies such as ACPI or FDT.

# 3.2 Exception levels, the ARMv7 privilege levels, and highest privilege

ARMv8 introduces explicit Exception levels that also define the software execution privilege hierarchy within a Security state. An increase in Exception level, for example from EL0 to EL1, corresponds to an increase in execution privilege.

In ARMv7, the Exception level hierarchy is implicit in the architecture:

The Virtualization Extensions provide the EL2 functionality. This is present only in Non-secure state. • The Security Extensions provide the EL3 functionality, including the support for two Security states. The control features of this functionality are provided by a Monitor mode that is present only in Secure state.

The ARMv7 architecture [1] uses *Privilege levels* (PLs) to describe the software execution privilege hierarchy. Because Monitor mode was defined as a peer of the other Secure state privileged processor modes, this means the ARMv7 privilege levels are asymmetrical between Non-secure state and Secure state, as follows:

- In Non-secure state, the privilege level hierarchy is:

- PL0, unprivileged. Applies to User mode.

- PL1, OS-level privilege. Applies to System, FIQ, IRQ, Supervisor, Abort, and Undefined modes.

- PL2, hypervisor privilege. Applies to Hyp mode.

- In Secure state, the privilege level hierarchy is:

- Secure PL0, unprivileged. Applies only to User mode.

- Secure PL1, Trusted OS, and Monitor level privilege. Applies to System, FIQ, IRQ, Supervisor, Abort, Undefined, and Monitor modes.

In the AArch32 description of execution privilege [5], which applies to both ARMv7 and ARMv8 implementations, the processor modes map to the Exception levels as follows:

- In Non-secure state, the processor modes implemented at each Exception level are:

- EL0: User mode.

- EL1: System, FIQ, IRQ, Supervisor, Abort, and Undefined modes.

- EL2: Hyp mode.

- In Secure state, the processor modes implemented at each Exception level are:

- Secure EL0: User mode.

- EL3: System, FIQ, IRQ, Supervisor, Abort, Undefined, and Monitor modes.

Note: In an ARMv8 implementation, this mapping of the Secure modes applies only when EL3 is using AArch32. When EL3 is using AArch64, Monitor mode is not implemented, and if Secure EL1 is using AArch32 then Secure System, FIQ, IRQ, Supervisor, Abort, and Undefined modes are implemented as part of Secure EL1. For more information see [5].

This document generally uses Exception level terminology. In the document:

References to EL1 and EL0 mean Non-secure EL1 and EL0, unless otherwise indicated. • *Highest privilege* refers to the first implemented Exception level in the following sequence, which runs from highest to lowest: EL3, Secure EL1, EL2, Non-secure EL1.

#### 3.3 Software stacks on ARM-based systems

On a given ARM device there can be a number of supervisory software kernels or privileged software components.

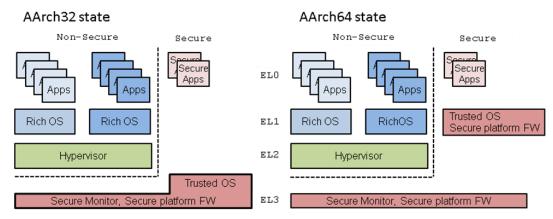

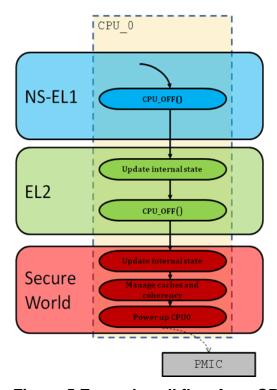

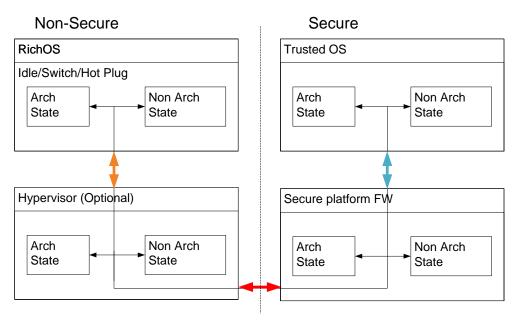

Figure 1 Software Layers of an ARM system

Figure 1 illustrates these various layers. The Normal (Non-secure) world has the following privileged components:

**Rich OS kernels:** Examples include Linux or Windows running in Nonsecure EL1. When running under a hypervisor, the Rich OS kernels can be running as guests or hosts depending on the hypervisor model.

**Hypervisor:** This component runs at EL2, which is always Non-secure. This component, when present and enabled, provides virtualization services to guests running Rich OS kernels.

The Secure world has the following privileged components:

Secure Platform Firmware (SPF): Owned by the silicon vendor and OEM. On an application processor, this firmware layer must be the first thing that runs at boot time. It provides a number of services, including platform initialization, the installation of the Trusted OS, and routing of Secure Monitor Calls. Some calls target the SPF and some target the Trusted OS. SPF can run in EL3 and secure EL1 on ARMv8 systems using AArch64 at EL3. ARM strongly recommends using EL3 for SPF. For ARMv7 systems, or ARMv8 systems using AArch32 at EL3, SPF executes in EL3. The implementation that acts on power management requests issued by the Power State Coordination Interface must reside in the SPF. A reference implementation for secure platform FW is provided by the ARM Trusted Firmware open source project [8].

**Trusted OS:** This provides secure services to the Normal world, and provides a runtime environment for executing secure applications. In AArch32 state Trusted OS software executes in Secure EL3, and in AArch64 state it primarily executes in Secure EL1.

**Note**: The ARM Architecture Reference Manuals [1, 5] define two Security states, Secure and Non-secure, and ARM processor documentation uses these state names. ARM software documentation often refers to these states as Secure and Normal world respectively. This reflects the fact that software normally executes in Non-secure state.

The PSCI specification focuses on the interface between Secure and Normal worlds for power management. It provides a method for issuing power management requests. To deal with the requests, the SPF must include a PSCI implementation. The ARM Trusted Firmware project [8] provides a reference implementation of the PSCI specification.

A PSCI implementation might require communication between the SPF and a Trusted OS. Currently, how this communication is handled is specific to individual vendors. Therefore this communication is IMPLEMENTATION DEFINED.

Although the PSCI specification focuses on power management requests between Secure and Normal worlds, the interface can also be reused easily at the junction between Rich OS kernels and hypervisors.

#### 3.4 Conduits

The PSCI interface must support interaction at all levels of execution implemented on the device, where multiple levels of supervisory software might be executing. For the caller operating in the Normal world, the interface must forward a message to the Secure world. In a system that implements EL2, it must be possible to trap interface calls made by the EL1 kernel context to the hypervisor (EL2). If the hypervisor determines that a change of physical power state is required, it must then be able to use the same interface to inform the Secure world.

The conduits available to transfer a message from one Exception level to another depend on the implemented Exception levels. For further information on the description of possible conduits, see [4].

# 3.5 Secure world software and power management

Many Trusted OS implementations are not SMP-capable. When running on MP devices, they are tied to a single core. Secure Monitor Calls destined for the Trusted OS are only expected to come from that core. The lack of MP support in the OS helps to keep Trusted code simple and small, which in turn aids certification. Trusted OS services are invoked from the Normal world through Rich OS drivers or daemons that are provided with the Trusted OS implementations. The threads associated with these drivers and daemons are normally affinitized to the core used by the Trusted OS.

ARM systems generally include a power controller, or control logic, that can manage core power. This normally provides interfaces that support a number of power management functions. Often these include support for transitioning cores, clusters, or a superset into low-power states. In the lowpower state, the cores are either fully switched off or in guiescent states where they are not executing code. ARM strongly recommends that the Secure world is responsible for the control of these states. Otherwise, cleanup of the Secure state, including Secure cache clean, is not possible prior to entering the low-power state. Other forms of power management, such as dynamic performance management through voltage and frequency scaling, are not covered by this interface. ARM strongly recommends that all policy in power and performance management is performed in the Normal world. The Normal world has greater visibility of the current use and purpose of a given device. Where the Secure world has performance requirements, ARM recommends that IMPLEMENTATION DEFINED mechanisms are used to communicate those requirements to the Normal world.

#### 3.6 Virtualization and core power policy

Hypervisors are broadly split into two basic types:

- **Type 1:** Sometimes described as native or bare metal. Type 1 hypervisors execute directly on the hardware. Any application guest OS sees a virtualized view of this hardware.

- **Type 2:** Sometimes described as hosted. Type 2 hypervisors run within a host OS. The host OS has a physical view of the hardware it runs on, but guest operating systems see a virtualized view.

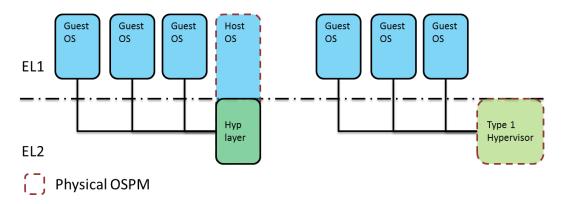

This is a very broad categorization. In reality, there are variations on the above. The ARMv8 architecture allows running a type 2 hypervisor at EL1 or EL2. This blurs the differences between type 1 and type 2. From a power management perspective, and for the purposes of this document, a type 2 hypervisor or host running at EL2, is analogous to a type 1 hypervisor. However, in general terms these two abstractions capture the forms of power management required by the hypervisors.

From the point of view of power management and virtualization there are two types of OSPM:

- **Physical OSPM:** This comprises the software components that select the physical power states.

- **Virtual OSPM:** This is an OSPM that is present in a guest OS running a virtual machine, which selects virtual, rather than physical power states.

With type 2 hypervisors, the physical OSPM resides in the host. Actual power policy is controlled from a Rich OS typically running at EL1. The physical OSPM is contained in this Rich OS. This layer has a physical view of the cores. An example of this is shown in Figure 2 on the left-hand side.

Figure 2 Typical Power management models in virtualization

For the power management functions covered in this document, type 2 hypervisor behavior depends on the caller. If the caller is the host, the hypervisor complies with the power request or allows the call to pass straight through to the secure platform firmware. The hypervisor typically only performs any necessary operations resulting from the call, for example, saving state on a powerdown if needed. From this point onwards, the hypervisor calls through to the secure platform firmware using the parameters supplied by the caller. If no special operations are required, the hypervisor does not even trap calls from the host, and instead routes them directly to the secure platform firmware. Guests, on the other hand, use a virtual OSPM. They can also issue power requests through the PSCI APIs, but the requests are issued in relation to virtual cores and virtual power states. These requests are trapped by the hypervisor, which issues them back to the physical OSPM. This component can then determine whether physical power management is required. For these guests, the power calls effectively terminate at the hypervisor.

With a type 1 hypervisor, power policy is typically owned entirely by the hypervisor. This is shown on the right-hand side in Figure 2. The physical OSPM is implemented in the hypervisor. In this case all guests have a virtualized view of the cores. The hypervisor determines from the virtual power states of the guests whether physical power control is required, and if so uses the PSCI API to coordinate with the secure platform firmware. Guests can also use this API to communicate virtual power requirements to the hypervisor. For these guests the calls effectively terminate at the hypervisor.

In some cases, type 1 hypervisors delegate power management to a privileged guest. In these cases, the physical OSPM is implemented in that privileged guest. This power management approach is equivalent to the model for type 2 hypervisors that is shown in Figure 2.

# 4 PSCI Use Cases and Use Case Requirements

#### 4.1 Idle management

When a core is idle, the OSPM transitions it into a low-power state. Typically, a choice of states is available, with different entry and exit latencies, and different levels of power consumption associated with each state. The state that is used typically depends on how quickly the core will be needed again. The power states that can be used at any one time might also depend on the activity of other components in a SoC, in addition to the cores. Each state is defined by the set of components that are clock-gated or power-gated when the state is entered. States are sometimes described as being shallow or deep. Typically, a state X is said to be deeper than a state Y if:

- The set of components that are powered down in state X subsumes and is a superset of the corresponding set for state Y.

- The set of components that is powered down in state X is the same as the corresponding set for state Y, but various power modes are supported, and the modes used in state X save more power than those used in state Y.

The time required to move from a low-power state to a running state is known as the *wakeup latency*. Generally, deeper power states have longer wakeup latencies, but this is not necessarily always the case.

Although idle power management is driven by thread behavior on a core, the OSPM can place the platform into states that affect many other components beyond the core itself. For example, if the last core in a SoC goes idle, the OSPM can target power states that affect the whole SoC. The choice is also driven by the use of other components in the system, and therefore might require coordination among multiple agents. A typical example is placing the system into a state where memory is in self-refresh when all cores, and any other bus masters, are idle. The OSPM has to provide the necessary power management software infrastructure to determine the correct choice of state.

In idle management, when a core has been placed into a low-power state, it can be reactivated at any time by a *wakeup event*, which is an event that might wake up a core from a low-power state, such as an interrupt. No explicit command is required by the OSPM to bring the core or cluster back into operation. The OSPM considers the affected core or cores to be available at all times even if they are currently in a low-power state.

An ARM core can be in any of the following power states:

**Run:** The core is powered up and operational.

**Standby**: The core is powered up, but measures are employed to reduce energy consumption. In a typical implementation, the core enters standby by executing a WFI or WFE instruction and exits on a

corresponding wakeup event. The core preserves all core state. Changing from standby to running operation does not require a reset of the core. In standby, all core context is maintained, and can be directly accessed on wakeup. No special actions are required by the OS to ensure that context is maintained. An external debugger can access debug registers in the core power domain [1,5].

Retention: The core state, including the debug settings, is preserved in low-power structures, allowing the core to be at least partially turned off. Changing from low-power retention to running operation does not require a reset of the core. The saved core state is restored on changing from low-power retention state to running operation. From an OS point of view, there is no difference between a retention state and standby state, other than the method of entry, latency, and usage-related constraints. However, from an external debugger point of view, the states differ as External Debug Request debug events stay pending and debug registers in the core power domain cannot be accessed [1, 5].

**Powerdown:** In this state the core is powered off. Software on the device needs to save all core state, so that it can be preserved over the powerdown. Changing from powerdown to running operation must include:

- A reset of the core, after the power has been restored.

- Restoring the saved core state.

The defining characteristic of powerdown states is that they are destructive of context. This affects all the components that are switched off in a given state, including the core, and in deeper states other components of the system such as the GIC or platform-specific IP. Depending on how debug and trace power domains are organized, in some powerdown states one or both of debug and trace contexts might be lost. Mechanisms must be provided to enable the OS to perform the relevant context saving and restoring for each given state. Resumption of execution starts at the reset vector, after which each OS must restore its context.

To an OS that is managing power, a standby state is mostly indistinguishable from a retention state. The difference is evident to an external debugger, and in hardware implementation, but not evident to the idle management subsystem of an OS. Consequently, unless otherwise stated, this document uses the term standby to refer to both standby and retention states.

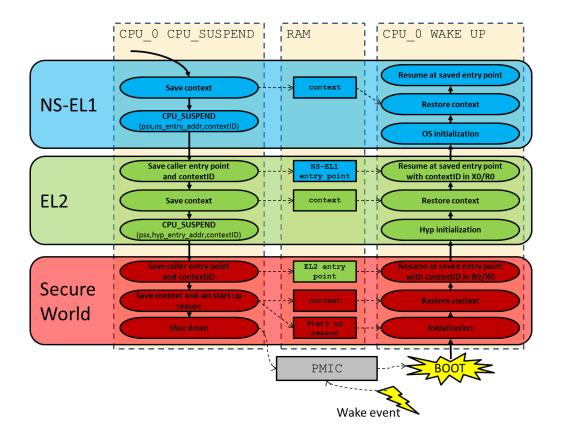

An interface is required so that the OSPM can place a core into a low-power state when it has no work for it. The messages sent through this interface must be received by all relevant levels of execution. That is, if EL2 and EL3 are implemented, a message sent by a Rich OS must be received by a hypervisor and the Secure world. Within the Secure world the message needs to be seen by a Trusted OS, if present, and by any secure platform firmware. This means that each level of supervisory software can determine whether it must perform context saving.

ARM expects the Exception level with the highest privilege, as defined in section 3.2, to be the component that can program the power controller to enter an idle state. Typically, this is the secure platform firmware. PSCI provides a mechanism for the OSPM to pass the desired idle state to the next Exception level.

For standby states that do not require any explicit programming of the power controller, no specific interface is required. The OSPM can use WFI or WFE instructions directly. However, for deeper standby or retention states that require programming a power controller, PSCI provides an interface that can hide the platform-specific code that accesses the power controller.

Powerdown states require an interface so that each level of execution can save and restore its context appropriately. For powerdown states, the interface requires a return address. This is the address at which the calling OS expects resumption of execution on wakeup at its Exception level. From a powered-down state, the core restarts at the reset vector, in Secure state if the implementation includes EL3. After initializing, the Secure world must re-start execution of the OS that called the powerdown interface, at the required return address. PSCI provides a method of specifying return addresses, and cookies that can be used for pointers to saved context.

## 4.2 Power state system topologies and coordination

Multiprocessor systems can have a number of different power domains to power different elements of the system. Each power domain might contain a combination of one or more processing elements (such as cores, coprocessors, or GPUs), memories (caches, DRAMs), and fabric (for example inter-cluster and intra-cluster coherency fabric). PSCA [1] provides detailed descriptions of how power domains can be constructed in systems that use ARM components.

Each component in a power domain has a set of power states that affect the components in the domain. Although physically the power domains are not necessarily built in a hierarchical fashion, from a software control point of view, they are arranged in a logical hierarchy. The hierarchy arises out of ordering dependencies that are required when placing the power domains into different power states. For example, consider a power domain that encompasses a shared cache, and power domains for the cores that use it. In such a system, the core power domains must be powered down before the shared cache domain, to guarantee correct operation.

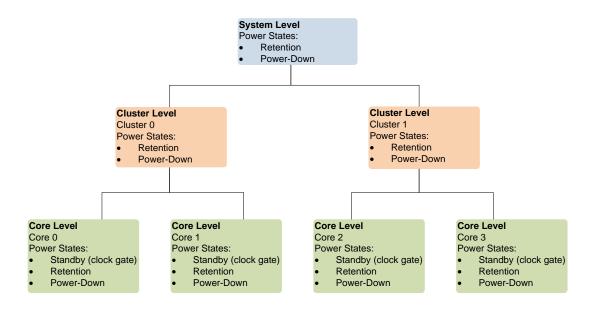

Figure 3 Example power domain topology

The diagram above shows the power domain topology of an example system. The example shows a system-level power domain that supports two power states. This power domain has two children power domains, each of which includes a cluster and supports a set of cluster power states. Each cluster power domain has two children core-level power domains. Each of the core-level power domains includes a core and supports additional power states.

From a hardware perspective, a system is divided into multiple exclusive or shared power domains. Each power domain can be represented as a node in a power domain topology tree. Sibling power domains are mutually exclusive. Parent power domains are shared by the children. The various levels in the tree (core, cluster, and system in the example) are referred to as power levels. Higher levels are closer to the root of the tree (system) and lower levels are closer to the leaves (the cores).

#### 4.2.1 Local power states and composite power states

Individual nodes in a topology have their own specific power states, which are referred to here as *local power states*. When an OS, running on an idle core, requests a power state, it might need to express not just a local power state for the core, but also for any parent nodes. For instance, taking our example system from Figure 3, if Core 1 was the last to go idle in Cluster 0, it would make sense for the OS to request a local power state for the cluster as well as the core. We refer to the combined power state that an OS might request as a composite power state. Not every combination of local states is possible. When a node at a power level is in a certain local power state, parent nodes at higher power levels cannot be in a deeper local state. In other words:

1. A powerdown in a higher-level node can only be combined with powerdown states in lower-level children.

- 2. A retention state in a higher-level node might only be combined with retention or powerdown states in lower-level children.

- 3. A standby (clock-gated) state in a higher-level node allows lower-level children to be in standby, retention, or powerdown states.

- 4. A running state in a higher-level node allows lower-level children to be in any state.

**Note**: The PSCI specification is only concerned with power states that require explicit software control. Hardware power modes, which are not exposed to software, are not relevant to PSCI.

Taking these rules into account, Table 3 illustrates the valid low-power composite states for the example system described in Figure 3.

Table 3 Valid local state combinations for composite power states in the example system

| System Level State | Cluster Level State | Core Level State |

|--------------------|---------------------|------------------|

| Run                | Run                 | Standby          |

| Run                | Run                 | Retention        |

| Run                | Run                 | Powerdown        |

| Run                | Retention           | Retention        |

| Run                | Retention           | Powerdown        |

| Run                | Powerdown           | Powerdown        |

| Retention          | Retention           | Retention        |

| Retention          | Retention           | Powerdown        |

| Retention          | Powerdown           | Powerdown        |

| Powerdown          | Powerdown           | Powerdown        |

#### 4.2.2 Affinity hierarchy

ARM systems can have multiple cores or even multiple clusters of cores. This specification uses the term *affinity hierarchy* to describe the hierarchical arrangement of cores. This often, but not always, maps directly to the processor power topology of the system.

This specification uses the term *affinity level* to describe a level in the affinity hierarchy, for example, the level of cores or clusters. Finally, the term *affinity instance* is used to refer to an individual entry in the affinity hierarchy, for example, an individual core or cluster.

#### 4.2.3 Power state coordination

Entry into local power states for high-level nodes in a power topology (for example, clusters or system) requires coordinating children nodes. For example, entry into a cluster powerdown state is only possible when all cores in the cluster are powered down. To achieve this, every core but the last one has to be placed into a powerdown state, and the last one places itself and the cluster into a powerdown state.

PSCI supports two modes of power state coordination, *platform-coordinated* mode and *OS-initiated* mode.

#### 4.2.3.1 Platform-coordinated mode

This is the default mode of coordination. In this mode, the PSCI implementation is responsible for coordinating power states. When a core has no more work to do, the OSPM requests the deepest state it can tolerate for that core and its parent nodes. For power state requests that affect a topology node above the core level, the implementation chooses the deepest power state that can be tolerated by all the cores in the node. In effect, the power state request expresses the following two constraints:

- 1. The caller allows entry to states of this depth, but no deeper.

- 2. The caller cannot tolerate a higher wakeup latency than that associated with the requested state.

The PSCI implementation then determines the deepest state that satisfies the constraints expressed by each core in a given node. Table 4 builds on the example system of Figure 3, and shows how composite power state requests are arbitrated for that system. In the example, the abbreviations Ret and PD denote retention and powerdown, respectively. The example is not exhaustive, and assumes that Cluster 1 has already been powered down. The example shows requests from Core0 and Core1, and the resulting power state for the clusters and the system.

Table 4 Example platform coordination of power state requests.

| Composite state requested |         |        |        |         |        | Power state | granted                                         |        |

|---------------------------|---------|--------|--------|---------|--------|-------------|-------------------------------------------------|--------|

| Core                      | 0       |        | Core 1 |         |        | _           | Cluster 1                                       |        |

| Core                      | Cluster | System | Core   | Cluster | System | Cluster 0   | (we assume this<br>has already<br>powered down) | System |

| Ret                       | Run     | Run    | Ret    | Run     | Run    | Run         | Powerdown                                       | Run    |

| Ret                       | Ret     | Run    | Ret    | Run     | Run    | Run         | Powerdown                                       | Run    |

| Ret                       | Ret     | Run    | Ret    | Ret     | Run    | Retention   | Powerdown                                       | Run    |

| Ret                       | Ret     | Ret    | Ret    | Ret     | Run    | Retention   | Powerdown                                       | Run    |

| Ret | Ret | Ret | Ret | Ret | Ret | Retention | Powerdown | Retention |

|-----|-----|-----|-----|-----|-----|-----------|-----------|-----------|

| PD  | Ret | Ret | Ret | Ret | Ret | Retention | Powerdown | Retention |

| PD  | PD  | Ret | PD  | Ret | Ret | Retention | Powerdown | Retention |

| PD  | PD  | Ret | PD  | PD  | Ret | Powerdown | Powerdown | Retention |

| PD  | PD  | PD  | PD  | PD  | Ret | Powerdown | Powerdown | Retention |

| PD  | PD  | PD  | PD  | PD  | PD  | Powerdown | Powerdown | Powerdown |

As a general rule, wakeup latency increases with depth of state, so in the example above we are assuming that the retention (for core, cluster, or system) has smaller wakeup latency than powerdown. However, this is not necessarily the case. There might be systems where this ordering breaks. As stated by the second constraint above, the state chosen by the implementation has to satisfy the wakeup time associated with every core's request. Consider a dual core system that has three system-level states, ordered by increasing depth, stateA, stateB, and stateC, but where wakeup latency ordering is state A < state C < state B. If Core 0 chooses State B and Core 1 chooses State C, the system will need to enter state A. State C is not possible as Core 0 does not want to go that deep, and State B is not possible as Core 1 cannot tolerate its longer wakeup latency.

Versions of PSCI prior to 1.0 support only the platform-coordinated mode.

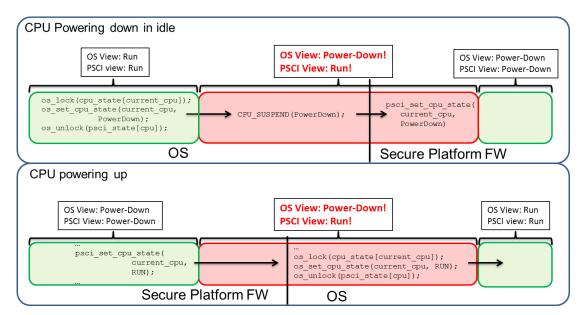

#### 4.2.3.2 OS-initiated mode

Introduced in PSCI 1.0, OS-initiated mode places the responsibility for coordination on the calling OS. In the OS-initiated coordination scheme, OSPM only requests an idle state for a particular topology node when the last underlying core goes idle.

When a core goes idle it always selects an idle state for itself, but idle states for higher-level nodes such as clusters are only selected when the last running core in the node goes idle. In addition, the implementation only considers the most recent request for a particular node when deciding on its idle state. Using the above example of a dual cluster, dual core per cluster system, the following table illustrates the steps involved in taking Cluster0 into a powerdown state. In the example, abbreviations R, Ret, and PD, denote run, retention and powerdown respectively. In addition, states where OS view and implementation view differ are marked in red, and states that change during a step are underlined.

Table 5 Example flow: Cluster powerdown entry

| Step | S View | PSCI View |

|------|--------|-----------|

|------|--------|-----------|

|                                                                      |        | Core0     | Core1     | Cluster0  | Core0     | Core1     | Cluster0  |

|----------------------------------------------------------------------|--------|-----------|-----------|-----------|-----------|-----------|-----------|

| 1: OS on Core0 requests Core0                                        | before | <u>R</u>  | R         | R         | R         | R         | R         |

| powerdown                                                            | after  | <u>PD</u> | R         | R         | R         | R         | R         |

| 2: PSCI Implementation observes                                      | before | PD        | R         | R         | <u>R</u>  | R         | R         |

| request and places Core0 into powerdown                              | after  | PD        | R         | R         | <u>PD</u> | R         | R         |

| 3: OS on Core1 requests Core1                                        | before | PD        | <u>R</u>  | <u>R</u>  | PD        | R         | R         |

| powerdown and, knowing it is last in the cluster, Cluster0 powerdown | after  | PD        | <u>PD</u> | <u>PD</u> | PD        | R         | R         |

| 4: PSCI Implementation observes                                      | before | PD        | PD        | PD        | PD        | <u>R</u>  | <u>R</u>  |

| requests for Core1 and Cluster0 and processes them                   | after  | PD        | PD        | PD        | PD        | <u>PD</u> | <u>PD</u> |

As the table illustrates, there are periods (marked in red) where the OS view of core state and the implementation view of core state do not match. This might happen after the OS requests a state, but before the implementation has processed the request. This can also happen when a core powers up, as the implementation sees the core before the OS. In order to implement OS-initiated mode, it is necessary to deal with the races that arise due to the differing views of core state. Solving the races gives rise to the following requirements:

- The implementation must deny any requests from the calling OS that are inconsistent with its view of core state.

- The calling OS must indicate when the calling core is the last running core at a particular power hierarchy level. It must also specify which power hierarchy level the core is last in, for example, whether it is the last core in the cluster or the last core in the system.

A full discussion of the reasoning behind these requirements, and races that arise is described in sections 6.2 and 6.3.

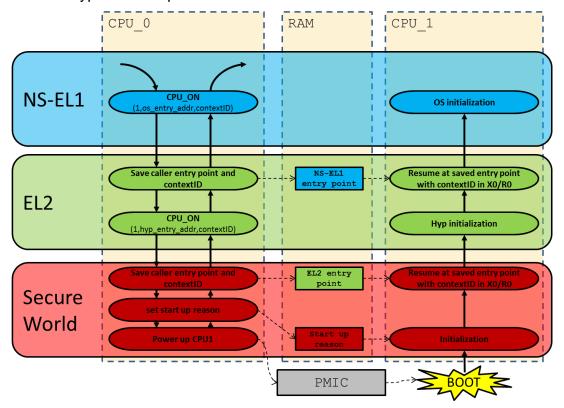

# 4.3 CPU hotplug and secondary CPU boot

CPU hotplug is a technique that can dynamically switch cores on or off. Hotplug can be used by an OSPM to change available compute capacity based on current compute requirements. Hotplug is also sometimes used for reliability reasons. There are a number of differences between using hotplug and using a powerdown state in idle management:

- When a core is hot unplugged, the supervisory software stops all use

of that core in interrupt and thread processing. The calling

supervisory software regards the core as no longer available.

- 2) The supervisory software has to issue an explicit command to bring a core back online, that is, to hotplug a core. The appropriate

- supervisory software only starts using that core in thread scheduling, or interrupt service routines, after this command.

- 3) With hotplug, wakeup events that could restart a powered-down core are not expected on the cores that have been hot unplugged.

Operating systems typically perform much of the kernel boot process on one primary core, bringing secondary cores online at a later stage. For systems that support hotplug, the operations involved in booting a core for secondary boot or hotplug, are the same. Therefore they can be provided as a single interface.

When using a uniprocessor Trusted OS, hot removal of a core might not be possible without first migrating the Trusted OS.

PSCI provides an interface with the following properties:

- The supervisory software can request that a core be powered up. The supervisory software must provide an appropriate start address for the Non-secure Exception Level where it will resume operation when it exits the secure platform firmware. The provision of a start address means the caller can shortcut any bootloader-related code when onlining a core, by providing an entry point directly in its own OS address space. Different addresses can be provided to handle different startup reasons. Alternatively, the supervisory software can use internal per-core data structures for this purpose.

- 2) The supervisory software can request powering down the core, and inform higher Exception levels that it is doing so.

- 3) The supervisory software can request that the Trusted OS, if present, be migrated to another core.

# 4.4 System shutdown, reset and suspend

PSCI provides an interface to allow an OS to request system shutdown, system reset, and system suspend (suspend to RAM). This allows a silicon vendor to provide a common implementation of these functions that is independent of the supervisory software running on the device. No explicit function is provided for suspend to disk, as this is a special case of system shutdown.

The usage of the term *system* in the PSCI function definitions refers to the machine view that is available to the calling OS. If the caller is a guest running in a virtual machine system, shutdown, reset, and suspend operations affect the virtual machine and might not result in any physical power changes. However, if a hypervisor is not present, or the caller is a hypervisor, the result is physical changes in power. Even if the caller is running on a physical machine, the term system might not mean the entire physical machine. For example, consider an advanced server system consisting of multiple boards, each with a board management controller (BMC), and each containing multiple SoCs. Such a system could run an OS instance per SoC. In this example, a PSCI command to shut down the

system applies to a single SoC, while powering down the entire board requires access to the BMC through an administration interface that is beyond the reach of the calling OS or a PSCI implementation. In this document, the term system refers only to the machine view that is visible to an OS. In the example above, this maps to a single SoC.

#### 5 Functions

This section introduces the functions for Power State Coordination.

The APIs are described here without reference to the underlying conduit (SMC or HVC). However, the functions adhere to the SMC Calling Conventions [4]. In an implementation that includes EL2 but not EL3, a hypervisor providing support to a PSCI-compliant EL1 Rich OS can use HVC as the conduit. In the HVC case, the format of the call, in terms of immediate value, and register usage, is the same as in the SMC case. PSCI functions can only be called from the Normal world (EL1 or EL2).

# 5.1 Function prototypes

#### 5.1.1 PSCI VERSION

#### Description

Return the version of PSCI implemented. See section 5.3 for more details.

| Parameters         |                           |  |  |

|--------------------|---------------------------|--|--|

| Declaration        | Value                     |  |  |

| uint32 Function ID | 0x8400 0000               |  |  |

| Return             |                           |  |  |

| Declaration        | Value                     |  |  |

| uint32             | Bits[31:16] Major Version |  |  |

| unitoz             | Bits[15:0] Minor Version  |  |  |

#### 5.1.2 CPU SUSPEND

#### Description

Suspend execution on a core or higher-level topology node. This call is intended for use in idle subsystems where the core is expected to return to execution through a wakeup event. See section 5.4 for more details.

| Parameters            |                                                                               |

|-----------------------|-------------------------------------------------------------------------------|

| Declaration           | Value                                                                         |

| uint32 Function ID    | <ul><li>0x8400 0001 SMC32 version</li><li>0xC400 0001 SMC64 version</li></ul> |

| uint32<br>power_state | This parameter is described in section 5.4.2                                  |

| SMC32 uint32<br>SMC64 uint64<br>entry_point_address | Address at which the core must resume execution, when it enters the return Non-secure Exception level, following wakeup from a powerdown state.  This parameter is only valid if the target power state is a powerdown state. For standby states, the value passed in is ignored.  For the SMC64 version, this parameter is a 64-bit entry point <i>Physical Address</i> (PA) or <i>Intermediate Physical Address</i> (IPA).  For the SMC32 version, this parameter is a 32-bit entry point PA or IPA.                                              |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                     | Note: An ARMv7 system must use the SMC32 version of the function. This limits the entry point addresses to 32 bits, even if the implementation includes the Large Physical Address Extension (LPAE), as the MMU will be disabled when the platform reenters at this address.                                                                                                                                                                                                                                                                        |

| SMC32 uint32<br>SMC64 uint64<br>context_id          | This parameter is only valid if the target power state is a powerdown state. For standby states the value is ignored.  For the SMC64 version, this parameter is a 64-bit value. Following wakeup from a powerdown state, when the calling core first enters the return Non-secure Exception level, this value must be present in X0.  For the SMC32 version, this parameter is a 32-bit value. Following wakeup from a powerdown state, when the calling core first enters the return Non-secure Exception level, this value must be present in R0. |

| Return                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Declaration                                         | Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| int32                                               | <ul> <li>SUCCESS</li> <li>INVALID_PARAMETERS</li> <li>INVALID_ADDRESS</li> <li>DENIED - Only in OS-initiated mode. See sections 4.2.3.2 and 5.4.</li> <li>See section 5.2.2 for integer values associated with each return code.</li> </ul>                                                                                                                                                                                                                                                                                                         |

#### 5.1.3 CPU\_OFF

#### Description

Power down the calling core. This call is intended for use in hotplug. A core that is powered down by  $\protect\operatorname{CPU}_OFF$  can only be powered up again in response to a  $\protect\operatorname{CPU}_ON$ . See section 5.5 for more details.

| Parameters            |                                                                        |

|-----------------------|------------------------------------------------------------------------|

| Declaration           | Value                                                                  |

| uint32 Function<br>ID | 0x8400 0002                                                            |

| Return                |                                                                        |

| Declaration           | Value                                                                  |

| int32                 | The call does not return when successful.                              |

|                       | Otherwise, it returns:                                                 |

|                       | • DENIED                                                               |

|                       | See section 5.2.2 for integer values associated with each return code. |

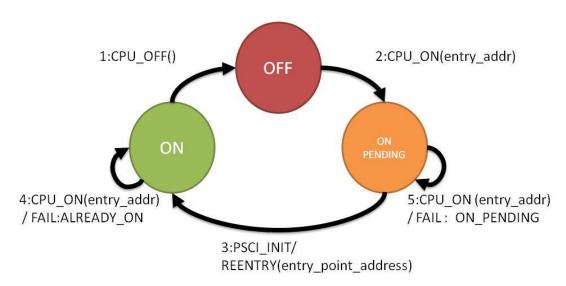

#### 5.1.4 CPU\_ON

#### **Description**

Power up a core. This call is used to power up cores that either:

- Have not yet been booted into the calling supervisory software.

- Have been previously powered down with a CPU\_OFF call.

See section 5.6 for more details.

| Parameters          |                                               |

|---------------------|-----------------------------------------------|

| Declaration         | Value                                         |

| uint32 Function ID  | • 0x8400 0003 SMC32 version                   |

| unit32 i unction iD | <ul> <li>0xC400 0003 SMC64 version</li> </ul> |

|                                  | This parameter contains a copy of the affinity fields of the MPIDR register (See [1,5]).                                                                                             |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  | If the calling Exception level is using AArch32, the format is:                                                                                                                      |

|                                  | <ul> <li>Bits[24:31]: Must be zero.</li> </ul>                                                                                                                                       |

|                                  | Bits[16:23] Aff2: Match Aff2 of target core MPIDR                                                                                                                                    |

|                                  | Bits[8:15] Aff1: Match Aff1 of target core MPIDR                                                                                                                                     |

| SMC32 uint32                     | Bits[0:7] Aff0: Match Aff0 of target core MPIDR                                                                                                                                      |

| SMC64 uint64                     |                                                                                                                                                                                      |

| target_cpu                       | If the calling Exception level is using AArch64, the format is:                                                                                                                      |

|                                  | <ul><li>Bits[40:63]: Must be zero</li></ul>                                                                                                                                          |

|                                  | <ul> <li>Bits[32:39] Aff3: Match Aff3 of target core MPIDR</li> </ul>                                                                                                                |

|                                  | Bits[24:31] Must be zero                                                                                                                                                             |

|                                  | <ul> <li>Bits[16:23] Aff2: Match Aff2 of target core MPIDR</li> </ul>                                                                                                                |

|                                  | <ul> <li>Bits[8:15] Aff1: Match Aff1 of target core MPIDR</li> </ul>                                                                                                                 |

|                                  | <ul> <li>Bits[0:7] Aff0: Match Aff0 of target core MPIDR</li> </ul>                                                                                                                  |

| SMC32 uint32                     | For the SMC64 version, this parameter is a 64-bit entry point physical address (PA) or intermediate physical address (IPA).                                                          |

| SMC64 uint64 entry_point_address | For the SMC32 version this parameter is a 32-bit entry point physical address (or IPA).                                                                                              |

| omry_pomr_addrood                | Address at which the core must commence execution, when it enters the return Non-secure Exception level.                                                                             |

| SMC32 uint32                     | For the SMC64 version this parameter is a 64-bit value. When the core identified by target_cpu first enters the return Non-secure Exception level, this value must be present in X0. |

| SMC64 uint64 context_id          | For the SMC32 version this parameter is a 32-bit value. When the core identified by target_cpu first enters the return Non-secure Exception level, this value must be present in R0. |

| Return                           |                                                                                                                                                                                      |

| Declaration                      | Value                                                                                                                                                                                |

|                                  |                                                                                                                                                                                      |

| int32 | • SUCCESS                                                              |

|-------|------------------------------------------------------------------------|

|       | • INVALID_PARAMETERS                                                   |

|       | • INVALID_ADDRESS                                                      |

|       | • ALREADY_ON                                                           |

|       | • ON_PENDING                                                           |

|       | • INTERNAL_FAILURE                                                     |

|       | See section 5.2.2 for integer values associated with each return code. |

|       | each return code.                                                      |

# 5.1.5 AFFINITY\_INFO

# **Description**

Enable the caller to request status of an affinity instance (as defined in section 4.2.2). See section 5.7 for more details.

| Parameters                                      |                                                                                                                                                                                  |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Declaration                                     | Value                                                                                                                                                                            |

| uint32 Function ID:                             | <ul><li>0x8400 0004 SMC32 version</li><li>0xC400 0004 SMC64 version</li></ul>                                                                                                    |

| SMC32 uint32<br>SMC64 uint64<br>target_affinity | In SMC32 version this is a uint32 value. In SMC64 version this is a uint64 value. This follows the same format as the target_cpu parameter of a CPU_ON call (see section 5.1.4). |

| Denotes the lowest affinity level field that is valid in the target_affinity parameter. This argument allows the caller of AFFINITY_INFO to request information about |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| affinity levels higher than 0.                                                                                                                                        |

| Possible values are:                                                                                                                                                  |

| 0: All affinity level fields in target_affinity are valid. In a system where processors are not hardware threaded,                                                    |

| the target_affinity parameter would represent an                                                                                                                      |

| individual core.                                                                                                                                                      |

# uint32 lowest\_affinity\_level

1: Aff0 field must be ignored. The target\_affinity parameter denotes an affinity level 1 processing unit.

- 2: Aff0 and Aff1 fields must be ignored. The target\_affinity parameter denotes an affinity level 2 processing unit.

- 3: Aff0, Aff1 and Aff2 fields must be ignored. The target\_affinity parameter denotes an affinity level 3 processing unit.

From version 1.0 of PSCI onwards, AFFINITY\_INFO is no longer required to support affinity levels higher than 0. For more details on return values when this parameter is non-zero, see section 5.7.1.

| Return      |                                                                                             |

|-------------|---------------------------------------------------------------------------------------------|

| Declaration | Value                                                                                       |

| int32       | <ul> <li>2 ON_PENDING: the affinity instance is transitioning<br/>to an ON state</li> </ul> |

|             | • <b>1</b> off                                                                              |

|             | <ul> <li>0 on: At least one core in the affinity instance is on</li> </ul>                  |

|             | • INVALID_PARAMETERS                                                                        |

|             | • DISABLED                                                                                  |

|             | See section 5.2.2 for integer values associated with each return code.                      |

#### **5.1.6 MIGRATE**

#### **Description**

Optional. This is used to ask a uniprocessor Trusted OS to migrate its context to a specific core. See section 5.8 for more details.

#### **Parameters**

| Declaration                 | Value                                                                                               |

|-----------------------------|-----------------------------------------------------------------------------------------------------|

| uint32 Function<br>ID:      | 0x8400 0005 SMC32 version                                                                           |

|                             | • 0xC400 0005 SMC64 version                                                                         |

| uint32/uint64<br>target_cpu | This field follows the same format as the target_cpu parameter of a CPU_ON call (see section 5.1.4) |

| Return                      |                                                                                                     |

| Declaration                 | Value                                                                                               |

|                             | • SUCCESS                                                                                           |

|                             | • NOT_SUPPORTED                                                                                     |

| int32                       | • INVALID_PARAMETERS                                                                                |

|                             | • DENIED                                                                                            |

|                             | • INTERNAL_FAILURE                                                                                  |

|                             | • NOT_PRESENT                                                                                       |

|                             | See section 5.2.2 for integer values associated with each return code.                              |

# 5.1.7 MIGRATE\_INFO\_TYPE

# **Description**

Optional. This function allows a caller to identify the level of multicore support present in the Trusted OS. See section 5.9 for more details.

| Parameters          |             |

|---------------------|-------------|

| Declaration         | Value       |

| uint32 Function ID: | 0x8400 0006 |

| Return              |             |

| Declaration         | Value       |

|                     |             |

- 0 Uniprocessor migrate capable Trusted OS. The Trusted OS will only run on one core. The Trusted OS supports the MIGRATE function and can be migrated to any core that has not been turned off with CPU\_OFF. Attempts to call CPU\_OFF on the core where the Trusted OS is resident, will fail with DENIED.

- 1 Uniprocessor not migrate capable Trusted OS.

The Trusted OS will only run one core. The

Trusted OS does not support the MIGRATE function

. Calls to MIGRATE will fail with DENIED. Attempts to

call CPU\_OFF on the core where the Trusted OS is

resident fail with DENIED.

- 2 Trusted OS is either not present or does not require migration. A system of this type does not require the caller to use the MIGRATE function.

MIGRATE function calls return NOT SUPPORTED.

- NOT\_SUPPORTED can be treated by the calling OS

as an indication that MIGRATE is not required, so

that the behavior is the same as for a return value

of 2. This effectively makes this function optional,

as for SMC32 a return value of NOT\_SUPPORTED

must be returned if the function is not

implemented.

Note that for issue B.b of this document MIGRATE\_INFO\_TYPE was compulsory, and NOT\_SUPPORTED was not a valid return value. This was fixed in issue C of this document, which acts a release of PSCI 1.0, and an errata fix release for PSCI 0.2. Therefore this change applies to all versions of PSCI from 0.2 onwards.

#### 5.1.8 MIGRATE\_INFO\_UP\_CPU

#### **Description**

Optional. For a uniprocessor Trusted OS, this function returns the current resident core. See section 5.9 for more details.

| Parameters          |                                                         |

|---------------------|---------------------------------------------------------|

| Declaration         | Value                                                   |

| uint32 Function ID: | 0x8400 0007 SMC32 version     0x8400 0007 SMC34 version |

|                     | 0xC400 0007 SMC64 version                               |

#### Return

int32

| Declaration                  | Value                                                                                                                                                                                                                                                                     |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|