# ARM® Debug Interface v5 Architecture Specification

## ARM Debug Interface v5 Architecture Specification

Copyright © 2006 ARM Limited. All rights reserved.

#### Release Information

The following changes have been made to this book.

#### **Change History**

| Date            | Issue | Confidentiality  | Change                  |

|-----------------|-------|------------------|-------------------------|

| 8 February 2006 | A     | Non-Confidential | First issue, for ADIv5. |

#### **Proprietary Notice**

ARM and the ARM Powered logo are registered trademarks of ARM Limited.

The ARM logo, AMBA, ARM7, ARM7TDMI, ARM9, ARM10, CoreSight, and TDMI, are trademarks of ARM Limited.

All other products or services mentioned herein may be trademarks of their respective owners.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM Limited in good faith.

- 1. Subject to the provisions set out below, ARM Limited hereby grants to you a perpetual, non-exclusive, nontransferable, royalty free, worldwide licence to use this ARM Architecture Reference Manual for the purposes of developing; (i) software applications or operating systems which are targeted to run on microprocessor cores distributed under licence from ARM Limited; (ii) tools which are designed to develop software programs which are targeted to run on microprocessor cores distributed under licence from ARM Limited; (iii) integrated circuits which incorporate a microprocessor core manufactured under licence from ARM Limited.

- 2. Except as expressly licensed in Clause 1 you acquire no right, title or interest in the ARM Architecture Reference Manual, or any Intellectual Property therein. In no event shall the licences granted in Clause 1, be construed as granting you expressly or by implication, estoppel or otherwise, licences to any ARM technology other than the ARM Architecture Reference Manual. The licence grant in Clause 1 expressly excludes any rights for you to use or take into use any ARM patents. No right is granted to you under the provisions of Clause 1 to; (i) use the ARM Architecture Reference Manual for the purposes of developing or having developed microprocessor cores or models thereof which are compatible in whole or part with either or both the instructions or programmer's models described in this ARM Architecture Reference Manual; or (ii) develop or have developed models of any microprocessor cores designed by or for ARM Limited; or (iii) distribute in whole or in part this ARM Architecture Reference Manual to third parties without the express written permission of ARM Limited; or (iv) translate or have translated this ARM Architecture Reference Manual into any other languages.

3.THE ARM ARCHITECTURE REFERENCE MANUAL IS PROVIDED "AS IS" WITH NO WARRANTIES EXPRESS, IMPLIED OR STATUTORY, INCLUDING BUT NOT LIMITED TO ANY WARRANTY OF SATISFACTORY QUALITY, NONINFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE.

4. No licence, express, implied or otherwise, is granted to LICENSEE, under the provisions of Clause 1, to use the ARM tradename, in connection with the use of the ARM Architecture Reference Manual or any products based thereon. Nothing in Clause 1 shall be construed as authority for you to make any representations on behalf of ARM Limited in respect of the ARM Architecture Reference Manual or any products based thereon.

Copyright © 2006 ARM Limited

110 Fulbourn Road Cambridge, England CB1 9NJ

Restricted Rights Legend: Use, duplication or disclosure by the United States Government is subject to the restrictions set forth in DFARS 252.227-7013 (c)(1)(ii) and FAR 52.227-19

Figure 4-3 on page 4-5 reproduced with permission IEEE Std 1149.1-1990 IEEE Standard Test Access Port and Boundary Scan Architecture Copyright 2006, by IEEE. The IEEE disclaims any responsibility or liability resulting from the placement and use in the described manner.

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### Web Address

http://www.arm.com

### Contents

## **ARM Debug Interface v5 Architecture Specification**

|           | Prefa | ace                                                         |      |

|-----------|-------|-------------------------------------------------------------|------|

|           |       | About this specification                                    | xvii |

|           |       | Conventions                                                 |      |

|           |       | Further reading                                             | xxi  |

|           |       | Feedback                                                    | xxii |

| Chapter 1 | Intro | duction                                                     |      |

| -         | 1.1   | About the ARM Debug Interface version 5 (ADIv5)             | 1-2  |

|           | 1.2   | The function of the ARM Debug Interface                     |      |

|           | 1.3   | The subdivisions of an ARM Debug Interface                  | 1-5  |

|           | 1.4   | Design choices for an ARM Debug Interface v5 implementation | 1-6  |

| Chapter 2 | Ove   | rview of the ARM Debug Interface and its components         | i    |

|           | 2.1   | ARM Debug Interface overview                                | 2-2  |

|           | 2.2   | The external interface, the Debug Port (DP)                 | 2-3  |

|           | 2.3   | The resource interface, the Access Ports (APs)              |      |

|           | 2.4   | ARM Debug Interface implementation examples                 |      |

|           | 2.5   | Accessing Access Ports                                      |      |

| Chapter 3  | Com   | mon Debug Port (DP) features                              |      |

|------------|-------|-----------------------------------------------------------|------|

| •          | 3.1   | Sticky flags and DP error responses                       | 3-2  |

|            | 3.2   | Pushed compare and pushed verify operations               |      |

|            | 3.3   | The Transaction Counter                                   | 3-8  |

|            | 3.4   | System and Debug power and Debug reset control            |      |

| Chapter 4  | The . | JTAG Debug Port (JTAG-DP)                                 |      |

|            | 4.1   | The Debug TAP State Machine introduction                  | 4-2  |

|            | 4.2   | The scan chain interface                                  |      |

|            | 4.3   | IR scan chain and IR instructions                         |      |

|            | 4.4   | DR scan chain and DR registers                            |      |

| Chapter 5  | The S | Serial Wire Debug Port (SW-DP)                            |      |

| ona-pro-   | 5.1   | Introduction to the DAP Serial Wire Debug Port            | 5-2  |

|            | 5.2   | Introduction to the ARM Serial Wire Debug (SWD) protocol  |      |

|            | 5.3   | Serial Wire Debug protocol operation                      |      |

|            | 5.4   | Protocol description                                      |      |

| Chapter 6  | Dehi  | ıg Port Registers                                         |      |

| Onapici o  | 6.1   | Debug Port registers overview                             | 6.0  |

|            | 6.2   | Debug Port (DP) register descriptions                     |      |

|            | 6.2   | Debug Port (DP) register descriptions                     | 6-0  |

| Chapter 7  | Com   | mon Access Port (AP) features                             |      |

|            | 7.1   | Overview of Access Ports (APs)                            |      |

|            | 7.2   | The identification model for Access Ports                 |      |

|            | 7.3   | Selecting and accessing an AP                             | 7-4  |

| Chapter 8  | The I | Memory Access Port (MEM-AP)                               |      |

|            | 8.1   | Overview of the function of a Memory Access Port (MEM-AP) | 8-2  |

|            | 8.2   | MEM-AP functions                                          | 8-8  |

|            | 8.3   | MEM-AP examples of pushed verify and pushed compare       | 8-22 |

|            | 8.4   | MEM-AP implementation requirements                        |      |

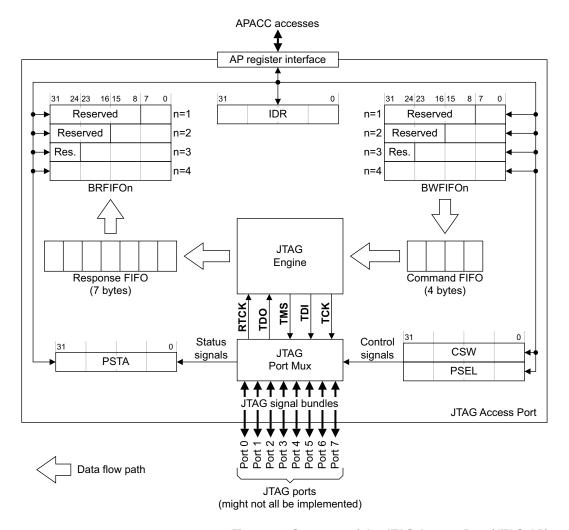

| Chapter 9  | The . | JTAG Access Port (JTAG-AP)                                |      |

| •          | 9.1   | Overview of the function of a JTAG Access Port (JTAG-AP)  | 9-2  |

|            | 9.2   | The JTAG Engine Byte Command Protocol                     |      |

| Chapter 10 | Acce  | ess Port (AP) Registers Overview and the Common           | AP   |

| •          | Regi  |                                                           |      |

|            | 10.1  | Access Port (AP) registers overview                       |      |

|            | 10.2  | The common Access Port register, the IDR                  | 10-3 |

| Chapter 11 | Mem   | ory Access Port (MEM-AP) Registers                        |      |

| -          | 11.1  | Memory Access Port (MEM-AP) register summary              | 11-2 |

|            | 11.2  | MEM-AP detailed register descriptions                     |      |

| Chapter 12 | JTAG | Access Port (JTAG-AP) Registers             |       |

|------------|------|---------------------------------------------|-------|

| -          | 12.1 | JTAG Access Port (JTAG-AP) register summary | 12-2  |

|            | 12.2 | JTAG-AP detailed register descriptions      | 12-5  |

| Chapter 13 | Com  | ponent and Peripheral ID Registers          |       |

| -          | 13.1 | Component and Peripheral ID registers       | 13-2  |

|            | 13.2 | The Component ID Registers                  |       |

|            | 13.3 | The Peripheral ID Registers                 |       |

| Chapter 14 | ROM  | Tables                                      |       |

| •          | 14.1 | ROM Table overview                          | 14-2  |

|            | 14.2 | ROM Table entries                           | 14-5  |

|            | 14.3 | The MEMTYPE Register                        | 14-9  |

|            | 14.4 | Component and Peripheral ID Registers       |       |

|            | 14.5 | ROM Table hierarchies                       | 14-12 |

|            |      |                                             |       |

|            | Glos | sary                                        |       |

# List of Tables ARM Debug Interface v5 Architecture Specification

|           | Change History                                                            | II   |

|-----------|---------------------------------------------------------------------------|------|

| Table 2-1 | Comparison of IEEE 1149.1 and JTAG-DP naming                              | 2-3  |

| Table 4-1 | JTAG-DP signal connections                                                | 4-4  |

| Table 4-2 | Standard IR instructions                                                  | 4-9  |

| Table 4-3 | Recommended implementation defined IR instructions for                    |      |

|           | IEEE 1149.1-compliance                                                    | 1-10 |

| Table 4-4 | DPACC and APACC ACK responses                                             | 1-14 |

| Table 4-5 | JTAG-DP target response summary, when previous scan was a DPACC acce 4-19 | SS . |

| Table 4-6 | JTAG-DP target response summary, when previous scan was an APACC acced-   | ess  |

| Table 4-7 | Summary of JTAG-DP host responses                                         | 1-21 |

| Table 5-1 | Target response summary for DP read transaction requests                  | 5-16 |

| Table 5-2 | Target response summary for AP read transaction requests                  | 5-17 |

| Table 5-3 | Target response summary for DP write transaction requests 5               | 5-17 |

| Table 5-4 | Target response summary for AP write transaction requests                 | 5-18 |

| Table 5-5 | Summary of host (debugger) responses to the SW-DP acknowledge 5           | 5-19 |

| Table 6-1 | Summary of Debug Port registers                                           | 6-2  |

| Table 6-2 | JTAG-DP register map                                                      | 6-3  |

| Table 6-3 | SW-DP register map                                                        | 6-5  |

| Table 6-4 | AP Abort Register bit assignments                                         | 6-6  |

|           |                                                                           |      |

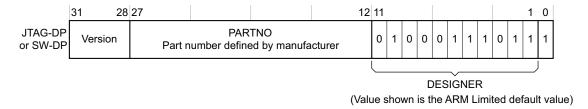

| Table 6-5   | Identification Code Register bit assignments                                | 6-9  |

|-------------|-----------------------------------------------------------------------------|------|

| Table 6-6   | JEDEC JEP-106 manufacturer ID code, with ARM Limited values                 |      |

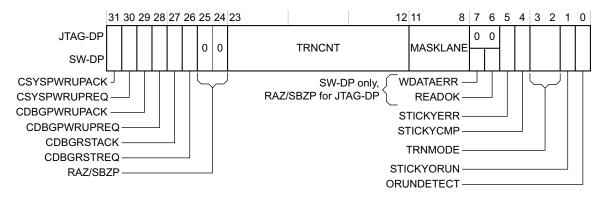

| Table 6-7   | Control/Status Register bit assignments                                     | 6-10 |

| Table 6-8   | Control of pushed operation comparisons by MASKLANE                         | 6-14 |

| Table 6-9   | Transfer Mode, TRNMODE, bit definitions                                     | 6-14 |

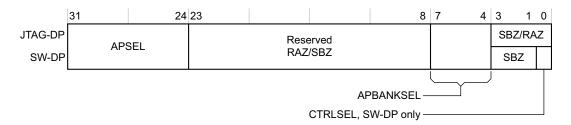

| Table 6-10  | Bit assignments for the AP Select Register, SELECT                          | 6-16 |

| Table 6-11  | CTRLSEL field bit definitions                                               | 6-17 |

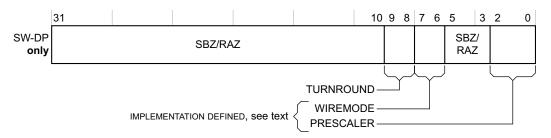

| Table 6-12  | Bit assignments for the Wire Control Register (SW-DP only)                  | 6-19 |

| Table 6-13  | Turnaround tri-state period field, TURNROUND, bit definitions               | 6-19 |

| Table 6-14  | Wire operating mode, WIREMODE, bit definitions                              | 6-20 |

| Table 8-1   | Summary of Addrinc field values                                             |      |

| Table 8-2   | Size field values when the MEM-AP supports different access sizes           | 8-13 |

| Table 8-3   | Byte-laning of memory accesses from the DRW                                 | 8-14 |

| Table 8-4   | Use of DbgSwEnable bit, bit [31], to control a slave memory port            |      |

| Table 8-5   | Use of DbgSwEnable bit, bit [31], to control the DBGSWENABLE signal .       | 8-20 |

| Table 9-1   | JTAG Access Port JTAG port signals                                          |      |

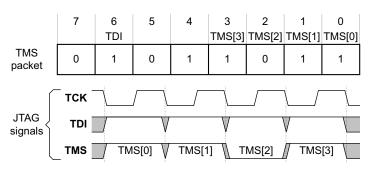

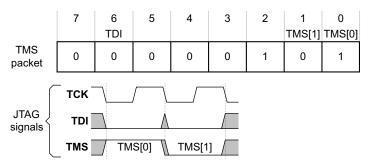

| Table 9-2   | Summary of JTAG Engine Byte Command Protocol                                | 9-10 |

| Table 9-3   | TMS packet encodings                                                        |      |

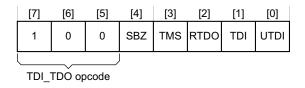

| Table 9-4   | TDI_TDO first byte (opcode) format                                          |      |

| Table 9-5   | TDI_TDO second byte (length byte), packed format                            |      |

| Table 10-1  | Summary of the common Access Port (AP) register                             |      |

| Table 10-2  | AP Identification Register, IDR, bit assignments                            | 10-4 |

| Table 10-3  | ARM AP Identification types                                                 |      |

| Table 11-1  | Summary of Memory Access Port (MEM-AP) registers                            |      |

| Table 11-2  | Access information for the MEM-AP registers                                 |      |

| Table 11-3  | Bit assignments for the MEM-AP Control/Status Word Register, CSW            |      |

| Table 11-4  | Bit assignments for the Transfer Address Register, TAR                      |      |

| Table 11-5  | Bit assignments for the Data Read/Write Register, DRW                       |      |

| Table 11-6  | Mapping of Banked Data Registers onto memory addresses                      |      |

| Table 11-7  | Bit assignments for the Banked Data Registers, BD0 to BD3                   |      |

| Table 11-8  | Bit assignments for the Configuration Register, CFG,                        |      |

| Table 11-9  | Bit assignments for the Debug Base Address Register, BASE,                  |      |

| Table 11-10 | Legacy Debug Base Address Register format when there are no debug er 11-14  |      |

| Table 11-11 | Legacy Debug Base Address Register format when holding a base address 11-14 |      |

| Table 12-1  | Summary of JTAG Access Port (JTAG-AP) registers                             | 12-2 |

| Table 12-2  | Bank and Offset values for accessing the JTAG-AP registers                  |      |

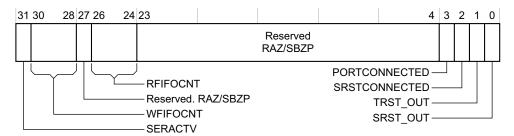

| Table 12-3  | Bit assignments for the JTAG-AP Control/Status Word Register, CSW           |      |

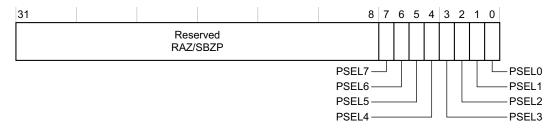

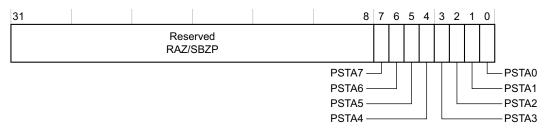

| Table 12-4  | Bit assignments for the JTAG-AP Port Select Register, PSEL                  |      |

| Table 12-5  | Bit assignments for the JTAG-AP Port Status Register, PSTA                  |      |

| Table 13-1  | Summary of Component and Peripheral ID Registers                            |      |

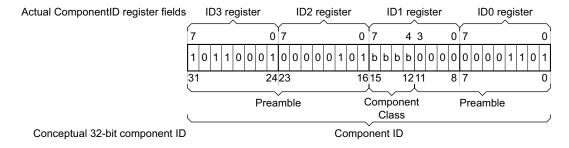

| Table 13-2  | Summary of the Component Identification Registers                           |      |

| Table 13-3  | Component Class values in the Component ID                                  |      |

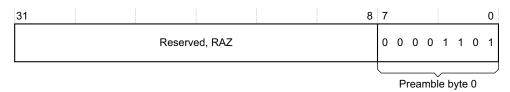

| Table 13-4  | Component ID0 Register bit assignments                                      |      |

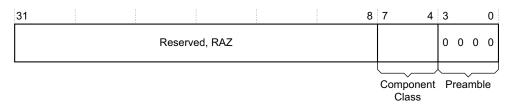

| Table 13-5  | Component ID1 Register bit assignments                                      |      |

| Table 13-6  | Component ID2 Register bit assignments                                      | 13-7 |

| Table 13-7  | Component ID3 Register bit assignments                      | 13-8  |

|-------------|-------------------------------------------------------------|-------|

| Table 13-8  | Summary of the peripheral identification registers          | 13-9  |

| Table 13-9  | Register fields for the peripheral identification registers | 13-10 |

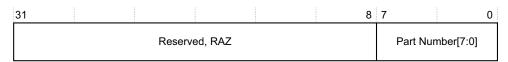

| Table 13-10 | Peripheral ID0 Register bit assignments                     | 13-12 |

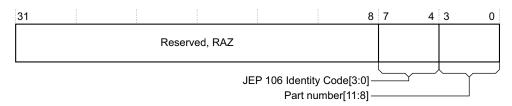

| Table 13-11 | Peripheral ID1 Register bit assignments                     | 13-13 |

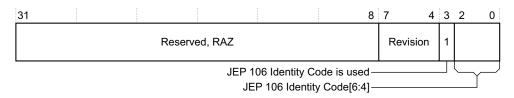

| Table 13-12 | Peripheral ID2 Register bit assignments                     | 13-14 |

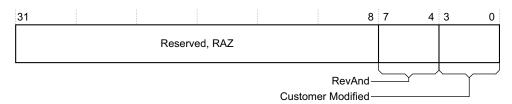

| Table 13-13 | Peripheral ID3 Register bit assignments                     | 13-14 |

| Table 13-14 | Peripheral ID4 Register bit assignments                     | 13-15 |

| Table 13-15 | Peripheral ID5 to Peripheral ID7 Registers, bit assignments | 13-16 |

| Table 13-16 | Identification Registers for a legacy component             | 13-17 |

| Table 14-1  | ROM Table regions                                           | 14-2  |

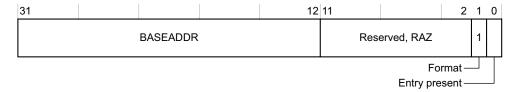

| Table 14-2  | Format of a ROM Table entry                                 | 14-5  |

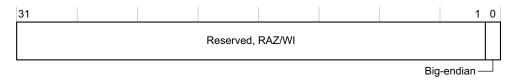

| Table 14-3  | MEMTYPE Register bit assignments                            | 14-9  |

# List of Figures ARM Debug Interface v5 Architecture Specification

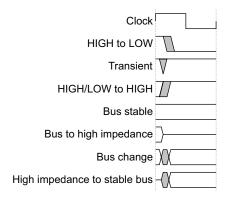

|            | Key to timing diagram conventionsx                                              | ίXΙ |

|------------|---------------------------------------------------------------------------------|-----|

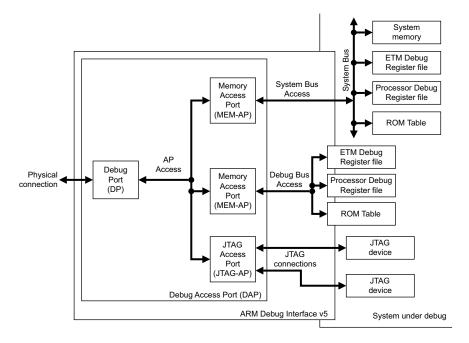

| Figure 1-1 | Subdivisions of an ARM Debug Interface                                          | -5  |

| Figure 1-2 | Debug Port options and their connections 1                                      | -7  |

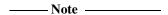

| Figure 1-3 | Simple ARM Debug Interface MEM-AP Implementation 1                              | -8  |

| Figure 1-4 | Simple ARM Debug Interface JTAG-AP Implementation 1                             | -8  |

| Figure 1-5 | Complex ARM Debug Interface, showing the Access Port options 1                  | -9  |

| Figure 2-1 | Simple example of an ARM Debug Interface implementation, with ROM Table 2-7     |     |

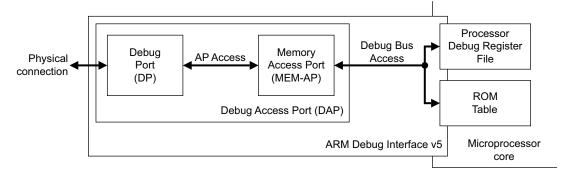

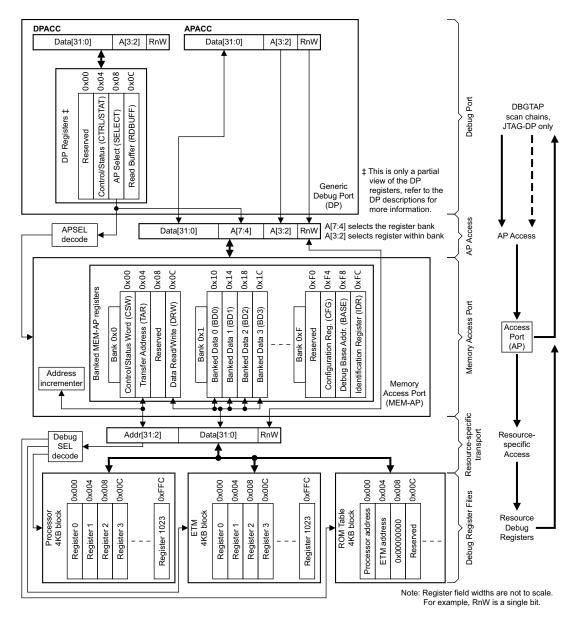

| Figure 2-2 | Structure of the Debug Access Port, showing JTAG-DP accesses to a generic A 2-9 | Ρ   |

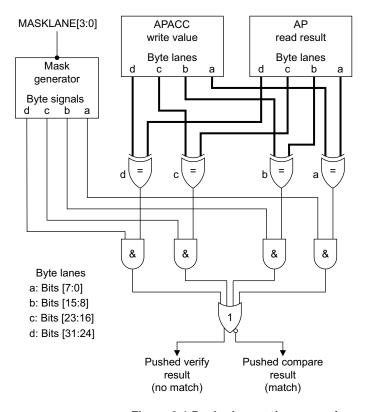

| Figure 3-1 | Pushed operations overview 3                                                    | -6  |

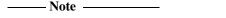

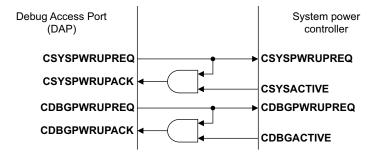

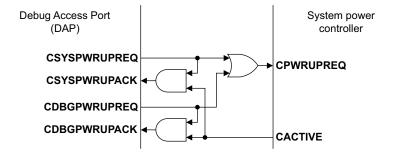

| Figure 3-2 | Power-up request and acknowledgement timing 3-                                  | 12  |

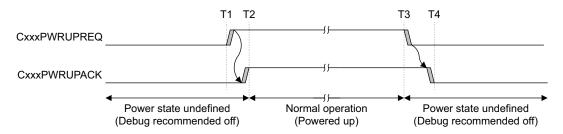

| Figure 3-3 | Emulation of power-up control 3-                                                | 13  |

| Figure 3-4 | Generation of ACK signals from REQ and ACITVE signals 3-                        | 13  |

| Figure 3-5 | Signal generation for a single power domain                                     | 14  |

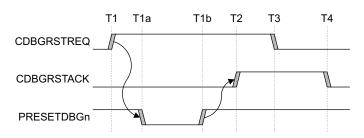

| Figure 3-6 | Reset request and acknowledge timing 3-                                         | 14  |

| Figure 4-1 | Mapping of the JTAG-DP scan chains onto the logical levels of the ARM Debug I   | n-  |

|            | terface 4                                                                       |     |

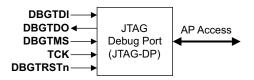

| Figure 4-2 | JTAG-DP physical connection 4                                                   | -4  |

| Figure 4-3 | The Debug TAP State Machine (DBGTAPSM) 4                                        |     |

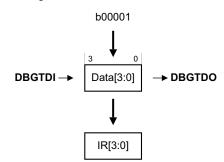

| Figure 4-4 | JTAG-DP Instruction Register operation                                          | -8  |

|            |                                                                                 |     |

| Figure 4-5  | JTAG-DP Bypass Register operation                                           | 4-12  |

|-------------|-----------------------------------------------------------------------------|-------|

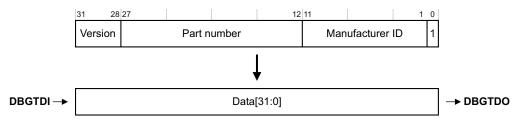

| Figure 4-6  | JTAG-DP Device ID Code Register operation                                   |       |

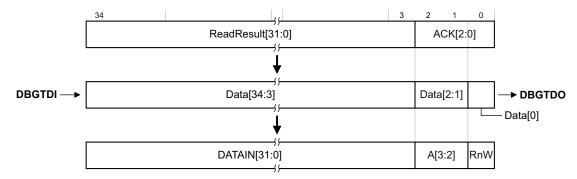

| Figure 4-7  | Operation of JTAG-DP DP Access and AP Access Registers                      |       |

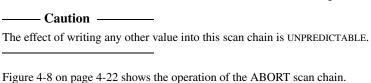

| Figure 4-8  | JTAG-DP ABORT scan chain operation                                          |       |

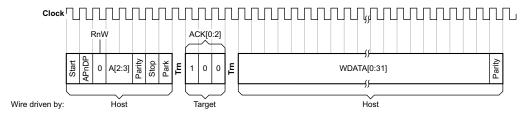

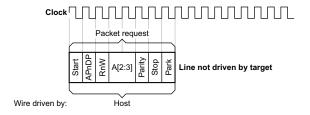

| Figure 5-1  | Serial Wire Debug successful write operation                                |       |

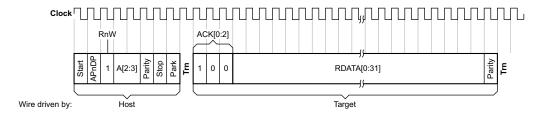

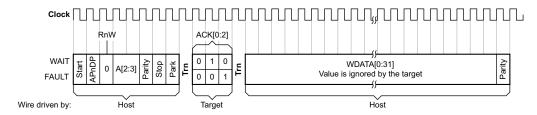

| Figure 5-2  | Serial Wire Debug successful read operation                                 |       |

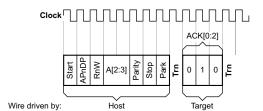

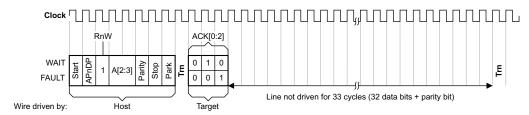

| Figure 5-3  | Serial Wire Debug WAIT response to a packet request                         | . 5-8 |

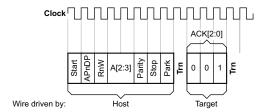

| Figure 5-4  | Serial Wire Debug FAULT response to a packet request                        |       |

| Figure 5-5  | Serial Wire Debug protocol error after a packet request                     | . 5-9 |

| Figure 5-6  | Serial Wire WAIT or FAULT response to a read operation                      |       |

|             | when overrun detection is enabled                                           | 5-13  |

| Figure 5-7  | Serial Wire WAIT or FAULT response to a write operation                     |       |

|             | when overrun detection is enabled                                           | 5-13  |

| Figure 6-1  | AP Abort Register bit assignments                                           | . 6-6 |

| Figure 6-2  | Identification Code Register bit assignments                                |       |

| Figure 6-3  | Control/Status Register bit assignments                                     | 6-10  |

| Figure 6-4  | Select Register, SELECT, bit assignments                                    |       |

| Figure 6-5  | Wire Control Register bit assignments (SW-DP only)                          |       |

| Figure 8-1  | MEM-AP connecting the DP to debug components                                |       |

| Figure 9-1  | JTAG-AP connecting the DP to JTAG devices                                   |       |

| Figure 9-2  | Structure of the JTAG Access Port (JTAG-AP)                                 |       |

| Figure 9-3  | TMS packet example with TDI held at 1                                       |       |

| Figure 9-4  | TMS packet example with TDI held at 0                                       | 9-12  |

| Figure 9-5  | TDI_TDO first byte (opcode) format                                          |       |

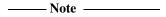

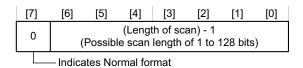

| Figure 9-6  | TDI_TDO second byte (length byte), normal format                            |       |

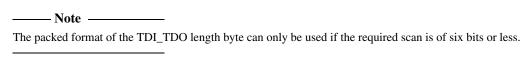

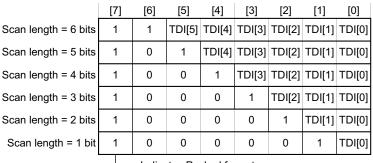

| Figure 9-7  | TDI_TDO second byte (length byte), packed format                            | 9-15  |

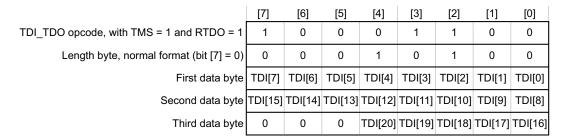

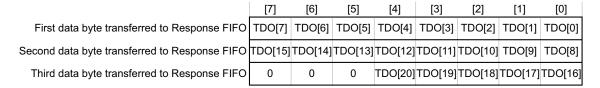

| Figure 9-8  | TDI_TDO formatting example. Complete packet for a scan of 21 TCK cycles     | 9-17  |

| Figure 9-9  | TDI_TDO response data formatting example. Scan of 21 TCK cycles             |       |

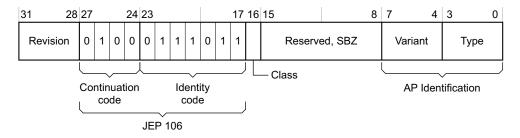

| Figure 10-1 | The AP Identification Register, IDR, for an ARM Limited AP implementation   | 10-3  |

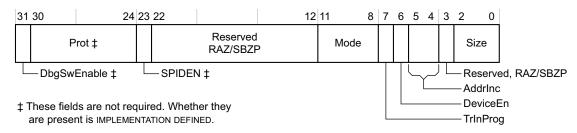

| Figure 11-1 | MEM-AP Control/Status Word Register, CSW, bit assignments                   |       |

| Figure 11-2 | Configuration Register, CFG, bit assignments                                |       |

| Figure 11-3 | Debug Base Address Register, BASE, bit assignments                          |       |

| Figure 12-1 | JTAG-AP Control/Status Word Register, CSW, bit assignments                  |       |

| Figure 12-2 | JTAG-AP Port Select Register, PSEL, bit assignments                         |       |

| Figure 12-3 | JTAG-AP Port Status Register, PSTA, bit assignments                         |       |

| Figure 12-4 | Bit assignments for the Byte Read FIFO Registers, BRFIFO1 to BRFIFO4        |       |

| Figure 12-5 | Bit assignments for the Byte Write FIFO Registers, BWFIFO1 to BWFIFO4       |       |

| Figure 13-1 | Mapping between the Component ID Registers and the Component ID value 13-4  |       |

| Figure 13-2 | Component ID0 Register bit assignments                                      |       |

| Figure 13-3 | Component ID1 Register bit assignments                                      |       |

| Figure 13-4 | Component ID2 Register bit assignments                                      |       |

| Figure 13-5 | Component ID3 Register bit assignments                                      |       |

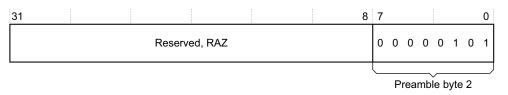

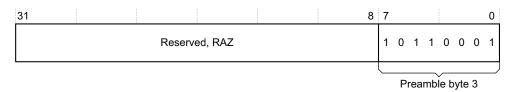

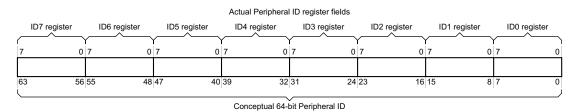

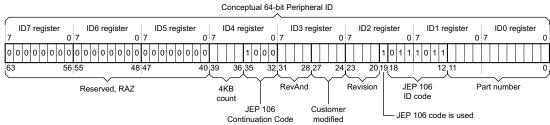

| Figure 13-6 | Mapping between the Peripheral ID Registers and the Peripheral ID value $ $ |       |

| Figure 13-7 | Peripheral ID fields                                                        |       |

| Figure 13-8 | Peripheral ID0 Register bit assignments                                     |       |

| Figure 13-9 | Peripheral ID1 Register bit assignments                                     | 13-12 |

| Figure 13-10 | Peripheral ID2 Register bit assignments                     | 13-13  |

|--------------|-------------------------------------------------------------|--------|

| Figure 13-11 | Peripheral ID3 Register bit assignments                     | 13-14  |

| Figure 13-12 | Peripheral ID4 Register bit assignments                     | 13-15  |

| Figure 13-13 | Peripheral ID5 to Peripheral ID7 Registers, bit assignments | 13-16  |

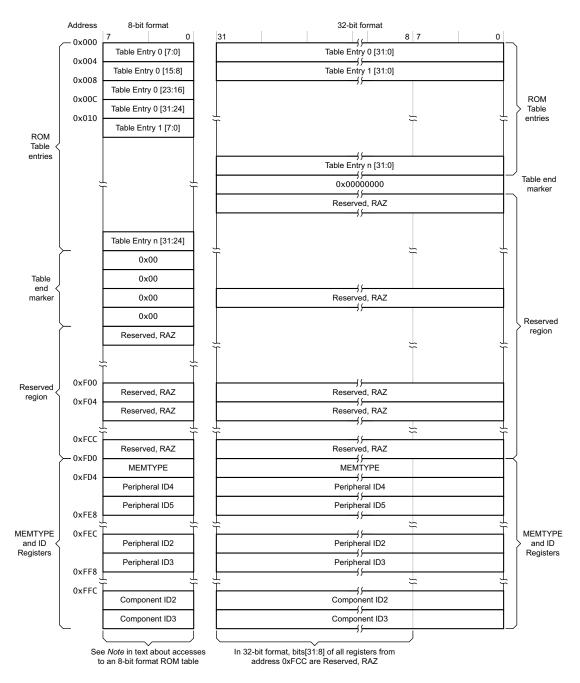

| Figure 14-1  | ROM Table formats, for 8-bit and 32-bit ROM                 | . 14-3 |

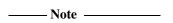

| Figure 14-2  | MEMTYPE Register bit assignments                            | . 14-9 |

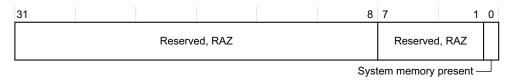

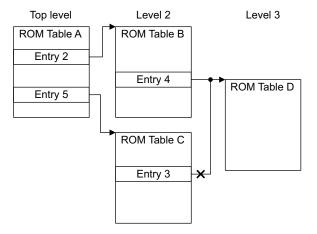

| Figure 14-3  | ROM Table hierarchy example                                 | 14-12  |

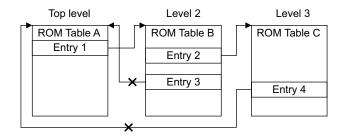

| Figure 14-4  | Prohibited duplicate ROM Table reference                    | 14-14  |

| Figure 14-5  | Prohibited circular ROM Table references                    | 14-14  |

### **Preface**

This preface introduces the *ARM Debug Interface v5 Architecture Specification*. It contains the following sections:

- About this specification on page xviii

- Conventions on page xx

- Further reading on page xxii

- Feedback on page xxiii.

#### About this specification

This is the Architecture Specification for the ARM Debug Interface v5 (ADIv5).

#### Intended audience

This specification is written for system designers and engineers who are specifying, designing or implementing a debug interface to the ADIv5 architecture specification. This includes system designers and engineers who are specifying, designing or implementing a *System-on-Chip* (SoC) device that incorporates a debug interface that complies with the ADIv5 specification.

This specification provides an architectural description of the ARM Debug Interface. It does not describe how to implement the interface.

This specification is also intended for engineers who are working with a debug interface that conforms to the ADIv5 specification. This includes:

- designers and engineers who are specifying, designing or implementing hardware debuggers

- those specifying, designing or writing debug software.

These engineers have no control over the design decisions made in the ARM Debug Interface implementation to which they are connecting, but must be able to identify the ADI components that are present, and understand how they operate.

#### Using this manual

This specification is organized into the following chapters:

#### Chapter 1 Introduction

Read this chapter for a high-level view of the *ARM Debug Interface* (ADI). This chapter defines the logical subdivisions of an ADI, and summarizes the design choices made when implementing an ADI.

#### Chapter 2 Overview of the ARM Debug Interface and its components

Read this chapter for a simple description of each of the components that might be included in an ADI, and for an introduction to the register model for accessing an ADI.

#### Chapter 3 Common Debug Port (DP) features

Read this chapter for a description of the features that must be implemented on the *Debug Port* (DP) of an ADI.

Every ADI includes a single DP, either a *JTAG Debug Port* (JTAG-DP) or a *Serial Wire Debug Port* (SW-DP)

#### Chapter 4 The JTAG Debug Port (JTAG-DP)

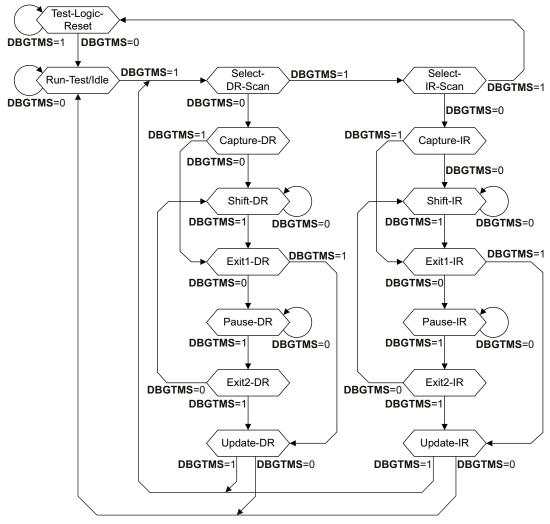

Read this chapter for a description of the *JTAG Debug Port* (JTAG-DP), and in particular the Debug Test Access Port State Machine (DBGTAPSM) and the scan chains that are used to access the JTAG-DP.

#### Chapter 5 The Serial Wire Debug Port (SW-DP)

Read this chapter for a description of the *Serial Wire Debug Port* (SW-DP), and the Serial Wire Debug protocol used for accesses to a SW-DP.

#### Chapter 6 Debug Port Registers

Read this chapter for a description of the Debug Port Registers.

Most of these registers are common to the JTAG-DP and the SW-DP, and the chapter describes the differences between the JTAG-DP and the SW-DP register implementations.

#### Chapter 7 Common Access Port (AP) features

Read this chapter for a description of ADI *Access Ports* (APs), and details of the features that every AP must implement.

#### Chapter 8 The Memory Access Port (MEM-AP)

Read this chapter for a description of the ADI *Memory Access Port* (MEM-AP).

#### Chapter 9 The JTAG Access Port (JTAG-AP)

Read this chapter for a description of the ADI JTAG Access Port (JTAG-AP).

#### Chapter 10 Access Port (AP) Registers Overview and the Common AP Register

Read this chapter for an overview of the AP registers, and for a description of the registers that are common to all ADI APs.

#### Chapter 11 Memory Access Port (MEM-AP) Registers

Read this chapter for a description of the MEM-AP register implementation.

#### Chapter 12 JTAG Access Port (JTAG-AP) Registers

Read this chapter for a description of the JTAG-AP register implementation.

#### Chapter 13 Component and Peripheral ID Registers

Read this chapter for a description of the Component and Peripheral ID Registers. These registers are part of the register space of every debug component that complies with the ADIv5 architecture specification.

#### Chapter 14 ROM Tables

Read this chapter for a description of ARM debug component ROM Tables. Any ADI can include a ROM Table, and an ADI with more than one debug component must include at least one ROM Table.

**Glossary** Read the Glossary for definitions of some of the terms used in this specification.

#### Conventions

Conventions that this specification can use are described in:

- Typographic

- Timing diagrams

- Signals on page xxi.

#### **Typographic**

The typographical conventions are:

italic Highlights important notes, introduces special terminology, and denotes internal

cross-references and citations.

bold Highlights interface elements, such as menu names. Denotes signal names. Also

used for terms in descriptive lists, where appropriate.

monospace Denotes text that you can enter at the keyboard, such as commands, file and program

names, and source code.

SMALL CAPITALS Denote a few terms that have specific technical meanings. Their meanings can be

found in the Glossary.

< and > Angle brackets enclose replaceable terms for assembler syntax where they appear

in code or code fragments. These terms appear in normal font in running text. For

example:

MRC p15, 0 <Rd>, <CRn>, <CRm>, <Opcode\_2>

The Opcode\_2 value selects which register is accessed.

#### Timing diagrams

The figure named *Key to timing diagram conventions* on page xxi explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

#### Key to timing diagram conventions

#### **Signals**

The signal conventions are:

Signal level The level of an asserted signal depends on whether the signal is active-HIGH or

active-LOW. Asserted means HIGH for active-HIGH signals and LOW for

active-LOW signals.

**Lower-case n** Denotes an active-LOW signal.

**Prefix DBG** Denotes debug signals.

#### **Further reading**

This section lists publications by ARM Limited, and by third parties.

ARM Limited periodically provides updates and corrections to its documentation. See http://www.arm.com for current errata sheets, addenda, and the Frequently Asked Questions list.

#### **ARM** publications

This specification contains information that is specific to the ARM Debug Interface architecture specification. See the following documents for other relevant information:

- ETM Architecture Specification (ARM IHI 0014)

- CoreSight Design Kit Technical Reference Manual (ARM DDI 0314)

- CoreSight Architecture Specification (ARM IHI 0029)

- ARM Architecture Reference Manual Debug Supplement (ARM DDI 0379).

#### Other publications

This section lists relevant documents published by third parties:

- IEEE 1149.1-2001 IEEE Standard Test Access Port and Boundary Scan Architecture (JTAG)

- JEP106M, Standard Manufacture's Identification Code, JEDEC Solid State Technology Association.

#### **Feedback**

ARM Limited welcomes feedback on the ARM Debug Interface architecture specification.

#### Feedback on this specification

If you have any comments on this specification, send email to errata@arm.com giving:

- the document title

- the document number

- the relevant page number(s) to which your comments apply

- a concise explanation of your comments.

ARM Limited also welcomes general suggestions for additions and improvements.

Preface

## Chapter 1 Introduction

This chapter introduces the ARM Debug Interface architecture and summarizes the design decisions required for an ARM Debug Interface implementation. It contains the following sections:

- About the ARM Debug Interface version 5 (ADIv5) on page 1-2

- The function of the ARM Debug Interface on page 1-3

- The subdivisions of an ARM Debug Interface on page 1-5

- Design choices for an ARM Debug Interface v5 implementation on page 1-6.

#### 1.1 About the ARM Debug Interface version 5 (ADIv5)

ADIv5 is the fifth major version of the ARM Debug Interface.

All previous versions of the ADI are based on the IEEE 1149.1 JTAG interface, but are intended only for accessing ARM processor cores and *Embedded Trace Macrocells* (ETMs):

#### Debug interface versions 1 and 2

Implemented on the ARM7TDMI® and ARM9® families of processor cores.

#### Debug interface version 3

Introduced for the ARM10<sup>™</sup> processor family.

ADIv4 The first version of the ADI to be linked with an ARM architecture version, rather than an implementation of an ARM processor core. ARM Limited recommends that ADIv4 is used with implementations of the ARMv6 architecture.

ADIv5 removes the link between the ADI and ARM processor cores. An implementation of ADIv5 can access any debug component that complies with the ADIv5 specification. The details of the resources accessed by ADIv5 are defined by the resources, rather than the ADI.

ADIv5 has three major advantages:

- ADIv5 interfaces can access a greater range of devices.

- Implementation of the ADI can be separated from implementation of the resource, enabling greater reuse of implementations. However, this separation is not required.

- Use of the ADIv5 abstractions permits reuse of software tools, such as debuggers.

Versions 1 to 4 of the debug interface require the physical connection to the interface to use an IEEE 1149.1 JTAG interface. ADIv5 specifies two alternatives for the physical connection:

- an IEEE 1149.1 JTAG interface

- a low pin count Serial Wire interface.

#### 1.2 The function of the ARM Debug Interface

This chapter describes the context in which an ARM Debug Interface (ADI) might be implemented.

This section gives a summary of the types of debug functionality provided by debug components in an embedded *System on Chip* (SoC). This information is given in the subsections:

- Embedded core debug functionality.

- System debug functionality on page 1-4.

The ADI is designed to provide easy access to Soc debug components.

See Compatibility between CoreSight and ARM Debug interfaces on page 1-4 for information about compatibility with the CoreSight™ architecture.

#### 1.2.1 Embedded core debug functionality

To enable applications to be debugged, an embedded microprocessor might provide facilities that enable you to:

- Modify the state of the processor. An external host must be able to modify the contents of the internal registers and the memory system.

- Determine the state of the processor. An external host must be able to read the values of the internal registers, and read from the memory system.

- Program debug events. An external host must be able to configure the debug logic so that when a

special event occurs, such as the program flow reaching a certain instruction in the code, the core

enters a special execution mode in which its state can be examined and modified by an external

system. In this chapter, this special execution mode is referred to as *Debug state*.

- Force the processor to enter or exit Debug state from an external system.

- Determine when the core enters or leaves Debug state.

- Trace program flow around programmable events.

Two examples of technologies that provide these facilities are:

- the ARMv7 Debug Architecture, see the ARM Architecture Reference Manual Debug Supplement

- the Embedded Trace Macrocell, see the ETM Architecture Specification.

In addition, the ARM Debug Interface v5 enables you to access legacy components that implement an IEEE 1149.1 JTAG interface. This means that the ADIv5 can access processors that implement earlier versions of the ADI.

#### 1.2.2 System debug functionality

Debug extends beyond the boundaries of an embedded microprocessor core. Engineers must be able to debug:

- components within an embedded SoC

- the interconnection fabric of the system.

Examples of debug facilities that might be provided at the system level, outside the embedded microprocessor core, include:

- Facilities to:

- Examine the state of the system, including state that might not be visible to the embedded microprocessor core.

- Trace accesses on the interconnection fabric. These might be accesses by the microprocessor core, or accesses by other devices such as *Direct Memory Access* (DMA) engines.

- Mechanisms for low-intrusion diagnostic messaging between software and a debugger.

- Cross-triggering mechanisms that enable debug components to signal each other.

- A fabric for the efficient streaming and collection of diagnostic information, such as program trace.

Ideally, functions operate with minimal change to the behavior of the system being debugged.

Examples of technologies that provide these facilities are:

- the ADI

- the CoreSight debug architecture, and the CoreSight components:

- CoreSight AHB Trace Macrocell (HTM)

- CoreSight Instrumentation Trace Macrocell (ITM)

- CoreSight Embedded Cross-Trigger (ECT)

- the  $AMBA^{\mathsf{TM}}$  Trace Bus (ATB) components.

For more information see the CoreSight Architecture Specification and the CoreSight Design Kit Technical Reference Manual.

#### 1.2.3 Compatibility between CoreSight and ARM Debug interfaces

ADIv5 is designed to be compatible with the ARM CoreSight architecture:

- a CoreSight interface implementation is a valid implementation of ADIv5

- the ADIv5 specification does not require an ADI to be CoreSight compliant.

The CoreSight Design Kit Technical Reference Manual includes a description of the CoreSight interface, the CoreSight Debug Access Port.

#### 1.3 The subdivisions of an ARM Debug Interface

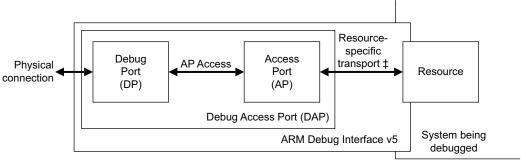

Figure 1-1 shows the logical subdivisions of an ADIv5.

‡ For example, a debug bus

Figure 1-1 Subdivisions of an ARM Debug Interface

\_\_\_\_\_Note \_\_\_\_\_

Although this specification logically divides the ARM Debug Interface into the elements shown in Figure 1-1, this specification does not require implementations to be structured in this way. This specification describes the programmer's model for the ADI, and these subdivisions give a convenient representation of the programmer's model.

#### 1.3.1 The conventional model of the ADI

Figure 1-1 shows a conventional model for using an ADI. In this, the Access Port of the ADI connects through a resource-specific transport, such as a debug bus, to a resource that is part of the system being debugged. This model is used extensively in this specification.

The ADI components defined by this specification include two alternatives for the resource-specific transport that connects the ADI to the system being debugged:

- An ADI can be used to connect to a memory-mapped resource, such as a debug peripheral. For such

connections the ADI defines a *Memory Access Port* (MEM-AP) programmer's model.

- An ADI can be used to connect to a legacy IEEE 1149.1 JTAG device. For such connections the ADI

defines a JTAG Access Port (JTAG-AP) and associated programmer's model.

This specification does not mandate the transport between the AP and the resource. In particular, it does not require an MEM-AP to use a bus to connect to the system being debugged. For example, an ADI might be directly integrated into the resource. However, referring to Figure 1-1, logically a MEM-AP always accesses a memory-mapped resource in the *system being debugged*. For this reason, this specification describes MEM-AP accesses to the system being debugged as *memory accesses*.

#### 1.4 Design choices for an ARM Debug Interface v5 implementation

The subdivisions of an ARM Debug Interface on page 1-5 introduces the logical subdivisions of an ARM

| Debug Interface, shown in Figure 1-1 on page 1-3. This section outlines the design choices that must be |

|---------------------------------------------------------------------------------------------------------|

| made before implementing an ARM Debug Interface. The following subsections consider each of the two     |

| functional blocks of the interface:                                                                     |

| • Choices for the Debug Port (DP)                                                                       |

| • Choices for the Access Ports (APs) on page 1-7.                                                       |

| Note                                                                                                    |

| This Audit at the Consideration is suited for an important in all most an ADM Dalor Later for an in-    |

This Architecture Specification is written for engineers wanting to implement an ARM Debug Interface, and for those using an ARM Debug Interface. If you are reading the Specification to learn more about a particular ARM Debug Interface implementation you must understand the design choices that have been made in that implementation. Those choices might be implicit in the connections to the Debug Interface. If you are uncertain about the choices you must obtain details from the implementor of the Debug Interface.

The Debug Port and Access Port implementations are described in more detail in Chapter 2 Overview of the ARM Debug Interface and its components.

#### 1.4.1 **Choices for the Debug Port (DP)**

An ARM Debug Interface has a single Debug Port. There are two implementation options for the DP, and these are summarized in the following subsections:

- The Serial Wire Debug Port (SW-DP)

- The JTAG Debug Port (JTAG-DP) on page 1-7.

If you are designing or specifying an ARM Debug Interface you must decide which of these Debug Ports to implement.

| Note        |                                       |

|-------------|---------------------------------------|

| ARM Limited | might define other DPs in the future. |

#### The Serial Wire Debug Port (SW-DP)

The SW-DP is a low pin count interface that uses a packet-based protocol to read or write register information. It is based on the CoreSight Serial Wire interface.

|         | Note ———                                            |                       |

|---------|-----------------------------------------------------|-----------------------|

| Contact | ARM Limited for details of tools support for the Se | erial Wire Debug Port |

#### The JTAG Debug Port (JTAG-DP)

The JTAG-DP is based on the *IEEE 1149.1 Test Access Port (TAP) and Boundary Scan Architecture*, widely referred to as JTAG.

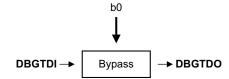

With the JTAG-DP, IEEE 1149.1 scan chains are used to read or write register information.

Only the logical Debug TAP State Machine (DBGTAPSM) architecture and associated support instructions and scan chain are included in this specification. The precise physical interface and mechanism for performing DBGTAPSM transactions are not mandated, and are not described here. However, ARM Limited recommends that an interface compatible with the IEEE 1149.1 standard is used.

#### **Connections to the Debug Port**

Figure 1-2 shows the connections to each of the Debug Port implementations:

Figure 1-2 Debug Port options and their connections

#### 1.4.2 Choices for the Access Ports (APs)

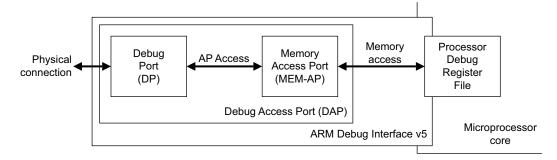

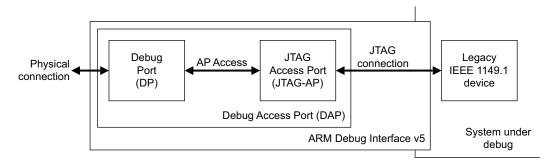

An ARM Debug Interface always includes at least one Access Port, and might contain multiple APs. The simplest ARM Debug Interface uses a single AP to connect to a single debug component. The basic examples of this are:

- using an MEM-AP to connect to a single debug component, such as a microprocessor core, as shown in Figure 1-3 on page 1-8

- using a JTAG-AP to connect to a single legacy IEEE 1149.1 device, as shown in Figure 1-4 on page 1-8.

Figure 1-3 Simple ARM Debug Interface MEM-AP Implementation

Figure 1-4 Simple ARM Debug Interface JTAG-AP Implementation

However, because a single ADI can include multiple APs, the design choices relating to APs are at two levels:

- Choices about the number of APs in the ADI, and whether each AP is a MEM-AP or a JTAG-AP.

These decisions are considered in *Top-level AP planning choices*.

- The choices that have to be made for each implemented AP. These choices are considered in:

- Choices for each JTAG-AP on page 1-11

- Choices for each MEM-AP on page 1-10.

#### **Top-level AP planning choices**

In a more complex debug system, three ways in which an AP can be implemented are:

- As a *Memory Access Port* (MEM-AP) with a memory-mapped Debug Bus connection. The Debug Bus connects directly to one or more Debug Register Files.

- As a Memory Access Port with a memory-mapped System Bus connection. The MEM-AP

connection to the System Bus provides access to one or more Debug Register Files.

As a JTAG Access Port (JTAG-AP). This connects directly to one or more JTAG devices, and enables

connection to legacy hardware components.

\_\_\_\_\_ Note \_\_\_\_\_

The connection between legacy hardware components and a JTAG-AP is defined by the JTAG standard. For more information see Chapter 9 *The JTAG Access Port (JTAG-AP)*.

If you are designing or specifying an ARM Debug Interface you must decide how many APs are required, and how each of them is implemented. This depends largely on the debug components of the system to which your ADI connects.

Figure 1-5 shows a more complex ARM Debug Interface, and illustrates the different Access Port options.

Figure 1-5 Complex ARM Debug Interface, showing the Access Port options

The ARM Debug Interface v5 architecture specification:

- Supports additional Access Ports. Every Access Port must follow the base standard for identification

given in this specification. Debuggers must be able to ignore Access Ports that they do not recognize.

- Permits multiple register files to be accessed by a single Memory Access Port. This specification

includes a base standard for register file identification, and debuggers must be able to ignore register

files that they do not recognize or do not support.

- Permits a Memory Access Port to access a mixture of system memory and Debug Register files.

In any ARM Debug Interface v5 implementation, such as those illustrated in Figure 1-3 on page 1-8 and Figure 1-5 on page 1-9, the Debug Port can be either an SW-DP or a JTAG-DP. The physical connections to each of these options are shown in Figure 1-2 on page 1-7.

#### Choices for each MEM-AP

The main decisions to be made for a MEM-AP concern the connection between the MEM-AP and the memory-mapped debug components connected to it. These decisions depend, largely, on the requirements of those debug components. They include:

- whether a bus is required for this connection

- if a bus connection is implemented, the width of the bus

- the memory map of the MEM-AP address space.

If an ADI MEM-AP connects to more than one debug component then the system must include one or more *ROM Tables*, to provide information about the debug system. However, a system designer might chose to include a ROM Table in a system that has only one other component. See *ROM Tables* on page 8-2 for more information.

It is IMPLEMENTATION DEFINED whether a MEM-AP includes certain features, for more information see:

- *MEM-AP functions* on page 8-8

- *MEM-AP implementation requirements* on page 8-24.

The implementation of the connection between the MEM-AP and the debug components can determine whether some of these features are included. In particular, certain features must be included if the connection is less than 32-bits wide. The debug components themselves might place limitations on the connection, for example a component might require 32-bit accesses.

For more information about implementing a MEM-AP see Chapter 8 The Memory Access Port (MEM-AP).

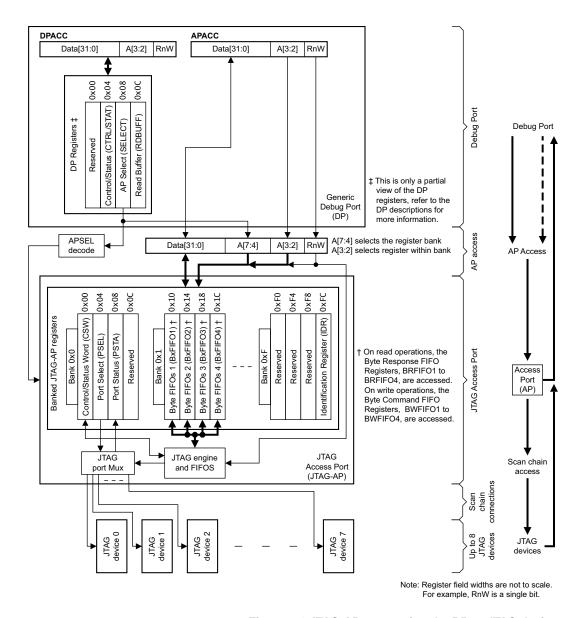

#### Choices for each JTAG-AP

A single JTAG-AP can connect to up to eight JTAG scan chains. These scan chains can be split across multiple devices or components within the system being debugged.

In addition, a single JTAG scan chain can contain multiple TAPs. However ARM Limited recommends that each scan chain connected to a JTAG-AP contains only one TAP.

Therefore, the design decisions that must be made for each JTAG-AP are:

- How many JTAG scan chains are connected to the JTAG-AP?

- Do any of the scan chains contain more than one TAP?

For more information see Chapter 9 The JTAG Access Port (JTAG-AP).

Introduction

## Chapter 2

# Overview of the ARM Debug Interface and its components

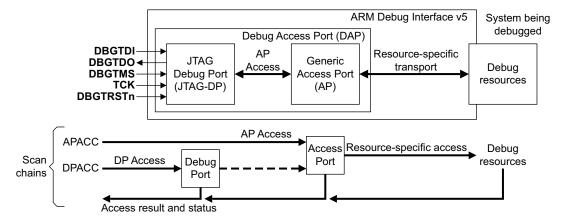

This section introduces the components of the ARM Debug Interface, in more detail than the descriptions in Chapter 1 *Introduction*. It also describes how the *Debug Access Port* (DAP) is used to access registers within the DAP and in the connected system. This description is based on JTAG-DP accesses to a Debug Interface, and shows how registers are located at different levels within the Debug Interface model.

This chapter contains the following sections:

- ARM Debug Interface overview on page 2-2

- The external interface, the Debug Port (DP) on page 2-3

- The resource interface, the Access Ports (APs) on page 2-5

- *ARM Debug Interface implementation examples* on page 2-7

- Accessing Access Ports on page 2-8.

## 2.1 ARM Debug Interface overview

Logically, the ARM Debug Interface (ADI) consists of:

- A number of registers that are private to the ADI. These are referred to as the *Debug Access Port* (DAP) Registers.

- A means to access the DAP registers.

- A means to access the debug registers of the debug components to which the ADI is connected.

This logical organization of the ADI is shown in Figure 1-1 on page 1-5.

Because the DAP logically consists of two parts, the Debug Port and Access Ports, it must support two types of access:

- Access to the Debug Port (DP) registers. This is provided by Debug Port accesses (DPACC).

- Access to Access Port (AP) registers. This is provided by Access Port accesses (APACC).

An ADI can include multiple Access Ports.

An AP is responsible for accessing debug component registers, such as processor debug logic, ETM and trace port registers. These accesses are made in response to APACC accesses in a manner defined by the AP.

The method of making these accesses depends on the Debug Port that is implemented, as summarized in *The external interface, the Debug Port (DP)* on page 2-3.

More generally, examples of possible targets of AP accesses include:

- the debug registers of the core processor

- ETM or Trace Port debug registers

- a ROM table, see Chapter 14 ROM Tables

- a memory system

- a legacy JTAG device.

## 2.2 The external interface, the Debug Port (DP)

An ARM Debug Interface implementation includes a single *Debug Port* (DP), that provides the external physical connection to the interface. The ARM Debug Interface v5 specification supports two DP implementations:

- the JTAG Debug Port (JTAG-DP), see *The JTAG Debug Port (JTAG-DP)*

- the Serial Wire Debug Port (SW-DP), see *The Serial Wire Debug Port (SW-DP)* on page 2-4.

These alternative DP implementations provide different mechanisms for making Access Port and Debug Port accesses. However, they have a number of common features. In particular, each implementation provides:

- a means of identifying the DAP, using an identification code scheme

- a means of making DP and AP accesses

- a means of aborting a register access that appears to have faulted.

#### 2.2.1 The JTAG Debug Port (JTAG-DP)

The JTAG-DP is based on the IEEE 1149.1 *Test Access Port* (TAP) and Boundary Scan Architecture, widely referred to as JTAG. Because the JTAG-DP is intended for accessing debug components, the naming conventions of IEEE 1149.1 are changed, as shown in Table 2-1:

Table 2-1 Comparison of IEEE 1149.1 and JTAG-DP naming

| IEEE 1149.1 | JTAG-DP  | JTAG-DP name                          |

|-------------|----------|---------------------------------------|

| TAP         | DBGTAP   | Debug Test Access Port.               |

| TAPSM       | DBGTAPSM | Debug Test Access Port State Machine. |

The signal naming conventions of IEEE 1149.1 are modified in a similar way, for example the IEEE 1149.1 **TDI** signal is named **DBGTDI** on a JTAG Debug Port. See *Physical connection to the JTAG-DP* on page 4-4 for the complete list of the JTAG-DP signal names.

For more information see IEEE 1149.1 Test Access Port and Boundary Scan Architecture.

With the JTAG-DP, IEEE 1149.1 scan chains are used to read or write register information. A pair of scan chain registers are used:

**DPACC** Used for Debug Port (DP) accesses.

**APACC** Used for Access Port (AP) accesses. An APACC access might access a register of a debug component of the system to which the interface is connected.

The scan chain model implemented by a JTAG-DP has the concepts of *capturing* the current value of APACC or DPACC, and of *updating* APACC or DPACC with a new value. An update might cause a read or write access to a DAP register that might then cause a read or write access to a debug register of a connected debug component.

The DBGTAP scan chains are described in more detail in Chapter 4 The JTAG Debug Port (JTAG-DP).

## 2.2.2 The Serial Wire Debug Port (SW-DP)

The Serial Wire Debug Port implementation provides a bi-directional serial connection to the ARM Debug Interface. It is based on the CoreSight Serial Wire Interface, and can be implemented as either a synchronous or an asynchronous serial port.

Communications with the SW-DP use a three-phase protocol:

- A host-to-target packet request.

- A target-to-host acknowledge response.

- A data transfer phase, if required. This can be target-to-host or host-to-target, depending on the request made in the first phase.

A packet request from a debugger indicates whether the required access is to a DP register (DPACC) or to an AP register (APACC), and includes a two-bit register address.

This protocol is described in more detail in Chapter 5 *The Serial Wire Debug Port (SW-DP)*.

## 2.3 The resource interface, the Access Ports (APs)

An Access Port provides the interface between an ADI and one or more debug components. This specification defines two Access Ports, and the complete description of each of these is summarized in:

- Guide to the detailed description of a MEM-AP

- Guide to the detailed description of a JTAG-AP on page 2-6.

ARM Limited might define additional access ports in the future. In addition, an ARM Debug Interface (ADI) might include additional access ports, not specified by ARM Limited.

All Access Ports *must* follow a base standard for identification, and debuggers must be able to recognize and ignore Access Ports that they do not support. For more information see Chapter 7 *Common Access Port* (AP) features.

As described in Chapter 1 Introduction:

- The simplest ADI has only one AP. This can be either a MEM-AP or a JTAG-AP.

- More complex ADIs can have multiple APs. These might be:

- a mixture of MEM-APs and JTAG-APs

- all MEM-APs

- all JTAG-APs.

The Debug Port uses exactly the same process for accessing MEM-APs and JTAG-APs. However the connection to the system being debugged is very different for MEM-APs and JTAG-APs. *Accessing Access Ports* on page 2-8 describes how to access any AP (MEM-AP or JTAG-AP), and summarizes how this gives access to resources in the system being debugged.

## 2.3.1 Guide to the detailed description of a MEM-AP

To understand the operation and use of a MEM-AP you must understand:

- the MEM-AP itself

- the MEM-AP registers

- the standard debug components registers, that you access through the MEM-AP.

The MEM-AP is described in the following chapters of this specification:

- Chapter 7 Common Access Port (AP) features

- Chapter 8 *The Memory Access Port (MEM-AP)*.

The MEM-AP registers are described in the following chapters of this specification:

- Chapter 10 Access Port (AP) Registers Overview and the Common AP Register

- Chapter 11 Memory Access Port (MEM-AP) Registers.

The MEM-AP provides access to one or more debug components. Any debug component that complies with the ARM Generic Identification Registers specification implements a set of Component Identification Registers. These are described in Chapter 13 *Component and Peripheral ID Registers*.

If the MEM-AP connects to more than one debug component then it must also include at least one ROM Table. ROM tables are accessed through a MEM-AP, and are described in Chapter 14 *ROM Tables*.

| ——Note ———                                                                                          |

|-----------------------------------------------------------------------------------------------------|

| As shown in Implementation examples with a single debug component on page 2-7, an ADI with only one |

| functional debug component might also implement a ROM Table.                                        |

|                                                                                                     |

## 2.3.2 Guide to the detailed description of a JTAG-AP

To understand the operation and use of a JTAG-AP you must understand:

- the JTAG-AP itself

- the JTAG-AP registers.

The JTAG-AP is described in the following chapters of this specification:

- Chapter 7 Common Access Port (AP) features

- Chapter 9 *The JTAG Access Port (JTAG-AP)*.

The JTAG-AP registers are described in the following chapters of this specification:

- Chapter 10 Access Port (AP) Registers Overview and the Common AP Register

- Chapter 12 JTAG Access Port (JTAG-AP) Registers.

| The JTAG-AP provides a standard JTAG connection to one or more legacy components. The connection           |   |

|------------------------------------------------------------------------------------------------------------|---|

| between the JTAG-AP and the components is described by the IEEE 1149.1-1990 IEEE Standard Test             |   |

| Access Port and Boundary Scan Architecture. Details of the use of this connection are outside the scope of | f |

| this specification.                                                                                        |   |

## 2.4 ARM Debug Interface implementation examples

To summarize the description of the ARM Debug Interface components it is useful to consider simple and more complex implementation examples.

## 2.4.1 Implementation examples with a single debug component

In the simplest ARM Debug Interface implementations, the interface connects to a single debug component. This is likely to be a microprocessor core that conforms to the ARMv7 Debug Architecture. The simplest possible implementation is shown in Figure 1-3 on page 1-8.

However, *ROM Tables* on page 8-2 explains that a system with only a single debug component often implements a ROM Table. This gives an implementation similar to the example shown in Figure 2-1.

Figure 2-1 Simple example of an ARM Debug Interface implementation, with ROM Table

## 2.4.2 Complex implementation example

In a more complex system, there can be multiple Access Ports, and each access port can be connected to multiple components, or multiple address spaces. An example of a more complex implementation is shown in Figure 1-5 on page 1-9.

In Figure 2-1, and in all other illustrations of the ARM Debug Interface, the Debug Port can be either a Serial Wire Debug Port or a JTAG Debug Port. See Figure 1-2 on page 1-7 for an illustration of the physical connection to each of these Debug Port options.

## 2.5 Accessing Access Ports

The Debug Port on an ADI provides the connection from an external debugger to the interface, and so to the system being debugged. Figure 2-2 on page 2-9 shows the different levels between the physical connection to the debugger and the debug resources of the system being debugged. These levels are designed to enable efficient access to the system being debugged, and several levels provide registers within the DAP. This section describes how these register accesses are implemented.

The DAP is split into two main control units, the Debug Port (DP) and the Access Port (AP), and the physical connection to the debugger is part of the DP. The DAP supports two types of access, Debug Port (DP) accesses and Access Port (AP) accesses. Because Debug Ports usually have serial interfaces, the methods of making these accesses are kept as short as possible. However, all accesses are 32-bits.

The description given here is of scan chain access to the registers, from a debugger connected to a JTAG Debug Port. However, the process is very similar when the access is from a Serial Wire Debug interface connection to a SW-DP. Differences when accessing the registers from a Serial Wire Debug interface connection are described in:

- Chapter 5 The Serial Wire Debug Port (SW-DP),

- Chapter 6 Debug Port Registers.

Every DP access transaction from the debugger includes two address bits, A[3:2]:

- for a DP register access, these bits determine which register is accessed

- these bits are also carried through into AP accesses, as summarized in Figure 2-2 on page 2-9.

One of the four registers within the DP is the AP Select Register, SELECT. This register specifies a particular Access Port, and a bank of four 32-bit words within the register map of that AP. It enables up to 256 Access Ports to be implemented, and gives access to any one of 16 four-word banks of registers on the selected AP.

In any AP access transaction from the debugger, the two address bits A[3:2] are decoded to select one of the four 32-bit words from the register bank indicated by the SELECT Register. In other words, they select a specific register within the selected four-register bank.

This access model is shown in Figure 2-2 on page 2-9. This figure shows how the contents of the SELECT register are combined with the A[3:2] bits of the APACC scan-chain to form the address of a register in an AP. Other parts of the JTAG-DP are also shown. These are explained in greater detail in later sections.

The implementation of this model is shown, also, in:

- Figure 8-1 on page 8-4, for a MEM-AP implementation

- Figure 9-1 on page 9-3, for a JTAG-AP implementation.

These figures give more details of the connections to the debug or system resources.

Figure 2-2 Structure of the Debug Access Port, showing JTAG-DP accesses to a generic AP

#### 2.5.1 Accessing debug resources

Accessing the AP gives access to the system being debugged, shown as the access to *Debug resources* in Figure 2-2 on page 2-9. The descriptions of the MEM-AP and JTAG-AP given earlier in this chapter show that the details of this access are very different for a MEM-AP and a JTAG-AP. In summary:

- With a MEM-AP, the debug resources are logically memory-mapped, and the connection between the MEM-AP and a debug resource is outside the scope of this specification. Chapter 8 *The Memory* Access Port (MEM-AP) describes the method of accessing these resources, in the section MEM-AP register accesses and memory accesses on page 8-6.

- With a JTAG-AP, the debug resources are connected through a standard JTAG serial connection, as defined in *IEEE 1149.1-1990 IEEE Standard Test Access Port and Boundary Scan Architecture*. More information about accessing the resources is given in Chapter 9 *The JTAG Access Port (JTAG-AP)*.

# Chapter 3 Common Debug Port (DP) features

This chapter describes the features that must be implemented by every ARM Debug Interface Debug Port. This means these features must be implemented on both Serial Wire Debug Ports (SW-DPs) and on JTAG Debug Ports (JTAG-DPs). Additional information about DPs is given in the following chapters:

- Chapter 4 The JTAG Debug Port (JTAG-DP)

- Chapter 5 The Serial Wire Debug Port (SW-DP)

- Chapter 6 Debug Port Registers.

This chapter contains the following sections:

- Sticky flags and DP error responses on page 3-2

- Pushed compare and pushed verify operations on page 3-5

- The Transaction Counter on page 3-8

- System and Debug power and Debug reset control on page 3-9.

## 3.1 Sticky flags and DP error responses

Within both a SW-DP and a JTAG-DP, error conditions are recorded using sticky flags. These sticky flags are described in the following sections:

- Read and write errors

- Overrun detection on page 3-3

- Protocol errors, SW-DP only on page 3-4.

Another sticky flag is used to report the result of pushed operations, see *Pushed compare and pushed verify operations* on page 3-5. This flag, STICKYCMP, behaves in the same way as the sticky flags described in this section.

When set to 1, a sticky flag remains set until it is explicitly cleared to 0. Even if the condition that caused the flag to be set to 1 no longer applies the flag remains set until the debugger clears it to 0.

The method for clearing sticky flags is different for the JTAG-DP and the SW-DP. Table 6-7 on page 6-10, summarizes how these flags are cleared to 0.

Errors can be returned by the DAP itself, or might come from a debug resource, for example, from a memory access made by a MEM-AP to a debug register file of a processor that is powered down.

Within the Debug Port, errors are flagged by sticky flags in the DP Control/Status Register (CTRL/STAT). When an error is flagged the current transaction is completed and any additional APACC (AP Access) transactions are discarded until the sticky flag is cleared to 0.

The DP response to an error condition might be:

- To signal an error response immediately. This happens with the SW-DP.

- To immediately discard all transactions as complete. This happens with the JTAG-DP.

This means that a debugger must check the Control/Status Register after performing a series of APACC transactions, to check if an error occurred. If a sticky flag is set to 1, the debugger clears the flag to 0 and then, if necessary, initiates more APACC transactions to find the cause of the sticky flag condition. Because the flags are sticky the debugger does not have to check the flags after every transaction, it only has to check the Control/Status Register periodically. This reduces the overhead of checking for errors.

#### 3.1.1 Read and write errors

A read or write error might occur within the DAP, or come from the resource being accessed. In either case, when the error is detected the Sticky Error flag, STICKYERR, in the Control/Status Register is set to 1.

A read/write error might be generated if the debugger makes an AP transaction request while the debug power domain is powered down. See *System and Debug power and Debug reset control* on page 3-9 for information about power domains.

#### 3.1.2 Overrun detection

Debug Ports support an overrun detection mode. This mode enables a user to send blocks of commands to an emulator on a high latency, high throughput connection. These commands should be sent with sufficient in-line delays to make overrun errors unlikely. However the DAP can be programmed so that, if an overrun error occurs, the DAP flags the error by setting the STICKYORUN flag in the DP Control/Status Register to 1. In this overrun detection mode the debugger must check for overrun errors after each sequence of APACC transactions, by checking this flag. For more information see *The Control/Status Register*; *CTRL/STAT* on page 6-10.

Overrun detection mode is enabled by setting the Overrun Detect bit, ORUNDETECT, in the DP Control/Status Register to 1. While this bit is set to 1, the only permitted response to any transaction is:

- OK/FAULT on the JTAG-DP

- OK on the SW-DP.

In overrun detection mode, any other response at any point is treated as an error and causes the Sticky Overrun flag STICKYORUN in the DP Control/Status Register to be set to 1. The value of the Sticky Error flag, STICKYERR, is not changed.

The debugger must clear STICKYORUN to 0 to enable transactions to resume. See *The Control/Status Register, CTRL/STAT* on page 6-10 for more information.

| Note                                                                                |                     |

|-------------------------------------------------------------------------------------|---------------------|

| The method of clearing the STICKYORUN flag to 0 is different for a JTAG-DP and a SV | V-DP. See Table 6-7 |

| on page 6-10 for more information.                                                  |                     |

The behavior of the Debug Port when the Sticky Overrun flag is set to 1 is Debug Port IMPLEMENTATION DEFINED.

If a new transaction is attempted, and results in an overrun error, before an earlier transaction has completed, the first transaction still completes normally. Other sticky flags might be set to 1 on completion of the first transaction.

If the overrun detection mode is disabled, by clearing the ORUNDETECT flag to 0, while STICKYORUN is set to 1, the subsequent value of STICKYORUN is UNPREDICTABLE. To leave overrun detection mode a debugger must:

- check the value of the STICKYORUN bit in the Control/Status register

- clear the STICKYORUN bit to 0, if it is set to 1

- clear the ORUNDETECT bit to 0, to disable overrun detection mode.

## 3.1.3 Protocol errors, SW-DP only

| Note                                                                                                  |    |

|-------------------------------------------------------------------------------------------------------|----|

| Ithough these errors can only occur with the SW-DP, they are described in this chapter because they a | re |

| rt of the sticky flags error handling mechanism.                                                      |    |

|                                                                                                       |    |

On the Serial Wire Debug interface, protocol errors can occur, for example because of wire-level errors. These errors might be detected by the parity checks on the data:

- If the SW-DP detects a parity error in a message header, the Debug Port does not respond to the message. The debugger must be aware of this possibility. If it does not receive a response to a message, the debugger must back off. It must then request a read of the IDCODE register, to ensure the Debug Port is responsive, before retrying the original access. For details of the IDCODE register see *The Identification Code Register, IDCODE* on page 6-8.

- If the SW-DP detects a parity error in the data phase of a write transaction, it sets the Sticky Write Data Error flag, WDATAERR, in the Control/Status (CTRL/STAT) Register. Subsequent accesses from the debugger, other than IDCODE, CTRL/STAT or ABORT, result in a FAULT response. For details of the CTRL/STAT register see *The Control/Status Register*, CTRL/STAT on page 6-10.

For more information about the parity check bits in the SW-DP protocol, see *Parity in the SWD protocol* on page 5-4.

If a debugger receives a FAULT response from the SW-DP, it must read the CTRL/STAT register and check the sticky flag values.

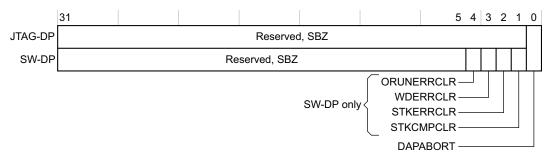

The WDATAERR flag is cleared to 0 by writing 1 to the WDERRCLR field of the AP Abort Register, see *The AP Abort Register, ABORT* on page 6-6.

## 3.2 Pushed compare and pushed verify operations

Debug Ports support operations where the value written as an AP transaction is used at the DP level to compare against a target read:

- the debugger writes a value as an AP transaction

- the DP performs a read from the AP

- the DP compares the two values and updates the Sticky Compare flag, STICKYCMP, in the DP Control/Status register, based on the result of the comparison:

- pushed compare sets STICKYCMP to 1 if the values match

- pushed verify sets STICKYCMP to 1 if the values do not match.

Whenever the STICKYCMP bit is set to 1 in this way, any outstanding transaction repeats are cancelled.

These operations are described as pushed operations. For more information see *The Control/Status Register, CTRL/STAT* on page 6-10.

Pushed operations are enabled using the Transfer Mode bits, TRNMODE, in the DP Control/Status Register, see *Transfer mode (TRNMODE)*, bits [3:2] on page 6-14.

The DP includes a byte lane mask, so that the compare or verify operation can be restricted to particular bytes in the word. This mask is set using the MASKLANE bits in the Control/Status register. For more information about this masking see *MASKLANE* and the bit masking of the pushed compare and pushed verify operations on page 6-14.

Figure 3-1 on page 3-6 gives an overview of the pushed operations.

Figure 3-1 Pushed operations overview

Pushed operations improve performance where writes might be faster than reads. They are used as part of in-line tests, for example Flash ROM programming and monitor communication.

Considering pushed operations on a specific AP makes it easier to understand how these operations are implemented. On a *Memory Access Port* (MEM-AP), if you perform an AP write transaction to the Data Read/Write (DRW) Register with either pushed compare or pushed verify active:

- The DP holds the data value from the AP write transaction in the pushed compare logic, see Figure 2-2 on page 2-9.

- The AP reads from the address indicated by the MEM-AP Transfer Address Register (TAR), see *The Transfer Address Register (TAR)* on page 11-7.

- The value returned by this read is compared with the value held in the pushed compare logic, and the STICKYCMP bit is set depending on the result. The comparison is masked as required by the MASKLANE bits. The logic used for this comparison is shown in Figure 3-1. For more information about masking see MASKLANE and the bit masking of the pushed compare and pushed verify operations on page 6-14.