# ARM<sup>®</sup> System Trace Macrocell

Programmers' Model Architecture Specification Version 1.1

### ARM System Trace Macrocell Programmers' Model Architecture Specification Version 1.1

Copyright © 2010, 2013 ARM. All rights reserved.

#### **Release Information**

The following changes have been made to this book.

|                   |       |                  | Change history         |

|-------------------|-------|------------------|------------------------|

| Date              | Issue | Confidentiality  | Change                 |

| 23 April 2010     | А     | Non-Confidential | First release for v1.0 |

| 26 September 2013 | В     | Non-Confidential | First release for v1.1 |

. . . .

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of ARM. **No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.**

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, ARM makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to ARM's customers is not intended to create or refer to any partnership relationship with any other company. ARM may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any signed written agreement covering this document with ARM, then the signed written agreement prevails over and supersedes the conflicting provisions of these terms.

Words and logos marked with @ or <sup>TM</sup> are registered trademarks or trademarks of ARM Limited or its affiliates in the EU and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow ARM's trademark usage guidelines at http://www.arm.com/about/trademark-usage-guidelines.php.

Copyright © 2010, 2013, ARM Limited or its affiliates. All rights reserved.

ARM Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

## Contents ARM System Trace Macrocell Programmers' Model Architecture Specification Version 1.1

|           | Prefa | ace                                                  |      |

|-----------|-------|------------------------------------------------------|------|

|           |       | About this book                                      | vi   |

|           |       | Using this book                                      | vii  |

|           |       | Conventions                                          | viii |

|           |       | Additional reading                                   |      |

|           |       | Feedback                                             | x    |

| Chapter 1 | Intro | oduction                                             |      |

| -         | 1.1   | About the System Trace Macrocell                     | 1-12 |

| Chapter 2 | Con   | figuration Registers Programmers' Model              |      |

| -         | 2.1   | About the configuration registers programmers' model | 2-14 |

|           | 2.2   | Register summary                                     |      |

|           | 2.3   | Register descriptions                                |      |

|           | 2.4   | Programming the STM                                  | 2-45 |

|           | 2.5   | Triggers                                             |      |

|           | 2.6   | Authentication control                               |      |

| Chapter 3 | Exte  | ended Stimulus Ports                                 |      |

| •         | 3.1   | About extended stimulus ports                        |      |

|           | 3.2   | STM transactions                                     |      |

|           | 3.3   | Address decoding                                     |      |

|           | 3.4   | Grouping stimulus ports                              |      |

|           | 3.5   | More than one master                                 |      |

|           | 3.6   | Data sizes                                           |      |

|           | 3.7   | Bus endianness                                       | 3-59 |

|           |       |                                                      |      |

|            | 3.9<br>3.10 | Implementation options<br>Reserved locations<br>Timestamping<br>Mapping onto STPv2                                                                 | 3-61<br>3-62 |

|------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Chapter 4  | 4.1<br>4.2  | nentation Defined Controls         About implementation defined controls and registers         Standard hardware event tracing         DMA control | 4-67         |

| Appendix A |             | About recommended configurations                                                                                                                   | A-82         |

| Appendix B | Revisi      | ons                                                                                                                                                |              |

Glossary

## Preface

This preface introduces the *System Trace Macrocell* (STM) Programmers' Model Architecture Specification. It contains the following sections:

- About this book on page vi.

- Using this book on page vii.

- *Conventions* on page viii.

- Additional reading on page ix.

- *Feedback* on page x.

## About this book

This book describes the ARM *System Trace Macrocell* (STM) programmers' model architecture. Some parts of the STM programmers' model architecture are IMPLEMENTATION DEFINED. For more information see the applicable STM *Technical Reference Manual* (TRM).

#### Intended audience

This book is written for the following target audiences:

- Designers of development tools providing support for STM functionality. All chapters in this book are of interest to these users.

- Advanced users of development tools providing support for STM functionality. Chapter 2 is particularly relevant to these users.

- Designers of an ARM processor based product that includes an STM trace port. Chapter 3 is particularly relevant to these users.

- Engineers who want to specify, design, or implement an STM to the ARM STM Architecture.

Hardware engineers who want to incorporate an ARM STM into their design must consult the applicable STM *Technical Reference Manual* listed in *Additional reading* on page ix. ARM recommends that all users of this book have experience of the ARM architecture.

### Using this book

This book is organized into the following chapters:

#### **Chapter 1** Introduction

Read this for an introduction to the STM.

#### Chapter 2 Configuration Registers Programmers' Model

Read this for information about the configuration registers, and how to program the STM. It also describes triggers and authentication control.

#### **Chapter 3** Extended Stimulus Ports

Read this for information about the extended stimulus ports and the transaction types.

#### **Chapter 4** Implementation Defined Controls

Read this for information about the IMPLEMENTATION DEFINED controls and registers.

#### Appendix A Recommended Configurations

Read this for information about the recommendations for using the STM architecture in different implementations.

#### **Appendix B** Revisions

Read this for a description of the technical changes between released issues of this book.

*Glossary* Read this for definitions of terms used in this book.

— Note —

ARM publishes a single glossary that relates to most ARM products, see the *ARM*<sup>®</sup> *Glossary* http://infocenter.arm.com/help/topic/com.arm.doc.aeg0014-. A definition in the glossary in this specification might be more detailed than the corresponding definition in the *ARM*<sup>®</sup> *Glossary*.

## Conventions

The following sections describe conventions that this book can use:

- Typographic conventions.

- Signals.

- Numbers.

#### **Typographic conventions**

The typographical conventions are:

| italic    | Introduces special terminology, and denotes citations.                                                                                                                   |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bold      | Denotes signal names, and is used for terms in descriptive lists, where appropriate.                                                                                     |

| monospace | Used for assembler syntax descriptions, pseudocode, and source code examples.                                                                                            |

|           | Also used in the main text for instruction mnemonics and for references to other items appearing in assembler syntax descriptions, pseudocode, and source code examples. |

#### SMALL CAPITALS

Used for a few terms that have specific technical meanings, and are included in the Glossary.

#### **Colored text** Indicates a link. This can be:

- A URL, for example http://infocenter.arm.com.

- A cross-reference, that includes the page number of the referenced information if it is not on the current page, for example, *About the System Trace Macrocell* on page 1-12.

- A link, to a chapter or appendix, or to a glossary entry, or to the section of the document that defines the colored term, for example STMSPSCR.

#### Signals

In general this specification does not define processor signals, but it does include some signal examples and recommendations. The signal conventions are:

| Signal level | The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means: |

|--------------|-------------------------------------------------------------------------------------------------------------|

|              | • HIGH for active-HIGH signals.                                                                             |

|              | • LOW for active-LOW signals.                                                                               |

| Lower-case n | At the start or end of a signal name denotes an active-LOW signal.                                          |

#### Numbers

Numbers are normally written in decimal. Binary numbers are preceded by 0b, and hexadecimal numbers by 0x. In both cases, the prefix and the associated value are written in a monospace font, for example 0xFFFF0000.

## Additional reading

This section lists relevant publications from ARM and third parties.

See *Infocenter* http://infocenter.arm.com, for access to ARM documentation.

#### **ARM** publications

This specification defines the System Trace Macrocell programmers' model architecture. See the following documents for other relevant information:

- ARM<sup>®</sup> CoreSight<sup>™</sup> System Trace Macrocell Technical Reference Manual (ARM DDI 0444).

- ARM<sup>®</sup> CoreSight<sup>™</sup> System Trace Macrocell-500 Technical Reference Manual (ARM DDI 0528).

- ARM<sup>®</sup> Architecture Reference Manual, ARMv7-M edition (ARM DDI 0403).

- ARM<sup>®</sup> Architecture Reference Manual, ARMv7-A and ARMv7-R edition (ARM DDI 0406).

- ARM® Architecture Reference Manual ARMv8, for ARMv8-A architecture profile (ARM DDI 0487).

- ARM<sup>®</sup> CoreSight<sup>™</sup> Architecture Specification (ARM IHI 0029).

- ARM<sup>®</sup> Debug Interface Architecture Specification, ADIv5.0 to ADIv5.2 (ARM IHI 0031).

- ARM<sup>®</sup> RealView<sup>®</sup> ICE and RealView Trace User Guide (ARM DUI 0155).

#### Other publications

This section lists relevant documents published by third parties:

MIPI System Trace Protocol version 2 (STPv2).

## Feedback

ARM welcomes feedback on its documentation.

#### Feedback on this book

If you have comments on the content of this book, send an e-mail to errata@arm.com. Give:

- The title.

- The number, ARM IHI 0054B.

- The page numbers to which your comments apply.

- A concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

#### — Note -

ARM tests PDFs only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the appearance or behavior of any document when viewed with any other PDF reader.

## Chapter 1 Introduction

This chapter introduces the System Trace Macrocell (STM). It contains the following section:

• About the System Trace Macrocell on page 1-12.

## 1.1 About the System Trace Macrocell

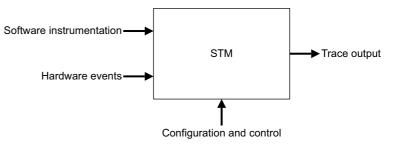

The STM enables tracing of system activity from various sources:

- Instrumented software, using memory-mapped stimulus ports.

- Hardware events.

The activity observed by the STM is packaged into a trace stream, for output to trace capture devices such as those provided by CoreSight technology.

This version of the STM architecture supports a trace stream that conforms to the MIPI *System Trace Protocol version 2* (STPv2).

Figure 1-1 shows the STM inputs and outputs.

#### Figure 1-1 STM inputs and outputs

The STM programmers' model has two main parts:

#### **Configuration registers**

These registers are accessible both by software running on the chip and by an external debugger and are used to configure the tracing activity of the STM. The configuration registers also include optional basic stimulus port registers. For more information on the configuration registers, see Chapter 2 *Configuration Registers Programmers' Model*.

#### Extended stimulus port registers

These registers are accessible by instrumented software running on the chip, but are not necessarily accessible by an external debugger. Up to 65536 extended stimulus ports are provided. For more information on the extended stimulus port registers, see Chapter 3 *Extended Stimulus Ports*.

The STM supports the following:

- Multiple software masters writing software instrumentation independently. Each master can use multiple stimulus ports.

- Timestamping of the system activity. The timestamp is a global timestamp which can be shared with other trace sources in the system, to enable correlation of activity from multiple trace sources.

- Interaction with DMA controllers, to manage the flow of data in the system.

- Indicating that specific events have occurred, such as the occurrence of a particular hardware event or a particular piece of software instrumentation. These events are known as triggers and can be indicated in the trace stream, or through signals to other system components.

## Chapter 2 Configuration Registers Programmers' Model

This chapter describes the configuration registers that you can program to set up and control the STM. It contains the following sections:

- About the configuration registers programmers' model on page 2-14.

- *Register summary* on page 2-15.

- *Register descriptions* on page 2-17.

- *Programming the STM* on page 2-45.

- Triggers on page 2-46.

- *Authentication control* on page 2-49.

2.1 About the configuration registers programmers' model

## 2.1 About the configuration registers programmers' model

The configuration registers occupy a 4KB block, with a CoreSight programmers' model compatible structure. The STM configuration registers are used to set up the STM implementation.

The following apply to the STM registers:

- Accesses to Reserved locations are UNK/SBZP.

- Accesses to Reserved bits in defined registers are UNK/SBZP unless otherwise stated.

- Registers reset to an UNKNOWN value unless specifically defined.

## 2.2 Register summary

- Table 2-1 shows the STM registers. In the table, access type is described as follows:

- **RW** Read and write.

- **RO** Read only.

- WO Write only.

#### Table 2-1 STM configuration register summary

| offset      | Name                                         | Туре      | Description                                                                      |

|-------------|----------------------------------------------|-----------|----------------------------------------------------------------------------------|

| 0x000-0x07C | Basic Stimulus Ports                         | RW        | See STMSTIMR <n>, Basic Stimulus Ports on page 2-17</n>                          |

| 0x080-0x9FC | -                                            | -         | Reserved                                                                         |

| 0xA00-0xAFC | IMPLEMENTATION DEFINED Blo                   | ck 3      | See Chapter 4 Implementation Defined Controls                                    |

| 0xB00-0xBFC | IMPLEMENTATION DEFINED Block 2               |           | -                                                                                |

| 0xC00-0xCFC | IMPLEMENTATION DEFINED Blo                   | ck 1      | -                                                                                |

| 0xD00-0xDFC | IMPLEMENTATION DEFINED Blo                   | ck 0      | -                                                                                |

| 0xE00-0xE7C | Stimulus Port Control Regist                 | ers       |                                                                                  |

| 0×E00       | Stimulus Port Enable                         | RW        | See STMSPER, Stimulus Port Enable Register on page 2-17                          |

| 0xE04-0xE1C | -                                            | -         | Reserved                                                                         |

| 0xE20       | Stimulus Port Trigger Enable                 | RW        | See STMSPTER, Stimulus Port Trigger Enable Register on page 2-18                 |

| 0xE24-0xE3C | -                                            | -         | Reserved                                                                         |

| 0xE40       | Trace Privilege                              | RW        | See STMPRIVMASKR, Trace Privilege Register on page 2-19                          |

| 0xE44-0xE5C | -                                            | -         | Reserved                                                                         |

| 0xE60       | Stimulus Port Select<br>Configuration        | RW        | See STMSPSCR, Stimulus Port Select Configuration Register on page 2-20           |

| 0xE64       | Stimulus Port Master Select<br>Configuration | RW        | See STMSPMSCR, Stimulus Port Master Select Configuration Register on page 2-22   |

| 0xE68       | Stimulus Port Override                       | RW        | See STMSPOVERRIDER, Stimulus Port Override Register on page 2-24                 |

| 0xE6C       | Stimulus Port Master<br>Override             | RW        | See STMSPMOVERRIDER, Stimulus Port Master Override Register on page 2-26         |

| 0xE70       | Stimulus Port Trigger Control and Status     | RW        | See STMSPTRIGCSR, Stimulus Port Trigger Control and Status Register on page 2-28 |

| 0xE74-0xE7C | -                                            | -         | Reserved                                                                         |

| 0xE80-0xE9C | Primary Control and Status I                 | Registers |                                                                                  |

| 0xE80       | Trace Control and Status                     | RW        | See STMTCSR, Trace Control and Status Register on page 2-29                      |

| 0xE84       | Timestamp Stimulus                           | WO        | See STMTSSTIMR, Timestamp Stimulus Register on page 2-31                         |

| 0xE88       | -                                            | -         | Reserved                                                                         |

| 0xE8C       | Timestamp Frequency                          | RW        | See STMTSFREQR, Timestamp Frequency Register on page 2-32                        |

| 0xE90       | Synchronization Control                      | RW        | See STMSYNCR, Synchronization Control Register on page 2-33                      |

2 Configuration Registers Programmers' Model

2.2 Register summary

| Address<br>offset | Name                     | Туре    | Description                                                    |

|-------------------|--------------------------|---------|----------------------------------------------------------------|

| 0xE94             | Auxiliary Control        | RW      | See STMAUXCR, Auxiliary Control Register on page 2-33          |

| 0xE94-0xE9C       | -                        | -       | Reserved                                                       |

| 0xEA0-0xEAC       | Identification Registers |         |                                                                |

| 0xEA0             | Features 1               | RO      | See STMFEAT1R, Features 1 Register on page 2-34                |

| 0xEA4             | Features 2               | RO      | See STMFEAT2R, Features 2 Register on page 2-36                |

| 0xEA8             | Features 3               | RO      | See STMFEAT3R, Features 3 Register on page 2-37                |

| 0xEAC-0xEFC       | -                        | -       | Reserved                                                       |

| 0xF00-0xFFC       | CoreSight Management Reg | gisters |                                                                |

| 0xF00             | Integration Mode Control | RW      | See STMITCTRL, Integration Mode Control Register on page 2-38  |

| 0xF04-0xF9C       | -                        | -       | Reserved                                                       |

| 0xFA0             | Claim Tag Set            | RW      | See STMCLAIMSET, Claim Tag Set Register on page 2-39           |

| 0xFA4             | Claim Tag Clear          | RW      | See STMCLAIMCLR, Claim Tag Clear Register on page 2-39         |

| 0xFA8-0xFAC       | -                        | -       | Reserved                                                       |

| 0xFB0             | Lock Access              | WO      | See STMLAR, Lock Access Register on page 2-40                  |

| 0xFB4             | Lock Status              | RO      | See STMLSR, Lock Status Register on page 2-41                  |

| 0xFB8             | Authentication Status    | RO      | See STMAUTHSTATUS, Authentication Status Register on page 2-41 |

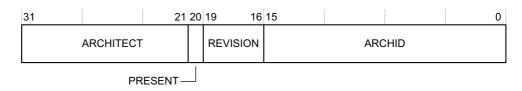

| 0xFBC             | Device Architecture      | RO      | See STMDEVARCH, Device Architecture Register on page 2-41      |

| 0xFC0-0xFC4       | -                        | -       | Reserved                                                       |

| 0xFC8             | Device Configuration     | RO      | See STMDEVID, Device Configuration Register on page 2-42       |

| 0xFCC             | Device Type              | RO      | See STMDEVTYPE, Device Type Register on page 2-43              |

| 0xFD0-0xFEC       | Peripheral ID            | RO      | See STMPIDR0-7, Peripheral ID Registers on page 2-43           |

| 0xFF0-0xFFC       | Component ID             | RO      | See STMCIDR0-3, Component ID Registers on page 2-44            |

#### Table 2-1 STM configuration register summary (continued)

## 2.3 Register descriptions

Table 2-1 on page 2-15 lists the STM registers. This section describes each of the registers.

#### 2.3.1 STMSTIMR<n>, Basic Stimulus Ports

The STMSTIMR<n> characteristics are:

| Purpose              | Provides up to 32 stimulus ports.                                                                                                                                                                                |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | Write accesses to these basic stimulus ports are identical to write accesses to the I_DMTS variant of the corresponding extended stimulus ports 0-31 on master 0. See Chapter 3 <i>Extended Stimulus Ports</i> . |

|                      | Read accesses are used to determine if a future write to the register is accepted.                                                                                                                               |

| Usage constraints    | There are no usage constraints. Accesses to these registers are unaffected by the lock mechanism, see <i>Lock Registers</i> on page 2-40.                                                                        |

| Configurations       | These registers are optional. Read STMFEAT2R to determine if the basic stimulus ports are implemented.                                                                                                           |

| Attributes           | See the register summary in Table 2-1 on page 2-15.                                                                                                                                                              |

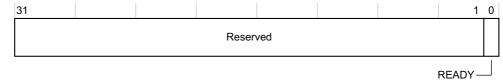

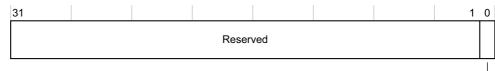

| Figure 2-1 shows the | STMSTIMR <n> bit assignments on reads.</n>                                                                                                                                                                       |

#### Figure 2-1 STMSTIMR<n> bit assignments on reads

Table 2-2 shows the STMSTIMR<n> bit assignments on reads.

#### Table 2-2 STMSTIMR<n> bit assignments on reads

| Bits   | Name  | Description  |                                                                                                                                                                                                        |

|--------|-------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:1] | -     | Reserved, UN | K/SBZP.                                                                                                                                                                                                |

| [0]    | READY | 0b0          | A write to the stimulus port is not accepted. This value is returned when the selected stimulus port is disabled or when the STM is unable to accept a write, for example, when any buffering is full. |

|        |       | 0b1          | The STM can accept a write to a stimulus port.                                                                                                                                                         |

—— Note ———

Only supports up to 32 basic stimulus ports, even if the STM supports more than 32 extended stimulus ports.

#### 2.3.2 STMSPER, Stimulus Port Enable Register

The STMSPER characteristics are:

| Purpose           | Enables the stimulus port registers to generate trace. This register defines one bit per stimulus port. Writing 0b1 enables the appropriate stimulus port, writing 0b0 disables the appropriate stimulus port. This register is used in conjunction with the STMSPSCR. |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Usage constraints | There are no usage constraints.                                                                                                                                                                                                                                        |

| Configurations    | This register is available in all implementations.                                                                                                                                                                                                                     |

2.3 Register descriptions

Attributes See the register summary in Table 2-1 on page 2-15.

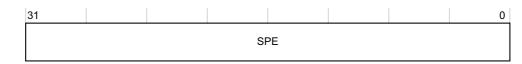

Figure 2-2 shows the STMSPER bit assignments.

#### Figure 2-2 STMSPER bit assignments

Table 2-3 shows the STMSPER bit assignments.

| Bits   | Name | Description                                                                                                                                                                     |

|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:0] | SPE  | Stimulus port enable, with one bit per stimulus port:                                                                                                                           |

|        |      | 0b0 Stimulus port disabled.                                                                                                                                                     |

|        |      | 0b1 Stimulus port enabled.                                                                                                                                                      |

|        |      | The reset value of each bit is 0b0.                                                                                                                                             |

|        |      | If the number of stimulus ports is less than or equal to 32, the number of bits in the SPE field is the number of stimulus ports.                                               |

|        |      | If the number of stimulus ports is greater than 32, the SPE field is 32-bits wide and the STMSPSCR controls which stimulus ports are enabled in conjunction with the SPE field. |

—— Note ——

Bit[0] applies to the lowest-numbered port and bit[31] to the highest-numbered port.

#### 2.3.3 STMSPTER, Stimulus Port Trigger Enable Register

The STMSPTER characteristics are:

| Purpose Enables trigger generation on writes to enabled stimulus port registers. |  |

|----------------------------------------------------------------------------------|--|

|----------------------------------------------------------------------------------|--|

**Usage constraints** There are no usage constraints.

**Configurations** This register is optional. Read **STMFEAT2R** to determine if it is implemented or write a non-zero value and read it back. If a non-zero value is returned, this register is implemented.

Attributes See the register summary in Table 2-1 on page 2-15.

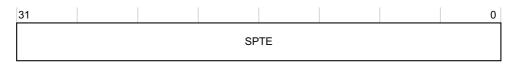

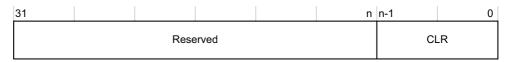

Figure 2-3 shows the STMSPTER bit assignments.

#### Figure 2-3 STMSPTER bit assignments

Table 2-4 shows the STMSPTER bit assignments.

#### Table 2-4 STMSPTER bit assignments

| Bits   | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:0] | SPTE | Bit mask to enable trigger generation from the stimulus port registers, with one bit per stimulus port register:         0b0       Disabled.         0b1       Enabled.         The reset value of each bit is 0b0.         If the number of stimulus ports is less than or equal to 32, the number of bits in the SPTE field is the number of stimulus ports.         If the number of stimulus ports is greater than 32         The SPTE field is 32-bits wide. |

|        |      | The STMSPSCR controls which stimulus ports have triggers enabled, in conjunction with the SPTE field.                                                                                                                                                                                                                                                                                                                                                             |

— Note –

Bit[0] applies to the lowest-numbered port and bit[31] to the highest-numbered port.

#### 2.3.4 STMPRIVMASKR, Trace Privilege Register

The STMPRIVMASKR characteristics are:

| Purpose                                                        | Enables an operating system to control which stimulus ports are accessible by user code.                                                                                               |  |  |  |  |

|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Usage constraints                                              | onstraints You can only write to this register in a privileged mode or from an external debugger.                                                                                      |  |  |  |  |

| Configurations                                                 | This register is optional. Read STMFEAT2R to determine if it is implemented or write a non-zero value and read it back. If a non-zero value is returned, this register is implemented. |  |  |  |  |

| Attributes See the register summary in Table 2-1 on page 2-15. |                                                                                                                                                                                        |  |  |  |  |

| Figure 2-4 shows the                                           | STMPRIVMASKR bit assignments                                                                                                                                                           |  |  |  |  |

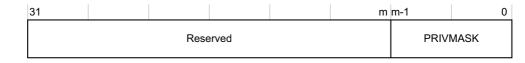

Figure 2-4 shows the STMPRIVMASKR bit assignments.

#### Figure 2-4 STMPRIVMASKR bit assignments

Table 2-5 shows the STMPRIVMASKR bit assignments.

#### Table 2-5 STMPRIVMASKR bit assignments

| Bits    | Name     | Description  | n                                                                                                                                                                                                                                                                         |

|---------|----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:m]  | -        | Reserved, RA | AZ.                                                                                                                                                                                                                                                                       |

| [m-1:0] | PRIVMASK | 0b0<br>0b1   | <ul> <li>control user mode access to stimulus ports. Each bit controls eight stimulus ports:<br/>User mode and privileged accesses are permitted.<br/>User mode accesses are ignored.</li> <li>ols access to stimulus ports (8n to 8n+7).</li> <li>lue is 0b0.</li> </ul> |

— Note –

- The variable m is defined by the number of supported stimulus ports. For example if 32 stimulus ports are supported, m is 4.

- This register only supports control for up to 256 stimulus ports. The access permissions apply to the basic stimulus ports and extended stimulus ports.

#### 2.3.5 STMSPSCR, Stimulus Port Select Configuration Register

The STMSPSCR characteristics are:

| Purpose           | Enables a debugger to program which stimulus ports the STMSPER and STMSPTER apply to.            |

|-------------------|--------------------------------------------------------------------------------------------------|

| Usage constraints | There are no usage constraints.                                                                  |

| Configurations    | If 32 or fewer stimulus ports are implemented, this register is not implemented and is Reserved. |

| Attributes        | See the register summary in Table 2-1 on page 2-15.                                              |

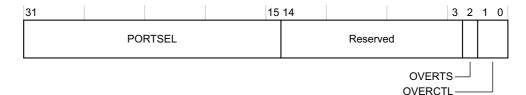

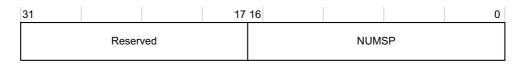

Figure 2-5 shows the STMSPSCR bit assignments.

| PORTSEL Reserved | 31 |         | 20 19 |         |    | 2 | 1 | 0 |

|------------------|----|---------|-------|---------|----|---|---|---|

|                  |    | PORTSEL |       | Reserve | ed |   |   |   |

PORTCTL

#### Figure 2-5 STMSPSCR bit assignments

Table 2-6 shows the STMSPSCR bit assignments.

#### Table 2-6 STMSPSCR bit assignments

| Bits    | Name    | Description     |                                                                                                                                                                                                                |  |  |  |

|---------|---------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| [31:20] | PORTSEL | The size of th  | Port Selection. This field defines which stimulus ports the STMSPER and/or STMSPTER apply to.<br>The size of this field is defined by the number of implemented stimulus ports.<br>The reset value is UNKNOWN. |  |  |  |

| [19:2]  | -       | Reserved, UN    | eserved, UNK/SBZP.                                                                                                                                                                                             |  |  |  |

| [1:0]   | PORTCTL | This defines l  | how the port selection is applied:                                                                                                                                                                             |  |  |  |

|         |         | 0b00            | Port selection not used.                                                                                                                                                                                       |  |  |  |

|         |         | 0b01            | Port selection applies only to the STMSPTER.                                                                                                                                                                   |  |  |  |

|         |         | 0b10            | Reserved.                                                                                                                                                                                                      |  |  |  |

|         |         | 0b11            | Port selection applies to both the STMSPER and STMSPTER.                                                                                                                                                       |  |  |  |

|         |         | The reset value | ue is 0b00.                                                                                                                                                                                                    |  |  |  |

#### PORTCTL == 0b00

When PORTCTL is 0b00, the STMSPER and STMSPTER apply equally to every group of 32 stimulus ports and PORTSEL is ignored. For example:

- Bit[0] of the STMSPER is 0b1.

- Bit[0] of the STMSPTER is 0b1.

This enables stimulus ports 0, 32, 64, 96, 128, and so on. Triggers are caused on writes to stimulus ports 0, 32, 64, 96, 128, and so on. All other stimulus ports are disabled and do not cause triggers.

#### PORTCTL != 0b00

When PORTCTL is not 0b00, the PORTSEL field enables you to select a subset of the full stimulus ports to which the STMSPER and STMSPTER apply. PORTSEL enables you to select a single group of 32 stimulus ports or power-of-two multiples of consecutive groups to which to apply the STMSPER and STMSPTER.

To program PORTSEL, the bottom N bits which are 0 define a mask to apply to the port selection, then a 1 in bit N+1 demarks the mask from the port selection. The bits from N+2 to M select the groups to which the STMSPER and STMSPTER apply.

For example:

**PORTSEL** = bbb\_bbbb\_bbbb\_1

A single group of 32 stimulus ports bbb\_bbbb\_bbbb is selected.

**PORTSEL** = bbb\_bbb1\_0000\_0

A selection of 32 groups of 32 stimulus ports from bbb\_bbb0\_0000 to bbb\_bbb1\_1111 is selected.

**PORTSEL** = 100\_0000\_0000\_0

All stimulus ports are selected. This is equivalent to PORTCTL == 0b00.

Programming PORTCTL != 00 and PORTSEL = 000\_0000\_0000\_0 is UNPREDICTABLE.

Programming a PORTSEL value which enables more stimulus ports than are implemented results in UNPREDICTABLE behavior, for example, programming 100\_0000\_0000\_0 when only 32 stimulus ports are implemented. To enable all 32 stimulus ports, program 000\_0001\_0000\_0.

Triggers cannot be generated by writes to stimulus ports which are not enabled. Enabling a trigger on a stimulus port which is not enabled results in UNPREDICTABLE behavior.

#### **Using PORTCTL**

Table 2-7 shows how to use PORTCTL.

#### Table 2-7 Using PORTCTL

| PORTCTL | Description |

|---------|-------------|

|         | Description |

| 0b00 | Port selection select is not used.                                                                       |

|------|----------------------------------------------------------------------------------------------------------|

|      | STMSPER and STMSPTER apply equally to every group of 32 stimulus ports. PORTSEL is ignored. For example: |

|      | • Only bit[0] of the STMSPER is 0b1.                                                                     |

|      | • Only bit[0] of the STMSPTER is 0b1.                                                                    |

|      |                                                                                                          |

This enables stimulus ports 0, 32, 64, 96, 128, and so on. Triggers are caused on writes to stimulus ports 0, 32, 64, 96, 128, and so on. All other stimulus ports are disabled and do not cause triggers.

#### Table 2-7 Using PORTCTL (continued)

| PORTCTL | Description                                                                                                                                                                         |  |  |  |  |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0b01    | Port selection only applies to the STMSPTER.                                                                                                                                        |  |  |  |  |  |

|         | STMSPER applies equally to every group of 32 stimulus ports.                                                                                                                        |  |  |  |  |  |

|         | STMSPTER only applies to the groups of 32 stimulus ports selected by PORTSEL and other groups do not cause triggers.                                                                |  |  |  |  |  |

|         | For example:                                                                                                                                                                        |  |  |  |  |  |

|         | • PORTSEL is b000_0000_0001_1 (select group 1).                                                                                                                                     |  |  |  |  |  |

|         | • Only bit[0] of the STMSPER is 0b1.                                                                                                                                                |  |  |  |  |  |

|         | • Only bit[0] of the STMSPTER is 0b1.                                                                                                                                               |  |  |  |  |  |

|         | This enables stimulus ports 0, 32, 64, 96, 128, and so on. Triggers are only caused on writes to stimulus port 32. All other stimulus ports are disabled and do not cause triggers. |  |  |  |  |  |

| 0b10    | Reserved.                                                                                                                                                                           |  |  |  |  |  |

| 0b11    | Port selection applies to STMSPER and STMSPTER.                                                                                                                                     |  |  |  |  |  |

|         | STMSPER and STMSPTER only apply to the groups selected by PORTSEL. Other groups are not enabled and do not cause triggers.                                                          |  |  |  |  |  |

|         | For example:                                                                                                                                                                        |  |  |  |  |  |

|         | • PORTSEL is b000_0000_0001_1 (select group 1).                                                                                                                                     |  |  |  |  |  |

|         | • Only bit[0] of the STMSPER is 0b1.                                                                                                                                                |  |  |  |  |  |

|         | • Only bit[0] of the STMSPTER is 0b1.                                                                                                                                               |  |  |  |  |  |

|         | This enables only stimulus port 32 and triggers are only caused on writes to stimulus port 32. All other stimulus ports are disabled and do not cause triggers.                     |  |  |  |  |  |

#### 2.3.6 STMSPMSCR, Stimulus Port Master Select Configuration Register

The STMSPMSCR characteristics are:

| Purpose                                                        | Enables a debugger to program which masters the STMSPSCR applies to.                            |  |  |  |  |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|--|

| Usage constraints                                              | ge constraints There are no usage constraints.                                                  |  |  |  |  |

| Configurations                                                 | igurations If only one master is implemented, this register is not implemented and is Reserved. |  |  |  |  |

| Attributes See the register summary in Table 2-1 on page 2-15. |                                                                                                 |  |  |  |  |

| Figure 2-6 shows the S                                         | STMSPMSCR hit assignments                                                                       |  |  |  |  |

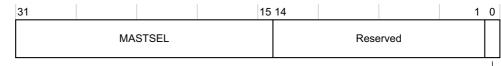

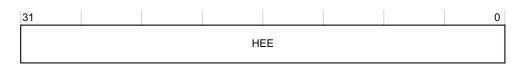

Figure 2-6 shows the STMSPMSCR bit assignments.

| 31 |        |   | 15 14 |          | 1 | 0 |

|----|--------|---|-------|----------|---|---|

|    | MASTSE | L |       | Reserved |   |   |

MASTCTL

#### Figure 2-6 STMSPMSCR bit assignments

Table 2-8 shows the STMSPMSCR bit assignments.

#### Table 2-8 STMSPMSCR bit assignments

| Bits    | Name    | Description                                                                                                                                                                          |  |

|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| [31:15] | MASTSEL | Master Selection. This field defines which master the STMSPSCR applies to.<br>The size of this field is defined by the number of implemented masters.<br>The reset value is UNKNOWN. |  |

| [14:1]  | -       | Reserved, UNK/SBZP.                                                                                                                                                                  |  |

| [0]     | MASTCTL | This bit defines how the master is applied:0b0Master selection not used.0b1Master selection applies to the STMSPSCR.The reset value is 0b0.                                          |  |

#### MASTCTL == 0b0

When MASTCTL is 0b0 the port selection used by the STMSPSCR applies equally to all masters and MASTSEL is ignored.

#### MASTCTL == 0b1

When MASTCTL is 0b1, the MASTSEL field enables you to select a subset of the full masters to which the STMSPSCR applies. MASTSEL enables you to select a single master or power-of-two multiples of consecutive masters to which to apply the STMSPSCR.

To program MASTSEL, the bottom N bits which are 0 define a mask to apply to the master selection, then a 1 in bit N+1 demarks the mask from the master selection. The bits from N+2 to M select the master to which the STMSPSCR applies.

For example:

**MASTSEL** = bbbb\_bbbb\_bbbb\_1

A single master bbbb\_bbbb\_bbbb is selected.

MASTSEL = bbbb\_bbbb\_bbb1\_0000\_0

MASTSEL = 1000\_0000\_0000\_0

All masters are selected. This is equivalent to MASTCTL == 0b0.

Programming MASTCTL == 1 and MASTSEL = 0000\_0000\_0000\_0 is UNPREDICTABLE.

Programming a MASTSEL value which enables more masters than are implemented results in UNPREDICTABLE behavior. For example, programming 1000\_0000\_0000\_0000\_0 when only 32 masters are implemented. To enable all 32 masters program 0000\_0000\_0001\_0000\_0.

#### Using MASTCTL

Table 2-9 shows how to use MASTCTL.

Table 2-9 Using MASTCTL

| MASTCTL | Description                                                                                                                                                                                                                                               |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0b0     | Master selection select is not used.                                                                                                                                                                                                                      |  |  |  |

|         | STMSPSCR applies equally to every master. MASTSEL is ignored.                                                                                                                                                                                             |  |  |  |

|         | For example:                                                                                                                                                                                                                                              |  |  |  |

|         | • MASTCTL is 0b0.                                                                                                                                                                                                                                         |  |  |  |

|         | STMSPSCR.PORTSEL is 0b00.                                                                                                                                                                                                                                 |  |  |  |

|         | • Only bit[0] of the STMSPER is 0b1.                                                                                                                                                                                                                      |  |  |  |

|         | • Only bit[0] of the STMSPTER is 0b1.                                                                                                                                                                                                                     |  |  |  |

|         | This enables stimulus ports 0, 32, 64, 96, 128, and so on, on all masters. Triggers are caused on writes to stimulus ports 0, 32, 64, 96, 128, and so on, on all masters. All other stimulus ports on all masters are disabled and do not cause triggers. |  |  |  |

| 0b1     | Master selection applies to STMSPSCR.                                                                                                                                                                                                                     |  |  |  |

|         | STMSPSCR only applies to the masters selected by MASTSEL. Other masters are not enabled and do not cause triggers.                                                                                                                                        |  |  |  |

|         | For example:                                                                                                                                                                                                                                              |  |  |  |

|         | • MASTCTL is 0b1.                                                                                                                                                                                                                                         |  |  |  |

|         | • MASTSEL is b0000_0000_0001_1 (select master 1).                                                                                                                                                                                                         |  |  |  |

|         | • STMSPSCR.PORTCTL is 0b11.                                                                                                                                                                                                                               |  |  |  |

|         | • STMSPSCR.PORTSEL is b000_0000_0001_1 (select group 1).                                                                                                                                                                                                  |  |  |  |

|         | • Only bit[0] of the STMSPER is 0b1.                                                                                                                                                                                                                      |  |  |  |

|         |                                                                                                                                                                                                                                                           |  |  |  |

• Only bit[0] of the STMSPTER is 0b1.

This enables only stimulus port 32 on master 1 and triggers are only caused on writes to stimulus port 32 on master 1. All other stimulus ports on all masters are disabled and do not cause triggers.

#### 2.3.7 STMSPOVERRIDER, Stimulus Port Override Register

The STMSPOVERRIDER characteristics are:

- Purpose

Enables a debugger to override various features of the STM. This register is used in conjunction with STMSPMOVERRIDER.

- Usage constraints There are no usage constraints.

- **Configurations** This register is optional. Read **STMFEAT2R** to determine if it is implemented.

- Attributes See the register summary in Table 2-1 on page 2-15.

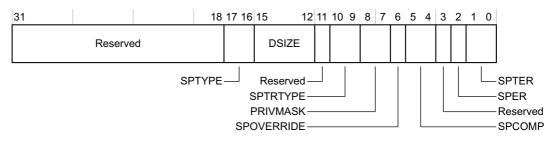

Figure 2-7 shows the STMSPOVERRIDER bit assignments.

#### Figure 2-7 STMSPOVERRIDER bit assignments

Table 2-10 shows the STMSPOVERRIDER bit assignments.

#### Table 2-10 STMSPOVERRIDER bit assignments

| Bits    | Name    | Description                                                                                                                                                                                                |  |  |

|---------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| [31:15] | PORTSEL | Port selection.                                                                                                                                                                                            |  |  |

|         |         | This field defines which stimulus ports the override controls apply to.                                                                                                                                    |  |  |

|         |         | The size of this field is defined by the number of implemented stimulus ports.                                                                                                                             |  |  |

|         |         | The reset value is UNKNOWN.                                                                                                                                                                                |  |  |

| [14:3]  | -       | Reserved, UNK/SBZP.                                                                                                                                                                                        |  |  |

| [2]     | OVERTS  | Timestamping override.                                                                                                                                                                                     |  |  |

|         |         | This override requests all stimulus port writes that cause trace to be traced with a timestamp (where possible). As with normal operation, this does not ensure all packets are generated with timestamps. |  |  |

|         |         | This field is independent of OVERCTL and PORTSEL and STMSPMOVERRIDER.                                                                                                                                      |  |  |

|         |         | 0b0 Override not enabled.                                                                                                                                                                                  |  |  |

|         |         | 0b1 Override enabled.                                                                                                                                                                                      |  |  |

|         |         | The reset value is 0b0.                                                                                                                                                                                    |  |  |

| [1:0]   | OVERCTL | This defines how the port selection is applied:                                                                                                                                                            |  |  |

|         |         | 0b00 Override controls disabled.                                                                                                                                                                           |  |  |

|         |         | 0b01 Ports selected by PORTSEL always behave as guaranteed transactions.                                                                                                                                   |  |  |

|         |         | 0b10 Ports selected by PORTSEL always behave as invariant timing transactions.                                                                                                                             |  |  |

|         |         | 0b11 Reserved.                                                                                                                                                                                             |  |  |

|         |         | The reset value is 0b00.                                                                                                                                                                                   |  |  |

#### OVERCTL != 0b00

When OVERCTL is not 0b00, the PORTSEL field enables you to select a subset of the full stimulus ports to which the override controls apply. PORTSEL enables you to select a single stimulus ports or power-of-two multiples of consecutive stimulus ports to which to apply the override controls.

To program PORTSEL, the bottom N bits which are 0 define a mask to apply to the port selection, then a 1 in bit N+1 delimits the mask from the port selection. The bits from N+2 to M select the ports to which the override controls apply.

For example:

**PORTSEL** = pppp\_pppp\_ppp\_1

A single port pppp\_pppp\_pppp is selected.

**PORTSEL** = pppp\_ppp1\_0000\_0

A selection of 32 ports from pppp\_ppp0\_0000 to pppp\_ppp1\_1111 are selected.

**PORTSEL** = 1000\_0000\_0000\_0

All ports are selected.

Programming OVERCTL != 00 and PORTSEL = 0000\_0000\_0000\_0 is UNPREDICTABLE.

Programming a PORTSEL value which enables more stimulus ports than are implemented results in UNPREDICTABLE behavior. For example, programming 1000\_0000\_0000\_0000\_0 when only 32 stimulus ports are implemented. To enable all 32 stimulus ports, program 0000\_0000\_0001\_0000\_0.

#### Using OVERCTL

Table 2-11 shows how to use OVERCTL.

Table 2-11 Using OVERCTL

| OVERCTL | Description                                                                                                                                                                                                                                                                                                     |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0b00    | Override controls disabled. PORTSEL is ignored.                                                                                                                                                                                                                                                                 |

| 0b01    | Ports selected by PORTSEL always behave as guaranteed transactions. For example, PORTSEL is b0000_0000_0000_0000_1, selecting port 0. All stimulus port writes to stimulus port 0 behave as guaranteed transactions.                                                                                            |

|         | Writes to other stimulus ports are treated as they would normally behave. For example, PORTSEL is b0000_0001_0000_0, selecting ports 32-63. All stimulus port writes to stimulus ports 32-63 behave as guaranteed transactions. Writes to other stimulus ports are treated as they would normally behave.       |

| 0b10    | Ports selected by PORTSEL always behave as invariant timing transactions. For example, PORTSEL is b0000_0000_0000_0000_1, selecting port 0. All stimulus port writes to stimulus port 0 behave as invariant timing transactions.                                                                                |

|         | Writes to other stimulus ports are treated as they would normally behave. For example, PORTSEL is b0000_0001_0000_0, selecting ports 32-63. All stimulus port writes to stimulus ports 32-63 behave as invariant timing transactions. Writes to other stimulus ports are treated as they would normally behave. |

| 0b11    | Reserved.                                                                                                                                                                                                                                                                                                       |

### 2.3.8 STMSPMOVERRIDER, Stimulus Port Master Override Register

The STMSPMOVERRIDER characteristics are:

| Purpose                                               | Enables a debugger to select which masters the STMSPOVERRIDER applies to.    |  |  |

|-------------------------------------------------------|------------------------------------------------------------------------------|--|--|

| Usage constraints                                     | There are no usage constraints.                                              |  |  |

| Configurations                                        | This register is optional. Read STMFEAT2R to determine if it is implemented. |  |  |

| Attributes                                            | See the register summary in Table 2-1 on page 2-15.                          |  |  |

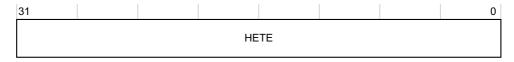

| Figure 2-8 shows the STMSPMOVERRIDER bit assignments. |                                                                              |  |  |

MASTCTL

#### Figure 2-8 STMSPMOVERRIDER bit assignments

Table 2-12 shows the STMSPMOVERRIDER bit assignments.

#### Table 2-12 STMSPMOVERRIDER bit assignments

| Bits    | Name    | Description                                                                                         |  |  |

|---------|---------|-----------------------------------------------------------------------------------------------------|--|--|

| [31:15] | MASTSEL | Master selection.                                                                                   |  |  |

|         |         | This field defines which master the override controls apply to.                                     |  |  |

|         |         | The size of this field is defined by the number of implemented masters.                             |  |  |

|         |         | The reset value is UNKNOWN.                                                                         |  |  |

| [14:1]  | -       | Reserved, UNK/SBZP.                                                                                 |  |  |

| [0]     | MASTCTL | This bit defines how the master selection is applied:                                               |  |  |

|         |         | 0b0 Master selection not enabled. STMSPOVERRIDER applies equally to all masters.                    |  |  |

|         |         | Øb1         Master selection enabled. STMSPOVERRIDER applies to the masters selected by<br>MASTSEL. |  |  |

|         |         | The reset value is 0b0.                                                                             |  |  |

#### MASTCTL == 0b0

When MASTCTL is 0b0 the override controls used by the STMSPOVERRIDER apply equally to all masters and MASTSEL is ignored.

#### MASTCTL == 0b1

When MASTCTL is 0b1, the MASTSEL field enables you to select a subset of the full masters to which the STMSPOVERRIDER applies. MASTSEL enables you to select a single master or power-of-two multiples of consecutive masters to which to apply the STMSPOVERRIDER.

To program MASTSEL, the bottom N bits which are 0 define a mask to apply to the master selection, then a 1 in bit N+1 demarks the mask from the master selection. The bits from N+2 to M select the master to which the STMSPOVERRIDER applies.

For example:

MASTSEL = bbbb\_bbbb\_bbbb\_1

A single master bbbb\_bbbb\_bbbb is selected.

MASTSEL = bbbb\_bbbb\_bbb1\_0000\_0

#### MASTSEL = 1000\_0000\_0000\_0

All masters are selected. This is equivalent to MASTCTL == 0b0.

Programming MASTCTL == 1 and MASTSEL = 0000\_0000\_0000\_0 is UNPREDICTABLE.

Programming a MASTSEL value which enables more masters than are implemented results in UNPREDICTABLE behavior. For example, programming 1000\_0000\_0000\_0000\_0 when only 32 masters are implemented. To enable all 32 masters, program 0000\_0000\_0000\_0000\_0.

#### Using MASTCTL

Table 2-13 shows how to use MASTCTL.

| MASTCTL | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0b0     | Master selection for override controls disabled and STMSPOVERRIDER applies equally to all masters. MASTSEL is ignored.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 0b1     | <ul> <li>The STMSPOVERRIDER applies to the masters selected by MASTSEL.</li> <li>For example: <ul> <li>MASTSEL is b0000_0000_0001_1, selecting master 1.</li> <li>STMSPOVERRIDER.OVERCTL is 0b01.</li> <li>STMSPOVERRIDER.PORTSEL is b0000_0000_0001_1, selecting port 1.</li> </ul> </li> <li>All stimulus port writes to stimulus port 1 on master 1 behave as guaranteed transactions. Writes to other stimulus ports on all other masters are treated as they would normally behave.</li> <li>For example: <ul> <li>MASTSEL is b0000_0000_0011_0, selecting masters 2-3.</li> <li>STMSPOVERRIDER.OVERCTL is 0b10.</li> <li>STMSPOVERRIDER.PORTSEL is b0000_0000_0011_0001_1, selecting ports 32-63.</li> </ul> </li> <li>All stimulus port writes to stimulus ports 32-63 on masters 2 and 3 behave as invariant timing transactions. Writes to other stimulus ports on all other masters are treated as they would normally behave.</li> </ul> |  |  |  |

#### 2.3.9 STMSPTRIGCSR, Stimulus Port Trigger Control and Status Register

The STMSPTRIGCSR characteristics are:

| Purpose           | Controls the STM triggers caused by the STMSPTER.                            |

|-------------------|------------------------------------------------------------------------------|

| Usage constraints | There are no usage constraints.                                              |

| Configurations    | This register is optional. Read STMFEAT1R to determine if it is implemented. |

| Attributes        | See the register summary in Table 2-1 on page 2-15.                          |

| F: 0.0.1 d        |                                                                              |

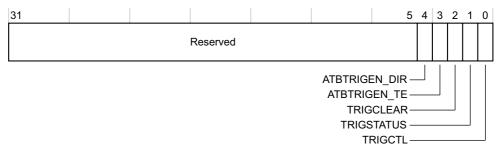

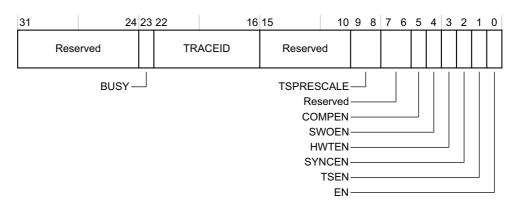

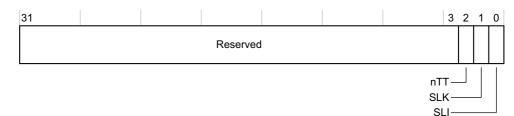

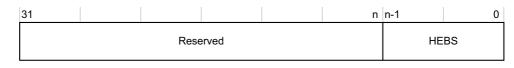

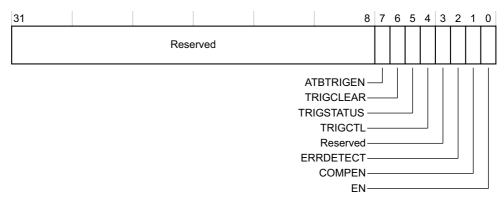

Figure 2-9 shows the STMSPTRIGCSR bit assignments.

Figure 2-9 STMSPTRIGCSR bit assignments

#### Table 2-14 shows the STMSPTRIGCSR bit assignments.

#### Table 2-14 STMSPTRIGCSR bit assignments

| Bits   | Туре | Name          | Description                                                                                                                                                                                                 |  |  |

|--------|------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| [31:5] | -    | -             | Reserved, UNK/SBZP.                                                                                                                                                                                         |  |  |

| [4]    | RW   | ATBTRIGEN_DIR | ATB trigger enable on direct writes to TRIG locations in an Extended Stimulus Port. When set, this bit enables the STM to use the ATID value of 0x7D when software writes to the TRIG locations.            |  |  |

|        |      |               | See Triggers on page 2-46 for more information.                                                                                                                                                             |  |  |

|        |      |               | The reset value is 0b0.                                                                                                                                                                                     |  |  |

| [3]    | RW   | ATBTRIGEN_TE  | ATB trigger enable on writes to Stimulus Ports being monitored using the STMSPTER.<br>When set, this bit enables the STM to use the ATID value of 0x7D when software writes to an<br>enabled Stimulus Port. |  |  |