# Arm<sup>®</sup> Embedded Trace Router Architecture Specification

# Arm Embedded Trace Router Architecture Specification

Copyright © 2018 Arm Limited or its affiliates. All rights reserved.

#### **Release Information**

The following changes have been made to this document.

|              |       |                  | Change History |

|--------------|-------|------------------|----------------|

| Date         | Issue | Confidentiality  | Change         |

| 13 July 2018 | А     | Non-Confidential | First Release. |

#### **Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or ™ are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at http://www.arm.com/company/policies/trademarks.

Copyright © 2018 Arm Limited or its affiliates. All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

# Contents Arm Embedded Trace Router Architecture Specification

|            | Prefa | ace                              |       |

|------------|-------|----------------------------------|-------|

|            |       | About this book                  | viii  |

|            |       | Using this book                  | ix    |

|            |       | Conventions                      | x     |

|            |       | Additional reading               |       |

|            |       | Feedback                         |       |

| Chapter 1  | Intro | oduction                         |       |

| •          | 1.1   | About trace capture              | 1-14  |

|            | 1.2   | About the ETR architecture       |       |

| Chapter 2  | Spec  | cification                       |       |

|            | 2.1   | Overview                         |       |

|            | 2.2   | Configurations                   |       |

|            | 2.3   | Operation                        |       |

|            | 2.4   | Trigger and Flush Operation      |       |

|            | 2.5   | Scatter mode                     |       |

| Chapter 3  | Prog  | grammers' model                  |       |

| •          | 3.1   | Memory-mapped registers          |       |

| Appendix A | Pseu  | udocode Definition               |       |

|            | A.1   | About Arm pseudocode             | A-104 |

|            | A.2   | Data types                       |       |

|            | A.3   | Expressions                      |       |

|            | A.4   | Operators and built-in functions |       |

|            |       |                                  |       |

| A.5 S | Statements and program structure | A-116 |

|-------|----------------------------------|-------|

|-------|----------------------------------|-------|

# Glossary

# Preface

This preface introduces the *Embedded Trace Router (ETR) Architecture Specification*. It contains the following sections:

- *About this book* on page viii.

- Using this book on page ix.

- *Conventions* on page x.

- Additional reading on page xi.

- *Feedback* on page xii.

# About this book

This book describes the architecture for the Embedded Trace Router (ETR).

# Intended audience

.

This document targets the following audiences:

- Designers of development tools supporting processor trace functionality.

- Advanced users of development tools supporting processor trace functionality.

- Designers of an Arm-based product that includes processor trace functionality.

Arm recommends that all users of this specification have experience of the Arm architecture.

# Using this book

This book is organized into the following chapters:

### **Chapter 1** Introduction

Read this chapter for an introduction to processor-originated trace, the Embedded Trace Router, and the overlap with the CoreSight Trace Memory Controller.

### **Chapter 2** Specification

Read this chapter for the Embedded Trace Router specification, register configurations for optional features, and operation modes.

## Chapter 3 Programmers' model

Read this chapter for a description of the programmers' model for the Embedded Trace Router.

## Appendix A Pseudocode Definition

Read this appendix for a description of the pseudocode that is used in this document.

*Glossary* Read this for definitions of some of the terms used in this book. The glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

# Conventions

The following sections describe conventions that this document might use:

- Typographic conventions.

- Signals.

- Numbers.

- Pseudocode descriptions.

### **Typographic conventions**

The typographical conventions are:

*italic* Introduces special terminology, and denotes citations.

bold Denotes signal names, and is used for terms in descriptive lists, where appropriate.

monospace Used for assembler syntax descriptions, pseudocode, and source code examples.

Also used in the main text for instruction mnemonics and for references to other items appearing in assembler syntax descriptions, pseudocode, and source code examples.

#### SMALL CAPITALS

Used for a few terms that have specific technical meanings, and are included in the Glossary.

**Colored text** Indicates a link. This can be:

- A URL, for example http://infocenter.arm.com.

- A cross-reference, that includes the page number of the referenced information if it is not on the current page, for example, *Pseudocode descriptions*.

- A link, to a chapter or appendix, or to a glossary entry, or to the section of the document that defines the colored term, for example *JTAG Access Port (JTAG-AP)* or Debug Access Port (DAP).

### Signals

The signal conventions are:

Signal level

The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

HIGH for active-HIGH signals.

LOW for active-LOW signals.

Lower-case n

At the start or end of a signal name denotes an active-LOW signal.

### Numbers

Numbers are normally written in decimal. Binary numbers are preceded by 0b, and hexadecimal numbers by 0x. In both cases, the prefix and the associated value are written in a monospace font, for example 0xFFFF0000.

### **Pseudocode descriptions**

This book uses a form of pseudocode to provide precise descriptions of the specified functionality. This pseudocode is written in a monospace font, and is described in Appendix A *Pseudocode Definition*.

# Additional reading

This section lists relevant publications from Arm and third parties.

See the Infocenter http://infocenter.arm.com, for access to Arm documentation.

# Arm publications

This book contains information that is specific to this product. See the following documents for other relevant information:

- CoreSight<sup>™</sup> Trace Memory Controller (ARM DDI 0461).

- Arm<sup>®</sup> CoreSight<sup>™</sup> Architecture Specification (ARM DDI 0029).

- Arm<sup>®</sup> CoreSight<sup>™</sup> System-on-Chip SoC-600 Technical Reference Manual (ARM 100806).

- Arm<sup>®</sup> Embedded Trace Macrocell Architecture Specification ETMv4.0to ETMv4.4 (ARM IHI 0064).

# Other publications

•

The following books are referred to in this book, or provide more information:

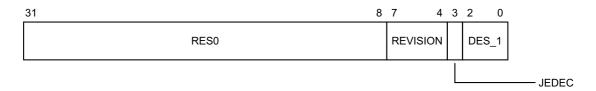

• JEDEC, Standard Manufacturers Identification Code, JEP106 hhtp://www.jedec.org.

# Feedback

Arm welcomes feedback on its documentation.

# Feedback on this book

If you have comments on the content of this book, send an e-mail to errata@arm.com. Give:

- The title.

- The number, ARM IHI 0081A.

- The page numbers to which your comments apply.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

—— Note ——

Arm tests PDFs only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the appearance or behavior of any document when viewed with any other PDF reader.

# Chapter 1 Introduction

This chapter introduces the Embedded Trace Router. It contains the following sections:

- *About trace capture* on page 1-14.

- *About the ETR architecture* on page 1-15.

# 1.1 About trace capture

In many CoreSight systems, trace is routed over a CoreSight trace fabric (AMBA ATB) through a series of trace funnels, and replicators, to one or more trace sinks.

One such trace sink is the CoreSight *Trace Memory Controller* (TMC). This can take various forms, one of which is an *Embedded Trace Router* (ETR). The function of the ETR is to write formatted trace to a buffer in memory. In effect, it is a bridge between the trace and memory fabrics.

This specification describes the ETR architecture, which is useful for both:

- Self-hosted trace, where trace is captured in system memory, for analysis by software running on the same system.

- External trace, where trace is captured in system memory, for subsequent export to an external debugger.

### Table 1-1 Comparison of self-hosted and external trace

| Term       | Self-hosted trace                                                                                                                                                                                                                                            | External trace                                                                                                                                                                                                               |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Definition | Located within the software stack.<br>The agent controlling trace collection is part of the same<br>software stack as the software being traced.                                                                                                             | Located outside of the software stack.<br>The agent controlling trace collection is<br>not part of the same software stack as the<br>software being traced.                                                                  |

| Examples   | <ul><li>perf: trace of applications and the operating system is collected by the operating system.</li><li>gdb: the debugger is an application but uses operating system services to trace another application running unde that operating system.</li></ul> | Arm DS-5 Debugger: Trace is collected<br>on-chip and exported to a debugger on a<br>different host for analysis.<br>r Post-mortem: Trace is collected by a<br>system control processor to provide<br>crash dump information. |

# 1.1.1 Trace format

This specification does not define the trace format used. It is expected that it is used in conjunction with an *ETMv4* trace unit. However, other options are permitted.

— Note —

If the trace protocol uses variable packet sizes, it must support an Alignment Synchronization mechanism to allow use in Circular Buffer mode.

The ETMv4 Ignore packet allows the ETM to pad trace in the trace buffer to an arbitrary alignment. For earlier versions of the ETMv4 protocol, a trace formatter must be implemented in the ETR.

## 1.1.2 Interrupts

An event is raised on a trigger or other buffer service event, such as an abort or the buffer filling.

For self-hosted trace, this is ideally a PPI interrupt. For external trace, this is either an SPI, LPI (MSI) or a cross-trigger event.

The ETR architecture also supports message-signaled interrupts, providing configuration registers to control these interrupts.

# **1.2** About the ETR architecture

The ETR architecture provides control mechanisms for storing trace data in a buffer in main system memory. Such a trace buffer can operate in one of the following modes:

### **Circular Buffer**

In Circular Buffer mode, trace data is written to the buffer continuously. When the end of the buffer is reached, trace continues to be written from the start of the buffer, overwriting the oldest data in the buffer.

Circular Buffer mode is used to continuously capture trace. When the trace capture stops, the buffer contains the most recently generated trace, and provides a recent history of trace up to the stop point. Trace data can only be read out of the buffer when trace capture has stopped.

An ETR always implements the Circular Buffer mode.

### Software Read FIFO Modes

In the Software Read FIFO modes, trace is written to the buffer continuously until the buffer is full. When the buffer is full, trace stops being written until space is freed in the buffer. Usually, a software agent concurrently reads trace data out of the buffer, and the memory buffer is used as an intermediate FIFO.

In Software Read FIFO mode 1, the trace data is read out of the buffer using the RRD in the ETR programmer's model.

In Software Read FIFO mode 2, the trace data is read directly out of the memory buffer, which is typically faster than Software Read FIFO mode 1. The software agent reading the buffer uses the RURP in the ETR programmers' model to indicate when data has been read out of the buffer.

The Software Read FIFO modes are optional.

# 1.2.1 Overlap with CoreSight Trace Memory Controller

The ETR architecture is based on the Embedded Trace Router configuration of the *CoreSight Trace Memory Controller (TMC)*, but makes the following major features optional:

- Scatter mode.

- Software Read FIFO mode 1.

- Buffer Watermark and Level registers.

An ETR without Scatter mode and without Software Read FIFO mode 1 means that the ETR does not need to read memory, which can simplify the ETR design.

An ETR without the buffer watermark feature can still generate interrupts, by initializing the RWP in a specific way.

— Note

To generate an interrupt when the buffer is almost full (around 90%), software can:

- Set DBA to the base of the buffer and RSZ to the size of the buffer.

- Set RWP to DBA + RSZ  $\times$  10%.

- Set MODE.MODE to Circular Buffer.

- Configure ETR to generate an interrupt on FULL event.

Software written for the *CoreSight TMC* is not guaranteed to be compatible with an ETR compliant with this specification.

Software written for this specification is not guaranteed to be compatible with the CoreSight TMC.

1 Introduction 1.2 About the ETR architecture

# Chapter 2 Specification

This chapter describes the Embedded Trace Router Specification. It contains the following sections:

- Overview on page 2-18.

- *Configurations* on page 2-19.

- *Operation* on page 2-20.

- Trigger and Flush Operation on page 2-23.

- Scatter mode on page 2-25.

# 2.1 Overview

•

| I <sub>JDFA</sub> | The ETR architecture specifies the following features not defined in CoreSight ETR: |

|-------------------|-------------------------------------------------------------------------------------|

|                   | •                                                                                   |

|                   | • Self-hosted support through interrupt generation.                                 |

| R <sub>ASDF</sub> | The following ETR features are optional:                                            |

|                   | • Trace formatter.                                                                  |

|                   | • Software Read FIFO mode 1, including the buffer watermark and level registers.    |

|                   | • Software Read FIFO mode 2, including the buffer watermark and level registers.    |

|                   | • Self-hosted support through interrupt generation.                                 |

|                   | • Periodic synchronization counter (PSCR).                                          |

|                   | Claim tags.                                                                         |

|                   | CoreSight Software Lock.                                                            |

|                   | • RAM Write Data register (RWD) and the Integration Test registers.                 |

| R <sub>IUYE</sub> | If the trace formatter is not implemented, the ETR does not support:                |

|                   | • Multiple trace sources.                                                           |

|                   | • Embedded Flush.                                                                   |

|                   | • Embedded Triggers on flush.                                                       |

Embedded Triggers on Trigger Events.

# 2.2 Configurations

| R <sub>AYIK</sub> | DEVID.MEMWIDTH specifies the IMPLEMENTATION DEFINED minimum alignment for the DBA, RRP, RURP, RWP, BUFWM and RSZ registers. Software must treat the corresponding low-order bits of these registers as SBZP:                                                                                             |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | • When software first writes to a pointer register, the value written must be aligned to a multiple of the size specified by DEVID.MEMWIDTH.                                                                                                                                                             |

|                   | • When context switching the ETR context, software must preserve the low-order bits.                                                                                                                                                                                                                     |

|                   | DBA, BUFWM and RSZ have a minimum architectural alignment of 32-bits. The BUFWM and RSZ registers always specify a number of 32-bit words.                                                                                                                                                               |

| R <sub>CXVZ</sub> | Circular Buffer mode must be implemented.                                                                                                                                                                                                                                                                |

| R <sub>ZXCA</sub> | It is IMPLEMENTATION DEFINED whether Software Read FIFO mode 1 is implemented.                                                                                                                                                                                                                           |

| R <sub>ZXCV</sub> | It is IMPLEMENTATION DEFINED whether Software Read FIFO mode 2 is implemented.                                                                                                                                                                                                                           |

| R <sub>IFHM</sub> | If both Software Read FIFO modes are not implemented, RRP, CBUFLEVEL, LBUFLEVEL and BUFWM are not implemented.                                                                                                                                                                                           |

| I <sub>NWUI</sub> | The mode is controlled by MODE.MODE. DEVID.MODES describes which modes are implemented.                                                                                                                                                                                                                  |

| I <sub>GHKL</sub> | A system including an ETR might support the input trace to the ETR being routed to trace sinks other than the ETR, for example via a AMBA ATB interface. Arm recommends that when CTL.TraceCaptEn is 0b1, the routing of trace to other trace sinks does not limit the input trace bandwidth to the ETR. |

#### Operation 2.3

IASDF

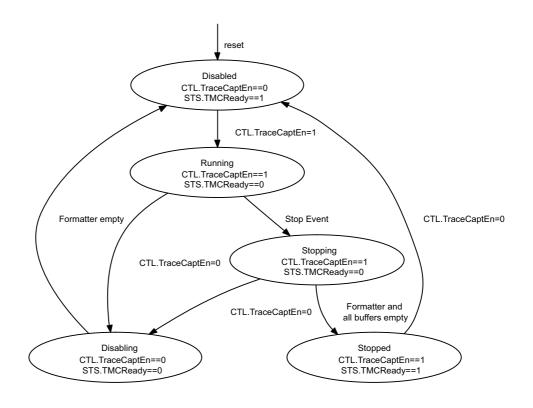

The ETR state machine is defined by CTL.TraceCaptEn, STS.TMCReady and the state of the trace formatter (if implemented) and internal buffers:

|           |                 | Table 2-1 ETR state machine index |                         |

|-----------|-----------------|-----------------------------------|-------------------------|

| State     | CTL.TraceCaptEn | STS.TMCReady                      | Formatter and buffer(s) |

| Disabled  | 0               | 1                                 | Empty                   |

| Running   | 1               | 0                                 | -                       |

| Stopping  | 1               | 0                                 | Not empty               |

| Stopped   | 1               | 1                                 | Empty                   |

| Disabling | 0               | 0                                 | Not empty               |

# Figure 2-1 ETR state machine

| I <sub>SDFV</sub> | When the ETR leaves the Disabled state, the ETR starts collecting trace to a buffer starting from the address in the RWP register.                                                                                                                                                          |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | Note                                                                                                                                                                                                                                                                                        |

|                   | In <i>CoreSight Trace Memory Controller (TMC)</i> , when leaving the Disabled state, RWP is set to the value in DBA. The ETR architecture does not automatically set RWP when leaving the Disabled state. To ensure compatibility, software should not rely on the ETR resetting RWP to DBA |

| R <sub>SDFG</sub> | If the trace formatter is not implemented or disabled, when the ETR is in the Running state, each trace data byte received by the ETR is written to the address specified by RWP.                                                                                                           |

| R <sub>XOVD</sub> | If the trace formatter is implemented and enabled, when the ETR is in the Running state, each trace byte received by the ETR is formatted. Each formatted byte is written to the address specified by RWP.                                                                                  |

|                   |                                                                                                                                                                                                                                                                                             |

| I <sub>DFAV</sub> | The trace formatter protocol is described by the CoreSight Architecture Specification.                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R <sub>KPDF</sub> | For each byte written by the ETR, RWP is incremented by 1.                                                                                                                                                                                                                                                                                                                                                                                         |

| I <sub>MGHJ</sub> | The ETR might buffer multiple bytes into a single write, and increment RWP by the number of bytes written, so long as it does not write past the end of the buffer.                                                                                                                                                                                                                                                                                |

| R <sub>BWUA</sub> | <ul> <li>If Scatter mode is not implemented or is disabled, and the ETR increments RWP to (DBA + RSZ×4), then all of:</li> <li>RWP is set to DBA.</li> <li>If MODE.MODE == 0b00 (Circular Buffer) then STS.Full is set to 1.</li> </ul>                                                                                                                                                                                                            |

| R <sub>CVBN</sub> | If Scatter mode is not implemented or is disabled, and the ETR increments RRP to (DBA + RSZ $\times$ 4), then RRP is set to DBA.                                                                                                                                                                                                                                                                                                                   |

| R <sub>NLSF</sub> | <ul> <li>If MODE.MODE != 0b00, the buffer fill level is defined as:</li> <li>((RWP - RRP) modulo (RSZ × 4)) when the trace buffer is not full.</li> <li>RSZ × 4 when the trace buffer is full.</li> </ul>                                                                                                                                                                                                                                          |

| R <sub>ALRU</sub> | <ul> <li>If MODE.MODE != 0b00, STS.Full is:</li> <li>Set to 1 when the buffer fill level is greater than or equal to (RSZ - BUFWM)×4.</li> <li>Set to 0 when the buffer fill level is less than (RSZ - BUFWM)×4.</li> </ul>                                                                                                                                                                                                                        |

| I <sub>FGHB</sub> | <ul> <li>In Software Read FIFO modes:</li> <li>The trace buffer is empty when RRP increments to RWP.</li> <li>The trace buffer is full when RWP increments to RRP.</li> </ul>                                                                                                                                                                                                                                                                      |

| R <sub>BYUU</sub> | In Circular Buffer mode, the ETR continues to write trace data to the trace buffer until a Stop Event occurs.                                                                                                                                                                                                                                                                                                                                      |

| R <sub>FGJH</sub> | In Software FIFO modes, the ETR continues to write trace data to the trace buffer until a Stop Event occurs or the trace buffer becomes full. While the trace buffer is full, the ETR stalls the acceptance of new trace data until space becomes available in the trace buffer.                                                                                                                                                                   |

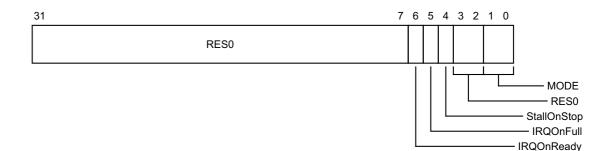

| I <sub>VNWN</sub> | If the self-hosted interrupts are implemented, software configures which interrupts are generated using MODE.IRQOnReady and MODE.IRQOnFull.                                                                                                                                                                                                                                                                                                        |

| R <sub>NZKO</sub> | If Software Read FIFO mode 2 is implemented, the buffer interrupt for Software Read FIFO mode 2 is enabled whenever Software Read FIFO mode 2 is selected and the ETR is enabled.                                                                                                                                                                                                                                                                  |

| R <sub>YDHF</sub> | In Circular Buffer mode and if RRP is implemented, if RWP increments to RRP then any subsequent increment to RWP also increments RRP to the new value of RWP. This tracking continues until the ETR stops or is disabled.                                                                                                                                                                                                                          |

| R <sub>LPZF</sub> | <ul> <li>If the trace formatter is implemented and enabled when trace capture is stopped, then the traces are padded in the formatted frames with additional bytes of data with a value of 0x00 and an ID of 0x00, until the following conditions are met:</li> <li>A whole number of frames have been generated.</li> <li>RWP is aligned to a multiple of DEVID.MEMWIDTH.</li> </ul>                                                              |

| R <sub>NQWE</sub> | <ul> <li>If the trace formatter is not implemented or is disabled when trace capture is stopped, then it is IMPLEMENTATION DEFINED whether the ETR writes the stop sequence to the end of the trace buffer. The stop sequence consists of:</li> <li>A single byte of value 0x01, to indicate the position of the last byte before the stop sequence.</li> <li>Zero or more bytes of 0x00, to align RWP to a multiple of DEVID.MEMWIDTH.</li> </ul> |

| I <sub>MLIU</sub> | If the trace formatter is not implemented and the ETR is tightly-coupled to a trace source, Arm recommends that the trace source generates sufficient padding bytes in its own trace protocol to align RWP before trace capture is stopped, and the ETR does not generate the stop sequence.                                                                                                                                                       |

| R <sub>OUYG</sub> | When the ETR is in the Running state, on a Stop Event the ETR enters the Stopping state.                                                                                                                                                                                                                                                                                                                                                           |

# 2 Specification 2.3 Operation

| R <sub>LQWE</sub> | A Stop Event occurs when any of the following occur:                                                                                                                                                                                                                                                             |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | • A Flush Completion occurs when FFCR.StopOnFl is 0b1.                                                                                                                                                                                                                                                           |

|                   | • A Trigger Event occurs when FFCR.StopOnTrigEvt is 0b1.                                                                                                                                                                                                                                                         |

| R <sub>HDGP</sub> | The ETR moves from Stopping state to Stopped state when all trace which was received by the ETR before entering Stopping state has been output to the trace buffer, including any stop sequence or padding frames.                                                                                               |

| R <sub>MFGS</sub> | In the Stopped state, the ETR moves to the Disabled state when CTL.TraceCaptEn is changed from 0b1 to 0b0.                                                                                                                                                                                                       |

| Ioutj             | In Software Read FIFO modes, the ETR might not move from the Stopping state to the Stopped state if there is insufficient space to insert the remaining trace data in the trace buffer. Reads of the trace buffer via the RRD or updates using the RURP might be needed before the ETR enters the Stopped state. |

| R <sub>PLOK</sub> | If CTL.TraceCaptEn is changed from 0b1 to 0b0 when not in the Stopped state, the trace captured in the trace buffer might be incomplete and the ETR pointers might not reflect the correct position of the trace buffer.                                                                                         |

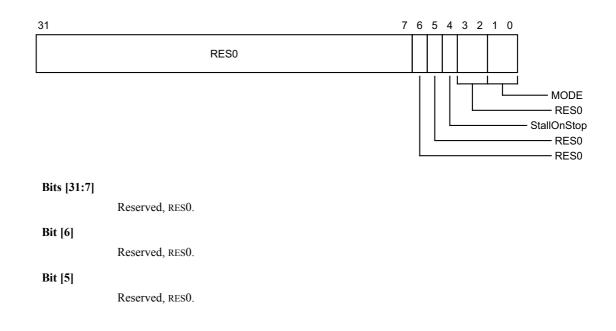

| R <sub>ZEWQ</sub> | <ul> <li>In the Stopping, Stopped, Disabling, and Disabled states, no new trace is captured by the ETR and:</li> <li>If MODE.StallOnStop is 0b0, the ETR discards any new trace received.</li> </ul>                                                                                                             |

• If MODE.StallOnStop is 0b1, the ETR does not discard any new trace received.

# 2.4 Trigger and Flush Operation

| I <sub>BUIR</sub> | The ETR architecture supports detection of a trigger condition. A trigger condition is typically used to stop trace capture to ensure trace is captured around a point of interest.                                                                                                                                                                               |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | A Detected Trigger is where the ETR detects a trigger condition from an external source, such as a trace source or a Cross Trigger Interface. A Detected Trigger consists of one or more of the following:                                                                                                                                                        |

|                   | An external Trigger Input.                                                                                                                                                                                                                                                                                                                                        |

|                   | • A Trigger ID indicated with the trace from the trace source(s).                                                                                                                                                                                                                                                                                                 |

|                   | An Embedded Trigger is where the ETR inserts a special trace source ID into a formatted trace stream. Embedded Triggers are not supported if the trace formatter is not implemented.                                                                                                                                                                              |

|                   | A Trigger Event occurs when the Trigger Counter has counted the specified number of trace bytes after a Detected Trigger.                                                                                                                                                                                                                                         |

|                   | The Trigger Counter is a counter used to delay a Trigger Event for a specified number of trace bytes after a Detected Trigger.                                                                                                                                                                                                                                    |

| I <sub>CHSD</sub> | The ETR architecture supports flushing of the ETR and any trace sources connected to the ETR. Flushing involves requesting all outstanding data from any upstream trace sources, and ensuring all of the flushed data is inserted into the trace buffer. Typically, a flush is used when stopping trace capture to ensure all outstanding data has been captured. |

|                   | A Detected Flush is where the ETR detects a request for a flush, such as via the ETR programmers' model or a Cross Trigger Interface. A Detected Flush consists of one or more of the following:                                                                                                                                                                  |

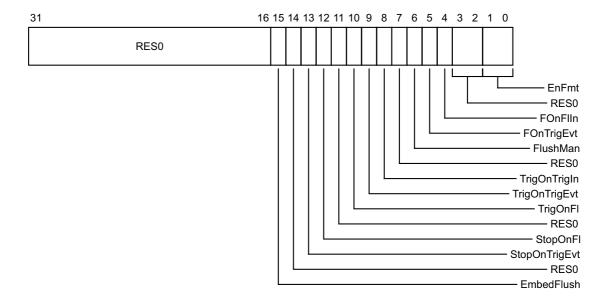

|                   | • An external Flush Input when FFCR.FOnFlIn is 0b1.                                                                                                                                                                                                                                                                                                               |

|                   | • A Manual Flush initiated via FFCR.FlushMan.                                                                                                                                                                                                                                                                                                                     |

|                   | • When a Trigger Event occurs FFCR.FOnTrigEvt is 0b1.                                                                                                                                                                                                                                                                                                             |

|                   | An Embedded Flush is where the ETR inserts a special trace source ID into a formatted trace stream. Embedded Flushes are not supported if the trace formatter is not implemented.                                                                                                                                                                                 |

|                   | A Flush Completion occurs when the ETR has ensured that all outstanding data has been captured in the trace buffer.                                                                                                                                                                                                                                               |

|                   |                                                                                                                                                                                                                                                                                                                                                                   |

| R <sub>ZXMN</sub> | When the first Detected Trigger occurs, the Trigger Counter starts counting the number of bytes written to the trace buffer.                                                                                                                                                                                                                                      |

| R <sub>KLFG</sub> | When the Trigger Counter has counted the number of bytes programmed into the TRG register, a Trigger Event occurs.                                                                                                                                                                                                                                                |

|                   | Note                                                                                                                                                                                                                                                                                                                                                              |

|                   | The TRG register specifies a number of 32-bit words.                                                                                                                                                                                                                                                                                                              |

| R <sub>VMCB</sub> | When the trace formatter is implemented and enabled, an Embedded Trigger is inserted into the formatted trace stream when any of the following occur:                                                                                                                                                                                                             |

|                   | • FFCR.TrigOnTrigEvt is 0b1 and a Trigger Event occurs.                                                                                                                                                                                                                                                                                                           |

|                   | • FFCR.TrigOnTrigIn is 0b1 and a Detected Trigger occurs via an external Trigger Input.                                                                                                                                                                                                                                                                           |

|                   | • FFCR.TrigOnFl is 0b1 and a Flush Completion occurs.                                                                                                                                                                                                                                                                                                             |

| R <sub>PWTY</sub> | An Embedded Trigger consists of a single zero data byte with a trace ID of 0x7D.                                                                                                                                                                                                                                                                                  |

| R <sub>HGFD</sub> | An Embedded Flush consists of a single zero data byte with a trace ID of 0x7B.                                                                                                                                                                                                                                                                                    |

| R <sub>VORH</sub> | A Detected Flush occurs when any of the following occur:                                                                                                                                                                                                                                                                                                          |

|                   | • The external Flush Input is asserted and FFCR.FOnFlIn is 0b1.                                                                                                                                                                                                                                                                                                   |

|                   | • FFCR.FlushMan is written with 0b1.                                                                                                                                                                                                                                                                                                                              |

|                   | • A Trigger Event occurs and FFCR.FOnTrigEvt is 0b1.                                                                                                                                                                                                                                                                                                              |

|                   | • A Higger Event occurs and FFCK.FOITHgEvt is obt.                                                                                                                                                                                                                                                                                                                |

| R <sub>LDFG</sub> | When a Detected Flush occurs, the ETR performs the following sequence:                                                                                                                                                                                                                 |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | 1. Requests all connected trace sources to output all data that has been accrued.                                                                                                                                                                                                      |

|                   | 2. Outputs all the data received from the trace sources to the trace buffer.                                                                                                                                                                                                           |

|                   | 3. Indicates a Flush Completion.                                                                                                                                                                                                                                                       |

|                   |                                                                                                                                                                                                                                                                                        |

| R <sub>SGCV</sub> | When the trace formatter is implemented and enabled, an Embedded Flush is inserted into the formatted trace stream when a Flush Completion occurs and FFCR.EmbedFlush is 0b1. The Embedded Flush is inserted after the last byte of trace data and before the end of the padding data. |

# 2.5 Scatter mode

| I <sub>ASDF</sub> | Scatter mode is used in CoreSight Trace Memory Controller (TMC) to distribute the trace buffer in non-contiguous |

|-------------------|------------------------------------------------------------------------------------------------------------------|

|                   | memory pages.                                                                                                    |

$R_{IJKS}$  Scatter mode is not implemented, and DEVID.NOSCAT is 0b1.

2 Specification 2.5 Scatter mode

# Chapter 3 Programmers' model

This chapter describes the Embedded Trace Router programmers' model. It contains the following sections:

• *Memory-mapped registers* on page 3-28.

# 3.1 Memory-mapped registers

Table 3-1 shows the register index for the Embedded Trace Router programmers' model.

### Table 3-1 Index of ETR registers ordered by offset

| Register   | Offset         | Length | Description, see                                             |

|------------|----------------|--------|--------------------------------------------------------------|

| RSZ        | 0x004          | 32     | RSZ, RAM Size Register on page 3-94                          |

| STS        | 0x00C          | 32     | STS, Status Register on page 3-98                            |

| RRD        | 0x010          | 32     | RRD, RAM Read Data register on page 3-92                     |

| RRP        | 0x014<br>0x038 | 64     | RRP, RAM Read Pointer on page 3-93                           |

| RWP        | 0x018<br>0x03C | 64     | RWP, RAM Write Pointer on page 3-97                          |

| TRG        | 0x01C          | 32     | TRG, Trigger Counter Register on page 3-102                  |

| CTL        | 0x020          | 32     | CTL, Control Register on page 3-52                           |

| RWD        | 0x024          | 32     | RWD, RAM Write Data register on page 3-96                    |

| MODE       | 0x028          | 32     | MODE, Mode Register on page 3-79                             |

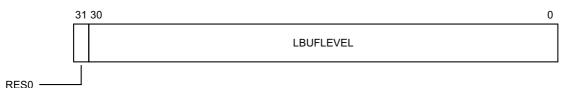

| LBUFLEVEL  | 0x02C          | 32     | LBUFLEVEL, Latched Buffer Fill Level on page 3-76            |

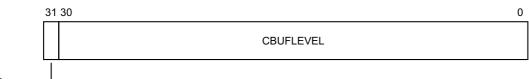

| CBUFLEVEL  | 0x030          | 32     | CBUFLEVEL, Current Buffer Fill Level on page 3-45            |

| BUFWM      | 0x034          | 32     | BUFWM, Buffer Watermark register on page 3-33                |

| BUSCTL     | 0x110          | 32     | BUSCTL, Bus Control Register on page 3-34                    |

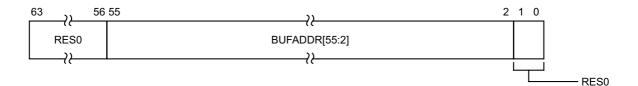

| DBA        | 0x118          | 64     | DBA, Data Buffer Address on page 3-53                        |

| RURP       | 0x120          | 32     | RURP, RAM Update Read Pointer on page 3-95                   |

| FFSR       | 0x300          | 32     | FFSR, Formatter and Flush Status Register on page 3-68       |

| FFCR       | 0x304          | 32     | FFCR, Formatter and Flush Control Register on page 3-63      |

| PSCR       | 0x308          | 32     | PSCR, Periodic Synchronization Control Register on page 3-90 |

| IRQCR0     | 0xE80          | 64     | IRQCR0, Interrupt Configuration Register on page 3-70        |

| IRQCR1     | 0xE88          | 32     | IRQCR1, Interrupt Configuration Register 1 on page 3-71      |

| IRQCR2     | 0xE8C          | 32     | IRQCR2, Interrupt Configuration Register 2 on page 3-72      |

| ITCTRL     | 0xF00          | 32     | ITCTRL, Integration Mode Control Register on page 3-74       |

| CLAIMSET   | 0xFA0          | 32     | CLAIMSET, Claim Tag Set Register on page 3-51                |

| CLAIMCLR   | 0xFA4          | 32     | CLAIMCLR, Claim Tag Clear Register on page 3-50              |

| LAR        | 0xFB0          | 32     | LAR, Lock Access Register on page 3-75                       |

| LSR        | 0xFB4          | 32     | LSR, Lock Status Register on page 3-77                       |

| AUTHSTATUS | 0xFB8          | 32     | AUTHSTATUS, Authentication Status Register on page 3-31      |

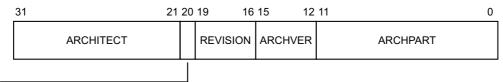

| DEVARCH    | 0xFBC          | 32     | DEVARCH, Device Architecture Register on page 3-54           |

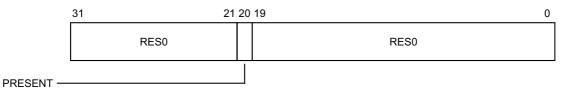

| DEVID1     | 0xFC4          | 32     | DEVID1, Device Configuration Register 1 on page 3-61         |

| Register | Offset | Length | Description, see                                        |

|----------|--------|--------|---------------------------------------------------------|

| DEVID    | 0xFC8  | 32     | DEVID, Device Configuration Register on page 3-56       |

| DEVTYPE  | 0xFCC  | 32     | DEVTYPE, CoreSight Device Type Register on page 3-62    |

| PIDR4    | 0xFD0  | 32     | PIDR4, Peripheral Identification Register on page 3-86  |

| PIDR5    | 0xFD4  | 32     | PIDR5, Peripheral Identification Register on page 3-87  |

| PIDR6    | ØxFD8  | 32     | PIDR6, Peripheral Identification Register on page 3-88  |

| PIDR7    | 0xFDC  | 32     | PIDR7, Peripheral Identification Register on page 3-89  |

| PIDR0    | 0xFE0  | 32     | PIDR0, Peripheral Identification Register on page 3-82  |

| PIDR1    | 0xFE4  | 32     | PIDR1, Peripheral Identification Register on page 3-83  |

| PIDR2    | 0xFE8  | 32     | PIDR2, Peripheral Identification Register on page 3-84  |

| PIDR3    | 0xFEC  | 32     | PIDR3, Peripheral Identification Register on page 3-85  |

| CIDR0    | 0xFF0  | 32     | CIDR0, Component Identification Register 0 on page 3-46 |

| CIDR1    | 0xFF4  | 32     | CIDR1, Component Identification Register 1 on page 3-47 |

| CIDR2    | 0xFF8  | 32     | CIDR2, Component Identification Register 2 on page 3-48 |

| CIDR3    | 0xFFC  | 32     | CIDR3, Component Identification Register 3 on page 3-49 |

# Table 3-1 Index of ETR registers ordered by offset (continued)

Table 3-2 shows the reset values for the Embedded Trace Router programmers' model.

| Table 3-2 | ETR | reaister | field | reset | values  |

|-----------|-----|----------|-------|-------|---------|

|           |     |          |       |       | , and o |

| Register field       | Reset value |

|----------------------|-------------|

| BUSCTL.SORGN         | 0           |

| BUSCTL.SIRGN         | 0           |

| BUSCTL.BAttr         | 0           |

| CLAIMCLR.CLR <m></m> | 0           |

| CTL.TraceCaptEn      | 0           |

| FFCR.EmbedFlush      | 0           |

| FFCR.StopOnTrigEvt   | 0           |

| FFCR.StopOnFl        | 0           |

| FFCR.TrigOnFl        | 0           |

| FFCR.TrigOnTrigEvt   | 0           |

| FFCR.TrigOnTrigIn    | 0           |

| FFCR.FlushMan        | 0           |

| FFCR.FOnTrigEvt      | 0           |

| FFCR.FOnFlIn         | 0           |

# Table 3-2 ETR register field reset values (continued)

| Register field     | Reset value |

|--------------------|-------------|

| FFCR.EnFmt         | 0           |

| FFCR.StopOnTrigEvt | 0           |

| FFCR.StopOnFI      | 0           |

| FFCR.FlushMan      | 0           |

| FFCR.FOnTrigEvt    | 0           |

| FFCR.FOnFIIn       | 0           |

| ITCTRL.IME         | 0           |

| PSCR.PSCount       | 10          |

| STS.TMCReady       | 1           |

# 3.1.1 AUTHSTATUS, Authentication Status Register

The AUTHSTATUS characteristics are:

### Purpose

Provides information about the state of the IMPLEMENTATION DEFINED authentication interface for debug.

### Usage constraints

There are no usage constraints.

### Configurations

There are no configuration notes.

### Attributes

AUTHSTATUS is a 32-bit register.

### **Field descriptions**

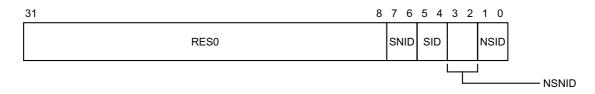

The AUTHSTATUS bit assignments are:

### Bits [31:8]

Reserved, RESO.

### SNID, bits [7:6]

Secure Non-invasive Debug. Indicates whether Secure non-invasive debug is enabled. The defined values of this field are:

0b00 Secure non-invasive debug not implemented.

This field reads as 0b00.

### SID, bits [5:4]

Secure Invasive Debug. Indicates whether Secure invasive debug is enabled. The defined values of this field are:

- 0b00 Secure invasive debug not implemented.

- 0b10 Secure invasive debug disabled.

- 0b11 Secure invasive debug enabled.

### NSNID, bits [3:2]

Non-secure Non-invasive Debug. Indicates whether Non-secure non-invasive debug is enabled. The defined values of this field are:

0b00 Non-secure non-invasive debug not implemented.

This field reads as 0b00.

### NSID, bits [1:0]

Non-secure Invasive Debug. Indicates whether Non-secure invasive debug is enabled. The defined values of this field are:

0b00 Non-secure invasive debug not implemented.

0b10 Non-secure invasive debug disabled.

0b11 Non-secure invasive debug enabled.

Arm recommends that Non-secure invasive debug is always enabled at the ETR.

# Accessing the AUTHSTATUS:

AUTHSTATUS can be accessed through its memory-mapped interface:

| Component | Offset |  |

|-----------|--------|--|

| ETR       | 0xFB8  |  |

This interface is accessible as follows:

Access to this register is RO.

## 3.1.2 BUFWM, Buffer Watermark register

The BUFWM characteristics are:

### Purpose

Provides threshold vacancy level in 32-bit words in the trace memory.

### Usage constraints

Writes to BUFWM are UNPREDICTABLE unless the ETR is in the Disabled state.

### Configurations

This register is present only when DEVID.MODES != 0b010. Otherwise, direct accesses to BUFWM are RES0.

### Attributes

BUFWM is a 32-bit register.

# **Field descriptions**

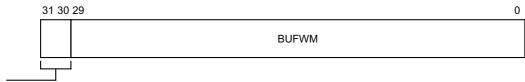

The BUFWM bit assignments are:

RES0 —

### Bits [31:30]

Reserved, RESO.

### BUFWM, bits [29:0]

Buffer Watermark. Indicates the desired threshold vacancy level in the trace memory in 32-bit words. When the available space in the trace memory is less than or equal to this value, STS.Full is set to 1.

Software must set this field to a multiple of the minimum alignment defined by DEVID.MEMWIDTH divided by 4.

This field is ignored by the ETR when MODE.MODE == 0b00, meaning Circular Buffer mode is selected.

# Accessing the BUFWM:

BUFWM can be accessed through its memory-mapped interface:

| Component | Offset |

|-----------|--------|

| ETR       | 0x034  |

This interface is accessible as follows:

Access to this register is RW.

# 3.1.3 BUSCTL, Bus Control Register

The BUSCTL characteristics are:

### Purpose

Controls ETR accesses to system memory.

### Usage constraints

If any field in this register is set to a reserved value:

- The behavior is as if the field is set to an UNKNOWN implemented value.

- The ETR must not generate invalid bus transactions.

- This might lead to a loss of coherency.

Writes to BUSCTL are UNPREDICTABLE unless the ETR is in the Disabled state.

### Configurations

Some or all RW fields of this register have defined reset values.

### Attributes

BUSCTL is a 32-bit register.

### **Field descriptions**

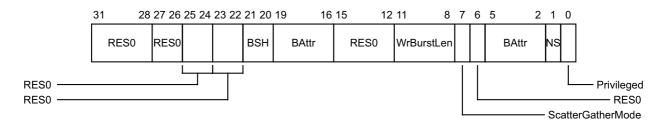

The BUSCTL bit assignments are:

### Bits [31:28]

Reserved, RESO.

### Bits [27:26]

Reserved, RESO.

## Bits [25:24]

Reserved, RESO.

### Bits [23:22]

Reserved, RESO.

### BSH, bits [21:20]

Buffer shareability domain. Defines the shareability domain for Normal memory used by the buffer. The possible values of this field are:

- 0b00Not shared.0b10Outer shareable.

- 0b11 Inner shareable.

- All other values are reserved.

### BAttr, bits [19:16]

#### When DEVID.CACHETYPE == 0b0x:

BAttr is a split field that occupies BUSCTL[19:16, 5:2].

Memory type. Defines the type of memory addressed by the buffer when an IMPLEMENTATION DEFINED bus interface, such as AXI, is implemented. The definition of this field is IMPLEMENTATION DEFINED. Recommended values for an AXI bus and a fully coherent system are defined. If DEVID.CACHETYPE == 0b00 and DEVID.NOSCAT == 0b00, then this field applies also to the scatter table. When AMBA AXI3 bus, the possible values of BAttr[7:0] are:

| BAttr      | Meaning                                                          |

|------------|------------------------------------------------------------------|

| 0b00000000 | Non-cacheable, Non-bufferable.                                   |

| 0b00000001 | Non-cacheable, Bufferable.                                       |

| 0b00000010 | Normal Memory, Cacheable, No-allocate.                           |

| 0b00000011 | Normal Memory, Cacheable and Bufferable, No-allocate.            |

| 0b00000110 | Normal Memory, Write-through cacheable, Read-allocate.           |

| 0b00000111 | Normal Memory, Write-back cacheable, Read-allocate.              |

| 0b00001010 | Normal Memory, Write-through cacheable, Write-allocate.          |

| 0b00001011 | Normal Memory, Write-back cacheable, Write-allocate.             |

| 0b00001110 | Normal Memory, Write-through cacheable, Read and Write-allocate. |

| 0b00001111 | Normal Memory, Write-back cacheable, Read and Write-allocate.    |

All other values are reserved.

When AMBA AXI4 bus, if Software Read FIFO and Scatter modes are not implemented, the possible values of values of BAttr[7:0] are:

| BAttr      | Meaning                                                 |

|------------|---------------------------------------------------------|

| 0b00000000 | Device-nGnRnE.                                          |

| 0b00000001 | Device-nGnRE.                                           |

| 0b00000010 | Normal Memory, Non-cacheable, Non-bufferable.           |

| 0b00000011 | Normal Memory, Non-Cacheable, Bufferable.               |

| 0b00000110 | Normal Memory, Write-through cacheable, No-allocate.    |

| 0b00000111 | Normal Memory, Write-back cacheable, No-allocate.       |

| 0b00001110 | Normal Memory, Write-through cacheable, Write-allocate. |

| 0b00001111 | Normal Memory, Write-back cacheable, Write-allocate.    |

All other values are reserved.

When AMBA AXI4 bus, if Software Read FIFO or Scatter modes are implemented, the possible values of values of BAttr[7:0] are:

| BAttr      | Meaning                                                          |

|------------|------------------------------------------------------------------|

| 0b00000000 | Device-nGnRnE.                                                   |

| 0b00010001 | Device-nGnRE.                                                    |

| 0b00100010 | Normal Memory, Non-cacheable, Non-bufferable.                    |

| 0b00110011 | Normal Memory, Non-Cacheable, Bufferable.                        |

| 0b10100110 | Normal Memory, Write-through cacheable, No-allocate.             |

| 0b10101110 | Normal Memory, Write-through cacheable, Write-allocate.          |

| 0b10110111 | Normal Memory, Write-back cacheable, No-allocate.                |

| 0b10111111 | Normal Memory, Write-back cacheable, Write-allocate.             |

| 0b11100110 | Normal Memory, Write-through cacheable, Read-allocate.           |

| 0b11101110 | Normal Memory, Write-through cacheable, Read and Write-allocate. |

| 0b11110111 | Normal Memory, Write-back cacheable, Read-allocate.              |

| Øb11111111 | Normal Memory, Write-back cacheable, Read and Write-allocate.    |

All other values are reserved.

When Fully coherent system, the possible values of values of BAttr[7:0] are:

All other values are reserved.

If this field is set to a type that this implementation does not support, the behavior is as if set to a compatible type and this field reads as an UNKNOWN value.

Note \_\_\_\_\_

The recommended AXI bus values match the ARCACHE and AWCACHE encodings on AXI.

On a reset, this field resets to 0.

### When DEVID.CACHETYPE == 0b1x:

BAttr is a split field that occupies BUSCTL[19:16, 5:2].

BAttr[7:4] Specifies the outer buffer memory type. Defines the Outer attributes for memory addressed by the buffer. The possible values of BAttr[7:4] are:

| BAttr[7:4] | Meaning                                                                          |

|------------|----------------------------------------------------------------------------------|

| 0b0000     | Device memory. The device memory type is defined by BAttr[3:0].                  |

| 0b0001     | Normal memory, Outer write-through cacheable, transient Write allocate.          |

| 0b0010     | Normal memory, Outer write-through cacheable, transient Read allocate.           |

| 0b0011     | Normal memory, Outer write-through cacheable, transient Read and Write allocate. |

| BAttr[7:4] | Meaning                                                                       |  |

|------------|-------------------------------------------------------------------------------|--|

| 0b0100     | Normal memory, Outer non-cacheable.                                           |  |

| 0b0101     | Normal memory, Outer write-back cacheable, transient Write allocate.          |  |

| 0b0110     | Normal memory, Outer write-back cacheable, transient Read allocate.           |  |

| 0b0111     | Normal memory, Outer write-back cacheable, transient Read and Write allocate. |  |

| 0b1000     | Normal memory, Outer write-through cacheable, No allocate.                    |  |

| 0b1001     | Normal memory, Outer write-through cacheable, Write allocate.                 |  |

| 0b1010     | Normal memory, Outer write-through cacheable, Read allocate.                  |  |

| 0b1011     | Normal memory, Outer write-through cacheable, Read and Write allocate.        |  |

| 0b1100     | Normal memory, Outer write-back cacheable, No allocate.                       |  |

| 0b1101     | Normal memory, Outer write-back cacheable, Write allocate.                    |  |

| 0b1110     | Normal memory, Outer write-back cacheable, Read allocate.                     |  |

| 0b1111     | Normal memory, Outer write-back cacheable, Read and Write allocate.           |  |

If this field is set to a type that this implementation does not support, the behavior is as if set to a compatible type and this field reads as an UNKNOWN value.

This field resets to 0x0.

— Note —

The generic encodings match the ARMv8 MAIR register values.

BAttr[3:0] specifies the inner buffer memory type. Defines the Inner attributes for memory addressed by the buffer.

When BAttr[7:4] != 0b0000 and separate Inner attributes are not supported, the possible values of BAttr[3:0] are:

| Ob 0000 Should be see | BAttr[3:0] | Meaning        |  |

|-----------------------|------------|----------------|--|

| Should be zero.       | 0b0000     | Should be zero |  |

All other values are reserved.

When BAttr[7:4] != 0b0000 and separate Inner attributes are supported, the possible values of BAttr[3:0] are:

| BAttr[3:0] | Meaning                                                                          |

|------------|----------------------------------------------------------------------------------|

| 0b0001     | Normal memory, Inner write-through cacheable, transient Write allocate.          |

| 0b0010     | Normal memory, Inner write-through cacheable, transient Read allocate.           |

| 0b0011     | Normal memory, Inner write-through cacheable, transient Read and Write allocate. |

| 0b0100     | Normal memory, Inner non-cacheable.                                              |

| 0b0101     | Normal memory, Inner write-back cacheable, transient Write allocate.             |

| 0b0110     | Normal memory, Inner write-back cacheable, transient Read allocate.              |

| BAttr[3:0] | Meaning                                                                       |  |

|------------|-------------------------------------------------------------------------------|--|

| 0b0111     | Normal memory, Inner write-back cacheable, transient Read and Write allocate. |  |

| 0b1000     | Normal memory, Inner write-through cacheable, No allocate.                    |  |

| 0b1001     | Normal memory, Inner write-through cacheable, Write allocate.                 |  |

| 0b1010     | Normal memory, Inner write-through cacheable, Read allocate.                  |  |

| 0b1011     | Normal memory, Inner write-through cacheable, Read and Write allocate.        |  |

| 0b1100     | Normal memory, Inner write-back cacheable, No allocate.                       |  |

| 0b1101     | Normal memory, Inner write-back cacheable, Write allocate.                    |  |

| 0b1110     | Normal memory, Inner write-back cacheable, Read allocate.                     |  |

| 0b1111     | Normal memory, Inner write-back cacheable, Read and Write allocate.           |  |

All other values are reserved.

When BAttr[7:4] == 0b0000, the possible values of BAttr[3:0] are:

| BAttr[3:0] | Meaning        |

|------------|----------------|

| 0b0000     | Device-nGnRnE. |

| 0b0100     | Device-nGnRE.  |

| 0b1000     | Device-nGRE.   |

| 0b1100     | Device-GRE.    |

All other values are reserved.

If this field is set to a type that this implementation does not support, the behavior is as if set to a compatible type and this field reads as an UNKNOWN value.

This field resets to 0x0.

— Note —

The generic encodings match the ARMv8 MAIR register values.

#### Otherwise:

Reserved, RESO.

### Bits [15:12]

Reserved, RESO.

### WrBurstLen, bits [11:8]

Write Burst Length.

Controls the maximum number of data transfers that can occur within each burst initiated by the ETR on the bus master interface. This field is a hint to the ETR.

Arm recommends that this value is set to no more than half the write buffer depth. Arm also recommends that this value is set to enable a burst of at least one frame of trace data.

The possible values of this field are:

0b0000 One data transfer per burst. This is the default.

| 0b0001      | Maximum of two data transfers per burst.      |

|-------------|-----------------------------------------------|

| 0b0010      | Maximum of three data transfers per burst.    |

| 0b0011      | Maximum of four data transfers per burst.     |

| 0b0100      | Maximum of five data transfers per burst.     |

| 0b0101      | Maximum of six data transfers per burst.      |

| 0b0110      | Maximum of seven data transfers per burst.    |

| 0b0111      | Maximum of eight data transfers per burst.    |

| 0b1000      | Maximum of nine data transfers per burst.     |

| 0b1001      | Maximum of ten data transfers per burst.      |

| 0b1010      | Maximum of eleven data transfers per burst.   |

| 0b1011      | Maximum of twelve data transfers per burst.   |

| 0b1100      | Maximum of thirteen data transfers per burst. |

| 0b1101      | Maximum of fourteen data transfers per burst. |

| 0b1110      | Maximum of fifteen data transfers per burst.  |

| 0b1111      | No maximum.                                   |

| N           | ote                                           |

| In the Core | Sight TMC programming on incompatible burst   |

In the CoreSight TMC programming an incompatible burst length results in UNPREDICTABLE behavior. In the ETR architecture, all values must give predictable behavior as the interpretation is IMPLEMENTATION DEFINED.

# ScatterGatherMode, bit [7]

#### When DEVID.NOSCAT == 0b0:

Scatter mode. Controls whether trace memory is accessed as a single buffer in system memory or through a scatter linked-list memory. The possible values of this bit are:

- 0b0 Trace memory is a single contiguous block of system memory.

- 0b1 Trace memory is spread over multiple blocks of system memory using a linked-list.

This bit is ignored when in Disabled state.

### Otherwise:

Reserved, RESO.

### Bit [6]

Reserved, RESO.

### BAttr, bits [5:2]

### *When DEVID.CACHETYPE == 0b0x:*

BAttr is a split field that occupies BUSCTL[19:16, 5:2].

Memory type. Defines the type of memory addressed by the buffer when an IMPLEMENTATION DEFINED bus interface, such as AXI, is implemented. The definition of this field is IMPLEMENTATION DEFINED. Recommended values for an AXI bus and a fully coherent system are defined. If DEVID.CACHETYPE == 0b00 and DEVID.NOSCAT == 0b0, then this field applies also to the scatter table. When AMBA AXI3 bus, the possible values of BAttr[7:0] are:

| BAttr      | Meaning                                |

|------------|----------------------------------------|

| 0b00000000 | Non-cacheable, Non-bufferable.         |

| 0b00000001 | Non-cacheable, Bufferable.             |

| 0b00000010 | Normal Memory, Cacheable, No-allocate. |

| BAttr      | Meaning                                                          |

|------------|------------------------------------------------------------------|

| 0b00000011 | Normal Memory, Cacheable and Bufferable, No-allocate.            |

| 0b00000110 | Normal Memory, Write-through cacheable, Read-allocate.           |

| 0b00000111 | Normal Memory, Write-back cacheable, Read-allocate.              |

| 0b00001010 | Normal Memory, Write-through cacheable, Write-allocate.          |

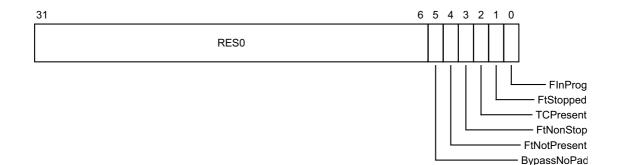

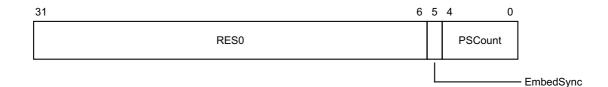

| 0b00001011 | Normal Memory, Write-back cacheable, Write-allocate.             |