This internally available PDF is enabled for shared review and commenting in Acrobat Reader. Do not distribute this outside ARM without permission from the Product Manager.

Do not add technical comments or corrections. You must raise a defect or enhancement request for this. Tech Pubs adds technical comments to the PDF after appropriate investigation.

You can add non-technical comments.

Click this for PDF commenting guidelines.

Revision: r0p0

**Technical Reference Manual**

## CoreSight SoC Technical Reference Manual

Copyright © 2011 ARM. All rights reserved.

#### **Release Information**

|                  |       |                  | Change history         |

|------------------|-------|------------------|------------------------|

| Date             | Issue | Confidentiality  | Change                 |

| 04 November 2011 | А     | Non-Confidential | First release for r0p0 |

#### **Proprietary Notice**

Words and logos marked with  ${}^{\otimes}$  or  ${}^{\sim}$  are registered trademarks or trademarks of ARM ${}^{\otimes}$  in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

# Contents CoreSight SoC Technical Reference Manual

|           | Prefa                                                                | ce                                                                                                                                                                                                                                                                                                                              |

|-----------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |                                                                      | About this book vii                                                                                                                                                                                                                                                                                                             |

|           |                                                                      | Feedbackxi                                                                                                                                                                                                                                                                                                                      |

|           |                                                                      |                                                                                                                                                                                                                                                                                                                                 |

| Chapter 1 | Introc                                                               | luction                                                                                                                                                                                                                                                                                                                         |

|           | 1.1                                                                  | About the CoreSight SoC 1-2                                                                                                                                                                                                                                                                                                     |

|           | 1.2                                                                  | CoreSight block summary 1-4                                                                                                                                                                                                                                                                                                     |

|           | 1.3                                                                  | Typical CoreSight debugging environment 1-6                                                                                                                                                                                                                                                                                     |

|           | 1.4                                                                  | Product revisions 1-7                                                                                                                                                                                                                                                                                                           |

| Chapter 2 | Funct                                                                | ional Overview                                                                                                                                                                                                                                                                                                                  |

|           | 2.1                                                                  | DAP components                                                                                                                                                                                                                                                                                                                  |

|           | 2.2                                                                  | ATB interconnect components 2-5                                                                                                                                                                                                                                                                                                 |

|           | 2.3                                                                  | Timestamp components                                                                                                                                                                                                                                                                                                            |

|           | ~ 4                                                                  |                                                                                                                                                                                                                                                                                                                                 |

|           | 2.4                                                                  | Standard CoreSight components 2-13                                                                                                                                                                                                                                                                                              |

| Chapter 3 |                                                                      |                                                                                                                                                                                                                                                                                                                                 |

| Chapter 3 |                                                                      | ammers Model                                                                                                                                                                                                                                                                                                                    |

| Chapter 3 | Progr                                                                | ammers Model<br>About this programmers model                                                                                                                                                                                                                                                                                    |

| Chapter 3 | Progr<br>3.1                                                         | cammers Model         About this programmers model         APB interconnect register summary         3-3                                                                                                                                                                                                                        |

| Chapter 3 | <b>Progr</b><br>3.1<br>3.2                                           | ammers Model<br>About this programmers model                                                                                                                                                                                                                                                                                    |

| Chapter 3 | <b>Progr</b><br>3.1<br>3.2<br>3.3                                    | rammers Model         About this programmers model         APB interconnect register summary         3-3         APB interconnect register descriptions         3-4                                                                                                                                                             |

| Chapter 3 | <b>Progr</b><br>3.1<br>3.2<br>3.3<br>3.4                             | rammers Model       3-2         About this programmers model       3-3         APB interconnect register summary       3-3         APB interconnect register descriptions       3-4         ATB funnel register summary       3-12                                                                                              |

| Chapter 3 | <b>Progr</b><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5                      | rammers Model       3-2         About this programmers model       3-3         APB interconnect register summary       3-3         APB interconnect register descriptions       3-4         ATB funnel register summary       3-12         ATB funnel register descriptions       3-13                                          |

| Chapter 3 | Progr<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                      | Pammers Model3-2About this programmers model3-3APB interconnect register summary3-3APB interconnect register descriptions3-4ATB funnel register summary3-12ATB funnel register descriptions3-13ATB replicator register summary3-37                                                                                              |

| Chapter 3 | Progr<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7               | Pammers Model3-2About this programmers model3-3APB interconnect register summary3-3APB interconnect register descriptions3-4ATB funnel register summary3-12ATB funnel register descriptions3-13ATB replicator register summary3-37ATB replicator register descriptions3-38                                                      |

| Chapter 3 | Progr<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8        | Pammers Model3-2About this programmers model3-3APB interconnect register summary3-3APB interconnect register descriptions3-4ATB funnel register summary3-12ATB funnel register descriptions3-13ATB replicator register summary3-37ATB replicator register descriptions3-38ETB register summary3-55                              |

| Chapter 3 | Progr<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9 | Pammers Model3-2About this programmers model3-3APB interconnect register summary3-3APB interconnect register descriptions3-4ATB funnel register summary3-12ATB funnel register descriptions3-13ATB replicator register summary3-37ATB replicator register descriptions3-38ETB register summary3-55ETB register descriptions3-57 |

|            | 3.13     | TPIU register descriptions                        | 3-125 |

|------------|----------|---------------------------------------------------|-------|

|            | 3.14     | DAP register summary                              | 3-163 |

|            | 3.15     | DAP register descriptions                         | 3-167 |

|            | 3.16     | Timestamp generator register summary              |       |

|            | 3.17     | Timestamp generator register description          | 3-195 |

| Chapter 4  | Debug A  | Access Port                                       |       |

|            | 4.1      | About the Debug Access Port                       | 4-2   |

|            | 4.2      | SWJ-DP                                            | 4-7   |

|            | 4.3      | JTAG-DP                                           | -     |

|            | 4.4      | SW-DP                                             |       |

|            | 4.5      | Common debug port features and registers          |       |

|            | 4.6      | Access ports                                      |       |

|            | 4.7      | AHB-AP                                            | 4-19  |

|            | 4.8      | AXI-AP                                            | 4-23  |

|            | 4.9      | АРВ-АР                                            | -     |

|            | 4.10     | JTAG-AP                                           |       |

|            | 4.11     | Auxiliary Access Port                             |       |

|            | 4.12     | Authentication requirements for Debug Access Port |       |

|            | 4.13     | Clocks, power, and resets                         | 4-35  |

| Chapter 5  | APB Inte | erconnect                                         |       |

| -          | 5.1      | Introduction                                      | 5-2   |

|            | 5.2      | APB interconnect interfaces                       | 5-3   |

|            | 5.3      | Device operation                                  | 5-4   |

| Chapter 6  | ATB Inte | erconnect Components                              |       |

| •          | 6.1      | ATB replicator                                    | 6-2   |

|            | 6.2      | ATB funnel                                        | 6-4   |

|            | 6.3      | ATB upsizer                                       | 6-12  |

|            | 6.4      | ATB downsizer                                     | 6-15  |

| Chapter 7  | DAPBU    | S Interconnect                                    |       |

| •          | 7.1      | About the DAPBUS interconnect                     |       |

|            | 7.2      | DAPBUS interconnect interfaces                    |       |

|            | 7.3      | Main modes of operation                           | 7-4   |

| Chapter 8  | Timesta  | mp Components                                     |       |

| -          | 8.1      | About the timestamp components                    | 8-2   |

|            | 8.2      | Timestamp solution                                |       |

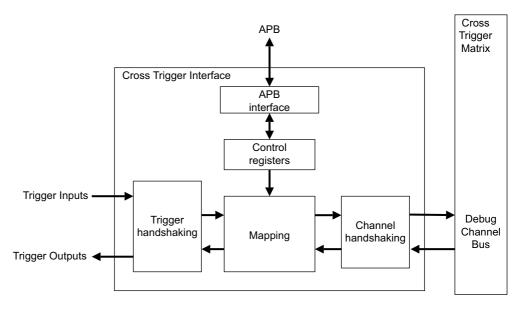

| Chapter 9  | Embedo   | led Cross Trigger                                 |       |

| •          | 9.1      | About the ECT                                     | 9-2   |

|            | 9.2      | ECT programmers model                             | 9-5   |

|            | 9.3      | ECT connectivity recommendations                  |       |

|            | 9.4      | ECT authentication requirements                   |       |

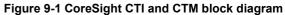

| Chapter 10 | Trace P  | ort Interface Unit                                |       |

| •          | 10.1     | About the Trace Port Interface Unit               | 10-2  |

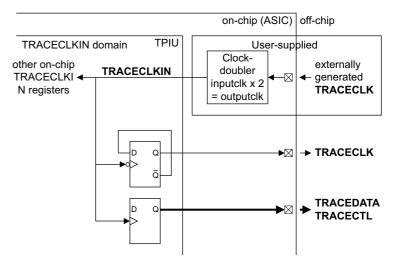

|            | 10.2     | Trace Out Port                                    | 10-3  |

|            | 10.3     | Miscellaneous connections                         |       |

|            | 10.4     | TPIU trace port sizes                             |       |

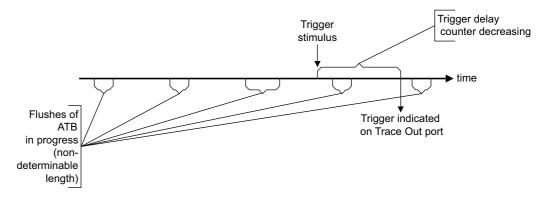

|            | 10.5     | TPIU triggers                                     |       |

|            | 10.6     | Other TPIU design considerations                  |       |

|            | 10.7     | Authentication requirements for TPIUs             |       |

|            | 10.8     | TPIU pattern generator                            |       |

|            | 10.9     | TPIU formatter and FIFO                           |       |

|            | 10.10    | Configuration options                             | 10-15 |

|            |          |                                                   |       |

|            | 10.11    | Example configuration scenarios 10-16                 |

|------------|----------|-------------------------------------------------------|

| Chapter 11 | Embedo   | led Trace Buffer                                      |

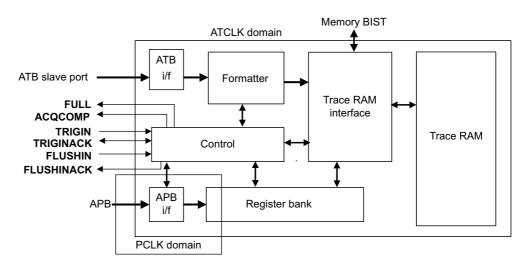

| -          | 11.1     | About the ETB 11-2                                    |

|            | 11.2     | ETB clocks, resets, and synchronization 11-5          |

|            | 11.3     | ETB trace capture and formatting 11-6                 |

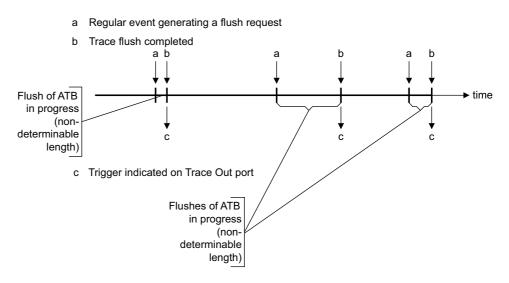

|            | 11.4     | Flush assertion 11-8                                  |

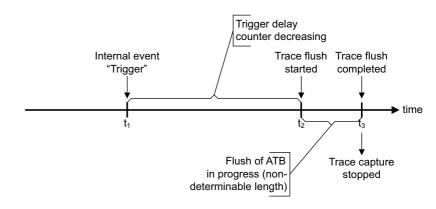

|            | 11.5     | Triggers 11-9                                         |

|            | 11.6     | Write address generation for trace data storage 11-10 |

|            | 11.7     | Trace data storage 11-11                              |

|            | 11.8     | APB configuration and RAM access 11-12                |

|            | 11.9     | Trace RAM 11-13                                       |

|            | 11.10    | Authentication requirements for CoreSight ETBs 11-14  |

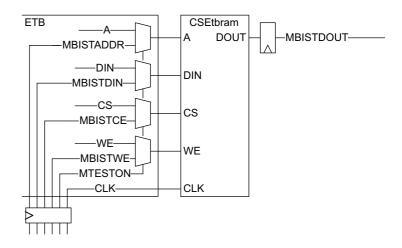

|            | 11.11    | ETB RAM support 11-15                                 |

| Appendix A | Signal D | Descriptions                                          |

|            | A.1      | Clock domains                                         |

|            | A.2      | AXI slave interface signals A-3                       |

|            | A.3      | AXI master interface signals A-7                      |

|            | A.4      | CoreSight DAP signals A-10                            |

|            | A.5      | CoreSight ECT signals A-15                            |

|            | A.6      | CoreSight TPIU signals A-18                           |

|            | A.7      | CoreSight ETB signals A-20                            |

|            | A.8      | CoreSight timestamp component signals A-22            |

|            | A.9      | APB IC signals A-24                                   |

|            | A.10     | Debug interconnect signals A-25                       |

|            |          |                                                       |

Appendix B Revisions

# Preface

This preface introduces the *CoreSight*<sup>™</sup> SoC Technical Reference Manual. It contains the following sections:

- About this book on page vii

- *Feedback* on page xi.

# About this book

This is the Technical Reference Manual (TRM) for the CoreSight components.

| Product revision status |                               |                                                                                                                                                          |  |

|-------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                         | rn                            | Identifies the major revision of the products described in this book, where:                                                                             |  |

|                         | p <i>n</i>                    | Identifies the minor revision or modification status of the product.                                                                                     |  |

| Intended audience       |                               |                                                                                                                                                          |  |

|                         | This book is                  | written for the following target audiences:                                                                                                              |  |

|                         |                               | are and software engineers who want to incorporate a CoreSight SoC into their and produce real-time instruction and data trace information from an ASIC. |  |

|                         | • Softwa                      | re engineers writing tools to use CoreSight SoC.                                                                                                         |  |

|                         | This book as                  | sumes that readers are familiar with AMBA bus design and JTAG methodology.                                                                               |  |

| Using this book         |                               |                                                                                                                                                          |  |

|                         | This book is                  | organized into the following chapters:                                                                                                                   |  |

|                         | Chapter 1 In                  | ntroduction                                                                                                                                              |  |

|                         |                               | Read this for an overview of the CoreSight components.                                                                                                   |  |

|                         | Chapter 2 Functional Overview |                                                                                                                                                          |  |

|                         |                               | Read this for a description of the major functional blocks and the operation of the CoreSight SoC.                                                       |  |

|                         | Chapter 3 P                   | rogrammers Model                                                                                                                                         |  |

|                         |                               | Read this for a description of the memory map and registers.                                                                                             |  |

|                         | Chapter 4 D                   | ebug Access Port                                                                                                                                         |  |

|                         |                               | Read this for a description of the <i>Debug Access Port</i> (DAP) components.                                                                            |  |

|                         | Chapter 5 A                   | PB Interconnect                                                                                                                                          |  |

|                         |                               | Read this for a description of the <i>Advanced Peripheral Bus</i> (APB) interconnect components.                                                         |  |

|                         | Chapter 6 A                   | TB Interconnect Components                                                                                                                               |  |

|                         |                               | Read this for a description of the <i>AMBA Trace Bus</i> (ATB) interconnect components.                                                                  |  |

|                         | Chapter 7 D                   | APBUS Interconnect                                                                                                                                       |  |

|                         |                               | Read this for a description of the <i>Debug Access Port Bus</i> (DAPBUS) interconnect components.                                                        |  |

|                         | Chapter 8 Ta                  | imestamp Components                                                                                                                                      |  |

|                         |                               | Read this for a description of the timestamp components.                                                                                                 |  |

|                         | Chapter 9 E                   | mbedded Cross Trigger                                                                                                                                    |  |

|                         |                               | Read this for a description of the <i>Embedded Cross Trigger</i> (ECT) components.                                                                       |  |

#### Chapter 10 Trace Port Interface Unit

Read this for a description of the Trace Port Interface Unit (TPIU) components.

#### Chapter 11 Embedded Trace Buffer

Read this for a description of the Embedded Trace Buffer (ETB) components.

#### **Appendix A Signal Descriptions**

Read this for a description of the CoreSight SoC component signals.

#### Appendix B Revisions

Read this for a description of the technical changes between released issues of this book.

#### Glossary

The *ARM Glossary* is a list of terms used in ARM documentation, together with definitions for those terms. The *ARM Glossary* does not contain terms that are industry standard unless the ARM meaning differs from the generally accepted meaning.

See ARM Glossary, http://infocenter.arm.com/help/topic/com.arm.doc.aeg0014-/index.html.

### Conventions

Conventions that this book can use are described in:

- Typographical

- *Timing diagrams* on page ix

- Signals on page ix.

#### Typographical

The typographical conventions are:

| italic            | Highlights important notes, introduces special terminology, denotes internal cross-references, and citations.                              |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bold              | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.      |

| monospace         | Denotes text that you can enter at the keyboard, such as commands, file<br>and program names, and source code.                             |

| <u>mono</u> space | Denotes a permitted abbreviation for a command or option. You can enter<br>the underlined text instead of the full command or option name. |

| monospace italic  | Denotes arguments to monospace text where the argument is to be replaced by a specific value.                                              |

| monospace bold    | Denotes language keywords when used outside example code.                                                                                  |

| < and >           | Enclose replaceable terms for assembler syntax where they appear in code or code fragments. For example:                                   |

|                   | MRC p15, 0 <rd>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></rd>                                                                      |

#### **Timing diagrams**

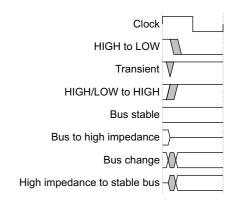

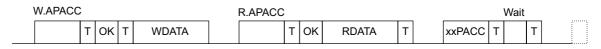

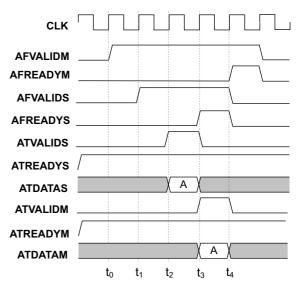

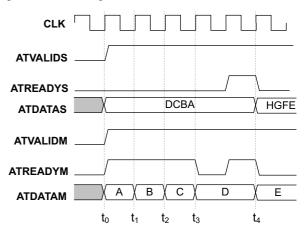

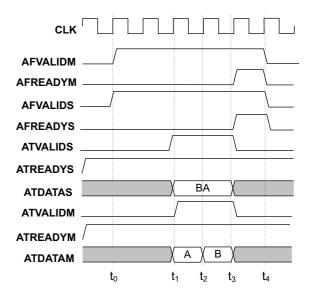

The figure named *Key to timing diagram conventions* explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

#### Key to timing diagram conventions

#### Signals

The signal conventions are:

| Signal level | The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means: |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------|--|--|

|              | • HIGH for active-HIGH signals                                                                              |  |  |

|              | • LOW for active-LOW signals.                                                                               |  |  |

| Lower-case n | At the start or end of a signal name denotes an active-LOW signal.                                          |  |  |

#### Additional reading

This section lists publications by ARM and by third parties.

See Infocenter, http://infocenter.arm.com, for access to ARM documentation.

#### **ARM** publications

This document contains information that is specific to the CoreSight components. See the following documents for other relevant information:

- CoreSight SoC Implementation Guide (ARM DII 0267)

- CoreSight SoC User Guide (ARM DSU 0563)

- CoreSight Technology System Design Guide (ARM DGI 0012)

- CoreSight Architecture Specification (ARM IHI 0029)

- CoreLink TrustZone Address Space Controller TZC-380 Technical Reference Manual (ARM DDI 0431)

- AMBA® AHB Trace Macrocell (HTM) Technical Reference Manual (ARM DDI 0328)

- Systems IP ARM11 AMBA (Rev 2.0) AHB Extensions (ARM IHI 0023)

- AMBA 3 APB Protocol (ARM IHI 0024)

- ARM Debug Interface v5 Architecture Specification (ARM IHI 0031)

- *ARM Debug Interface v5.1 Architecture Supplement* (DSA09-PRDC-008772).

#### Other publications

This section lists relevant documents published by third parties:

• IEEE 1149.1-2001 IEEE Standard Test Access Port and Boundary Scan Architecture (JTAG).

## Feedback

ARM welcomes feedback on this product and its documentation.

#### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

#### Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- the title

- the number, ARM DDI 0480A

- the page numbers to which your comments apply

- a concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

#### — Note —

ARM tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader.

# Chapter 1 Introduction

This chapter introduces the CoreSight SoC. It contains the following sections:

- *About the CoreSight SoC* on page 1-2

- CoreSight block summary on page 1-4

- *Typical CoreSight debugging environment* on page 1-6

- *Product revisions* on page 1-7.

# 1.1 About the CoreSight SoC

The CoreSight SoC is a set of highly configurable components that you can use to:

- build CoreSight systems

- graphically configure all acceptable configuration options of components

- run the design rule checks to ensure that the configurations match the compliance limitations

- create a testbench infrastructure to run system-level tests to certify the debug and trace system operation.

### 1.1.1 CoreSight SoC features

The CoreSight SoC provide the following features for system-wide trace:

- configurability

- debug and trace visibility of whole systems

- cross triggering support between SoC subsystems

- multi-source trace in a single stream

- higher data compression than previous solutions

- standard programmers models for standard tools support

- open interfaces for third-party cores

- low pin count

- low silicon overhead.

#### 1.1.2 Structure of the CoreSight SoC

Sinks

The CoreSight SoC include the following:

#### Control and access components

Configure, access, and control the generation of trace. They do not generate trace, and process the trace data. Examples include:

- DAP. See Chapter 4 Debug Access Port.

- Sources Generate trace data for output through the *AMBA Trace Bus* (ATB). Examples include:

- *AHB Trace Macrocell* (HTM), documented separately. See *Additional reading* on page ix.

- CoreSight *Embedded Trace Macrocells* (ETMs), documented separately. See *Additional reading* on page ix.

- Instrumentation Trace Macrocell (ITM). See Additional reading on page ix.

#### Links Provide connection, triggering, and flow of trace data. Examples include:

- Synchronous 1:1 ATB bridge

- Replicator

- Trace funnel.

#### Are the end points for trace data on the SoC. Examples include:

- TPIU for output of trace data off-chip

- ETB for on-chip storage of trace data in RAM

• *Serial Wire Output* (SWO) for output of STM trace through a single pin.

Table 1-1 CoreSight block summary

# 1.2 CoreSight block summary

Table 1-1 shows the CoreSight blocks and their current versions.

|                          |                                      | 10            | ole 1-1 obleoight block summary |

|--------------------------|--------------------------------------|---------------|---------------------------------|

| Block name               | Description                          | Block version | Revision in programmers model   |

| CSCTI                    | Cross trigger interface              | r0p3          | 3                               |

| CSCTM                    | Cross trigger matrix                 | r0p3          | -                               |

| CSETB                    | Embedded trace buffer                | r0p3          | 3                               |

| CXATBREPLICATOR          | ATB replicator                       | r1p0          | 2                               |

| CXAUTHREPLICATOR         | Authentication replicator            | r0p0          | -                               |

| CXEVENTASYNCBRIDGE       | Event asynchronous bridge            | r0p0          | -                               |

| CXTSREPLICATOR           | Timestamp replicator                 | r0p0          | -                               |

| CXATBFUNNEL              | Trace funnel                         | r2p0          | 2                               |

| CSTPIU                   | Trace port interface unit            | r0p4          | 4                               |

| CXATBUPSIZER             | ATB upsizer                          | r0p0          | -                               |

| CXATBDOWNSIZER           | ATB downsizer                        | r0p0          | -                               |

| CXATBASYNCBRIDGE         | ATB asynchronous bridge              | r0p0          | -                               |

| CXATBSYNCBRIDGE          | ATB synchronous bridge               | r0p0          | -                               |

| CXAPBASYNCBRIDGE         | APB asynchronous bridge              | r0p0          | -                               |

| CXAPBSYNCBRIDGE          | APB synchronous bridge               | r0p0          | -                               |

| CXAUTHASYNCBRIDGE        | Authentication asynchronous bridge   | r0p0          | -                               |

| CXAUTHSYNCBRIDGE         | Authentication synchronous bridge    | r0p0          | -                               |

| CXTSGEN                  | Master timestamp generator           | r0p0          | -                               |

| CXTSE                    | Timestamp encoder                    | r0p0          | -                               |

| CXNTSREPLICATOR          | Narrow timestamp replicator          | r0p0          | -                               |

| CXNTSASYNCBRIDGE         | Narrow timestamp asynchronous bridge | r0p0          | -                               |

| CXNTSAYNCBRIDGE          | Narrow timestamp synchronous bridge  | r0p0          | -                               |

| CXTSD                    | Timestamp decoder                    | r0p0          | -                               |

| Debug Access Port blocks |                                      |               |                                 |

| DAPAHBAP                 | AHB access port                      | r0p5          | 5                               |

| DAPAPBAP                 | APB access port                      | r0p3          | 3                               |

| APBIC                    | APB interconnect                     | r0p0          | -                               |

| DAPJTAGAP                | JTAG access port                     | r0p2          | 2                               |

| CXDAPASYNCBRIDGE         | DAPBUS asynchronous bridge           | r0p0          | -                               |

| CXDAPSYNCBRIDGE          | DAPBUS synchronous bridge            | r0p0          | -                               |

|                          |                                      |               |                                 |

#### Table 1-1 CoreSight block summary (continued)

| Block name | Description                                                                          | Block version     | Revision in programmers model |

|------------|--------------------------------------------------------------------------------------|-------------------|-------------------------------|

| DAPAXIAP   | AXI access port                                                                      | r0p0              | 0                             |

| DAPBUSIC   | DAPBUS interconnect                                                                  | r0p0              | -                             |

| DAPSWJDP   | <ul><li>Serial wire and JTAG debug port:</li><li>DAPSWDP</li><li>DAPJTAGDP</li></ul> | -<br>r1p1<br>r0p5 | -<br>4<br>5                   |

#### — Note —

See the *CoreSight SoC Release Notes* for a list of the blocks and their versions supplied with the version of the product you have received.

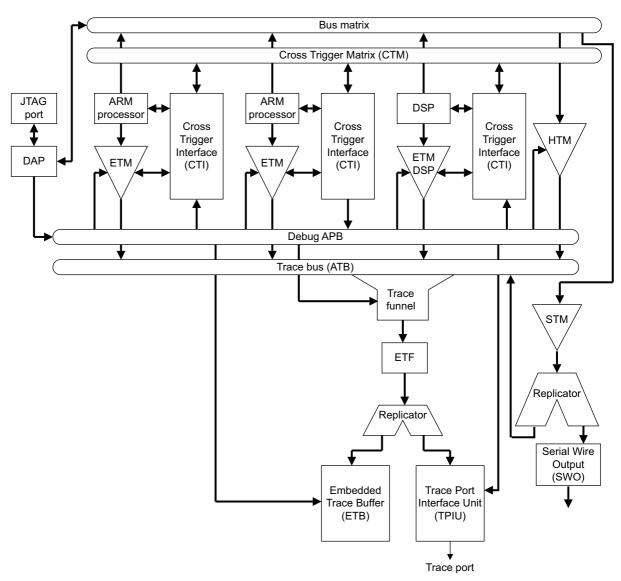

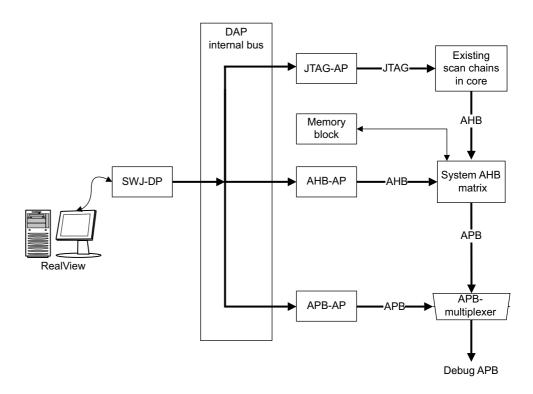

# 1.3 Typical CoreSight debugging environment

Figure 1-1 shows an example CoreSight components in one possible debugging environment.

Figure 1-1 CoreSight debugging environment

# 1.4 Product revisions

This section describes the differences in functionality between product revisions:

r0p0 First release.

# Chapter 2 Functional Overview

This chapter describes the various components of the CoreSight SoC and its features. It contains the following sections:

- *DAP components* on page 2-2

- *ATB interconnect components* on page 2-5

- *Timestamp components* on page 2-9

- *Standard CoreSight components* on page 2-13.

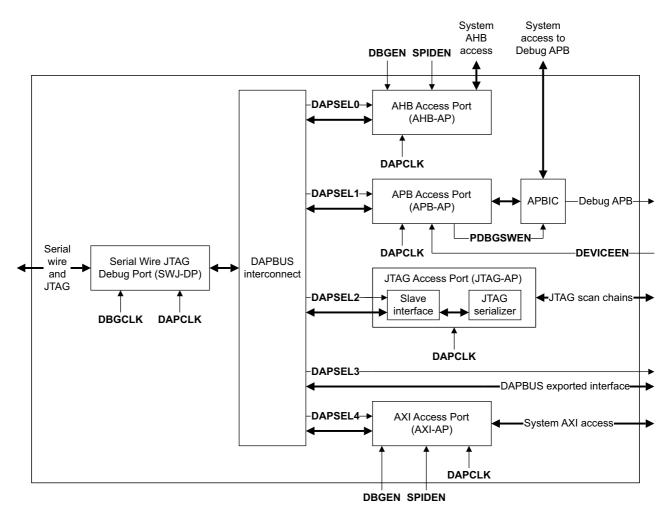

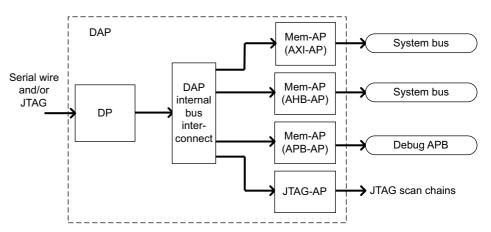

## 2.1 DAP components

The DAP components include:

- Serial Wire or JTAG (SWJ) debug port

- DAPBUS interconnect

- Advanced eXtensible Interface Access Port (AXI-AP) on page 2-3

- Advanced Peripheral Bus Access Port (APB-AP) on page 2-3

- Advanced High-performance Bus Access Port (AHB-AP) on page 2-4

- *JTAG-AP* on page 2-4.

For more information about the configurable parameters and its options of the DAP components, see the *CoreSight SoC User Guide*.

#### 2.1.1 Serial Wire or JTAG (SWJ) debug port

The SWJ debug port connects to either a Serial Wire Debug or JTAG probe to a target.

See Chapter 4 Debug Access Port for more information.

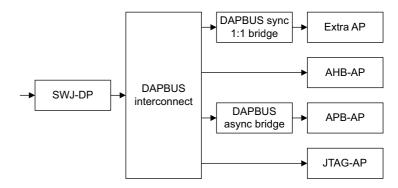

#### 2.1.2 DAPBUS interconnect

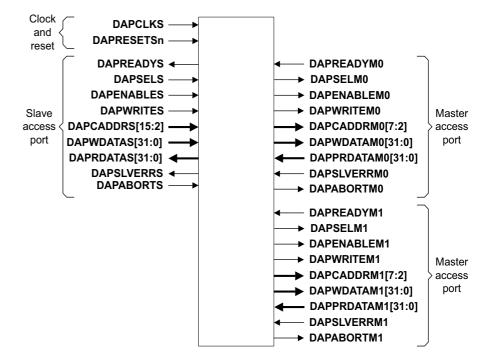

The DAPBUS interconnect connects a debug port with a configurable number of access ports.

The DAPBUS interconnect operates in a single clock domain. You can connect other components that are not synchronous to the DAPBUS interconnect by using asynchronous bridges.

You can configure the number of master ports, from 1-32.

Figure 2-1 shows the external connections to the DAPBUS interconnect.

Figure 2-1 DAPBUS interconnect

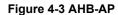

#### 2.1.3 Advanced eXtensible Interface Access Port (AXI-AP)

The AXI-AP connects a DAP to an AXI memory system. You can also connect to other memory systems using a suitable bridge component.

You can configure the AXI-AP during implementation, with the following features:

- AXI\_ADDR\_WIDTH, 32 or 64-bit

- AXI\_DATA\_WIDTH, 32 or 64-bit.

See Chapter 4 Debug Access Port for more information.

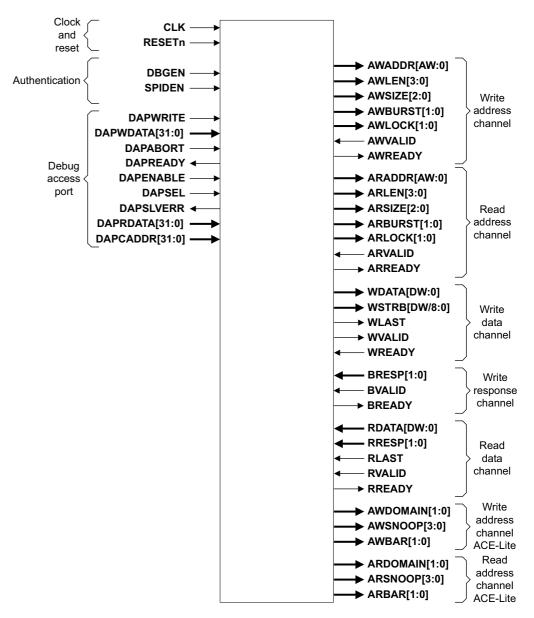

Figure 2-2 shows the external connections to the AXI-AP.

#### Figure 2-2 AXI-AP

#### 2.1.4 Advanced Peripheral Bus Access Port (APB-AP)

The APB-AP connects a DAP to an APB system bus. The APB-AP has no configurable features.

See Chapter 4 Debug Access Port for more information.

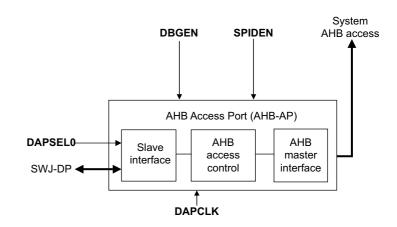

#### 2.1.5 Advanced High-performance Bus Access Port (AHB-AP)

The AHP-AP connects a DAP to an AHB system bus. The AHB-AP has no configurable features.

See Chapter 4 Debug Access Port for more information.

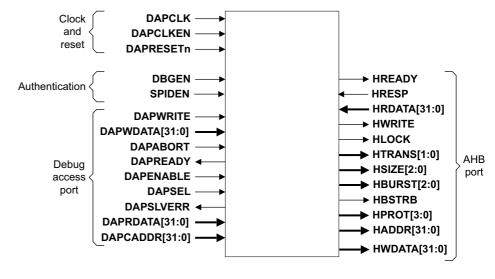

Figure 2-3 shows the external connections to the AHB-AP.

Figure 2-3 AHB-AP

#### 2.1.6 JTAG-AP

The JTAG-AP provides JTAG access to on-chip components. See Chapter 4 *Debug Access Port* for more information.

### 2.2 ATB interconnect components

The interconnect components include:

- APB Interconnect (APBIC) with ROM table

- ATB replicator

- *ATB funnel* on page 2-6

- ATB upsizer on page 2-7

- *ATB downsizer* on page 2-7.

For information about the configurable parameters and its options of the Interconnect components, see the *CoreSight SoC User Guide*.

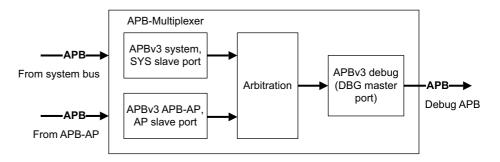

#### 2.2.1 APB Interconnect (APBIC) with ROM table

The APBIC with ROM table connects multiple APB masters to multiple slaves. The APBIC implements a ROM table that contains information about the components in a CoreSight system.

The APBIC operates in a single clock domain. You can connect other components that are not synchronous by using asynchronous bridges.

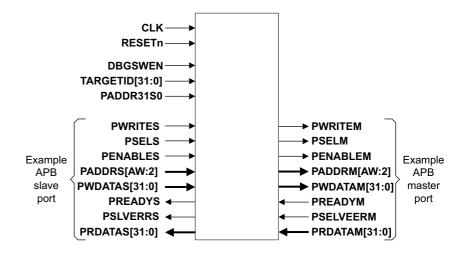

Figure 2-4 shows the external connections to the APBIC.

#### Figure 2-4 APB interconnect with ROM table

For informations about the user programmable registers for the APBIC, see Chapter 3 *Programmers Model*.

#### **Cascading APBICs**

Systems that require more than the maximum configurable number of slaves can use a cascading approach. You can connect two or more APBICs to implement a hierarchy of APB peripherals.

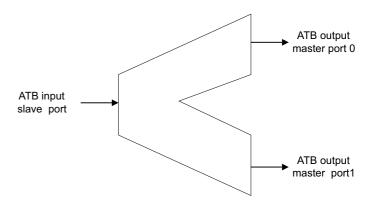

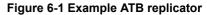

#### 2.2.2 ATB replicator

The ATB replicator propagates data from a single master to two slaves.

Figure 2-5 on page 2-6 shows the external connections to the ATB replicator.

Figure 2-5 ATB replicator

#### 2.2.3 ATB funnel

The ATB funnel merges the trace from multiple ATB busses and sends the data to a single ATB bus.

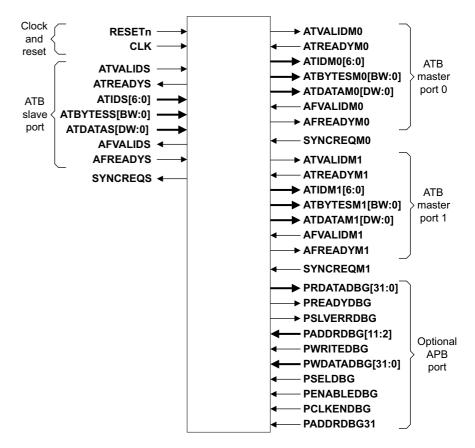

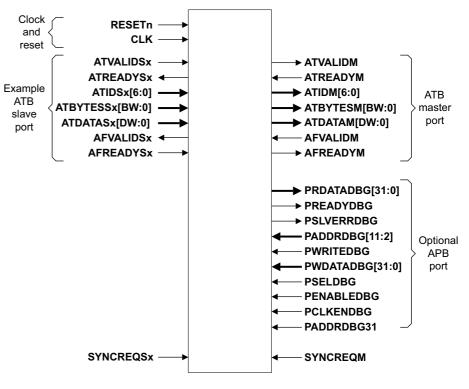

Figure 2-6 on page 2-7 shows the external connections to the ATB funnel.

Figure 2-6 ATB funnel

#### 2.2.4 ATB upsizer

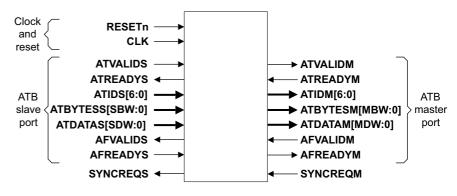

The ATB upsizer converts the trace data on a narrow width ATB bus onto a higher width bus. Figure 2-7 shows the external connections to the ATB upsizer.

Figure 2-7 ATB upsizer

#### 2.2.5 ATB downsizer

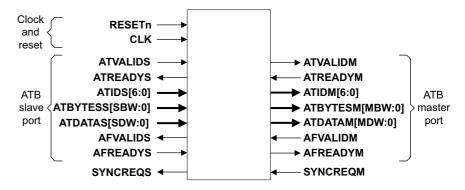

The ATB downsizer converts the trace data on a wide width ATB bus onto a narrower width bus.

Figure 2-8 on page 2-8 shows the external connections to the ATB downsizer.

Figure 2-8 ATB downsizer

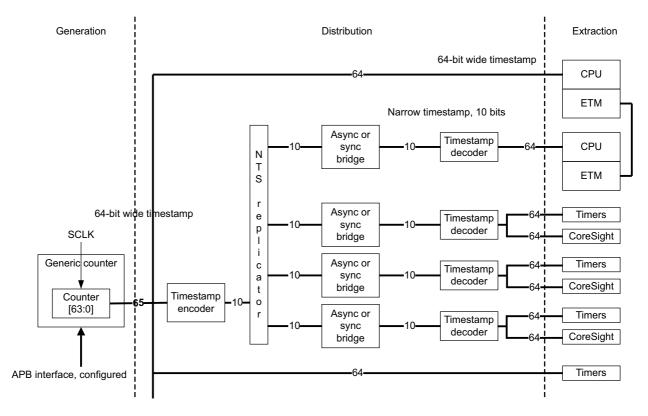

## 2.3 Timestamp components

The timestamp components generate and distribute a consistent timestamp value for multiple processors and other IPs within a SoC.

See Chapter 8 Timestamp Components for more information.

For information about the configurable parameters of the timestamp components, see the *CoreSight SoC User Guide*.

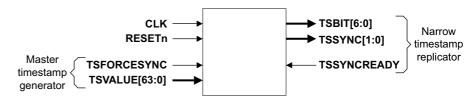

#### 2.3.1 Master timestamp generator

The master timestamp generator generates a timestamp value that provides a consistent view of time for multiple processors and other IPs in a SoC.

The master timestamp generator has no configurable features.

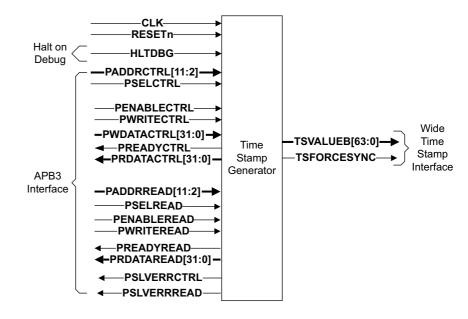

Figure 2-9 shows the master timestamp generator block diagram.

Figure 2-9 Master timestamp generator

#### **Timestamp generator**

This component has a fixed configuration. See Chapter 8 *Timestamp Components* and Chapter 3 *Programmers Model* for more information about timestamp generator and its register description.

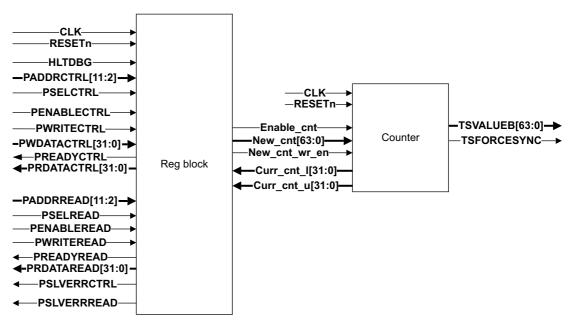

Figure 2-10 on page 2-10 shows the external connections to the timestamp generator.

#### Figure 2-10 Timestamp generator

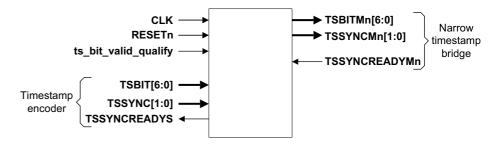

#### 2.3.2 Timestamp encoder

The timestamp encoder converts the 64-bit timestamp value from the master timestamp generator to a 7-bit encoded value. It also encodes and sends the timestamp value over a 2-bit synchronization channel.

The timestamp encoder has no configurable features.

Figure 2-11 shows the external connections to the timestamp encoder.

Figure 2-11 Timestamp encoder

#### 2.3.3 Narrow timestamp replicator

The narrow timestamp replicator distributes the encoded timestamp and synchronization data to multiple slave bridges. You can configure the number of slave bridges to be connected to the narrow timestamp replicator.

Figure 2-12 on page 2-11 shows the external connections to the narrow timestamp replicator.

#### 2.3.4 Narrow timestamp asynchronous bridge

The narrow timestamp asynchronous bridge enables the transfer of timestamp information across different clock domains. You can configure the FIFO depth of the asynchronous bridge.

Figure 2-13 Narrow timestamp asynchronous bridge

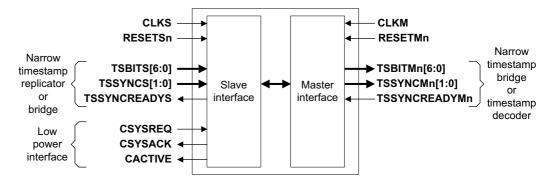

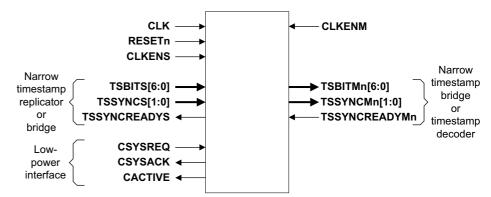

#### 2.3.5 Narrow timestamp synchronous bridge

The narrow timestamp synchronous bridge enables the transfer of timestamp information across clock domains that have individual clock enables.

You can configure the FIFO depth of the narrow timestamp synchronous bridge,

Figure 2-14 shows the external connections to the narrow timestamp synchronous bridge.

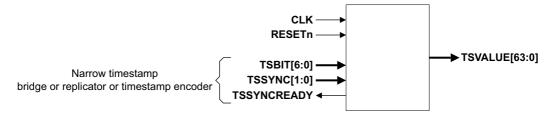

### 2.3.6 Timestamp decoder

The timestamp decoder converts the encoded timestamp and synchronization data into a 64-bit value, that the CoreSight trace component uses.

Figure 2-15 shows the external connections to the timestamp decoder.

Figure 2-15 Timestamp decoder

# 2.4 Standard CoreSight components

The CoreSight SoC includes the following standard CoreSight components.

- ECT

- TPIU

- ETB

- Cross Trigger Matrix (CTM)

- System Trace Macrocell (STM)

- Trace Memory Controller (TMC).

# Chapter 3 Programmers Model

This chapter describes the programmers model for the CoreSight components. It contains the following sections:

- About this programmers model on page 3-2

- *APB interconnect register summary* on page 3-3

- *APB interconnect register descriptions* on page 3-4

- *ATB funnel register summary* on page 3-12

- *ATB funnel register descriptions* on page 3-13

- *ATB replicator register summary* on page 3-37

- *ATB replicator register descriptions* on page 3-38

- ETB register summary on page 3-55

- *ETB register descriptions* on page 3-57

- *CTI register summary* on page 3-84

- *CTI register descriptions* on page 3-86

- *TPIU register summary* on page 3-123

- *TPIU register descriptions* on page 3-125

- DAP register summary on page 3-163

- *DAP register descriptions* on page 3-167.

- *Timestamp generator register summary* on page 3-194

- *Timestamp generator register description* on page 3-195.

## 3.1 About this programmers model

•

This section describes register information for the following components:

- APB interconnect

- ATB funnel

- ATB replicator

- ETB

- CTI

- TPIU

- DAP

- Timestamp generator.

APB interconnect, ATB funnel, and ATB replicator registers:

- The base address is not fixed, and can be different for any particular system implementation. The offset of each register from the base address is fixed.

- Do not attempt to access reserved or unused address locations. Attempting to access these locations can result in UNPREDICTABLE behavior.

- Unless otherwise stated in the accompanying text:

- do not modify undefined register bits

- ignore undefined register bits on reads

- all register bits are reset to a logic 0 by a system or power-on reset.

- Access type in Table 3-1 on page 3-3 is described as follows:

| RW     | Read and write.               |

|--------|-------------------------------|

| R/W    | Read or write.                |

| RO     | Read-only.                    |

| WO     | Write-only.                   |

| SBZ    | Should-Be-Zero.               |

| RAZ    | Read-As-Zero.                 |

| RAZ/WI | Read-As-Zero, Writes Ignored. |

## 3.2 APB interconnect register summary

Table 3-1 shows the APB interconnect registers in offset order from the base memory address 0x00000000.

| Offset      | Name                     | Туре | Reset                | Width | Description                           |

|-------------|--------------------------|------|----------------------|-------|---------------------------------------|

| 0x000-0x0FC | ROM_ENTRY_n <sup>a</sup> | RO   | _b                   | 32    | ROM Table entry n on page 3-4         |

| 0xFE0       | PERIPHID0                | RO   | _c                   | 32    | Peripheral ID0 Register on page 3-5   |

| 0xFE4       | PERIPHID1                | RO   | UNKNOWN <sup>d</sup> | 32    | Peripheral ID1 Register on page 3-5   |

| 0xFE8       | PERIPHID2                | RO   | UNKNOWN <sup>e</sup> | 32    | Peripheral ID2 Register on page 3-6   |

| 0xFEC       | PERIPHID3                | RO   | 0x00000000           | 32    | Peripheral ID3 Register on page 3-7   |

| 0xFD0       | PERIPHID4                | RO   | UNKNOWN <sup>f</sup> | 32    | Peripheral ID4 Register on page 3-7   |

| 0xFD4       | PERIPHID5                | RO   | 0x00000000           | 32    | Peripheral ID5-7 Register on page 3-8 |

| 0xFD8       | PERIPHID6                | RO   | 0x00000000           | 32    | -                                     |

| 0xFDC       | PERIPHID7                | RO   | 0x00000000           | 32    | -                                     |

| 0xFF0       | COMPID0                  | RO   | 0x0000000D           | 32    | Component ID0 Register on page 3-8    |

| 0xFF4       | COMPID1                  | RO   | 0x00000090           | 32    | Component ID1 Register on page 3-9    |

| 0xFF8       | COMPID2                  | RO   | 0x00000005           | 32    | Component ID2 Register on page 3-10   |

| 0xFFC       | COMPID3                  | RO   | 0x000000B1           | 32    | Component ID3 Register on page 3-10   |

Table 3-1 APB interconnect register summary

a. Where *n* is 0-63.

b. The reset value depends on the value of the MASTER\_INTFn\_BASE\_ADDR parameter, where n is 0-63. See the *CoreSight SoC* User Guide for more information.

c. The reset value depends on the system configuration, and identifies this as either a generic ROM table or a top-level ROM table.

d. See Table 3-4 on page 3-6 for more information on the reset value and its dependencies.

e. See Table 3-5 on page 3-6 for more information on the reset value and its dependencies.

f. See Table 3-7 on page 3-8 for more information on the reset value and its dependencies.

## 3.3 APB interconnect register descriptions

This section describes the CXAPBIC registers. Table 3-1 on page 3-3 provides cross references to individual registers.

#### 3.3.1 ROM Table entry *n*

The ROM\_ENTRY\_*n* Register characteristics are:

| Purpose           | Returns the value of ROM Entry <i>n</i> , where <i>n</i> is 0-63.                                                      |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------|--|--|

| Usage constraints | There are no usage constraints.                                                                                        |  |  |

| Configurations    | This register is available when the NUM_MASTER_INTF configuration option set to a value greater than $n$ .             |  |  |

|                   | For example:                                                                                                           |  |  |

|                   | • the ROM_ENTRY_1 Register is available when the NUM_MASTER_INTF configuration option is set to a value greater than 1 |  |  |

|                   | • the ROM_ENTRY_62 Register is available when the                                                                      |  |  |

NUM\_MASTER\_INTF configuration option is set to a value greater than 62.

Attributes See the register summary in Table 3-1 on page 3-3.

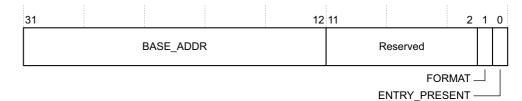

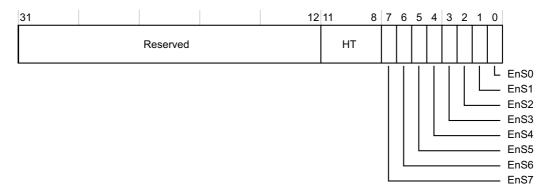

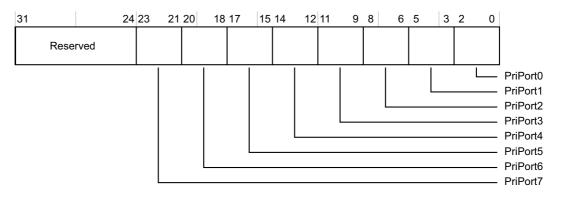

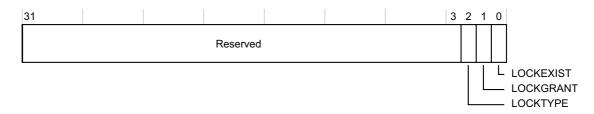

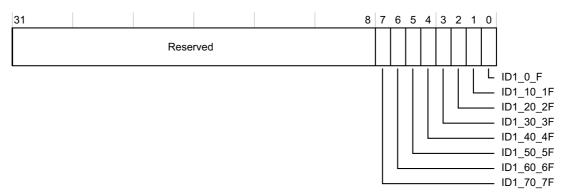

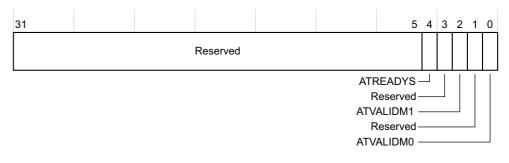

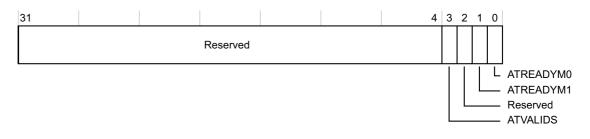

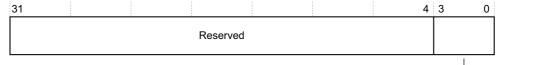

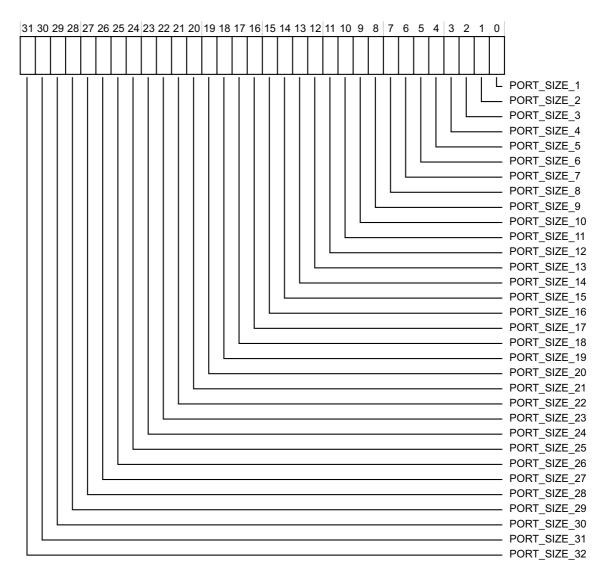

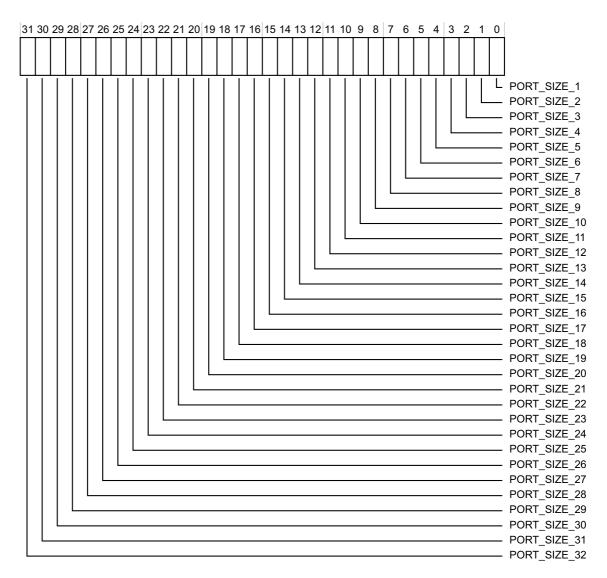

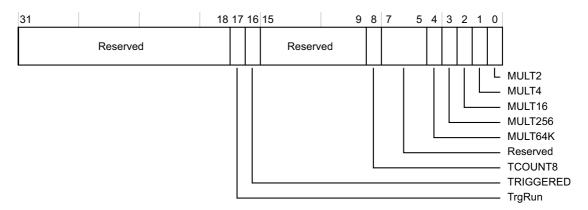

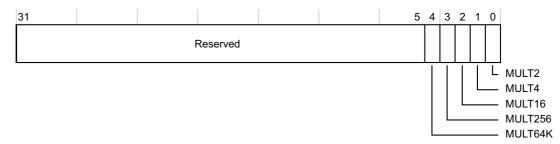

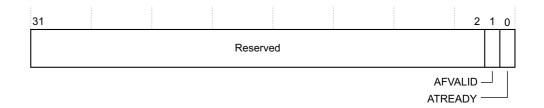

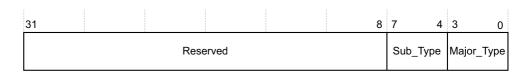

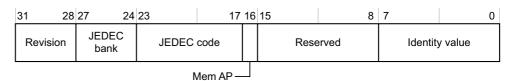

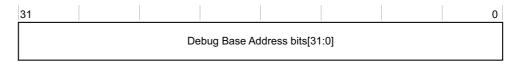

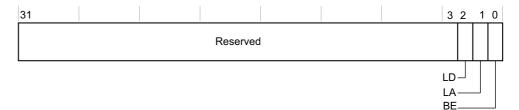

Figure 3-1 shows the ROM\_ENTRY\_*n* bit assignments.

#### Figure 3-1 ROM\_ENTRY\_n Register bit assignments

Table 3-2 shows the ROM\_ENTRY\_*n* bit assignments.

#### Table 3-2 ROM\_ENTRY\_n Register bit assignments

| Bits    | Name          | Function                                                                                                                            |  |  |  |

|---------|---------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| [31:12] | BASE_ADDR     | Base address for master interface 0.                                                                                                |  |  |  |

| [11:2]  | Reserved      | -                                                                                                                                   |  |  |  |

| [1]     | FORMAT        | Indicates that the ROM table entry is of 32-bit format.1ROM table entry is of 32-bit format.                                        |  |  |  |

| [0]     | ENTRY_PRESENT | Indicates whether there is a valid ROM entry at this location. This must be one for valid ROM table entries. The possible value is: |  |  |  |

|         |               | <b>0</b> Valid ROM table entry not present at this address location.                                                                |  |  |  |

|         |               | 1 Valid ROM table entry present at this address location.                                                                           |  |  |  |

#### 3.3.2 Peripheral ID0 Register

The Peripheral Identification Register 0, PERIPHID0, characteristics are:

| Purpose                                                                 | Part of the set of Peripheral Identification registers. Contains part of the designer-specific part number. This reflects either TARGETID[23:16] from the DAP, or a sub-system identifier. |  |  |  |  |  |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Usage constraints                                                       | There are no usage constraints.                                                                                                                                                            |  |  |  |  |  |

| <b>Configurations</b> This register is available in all configurations. |                                                                                                                                                                                            |  |  |  |  |  |

| Attributes                                                              | See the register summary in Table 3-1 on page 3-3.                                                                                                                                         |  |  |  |  |  |

| Figure 3-2 shows the PERIPHID0 Register bit assignments.                |                                                                                                                                                                                            |  |  |  |  |  |

| 31 |  |          |  | 8 | 7 |       | 0 |

|----|--|----------|--|---|---|-------|---|

|    |  | Reserved |  |   | P | ART_0 |   |

#### Figure 3-2 PERIPHID0 Register bit assignments

Table 3-3 shows the PERIPHID0 Register bit assignments.

#### Table 3-3 PERIPHID0 Register bit assignments

| Bits   | Name     | Function                                                                                     |

|--------|----------|----------------------------------------------------------------------------------------------|

| [31:8] | Reserved | -                                                                                            |

| [7:0]  | PART_0   | Bits [7:0] of the components part number. This is selected by the designer of the component. |

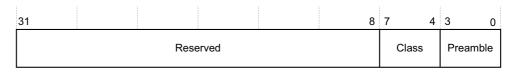

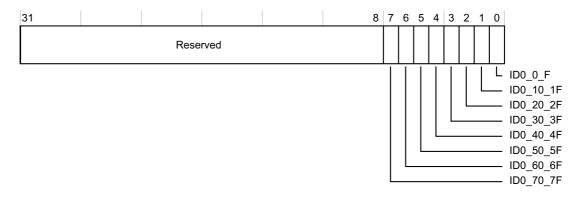

#### 3.3.3 Peripheral ID1 Register

The PERIPHID1 Register characteristics are:

| Purpose | Part of the set of Peripheral Identification registers. Contains part of the |

|---------|------------------------------------------------------------------------------|

|         | designer-specific part number and part of the designer identity.             |

Usage constraints There are no usage constraints.

**Configurations** This register is available in all configurations.

Attributes See the register summary in Table 3-1 on page 3-3.

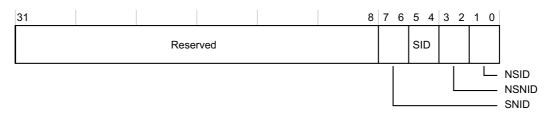

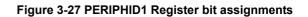

Figure 3-3 shows the PERIPHID1 Register bit assignments.

| 31       |  |  |  |  | 8 | 7 | 4    | 3 0    |  |

|----------|--|--|--|--|---|---|------|--------|--|

| Reserved |  |  |  |  |   | D | ES_0 | PART_1 |  |

#### Figure 3-3 PERIPHID1 Register bit assignments

Table 3-4 shows the PERIPHID1 Register bit assignments.

#### Table 3-4 PERIPHID1 Register bit assignments

| Bits   | Name     | Function                                                                                                                                                                                                           |  |  |  |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| [31:8] | Reserved | -                                                                                                                                                                                                                  |  |  |  |

| [7:4]  | DES_0    | Bits [3:0] of the JEDEC identity code indicate the designer of the component along with the continuation code. This reflects either TARGETID[4:1] from the DAP, or a sub-system identifier. The possible value is: |  |  |  |

|        |          | b1011 Lowest 4 bits of the JEP106 Identity code. The default value is ARM Ltd.                                                                                                                                     |  |  |  |

| [3:0]  | PART_1   | Bits [11:8] of the components part number. This is selected by the designer of the component. This reflects either TARGETID[4:1] from the DAP, or a sub-system identifier.                                         |  |  |  |

### 3.3.4 Peripheral ID2 Register

The PERIPHID2 Register characteristics are:

| Purpose             | Part of the set of Peripheral Identification registers. Contains part of the designer identity and the product revision. |

|---------------------|--------------------------------------------------------------------------------------------------------------------------|

| Usage constraints   | There are no usage constraints.                                                                                          |

| Configurations      | This register is available in all configurations.                                                                        |

| Attributes          | See the register summary in Table 3-1 on page 3-3.                                                                       |

| Figure 3.4 shows th | e PERIPHID? Register hit assignments                                                                                     |

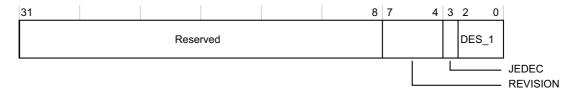

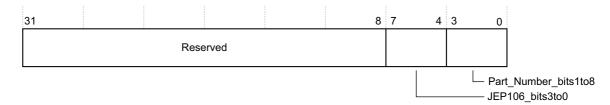

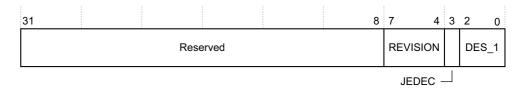

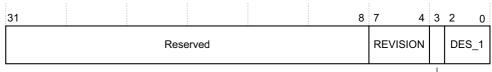

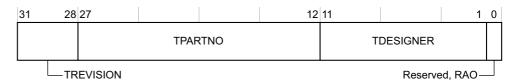

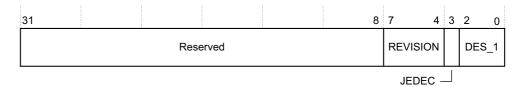

Figure 3-4 shows the PERIPHID2 Register bit assignments.

### Figure 3-4 PERIPHID2 Register bit assignments

Table 3-5 shows the PERIPHID2 Register bit assignments.

### Table 3-5 PERIPHID2 Register bit assignments

| Bits   | Name     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:8] | Reserved | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| [7:4]  | REVISION | The Revision field is an incremental value starting at 0x0 for the first design of this component.<br>This only increases by one for both major and minor revisions and is used as a look-up to establish<br>the exact major or minor revision. If the IS_TOP_LEVEL_APBIC parameter is set to true, the value of<br>this field is set by the value on the <b>targetid</b> [31:28] port. Otherwise, the value of this field is set by<br>the value of the REVISION parameter. |

| [3]    | JEDEC    | Always set. Indicates that a JEDEC assigned value is used. The possible value is:1The designer ID is specified by JEDEC, http://www.jedec.org.                                                                                                                                                                                                                                                                                                                               |

| [2:0]  | DES_1    | Bits [6:4] of the JEDEC identity code indicate the designer of the component along with the continuation code. This reflects either TARGETID[4:1] from the DAP, or a sub-system identifier.                                                                                                                                                                                                                                                                                  |

### 3.3.5 Peripheral ID3 Register

The PERIPHID3 Register characteristics are:

| Purpose           | Part of the set of Peripheral Identification registers. Contains the RevAnd and Customer Modified fields. |  |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Usage constraints | There are no usage constraints.                                                                           |  |  |  |  |  |

| Configurations    | This register is available in all configurations.                                                         |  |  |  |  |  |

| Attributes        | See the register summary in Table 3-1 on page 3-3.                                                        |  |  |  |  |  |

| E: 0.5.1 d        |                                                                                                           |  |  |  |  |  |

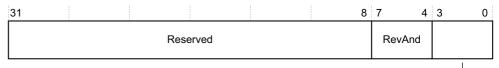

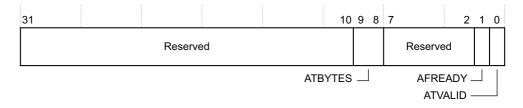

Figure 3-5 shows the PERIPHID3 Register bit assignments.

| 31 |  |          |  | 8 | 7      | 4 | 3    | 0 |

|----|--|----------|--|---|--------|---|------|---|

|    |  | Reserved |  |   | REVAND | ) | CMOD |   |

#### Figure 3-5 PERIPHID3 Register bit assignments

Table 3-6 shows the PERIPHID3 Register bit assignments.

#### Table 3-6 PERIPHID3 Register bit assignments

| Bits   | Name     | Function                                                                                                                                                                                                                                                           |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:8] | Reserved | -                                                                                                                                                                                                                                                                  |

| [7:4]  | REVAND   | This field indicates minor errata fixes specific to this design, for example, metal fixes afterimplementation. In most cases this field is zero. The possible value is:0Indicates that there have been no metal fixes to this component.                           |

| [3:0]  | CMOD     | <ul><li>Where the component is reusable IP, this value indicates whether the customer has modified the behavior of the component. In most cases this field is zero. The possible value is:</li><li>Indicates that there have been no modifications made.</li></ul> |

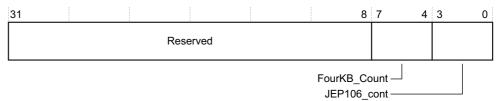

### 3.3.6 Peripheral ID4 Register

The PERIPHID4 Register characteristics are:

| Purpose           | Part of the set of Peripheral Identification registers. Contains part of the designer identity and the memory footprint indicator. |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Usage constraints | There are no usage constraints.                                                                                                    |

| Configurations    | This register is available in all configurations.                                                                                  |

| Attributes        | See the register summary in Table 3-1 on page 3-3.                                                                                 |

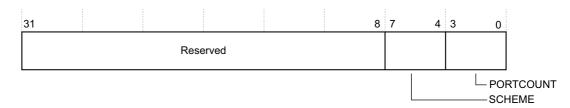

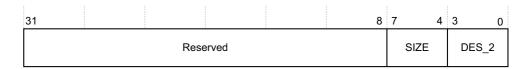

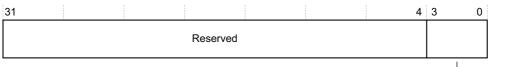

Figure 3-6 shows the PERIPHID4 Register bit assignments.

| 31 |  |          |  | 8 | 7    | 4 | 3 0   |

|----|--|----------|--|---|------|---|-------|

|    |  | Reserved |  |   | SIZE |   | DES_2 |

#### Figure 3-6 PERIPHID4 Register bit assignments

Table 3-7 shows the PERIPHID4 Register bit assignments.

#### Table 3-7 PERIPHID4 Register bit assignments

| Bits   | Name     | Function                                                                                                                                                                                                                          |  |

|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| [31:8] | Reserved | -                                                                                                                                                                                                                                 |  |

| [7:4]  | SIZE     | This is a 4-bit value that indicates the total contiguous size of the memory window used by thiscomponent in powers of 2 from the standard 4KB. The possible value is:b0000Indicates that the device only occupies 4KB of memory. |  |

| [3:0]  | DES_2    | JEDEC continuation code indicate the designer of the component along with the identity code.<br>This reflects either TARGETID[11:8] from the DAP, or a sub-system specific value.                                                 |  |

### 3.3.7 Peripheral ID5-7 Register

The PERIPHID5-7 Register characteristics are:

| Purpose           | Reserved.                                            |

|-------------------|------------------------------------------------------|

| Usage constraints | There are no usage constraints.                      |

| Configurations    | These registers are available in all configurations. |

| A • <b>1</b>      |                                                      |

Attributes See the register summary in Table 3-1 on page 3-3.

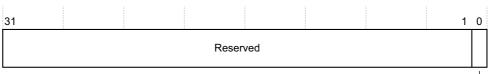

Figure 3-7 shows the PERIPHID5-7 Register bit assignments.

| 3 | 31 |  |      |       |  | 0 |

|---|----|--|------|-------|--|---|

|   |    |  | Rese | erved |  |   |

#### Figure 3-7 PERIPHID5-7 Register bit assignments

Table 3-8 shows the PERIPHID5-7 Register bit assignments.

#### Table 3-8 PERIPHID5-7 Register bit assignments

| Bits   | Name     | Function |

|--------|----------|----------|

| [31:0] | Reserved | -        |

#### 3.3.8 Component ID0 Register

The COMPID0 Register characteristics are:

- **Purpose** A Component Identification Register that indicates the identification registers are present.

- **Usage constraints** There are no usage constraints.

- **Configurations** This register is available in all configurations.

- Attributes See the register summary in Table 3-1 on page 3-3.

Figure 3-8 on page 3-9 shows the COMPID0 Register bit assignments.

| 31 |  |          |  | 8 7 |         | 0 |

|----|--|----------|--|-----|---------|---|

|    |  | Reserved |  |     | PRMBL_0 |   |

#### Figure 3-8 COMPID0 Register bit assignments

Table 3-9 shows the COMPID0 Register bit assignments.

### Table 3-9 COMPID0 Register bit assignments

| Bits   | Name     | Function                                                                                            |

|--------|----------|-----------------------------------------------------------------------------------------------------|

| [31:8] | Reserved | -                                                                                                   |

| [7:0]  | PRMBL_0  | Contains bits [7:0] of the component identification. The possible value is:0xDIdentification value. |

### 3.3.9 Component ID1 Register

The COMPID1 Register characteristics are:

| Purpose           | A Component Identification Register that indicates the identification registers are present. This register also indicates the component class. |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Usage constraints | There are no usage constraints.                                                                                                                |

| Configurations    | This register is available in all configurations.                                                                                              |

| Attributes        | See the register summary in Table 3-1 on page 3-3.                                                                                             |

|                   |                                                                                                                                                |

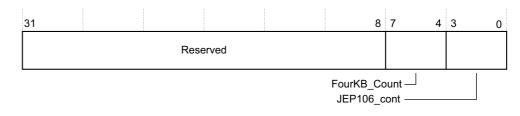

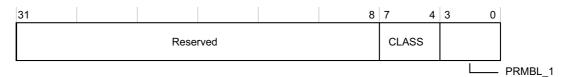

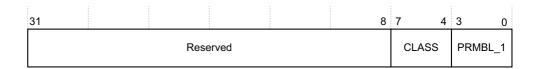

Figure 3-9 shows the COMPID1 Register bit assignments.

| 31 |      |       | 8 | 7 4   | 30      |

|----|------|-------|---|-------|---------|

|    | Rese | erved |   | CLASS | PRMBL_1 |

#### Figure 3-9 COMPID1 Register bit assignments

Table 3-10 shows the COMPID1 Register bit assignments.

### Table 3-10 COMPID1 Register bit assignments

| Bits   | Name     | Function                                                                                                                                                                                                                                                                                   |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:8] | Reserved | -                                                                                                                                                                                                                                                                                          |

| [7:4]  | CLASS    | Class of the component. For example, the ROM table and the CoreSight component. Constitutesbits [15:12] of the component identification. The possible value is:b0001Indicates the component is a ROM table.See the ARM Debug Interface v5 Architecture Specification for more information. |

| [3:0]  | PRMBL_1  | Contains bits [11:8] of the component identification. The possible value is:b0000Identification value.                                                                                                                                                                                     |

### 3.3.10 Component ID2 Register

The COMPID2 Register characteristics are:

| Purpose           | A Component Identification Register that indicates the identification registers are present. |

|-------------------|----------------------------------------------------------------------------------------------|

| Usage constraints | There are no usage constraints.                                                              |

| Configurations    | This register is available in all configurations.                                            |

| Attributes        | See the register summary in Table 3-1 on page 3-3.                                           |

|                   |                                                                                              |

Figure 3-10 shows the COMPID2 Register bit assignments.

| 31 |  |          |  | 8 | 7   | 0    |

|----|--|----------|--|---|-----|------|

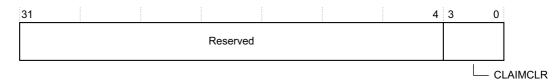

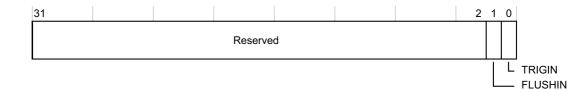

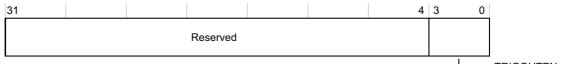

|    |  | Reserved |  |   | PRM | BL_2 |