# AS950 ARM Applications Library

**Programmer's Guide**

Copyright © 1998-2001 ARM Limited. All rights reserved. ARM DUI 0081B

# AS950 ARM Applications Library Programmer's Guide

Copyright © 1998-2001 ARM Limited. All rights reserved.

#### **Release Information**

The following changes have been made to this document.

**Change History**

| Date    | Issue | Change         |

|---------|-------|----------------|

| Oct. 98 | А     | First release  |

| Oct. 01 | В     | Second release |

#### **Proprietary Notice**

Words and logos marked with <sup>®</sup> or <sup>™</sup> are registered trademarks or trademarks owned by ARM Limited. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

# Contents AS950 ARM Applications Library Programmer's Guide

|           | Pref  | ace                                      |     |

|-----------|-------|------------------------------------------|-----|

|           |       | About this book                          | vi  |

|           |       | Feedback                                 | x   |

| Chapter 1 | Intro | oduction                                 |     |

| -         | 1.1   | About the ARM Applications Library       | 1-2 |

|           | 1.2   | Registers in macro arguments             | 1-7 |

|           | 1.3   | Building and running a demonstration     | 1-8 |

| Chapter 2 | Ada   | ptive Differential Pulse Code Modulation |     |

|           | 2.1   | Overview                                 | 2-2 |

|           | 2.2   | ADPCMState data structure                |     |

|           | 2.3   | Functions                                | 2-8 |

| Chapter 3 | G.71  | 1—A-law, µ-law, PCM Conversions          |     |

|           | 3.1   | Overview                                 | 3-2 |

|           | 3.2   | Functions                                | 3-3 |

| Chapter 4 | Fast  | Fourier Transform and Windowing          |     |

| -         | 4.1   | Overview                                 | 4-2 |

|           |       |                                          |     |

|            | 4.2<br>4.3 | Complex data structure<br>Functions       |       |

|------------|------------|-------------------------------------------|-------|

| Chapter 5  | Two-       | Dimensional Discrete Cosine Transform     |       |

| onapter o  | 5.1        | Overview                                  | 5-2   |

|            | 5.2        | SCALETABLE data structure                 |       |

|            | 5.3        | Functions                                 |       |

|            | 5.4        | Supplementary macros                      |       |

| Chapter 6  | Huffi      | man and Bit Coding/Decoding               |       |

| -          | 6.1        | Overview                                  |       |

|            | 6.2        | BitStreamState data structure             |       |

|            | 6.3        | Functions                                 | 6-10  |

| Chapter 7  | Filte      | rs                                        |       |

|            | 7.1        | Files                                     |       |

|            | 7.2        | Finite impulse response                   |       |

|            | 7.3        | Infinite impulse response                 |       |

|            | 7.4        | Least mean square                         |       |

| Chapter 8  | IS-54      | Convolutional Encoder                     |       |

|            | 8.1        | Overview                                  |       |

|            | 8.2        | Macro and function                        |       |

| Chapter 9  | Multi      | i-tone Multi-frequency Generation/Detecti | on    |

|            | 9.1        | Overview                                  |       |

|            | 9.2        | ToneState data structure                  |       |

|            | 9.3        | Functions                                 |       |

| Chapter 10 | Bit N      | lanipulation                              |       |

| -          | 10.1       | Files                                     |       |

|            | 10.2       | Macros                                    | 10-3  |

| Chapter 11 | Math       | ematics                                   |       |

|            | 11.1       | Overview                                  |       |

|            | 11.2       | Integer multiplication                    | 11-3  |

|            | 11.3       | Integer division                          | 11-8  |

|            | 11.4       | Fixed-point division                      |       |

|            | 11.5       | Integer square and cube root              | 11-28 |

|            | 11.6       | Trigonometric functions                   | 11-31 |

|            | 11.7       | General macros                            | 11-34 |

|            |            |                                           |       |

# Preface

This preface introduces the AS950 ARM Applications Library Programmer's Guide. It contains the following sections:

- About this book on page vi

- *Feedback* on page x.

# About this book

This guide is provided with the ARM Applications Library. It is assumed that the ARM Applications Library sources are available as a reference. It is also assumed that the reader has access to programmer guides for C and ARM assembly language.

#### Intended audience

This book is written for all developers who want to to evaluate, develop, and optimize software applications for the ARM RISC processor family. It assumes you are an experienced software developer, and that you are familiar with using ADS.

#### Using this book

This book is organized into the following chapters:

#### **Chapter 1** Introduction

Read this chapter for an introduction to the ARM Applications Library.

#### Chapter 2 Adaptive Differential Pulse Code Modulation

Read this chapter for details on implementation, and for function descriptions for *adaptive differential pulse code modulation* (ADPCM).

#### Chapter 3 G.711-A-law, µ-law, PCM Conversions

Read this chapter for details on implementation, and for function descriptions for the G.711 standard for A-law and  $\mu$ -law conversion of *pulse code modulation* (PCM) signals.

#### Chapter 4 Fast Fourier Transform and Windowing

Read this chapter for details on implementation, and for function descriptions for the *fast Fourier transform* (FFT), and implementations of Hamming and Hanning windows that can be used with the FFT.

#### Chapter 5 Two-Dimensional Discrete Cosine Transform

Read this chapter for details on implementation, and for function and macro descriptions for *two-dimensional* (2D) *discrete cosine transform* (DCT).

#### Chapter 6 Huffman and Bit Coding/Decoding

Read this chapter for details on implementation, and for function descriptions of a Huffman coder/decoder that uses a general bit codec based on lookup tables.

#### **Chapter 7** Filters

Read this chapter for details on implementation, and for function and macro descriptions for *finite impulse response* (FIR), *infinite impulse response* (IIR), and *least mean square* (LMS) filters.

#### Chapter 8 IS-54 Convolutional Encoder

Read this chapter for details on implementation, and for function and macro descriptions for the convolutional encoder from the IS-54 standard for digital mobile telephones in the United States of America.

#### Chapter 9 Multi-tone Multi-frequency Generation/Detection

Read this chapter for details on implementation, and for function descriptions for the *multi-tone multi-frequency* (MTMF) detector and generator.

#### Chapter 10 Bit Manipulation

Read this chapter for details on macro descriptions for performing common bit manipulation routines.

#### Chapter 11 Mathematics

Read this chapter for details on macro descriptions for performing common mathematical functions.

#### **Typographical conventions**

The following typographical conventions are used in this book:

| monospace         | Denotes text that may be entered at the keyboard, such as commands, file<br>and program names, and source code.                                |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>mono</u> space | Denotes a permitted abbreviation for a command or option. The<br>underlined text may be entered instead of the full command or option<br>name. |

| monospace i       | talic                                                                                                                                          |

|                   | Denotes arguments to commands and functions where the argument is to be replaced by a specific value.                                          |

| monospace bo      | bld                                                                                                                                            |

|                   | Denotes language keywords when used outside example code and ARM processor signal names.                                                       |

| italic            | Highlights important notes, introduces special terminology, denotes internal cross-references, and citations.                                  |

| bold              | Highlights interface elements, such as menu names and buttons. Also used for terms in descriptive lists, where appropriate.                    |

#### **Further reading**

This section lists publications from both ARM Limited and third parties that provide additional information on developing code for the ARM family of processors.

ARM periodically provides updates and corrections to its documentation. See http://www.arm.com for current errata sheets and addenda.

See also the ARM Frequently Asked Questions list at: http://www.arm.com/DevSupp/Sales+Support/faq.html

#### **ARM** publications

This book contains information that is specific to the version of the Applications Library supplied with the *ARM Developer Suite* (ADS). Refer to the books in the ADS document suite for information on other components of ADS.

In addition, refer to the following documentation for specific information relating to ARM products:

• ARM Reference Peripheral Specification (ARM DDI 0062)

• the ARM datasheet or technical reference manual for your hardware device.

#### Other publications

For information that may be useful when using the ARM Applications Library, refer to:

- General Aspects of Digital Transmission Systems; Terminal Equipments, Volume III, Recommendations G.700-G.795, International Telegraph and Telephone Consultative Committee (ISBN 92-61-033415)

- Y.Arai, T.Agui, and M.Nakajima. A Fast DCT-SQ Scheme for Images. Trans. of the IEICE. E 71(11):1095 (Nov. 1988)

- Mark Nelson, *The Data Compression Book* (ISBN 1-55851-214-4)

- Kernighan, Brian W. and Ritchie, Dennis M., *The C Programming Language* (ISBN 0-13-110370-8)

# Feedback

ARM Limited welcomes feedback on both the ARM Applications Library, and its documentation.

#### Feedback on the ARM Developer Suite

If you have any problems with the ARM Developer Suite, please contact your supplier. To help your supplier provide a rapid and useful response, please give:

- details of the release you are using

- details of the platform you are running on, such as the hardware platform, operating system type and version

- a small standalone sample of code that reproduces the problem

- a clear explanation of what you expected to happen, and what actually happened

- the commands you used, including any command-line options

- sample output illustrating the problem

- the version string of the tool, including the version number and date.

#### Feedback on this book

If you have any comments on this book, please send email to errata@arm.com giving:

- the document title

- the document number

- the page number(s) to which you comments apply

- a concise explanation of your comments.

General suggestions for additions and improvements are also welcome.

# Chapter 1 Introduction

This chapter introduces the AS950 ARM Applications Library. It contains the following sections:

- About the ARM Applications Library on page 1-2

- Registers in macro arguments on page 1-7

- Building and running a demonstration on page 1-8.

# 1.1 About the ARM Applications Library

The ARM Applications Library Version 1.1 is a suite of optimized ARM assembly language and C source code for commonly used *digital signal processing* (DSP), mathematical, and bit manipulation functions. It has been designed to help you to evaluate, develop, and optimize software applications for the ARM RISC processor family. The library should be used in conjunction with the *ARM Developer Suite* (ADS).

The following is provided with each of the code modules:

- comprehensive documentation

- example and test applications in two subdirectories:

- src contains C routines and source files

- tstfiles contains test data files (for example, a bitmap image for DCT)

- supporting utilities needed to build the examples using ADS.

A general C utility library, util\_lib, is also provided to demonstrate each of the main components. You are free to incorporate any of the source code contained in the library into any products, subject to the terms of the license agreement.

The following sections briefly describe each of the code components, and give examples of potential applications.

#### 1.1.1 Noncompliant adaptive differential pulse code modulation

Adaptive differential pulse code modulation (ADPCM) is a compression and decompression algorithm that uses adaptive quantizers and adaptive predictors to compress sound data, typically speech. The implemented encoder takes 16-bit *pulse code modulation* (PCM) data to produce a representation using 4-bit ADPCM values.

The ADPCM implementation is not compliant with the G.726 standard or any other ADPCM standard. Therefore, it cannot be used to interface to other ADPCM compressors/decompressors. It does not include error correction, so it is not suitable for transmission over an imperfect link. However, the implementation is suitable for reducing audio storage overheads.

See Chapter 2 Adaptive Differential Pulse Code Modulation.

#### 1.1.2 G.711

G.711 is a recommendation defined by the *International Telegraph and Telephone Consultative Committee* (CCITT) (now the *Telecommunication Standardization Sector* of the *International Telecommunication Union* (ITU-T)).

Analog signals are digitized using *pulse code modulation* (PCM) and are then compressed from linear 16-bit PCM values to 8-bit A-law or  $\mu$ -law values using logarithmic compression. Conversely, 8-bit A-law or  $\mu$ -law values can be decompressed to linear 16-bit PCM values.

This compression is recommended for encoding voice-frequency signals because logarithmic compression only loses information that the human ear cannot hear.

Applications include telecommunications (cordless phones), multimedia (lower audio storage overheads), and inter-chip connections (reduces bus width to 8-bits).

See Chapter 3 G.711—A-law, µ-law, PCM Conversions.

#### 1.1.3 Fast Fourier transform and windowing

The *fast Fourier transform* (FFT) is one of the main *digital signal processing* (DSP) algorithms. FFTs convert *one-dimensional* (1D) data, typically sound, between the time domain and the 1D frequency domain.

Windowing selects segments of data (pre-weighting of the data) for subsequent frequency domain analysis using the FFT. Both Hamming and Hanning windows are provided.

FFT can be used for:

#### spectral analysis

Identifying the magnitude of each frequency within a signal (the spectral components).

#### digital filtering

Applying FFT, removing a range of frequency components using a filtering technique and reconstructing the signal using the inverse FFT. Windowing can be used to prevent clicks at frame boundaries.

#### calculation of correlations

Increasing the speed of a traditional *finite impulse response* (FIR) filter that requires the calculation of large correlations.

#### calculation of convolutions

Common calculations in the construction of filters.

See Chapter 4 Fast Fourier Transform and Windowing.

#### 1.1.4 Discrete cosine transform

The *discrete cosine transform* (DCT) converts a *two-dimensional* (2D) graphics image between the spatial domain and the 2D frequency domain.

The DCT is implemented using an 8x8 block and does not directly lead to compression. However, the DCT does produce frequency data that is suitable for use in graphics compression algorithms such as JPEG or MPEG.

See Chapter 5 Two-Dimensional Discrete Cosine Transform.

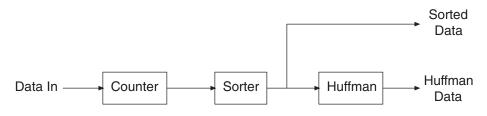

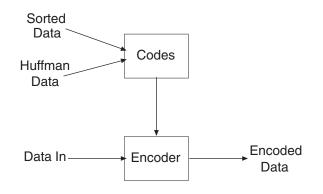

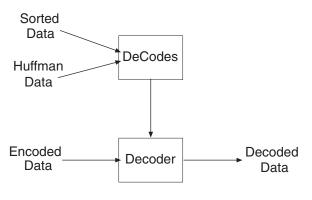

#### 1.1.5 Huffman encoding/decoding

Huffman encoding/decoding exploits the fact that discrete amplitudes of a signal do not occur with equal probability. Huffman encoding creates variable length codes that are an integral number of bits. Symbols with higher probabilities have fewer bits in their codes. The codes can be uniquely decoded, despite being of different lengths, because each is created with a unique prefix.

Most compression algorithms use some form of Huffman encoding/decoding where performance is more important than compression rate. Applications include JPEG, font compression, and dictionary compression.

See Chapter 6 Huffman and Bit Coding/Decoding.

#### 1.1.6 Filtering

Digital filters can be used to remove data from a sound signal, such as noise and unwanted frequencies, by attenuating or reducing certain bands of frequencies and allowing the others to pass. Digital filters are often classed into one of four types:

- low-pass

- high-pass

- band-pass

- band-stop.

A low-pass filter allows frequencies below a certain value to pass through as-is while attenuating frequencies above that point. Conversely, a high-pass filter lets frequencies above a certain value pass through as-is while attenuating frequencies below that point. For example, a low-pass filter may be used to remove high frequency noise from a speech signal.

A band-pass filter allows a selected frequency band in a signal to pass through as-is and reduces all frequencies outside of this band. This has the effect of emphasizing the selected band. For example, band-pass filters might be used in a graphic equalizer.

A band-stop filter reduces a selected frequency band in a signal and allows all frequencies outside this band to pass through unaffected. For example, it can be used to remove a 50Hz mains hum from a signal.

Three filters are provided:

- *finite impulse response* (FIR)

- *infinite impulse response* (IIR)

- *least mean square* (LMS).

The type of filter to be used, such as a low-pass or band-stop, is identified by the coefficients (weight values) that are used with the filter.

The FIR filter is a nonrecursive linear filter (no feedback) and performs a moving and weighted average on the input data. Finite refers to the fact that an input pulse results in energy at only a finite number of samples after which the output returns to zero. FIR filters are suitable for telecommunications use, such as distinguishing between the channels used in a V.22bis modem link.

The IIR filter is a recursive linear filter that employs feedback to allow sharper frequency responses to be obtained for fewer filter coefficients. Infinite refers to the fact that the output from a unit pulse input exhibits non-zero outputs for an arbitrarily long time.

The LMS filter is an adaptive FIR digital filter that is self-learning and adapts the impulse response of the FIR filter to a desired signal.

The IIR and LMS filters are suitable for echo cancellation and line equalization, compensating for errors introduced by transmission over a channel.

See Chapter 7 Filters.

#### 1.1.7 IS-54 convolutional encoder

IS-54 is the *Telecommunications Industry Association/Electronic Industries Association* (TIA/EIA) interim standard for the Cellular System Dual-Mode Mobile Station-Base Station Compatibility Standard. This is the digital mobile telephone standard used in the United States of America.

The convolutional encoder is used to code 89 bits of data at a time:

- 77 class 1 bits from the IS-54 speech coder

- seven bits of cyclic redundancy check

- five bits of tail.

This algorithm also demonstrates how to optimally interleave two 16-bit words to generate a 32-bit word. See Chapter 8 *IS-54 Convolutional Encoder*.

#### 1.1.8 Multi-tone multi-frequency and Goertzel algorithm

The multi-frequency algorithm is used in detecting and generating tones such as *dual-tone multi-frequency* (DTMF), multi-frequency, busy, and dial tones.

DTMF transmission and reception is resistant to line noise and distortion, and is performed in applications such as answering machines, modems, telephones and PBXs. E1 applications (the European equivalent to T1) and US telephone frame equipment are applications that perform multi-frequency tone detection and generation functions. Busy and dial tone generation and detection capabilities are required by various telephony applications.

See Chapter 9 Multi-tone Multi-frequency Generation/Detection.

#### 1.1.9 Bit manipulation

The bit manipulation routines perform a number of operations on words on a per-bit basis. The routines include bit and byte reversal over a word, binary coded decimal addition, finding the least and most significant bits set in a word, and population count over a set of words (determining the number of bits set).

See Chapter 10 Bit Manipulation.

#### 1.1.10 Mathematics

The mathematics functions provide optimal algorithms to perform common mathematical tasks using differing precision and fixed-point input data. These algorithms are suitable for high-precision work such as encryption or vector manipulation (three-dimensional graphics).

The mathematics component also contains routines to perform addition of absolute values, c = a + abs(b), and signed-saturated addition of two 32-bit integers.

See Chapter 11 Mathematics.

# 1.2 Registers in macro arguments

In the ARM Assembler macro definitions, arguments are prefixed with a dollar sign (\$). Except where otherwise noted, these arguments represent variable names for registers that must be substituted for actual registers when creating an instantiation of the macro.

#### 1.2.1 Example

In the following example, an ARM assembly language macro example\_macro could be defined in a file examplem.h:

```

MACRO

example_macro $c, $a, $b

ADD $c, $a, $b

MEND

```

The macro arguments \$a and \$b represent the two input registers, and \$c is the output register

The macro file can be included in an assembly language source file using the INCLUDE directive. The following example shows how the macro might be instantiated:

```

INCLUDE examplem.h

example_macro_start

example_macro R0, R0, R1

MOV pc, lr

```

The macro adds the values of the input registers r0 and r1, and stores the result in r0.

Refer to the *ADS Developer Guide* in the ADS documentation for information on register usage conventions and the *ARM Procedure Call Standard* (APCS).

# 1.3 Building and running a demonstration

This section describes how to build and run the Applications Library using ADS. For more information on using ADS, refer to the ADS documentation.

#### 1.3.1 Variants

Each component of the Applications Library has a UNIX makefile and two CodeWarrior IDE .mcp project files, which are:

- the core, library components file

- the executable version of the core, library components file.

These files provide options for building different variants of the components. You can build variants for:

- little-endian and big-endian ARM versions

- little-endian and big-endian Thumb versions.

The variations are identified by the following variant names:

| ArmBigDebug                                              | ARM, big-endian, debug information       |  |  |

|----------------------------------------------------------|------------------------------------------|--|--|

| ArmBigRelease                                            | ARM, big-endian, no debug information    |  |  |

| ArmLittleDebug                                           | ARM, little-endian, debug information    |  |  |

| ArmLittleRelease                                         | ARM, little-endian, no debug information |  |  |

| ThumbBigDebug                                            | Thumb, big-endian, debug information     |  |  |

| ThumbBigRelease                                          | Thumb, big-endian, no debug information  |  |  |

| ThumbLittleDebug Thumb, little-endian, debug information |                                          |  |  |

| ThumbLittleRelease                                       |                                          |  |  |

Thumb, little-endian, no debug information.

#### 1.3.2 Linker output

The output produced when building a variant is the default format defined by the version of the toolkit used to perform the build. To build a different output, add the appropriate command-line argument to the linker configuration. For information on the output formats supported by the linker and how to change the output produced by the linker, see the *ADS Linker and Utilities Guide* in the ADS documentation.

#### 1.3.3 Building and running

This section describes how to build and run an Applications Library component. To compile components of the Applications Library on Windows with the supplied projects, ADS is required. Refer to *CodeWarrior IDE Guide* in the ADS documentation for details on building using project files.

- 1. Double click on the executable .mcp file located in the appropriate component folder, not the library .mcp file (identified by lib appended to the component name).

- 2. Build one of the variants of the project.

- 3. Run the binary under the Windows debugger, ensuring the byte-sex for the debugger is that of the selected variant.

#### 1.3.4 Execution considerations

Each component allows you to enter values at run-time for options on testing and demonstrating the functionality. If you are prompted for an input data file, suitable test files can be found in the tstfiles folder for the appropriate component.

When running C-based test versions, some of the demonstrations (such as Discrete Cosine Transform and Fast Fourier Transform) require considerable time to complete if running under the ARMulator. For these cases, it is advisable to download the executable to an ARM Integrator, or other hardware, and run the test there. The ARM Integrator can be purchased from ARM. See http://www.arm.com.

Introduction

# Chapter 2 Adaptive Differential Pulse Code Modulation

This chapter describes an implementation of *adaptive differential pulse code modulation* (ADPCM). It contains the following sections:

- Overview on page 2-2

- ADPCMState data structure on page 2-7

- *Functions* on page 2-8.

# 2.1 Overview

This section provides general information on ADPCM encoding and decoding.

#### 2.1.1 Implementation

This section describes the formulas that have been used in the implementation for the encoding and decoding ADPCM.

This implementation of ADPCM is noncompliant with G.726 or any other standard, including the earlier G.721 and G.723 standards. The ARM implementation is suitable only for use where bit errors cannot occur, such as in computer systems. If bit errors are introduced into the process, they propagate through the coder. Therefore, this implementation is not suitable for compression before transmission across channels that can add bit errors.

The encoder for the ADPCM has been implemented to take 16-bit PCM input values and produce a 4-bit compressed ADPCM output value for each input value. Conversely, the ADPCM decoder has been implemented to take 4-bit compressed ADPCM input values that were generated by the encoder and produce the corresponding 16-bit PCM output value for each input value.

The decoder is discussed before the encoder because the encoder makes use of the decoder.

#### **Decoding ADPCM**

For each ADPCM value  $y_i$ , where  $0 \le i < N$ , the corresponding PCM output,  $x_i$ , is given by:

$step_i = stepSize[index_i]$

$delta_i = y_i$

$index_{i+1} = index_i + indexTable[delta_i]$

$delta_{i} = \begin{cases} delta_{i} - 8 & delta_{i} > 7 \\ delta_{i} & otherwise \end{cases}$

$$x_{i} = \begin{cases} x_{i-1} - (2 \times delta_{i} + 1) \times \frac{step_{i}}{8} & y_{i} > 7\\ x_{i-1} + (2 \times delta_{i} + 1) \times \frac{step_{i}}{8} & otherwise \end{cases}$$

where:

$x_{-1} = 0$

$index_0 = 0$

*indexTable* and *StepSize* are defined as follows:

$indexTable[16] = \begin{bmatrix} & & & \\ -1 & -1 & -1 & -1 & 2 & 4 & 6 & 8 \\ & -1 & -1 & -1 & -1 & 2 & 4 & 6 & 8 \\ & & & & \\ \end{bmatrix}$

| [   |    |       |       |       |       |       |       |       |       |       |

|-----|----|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 7   | ,  | 8     | 9     | 10    | 11    | 12    | 13    | 14    | 16    | 17    |

| 1   | 9  | 21    | 23    | 25    | 28    | 31    | 34    | 37    | 41    | 45    |

| 5   | 0  | 55    | 60    | 66    | 73    | 80    | 88    | 97    | 107   | 118   |

| 13  | 0  | 143   | 157   | 173   | 190   | 209   | 230   | 253   | 279   | 307   |

| 33  | 7  | 371   | 408   | 449   | 494   | 544   | 598   | 658   | 724   | 796   |

| 87  | 6  | 963   | 1060  | 1166  | 1282  | 1411  | 1552  | 1707  | 1878  | 2066  |

| 22  | 72 | 2499  | 2749  | 3024  | 3327  | 3660  | 4026  | 4428  | 4871  | 5358  |

| 58  | 94 | 6484  | 7132  | 7845  | 8630  | 9493  | 10442 | 11487 | 12635 | 13899 |

| 152 | 89 | 16818 | 18500 | 20350 | 22385 | 24623 | 27086 | 29794 | 32767 |       |

| ]   |    |       |       |       |       |       |       |       |       |       |

|     |    |       |       |       |       |       |       |       |       |       |

stepSize[89] =

Saturation is also incorporated into the algorithm so that:

$x_i$  cannot exceed the range  $-2^{15} \le x_i \le 2^{15} - 1$

*index*<sub>*i*</sub> cannot exceed the range  $0 \le index_i \le 88$ .

#### **Encoding ADPCM**

For each value  $x_i$ , where  $0 \le i < N$ , the corresponding ADPCM output,  $y_i$ , is given by:

$$difference_i = x_i - DecodeADPCM(y_{i-1})$$

$$step_i = stepSize[index_i]$$

$$delta_i = \frac{|difference_i| \times 4}{step_i}$$

(integer division)

$$delta_{i} = \begin{cases} delta_{i} + 8 & difference_{i} < 0 \\ delta_{i} & otherwise \end{cases}$$

$$index_{i+1} = index_i + indexTable[delta_i]$$

$y_i = delta_i$

where:

$y_{-1} = 0$

$index_0 = 0$

indexTable and stepSize are defined as given in Decoding ADPCM on page 2-3.

Saturation is also incorporated into the algorithm so that:

$delta_i$  when initially calculated, before the addition of 8 for negative values, cannot exceed the range  $0 \le delta_i \le 7$

*index*<sub>*i*</sub> cannot exceed the range  $0 \le index_i \le 88$ .

## 2.1.2 Files

The files in Table 2-1 are provided in the implementation.

#### Table 2-1 ADPCM files

| Filename   | Archive name | Code type             | Functionality              |

|------------|--------------|-----------------------|----------------------------|

| adpcms.s   | arm_adpm     | ARM assembly language | ADPCM coding and decoding  |

| adpcms.h   | arm_adpm     | C header              | ADPCM function prototypes  |

| adpstruc.h | arm_adpm     | C header              | ADPCM structure definition |

# 2.2 ADPCMState data structure

This structure is used to maintain step-size and prediction values internally during the ADPCM operations and between routine calls.

The ADPCM encode and decode routines are passed a pointer to this structure.

## 2.2.1 Definition

typedef struct ADPCMState ADPCMState ;

typedef ADPCMState ADPCMState ;

struct ADPCMState {

int stepIndex ;

int prediction ;

};

## 2.2.2 Description

The ADPCM routines operate over a set of data values where the current output value is directly related to the previous output value. Because of this, each call to one of the routines requires some history of the previous values. This history is defined by the step-size and the prediction for the next input value, and is maintained in the ADPCMState structure between routine calls.

## 2.2.3 Usage

When starting a new coding or decoding sequence, before you pass the structure to the ADPCM routines, you must initialize the stepIndex and prediction entries to zero. Between the routine calls for the sequence of input values, you must maintain the structure with the values that are updated during the operation of the routine.

# 2.3 Functions

This section describes the ADPCM routines. The functions are:

- Encode 16-bit *pulse code modulation* (PCM) to 4-bit ADPCM (*adpcm\_encode*)

- Decode 4-bit ADPCM to 16-bit PCM (*adpcm\_decode* on page 2-9).

#### 2.3.1 adpcm\_encode

You can call this function repeatedly to encode a set of 16-bit PCM inputs to a set of corresponding 4-bit compressed ADPCM samples.

#### Syntax

int adpcm\_encode(int pcmSample, ADPCMStatePtr encodeStatePtr)

where:

| pcmSample      | is the current 16-bit PCM data value to be encoded. This value must be a 16-bit quantity, even though it is passed in a 32-bit integer word.                                                                                |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| encodeStatePtr | is a pointer to the ADPCMState structure required during the encoding operation.                                                                                                                                            |

|                | When this function returns, <i>encodeStatePtr</i> points to an updated ADPCMState structure that contains the values required during the next call to adpcm_encode(). The structure must be maintained as-is between calls. |

#### **Return Value**

The 4-bit compressed ADPCM encoding of the given 16-bit PCM input data value.

#### Usage

For each set of PCM data values to be encoded, the entries in the ADPCMState structure must be zero-initialized before the first call to adpcm\_encode(). The ADPCMState structure must then be passed to each subsequent function call with the values returned from the previous function call.

#### 2.3.2 adpcm\_decode

You can call this function repeatedly to decode a set of 4-bit compressed ADPCM inputs to a set of corresponding uncompressed 16-bit PCM samples.

#### Syntax

int adpcm\_decode(int adpcmSample, ADPCMStatePtr decodeStatePtr)

where:

| adpcmSample    | is the current 4-bit compressed ADPCM data value to be decoded.<br>This value must be a 4-bit quantity, even though it is passed in a 32-bit integer word.                                                                  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| decodeStatePtr | is a pointer to the ADPCMState structure required during the decoding operation.                                                                                                                                            |

|                | When this function returns, <i>decodeStatePtr</i> points to an updated ADPCMState structure that contains the values required during the next call to adpcm_decode(). The structure must be maintained as-is between calls. |

#### **Return Value**

The 16-bit uncompressed PCM decoding of the given 4-bit ADPCM input data value.

#### Usage

Because the ADPCM implementation is specific, the values in *adpcmSample* must be values that have been returned from adpcm\_encode(). Data from another ADPCM encoder may not be in the correct format.

For each set of ADPCM data values to be decoded, the entries in the ADPCMState structure must be zero-initialized before the first call to adpcm\_decode(). The ADPCMState structure must then be passed to each subsequent function call with the values returned from the previous function call.

Adaptive Differential Pulse Code Modulation

# Chapter 3 G.711—A-law, µ-law, PCM Conversions

This chapter describes an implementation of the *International Telecommunications Union* (ITU) G.711 standard for A-law and  $\mu$ -law conversion of *pulse code modulation* (PCM) signals. It contains the following sections:

- Overview on page 3-2

- *Functions* on page 3-3.

# 3.1 Overview

This section provides general information on G.711.

## 3.1.1 Implementation

The implementation is based on the G.711 standard from the ITU. The G.711 standard is defined in *General Aspects of Digital Transmission Systems; Terminal Equipments, Volume III, Recommendations G.700-G.795.*

#### 3.1.2 Files

The files in Table 3-1 are provided with the implementation. The G.711 standard is implemented as a set of ARM assembly language macros in g711m.h.

#### Table 3-1 G711 files

| File name  | Archive name | Code type             | Functionality                                                                            |

|------------|--------------|-----------------------|------------------------------------------------------------------------------------------|

| g711m.h    | arm_g711     | ARM assembly language | PCM, A-law, and µ-law conversions                                                        |

| g711uats.s | arm_g711     | ARM assembly language | A-law to and from μ-law conversion lookup tables,<br>G711_u2a_lookup and G711_a2u_lookup |

| g711s.s    | arm_g711     | ARM assembly language | G.711 macro initializations with C-based code wrapping                                   |

| g711s.h    | arm_g711     | C header              | G.711 function prototypes                                                                |

# 3.2 Functions

This section describes the G.711 macros. The macros are:

- 16-bit linear PCM to 8-bit A-law conversion (*G711\_linear2alaw\_macro*)

- 8-bit A-law to 16-bit linear PCM conversion (*G711\_alaw2linear\_macro* on page 3-4)

- 16-bit linear PCM to 8-bit μ-law conversion (*G711\_linear2ulaw\_macro* on page 3-5)

- 8-bit µ-law to 16-bit linear PCM conversion (*G711\_ulaw2linear\_macro* on page 3-6)

- 8-bit A-law to 8-bit µ-law conversion (*G711\_alaw2ulaw\_macro* on page 3-7)

- 8-bit μ-law to 8-bit A-law conversion (*G711\_ulaw2alaw\_macro* on page 3-9).

#### 3.2.1 G711\_linear2alaw\_macro

This macro converts a 16-bit linear PCM value to an 8-bit compressed A-law value.

#### Syntax

MACRO G711\_linear2alaw\_macro \$pcm, \$alaw, \$t1, \$t2, \$msk

where:

| \$pcm             | is a register that holds the 16-bit linear PCM value to be converted.<br>This value must be no more than a 16-bit quantity with the least<br>significant bit first, even though it is in a 32-bit register. The value<br>can be less than 16 bits, but each sample must occupy two bytes<br>and must be shifted up, leaving zeros in the bottom unused bits, so<br>that dynamic range is not lost. |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \$alaw            | is a register that holds the 8-bit compressed A-law result.                                                                                                                                                                                                                                                                                                                                        |

| \$t1, \$t2, \$msk | are temporary registers required during the conversion. On output, any value is undefined.                                                                                                                                                                                                                                                                                                         |

#### **Register differentiation**

*\$pcm*, *\$t1*, *\$t2* and *\$msk* must be distinct registers.

*\$a1aw*, *\$t1* and *\$t2* must be distinct registers.

*\$pcm* and *\$a1aw* need not be distinct registers.

\$a1aw and \$msk need not be distinct registers.

#### 3.2.2 G711\_alaw2linear\_macro

This macro converts an 8-bit compressed A-law value to a 16-bit linear PCM value.

#### Syntax

MACRO G711\_alaw2linear\_macro \$alaw, \$pcm, \$t1, \$t2

where:

- \$a1aw is a register that holds the 8-bit compressed A-law value to be converted. This value must be an 8-bit quantity with the least significant bit first, even though it is in a 32-bit register.

- *\$pcm* is a register that holds the 16-bit linear PCM result.

- *\$t1, \$t2* are temporary registers required during the conversion. On output, any value is undefined.

#### **Register differentiation**

*\$a1aw*, *\$t1* and *\$t2* must be distinct registers.

*\$pcm*, *\$t1* and *\$t2* must be distinct registers.

\$alaw and \$pcm need not be distinct registers.

#### 3.2.3 G711\_linear2ulaw\_macro

This macro converts a 16-bit linear PCM value to an 8-bit compressed µ-law value.

#### **Syntax**

```

MACRO G711_linear2ulaw_macro $pcm, $ulaw, $msk, $t1, $t2

```

where:

| \$pcm             | is a register that holds the 16-bit linear PCM value to be converted. This value must be no more than a 16-bit quantity with the least significant bit first, even though it is in a 32-bit register. The value can be less than 16 bits, but each sample must occupy two bytes and must be shifted up, leaving zeros in the bottom unused bits, so that dynamic range is not lost. |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \$ulaw            | is a register that holds the 8-bit compressed $\mu$ -law result.                                                                                                                                                                                                                                                                                                                    |

| \$msk, \$t1, \$t2 | are temporary registers required during the conversion. On output, any value is undefined.                                                                                                                                                                                                                                                                                          |

#### **Register differentiation**

\$pcm, \$t1, \$t2 and \$msk must be distinct registers.

*\$u1aw*, *\$t1* and *\$t2* must be distinct registers.

*\$pcm* and *\$u1aw* need not be distinct registers.

*\$u1aw* and *\$msk* need not be distinct registers.

## 3.2.4 G711\_ulaw2linear\_macro

This macro converts an 8-bit compressed µ-law value to a 16-bit linear PCM value.

#### Syntax

MACRO G711\_ulaw2linear\_macro \$ulaw, \$pcm, \$seg

where:

| \$ulaw | is a register that holds the 8-bit compressed $\mu$ -law value to be converted.<br>This value must be an 8-bit quantity with the least significant bit first, even though it is in a 32-bit register. |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \$pcm  | is a register that holds the 16-bit linear PCM result.                                                                                                                                                |

| \$seg  | is a temporary register required during the conversion. On output, any                                                                                                                                |

#### **Register differentiation**

*\$u1aw* and *\$seg* must be distinct registers.

value is undefined.

*\$pcm* and *\$seg* must be distinct registers.

*\$u1aw* and *\$pcm* need not be distinct registers.

### 3.2.5 G711\_alaw2ulaw\_macro

This macro converts an 8-bit compressed A-law value to an 8-bit compressed  $\mu$ -law value.

### Syntax

MACRO G711\_alaw2ulaw\_macro \$alaw, \$ulaw, \$tmp, \$table, \$hastable

where:

| \$alaw     | is a register that holds the 8-bit compressed A-law value to be converted.<br>This value must be an 8-bit quantity with the least significant bit first,<br>even though it is in a 32-bit register.                                                                                               |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \$ulaw     | is a register that holds the 8-bit compressed µ-law result.                                                                                                                                                                                                                                       |

| \$tmp      | is a temporary register required during the conversion. On output, any value is undefined.                                                                                                                                                                                                        |

| \$table    | is a register that holds the address of the G711_a2u_lookup table, either<br>supplied on input or initialized by the macro. If the macro is to be used<br>repeatedly, <i>\$table</i> can be initialized the first time the macro is used and<br>passed as a parameter with each subsequent usage. |

| \$hastable | is an optional parameter that can contain any value. If <i>\$hastable</i> is present, <i>\$table</i> must contain the address of the G711_a2u_lookup table. If <i>\$hastable</i> is not present, <i>\$table</i> is initialized by the macro.                                                      |

## Usage

The macro requires the address of the G711\_a2u\_lookup table (defined in g711uats.s) for the conversion. This address is held in the register identified by *\$table*, and can either be:

- supplied to the macro, in which case *\$hastable* must be supplied

- initialized by the macro, in which case *\$hastable* must not be supplied.

## **Register differentiation**

*\$a1aw, \$tmp* and *\$tab1e* must be distinct registers.

*\$u1aw* and *\$tmp* must be distinct registers.

*\$u1aw* and *\$tab1e* need not be distinct registers. However, the address of the lookup table is overwritten if the same register is used for both parameters.

*\$a1aw* and *\$u1aw* need not be distinct registers.

### 3.2.6 G711\_ulaw2alaw\_macro

This macro converts an 8-bit compressed  $\mu\text{-law}$  value to an 8-bit compressed A-law value.

### Syntax

MACRO G711\_ulaw2alaw\_macro \$ulaw, \$alaw, \$tmp, \$table, \$hastable

where:

| \$ulaw     | is a register that holds the 8-bit compressed $\mu$ -law value to be converted.<br>This value must be an 8-bit quantity with the least significant bit first, even though it is given in a 32-bit register.                                                                              |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \$alaw     | is a register that holds the 8-bit compressed A-law result.                                                                                                                                                                                                                              |

| \$tmp      | is a temporary register required during the conversion. On output, any value is undefined.                                                                                                                                                                                               |

| \$table    | is a register that holds the address of the G711_u2a_lookup table, either supplied on input or initialized by the macro. If the macro is to be used repeatedly, <i>\$table</i> can be initialized the first time the macro is used and passed as a parameter with each subsequent usage. |

| \$hastable | is an optional parameter that can contain any value. If <i>\$hastable</i> is present, <i>\$table</i> must contain the address of the G711_u2a_lookup table. If <i>\$hastable</i> is not present, <i>\$table</i> is initialized by the macro.                                             |

## Usage

The macro requires the address of the G711\_u2a\_lookup table (defined in g711uats.s) for the conversion. This address is held in the register identified by *\$table*, and can either be:

- supplied to the macro, in which case *\$hastable* must be supplied

- initialized by the macro, in which case *\$hastable* must not be supplied.

## **Register differentiation**

*\$u1aw, \$tmp* and *\$tab1e* must be distinct registers.

*\$a1aw* and *\$tmp* must be distinct registers.

*\$a1aw* and *\$tab1e* need not be distinct registers. However, the address of the lookup table is overwritten if the same register is used for both parameters.

*\$u1aw* and *\$a1aw* need not be distinct registers.

# Chapter 4 Fast Fourier Transform and Windowing

This chapter describes an implementation of the *fast Fourier transform* (FFT) and implementations of Hamming and Hanning windows that can be used with the FFT. It contains the following sections:

- *Overview* on page 4-2

- *Complex data structure* on page 4-9

- *Functions* on page 4-10.

## 4.1 Overview

This section provides general information on:

- the implementation of forward FFT and inverse FFT

- the flags relating to FFT optimization and conditional assembly

- Hamming and Hanning windows

- the files provided with the FFT implementation.

### 4.1.1 Implementation

This section describes the formulas used in the implementation of the forward and inverse FFTs, and the settings that can be adjusted for the implementation. A Radix2 algorithm is used. It also describes the formulas for the windowing techniques.

## **Forward FFT**

The forward FFT, given by:

$$\underline{X} = FFT(\underline{x})$$

performs the calculation specified by the formula:

$$X[k] = \frac{1}{N} \sum_{n=0}^{N-1} x[n] (\cos(nk\omega) - i\sin(nk\omega))$$

where  $\omega = 2\pi / N$  and the 1 / N scaling that multiplies the summation prevents overflow within the algorithm.

Using the complex identity  $e^{i\theta} = \cos\theta + i \sin\theta$ , the transform can be written as:

$$X[k] = \frac{1}{N} \sum_{n=0}^{N-1} x[n] e^{-ink\omega}$$

Evaluating the sum directly requires of the order of  $N^2$  multiplications. However, this can be reduced to the order of  $N \log N$  by rearranging the terms in the following way:

Separate out the even-numbered and odd-numbered elements:

$$X[k] = \frac{1}{N} \left( \sum_{n=0}^{N/2-1} x[2n] e^{-2ink\omega} + \sum_{n=0}^{N/2-1} x[2n+1] e^{-i(2n+1)k\omega} \right)$$

Take out a factor of  $e^{-ik\omega}$ :

$$X[k] = \frac{1}{N} \left( \sum_{n=0}^{N/2-1} x[2n]e^{-2ink\omega} + e^{-ik\omega} \sum_{n=0}^{N/2-1} x[2n+1]e^{-2ink\omega} \right)$$

Inspection shows that if:

$$Y = FFT(x[0], x[2], x[4], ..., x[N-2])$$

and:

$$Z = FFT(x[1], x[3], x[5], ..., x[N-1])$$

then:

$$X[k] = \frac{1}{2} (Y[k] + e^{-ik\omega} Z[k]) \qquad 0 \le k < N/2$$

$$X[k] = \frac{1}{2} (Y[k - N/2] - e^{-ik\omega} Z[k - N/2]) \qquad N/2 \le k < N$$

The problem has been reduced to calculating two FFTs of size N/2 and performing N complex multiplications.

— Note ——

The bottom bit of k determines whether x[k] is in the FFT calculation for Y or for Z.

By repeating this process for *Y* and *Z*, and recursing the FFT algorithm, the next subsection is derived. This process is known as *decimation in time*.

### **Inverse FFT**

The inverse FFT, given by:

$$x = IFFT(X)$$

performs the calculation specified by the formula:

$$x[k] = \frac{1}{N} \sum_{n=0}^{N-1} X[n](\cos(nk\omega) + i\sin(nk\omega))$$

where  $\omega = 2\pi / N$  and the 1 / N scaling that multiplies the summation prevents overflow within the algorithm.

This can be simplified as given in the case of the forward FFT above.

## Table lookup

The cosine and sine values used in the forward and inverse FFT algorithms only depend on the value of *N*. If the value of *N* is fixed, the cosine and sine values required are a set of constants and a lookup table can be created. In addition, the lookup table has symmetries so that only the values between 0 and  $\pi$  / 4 radians need calculating, and all other cosine and sine values can be determined from these values.

Therefore, the FFT is implemented using a cosine and sine lookup table that must be generated and included before assembling the FFT functions. The generation of the lookup table is handled by a separate set of files contained in the arm\_fft\arm\_tgen directory. When the archive files are compiled and executed, a table is generated in ffttabls.h. The directory location for the file and the maximum number of points in the FFT, *N*, are specified at runtime.

The directory path should locate the directory for ffts.s from that of the executable creating the table, so that the header file is included when assembling ffts.s.

For example, given the following structure:

```

apps_lib\arm_fft\fft.mcp

apps_lib\arm_fft\src\ffts.s

apps_lib\arm_fft\variants\[variations]\fft.axf

apps_lib\arm_fft\fft_tgen\fft_tgen.mcp

apps_lib\arm_fft\fft_tgen\variants\[variations]\fft_tgen.axf

```

the ffttabls.h table must be in the apps\_lib\fft\src\ directory, which must be identified when executing fft\_tgen.axf. (The *variations* can be found in *Variants* on page 1-8.)

If fft\_tgen.axf is executed in apps\_lib\fft\fft\_tgen\variants\[*variations*], the directory location for the table is ..\..\src because the creation process must change directory by going back through the \fft\_tgen\variants\[*variations*] directories to apps\_lib\fft\ and then forward into the src directory.

However, if ...\fft\_tgen\variants\[*variations*]\fft\_tgen.axf is executing in apps\_lib\fft\src, the directory path for the table is empty because the directory structure has been incorporated into the execution of fft\_tgen.axf.

The number of points in the FFT must be given as the maximum number of points that the FFT can perform with each call, and therefore, the maximum number of inputs to, and outputs from, the FFT. The number of points in the FFT must be a power of two and should be set with consideration to speed and memory.

The more points in the FFT, the larger the lookup table, and hence the data size, and the slower the FFT functions perform due to cache misses. However, the more points in the FFT and the greater the number of possible input values that can be given to each call of the FFT, the greater the number of possible outputs that can be generated. The fewer the points in the FFT and the smaller the table and data size, the quicker the FFT performs, but with fewer inputs that can be processed with each FFT call.

The number of points in the FFT given here only determines the maximum number of possible inputs to the FFT functions, and not the number of inputs that must be passed to each call of the FFT.

If the directory path and/or the number of points are not given at runtime, their default values are used. The default directory path is the directory of the executable creating the table and the default maximum number of points in the FFT is 1024.

## 4.1.2 FFT optimization and conditional assembly

The following flags are defined in ffts.s and relate to FFT optimization and conditional assembly.

### OPTIMISE

This flag determines which algorithm the FFT uses. There are two separate algorithms, one optimized for size and one optimized for speed.

If the smaller but slower algorithm is required, the flag must be set to 0 (false). If the larger but highly optimized algorithm is required, this flag must be set to 1 (true). On average, the unoptimized algorithm takes approximately 1.5 times as long as the optimized version for large FFTs and twice as long for smaller FFTs.

Given that the FFT is an N-point function, the code size for the optimized algorithm is (1592 + N) / 2 bytes, including the lookup table. The read/write data size is 64 bytes, not including the input and output buffers. The unoptimized algorithm has a smaller code size of (548 + N) / 2 bytes but the same read/write data size of 64 bytes.

## FORWARD, INVERSE

The same function is used to perform a forward and inverse FFT. The direction of the FFT is determined by the FORWARD or INVERSE flags. To reduce code size, support for either the forward or inverse FFT can be enabled or disabled independently by setting the appropriate flags.

- To enable the forward FFT, set the FORWARD flag to 1. To disable the forward FFT, set it to 0.

- To enable the inverse FFT, set the INVERSE flag to 1. To disable the forward FFT, set it to 0.

If either or both flags are disabled and the FFT function is called with the direction set to an operation that is disabled, the result is undetermined.

## INPLACE, OUTPLACE

The addresses for the input and output buffers are given as arguments to the FFT functions. The FFT is *in-place* if the input buffer and output buffer reference the same block of memory. Conversely, if the input and output buffers reference different blocks of memory, the FFT is *out-of-place*.

- To permit in-place buffers, set the INPLACE flag to 1. When INPLACE is set to 0, in-place buffers are not supported.

- To permit out-of-place buffers, set the OUTPLACE flag to 1. When OUTPLACE is set to 0, out-of-place buffers are not supported.

The results are undetermined if:

- the buffers are in-place when only out-of-place buffers are allowed

- the buffers are out-of-place and only in-place buffers are allowed

- neither in-place nor out-of-place buffers are allowed.

## REALFFTS

The ffts.s file defines a REALFFT() function that can be used when the inputs to the FFT are real values.

- If this function is not required, set the REALFFTS flag to 0 (false), so that the function is not defined.

- Otherwise, set the flag to 1 (true) to define and export the function.

## 4.1.3 Hamming and Hanning windows

The Hamming and Hanning Windows are defined by the formula:

$$h[i] = in[i] \times \left( (1 - \alpha) - \alpha \cos\left(\frac{2\pi i}{N}\right) \right)$$

where:

$$\alpha = \begin{cases} 0.46 & \text{Hamming Window} \\ 0.50 & \text{Hanning Window} \end{cases}$$

## 4.1.4 Files

The files in Table 4-1 are provided with the implementation.

### Table 4-1 FFT files

| Filename   | Archive name     | Code type             | Functionality                                                   |

|------------|------------------|-----------------------|-----------------------------------------------------------------|

| ffts.s     | arm_fft          | ARM assembly language | FFT real coding, and imaginary coding and decoding              |

| ffttabls.h | arm_fft          | ARM assembly language | FFT point lookup table for FFT calculation                      |

| fftstruc.h | arm_fft          | C header              | Complex structure definition                                    |

| ffts.h     | arm_fft          | C header              | FFT function prototypes                                         |

| windowsc.c | arm_fft          | С                     | GenerateWindow(), Hamming() and Hanning() windowing functions   |

| windowsc.h | arm_fft          | C header              | Window function prototypes and constant definitions             |

| ffttgenc.c | arm_fft\arm_tgen | С                     | Code for creation of the FFT point lookup table file ffttabls.h |

| ffttgenc.h | arm_fft\arm_tgen | C header              | Constant definitions for creation of the FFT point lookup table |

## 4.2 Complex data structure

This section describes the Complex data structure required by the FFT functions. This structure is used to pass or retrieve complex data values to or from the FFT routines.

### 4.2.1 Definition

```

typedef struct Complex Complex ;

struct Complex {

int r ;

int i ;

};

```

### 4.2.2 Description

The FFT routines operate over complex data values. Each complex number consists of a 32-bit integer containing the real part, followed by a 32-bit integer containing the imaginary part. The Complex structure is used to maintain each data value with a real and imaginary part, and is eight bytes long.

# 4.3 Functions

This section describes the FFT and windowing routines. The functions are:

- Forward or inverse FFT on complex values (*FFT*)

- Forward FFT on real values (*REALFFT* on page 4-12)

- Generating coefficients for Hamming or Hanning window (*GenerateWindow* on page 4-14)

- Perform Hamming window (*HammingWindow* on page 4-15)

- Perform Hanning window (*HanningWindow* on page 4-16).

## 4.3.1 FFT

This function calculates the forward or inverse FFT for a given set of complex data values and outputs a set of complex transform coefficients to an output data buffer.

### Syntax

int FFT(Complex \*in, Complex \*out, int logN, int direction)

where:

| in        | -                                                                                                                                                                                           | er to the starting address of the input data consisting of $N$ values. The buffer is $8N$ bytes long.                                                                                                                            |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|           | the comp                                                                                                                                                                                    | In the overflow within the algorithm, the real and imaginary parts of lex input data values referenced by <i>in</i> must be sign extended antities and must be between $-32768$ and $+32767$ .                                   |  |

| out       | which mu                                                                                                                                                                                    | alized pointer to the starting address of the output data buffer<br>ast reference at least as many Complex data items as <i>in</i> references<br>a points. The <i>out</i> parameter must also be at least 8 <i>N</i> bytes long. |  |

|           |                                                                                                                                                                                             | e function returns, <i>out</i> contains a pointer to the starting address ffer that holds the <i>N</i> outputs.                                                                                                                  |  |

| logN      | is an integer that defines the base-2 logarithm of the number of complex data input values, <i>N</i> , that are referenced by <i>in</i> . <i>N</i> defines the number of points in the FFT. |                                                                                                                                                                                                                                  |  |

| direction | is a flag that indicates the direction of the FFT:                                                                                                                                          |                                                                                                                                                                                                                                  |  |

|           | 1                                                                                                                                                                                           | the forward FFT is to be performed.                                                                                                                                                                                              |  |

|           | 0                                                                                                                                                                                           | the inverse FFT is to be performed (the data is to be inverted to its original state).                                                                                                                                           |  |

## **Return Value**

- the FFT was successful and *out* points to the buffer containing valid FFT transform coefficients.

- 1 the FFT was unsuccessful because the trigonometry table is not large enough for the given size of *N*. The values in the output data buffer pointed to by *out* are unspecified.

## Usage

The number of data inputs that are referenced by *in* and the number of outputs that are returned by the FFT function can be determined from the value given by *logN*. The value defined by *logN* must be the power to which 2 is raised to give the number of inputs. That is, *logN* is the base-2 logarithmic value of N, and is equivalent to the highest bit that is set in N, such that N = (1 << logN).

N must be a power of 2. The largest value of N that can be passed to the FFT depends on the size of the trigonometry table that was used when the FFT was assembled. For the optimized version of the FFT, the smallest value of N that can be used is 16, such that *logN* is at least 4.

## Notes

The output data is scaled by a factor of 1/N to reduce the possibility of overflow during the FFT algorithm.

The input and output buffers can be in-place or out-of-place. However, if memory is slow on the host system, the FFT calculations are slightly faster when performed in-place.

### 4.3.2 REALFFT

This function calculates the forward FFT for a given set of real data values.

### Syntax

int REALFFT(int \*in, Complex \*out, int logN)

where:

| in          | is a pointer to the starting address of the input data consisting of $2N$ real values. The buffer is $8N$ bytes long.                                                                                                                                                      |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | To prevent overflow within the algorithm, the real input data values referenced by <i>in</i> must be sign extended 16-bit quantities and must be between $-32768$ and $+32767$ .                                                                                           |

| out         | is an initialized pointer to the starting address of the output data buffer, which must reference at least as many Complex data items as half the number of real input data points referenced by <i>in</i> . Therefore, <i>out</i> must be at least 8 <i>N</i> bytes long. |

|             | When the function returns, <i>out</i> contains a pointer to the starting address of the buffer that holds the $N$ outputs.                                                                                                                                                 |

| 1ogN        | is an integer that defines the base-2 logarithm of the number of real input data values referenced by <i>in</i> , divided by two. Therefore, <i>logN</i> defines half the number of points in the FFT and the number of outputs that are returned by REALFFT().            |

| Return Valu | e                                                                                                                                                                                                                                                                          |

- 0 the FFT was successful and *out* points to the buffer containing valid FFT transform coefficients.

- 1 the FFT was unsuccessful because the trigonometry table is not large enough for the given size of *N*. The values in the output data buffer pointed to by *out* are unspecified.

## Usage

If the values to be fast Fourier transformed are real values (complex numbers with a zero-value imaginary part), REALFFT() can be used instead of FFT() to perform the forward FFT and almost double the speed of the transform.

The FFT of 2*N* real values is calculated using an *N*-point complex FFT. Therefore, the size of the input buffer referenced by *in* must be at least 2*N* and filled with the real parts of:

x[0], ..., x[2N-1]

After performing the real FFT, the output buffer referenced by *out* contains the first half of the FFT transform coefficients, *N* complex values given by:

X[0], ..., X[N-1]

The second half can be calculated by symmetry because:

X[2N-k]

is the complex conjugate of:

X[k]

in the real case.

The number of data inputs that are referenced by *in* and the number of outputs that are returned by the FFT function can be determined from the value given by *logN*. The value defined by *logN* must be the power to which 2 is raised to give the number of outputs and, therefore, half the number of inputs. In other words, *logN* is the base-2 logarithmic value of N and is equivalent to the highest bit that is set in N, such that N = (1 << logN) and the number of inputs is given as 2N.

*N* must be a power of 2. The largest value of *N* that can be passed to the FFT depends on the size of the trigonometry table that was used when the FFT was assembled. In other words, for each *N* the trigonometry table must be at least of size 2N. For the optimized version of the FFT, the smallest value of *N* that can be used is 16, such that *logN* is at least 4, and therefore the minimum number of points in the real FFT is 32.

#### Notes

The input and output buffers are both 8*N* bytes and can be in-place or out-of-place. However, if memory is slow on the host system, the FFT calculations are slightly faster when performed in-place.

### 4.3.3 GenerateWindow

This function generates an array of coefficients that describe either a Hamming or Hanning window to be performed on data that is to be passed to the FFT. The array can then be multiplied by the input data pre-FFT to perform the window.

### Syntax

int \*GenerateWindow(int windowCoefficient, int nDataPoints)

where:

windowCoefficient

is the fixed-point coefficient value,  $\alpha$ , with the fixed-point between bits 13 and 14. This value determines whether the generated window coefficients are Hamming or Hanning window coefficients. The *windowCoefficient* parameter must be either 0x1d70 for a Hamming Window or 0x2000 for a Hanning Window.

### nDataPoints

is the number of points in the Hamming or Hanning Window. This is usually the number of data points to be input to the FFT.

## **Return Value**

An array of *nDataPoints* sign-extended, fixed-point windowing coefficients, with the fixed-point between bits 13 and 14, or NULL if an error occurred.

## Usage

The GenerateWindow() function should be used if the required window is to be performed on several sets of input data. Otherwise, HammingWindow() or HanningWindow() should be used.

### 4.3.4 HammingWindow

This function multiplies the input data to be passed to the FFT by the Hamming Window coefficients.

### Syntax

void HammingWindow(int outputs[], int inputs[], int nDataPoints) where: outputs is an initialized array that must reference at least nDataPoints entries. When the function returns, outputs is an array that contains nDataPoints data values, which are the result of multiplying the input data values by the Hamming Window. inputs is an array of *nDataPoints* data values to be multiplied by the Hamming Window. The values must be no more than 16-bit quantities. Otherwise, the multiplication by the Hamming Window overflows. nDataPoints is the number of data points in *inputs* and the number of entries in outputs, after performing the Hamming Window.

### Usage

The input data array and the output data array can be in-place. That is, the result of the multiplication by the Hamming Window can be returned in the same memory as the input data so that the input data is overwritten.

The HammingWindow() function should be used if the window is to be performed on the given set of input data only. If the window is to be applied to several sets of data values, each with the same number of data points, GenerateWindow() should be used instead to obtain the Hamming Window coefficients, and the multiplication should be carried out separately.

## 4.3.5 HanningWindow

This function multiplies the input data to be passed to the FFT by the Hanning Window coefficients.

### Syntax

void HanningWindow(int outputs[], int inputs[], int nDataPoints)

where:

| outputs     | is an initialized array that must reference at least <i>nDataPoints</i> entries.                                                                                                                        |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | When the function returns, <i>outputs</i> is an array that contains <i>nDataPoints</i> data values, which are the result of multiplying the input data values by the Hanning Window.                    |

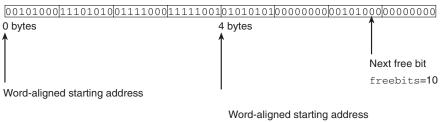

| inputs      | is an array of <i>nDataPoints</i> data values to be multiplied by the Hanning Window. The values must be no more than 16-bit quantities. Otherwise, the multiplication by the Hanning Window overflows. |