# **Fast Models**

Version 11.3

Fixed Virtual Platforms (FVP) Reference Guide

### **Fast Models**

### Fixed Virtual Platforms (FVP) Reference Guide

Copyright © 2014–2018 Arm Limited (or its affiliates). All rights reserved.

### **Release Information**

### **Document History**

| Issue   | Date             | Confidentiality  | Change                                                     |

|---------|------------------|------------------|------------------------------------------------------------|

| A       | 31 May 2014      | Non-Confidential | New document for Fast Models v9.0, from DUI0575H for v8.3. |

| В       | 30 November 2014 | Non-Confidential | Update for v9.1.                                           |

| С       | 28 February 2015 | Non-Confidential | Update for v9.2.                                           |

| D       | 31 May 2015      | Non-Confidential | Update for v9.3.                                           |

| Е       | 31 August 2015   | Non-Confidential | Update for v9.4.                                           |

| F       | 30 November 2015 | Non-Confidential | Update for v9.5.                                           |

| G       | 29 February 2016 | Non-Confidential | Update for v9.6.                                           |

| Н       | 31 May 2016      | Non-Confidential | Update for v10.0.                                          |

| I       | 31 August 2016   | Non-Confidential | Update for v10.1.                                          |

| J       | 11 November 2016 | Non-Confidential | Update for v10.2.                                          |

| K       | 17 February 2017 | Non-Confidential | Update for v10.3.                                          |

| 1100-00 | 31 May 2017      | Non-Confidential | Update for v11.0. Document numbering scheme has changed.   |

| 1101-00 | 31 August 2017   | Non-Confidential | Update for v11.1.                                          |

| 1102-00 | 17 November 2017 | Non-Confidential | Update for v11.2.                                          |

| 1103-00 | 23 February 2018 | Non-Confidential | Update for v11.3.                                          |

### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is

not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or TM are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at http://www.arm.com/company/policies/trademarks.

Copyright © 2014-2018 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

### **Product Status**

The information in this document is Final, that is for a developed product.

### Web Address

http://www.arm.com

# Contents

# Fast Models Fixed Virtual Platforms (FVP) Reference Guide

|           | Prei  | race                                         |      |

|-----------|-------|----------------------------------------------|------|

|           |       | About this book                              | 7    |

| Chapter 1 | Intro |                                              |      |

|           | 1.1   | About FVPs                                   | 1-10 |

| Chapter 2 | Gett  | ting Started with Fixed Virtual Platforms    |      |

|           | 2.1   | Loading and running an application on an FVP | 2-12 |

|           | 2.2   | Configuring the model                        | 2-13 |

|           | 2.3   | FVP debug                                    | 2-14 |

|           | 2.4   | Using the VE CLCD window                     | 2-15 |

|           | 2.5   | Ethernet with VE FVPs                        | 2-18 |

|           | 2.6   | Using a terminal with a system model         | 2-20 |

|           | 2.7   | Virtio P9 device component                   | 2-22 |

| Chapter 3 | Prog  | gramming Reference for Base FVPs             |      |

|           | 3.1   | Base - about                                 | 3-24 |

|           | 3.2   | Base Platform RevC changes                   | 3-25 |

|           | 3.3   | BasePlatformPCIRevC component                | 3-27 |

|           | 3.4   | Base - memory                                | 3-29 |

|           | 3.5   | Base - interrupt assignments                 | 3-33 |

|           | 3.6   | Base - clocks                                | 3-36 |

|           |       |                                              |      |

|           | 3.7  | Base - parameters                                        | 3-37 |

|-----------|------|----------------------------------------------------------|------|

|           | 3.8  | Base - components                                        | 3-38 |

|           | 3.9  | Base - differences between the AEMv8-A FVP and core FVPs | 3-45 |

|           | 3.10 | Base - VE compatibility                                  | 3-46 |

|           | 3.11 | Base - unsupported VE features                           | 3-48 |

| Chapter 4 | Prog | gramming Reference for MPS2 FVPs                         |      |

|           | 4.1  | MPS2 - about                                             | 4-50 |

|           | 4.2  | MPS2 platform types                                      | 4-51 |

|           | 4.3  | MPS2 - memory maps                                       | 4-52 |

|           | 4.4  | MPS2 - interrupt assignments                             | 4-58 |

|           | 4.5  | MPS2 - differences between models and hardware           | 4-59 |

| Chapter 5 | Prog | gramming Reference for VE FVPs                           |      |

|           | 5.1  | VE - about                                               | 5-61 |

|           | 5.2  | Memory maps for VE FVPs                                  | 5-63 |

|           | 5.3  | Interrupt maps for VE FVPs                               | 5-67 |

|           | 5.4  | VE parameters                                            | 5-69 |

|           | 5.5  | VE - components                                          | 5-71 |

|           | 5.6  | Differences between the VE hardware and the system model | 5-77 |

# Preface This preface introduces the Fast Models Fixed Virtual Platforms (FVP) Reference Guide. It contains the following: • About this book on page 7.

### About this book

Arm® Fixed Virtual Platform Reference. This manual introduces the Fixed Virtual Platforms, and describes how you can use them with other tools.

### Using this book

This book is organized into the following chapters:

### **Chapter 1 Introduction**

This chapter introduces the document.

### Chapter 2 Getting Started with Fixed Virtual Platforms

This chapter describes how to use FVPs.

### Chapter 3 Programming Reference for Base FVPs

This chapter describes the memory map and the parameters for the peripheral and system component models.

### Chapter 4 Programming Reference for MPS2 FVPs

This chapter describes the model of the hardware platform.

### Chapter 5 Programming Reference for VE FVPs

This chapter describes the memory map and the parameters for the peripheral and system component models.

### **Glossary**

The Arm® Glossary is a list of terms used in Arm documentation, together with definitions for those terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

See the Arm® Glossary for more information.

### Typographic conventions

italic

Introduces special terminology, denotes cross-references, and citations.

### bold

Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.

### monospace

Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.

### <u>mono</u>space

Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.

### monospace italic

Denotes arguments to monospace text where the argument is to be replaced by a specific value.

### monospace bold

Denotes language keywords when used outside example code.

### <and>

Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example:

```

MRC p15, 0, <Rd>, <CRn>, <CRm>, <Opcode 2>

```

### SMALL CAPITALS

Used in body text for a few terms that have specific technical meanings, that are defined in the *Arm® Glossary*. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE.

### **Feedback**

### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

### Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

• The title Fast Models Fixed Virtual Platforms (FVP) Reference Guide.

Arm also welcomes general suggestions for additions and improvements.

- The number 100966 1103 00 en.

- If applicable, the page number(s) to which your comments refer.

- A concise explanation of your comments.

| Note                                                                                                |

|-----------------------------------------------------------------------------------------------------|

| Arm tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the |

| represented document when used with any other PDF reader.                                           |

### Other information

- Arm® Developer.

- Arm® Information Center.

- Arm® Technical Support Knowledge Articles.

- Technical Support.

- Arm® Glossary.

# Chapter 1 **Introduction**

This chapter introduces the document.

It contains the following section:

• 1.1 About FVPs on page 1-10.

### 1.1 About FVPs

Fixed Virtual Platforms (FVPs), or system models, enable development of software without the requirement for actual hardware.

FVPs provide *Programmer's View* (PV) models of processors and devices. The functional behavior of a model is equivalent to real hardware. PV models sacrifice absolute timing accuracy to achieve fast simulated execution speed. This means that you can use PV models for confirming software functionality, but you must not rely on the accuracy of cycle counts, low-level component interactions, or other hardware-specific behavior.

Arm supplies some PV models, Fast Models, as *Component Architecture Debug Interface* (CADI) shared libraries. Any environment compatible with the CADI API can load them, like Model Debugger, Model Shell, and System Canvas.

FVPs are non-customizable PV models suitable for software development, which Arm supplies as executable files. Arm provides different types of FVP, including the following:

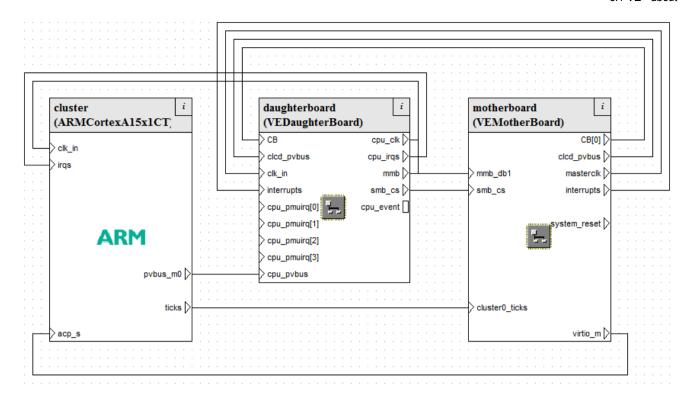

### VE FVPs

These are models of Arm Versatile™ Express development boards.

### **Base FVPs**

These are models of the Army8-A and Army8-R Base platform.

### **MPS2 FVPs**

These are models of the Arm MPS2 and Arm MPS2+ platforms, for Cortex®-M series processors.

# Chapter 2 **Getting Started with Fixed Virtual Platforms**

This chapter describes how to use FVPs.

It contains the following sections:

- 2.1 Loading and running an application on an FVP on page 2-12.

- 2.2 Configuring the model on page 2-13.

- 2.3 FVP debug on page 2-14.

- 2.4 Using the VE CLCD window on page 2-15.

- 2.5 Ethernet with VE FVPs on page 2-18.

- 2.6 Using a terminal with a system model on page 2-20.

- 2.7 Virtio P9 device component on page 2-22.

### 2.1 Loading and running an application on an FVP

There are different ways to run an application on an FVP, for example from a command prompt, or from Model Debugger, or DS-5.

To run an FVP from the command prompt, change to the directory where your model is located. At the command prompt, enter the model name followed by the model options. To see all available options, use the --help option. The following options are commonly used when running an application on an FVP:

### -a filename.axf

Specifies the application to load. The file can be in one of the following formats, or in gzip-compressed versions of them:

- ELF

- · Motorola S-Record.

- Intel-Hex.

- Verilog-Hex, in the format:

```

@<address_in_hex> <byte_in_hex>

```

### --data filename.bin@address

Loads binary data into memory at the address you specify.

### -C instance.parameter=value

Sets a single model parameter. Parameters are specified as a path that separates the instance names and the parameters using dots. For example, -C bp.flashloader@.fname=fip.bin loads a program into flash. To list all the available parameters, with their type, default value, and description, invoke the model with the --list-params, or -1 option. To set multiple parameters at the same time, use the -f option instead.

### -f config\_file.txt

Specifies the name of a plain text configuration file. Configuration files simplify managing multiple model parameters. You can set the same parameters using this option as with the -c option.

-S

Starts a CADI debug server. This option allows a CADI-enabled debugger, such as Model Debugger or DS-5 Debugger, to connect to the running model. The model waits for the debugger to connect before starting.

For example:

```

models_directory/FVP_Base_Cortex-A57x1 -a __image.axf -f params.txt

```

You can also launch and debug bare metal and Linux applications on an FVP from Model Debugger or DS-5 Debugger. These debuggers use CADI to communicate with the FVP, so you must use the -5 option when launching the FVP.

Starting the model opens the FVP CLCD display, which shows the contents of the simulated color LCD framebuffer.

### Related information

Arm DS-5 Debugger User Guide. Model Debugger for Fast Models User Guide.

### 2.2 Configuring the model

When you start the model from the command line, you can configure it using either:

- One or more -c command-line arguments.

- A configuration file and the -f command-line argument.

Each -c command-line argument or line in the configuration file must contain:

- The name of the component instance.

- The parameter to modify.

- · Its value.

Use the following format:

instance.parameter=value

The instance can be a hierarchical path, with each level separated by a dot "." character.

\_\_\_\_\_ Note \_\_\_\_\_

- Comment lines in the configuration file begin with a # character.

- You can set Boolean values using either true or false, or 1 or 0.

You can generate a configuration file with all parameters set to default values by redirecting the output from the --list-params option into a new file, for example:

```

FVP_Base_AEMv8A.exe --list-params > params.txt

```

### Example 2-1 Sample lines in a configuration file

```

# Disable semihosting using true/false syntax

coretile.cluster0.cpu0.semihosting-enable=false

#

# Enable VFP at reset using 1/0 syntax

coretile.cluster0.cpu0.vfp-enable_at_reset=1

#

# Set the baud rate for UART 0

motherboard.pl011_uart0.baud_rate=0x4800

```

### 2.3 FVP debug

This section describes how to debug an FVP.

### **FVP** debug options

To debug an FVP, you can either:

- Run the FVP from within a CADI-enabled debugger.

- Start the FVP with the -s command-line argument and then connect a CADI-enabled debugger to it.

For information about using your debugger in these ways, see your debugger documentation.

### **Semihosting support**

Semihosting enables code running on a platform model to directly access the I/O facilities on a host computer. Examples of these facilities include console I/O and file I/O.

The simulator handles semihosting by intercepting HLT 0xF000, SVC 0x123456, or SVC 0xAB, depending on whether the processor is in A64, A32 or T32 state. It handles all other HLTs and SVCs as normal.

If the operating system does not use HLT 0xF000, SVC 0x123456, or SVC 0xAB for its own purposes, it is not necessary to disable semihosting support to boot an operating system.

To temporarily or permanently disable semihosting support for a current debug connection, see your debugger documentation.

### Related information

Arm Compiler Software Development Guide.

### 2.4 Using the VE CLCD window

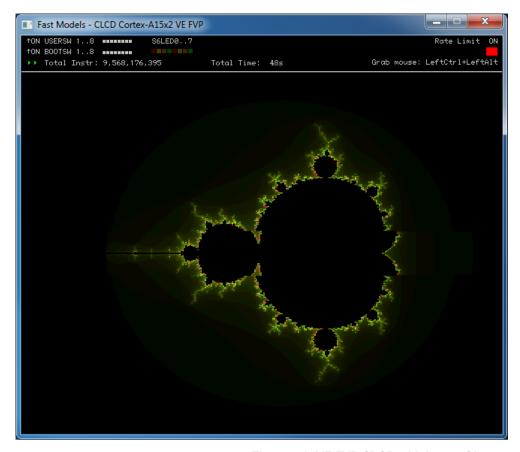

When an FVP starts, the FVP CLCD window opens, representing the contents of the simulated color LCD framebuffer. It automatically resizes to match the horizontal and vertical resolution that are set in the CLCD peripheral registers.

Figure 2-1 CLCD window in its default state at startup

The top section of the CLCD window displays the status information.

### **USERSW**

Eight white boxes show the state of the VE User DIP switches:

These represent switch S6 on the VE hardware, USERSW[8:1], which is mapped to bits [7:0] of the SYS SW register at address 0x1C010004.

The switches are in the off position by default. To change its state, click in the area above or below a white box.

### **BOOTSW**

Eight white boxes show the state of the VE Boot DIP switches.

These represent switch S8 on the VE hardware, BOOTSEL[8:1], which is mapped to bits [15:8] of the SYS SW register at address 0x1C010004.

The switches are in the off position by default.

Arm recommends that you configure the Boot DIP switches using the boot\_switch model parameter instead of using the CLCD interface. Changing Boot DIP switch positions while the model is running can result in unpredictable behavior.

### **S6LED**

Eight colored boxes indicate the state of the VE User LEDs.

These represent LEDs D[21:14] on the VE hardware, which are mapped to bits [7:0] of the SYS\_LED register at address 0x1C010008. The boxes correspond to the red/yellow/green LEDs on the VE hardware.

### **Total Instr**

A counter showing the total number of instructions executed.

Because the FVP models provide a *Programmer's View* (PV) of the system, the CLCD displays total instructions rather than total processor cycles. Timing might differ substantially from the hardware because:

- Bus fabric is simplified.

- Memory latencies are minimized.

- Cycle approximate processor and peripheral models are used.

In general, bus transaction timing is consistent with the hardware, but the timing of operations within the model is not accurate.

### **Total Time**

A counter showing the total elapsed time, in seconds.

This time is wall clock time, not simulated time.

### **Rate Limit**

A feature that disables or enables fast simulation.

Because the system model is highly optimized, your code might run faster than it would on real hardware. This effect might cause timing issues.

Rate Limit is enabled by default. Simulation time is restricted so that it more closely matches real time.

To disable or enable Rate Limit, click the square button. When you disable Rate Limit, the text changes from ON to OFF and the colored box becomes darker. You can configure this option when instantiating the model with the rate limit-enable visualization component parameter.

When you click the **Total Instr** or **Total Time** items in the CLCD, the display changes to show **Instr/sec** (instructions per second) and **Perf Index** (performance index).

Figure 2-2 CLCD window with Rate Limit ON, showing Instr/sec and Perf Index

You can click the items again to toggle between the original and alternative displays.

### Instr/sec

The number of instructions that execute per second of wall clock time.

### **Perf Index**

The ratio of real time to simulation time. The larger the ratio, the faster the simulation runs. If you enable the Rate Limit feature, the Perf Index approaches unity.

You can reset the simulation counters by resetting the model.

The VE FVP CLCD displays the core run state for each core with a colored icon. The icons are to the left of the **Total Instr** (or **Inst/sec**) item. They appear when you start the simulation.

Figure 2-3 Core run state icons for a quad core model

Table 2-1 Core run state icon descriptions

| Icon | State label | Description                                                          |

|------|-------------|----------------------------------------------------------------------|

| ?    | UNKNOWN     | Run status unknown, that is, simulation has not started.             |

| H    | RUNNING     | Core running, is not idle, and is executing instructions.            |

| •    | HALTED      | External halt signal asserted.                                       |

| E    | STANDBY_WFE | Last instruction executed was WFE and standby mode has been entered. |

| I    | STANDBY_WFI | Last instruction executed was WFI and standby mode has been entered. |

|      | IN_RESET    | External reset signal asserted.                                      |

|      | DORMANT     | Partial core power down.                                             |

|      | SHUTDOWN    | Complete core power down.                                            |

If the CLCD window has focus:

- Any keyboard input is translated to PS/2 keyboard data.

- Any mouse activity over the window is translated into PS/2 relative mouse motion data. The data is then streamed to the KMI peripheral model FIFOs.

| Note                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The simulator only sends relative mouse motion events to the model. As a result, the host mouse pointer does not necessarily align with the target OS mouse pointer. |

|                                                                                                                                                                      |

You can hide the host mouse pointer by pressing the **left Ctrl**+**left Alt** keys. Press the keys again to redisplay the host mouse pointer. Only the **left Ctrl** key is operational. The **right Ctrl** key does not have the same effect.

If you prefer to use a different key, configure it with the  $trap\_key$  visualization component parameter.

### Related references

VEVisualisation - parameters on page 5-73.

### 2.5 Ethernet with VE FVPs

This section describes how to use Ethernet with VE FVPs.

### Using Ethernet with VE FVPs

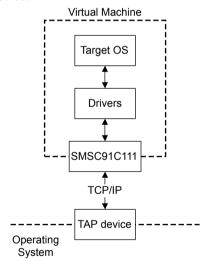

The VE FVPs have a virtual Ethernet component. This component is a model of the SMSC 91C111 Ethernet controller, and uses a TAP device to communicate with the network. By default, the Ethernet component is disabled.

### Host requirements

Before you can use the Ethernet capability of VE FVPs, set up your host computer.

### **Target requirements**

This section describes the target requirements.

### Target requirements - about

The VE FVPs include a software implementation of the SMSC 91C111 Ethernet controller. Your target OS must therefore include a driver for this specific device. To use the SMSC chip, configure the kernel. Linux supports the SMSC 91C111.

The configurable SMSC 91C111 component parameters are:

- enabled.

- mac address.

- promiscuous.

### enabled

When the device is disabled, the kernel cannot detect the device.

Figure 2-4 Model networking structure block diagram

To perform read and write operations on the TAP device, configure a HostBridge component. The HostBridge component is a virtual *Programmer's View* (PV) model. It acts as a networking gateway to exchange Ethernet packets with the TAP device on the host, and to forward packets to NIC models.

### mac address

There are two options for the mac\_address parameter.

If a MAC address is not specified, when the simulator is run it takes the default MAC address, which is randomly generated. This random generation provides some degree of MAC address uniqueness when running models on multiple hosts on a local network.

### promiscuous

The Ethernet component starts in promiscuous mode by default. In this mode, it receives all network traffic, even any not addressed to the device. Use this mode if you are using a single network device for multiple MAC addresses. Use this mode if, for example, you share the network card between your host OS and the VE FVP Ethernet component.

By default, the Ethernet device on the VE FVP has a randomly generated MAC address and starts in promiscuous mode.

### 2.6 Using a terminal with a system model

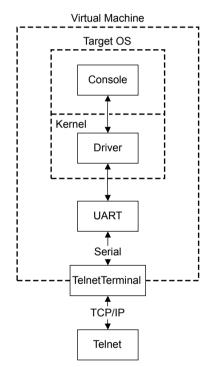

The Terminal component is a virtual component that enables UART data to be transferred between a TCP/IP socket on the host and a serial port on the target.

To use the Terminal component with a Microsoft Windows 7 client, you must first install Telnet. The Telnet application is not installed on Microsoft Windows 7 by default.

Download the application by following the instructions on the Microsoft web site. Search for "Windows 7 Telnet" to find the Telnet FAQ page. To install Telnet:

- 1. Select **Start > Control Panel > Programs and Features** to open a window that enables you to uninstall or change programs.

- 2. Select **Turn Windows features on or off** on the left side of the bar. This opens the Microsoft Windows Features dialog. Select the **Telnet Client** check box.

- 3. Click **OK**. The installation of Telnet might take several minutes to complete.

The following figure shows a block diagram of one possible relationship between the target and host through the Terminal component. The TelnetTerminal block is what you configure when you define Terminal component parameters. The Virtual Machine is your FVP.

Figure 2-5 Terminal block diagram

On the target side, the console process that is invoked by your target OS relies on a suitable driver being present. Such drivers are normally part of the OS kernel. The driver passes serial data through a UART. The data is forwarded to the TelnetTerminal component, which exposes a TCP/IP port to the world outside of the FVP. This port can be connected to by, for example, a Telnet process on the host.

By default, the FVP starts four telnet Terminals when the model is initialized. You can change the startup behavior for each of the four Terminals by modifying the corresponding component parameters.

If the Terminal connection is broken, for example by closing a client telnet session, the port is re-opened on the host. This might have a different port number if the original one is no longer available. Before the first data access, you can connect a client of your choice to the network socket. If there is no existing

connection when the first data access is made, and the start\_telnet parameter is true, a host telnet session is started automatically.

The port number of a particular Terminal instance can be defined when the FVP starts. The actual value of the port that is used by each Terminal is declared when it starts or restarts, and might not be the value that you specified if the port is already in use. If you are using Model Shell, the port numbers are displayed in the host window in which you started the model.

You can start the Terminal component in either telnet mode or raw mode.

### **Telnet mode**

In telnet mode, the Terminal component supports a subset of the RFC 854 protocol. This means that the Terminal participates in negotiations between the host and client concerning what is and is not supported, but flow control is not implemented.

### Raw mode

Raw mode enables the byte stream to pass unmodified between the host and the target. This means that the Terminal component does not participate in initial capability negotiations between the host and client. It acts as a TCP/IP port. You can use this feature to directly connect to your target through the Terminal component.

### 2.7 Virtio P9 device component

The VirtioP9Device component is included in Base, BaseR, and A-profile VE platforms. It implements a subset of the Plan 9 file protocol over a virtio transport. It enables accessing a directory on the host's filesystem within Linux, or another operating system that implements the protocol, running on a platform model.

Take the following steps to use this component:

- Use a version of Linux that supports v9fs over virtio and virtio-mmio devices.

- Update the device tree to include the VirtioP9Device component, or specify it on the kernel command-line, as shown below. The address range for both VE and Base platforms is 0x1C140000-0x1C14FFFF. The interrupt number is 43, or IRQ 75, for both VE and Base platforms.

- Set the following parameter to the directory on the host that you want to mount in the model:

VE:

motherboard.virtiop9device.root\_path

Base:

bp.virtiop9device.root path

• On Linux, mount the host directory by using the following command in the model:

```

$ mount -t 9p -o trans=virtio,version=9p2000.L FM <mount point>

```

Example kernel command-line argument:

virtio\_mmio.device=0x10000@0x1c140000:75 Example entries for DTS files:

• Add this entry next to the corresponding virtio\_block entry:

```

virtio_p9@0140000 {

compatible = "virtio,mmio";

reg = <0x140000 0x1000>;

interrupts = <0x2b>;

};

```

• Add this entry to the interrupt map:

```

<0 0 43 &gic 0 43 4>;

```

## Chapter 3

# **Programming Reference for Base FVPs**

This chapter describes the memory map and the parameters for the peripheral and system component models.

### It contains the following sections:

- *3.1 Base about* on page 3-24.

- 3.2 Base Platform RevC changes on page 3-25.

- 3.3 BasePlatformPCIRevC component on page 3-27.

- *3.4 Base memory* on page 3-29.

- 3.5 Base interrupt assignments on page 3-33.

- 3.6 Base clocks on page 3-36.

- 3.7 Base parameters on page 3-37.

- 3.8 Base components on page 3-38.

- 3.9 Base differences between the AEMv8-A FVP and core FVPs on page 3-45.

- 3.10 Base VE compatibility on page 3-46.

- 3.11 Base unsupported VE features on page 3-48.

### 3.1 Base - about

The Base Platform system model allows early development, distribution, and demonstration of software deliverables. A range of Base FVPs are supplied as standalone products and as examples in Fast Models.

The standard peripheral set enables software development and porting. The platform is an evolution of the VE *Fixed Virtual Platforms* (FVPs), based on the Arm Versatile Express (VE) hardware development platform.

The Base Platform system model provides:

- Two configurable clusters of up to four core models that implement:

- AArch64 at all exception levels.

- Configurable AArch32 support at all exception levels.

- Configurable support for little and big endian at all exception levels.

- Generic timers.

- Self-hosted debug.

- CADI debug.

- GICv3 memory-mapped processor interfaces and distributor.

- Peripherals for multimedia or networking environments.

- Four PL011 UARTs.

- A CoreLink™ CCI-400 Cache Coherent Interconnect.

- Architectural GICv3 model.

- High Definition LCD Display Controller, 1920×1080 resolution at 60fps, with single I2S and four stereo channels.

- 64MB NOR flash and board peripherals.

- CoreLink TZC-400 TrustZone® Address Space Controller.

To run FVP\_Base\_AEMv8A-AEMv8A-MMU500+DMA330\* models, reconfigure the DMAC or SMMU ranges because the default ranges for these components overlap.

### 3.2 Base Platform RevC changes

The Base Platform RevC includes the following changes from the previous revision.

- It includes a PCIe config region and two PCIe memory regions. See the memory map for details.

- It includes a CoreLink CCI-550 Cache Coherent Interconnect.

- It includes an SMMUv3 AEM. This is an architectural model that implements the SMMUv3.0 and SMMUv3.1 architectures. These architectures are for I/O virtualization of devices. The SMMU is placed so that accesses to memory by PCI devices acting as bus masters are affected by it.

The SMMU has the following features:

- Memory that is mapped to the range 0x2B400000-0x2B4FFFFF.

- Interrupts with IRQ IDs in the range 103-111.

- The event output pin of the SMMU is passed to the clusters.

- The downstream ports of the SMMU attach to the coherent bus infrastructure and so are coherent with the core clusters. All cores and the SMMU are in the same shareability domain. There is no distinction between the inner and outer shareability domains.

- The parameters of the SMMU determine its capabilities and have default values which can be overwritten if necessary.

- The SMMU is configured to only accept 16-bit StreamIDs and there is a 1:1 correspondence between RequestorID and StreamID.

- By default, the SMMU uses DeviceID 0x10000 to identify itself to the GIC (pci.pci\_smmuv3.mmu\_ssmu\_msi\_device\_id).

The parameter gic\_distributor.ITS-device-bits is set to 17 by default to support the 17-bit DeviceIDs.

The SMMU has the following limitations:

- It does not support RAS.

- The PMU has limited functionality. Only a subset of the architecturally mandatory events are supported, as indicated by the SMMU\_PMCG\_CEIDØ fields. The PMU is intended for demonstration purposes only and for driver development.

- Two PCIe virtio devices are above the SMMU. By default they are configured to be device 0 and 2 on bus 0.

- The PCIe devices use a DeviceID that is the same as their RequestorID (BDF).

- Legacy PCI interrupts:

- Each PCI device is hardwired to use INTA, with a value of 1 in the interrupt\_pin register. This is required by the PCI specification for single-function devices.

- The interrupts in the PCI host bridge are mapped according to section 2.2.6 of the PCI Local Bus Specification Revision 3.0, using the following formula, where the values for DeviceInterrupt are INTA = 0, INTB = 1, INTC = 2, INTD = 3:

```

BridgeInterrupt = (Device + DeviceInterrupt) % 4

```

This formula produces the following mappings:

| BridgeInterrupt ID | DeviceInterrupt |

|--------------------|-----------------|

| 200                | INTA            |

| 201                | INTB            |

| 202                | INTC            |

| 203                | INTD            |

| 207                | SERR            |

| • | The model optionally implements MSI-X, depending on whether a parameter is set. If this parameter is set, an MSI-X capability is advertised as a PCI capability.                                                          |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Note                                                                                                                                                                                                                      |

|   | The virtio specification is not fully compliant with the PCI specification and the virtio block device cannot be used in a pure-polling mode where MSI-X is always masked and only polling the pending bit array is used. |

|   |                                                                                                                                                                                                                           |

|   | The MSIs produced by the models, when directed to the GIC, have their payload rewritten to carry the DeviceID of the originating device to the GIC.                                                                       |

• The processor models implement architecture version v8.0, which does not support the Statistical Profiling Extension (SPE). To include SPE, add parameter cluster@.has\_arm\_v8-3=1, or similar, to the command line.

### Related references

*3.4.2 Base - memory map* on page 3-29.

3.5 Base - interrupt assignments on page 3-33.

### 3.3 BasePlatformPCIRevC component

This component is an integrated PCIe subsystem which forms part of the Base Platform RevC. It incorporates an SMMUv3, a PCIe, and two PCI devices which wrap a pair of virtio PCI block devices. This model is written in LISA+

### About BasePlatformPCIRevC

- You can include this component in a platform model, but Arm does not support using its subcomponents to create your own PCIe platform.

- The PCIe is not an implementation of any specific IP, but a functional, and limited, implementation of the PCIe standard.

BasePlatformPCIRevC is composed of the following model components:

```

pci.pvbus2pci

```

The bridge from the Programmer's View bus to the PCI bus.

pci.pcidevice<n>

A wrapper around the underlying virtio block device. There are two block devices in the system, 0 and 1.

pci.pcivirtioblockdevice<n>

The instances of the virtio block device component.

Some interesting options are:

• If the following options are set to non-zero values, they print messages about the operation of the bridge. The higher the value, the more verbose the component is:

```

pci.pvbus2pci.diagnostics=0x0 # (int) default = '0x0': Diagnostics level: [0x0..0x4]

pci.pcidevice<N>.diagnostics=0x0 # (int) default = '0x0': Diagnostics level: [0x0..0x4]

```

• Each PCI device uses three BARs; one for config space, one for the MSI-X table structure and one for the MSI-X Pending Bit Array. Each of these can be configured to be 32 bits or 64 bits wide.

The Bus and Device number can be configured for each PCI device. If the device advertises MSI-X, support can be configured.

```

pci.pcidevice<N>.bus=0x0  # (int ) default = '0x0' : Bus number for this device : [0x0..0xFF]

pci.pcidevice<N>.device=0x0  # (int ) default = '0x0' : Device number on this bus : [0x0..0x1F]

pci.pcidevice<N>.bar0_64bit=0  # (bool) default = '0' : If BAR 0 is 64 bits wide, if region size is nonzero

pci.pcidevice<N>.msix_support=0  # (bool) default = '0' : Enable device support for MSI-X

pci.pcidevice<N>.bar2_64bit=0  # (bool) default = '0' : If BAR 2 is 64 bits wide, if region size is nonzero

pci.pcidevice<N>.bar4_64bit=0  # (bool) default = '0' : If BAR 4 is 64 bits wide, if region size is nonzero

```

• The following option configures the image file that the virtio block device exposes:

```

pci.pcivirtioblockdevice<N>.image_path="" # (string) default = '' : image file path

```

• There are two PVBusLoggers in the pvbus2pci component. One is in front of the Configuration space and one is in front of the Device space:

```

FVP_Base_AEMv8A_AEMv8A-PCI.pci.pvbus2pci.devicelogger

FVP_Base_AEMv8A_AEMv8A-PCI.pci.pvbus2pci.cfglogger

```

There is one PVBusLogger in the pcidevice component. This reports on DMA accesses by the PCI device:

```

FVP_Base_AEMv8A_AEMv8A-PCI.pci.pcidevice0.dmalogger

```

• There is a PVBusLogger downstream of the SMMU. This reports on the transactions after they have been transformed by the SMMU:

```

{\tt FVP\_Base\_AEMv8A\_AEMv8A\_PCI.pci.smmulogger}

```

For example, you can see all accesses to device space by adding the following options to the command line:

--plugin GenericTrace.so

-C TRACE.GenericTrace.trace-sources="FVP\_Base\_AEMv8A\_AEMv8A-PCI.pci.pvbus2pci.devicelogger.\*"

### Table 3-1 BasePlatformPCIRevC ports

| Name                | Protocol    | Туре   | Description                                                                                   |

|---------------------|-------------|--------|-----------------------------------------------------------------------------------------------|

| pvbus_address_map_s | PVBus       | Slave  | Input port to service transactions based on the PVBus protocol.                               |

| pvbus_address_map_m | PVBus       | Master | Output port to send out PVBus transactions that are not handled by this component.            |

| system_reset        | Signal      | Slave  | Input port to handle reset signals. It is used to reset the internal state of this component. |

| sev_out             | Signal      | Peer   | Port to send out a notification of the occurrence of an event as sg::Signal to a peer.        |

| interrupts[224]     | Signal      | Master | Array of output ports of type sg::Signal to send out interrupts generated by this component.  |

| pvbus_pci_dma_m     | PVBus       | Master | Output port to send out any DMA (of PVBus protocol) accesses originating from this component. |

| clk_in              | ClockSignal | Slave  | Input port to connect to a ClockSignal provider.                                              |

### Table 3-2 BasePlatformPCIRevC parameters

| Name                              | Туре     | Allowed values       | Default value | Description                                                                                                                                                                                    |

|-----------------------------------|----------|----------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ITS0-base                         | uint64_t | 0-0xFFFFffffFFFFffff | 0x2f020000    | The ITS0 Base address.                                                                                                                                                                         |

| pci_smmuv3.mmu.SMMU_IDR1          | uint32_t | 0-0xFFFFffff         | 0xe739d10     | SMMU_IDR1.                                                                                                                                                                                     |

| pci_smmuv3.mmu.smmu_msi_device_id | uint32_t | 0-0xfffffff          | 0x10000       | When appropriately enabled, assume that MSIs that are generated by the SMMU are presented to the GIC with this DeviceID.  See parameter  msi_attribute_transform and  enable_device_id_checks. |

### Related information

SMMUv3AEM component. VirtioBlockDevice component.

### 3.4 Base - memory

This section describes the memory of the Base Platform.

This section contains the following subsections:

- 3.4.1 Base secure memory on page 3-29.

- 3.4.2 Base memory map on page 3-29.

- 3.4.3 Base DRAM on page 3-32.

### 3.4.1 Base - secure memory

Enable security checking on memory transactions by the TZC-400 by using the bp.secure\_memory parameter.

Table 3-3 Secure and Non-secure access permissions

| Security | bp.secure_memory=false                  | bp.secure_memory=true                                 |  |

|----------|-----------------------------------------|-------------------------------------------------------|--|

| S        | Secure and Non-secure access permitted. | Secure access is permitted, Non-secure access aborts. |  |

| S/NS     | Secure and Non-secure access permitted. | Secure and Non-secure access permitted.               |  |

| P        | Secure and Non-secure access permitted. | Access conditions are programmable by the TZC-400.    |  |

——— Note ———— The default state of the TZC-400 is to abort all accesses, even from Secure state.

Table 3-4 NSAIDs and filters that masters present to the TZC-400

| Component | NSAIDa | Filter |

|-----------|--------|--------|

| Cluster 0 | 9      | 0      |

| Cluster 1 | 9      | 0      |

| VirtIO    | 8      | 0      |

| HDLCD0    | 2      | 2      |

| CLCD      | 1      | 2      |

### 3.4.2 Base - memory map

The basis of this map is the Versatile Express RS2 memory map with extensions.

Table 3-5 Base Platform memory map

| Peripheral                                         | Start address  | Size  | End address    | Security |

|----------------------------------------------------|----------------|-------|----------------|----------|

| Trusted Boot ROM, secure flash, IntelStrataFlashJ3 | 0×00_0000_0000 | 64MB  | 0x00_03FF_FFFF | S        |

| Trusted SRAM                                       | 0×00_0400_0000 | 256KB | 0x00_0403_FFFF | S        |

| Trusted DRAM                                       | 0x00_0600_0000 | 32MB  | 0x00_07FF_FFFF | S        |

| NOR flash, flash0, IntelStrataFlashJ3              | 0×00_0800_0000 | 64MB  | 0x00_0BFF_FFFF | S/NS     |

| NOR flash, flash1, IntelStrataFlashJ3              | 0×00_0C00_0000 | 64MB  | 0x00_0FFF_FFFF | S/NS     |

| PSRAM <sup>b</sup>                                 | 0×00_1400_0000 | 64MB  | 0x00_17FF_FFFF | S/NS     |

a Non-Secure Access IDentity.

Table 3-5 Base Platform memory map (continued)

| Peripheral                                  | Start address  | Size  | End address    | Security |

|---------------------------------------------|----------------|-------|----------------|----------|

| VRAM                                        | 0×00_1800_0000 | 32MB  | 0x00_19FF_FFFF | S/NS     |

| Ethernet, SMSC 91C111                       | 0×00_1A00_0000 | 16MB  | 0x00_1AFF_FFFF | S/NS     |

| USB, unimplemented                          | 0×00_1B00_0000 | 16MB  | 0x00_1BFF_FFFF | S/NS     |

| VE System Registers                         | 0×00_1C01_0000 | 64KB  | 0x00_1C01_FFFF | S/NS     |

| System Controller, SP810                    | 0×00_1C02_0000 | 64KB  | 0x00_1C02_FFFF | S/NS     |

| AACI, PL041                                 | 0x00_1C04_0000 | 64KB  | 0x00_1C04_FFFF | S/NS     |

| MCI, PL180                                  | 0x00_1C05_0000 | 64KB  | 0x00_1C05_FFFF | S/NS     |

| KMI - Keyboard, PL050                       | 0x00_1C06_0000 | 64KB  | 0x00_1C06_FFFF | S/NS     |

| KMI - Mouse, PL050                          | 0×00_1C07_0000 | 64KB  | 0x00_1C07_FFFF | S/NS     |

| UARTO, PL011                                | 0x00_1C09_0000 | 64KB  | 0x00_1C09_FFFF | S/NS     |

| UART1, PL011                                | 0x00_1C0A_0000 | 64KB  | 0x00_1C0A_FFFF | S/NS     |

| UART2, PL011                                | 0x00_1C0B_0000 | 64KB  | 0x00_1C0B_FFFF | S/NS     |

| UART3, PL011                                | 0×00_1C0C_0000 | 64KB  | 0x00_1C0C_FFFF | S/NS     |

| Watchdog, SP805                             | 0x00_1C0F_0000 | 64KB  | 0x00_1C0F_FFFF | S/NS     |

| Base Platform Power Controller              | 0×00_1C10_0000 | 64KB  | 0x00_1C10_FFFF | S/NS     |

| Dual-Timer 0, SP804                         | 0×00_1C11_0000 | 64KB  | 0x00_1C11_FFFF | S/NS     |

| Dual-Timer 1, SP804                         | 0×00_1C12_0000 | 64KB  | 0x00_1C12_FFFF | S/NS     |

| Virtio block device                         | 0x00_1C13_0000 | 64KB  | 0x00_1C13_FFFF | S/NS     |

| Virtio Plan 9 device                        | 0x00_1C14_0000 | 64KB  | 0x00_1C14_FFFF | S/NS     |

| Virtio net device                           | 0x00_1C15_0000 | 64KB  | 0x00_1C15_FFFF | S/NS     |

| Real-time Clock, PL031                      | 0×00_1C17_0000 | 64KB  | 0x00_1C17_FFFF | S/NS     |

| CF Card, unimplemented                      | 0×00_1C1A_0000 | 64KB  | 0x00_1C1A_FFFF | S/NS     |

| Color LCD Controller, PL111                 | 0x00_1C1F_0000 | 64KB  | 0x00_1C1F_FFFF | S/NS     |

| Non-trusted ROM, nontrustedrom              | 0x00_1F00_0000 | 4KB   | 0x00_1F00_0FFF | S/NS     |

| CoreSight <sup>™</sup> and peripherals      | 0×00_2000_0000 | 128MB | 0x00_27FF_FFFF | S/NS     |

| REFCLK CNTControl, Generic Timer            | 0x00_2A43_0000 | 64KB  | 0x00_2A43_FFFF | S        |

| EL2 Generic Watchdog Control                | 0×00_2A44_0000 | 64KB  | 0x00_2A44_FFFF | S/NS     |

| EL2 Generic Watchdog Refresh                | 0x00_2A45_0000 | 64KB  | 0x00_2A45_FFFF | S/NS     |

| Trusted Watchdog, SP805                     | 0×00_2A49_0000 | 64KB  | 0x00_2A49_FFFF | S        |

| TrustZone Address Space Controller, TZC-400 | 0x00_2A4A_0000 | 64KB  | 0x00_2A4A_FFFF | S        |

| REFCLK CNTRead, Generic Timer               | 0x00_2A80_0000 | 4KB   | 0x00_2A80_0FFF | S/NS     |

| AP_REFCLK CNTCTL, Generic Timer             | 0×00_2A81_0000 | 4KB   | 0x00_2A81_0FFF | S/NS     |

| AP_REFCLK CNTBase0, Generic Timer           | 0×00_2A82_0000 | 4KB   | 0x00_2A82_0FFF | S        |

b The device is implemented as RAM and is 8MB in size.

Table 3-5 Base Platform memory map (continued)

| Peripheral                                    | Start address       | Size   | End address        | Security |

|-----------------------------------------------|---------------------|--------|--------------------|----------|

| AP_REFCLK CNTBase1, Generic Timer             | 0×00_2A83_0000      | 4KB    | 0x00_2A83_0FFF     | S/NS     |

| DMC-400 CFG, unimplemented                    | 0x00_2B0A_0000      | 64KB   | 0x00_2B0A_FFFF     | S/NS     |

| SMMUv3 AEM <sup>c</sup>                       | 0×00_2B40_0000      | 1MB    | 0x00_2B4F_FFFF     | S/NS     |

| GIC Physical CPU interface, GICC <sup>d</sup> | 0×00_2C00_0000      | 8KB    | 0x00_2C00_1FFF     | S/NS     |

| GIC Virtual Interface Control, GICHd          | 0×00_2C01_0000      | 4KB    | 0x00_2C01_0FFF     | S/NS     |

| GIC Virtual CPU Interface, GICV <sup>d</sup>  | 0x00_2C02_F000      | 8KB    | 0x00_2C03_0FFF     | S/NS     |

| CCI-400                                       | 0×00_2C09_0000      | 64KB   | 0x00_2C09_FFFF     | S/NS     |

| Non-trusted SRAM                              | 0×00_2E00_0000      | 64KB   | 0x00_2E00_FFFF     | S/NS     |

| GICv3 IRI GICD <sup>d</sup>                   | 0×00_2F00_0000      | 64KB   | 0x00_2F00_FFFF     | S/NS     |

| GICv3 IRI GITS <sup>d</sup>                   | 0x00_2F02_0000      | 128KB  | 0x00_2F03_FFFF     | S/NS     |

| GICv3 IRI GICR <sup>d</sup>                   | 0x00_2F10_0000      | 1MB    | 0x00_2F1F_FFFF     | S/NS     |

| PCIe config region <sup>c</sup>               | 0×00_4000_0000      | 256MB  | 0x00_4FFF_FFFF     | S/NS     |

| PCIe memory region 1 <sup>c</sup>             | 0×00_5000_0000      | 256MB  | 0x00_5FFF_FFFF     | S/NS     |

| Trusted Random Number Generator               | 0x00_7FE6_0000      | 4KB    | 0x00_7FE6_0FFF     | S        |

| Trusted Non-volatile counters                 | 0x00_7FE7_0000      | 4KB    | 0x00_7FE7_0FFF     | S        |

| Trusted Root-Key Storage                      | 0x00_7FE8_0000      | 4KB    | 0x00_7FE8_0FFF     | S        |

| DDR3 PHY, unimplemented                       | 0x00_7FEF_0000      | 64KB   | 0x00_7FEF_FFFF     | S/NS     |

| HD LCD Controller, PL370                      | 0x00_7FF6_0000      | 64KB   | 0x00_7FF6_FFFF     | S/NS     |

| DRAM, 0GB-2GB                                 | 0×00_8000_0000      | 2GB    | 0x00_FFFF_FFFF     | P        |

| DRAM, 2GB-32GB                                | 0×08_8000_0000      | 30GB   | 0x0F_FFFF_FFF      | P        |

| PCIe memory region 2°                         | 0×40_0000_0000      | 256GB  | 0x7F_FFFF_FFFF     | S/NS     |

| DRAM, 32GB-512GB                              | 0×88_0000_0000      | 480GB  | 0xFF_FFFF_FFF      | P        |

| DRAM, 512GB-8TB                               | 0×00_0880_0000_0000 | 7TB    | 0x00_0FFF_FFFF_FFF | P        |

| DRAM, 8TB-128TB                               | 0×00_8800_0000_0000 | 120TB  | 0x00_FFFF_FFFF_FFF | P        |

| DRAM, 128TB-2PB                               | 0×08_8000_0000_0000 | 1920TB | 0x0F_FFFF_FFFF_FFF | P        |

| DRAM, 2PB-4PB                                 | 0×88_0000_0000_0000 | 2PB    | 0x8F_FFFF_FFFF_FFF | P        |

\_\_\_\_\_ Note \_\_\_\_\_

The BaseR platform copies its memory map from the Base platform, but swaps the upper 2GB of address space with the lower 2GB. Therefore any peripherals in the memory range [0x0-0x7FFFFFFF] in Base are available at the same offset in the memory range [0x8000000-0xFFFFFFFF] in BaseR. Any peripherals in the memory range [0x80000000-0xFFFFFFFF] in Base are available at the same offset in the memory range [0x0-0x7FFFFFFF] in BaseR. The DRAM in the Base platform memory map starts at address 0x80000000, which in BaseR would prevent any code from running from DRAM after reset. The code would be

Base Platform RevC only

d You can configure the address of this region using parameters to the model. See the parameters in section GICv3IRI component of Peripheral components in the Fast Models Reference Manual.

prevented from running because in the Armv8-R architecture the upper 2GB of memory does not have execution permissions by default.

### 3.4.3 Base - DRAM

The multiple DRAM regions do not alias each other and form a contiguous 4PB area. The total amount of DRAM on the Base Platform system model is configurable. This ability affects where usable DRAM appears.

If the Base Platform system model has bp.dram\_size=4, the default, then 2GB of DRAM is accessible at  $0\times00_8000_0000$  to  $0\times00_{\text{FFFF}}$  and the remaining 2GB is accessible at  $0\times08_8000_0000$  to  $0\times08_{\text{FFFF}}$  FFFF.

If, instead, the Base Platform system model has bp.dram\_size=8, then 2GB of DRAM is accessible at 0x00\_8000\_0000 to 0x00\_FFFF\_FFFF and the remaining 6GB is accessible at 0x08\_8000\_0000 to 0x09 FFFF FFFF.

|           | Note ———                                                                                |

|-----------|-----------------------------------------------------------------------------------------|

| Memory is | allocated on demand, and performance degrades if very large amounts of memory are used. |

### 3.5 Base - interrupt assignments

The platform assigns the *Shared Peripheral Interrupts* (SPIs) and *Private Peripheral Interrupts* (PPIs) on the GIC.

| <br>Note — |

|------------|

| <br>1016   |

- SPI and PPI numbers are mapped onto GIC interrupt IDs as the *Arm® Generic Interrupt Controller Specification* describes.

- IRQ IDs 103-111 and 200-207 apply to the Base Platform RevC only.

Table 3-6 SPI GIC assignments

| IRQ ID | SPI offset | Device                               |

|--------|------------|--------------------------------------|

| 32     | 0          | Watchdog, SP805.                     |

| 34     | 2          | Dual-Timer 0, SP804.                 |

| 35     | 3          | Dual-Timer 1, SP804.                 |

| 36     | 4          | Real-time Clock, PL031.              |

| 37     | 5          | UARTO, PL011.                        |

| 38     | 6          | UART1, PL011.                        |

| 39     | 7          | UART2, PL011.                        |

| 40     | 8          | UART3, PL011.                        |

| 41     | 9          | MCI, PL180, MCIINTR0.                |

| 42     | 10         | MCI, PL180, MCIINTR1.                |

| 43     | 11         | AACI, PL041.                         |

| 44     | 12         | KMI - Keyboard, PL050.               |

| 45     | 13         | KMI - Mouse, PL050.                  |

| 46     | 14         | Color LCD Controller, PL111.         |

| 47     | 15         | Ethernet, SMSC 91C111.               |

| 56     | 24         | Trusted Watchdog, SP085.             |

| 57     | 25         | AP_REFCLK, Generic Timer, CNTPSIRQ.  |

| 58     | 26         | AP_REFCLK, Generic Timer, CNTPSIRQ1. |

| 59     | 27         | EL2 Generic Watchdog WS0.            |

| 60     | 28         | EL2 Generic Watchdog WS1.            |

| 74     | 42         | Virtio block device.                 |

| 75     | 43         | Virtio P9 device.                    |

| 76     | 44         | Virtio net device.                   |

| 80     | 48         | TZC-400.                             |

| 92     | 60         | cluster0.cpu0 PMUIRQ.                |

| 93     | 61         | cluster0.cpu1 PMUIRQ.                |

| 94     | 62         | cluster0.cpu2 PMUIRQ.                |

### Table 3-6 SPI GIC assignments (continued)

| IRQ ID           | SPI offset | Device                                                                    |

|------------------|------------|---------------------------------------------------------------------------|

| 95               | 63         | cluster0.cpu3 PMUIRQ.                                                     |

| 96               | 64         | cluster1.cpu0 PMUIRQ.                                                     |

| 97               | 65         | cluster1.cpu1 PMUIRQ.                                                     |

| 98               | 66         | cluster1.cpu2 PMUIRQ.                                                     |

| 99               | 67         | cluster1.cpu3 PMUIRQ.                                                     |

| 103 <sup>e</sup> | 71         | SMMUv3 non-secure combined interrupt.                                     |

| 104 <sup>e</sup> | 72         | SMMUv3 secure combined interrupt. Unused because there is no secure side. |

| 105 <sup>e</sup> | 73         | SMMUv3 secure event queue. Unused because there is no secure side.        |

| 106 <sup>e</sup> | 74         | SMMUv3 non-secure event queue.                                            |

| 107 <sup>e</sup> | 75         | SMMUv3 PRI queue. Unused because no PCIe device supports PRI.             |

| 108e             | 76         | SMMUv3 secure command queue sync. Unused because there is no secure side. |

| 109 <sup>e</sup> | 77         | SMMUv3 non-secure command queue sync.                                     |

| 110 <sup>e</sup> | 78         | SMMUv3 secure GERROR. Unused because there is no secure side.             |

| 111 <sup>e</sup> | 79         | SMMUv3 non-secure GERROR.                                                 |

| 117              | 85         | HD LCD Controller, PL370.                                                 |

| 139              | 107        | Trusted Random Number Generator.                                          |

| 200e             | 168        | PCIe INTA.                                                                |

| 201 <sup>e</sup> | 169        | PCIe INTB.                                                                |

| 202 <sup>e</sup> | 170        | PCIe INTC.                                                                |

| 203 <sup>e</sup> | 171        | PCIe INTD.                                                                |

| 207 <sup>e</sup> | 175        | PCIe SERR.                                                                |

Table 3-7 PPI GIC assignments

| IRQ ID | PPI offset | Device                                      |

|--------|------------|---------------------------------------------|

| 19     | 3          | Secure hypervisor virtual timer interrupt   |

| 20     | 4          | Secure hypervisor physical timer interrupt  |

| 22     | 6          | DCC, comms channel, interrupt               |

| 23     | 7          | PMU, performance counter, overflow          |

| 24     | 8          | CTI, Cross Trigger Interface, interrupt     |

| 25     | 9          | Virtual CPU interface maintenance interrupt |

| 26     | 10         | Hypervisor timer interrupt                  |

| 27     | 11         | Virtual timer interrupt                     |

| 28     | 12         | Hypervisor virtual timer interrupt          |

e Base Platform RevC only

### Table 3-7 PPI GIC assignments (continued)

| IRQ ID | PPI offset | Device                              |  |

|--------|------------|-------------------------------------|--|

| 29     | 13         | Secure physical timer interrupt     |  |

| 30     | 14         | Non-secure physical timer interrupt |  |

### 3.6 Base - clocks

This section describes the clock frequencies of the Base Platform peripherals.

Table 3-8 Peripheral clock frequencies in the Base Platform

| Device                           | Clock     |

|----------------------------------|-----------|

| Clusters                         | 100MHz    |

| REFCLK CNTControl, Generic Timer | 100MHz    |

| AP_REFCLK CNTCTL, Generic Timer  | 100MHz    |

| Dual-Timer 0-1, SP804            | 35MHz     |

| VE system registers              | 24MHz     |

| UART 0-3, PL011                  | 24MHz     |

| KMI 0-1, PL050                   | 24MHz     |

| MCI, PL180                       | 24MHz     |

| AACI, PL041                      | 24MHz     |

| Ethernet, SMSC 91C111            | 24MHz     |

| Watchdog, SP805                  | 24MHz     |

| Color LCD Controller, PL111      | 23.75MHz  |

| HD LCD Controller, PL370         | 10MHz     |

| Trusted Watchdog, SP805          | 32.768kHz |

| Real-time Clock, PL031           | 1Hz       |

# 3.7 Base - parameters

This section describes the parameters.

Table 3-9 Base Platform parameters

| Parameter                | Туре     | Allowed values     | Default value | Description                                                                 |

|--------------------------|----------|--------------------|---------------|-----------------------------------------------------------------------------|

| bp.dram_size             | int      | 2, 4, or 8-4000000 | 4             | Size of main memory in gigabytes: 2, 4, or any value between 8 and 4000000. |

| bp.proc_idn <sup>f</sup> | uint32_t | -                  | _g            | Processor ID for VE_SysRegs SYS_PROCIDn.                                    |

| bp.secure_memory         | bool     | true, false        | true          | The security state of the processor limits access to peripherals and RAM.   |

| bp.variant <sup>f</sup>  | uint32_t | 0x0-0xF            | _g            | Board variant for VE_SysRegs SYS_ID.                                        |

| cache_state_modelled     | bool     | true, false        | true          | Enable d-cache and i-cache state for all components.                        |

Table 3-10 Base Platform debug parameters

| Parameter | Туре | Allowed values | Default value | Description                                   |

|-----------|------|----------------|---------------|-----------------------------------------------|

| dbgen     | bool | true, false    | true          | Debug authentication signal, <b>dbgen</b> .   |

| niden     | bool | true, false    | true          | Debug authentication signal, <b>niden</b> .   |

| spiden    | bool | true, false    | true          | Debug authentication signal, <b>spiden</b> .  |

| spniden   | bool | true, false    | true          | Debug authentication signal, <b>spniden</b> . |

Some platforms do not expose this parameter.

g Platform specific.

## 3.8 Base - components

This section describes the components.

This section contains the following subsections:

- 3.8.1 Base components about on page 3-38.

- 3.8.2 Base Base PowerController component on page 3-38.

- 3.8.3 Base DebugAccessPort component on page 3-42.

- 3.8.4 Base simulator visualization component on page 3-43.

- 3.8.5 Base VE SysRegs component on page 3-43.

## 3.8.1 Base - components - about

These component models implement some of the functionality of the Versatile Express (VE) hardware.

A complete model implementation of a Base Platform system model includes both Base Platform-specific components and generic components such as buses and timers.

## 3.8.2 Base - Base\_PowerController component

This section describes the Base\_PowerController component.

## Base\_PowerController - control interface

The Base\_PowerController provides a basic register interface for software to control the power-up and power-down of cores in the cluster.

Identify cores in the system to the Base\_PowerController by writing 24 bits in MPIDR format, providing the following levels of affinity:

Bits [23:16]

Affinity level 2.

Bits [15:8]

Affinity level 1.

Bits [7:0]

Affinity level 0.

Examples of affinity usage are not applicable/cluster/processor and cluster/processor/thread.

# Base\_PowerController - parameters

This section describes the parameters.

Table 3-11 Base\_PowerController parameters

| Parameter | Allowed values | Default value | Description                                                                                                                                                                                                                                                                                                                                                    |

|-----------|----------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| startup   | -              | '0.0.0.*'     | A comma-separated list of cores to power up at startup or system reset. Specify core affinities with a dotted-quad ('0.0.0.0' refers to cluster0.cpu0 and '0.0.1.1' refers to cluster1.cpu1). Use wildcards to indicate all cores at an affinity level ('0.0.0.*' indicates all cores in cluster 0 and is equivalent to '0.0.0.0,0.0.0.1,0.0.0.2,,0.0.0.255'). |

#### Base PowerController - registers

This section describes the registers.

#### **Register summary**

This section describes the power control registers in order of offset from the base memory address.

Table 3-12 Base\_PowerController register summary

| Offset | Name   | Туре | Reset | Width | Description                          |

|--------|--------|------|-------|-------|--------------------------------------|

| 0x00   | PPOFFR | RW   | 0x    | 32    | Power Control Processor Off Register |

| 0x04   | PPONR  | RW   | 0x    | 32    | Power Control Processor On Register  |

| 0x08   | PCOFFR | RW   | 0x    | 32    | Power Control Cluster Off Register   |

| 0x0C   | PWKUPR | RW   | 0x    | 32    | Power Control Wakeup Register        |

| 0x10   | PSYSR  | RW   | 0x    | 32    | Power Control SYS Status Register    |

#### **PPOFFR**

The *Power Control Processor Off Register* (PPOFFR) characteristics are: purpose, usage constraints, configurations, and attributes.

#### **Purpose**

Processor SUSPEND command when PWKUPR and the GIC are programmed appropriately to provide wakeup events from IRQ and FIQ events to that processor.

#### Usage constraints

Processor must make power-off requests only for itself.

#### Configurations

Available in all configurations.

#### **Attributes**

See the register summary table.

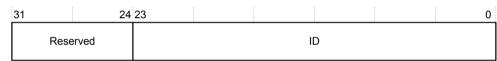

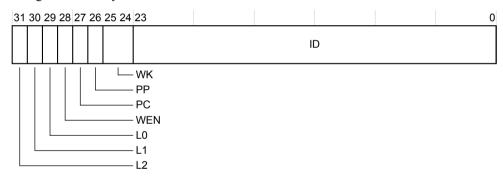

Figure 3-1 Power Control Processor Off Register bit assignments

Table 3-13 Power Control Processor Off Register bit assignments

| Bits    | Name | Function                                                                                             |

|---------|------|------------------------------------------------------------------------------------------------------|

| [31:24] | -    | Reserved.                                                                                            |

| [23:0]  | ID   | MPIDR format affinity value of the processor to be switched off. Programming error if MPIDR != self. |

## **PPONR**

The *Power Control Processor On Register* (PPONR) characteristics are: purpose, usage constraints, configurations, and attributes.

## Purpose

Brings up a processor from low-power mode.

#### **Usage constraints**

Processor must make power-on requests only for other powered-off processors in the system.

#### **Configurations**

Available in all configurations.

#### **Attributes**

See the register summary table.

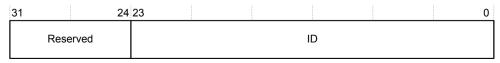

Figure 3-2 Power Control Processor On Register bit assignments

Table 3-14 Power Control Processor On Register bit assignments

| Bits    | Name | Function                                                                                            |

|---------|------|-----------------------------------------------------------------------------------------------------|

| [31:24] | -    | Reserved.                                                                                           |

| [23:0]  | ID   | MPIDR format affinity value of the processor to be switched on. Programming error if MPIDR == self. |

#### **PCOFFR**

The *Power Control Cluster Off Register* (PCOFFR) characteristics are: purpose, usage constraints, configurations, and attributes.

### Purpose

Turns the cluster off.

#### **Usage constraints**

Cluster must make power-off requests only for itself.

#### **Configurations**

Available in all configurations.

#### **Attributes**

See the register summary table.

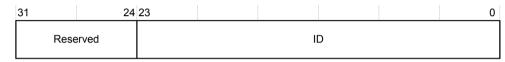

Figure 3-3 Power Control Cluster Off Register bit assignments

Table 3-15 Power Control Cluster Off Register bit assignments

| Bits    | Name | Function                                                                                                                   |

|---------|------|----------------------------------------------------------------------------------------------------------------------------|

| [31:24] | -    | Reserved.                                                                                                                  |

| [23:0]  | ID   | MPIDR format affinity value of powered-on processor in the cluster to be switched off. Programming error if MPIDR != self. |

#### **PWKUPR**

The *Power Control Wakeup Register* (PWKUPR) characteristics are: purpose, usage constraints, configurations, and attributes.

### **Purpose**

Configures whether wakeup requests from the GIC are enabled for this cluster.

## Usage constraints

There are no usage constraints.

# Configurations

Available in all configurations.

## Attributes

See the register summary table.

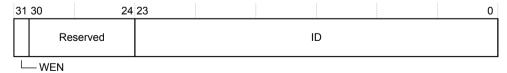

Figure 3-4 Power Control Wakeup Register bit assignments

Table 3-16 Power Control Wakeup Register bit assignments

| Bits    | Name | Function                                                                              |

|---------|------|---------------------------------------------------------------------------------------|

| [31]    | WEN  | If set, enables wakeup interrupts (return from SUSPEND) for this cluster.             |

| [30:24] | -    | Reserved.                                                                             |

| [23:0]  | ID   | MPIDR format affinity value of processor whose Wakeup Enable bit is to be configured. |

#### **PSYSR**

The *Power Control SYS Status Register* (PSYSR) characteristics are: purpose, usage constraints, configurations, and attributes.

### **Purpose**

Provides information on the powered status of a given core. Software writes bits [23:0] for the required core and reads the value along with the associated status in bits [31:24].

#### **Usage constraints**

There are no usage constraints.

#### **Configurations**

Available in all configurations.

#### **Attributes**

See the register summary table.

Figure 3-5 Power Control SYS Status Register bit assignments

Table 3-17 Power Control SYS Status Register bit assignments

| Bits | Name | Function                                                                                                                                 |

|------|------|------------------------------------------------------------------------------------------------------------------------------------------|

| [31] | L2   | Read-only.                                                                                                                               |

|      |      | A value of 1 indicates that affinity level 2 is active/on. If affinity level 2 is not implemented this bit is RAZ.                       |

| [30] | L1   | Read-only.                                                                                                                               |

|      |      | A value of 1 indicates that affinity level 1 is active/on. If affinity level 1 is not implemented this bit is RAZ.                       |

| [29] | L0   | Read-only.                                                                                                                               |

|      |      | A value of 1 indicates that affinity level 0 is active/on.                                                                               |

| [28] | WEN  | Read-only.                                                                                                                               |

|      |      | A value of 1 indicates wakeup interrupts, return from SUSPEND, enabled for this processor. This is an alias of PWKUPR.WEN for this core. |