# Arm<sup>®</sup> Neoverse<sup>™</sup> N1 System Development Platform

**Technical Reference Manual**

# **Arm® Neoverse™ N1 System Development Platform**

#### **Technical Reference Manual**

Copyright © 2019, 2020 Arm Limited or its affiliates. All rights reserved.

#### **Release Information**

#### **Document History**

| Issue   | Date              | Confidentiality  | Change          |

|---------|-------------------|------------------|-----------------|

| 0000-00 | 01 March 2019     | Confidential     | Alpha1 release  |

| 0000-01 | 17 September 2019 | Non-Confidential | Alpha2 release. |

| 0000-02 | 06 April 2020     | Non-Confidential | Beta release.   |

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or TM are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at http://www.arm.com/company/policies/trademarks.

Copyright  $\ensuremath{\mathbb{C}}$  2019, 2020 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

#### **Product Status**

The information in this document is for a Beta product, that is a product under development.

#### Web Address

www.arm.com

#### **Conformance Notices**

This section contains conformance notices.

#### **Federal Communications Commission Notice**

This device is test equipment and consequently is exempt from part 15 of the FCC Rules under section 15.103 (c).

# **CE Conformity**

The Waste Electrical and Electronic Equipment (WEEE) marking, that is, the crossed out wheelie-bin figure, indicates that this product must not be disposed of with general waste within the European Union. To prevent possible harm to the environment from uncontrolled waste disposal, the user is required to recycle the product responsibly to promote reuse of material resources. To comply with EU law, you must dispose of the product in one of the following ways:

- · Return it to the distributer where it was purchased. The distributer is required to arrange free collection when requested.

- · Recycle it using local WEEE recycling facilities. These facilities are now very common and might provide free collection.

- If purchased directly from Arm, Arm provides free collection. Please e-mail weee@arm.com for instructions.

The CE Declaration of Conformity for this product is available on request.

The system should be powered down when not in use.

It is recommended that ESD precautions be taken when handling this product.

The product generates, uses, and can radiate radio frequency energy and may cause harmful interference to radio communications. There is no guarantee that interference will not occur in a particular installation. If this equipment causes harmful interference to radio or television reception, which can be determined by turning the equipment off or on, you are encouraged to try to correct the interference by one or more of the following measures:

- Ensure attached cables do not lie across any sensitive equipment.

- Reorient the receiving antenna.

- Increase the distance between the equipment and the receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/TV technician for help.

| Note                                |                                           |

|-------------------------------------|-------------------------------------------|

| It is recommended that wherever po- | ssible shielded interface cables be used. |

# Contents

# **Arm® Neoverse™ N1 System Development Platform Technical Reference Manual**

|           | Pref                 | face                           |      |  |

|-----------|----------------------|--------------------------------|------|--|

|           |                      | About this book                |      |  |

|           |                      | Feedback                       |      |  |

| Chapter 1 | Intro                | oduction                       |      |  |

|           | 1.1                  | Precautions                    | 1-12 |  |

|           | 1.2                  | About the N1 SDP               | 1-13 |  |

|           | 1.3                  | The N1 SDP at a glance         | 1-14 |  |

|           | 1.4                  | Getting started                | 1-19 |  |

|           | 1.5                  | Accessing the ATX power cables | 1-20 |  |

| Chapter 2 | Hardware description |                                |      |  |

|           | 2.1                  | N1 SDP hardware                | 2-22 |  |

|           | 2.2                  | N1 SoC                         | 2-25 |  |

|           | 2.3                  | External power                 | 2-27 |  |

|           | 2.4                  | Clocks                         | 2-28 |  |

|           | 2.5                  | Resets                         | 2-38 |  |

|           | 2.6                  | IOFPGA                         | 2-37 |  |

|           | 2.7                  | HDLCD video                    | 2-43 |  |

|           | 2.8                  | PCI Express and CCIX systems   | 2-45 |  |

|           | 2.9                  | Chip to Chip communications    | 2-48 |  |

|           | 2.10                 | UARTs                          | 2-5  |  |

|            | 2.11 | LEDs, switches, and buttons                 | 2-55       |

|------------|------|---------------------------------------------|------------|

|            | 2.12 | Debug                                       | 2-59       |

| Chapter 3  | Conf | figuration                                  |            |

|            | 3.1  | Overview of the configuration process       | 3-61       |

|            | 3.2  | Powerup and powerdown sequences             | 3-62       |

|            | 3.3  | Configuration files                         | 3-64       |

|            | 3.4  | Configuration switches                      | 3-68       |

|            | 3.5  | Use of reset push buttons                   | 3-70       |

|            | 3.6  | Command-line interface                      | 3-71       |

| Chapter 4  | Prog | rammers model                               |            |

|            | 4.1  | About this programmers model                | 4-75       |

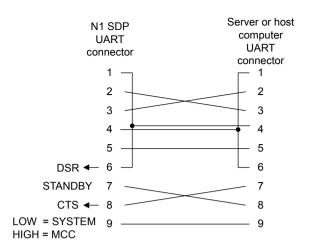

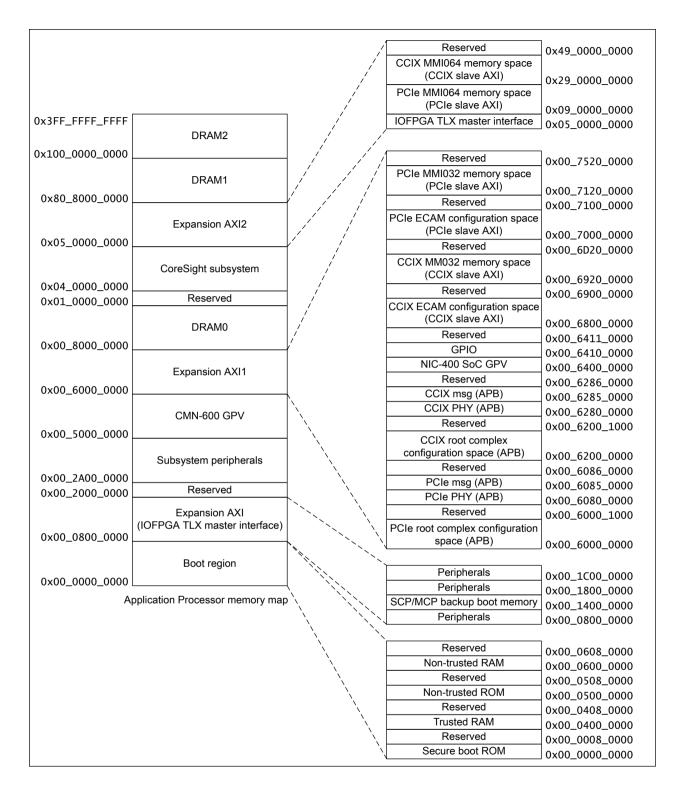

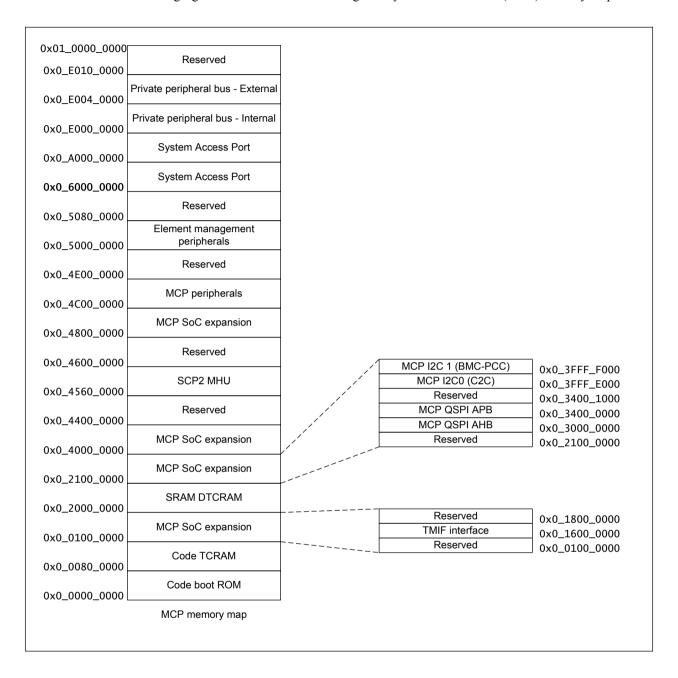

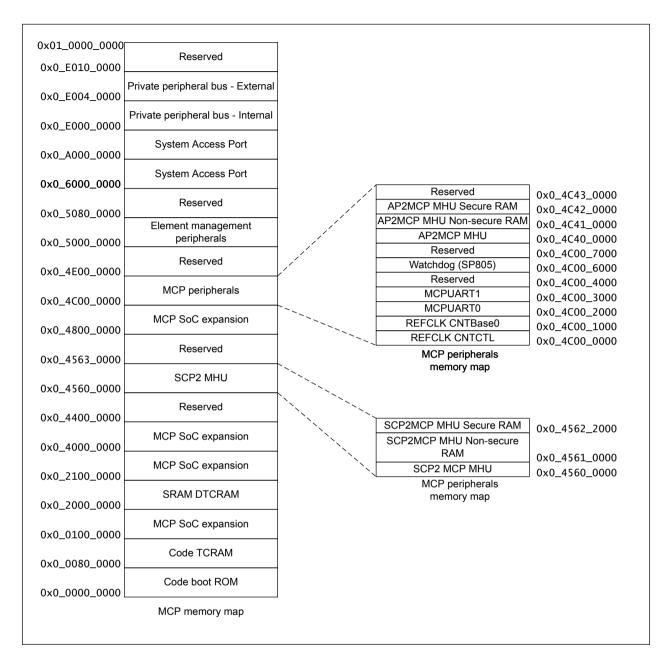

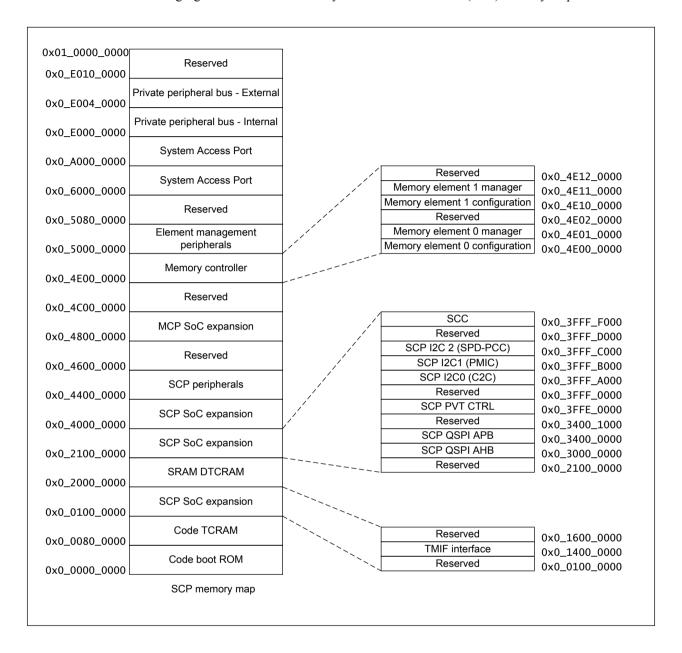

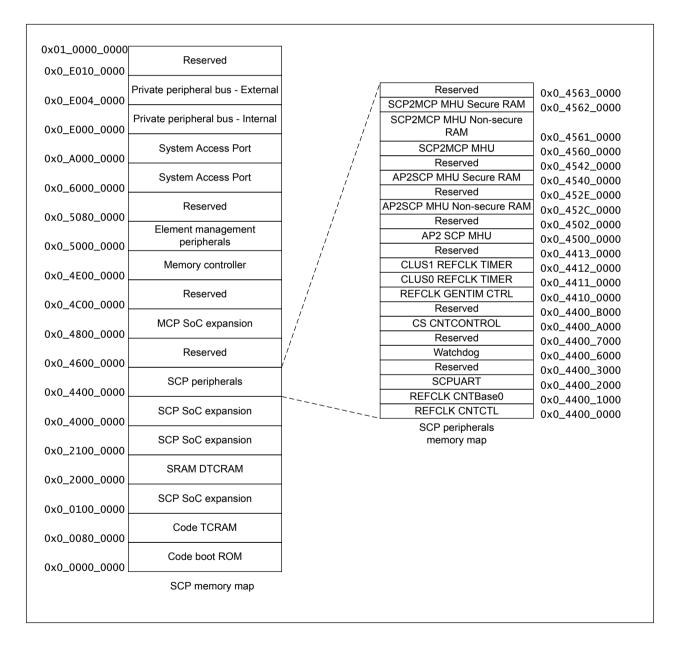

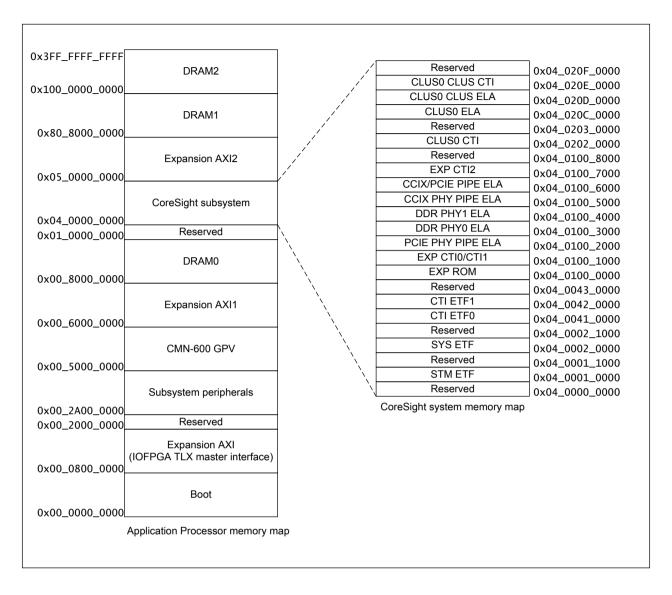

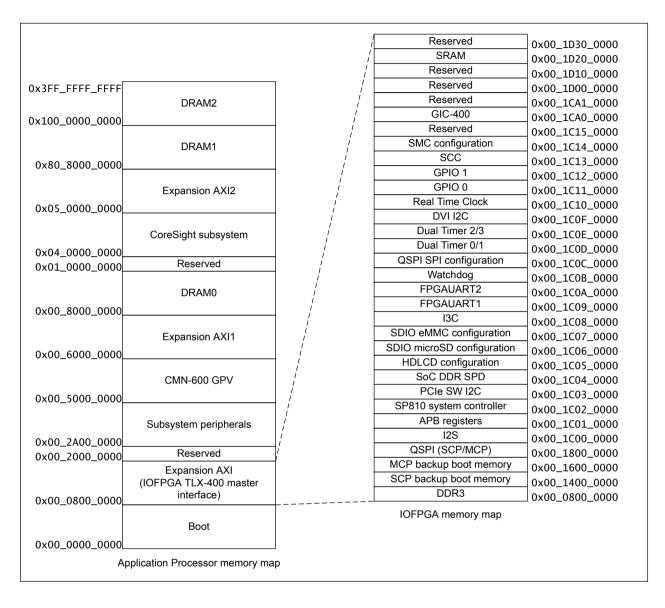

|            | 4.2  | N1 SDP memory maps                          |            |

|            | 4.3  | N1 SoC interrupt maps                       | 4-95       |

|            | 4.4  | System Security Control registers           | 4-105      |

|            | 4.5  | Serial Configuration Control registers      | 4-119      |

|            | 4.6  | APB system registers                        | 4-197      |

|            | 4.7  | APB energy meter registers                  | 4-206      |

|            | 4.8  | UART memory addresses and control registers | 4-225      |

| Appendix A | Sign | al descriptions                             |            |

|            | A.1  | UART headers                                | Appx-A-229 |

|            | A.2  | UART DB9 connectors                         | Appx-A-231 |

|            | A.3  | N1-SoC JTAG connector                       | Appx-A-232 |

|            | A.4  | Trace connector                             | Appx-A-233 |

|            | A.5  | Front panel I/O header                      | Appx-A-235 |

|            | A.6  | PCI Express and CCIX slots                  | Appx-A-236 |

|            | A.7  | C2C connector                               | Appx-A-237 |

|            | A.8  | Power connectors                            | Appx-A-238 |

| Appendix B | Revi | sions                                       |            |

|            | B.1  | Revisions                                   | Appx-B-240 |

# **Preface**

This preface introduces the  $Arm^{\oplus}$  Neoverse<sup>TM</sup> NI System Development Platform Technical Reference Manual.

It contains the following:

- About this book on page 7.

- Feedback on page 10.

#### About this book

This book describes the Arm® Neoverse™ N1 System Development Platform.

#### Intended audience

This book is written for experienced hardware and software developers. It enables demonstration of coherent traffic between the N1 SoC and an accelerator daughterboard, and PCI Express Gen 4 development.

# Using this book

This book is organized into the following chapters:

#### **Chapter 1 Introduction**

This chapter introduces the Arm Neoverse N1 System Development Platform (N1 SDP).

#### Chapter 2 Hardware description

This chapter describes the N1 SDP hardware.

#### **Chapter 3 Configuration**

This chapter describes the powerup and configuration process of the N1 SDP.

#### Chapter 4 Programmers model

This chapter describes the programmers model of the N1 SDP.

#### Appendix A Signal descriptions

This appendix describes the signals that are present at the N1 SDP ports.

#### Appendix B Revisions

This appendix describes the technical changes between released issues of this book.

#### Glossary

The Arm® Glossary is a list of terms used in Arm documentation, together with definitions for those terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

See the Arm® Glossary for more information.

# Typographic conventions

italic

Introduces special terminology, denotes cross-references, and citations.

#### bold

Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.

#### monospace

Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.

# <u>mono</u>space

Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.

#### monospace italic

Denotes arguments to monospace text where the argument is to be replaced by a specific value.

# monospace bold

Denotes language keywords when used outside example code.

#### <and>

Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example:

#### SMALL CAPITALS

Used in body text for a few terms that have specific technical meanings, that are defined in the *Arm*<sup>®</sup> *Glossary*. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE.

# **Timing diagrams**

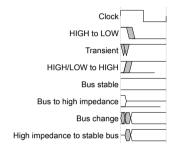

The following figure explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

Figure 1 Key to timing diagram conventions

#### **Signals**

The signal conventions are:

#### Signal level

The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

- HIGH for active-HIGH signals.

- LOW for active-LOW signals.

#### Lowercase n

At the start or end of a signal name, n denotes an active-LOW signal.

# Additional reading

This book contains information that is specific to this product. See the following documents for other relevant information.

#### **Arm publications**

- Arm<sup>®</sup> Neoverse<sup>™</sup> N1 Core Technical Reference Manual (100616).

- Arm® CoreLink™ DMC-620 Dynamic Memory Controller Technical Reference Manual (100568).

- Arm® CoreLink™ MMU-600 System Memory Management Unit Technical Reference Manual (100310).

- Arm® CoreLink™ NIC-400 Network Interconnect Technical Reference Manual (DDI 0475).

- Arm® CoreLink™ CMN-600 Coherent Mesh Network Technical Reference Manual (100180).

- Arm® CoreLink™ TLX-400 Network Interconnect Thin Links Supplement to Arm® CoreLink™ NIC-400 Network Interconnect Technical Reference Manual (DSU 0028).

- Arm® CoreLink™ GIC-600 Generic Interrupt Controller Technical Reference Manual (100336).

- Arm<sup>®</sup> CoreLink<sup>™</sup> GIC-400 Generic Interrupt Controller Technical Reference Manual (DDI 0471).

- Arm® Cortex®-M7 Processor Technical Reference Manual (DDI 0489).

- Arm® PrimeCell UART(PL011) Technical Reference Manual (DDI 0183).

- Arm® PrimeCell General Purpose Input/Output (PL061) Technical Reference Manual (DDI 0190).

- Arm® PrimeCell Real Time Clock (PL031) Technical Reference Manual (DDI 0224).

- Arm® Dual-Timer (SP804) Technical Reference Manual (DDI 0271).

- Arm® Watchdog Module (SP805) Technical Reference Manual (DDI 0270).

- Arm® PrimeCell System Controller SP810 Technical Reference Manual (DDI 0254)

- Arm® CoreSight™ Components Technical Reference Manual (DDI 0314).

- Arm® DS-5 Getting Started Guide (100950).

- Arm® DS-5 Arm DSTREAM User Guide (100955).

- Arm® DS-5 Debugger User Guide (100953).

The following book is only available to licensees or requires registration with Arm.

• *Arm*<sup>®</sup> *DynamIQ*<sup>™</sup> *Shared Unit Technical Reference Manual* (100453).

# **Feedback**

# Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

# Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- The title Arm Neoverse N1 System Development Platform Technical Reference Manual.

- The number 101489 0000 02 en.

- If applicable, the page number(s) to which your comments refer.

- A concise explanation of your comments.

| Arm also welcomes general suggestions for additions and improvements.                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note                                                                                                                                                          |

| Arm tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader. |

# Chapter 1 **Introduction**

This chapter introduces the Arm Neoverse N1 System Development Platform (N1 SDP).

It contains the following sections:

- 1.1 Precautions on page 1-12.

- 1.2 About the N1 SDP on page 1-13.

- 1.3 The N1 SDP at a glance on page 1-14.

- 1.4 Getting started on page 1-19.

- 1.5 Accessing the ATX power cables on page 1-20.

# 1.1 Precautions

This section describes precautions that ensure safety and prevent damage to your N1 SDP.

This section contains the following subsections:

- 1.1.1 Ensuring safety on page 1-12.

- 1.1.2 Operating temperature on page 1-12.

- 1.1.3 Preventing damage on page 1-12.

# 1.1.1 Ensuring safety

The N1 SDP is supplied in a mains-powered standard PC tower. A standard 5V ATX supply powers the board.

- Do not use the N1 SDP near equipment that is sensitive to electromagnetic emissions, for example, medical equipment.

- To reduce the risk of injury, ensure that the N1 SDP is powered down and that the fans have stopped turning before opening the chassis.

# 1.1.2 Operating temperature

The N1 SDP has been tested in the temperature range 15°C-30°C.

# 1.1.3 Preventing damage

The N1 SDP is intended for use within a laboratory or engineering development environment.

If you remove the N1 SDP from the PC tower, observe the following precautions:

- Never subject the board to high electrostatic potentials. Observe *ElectroStatic Discharge* (ESD) precautions when handling any board.

- Always wear a grounding strap when handling the board.

- Only hold the board by the edges.

- Avoid touching the component pins or any other metallic element.

# 1.2 About the N1 SDP

The N1 SDP provides access to the Arm Neoverse N1 SoC.

#### N1 SoC and board

The N1 SDP enables software development for key enterprise technology and general Arm software development.

The N1 SDP consists of the N1 board containing the N1 SoC. The N1 board is a micro-ATX form factor board and is supplied in a standard PC tower unit. The N1 SoC contains two dual-core Arm Neoverse N1 processor clusters.

The system demonstrates Arm technology in the context of *Cache-Coherent Interconnect for Accelerators* (CCIX) protocol by:

- Running coherent traffic between the N1 SoC and an accelerator card.

- Coherent communication between two N1 SoCs.

- Enabling development of CCIX-enabled FPGA accelerators.

# 1.3 The N1 SDP at a glance

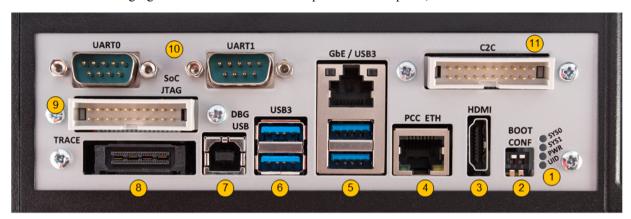

The following figures show the PC tower back panel and front panel, and the N1 board.

Figure 1-1 Back panel

Figure 1-2 Front panel reset buttons

Figure 1-3 N1 board

The following table describes the components, connectors, and push buttons.

# Table 1-1 Key to figures

| Component number | Component name                      | Access                               | Comment                                                                                                                                                                                                                                                                                                                         |

|------------------|-------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | System LEDs                         | Back panel.                          | -                                                                                                                                                                                                                                                                                                                               |

| 2                | Configuration switches              |                                      |                                                                                                                                                                                                                                                                                                                                 |

| 3                | HDMI port                           |                                      |                                                                                                                                                                                                                                                                                                                                 |

| 4                | PCC Ethernet port                   |                                      |                                                                                                                                                                                                                                                                                                                                 |

| 5                | GbE port. USB 3.0 ports.            |                                      |                                                                                                                                                                                                                                                                                                                                 |

| 6                | USB 3.0 ports.                      |                                      |                                                                                                                                                                                                                                                                                                                                 |

| 7                | DBG USB port                        |                                      |                                                                                                                                                                                                                                                                                                                                 |

| 8                | N1 SoC trace port                   |                                      |                                                                                                                                                                                                                                                                                                                                 |

| 9                | N1 SoC JTAG port                    |                                      | Ribbon cable to N1 SoC JTAG port, connector 17, on board.                                                                                                                                                                                                                                                                       |

| 10               | UART0 and UART1 DB9 male connectors |                                      | <ul> <li>Arm supplies the N1 SDP with the following ribbon cable connections:</li> <li>Header UART0 on board to DB9 connector UART0 on back panel.</li> <li>Header UART1 on board to DB9 connector UART1 on back panel.</li> <li>The DB9 connectors are logically UARTs but the pins follow the RS232 specification.</li> </ul> |

| 11               | Chip-to-Chip (C2C)<br>Connector     |                                      | Ribbon cable to <i>Chip-to-Chip</i> (C2C) connector, 19, on board.                                                                                                                                                                                                                                                              |

| 12               | Slot 4: PCIe, CCIX, ×16 connector.  | Board. Remove side panel for access. | 16 lanes used. Gen 4 link.                                                                                                                                                                                                                                                                                                      |

| 13               | Slot 3: PCIe ×16 connector.         |                                      | 8 lanes used, 8 lanes unused. Gen 3 link.                                                                                                                                                                                                                                                                                       |

| 14               | Slot 2: PCIe ×16 connector.         |                                      | 16 lanes used. Gen 3 link.                                                                                                                                                                                                                                                                                                      |

| 15               | Slot 1: PCIe ×4 connector.          |                                      | 1 lane used. 3 lanes unused. Gen 3 link.                                                                                                                                                                                                                                                                                        |

| 16               | ATX/EPS connector                   |                                      | -                                                                                                                                                                                                                                                                                                                               |

| 17               | N1 SoC JTAG port                    | Board.                               | Ribbon cable to N1 SoC JTAG port, connector 9, on back panel.                                                                                                                                                                                                                                                                   |

# Table 1-1 Key to figures (continued)

| Component number | Component name                                             | Access                               | Comment                                                                                                                                                                                                                                 |

|------------------|------------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18               | UART0, UART1, UART2, and UART3 5×2 way headers, no pin 10. | Board. Remove side panel for access. | Arm supplies the N1 SDP with the following ribbon cable connections:  • Header UART0 on board to DB9 connector UART0 on back panel.  • Header UART1 on board to DB9 connector UART1 on back panel.  ——————————————————————————————————— |

| 19               | Chip-to-Chip (C2C) Connector                               | Back panel                           | Ribbon cable to <i>Chip-to-Chip</i> (C2C) connector, 11, on back panel.                                                                                                                                                                 |

| 20               | RDIMM1 memory                                              | Board. Remove side                   | -                                                                                                                                                                                                                                       |

| 21               | RDIMM0 memory                                              | panel for access.                    |                                                                                                                                                                                                                                         |

| 22               | ATX power connector and power indicator LEDs               |                                      |                                                                                                                                                                                                                                         |

| 23               | User switch SW8                                            |                                      |                                                                                                                                                                                                                                         |

| 24               | User switch SW1                                            |                                      |                                                                                                                                                                                                                                         |

| 25               | Reserved for use by Arm                                    |                                      |                                                                                                                                                                                                                                         |

| 26               | IOFPGA microSD card                                        |                                      |                                                                                                                                                                                                                                         |

| 27               | IOFPGA                                                     |                                      |                                                                                                                                                                                                                                         |

| 28               | User LED0                                                  |                                      |                                                                                                                                                                                                                                         |

| 29               | User LED7                                                  |                                      |                                                                                                                                                                                                                                         |

| 30               | Reserved for use by Arm                                    |                                      |                                                                                                                                                                                                                                         |

| 31               | IOFPGA JTAG                                                |                                      |                                                                                                                                                                                                                                         |

| 32               | Platform Controller Chip (PCC)                             |                                      |                                                                                                                                                                                                                                         |

| 33               | 7-segment display                                          |                                      |                                                                                                                                                                                                                                         |

| 34               | Motherboard Configuration<br>Controller (MCC)              |                                      |                                                                                                                                                                                                                                         |

| 35               | MCC configuration microSD card                             |                                      |                                                                                                                                                                                                                                         |

| 36               | Front panel I/O connectors                                 | ]                                    |                                                                                                                                                                                                                                         |

| 37               | PCIe SATA0                                                 |                                      |                                                                                                                                                                                                                                         |

| 38               | PCIe SATA1.                                                |                                      |                                                                                                                                                                                                                                         |

| 39               | Reserved push button                                       | -                                    |                                                                                                                                                                                                                                         |

# Table 1-1 Key to figures (continued)

| Component number | Component name                                            | Access                               | Comment                                                                                                                           |

|------------------|-----------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 40               | Hardware reset button,<br>PBRESET                         | Board. Remove side panel for access. | The front panel I/O connector:  Brings the PBON and PBRESET push button functions to the front panel.  Connects to the power LED. |

| 41               | On/Off/Soft reset push<br>button, PBON                    |                                      |                                                                                                                                   |

| 42               | Hardware reset button,<br>PBRESET                         | Front panel                          |                                                                                                                                   |

| 43               | On/Off/Soft reset push<br>button, PBON, and power<br>LED. |                                      |                                                                                                                                   |

| 44               | HDD activity LED.                                         |                                      | Combined signal from SATA0 and SATA1 from front panel I/O connector on board.                                                     |

# 1.4 Getting started

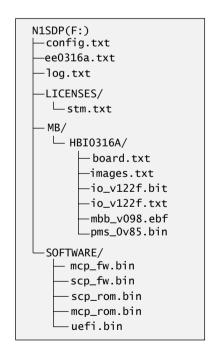

The N1 SDP is controlled from a serial terminal that you connect to the DBG USB port. A set of files in the non-volatile *Motherboard Configuration Controller* (MCC) configuration microSD card configures the board. The configuration microSD card is accessible through the DBG USB port.

The board is factory-programmed with the MCC and *Platform Controller Chip* (PCC), *System Control Processor* (SCP), *Manageability Control Processor* (MCP), and *Application Processor* (AP) firmware.

#### Powering up into the operating state

The minimum actions to boot the N1 SDP are as follows:

- 1. Connect a serial terminal to the DBG USB port on the back panel. The serial port settings must be:

- 115.2kBaud.

- 8N1.

- No hardware or software flow control.

By default, the four COM ports are connected to the following devices:

- COM<n> *Motherboard Configuration Controller* (MCC).

- COM<n+1> Application Processor (AP).

- COM<n+2) System Control Processor (SCP).

- COM<n+3) Manageability Control Processor (MCP).

- 2. Turn the mains power switch on the PC tower ON. The MCC window command prompt is shown and the system is now in the standby state. Ensure that both configuration switches on the back panel are in the OFF (up) position. See 1.3 The N1 SDP at a glance on page 1-14 for the location of the configuration switches.

- 3. To complete the powerup sequence from the standby state, briefly press the PBON button. The system is now fully-powered and in the operating state.

#### **Editing configuration files**

The configuration microSD card contains the system configuration files. To modify the system default settings, edit or replace configuration files while the system is in standby state:

- 1. Ensure that the serial terminal is connected to the DBG USB port on the back panel.

- 2. Turn the power switch ON. The MCC window command prompt is shown and the system is now in the standby state. Ensure that both configuration switches are in the OFF (up) position.

- 3. Issue the following command at the MCC command prompt on the serial terminal:

- Cmd> usb\_on

The serial terminal now recognizes the configuration microSD card as a *USB Mass Storage Device* (USBMSD).

- 4. Edit the existing configuration files, or Drag and Drop new files.

- 5. Perform a Hardware Reset by pressing the PBRESET button. The system is now in the standby state.

- 6. Briefly press the PBON button. The system is now fully powered and in the operating state.

| Note |  |

|------|--|

|      |  |

|      |  |

See 3.3 Configuration files on page 3-64 for information about the configuration files.

# 1.5 Accessing the ATX power cables

The N1 SDP PC tower provides SATA and other ATX power cables that you can use to connect to external hard drives. The power cables are accessed by removing the metal side panel.

| ——— Warning ———                   |                                                                  |

|-----------------------------------|------------------------------------------------------------------|

| Before accessing the ATX power of | ables, ensure that the unit is disconnected from the mains power |

| supply.                           |                                                                  |

# Access the ATX power cables

To access the ATX power cables, you must gain access to the chassis:

- 1. Remove the large metal side panel:

- Undo the thumbscrews at the rear of the tower.

- Slide the side panel away from the tower.

2. The ATX power cables are now accessible, folded up inside the tower. Unfold the power cables to connect them to external hard drives.

# Chapter 2 **Hardware description**

This chapter describes the N1 SDP hardware.

It contains the following sections:

- 2.1 N1 SDP hardware on page 2-22.

- 2.2 N1 SoC on page 2-25.

- 2.3 External power on page 2-27.

- 2.4 Clocks on page 2-28.

- 2.5 Resets on page 2-35.

- 2.6 IOFPGA on page 2-37.

- 2.7 HDLCD video on page 2-43.

- 2.8 PCI Express and CCIX systems on page 2-45.

- 2.9 Chip to Chip communications on page 2-48.

- 2.10 UARTs on page 2-51.

- 2.11 LEDs, switches, and buttons on page 2-55.

- 2.12 Debug on page 2-59.

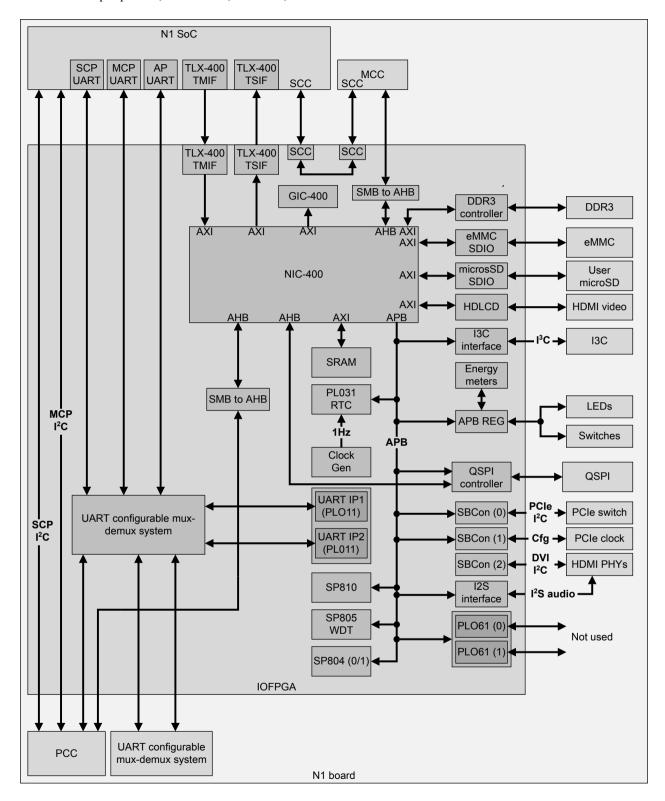

# 2.1 N1 SDP hardware

The support logic and peripheral interfaces of the N1 SDP support access to the N1 SoC.

# Overview of the N1 SDP hardware

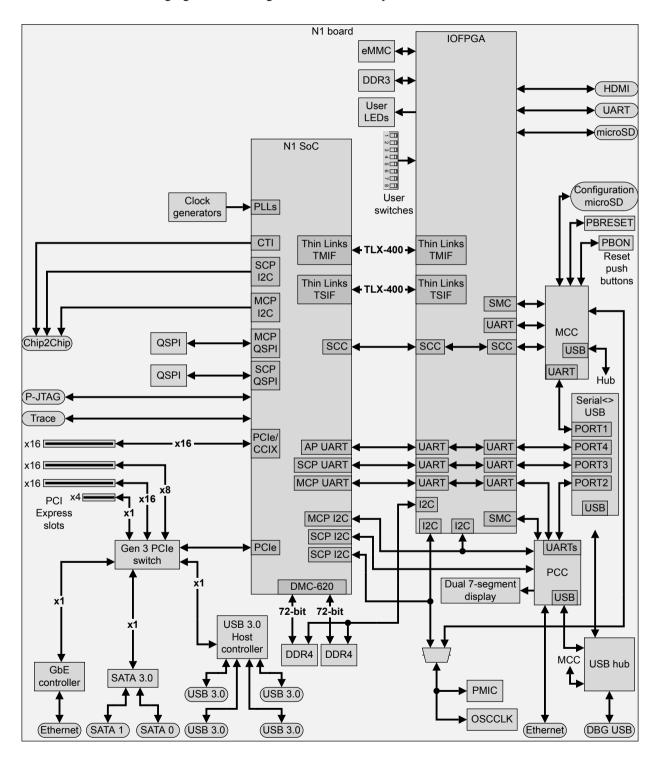

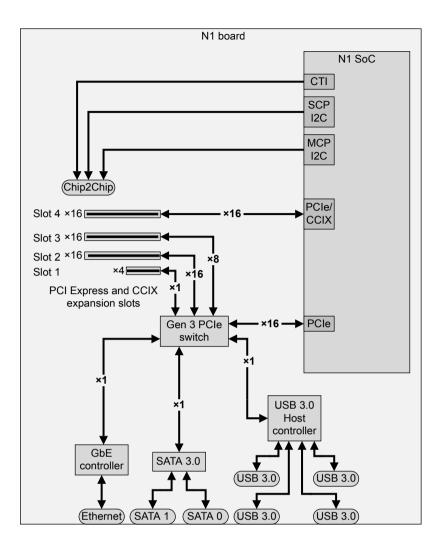

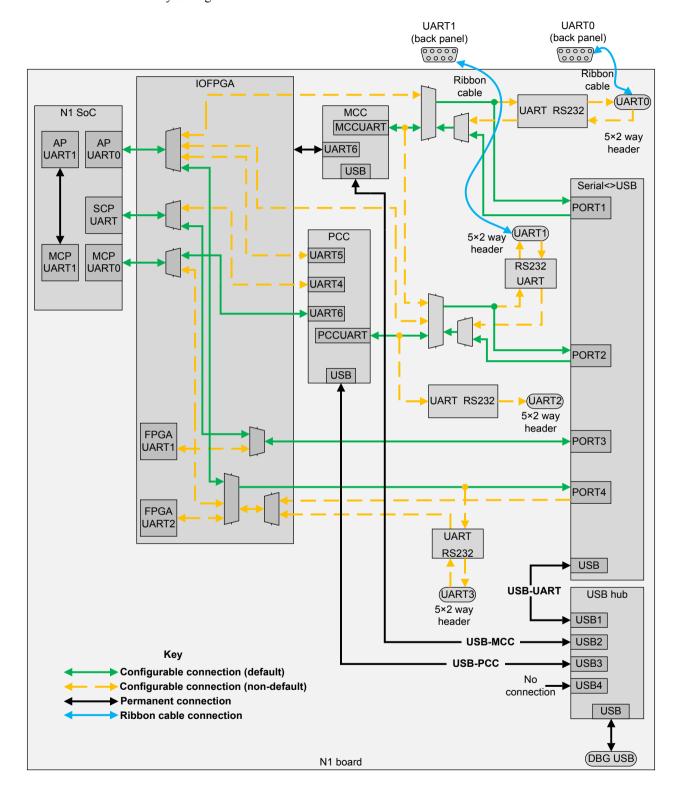

The following figure shows a high-level view of the system architecture.

Figure 2-1 N1 SDP architecture

| <br>Note - |

|------------|

| 110tc      |

The figure shows the default UART and USB connectivity between the components on the N1 board. The UART system is configurable using the settings in the config.txt file on the configuration microSD card. See the following for more information:

- 2.10 UARTs on page 2-51.

- 3.3.2 config. txt board configuration file on page 3-65.

#### Components and systems of the N1 SDP

The N1 SDP contains the following components and systems.

- Motherboard Configuration Controller (MCC):

- Cortex-M4 based controller.

- Controls board powerup, reset, and configuration process.

- Controls IOFPGA configuration.

- Enables drag and drop configuration using the DBG USB connector.

- Always powered up.

- Static Memory Bus (SMB) connection to the IOFPGA.

- Reads temperature measurements from the N1 SoC and ambient sensors and controls cooling fans.

- Platform Controller Chip (PCC):

- Cortex-M4 based controller.

- Board and SoC management.

- Always powered up.

- Static Memory Bus (SMB) connection to the IOFPGA.

- Dual 7-segment LED display.

- System Control Processor (SCP) OSPI memory.

- Manageability Control Processor (MCP) QSPI memory.

- DDR4 memory.

- Cache-Coherent Interconnect for Accelerators (CCIX)/PCI Express ×16 Gen 4 slot:

- Connects to Gen 4 root complex and PHY on the N1 SoC.

- PCI Express 48-lane, 18-port, Gen 3 switch:

- Gigabit Ethernet controller, ×1 Gen 1 link to PCIe switch.

- SATA 3.0 controller, ×1 Gen 2 link to PCIe switch.

- USB 3.0 controller, ×1 Gen 2 link to PCIe switch.

- ×16 PCIe Gen 3 slot.

- ×8 PCIe Gen 3 slot.

- ×1 PCIe Gen 3 slot.

- Four USB 3.0 ports from USB 3.0 controller.

- Two SATA 3.0 ports from SATA 3.0 controller.

- Chip to Chip (C2C) connector, sideband signals for N1 SoC to N1 SoC CCIX connectivity.

- IOFPGA:

- Low-bandwidth peripherals.

- AXI Thin Links Master (TMIF) and Slave (TSIF) interface to the N1 SoC.

- APB energy meter registers, for processor voltage control and current monitoring.

- HDLCD controller, low-resolution output from the N1 cores or the PCC (boot).

- I<sup>2</sup>S audio from HDLCD controller.

- IOFPGA connections to N1 board:

- HDMI connector, driven by HDLCD controller.

- DDR3 memory.

- eMMC, provides user boot memory image storage.

- microSD card, provides user boot memory image storage.

- Two UART ports (PL011).

- System registers, Watchdog and Real Time Clock.

- Eight user DIP switches.

- Eight user LEDs.

I<sup>3</sup>C master connector, for future external expansion.

- Two reset push buttons:

- On/Off/Soft reset button PBON.

- Hardware reset button, PBRESET.

- Programmable oscillators.

- JTAG debug port.

- 32-bit Trace port.

# Related information

1.3 The N1 SDP at a glance on page 1-14

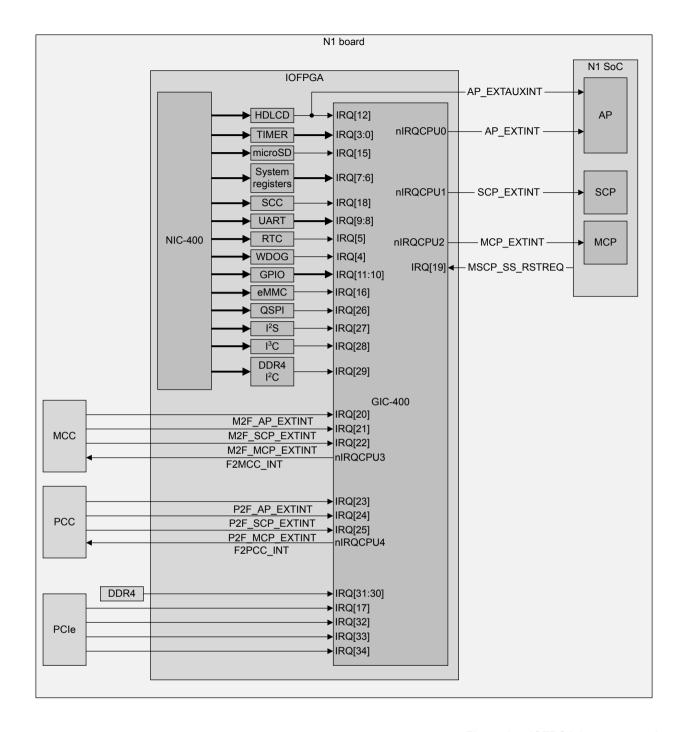

# 2.2 N1 SoC

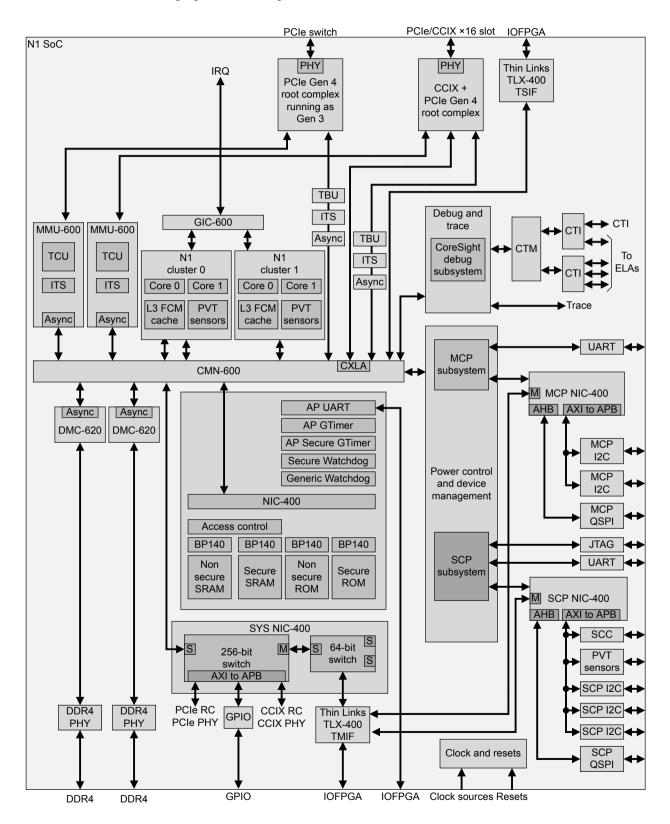

The following figure shows a high-level view of architecture of the N1 SoC.

Figure 2-2 N1 SoC

#### Major components of the N1 SoC

The N1 SoC contains the following components and interfaces:

- Two dual-core N1 clusters. Each cluster has:

- 64KB private L1 data cache for each core, and 64KB private L1 instruction cache for each core.

- 1MB private L2 unified cache for each core.

- 1MB shared L3 unified cache in the *DynamIO Shared Unit* (DSU) *Flash Cache Module* (FCM).

- CMN-600 interconnect with *Coherent Multichip Link* (CML):

- Runs from **INTPLLCLK** default 1.6GHz.

- 1GHz clock, CXSCLK for CCIX block in CMN-600 interconnect.

| <br>Note — |  |

|------------|--|

| 11016      |  |

Arm recommends that you set the CMN-600 clock, **INTPLLCLK**, to 1.5GHz maximum using the SCC registers. See 2.4.3 Clock programming and control on page 2-31, 4.5.42 INT\_PLL\_CTRL0 Register on page 4-158, and 4.5.43 INT\_PLL\_CTRL1 Register on page 4-159.

- Embedded Logic Analyzer (ELA) on the N1 cores and FCM DSU.

- Base element:

- Secure region. 512KB RAM, 128KB ROM.

- Non-secure region. 64KB RAM, 4KB ROM

- GIC-600 (GICv3).

- MMU-600 Memory Management Units.

- Cortex-M7 based internal System Control Processor (SCP) and Manageability Control Processor (MCP):

- Secure boot, power management, and device management.

- · CoreSight debug and trace.

- One Cache-Coherent Interconnect for Accelerators (CCIX) Gen 4 root complex and PHY:

- Connects to one ×16 PCI Express slot.

- Backwards compatible to PCI Express Gen 4.

- One PCIe Gen 4 root complex and PHY, running as Gen 3. Connects to the following downstream slots and peripherals through a PCI Express Gen 3 switch:

- One ×16 PCI Express slot.

- One ×8 PCI Express slot.

- One ×1 PCI Express slot.

- One ×1 Gigabit Ethernet controller.

- One ×1 SATA 3 controller.

- One ×1 USB 3 controller.

- Master and slave Thin Links (TLX-400) interfaces:

- Expansion to IOFPGA on the board.

- Two 72-bit DMC-620 DDR4 controllers:

- Support for one 288-pin RDIMM DDR4 per interface. Up to DDR4-3200 speed.

- Interfaces for AP, SCP, and MCP, routed to the *Platform Controller Chip* (PCC) on the board:

- Three UART (PL011) interfaces.

- Three I<sup>2</sup>C for SCP and two I<sup>2</sup>C interfaces for MCP.

- Two QSPI interfaces bot bootup, one for SCP, one for MCP.

- 8-bit GPIO (PL061) for on-board I/O and interrupt.

- Serial Configuration Controller (SCC) interface to IOFPGA.

- Process, Voltage, and Temperature (PVT) sensors.

- 32-bit *Mobile Industry Process Interface* (MIPI-60) Trace port.

- JTAG debug port.

## Related information

1.3 The N1 SDP at a glance on page 1-14

# 2.3 External power

A mains supply in the range 100-240V AC powers the N1 SDP.

This section contains the following subsections:

- 2.3.1 Overview of power scheme on page 2-27.

- *2.3.2 Power islands* on page 2-27.

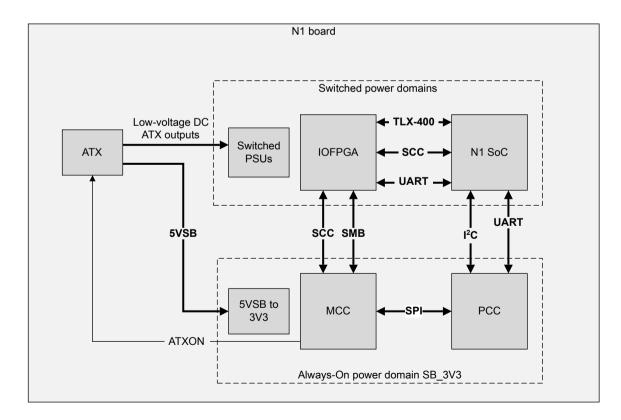

# 2.3.1 Overview of power scheme

A standard ATX power supply unit converts the mains power to low DC voltages which power the N1 board. On-board regulators supply power to the N1 board and to the power domains of the N1 SoC.

Power LEDs indicate the active power domains. See 2.11 LEDs, switches, and buttons on page 2-55 for information on the power LEDs.

#### 2.3.2 Power islands

The N1 board has the following power islands:

- ATX Always-On region:

- Operates in standby state.

- Powers the *Motherboard Configuration Controller* (MCC) and *Platform Controller Chip* (PCC) subsystems only.

- · Switched region:

- Main board VIO and all other non-MCC and non-PCC supplies, including the IOFPGA.

This arrangement enables the PCC to receive a request to place the board into standby state over its local Ethernet connection. The following figure shows the N1 board power islands.

Figure 2-3 N1 board power islands

# 2.4 Clocks

The N1 SDP clocks drive the board and the N1 SoC.

This section contains the following subsections:

- 2.4.1 Overview of clocks on page 2-28.

- 2.4.2 SoC clocks on page 2-28.

- 2.4.3 Clock programming and control on page 2-31.

- 2.4.4 IOFPGA clocks on page 2-34.

# 2.4.1 Overview of clocks

Programmable clock generators on the N1 board generate clocks for the board peripherals, internal blocks in the IOFPGA, and the systems in the N1 SoC.

Phase-locked loops (PLLs) generate internal clocks in the N1 SoC for the processor clusters and other systems.

During powerup or reset, the MCC programs the clock generators according to default values defined in the io\_v0.txt configuration file. You can change the operational clock frequencies by modifying the configuration file. See 3.3.3 Contents of the MB directory on page 3-65 for an example io\_v?.txt configuration file.

| -                                                                              |  |

|--------------------------------------------------------------------------------|--|

| Note                                                                           |  |

| Arm recommends that you operate the N1 board at the default clock frequencies. |  |

|                                                                                |  |

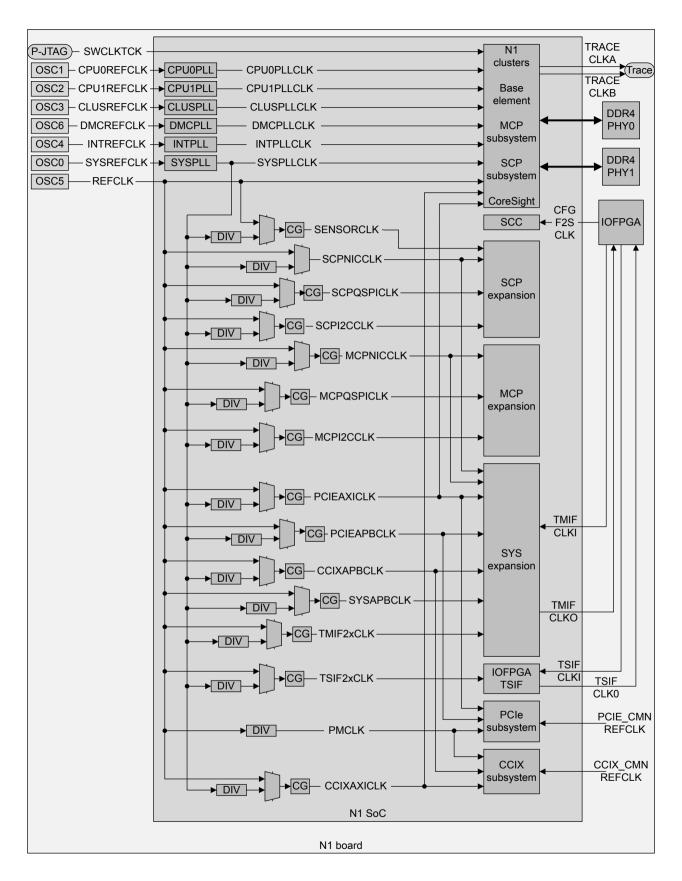

#### 2.4.2 SoC clocks

Programmable clock generators on the N1 board drive PLLs in the N1 SoC which generate the internal N1 SoC clocks.

The following figure shows the programmable clock generators on the board, OSC0-OSC6, and the internal clocking scheme of the N1 SoC.

Figure 2-4 N1 SoC clocks

| during bootup.                                                                                       |

|------------------------------------------------------------------------------------------------------|

| The following table shows the N1 SoC clocks.                                                         |

| Note                                                                                                 |

| The default clock frequencies in this table represent an example clock configuration which enables   |

| correct operation of the N1 SoC. Further SoC testing and measurement, by Arm or by other developers, |

| might result in other default frequencies.                                                           |

The System Control Processor (SCP) configures the PLLs, muliplexers, and dividers in the clock system

Table 2-1 N1 SoC clocks

| Clock      | Source            | Default<br>frequency | Description                                                                                                            |  |

|------------|-------------------|----------------------|------------------------------------------------------------------------------------------------------------------------|--|

| SWCLKTCK   | External debugger | -                    | Combined P-JTAG and Serial Wire Debug (SWD) clock.                                                                     |  |

| CPU0REFCLK | OSC1              | 50MHz                | Reference clock for CPU0PLL. Generates CPU0PLLCLK for cluster 0.                                                       |  |

| CPU1REFCLK | OSC2              | 50MHz                | Reference clock for CPU1PLL. Generates CPU1PLLCLK for cluster 1.                                                       |  |

| CLUSREFCLK | OSC3              | 50MHz                | Reference clock for CLUSPLL. Generates CLUSPLLCLK, a common cluster clock for cluster 0 and cluster 1.                 |  |

| DMCREFCLK  | OSC6              | 50MHz                | Reference clock for DMCPLL. Generates <b>DMCPLLCLK</b> for the DDR subsystem.                                          |  |

| INTREFCLK  | OSC4              | 50MHz                | Reference clock for INTPLL. Generates <b>INTPLLCLK</b> for the CMN-600 Coherent Mesh Network.                          |  |

| SYSREFCLK  | OSC0              | 50MHz                | Reference clock for SYSPLL. Generates the main system clock SYSPLLCLK, and other clocks through programmable dividers. |  |

| REFCLK     | OSC5              | 50MHz                | Always-On reference clock.                                                                                             |  |

| CPU0PLLCLK | CPU0PLL           | 2.4GHz               | Cluster-specific clock for cluster 0.                                                                                  |  |

| CPU1PLLCLK | CPU1PLL           | 2.4GHz               | Cluster-specific clock for cluster 1.                                                                                  |  |

| CLUSPLLCLK | CLUSPLL           | 1.6GHz               | Clock for cluster 0 and cluster 1.                                                                                     |  |

| DMCPLLCLK  | DMCPLL            | 1.6GHz               | Clock for DDR4 subsystem.                                                                                              |  |

| INTPLLCLK  | INTPLL            | 1.6GHz               | CMN-600 Coherent Mesh network clock.                                                                                   |  |

| SYSPLLCLK  | SYSPLL            | 2.4GHz               | Main system clock.                                                                                                     |  |

# Table 2-1 N1 SoC clocks (continued)

| Clock           | Source                             | Default<br>frequency | Description                                                                                                   |  |

|-----------------|------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------|--|

| SENSORCLK       | SYSPLL                             | 100MHz               | Sensor clock                                                                                                  |  |

| SCPNICLK        |                                    | 300MHz               | SCP NIC-400 clock.                                                                                            |  |

| SCPQSPICLK      |                                    | 50MHz                | SCP QSPI reference clock                                                                                      |  |

| SCPI2CCLK       |                                    | 50MHz                | SCP I2C clock                                                                                                 |  |

| MCPNICCLK       |                                    | 300MHz               | MCP NIC-400 clock.                                                                                            |  |

| MCPQSPICLK      |                                    | 50MHz                | MCP QSPI reference clock                                                                                      |  |

| MCPI2CCLK       |                                    | 50MHz                | MCP I2C clock                                                                                                 |  |

| PCIEAXICLK      |                                    | 1.2GHz               | PCIe AXI clock                                                                                                |  |

| PCIEAPBCLK      |                                    | 200MHz               | PCIe APB clock                                                                                                |  |

| CCIXAPBCLK      |                                    | 200MHz               | CCIX APB clock                                                                                                |  |

| SYSAPBCLK       |                                    | 120MHz               | System expansion APB peripherals                                                                              |  |

| TMIF2xCLK       |                                    | 120MHz               | IOFPGA TMIF 2× clock                                                                                          |  |

| TSIF2xCLK       |                                    | 120MHz               | IOFPGA TSIF 2× clock                                                                                          |  |

| CCIXAXICLK      |                                    | 1.2GHz               | CCIX AXI clock                                                                                                |  |

| TRACECLKA       | TPIU                               | 10MHz                | Trace clocks to connector                                                                                     |  |

| TRACECLKB       |                                    |                      |                                                                                                               |  |

| PMCLK           | OSC5, REFCLK                       | 25MHz                | Power management clock for PCIe and CCIX                                                                      |  |

| CFG_F2S_CLK     | MCC                                | 10MHz                | Serial Configuration Controller (SCC) interface clock. This clock is a data strobe, not a free running clock. |  |

| TMIF_CLKI       | IOFPGA TLX-400<br>master interface | 80MHz                | Thin Links-based AXI master interface clock received from IOFPGA with incoming data from IOFPGA.              |  |

| TMIF_CLKO       | N1 SoC TLX-400<br>master interface | 75MHz                | Thin Links-based AXI master interface clock exported from N1 SoC with data transmitted from N1 SoC to IOFPGA. |  |

| TSIF_CLKI       | IOFPGA TLX-400<br>slave interface  | 80MHz                | Thin Links-based AXI slave interface clock received from IOFPGA with incoming data from IOFPGA.               |  |

| TSIF_CLKO       | N1 SoC TLX-400 slave interface     | 75MHz                | Thin Links-based AXI slave interface clock exported from N1 SoC with data transmitted from N1 SoC to IOFPGA.  |  |

| PCIE_CMN_REFCLK | Clock buffer                       | 100MHz               | Fixed differential reference clock for PCIe U-PHY                                                             |  |

| CCIX_CMN_REFCLK | Clock buffer                       | 100MHz               | Fixed differential reference clock for CCIX U-PHY                                                             |  |

| CXSCLK          | CCIX PCIe PHY                      | 1GHz                 | CXLA clock in CMN-600                                                                                         |  |

# 2.4.3 Clock programming and control

The *Serial Configuration Control* (SCC) clock control registers in the N1 SoC control the clock frequencies by modifying the clock PLLs and dividers.

The PLLs generate the internal clocks from the board OSC clock generators according to the formula:

Output clock frequency = (Input clock frequency/REFDIV)×FBDIV/POSTDIV where:

- REFDIV is input frequency division value.

- FBDIV is the PLL feedback division value.

- POSTDIV is the PLL output frequency division value.

The SCC PLL control registers set the values REFDIV, FBDIV, and POSTDIV for each PLL. Other SCC registers control the clock dividers and select the inputs for the internal clocks. See *2.4.2 SoC clocks* on page 2-28.

The following table shows the SCC clock control registers.

Table 2-2 Clock control SCC registers

| Register        | Register function                                                                                                  | Register description                                    |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|

| PMCLK_DIV       | Sets value of divider value to generate PMCLK from REFCLK.                                                         | See 4.5.2 PMCLK_DIV Register on page 4-124.             |  |

| SYSAPBCLK_CTRL  | Selects input clock to generate SYSAPBCLK.                                                                         | See 4.5.3 SYSAPBCLK_CTRL Register on page 4-125.        |  |

| SYSAPBCLK_DIV   | Sets value of divider value to generate SYSAPBCLK from SYSPLLCLK.                                                  | See 4.5.4 SYSAPBCLK _DIV Register on page 4-126.        |  |

| TMIF2XCLK_CTRL  | Selects input clock to generate TMIF2XCLK.                                                                         | See 4.5.5 IOFPGA_TMIF2XCLK_CTRL Register on page 4-127. |  |

| TMIF2XCLK_DIV   | Sets value of divider value to generate TMIF2XCLK from SYSPLLCLK.                                                  | See 4.5.6 IOFPGA_TMIF2XCLK_DIV Register on page 4-128.  |  |

| TSIF2XCLK_CTRL  | Selects input clock to generate TSIF2XCLK.                                                                         | See 4.5.7 IOFPGA_TSIF2XCLK_CTRL Register on page 4-128. |  |

| TSIF2XCLK_DIV   | Sets value of divider value to generate TSIF2XCLK from SYSPLLCLK.  See 4.5.8 IOFPGA_TSIF2XCLK_DIV Register or      |                                                         |  |

| SCPNICCLK_CTRL  | Selects input clock to generate SCPNICLK.                                                                          | See 4.5.9 SCPNICCLK_CTRL Register on page 4-130.        |  |

| SCPNICCLK_DIV   | Sets value of divider value to generate SCPNICCLK from SYSPLLCLK.                                                  | See 4.5.10 SCPNICCLK_DIV Register on page 4-131.        |  |

| SCPI2CCLK_CTRL  | Selects input clock to generate SCPI2CCLK.                                                                         | See 4.5.11 SCP12CCLK_CTRL Register on page 4-131.       |  |

| SCPI2CCLK_DIV   | Sets value of divider value to generate SCPI2CCLK from SYSPLLCLK.                                                  | See 4.5.12 SCP12CCLK_DIV Register on page 4-132.        |  |

| SCPQSPICLK_CTRL | Selects input clock to generate SCPQSPICLK.                                                                        | See 4.5.13 SCPQSPICLK_CTRL Register on page 4-133.      |  |

| SCPQSPICLK_DIV  | Sets value of divider value to generate SCPQSPICLK from SYSPLLCLK.                                                 | See 4.5.14 SCPQSPICLK_DIV Register on page 4-134.       |  |

| SENSORCLK_CTRL  | Selects input clock to generate SENSORCLK.                                                                         | See 4.5.15 SENSORCLK_CTRL Register on page 4-134.       |  |

| SENSORCLK_DIV   | Sets value of divider value to generate SENSORCLK from SYSPLLCLK.  See 4.5.16 SENSORCLK_DIV Register on page 4-135 |                                                         |  |

| MCPNICCLK_CTRL  | Selects input clock to generate  MCPNICCLK.  See 4.5.17 MCPNICCLK_CTRL Register on page 4-136.                     |                                                         |  |

| MCPNICCLK_DIV   | Sets value of divider value to generate MCPNICCLK from SYSPLLCLK.                                                  | See 4.5.18 MCPNICCLK_DIV Register on page 4-137.        |  |

# Table 2-2 Clock control SCC registers (continued)

| Register        | Register function                                                  | Register description                               |

|-----------------|--------------------------------------------------------------------|----------------------------------------------------|

| MCPI2CCLK_CTRL  | Selects input clock to generate MCPI2CCLK.                         | See 4.5.19 MCP12CCLK_CTRL Register on page 4-137.  |

| MCPI2CCLK_DIV   | Sets value of divider value to generate MCPI2CCLK from SYSPLLCLK.  | See 4.5.20 MCPI2CCLK_DIV Register on page 4-138.   |

| MCPQSPICLK_CTRL | Selects input clock to generate MCPQSPICLK.                        | See 4.5.21 MCPQSPICLK_CTRL Register on page 4-139. |

| MCPQSPICLK_DIV  | Sets value of divider value to generate MCPQSPICLK from SYSPLLCLK. | See 4.5.22 MCPQSPICLK_DIV Register on page 4-140.  |

| PCIEAXICLK_CTRL | Selects input clock to generate PCIEAXICLK.                        | See 4.5.23 PCIEAXICLK_CTRL Register on page 4-140. |

| PCIEAXICLK_DIV  | Sets value of divider value to generate PCIEAXICLK from SYSPLLCLK. | See 4.5.24 PCIEAXICLK_DIV Register on page 4-141.  |

| CCIXAXICLK_CTRL | Selects input clock to generate CCIXAXICLK.                        | See 4.5.25 CCIXAXICLK_CTRL Register on page 4-142. |

| CCIXAXICLK_DIV  | Sets value of divider value to generate CCIXAXICLK from SYSPLLCLK. | See 4.5.26 CCIXAXICLK_DIV Register on page 4-143.  |

| PCIEAPBCLK_CTRL | Selects input clock to generate PCIEAPBCLK.                        | See 4.5.27 PCIEAPBCLK_CTRL Register on page 4-143. |

| PCIEAPBCLK_DIV  | Sets value of divider value to generate PCIEAPBCLK from SYSPLLCLK. | See 4.5.28 PCIEAPBCLK_DIV Register on page 4-144.  |

| CCIXAPBCLK_CTRL | Selects input clock to generate CCIXAPBCLK.                        | See 4.5.29 CCIXAPBCLK_CTRL Register on page 4-145. |

| CCIXAPBCLK_DIV  | Sets value of divider value to generate CCIXAPBCLK from SYSPLLCLK. | See 4.5.30 CCIXAPBCLK_DIV Register on page 4-146.  |

| SYS_CLK_EN      | Enables or disables internally generated clocks.                   | See 4.5.31 SYS_CLK_EN Register on page 4-146.      |

| CPU0_PLL_CTRL0  | Control CPU0PLL to generate                                        | See 4.5.32 CPU0_PLL_CTRL0 Register on page 4-148.  |

| CPU0_PLL_CTRL1  | CPU0PLLCLK.                                                        | See 4.5.33 CPU0_PLL_CTRL1 Register on page 4-149.  |

| CPU1_PLL_CTRL0  | Control CPU1PLL to generate                                        | See 4.5.34 CPU1_PLL_CTRL0 Register on page 4-150.  |

| CPU1_PLL_CTRL1  | CPU1PLLCLK.                                                        | See 4.5.35 CPU1_PLL_CTRL1 Register on page 4-151.  |

| CLUS_PLL_CTRL0  | Control CLUSPLL to generate                                        | See 4.5.36 CLUS_PLL_CTRL0 Register on page 4-152.  |

| CLUS_PLL_CTRL1  | CLUSPLLCLK.                                                        | See 4.5.37 CLUS_PLL_CTRL1 Register on page 4-153.  |

| SYS_PLL_CTRL0   | Control SYSPLL to generate                                         | See 4.5.38 SYS_PLL_CTRL0 Register on page 4-154.   |

| SYS_PLL_CTRL1   | SYSPLLCLK.                                                         | See 4.5.39 SYS_PLL_CTRL1 Register on page 4-155.   |

| DMC_PLL_CTRL0   | Control DMCPLL to generate                                         | See 4.5.40 DMC_PLL_CTRL0 Register on page 4-156.   |

| DMC_PLL_CTRL1   | DMCPLLCLK.                                                         | See 4.5.41 DMC_PLL_CTRL1 Register on page 4-157.   |

| INT_PLL_CTRL0   | Control INTPLL to generate                                         | See 4.5.42 INT_PLL_CTRL0 Register on page 4-158.   |

| INT_PLL_CTRL1   | INTPLLCLK.                                                         | See 4.5.43 INT_PLL_CTRL1 Register on page 4-159.   |

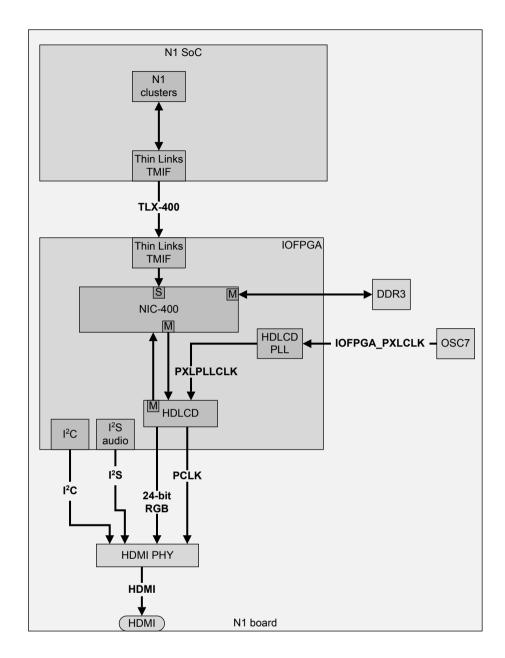

# 2.4.4 IOFPGA clocks

Programmable clock generators on the N1 board generate clocks for the internal systems of the IOFPGA.

The IOFPGA Thin Links interfaces generate clocks for data transmitted to the N1 SoC interfaces. The IOFPGA also generates the *Serial Configuration Controller* (SCC) clock data strobe.

The following table shows the IOFPGA clocks.

Table 2-3 IOFPGA clocks

| Clock                                                                             | Source               | Frequency                                                          | Description                                                                                                   |

|-----------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| IOFPGA_ACLK                                                                       | OSC9                 | 60MHz                                                              | Boot up clock. Drives IOFPGA OSC0.                                                                            |

| IOFPGA_TLXCLK                                                                     | OSC8                 | 80MHz                                                              | IOFPGA Thin Links                                                                                             |

| IOFPGA_PXLCLK                                                                     | OSC7                 | 23.75MHz                                                           | Drives HDLCDPLL. Low-performance pixel clock output, range 25-100MHz.                                         |

| IOFPGA_AUDCLK                                                                     | OSC10                | 24.576MHz                                                          | Drives audio clock I2SCLK.                                                                                    |

| IOFPGA_CLK24M                                                                     | FPGA_CLK24M          | 24MHz                                                              | Drives MMCM at 100MHz.                                                                                        |

| IOFPGA_RSVD                                                                       | OSC11                | 24MHz                                                              | Reserved                                                                                                      |

| S32KCLK                                                                           | CLK_32K              | 32.768kHz                                                          | Standalone clock for Real Time Clock (RTC)                                                                    |

| IOFPGA_DDR3_SYSCLK                                                                | GTX clock            | 100MHz                                                             | Drives DDR3 controller reference clock at 400MHz.                                                             |

| Thin Links-based AXI master and slave interface clocks between IOFPGA and N1 SoC. | -                    | 75MHz from N1<br>SoC to IOFPGA.<br>80MHz from<br>IOFPGA to N1 SoC. | See 2.4.2 SoC clocks on page 2-28 for descriptions of Thin Links clocks.                                      |

| SMBM_CLK                                                                          | MCC                  | 40MHz                                                              | SMB clock                                                                                                     |

| SMBP_CLK                                                                          | PCC                  | 40MHz                                                              | SMB clock                                                                                                     |

| CFG_M2F_CLK                                                                       | MCC                  | 10MHz                                                              | Serial Configuration Controller (SCC) interface clock. This clock is a data strobe, not a free running clock. |

| CFG_CLK                                                                           | IOFPGA SCC interface | 25MHz                                                              | Serial Configuration Controller (SCC) interface clock. This clock is a data strobe, not a free running clock. |

| PCIE_CMN_REFCLK                                                                   | Clock buffer         | 100MHz                                                             | Fixed differential reference clock for PCIe U-PHY                                                             |

| CCIX_CMN_REFCLK                                                                   | Clock buffer         | 100MHz                                                             | Fixed differential reference clock for CCIX U-PHY                                                             |

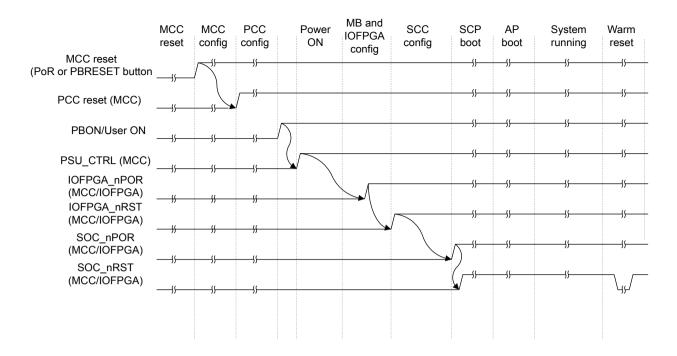

# 2.5 Resets

The N1 SDP provides reset signals for the N1 board and N1 SoC.

# N1 board resets

The N1 board has the following resets.

Table 2-4 N1 board resets

| Reset       | Source                                                   | Target                                                            | Comment                                                                                                                                                                              |

|-------------|----------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nPBRESET    | Powerup reset.  Hardware reset user push button PBRESET. | Motherboard Configuration<br>Controller (MCC) and entire<br>board | Main board powerup reset and hard reset from the user hardware reset push button. The entire system goes to standby state.                                                           |

| UART0_DSR   | External device                                          | MCC and entire board                                              | Remote UART reset.  Must be enabled by use of configuration switch SW1. See 2.11.5 Push buttons and switches on page 2-57.                                                           |

| CB_CFGnRST  | MCC                                                      | Platform Controller Chip (PCC) and entire board                   | The MCC controls the PCC reset.                                                                                                                                                      |

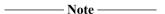

| IOFPGA_nPOR | MCC                                                      | IOFPGA, powerup reset sections.                                   | Enables the IOFPGA internal PLLs to be reset and become stable before release of logic reset.                                                                                        |