# Arm<sup>®</sup> CoreLink<sup>™</sup> SIE-300 AXI5 System IP for Embedded

Revision: r1p1

**Technical Reference Manual**

# Arm<sup>®</sup> CoreLink<sup>™</sup> SIE-300 AXI5 System IP for Embedded

#### **Technical Reference Manual**

Copyright © 2019, 2020 Arm Limited or its affiliates. All rights reserved.

#### **Release Information**

#### **Document History**

| Issue   | Date           | Confidentiality  | Change                                 |

|---------|----------------|------------------|----------------------------------------|

| 0000-00 | 12 March 2019  | Non-Confidential | First beta release for r0p0.           |

| 0000-01 | 06 June 2019   | Non-Confidential | First limited access release for r0p0. |

| 0100-02 | 15 August 2019 | Non-Confidential | First early access release for r1p0.   |

| 0101-03 | 17 July 2020   | Non-Confidential | First full release for r1p1.           |

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. **No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.**

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with <sup>®</sup> or <sup>™</sup> are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at *http://www.arm.com/company/policies/trademarks*.

Copyright © 2019, 2020 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

(LES-PRE-20349)

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

#### **Product Status**

The information in this document is Final, that is for a developed product.

Web Address

www.arm.com

# Contents Arm<sup>®</sup> CoreLink<sup>™</sup> SIE-300 AXI5 System IP for Embedded Technical Reference Manual

| 7<br>10<br>. 1-12          |  |  |  |

|----------------------------|--|--|--|

|                            |  |  |  |

| . 1-12                     |  |  |  |

| . 1-12                     |  |  |  |

|                            |  |  |  |

| 1-13                       |  |  |  |

| 1-14                       |  |  |  |

| 1-15                       |  |  |  |

| . 1-16                     |  |  |  |

| MSC functional description |  |  |  |

| . 2-18                     |  |  |  |

| . 2-19                     |  |  |  |

| . 2-20                     |  |  |  |

| . 2-21                     |  |  |  |

| 2-22                       |  |  |  |

| MPC functional description |  |  |  |

| 3-24                       |  |  |  |

| . 3-25                     |  |  |  |

| . 3-26                     |  |  |  |

|                            |  |  |  |

|            | 3.4                        | MPC Q-Channels                                    |            |  |

|------------|----------------------------|---------------------------------------------------|------------|--|

|            | 3.5                        | MPC AMBA bus properties                           |            |  |

| Chapter 4  | PPC                        | functional description                            |            |  |

|            | 4.1                        | About the PPC                                     |            |  |

|            | 4.2                        | PPC configuration options                         |            |  |

|            | 4.3                        | PPC interrupts                                    |            |  |

|            | 4.4                        | PPC Q-Channels                                    |            |  |

|            | 4.5                        | PPC AMBA bus properties                           | 4-34       |  |

| Chapter 5  | SMC functional description |                                                   |            |  |

|            | 5.1                        | About the SMC                                     | 5-36       |  |

|            | 5.2                        | SMC configuration options                         | 5-39       |  |

|            | 5.3                        | SMC Q-Channels                                    | 5-40       |  |

|            | 5.4                        | External gating of the SRAM interface             | 5-41       |  |

|            | 5.5                        | SMC AMBA bus properties                           | 5-42       |  |

| Chapter 6  | ACG                        | G, SDB, and SUB functional description            |            |  |

|            | 6.1                        | About the bridge components                       |            |  |

|            | 6.2                        | Bridge configuration options                      |            |  |

|            | 6.3                        | Bridge upstream Q-Channels                        |            |  |

|            | 6.4                        | Bridge downstream Q-Channels                      |            |  |

|            | 6.5                        | Intra-bridge Q-Channels                           |            |  |

|            | 6.6                        | External gating of the AXI interface (upstream)   |            |  |

|            | 6.7                        | External gating of the AXI interface (downstream) |            |  |

|            | 6.8                        | AMBA bus properties for bridge components         |            |  |

| Chapter 7  | Prog                       | grammers model                                    |            |  |

|            | 7.1                        | About the programmers model                       |            |  |

|            | 7.2                        | Register summary                                  |            |  |

|            | 7.3                        | Register descriptions                             |            |  |

|            | 7.4                        | Gating AXI transactions during register updates   |            |  |

|            | 7.5                        | Programming the LUT                               |            |  |

|            | 7.6                        | Configuration lockdown                            |            |  |

| Appendix A | Signal descriptions        |                                                   |            |  |

|            | A.1                        | MSC signals                                       | Аррх-А-74  |  |

|            | A.2                        | MPC signals                                       | Аррх-А-80  |  |

|            | A.3                        | PPC signals                                       | Аррх-А-86  |  |

|            | A.4                        | SMC signals                                       | Аррх-А-92  |  |

|            | A.5                        | Bridge components signals                         | Аррх-А-95  |  |

| Appendix B | Revi                       | isions                                            |            |  |

|            | B.1                        | Revisions                                         | Аррх-В-106 |  |

# Preface

This preface introduces the Arm<sup>®</sup> CoreLink<sup>™</sup> SIE-300 AXI5 System IP for Embedded Technical Reference Manual.

It contains the following:

- *About this book* on page 7.

- Feedback on page 10.

### About this book

This book describes the functionality of the components in the Arm<sup>®</sup> CoreLink<sup>™</sup> SIE-300 AXI5 System IP for Embedded. It also provides the programming information and the signal descriptions.

#### Product revision status

The *rmpn* identifier indicates the revision status of the product described in this book, for example, r1p2, where:

- rm Identifies the major revision of the product, for example, r1.

- pn Identifies the minor revision or modification status of the product, for example, p2.

#### Intended audience

This book is written for system designers and programmers who are designing or programming a *System* on *Chip* (SoC) that uses the SIE-300.

#### Using this book

This book is organized into the following chapters:

#### **Chapter 1 Introduction**

This chapter introduces the SIE-300 AXI5 System IP for Embedded.

#### Chapter 2 MSC functional description

This chapter describes the functionality of the Master Security Controller (MSC) component.

#### **Chapter 3 MPC functional description**

This chapter describes the functionality of the Memory Protection Controller (MPC) component.

#### Chapter 4 PPC functional description

This chapter describes the functionality of the *Peripheral Protection Controller* (PPC) component.

#### **Chapter 5 SMC functional description**

This chapter describes the functionality of the SRAM Memory Controller (SMC) component.

#### Chapter 6 ACG, SDB, and SUB functional description

This chapter describes the functionality of the three bridge components, that is, the Access Control Gate, Sync-Down Bridge, and Sync-Up Bridge.

#### Chapter 7 Programmers model

This chapter describes the memory regions and registers that the *Memory Protection Controller* (MPC) provides.

#### Appendix A Signal descriptions

This appendix describes the interface signals that are present for each SIE-300 component.

#### Appendix B Revisions

This appendix describes the technical changes between released issues of this book.

#### Glossary

The Arm<sup>®</sup> Glossary is a list of terms used in Arm documentation, together with definitions for those terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

See the Arm® Glossary for more information.

#### **Typographic conventions**

italic

Introduces special terminology, denotes cross-references, and citations.

#### bold

Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.

#### monospace

Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.

#### <u>mono</u>space

Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.

#### monospace italic

Denotes arguments to monospace text where the argument is to be replaced by a specific value.

#### monospace bold

Denotes language keywords when used outside example code.

#### <and>

Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example:

MRC p15, 0, <Rd>, <CRn>, <CRm>, <Opcode\_2>

#### SMALL CAPITALS

Used in body text for a few terms that have specific technical meanings, that are defined in the *Arm*<sup>®</sup> *Glossary*. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE.

#### **Timing diagrams**

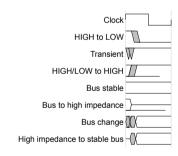

The following figure explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

#### Figure 1 Key to timing diagram conventions

#### Signals

The signal conventions are:

#### Signal level

The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

- HIGH for active-HIGH signals.

- LOW for active-LOW signals.

#### Lowercase n

At the start or end of a signal name, n denotes an active-LOW signal.

#### Additional reading

This book contains information that is specific to this product. See the following documents for other relevant information.

#### Arm publications

- AMBA® AXI and ACE Protocol Specification (IHI 0022).

- AMBA® APB Protocol Specification Version 2.0 (IHI 0024).

- AMBA<sup>®</sup> Low Power Interface Specification, Arm<sup>®</sup> Q-Channel and P-Channel Interfaces (IHI 0068).

The following confidential books are only available to licensees or require registration with Arm:

• Arm<sup>®</sup> CoreLink<sup>™</sup> SIE-300 AXI5 System IP for Embedded Configuration and Integration Manual (101527).

#### Other publications

• JEDEC, Standard Manufacturer's Identification Code, JEP106.

# Feedback

#### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

#### Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- The title Arm CoreLink SIE-300 AXI5 System IP for Embedded Technical Reference Manual.

- The number 101526 0101 03 en.

- If applicable, the page number(s) to which your comments refer.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

\_\_\_\_\_ Note \_\_\_\_\_

Arm tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader.

# Chapter 1 Introduction

This chapter introduces the SIE-300 AXI5 System IP for Embedded.

It contains the following sections:

- 1.1 About the AXI5 System IP for Embedded on page 1-12.

- *1.2 Compliance* on page 1-13.

- *1.3 Configurable options* on page 1-14.

- 1.4 Product documentation on page 1-15.

- 1.5 Product revisions on page 1-16.

# 1.1 About the AXI5 System IP for Embedded

The SIE-300 AXI5 System IP for Embedded provides a set of configurable AXI5 security-aware components. The components can protect peripherals and memories that are unaware of security, so that a peripheral or memory is only accessible to trusted software. The SIE-300 also provides clock synchronizing bridges and an access control gate.

The SIE-300 consists of the following components:

#### Master Security Controller (MSC)

The MSC acts as security gate for AXI transactions, and it can transform the security attribute.

#### Memory Protection Controller (MPC)

The MPC acts as security gate for AXI transactions that target a memory interface. The security checks operate on block or page level, and are programmable by using the APB slave interface.

#### **Peripheral Protection Controller (PPC)**

The PPC gates AXI5 transactions to, and responses from, peripherals when a security violation occurs.

#### Access Control Gate (ACG)

The ACG component can be placed on a clock or power domain boundary to pass or block AXI5 transactions whenever the downstream component cannot accept the transaction, or is explicitly asked not to do so. The transaction is latched internally and the ACG generates automatic responses when necessary.

#### Sync-Down Bridge (SDB)

The SDB synchronizes AXI5 interfaces where the upstream side is faster than the downstream side, and the clocks are synchronous, in phase, and have an N:1 frequency ratio.

#### Sync-Up Bridge (SUB)

The SUB synchronizes AXI5 interfaces where the upstream side is slower than the downstream side, and the clocks are synchronous, in phase, and have a 1:N frequency ratio.

#### **SRAM Memory Controller (SMC)**

The SMC enables on-chip synchronous RAM blocks to attach to an AXI5 interface. The SMC supports 32, 64, 128, or 256-bit SRAM with byte writes.

# 1.2 Compliance

The SIE-300 AXI5 System IP for Embedded is compliant with Arm specifications and protocols.

The SIE-300 components are compliant with the:

- AMBA 5 AXI protocol. See the AMBA® AXI and ACE Protocol Specification.

- AMBA 4 APB protocol. See the AMBA® APB Protocol Specification Version 2.0.

- AMBA Low Power Interface specification. See the AMBA<sup>®</sup> Low Power Interface Specification, Arm<sup>®</sup> Q-Channel and P-Channel Interfaces.

This *Technical Reference Manual* (TRM) complements the architecture specifications and protocol specifications. The TRM does not duplicate information from these sources.

# 1.3 Configurable options

The SIE-300 provides design-time configuration options for each component. These options enable the design team to configure a component so that it is suitable for its location in an SoC.

#### **Related concepts**

- 2.2 MSC configuration options on page 2-19

- 3.2 MPC configuration options on page 3-25

- 4.2 PPC configuration options on page 4-31

- *5.2 SMC configuration options* on page 5-39

- 6.2 Bridge configuration options on page 6-46

## 1.4 Product documentation

Documentation that is provided with this product includes a *Technical Reference Manual* (TRM) and a *Configuration and Integration Manual* (CIM), together with architecture and protocol information.

For relevant protocol and architectural information that relates to this product, see *Additional reading* on page 9.

The SIE-300 documentation is as follows:

#### **Technical Reference Manual**

The TRM describes the functionality and the effects of functional options on the behavior of SIE-300. It is required at all stages of the design flow. The choices that are made in the design flow can mean that some behaviors that the TRM describes are not relevant. If you are programming SIE-300, contact:

- The implementer to determine:

- The build configuration of the implementation.

- What integration, if any, was performed before implementing SIE-300.

- The integrator to determine the signal configuration of the device that you use.

The TRM complements architecture and protocol specifications and relevant external standards. It does not duplicate information from these sources.

#### **Configuration and Integration Manual**

The CIM describes:

- The available build configuration options.

- How to configure the RTL with the build configuration options.

- How to integrate SIE-300 into an SoC.

- How to implement SIE-300 into your design.

- The processes to validate the configured design.

The Arm product deliverables include reference scripts and information about using them to implement your design.

The CIM is a confidential book that is only available to licensees.

# 1.5 **Product revisions**

This section describes the differences in functionality between product revisions.

r0p0 First release.

- **r0p0-r1p0** The functional changes are:

- Added the **cfg\_ext\_gt\_err\_resp** configuration signal. See *Configuration interface* on page 6-45.

- Changed the SMC arbitration scheme. See *Read and write transaction scheduling* on page 5-37.

- Changed the eviction of an SMC TAG table entry, when all EAMs are occupied. See *Exclusive accesses* on page 5-37.

- Changed when the SMC samples cfg\_gate\_resp. See *Table A-31 SMC external-gating configuration signal* on page Appx-A-94.

r1p0-r1p1 No functional changes.

# Chapter 2 MSC functional description

This chapter describes the functionality of the Master Security Controller (MSC) component.

It contains the following sections:

- 2.1 About the MSC on page 2-18.

- 2.2 MSC configuration options on page 2-19.

- 2.3 MSC interrupts on page 2-20.

- 2.4 MSC Q-Channels on page 2-21.

- 2.5 MSC AMBA bus properties on page 2-22.

# 2.1 About the MSC

The *Master Security Controller* (MSC) acts as security gate for AXI transactions, and it can transform the security attribute.

The MSC enables AXI masters that are designed for A-class systems to be inserted into M-class systems. Since A-class and M-class systems handle security differently, the MSC can transform the security attributes of a transaction to satisfy the M-class requirements.

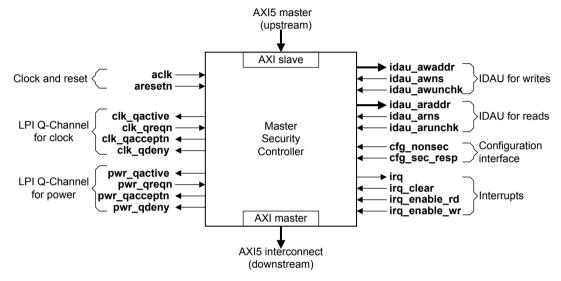

The following figure shows the MSC interfaces.

Figure 2-1 MSC interfaces

The AXI slave and AXI master interfaces provide the AXI data path from the AXI master to the interconnect.

To support low-power quiescence, the MSC has two Q-Channel interfaces. One Q-Channel is for clock quiescence and the other Q-Channel is for power quiescence.

#### **Configuration interface**

The **cfg\_nonsec** input tells the MSC whether the AXI5 master, which connects to its slave interface, is in the Secure state or the Non-secure state. The MSC uses this information to control whether it blocks a transaction from going downstream.

When the MSC blocks a transaction, the cfg\_sec\_resp controls whether the MSC:

- Responds with an AXI slave error (SLVERR).

- Ignores a write transaction or returns zero for a read transaction.

#### **IDAU** interfaces

The MSC has two *Implementation Defined Attribution Unit* (IDAU) interfaces that it uses to discover the Security state of an addressed region. One IDAU is for read transactions and the other IDAU is for write transactions.

When the MSC receives an AXI transaction, it accesses the corresponding IDAU and retrieves the Security state for that transaction address. By using the Security state information, the incoming AXI access permissions (**AxPROT**), and the state of **cfg\_nonsec**, the MSC can do one of the following:

- Block the transaction from going downstream.

- Forward the transaction.

- Transform the security attributes and then forward the transaction.

# 2.2 MSC configuration options

The MSC has design options that configure some AXI signal widths and the presence of synchronization logic on the Q-Channel inputs.

When implementing the MSC in an SoC, you can configure:

- The width of the AXI data bus, by using the DATA\_WIDTH parameter. The possible widths are 32, 64, 128, or 256 bits.

- The width of the ID signals on the AXI interfaces, by using the ID\_WIDTH parameter. The parameter can be set to a value from 2-32 inclusive.

- The width of the User signals on each AXI channel, by using the ARUSER\_WIDTH, AWUSER\_WIDTH, BUSER\_WIDTH, RUSER\_WIDTH, and WUSER\_WIDTH parameters. A parameter can be set to a value from 0-256 inclusive.

- The presence of a synchronizer on the Q-Channel **QREQn** inputs. See 2.4 MSC Q-Channels on page 2-21.

# 2.3 MSC interrupts

The MSC has a level-sensitive interrupt output, **irq**, that can indicate the occurrence of a security violation or a faulty security attribute conversion.

For read transactions, the **irq\_enable\_rd** signal controls whether the MSC can set **irq** HIGH when a security violation or a faulty security attribute conversion occurs during a read transaction.

For write transactions, the **irq\_enable\_wr** signal controls whether the MSC can set **irq** HIGH when a security violation or a faulty security attribute conversion occurs during a write transaction.

## 2.4 MSC Q-Channels

The MSC provides two Q-Channel device interfaces. You can use one channel for clock control and the other channel for power control, which enables the MSC to indicate when it requires clock and power.

Both Q-Channels implement the low-power interfaces that the *AMBA*<sup>®</sup> *Low Power Interface Specification, Arm*<sup>®</sup> *Q*-*Channel and P-Channel Interfaces* describes.

The presence of a synchronizer on the **clk\_qreqn** and **pwr\_qreqn** inputs of the Q-Channels is configurable, by using the QCLK\_SYNC\_EN and QPWR\_SYNC\_EN parameters.

# 2.5 MSC AMBA bus properties

The AMBA protocols define multiple property types that indicate the capabilities of a device. The following table lists the AXI5 properties of the MSC.

#### Table 2-1 MSC AXI5 properties

| AXI5 property             | Value | Comment                                                                                                          |

|---------------------------|-------|------------------------------------------------------------------------------------------------------------------|

| Wakeup_Signals            | TRUE  | Q-Channel activity is generated from the <b>awakeup</b> input signal.                                            |

| Check_Type                | FALSE | -                                                                                                                |

| Poison                    | TRUE  | The component forwards the poison data downstream, it does not use the information that the poison bits contain. |

| Trace_Signals             | FALSE | -                                                                                                                |

| QoS_Accept                | FALSE | -                                                                                                                |

| Loopback_Signals          | FALSE | -                                                                                                                |

| Untranslated_Transactions | FALSE | -                                                                                                                |

| NSAccess_Identifiers      | FALSE | -                                                                                                                |

| Atomic_Transactions       | FALSE | -                                                                                                                |

# Chapter 3 MPC functional description

This chapter describes the functionality of the Memory Protection Controller (MPC) component.

It contains the following sections:

- *3.1 About the MPC* on page 3-24.

- 3.2 MPC configuration options on page 3-25.

- 3.3 MPC interrupts on page 3-26.

- 3.4 MPC Q-Channels on page 3-27.

- 3.5 MPC AMBA bus properties on page 3-28.

### 3.1 About the MPC

The *Memory Protection Controller* (MPC) acts as security gate for AXI transactions that target a memory interface. The security checks operate on block or page level, and are programmable by using the APB slave interface.

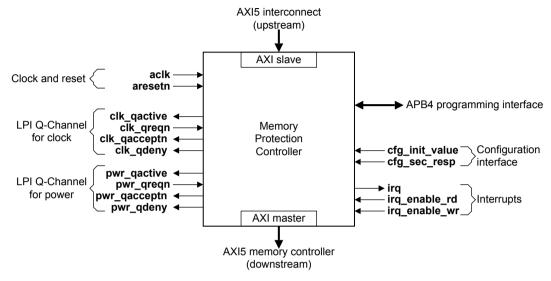

The following figure shows the MPC interfaces.

Figure 3-1 MPC interfaces

The AXI slave and AXI master interfaces provide the AXI data path from the interconnect to the memory controller.

To support low-power quiescence, the MPC has two Q-Channel interfaces. One Q-Channel is for clock quiescence and the other Q-Channel is for power quiescence.

#### **Configuration interface**

At powerup, the MPC uses the value of the **cfg\_init\_value** input as the initialization value for the *Look Up Table* (LUT) to be Secure or Non-secure for the entire memory range that the MPC protects.

If a security violation occurs, the MPC generates an interrupt and the **cfg\_sec\_resp** controls whether the MPC:

- Responds with an AXI slave error (SLVERR).

- Ignores a write transaction or returns zero for a read transaction.

\_\_\_\_\_ Note \_\_\_\_\_

• When accessing all internal registers (except for the PID/CID registers) with a Secure but unprivileged APB transaction, the response is always RAZ/WI, regardless of the value of the **cfg\_sec\_resp** input signal.

<sup>•</sup> When accessing all internal registers (except for the PID/CID registers) with a Non-secure APB transaction, the response is either an error or RAZ/WI depending on the value of the **cfg\_sec\_resp** input signal. See *Table A-8 MSC configuration signals* on page Appx-A-78 for more information.

# 3.2 MPC configuration options

The MPC has design options that configure the memory block size, the widths of some AXI signals, and the presence of synchronization logic on the Q-Channel inputs. You can also configure the MPC to support the AXI transaction gating feature.

When implementing the MPC in an SoC, you can configure:

- The width of the AXI address bus, by using the ADDR\_WIDTH parameter. The parameter can be set to a value from 12-32 inclusive.

- The width of the AXI data bus, by using the DATA\_WIDTH parameter. The possible widths are 32, 64, 128, or 256 bits.

- The width of the ID signals on the AXI interfaces, by using the ID\_WIDTH parameter. The parameter can be set to a value from 2-32 inclusive.

- The width of the User signals on each AXI channel, by using the ARUSER\_WIDTH, AWUSER\_WIDTH, BUSER\_WIDTH, RUSER\_WIDTH, and WUSER\_WIDTH parameters. A parameter can be set to a value from 0-256 inclusive.

- The size of a memory block, by using the BLK\_SIZE parameter. The block size can be 256 bytes to 1MB. See 7.3.3 Block LUT configuration status register; BLK\_CFG on page 7-58 for the possible values.

- The MPC to support the AXI transaction gating feature, by using the GATE\_PRESENT parameter. See 7.4 Gating AXI transactions during register updates on page 7-70 for more information.

- The presence of a synchronizer on the Q-Channel **QREQn** inputs. See *3.4 MPC Q-Channels* on page 3-27.

# 3.3 MPC interrupts

The MPC has a level-sensitive interrupt output, **irq**, that can indicate the occurrence of a security violation.

If a security violation occurs when **irq** is LOW, and the corresponding **irq\_enable\_**\* signal is HIGH, the MPC saves information about the violation in the IRQ\_STAT, IRQ\_INFO1, and IRQ\_INFO2 registers. Also, if the IRQ\_EN register bit is set to 1 and the corresponding **irq\_enable\_**\* signal is HIGH, then the MPC sets the **irq** interrupt HIGH. The **irq** signal remains HIGH until the IRQ\_CLEAR register is written to.

\_\_\_\_\_ Note \_\_\_\_\_

- If more security violations occur, then the MPC does not update the IRQ\_STAT, IRQ\_INFO1, and IRQ\_INFO2 registers. However, if a security violation occurs while already in interrupt and **irq\_enable\_\*** is set, then the MPC does update the IRQ\_INFO2.ERR\_MULTI bit.

- When IRQ\_EN.IRQ\_EN == 0 and **irq** is LOW, if coincident violations occur for a read transaction and a write transaction, the MPC saves information about the read violation in the IRQ\_STAT, IRQ\_INFO1, and IRQ\_INFO2 registers.

#### Disabling interrupts for memory accesses from a debugger

If the IRQ\_SET register bit is set to 0, a debugger can use the **irq\_enable\_**\* signals to prevent interrupt generation when it accesses memory regions. The **irq\_enable\_rd** signal controls whether the MPC can set **irq** HIGH when a security violation occurs during a read transaction. The **irq\_enable\_wr** signal controls whether the MPC can set **irq** HIGH when a security violation occurs during a write transaction. The **irq\_enable\_**\* signals also prevent the saving of the violating transaction to IRQ\_INFO1 and IRQ\_INFO2 registers.

---- Note -

If the IRQ\_SET register bit is set to 1, then the MPC ignores the **irq\_enable\_\*** signals and generates interrupts when IRQ\_EN.IRQ\_EN == 1.

## 3.4 MPC Q-Channels

The MPC provides two Q-Channel interfaces. You can use one channel for clock control and the other channel for power control, which enables the MPC to indicate when it requires clock and power.

Both Q-Channels implement the low-power interfaces that the *AMBA*<sup>®</sup> *Low Power Interface Specification, Arm*<sup>®</sup> *Q*-*Channel and P-Channel Interfaces* describes.

The presence of a synchronizer on the **clk\_qreqn** and **pwr\_qreqn** inputs of the Q-Channels is configurable, by using the QCLK\_SYNC\_EN and QPWR\_SYNC\_EN parameters.

# 3.5 MPC AMBA bus properties

The AMBA protocols define multiple property types that indicate the capabilities of a device. The following table lists the AXI5 properties of the MPC.

#### Table 3-1 MPC AXI5 properties

| AXI5 property             | Value | Comment                                                                                                          |

|---------------------------|-------|------------------------------------------------------------------------------------------------------------------|

| Wakeup_Signals            | TRUE  | Q-Channel activity is generated from the <b>awakeup</b> input signal.                                            |

| Check_Type                | FALSE | -                                                                                                                |

| Poison                    | TRUE  | The component forwards the poison data downstream, it does not use the information that the poison bits contain. |

| Trace_Signals             | FALSE | -                                                                                                                |

| QoS_Accept                | FALSE | -                                                                                                                |

| Loopback_Signals          | FALSE | -                                                                                                                |

| Untranslated_Transactions | FALSE | -                                                                                                                |

| NSAccess_Identifiers      | FALSE | -                                                                                                                |

| Atomic_Transactions       | FALSE | -                                                                                                                |

# Chapter 4 **PPC functional description**

This chapter describes the functionality of the Peripheral Protection Controller (PPC) component.

It contains the following sections:

- *4.1 About the PPC* on page 4-30.

- 4.2 PPC configuration options on page 4-31.

- *4.3 PPC interrupts* on page 4-32.

- 4.4 PPC Q-Channels on page 4-33.

- 4.5 PPC AMBA bus properties on page 4-34.

# 4.1 About the PPC

The Peripheral Protection Controller (PPC) provides security checks for AXI peripherals.

The PPC gates AXI transactions towards a peripheral when a security violation occurs. It can be instantiated in the system in connection to any non-security aware AXI5 peripheral. Security checking is performed against the state of the **cfg\_ap** and **cfg\_nonsec** signals, which indicate the privilege and Security state of the peripheral.

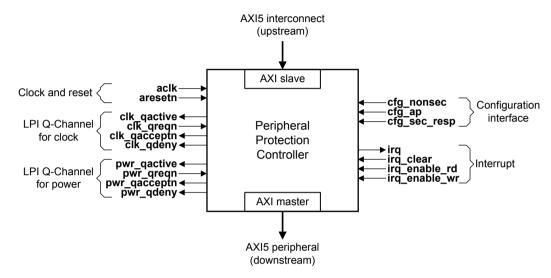

The following figure shows the PPC interfaces.

#### Figure 4-1 PPC interfaces

The AXI slave and AXI master interfaces provide the AXI data path from the AXI master to the attached peripheral.

To support low-power quiescence, the PPC has two Q-Channel interfaces. One Q-Channel is for clock quiescence and the other Q-Channel is for power quiescence.

#### **Configuration interface**

The **cfg\_nonsec** signal controls the security settings of the attached peripheral:

- If HIGH, only Non-secure accesses to the peripheral are allowed.

- If LOW, only Secure accesses to the peripheral are allowed.

The cfg\_ap signal controls the privilege settings of the attached peripheral:

- If HIGH, only privileged accesses to the peripheral are allowed.

- If LOW, the privilege attribute is ignored for security checks.

When the PPC blocks a transaction, the cfg\_sec\_resp signal controls whether the PPC:

- Responds with an AXI slave error (SLVERR).

- Ignores a write transaction or returns zero for a read transaction.

# 4.2 PPC configuration options

The PPC has design options that configure some AXI signal widths and the presence of synchronization logic on the Q-Channel inputs.

When implementing the PPC in an SoC, you can configure:

- The width of the AXI address bus, by using the ADDR\_WIDTH parameter. The parameter can be set to a value from 12-32 inclusive.

- The width of the AXI data bus, by using the DATA\_WIDTH parameter. The possible widths are 32, 64, 128, or 256 bits.

- The width of the ID signals on the AXI interfaces, by using the ID\_WIDTH parameter. The parameter can be set to a value from 2-32 inclusive.

- The width of the User signals on each AXI channel, by using the ARUSER\_WIDTH, AWUSER\_WIDTH, BUSER\_WIDTH, RUSER\_WIDTH, and WUSER\_WIDTH parameters. A parameter can be set to a value from 0-256 inclusive.

- The presence of a synchronizer on the Q-Channel **QREQn** inputs. See 4.4 PPC Q-Channels on page 4-33.

# 4.3 **PPC interrupts**

The PPC has a level-sensitive interrupt output, **irq**, that can indicate the occurrence of a security violation.

For read transactions, the **irq\_enable\_rd** signal controls whether the PPC can set **irq** HIGH when a security violation occurs during a read transaction.

For write transactions, the **irq\_enable\_wr** signal controls whether the PPC can set **irq** HIGH when a security violation occurs during a write transaction.

# 4.4 PPC Q-Channels

The PPC provides two Q-Channel interfaces for power and clock control. You can use one channel for clock control and the other channel for power control, which enables the PPC to indicate when it requires clock and power.

Both Q-Channels implement the low-power interfaces that the *AMBA*<sup>®</sup> *Low Power Interface Specification, Arm*<sup>®</sup> *Q*-*Channel and P-Channel Interfaces* describes.

The presence of a synchronizer on the **clk\_qreqn** and **pwr\_qreqn** inputs of the Q-Channels is configurable, by using the QCLK\_SYNC\_EN and QPWR\_SYNC\_EN parameters.

# 4.5 **PPC AMBA bus properties**

The AMBA protocols define multiple property types that indicate the capabilities of a device. The following table lists the AXI5 properties of the PPC.

#### Table 4-1 PPC AXI5 properties

| AXI5 property             | Value | Comment                                                                                                          |

|---------------------------|-------|------------------------------------------------------------------------------------------------------------------|

| Wakeup_Signals            | TRUE  | Q-Channel activity is generated from the <b>awakeup</b> input signal.                                            |

| Check_Type                | FALSE | -                                                                                                                |

| Poison                    | TRUE  | The component forwards the poison data downstream, it does not use the information that the poison bits contain. |

| Trace_Signals             | FALSE | -                                                                                                                |

| QoS_Accept                | FALSE | -                                                                                                                |

| Loopback_Signals          | FALSE | -                                                                                                                |

| Untranslated_Transactions | FALSE | -                                                                                                                |

| NSAccess_Identifiers      | FALSE | -                                                                                                                |

| Atomic_Transactions       | FALSE | -                                                                                                                |

# Chapter 5 SMC functional description

This chapter describes the functionality of the SRAM Memory Controller (SMC) component.

It contains the following sections:

- 5.1 About the SMC on page 5-36.

- 5.2 SMC configuration options on page 5-39.

- 5.3 SMC Q-Channels on page 5-40.

- 5.4 External gating of the SRAM interface on page 5-41.

- 5.5 SMC AMBA bus properties on page 5-42.

## 5.1 About the SMC

The SRAM Memory Controller (SMC) is an AXI5 memory controller for static memory devices.

The SMC has the following features:

- A single clock and reset domain.

- An AXI5 slave interface.

- An SRAM interface.

- Two Q-Channels for clock and power control.

- No data width conversion.

- An external-gating interface that prevents the SMC from issuing new transactions on the SRAM interface.

\_\_\_\_\_ Note \_\_\_\_\_

The SRAM controller primarily supports memory macros that the Arm SRAM Compiler generates.

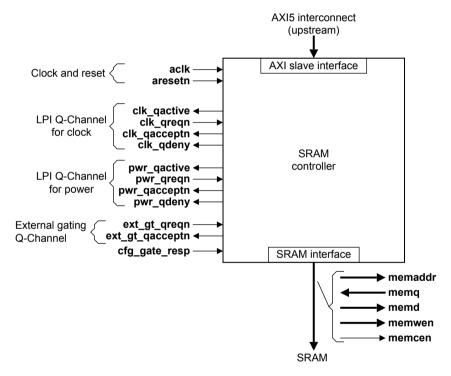

The following figure shows the SMC interfaces.

Figure 5-1 SMC interfaces

To support low-power quiescence, the SMC has two Q-Channel device interfaces. One Q-Channel is for clock quiescence and the other Q-Channel is for power quiescence.

The SMC also provides a partial Q-Channel device interface to support external gating, which stops the SMC from starting any new transactions on the SRAM interface. See *5.4 External gating of the SRAM interface* on page 5-41.

#### Early write response

The SMC buffers the write transactions and for non-exclusive writes it returns an early write response. If the write buffers become full, then the SMC does not return an early write response.

#### Read and write transaction scheduling

The AXI has separate buses for reads and writes, but the SRAM interface is a single bus for reads and writes. Therefore, the SMC must arbitrate between the AXI channels. The SMC performs arbitration between read and write bursts.

If the write buffers become full, then the arbitration scheme uses the QoS value of the incoming read, **arqos**, and write, **awqos** signal. For example, if the SMC receives a write with a QoS value that is higher than the read QoS, it forwards the oldest transaction from the write queue to the SRAM to allow the new write into the write buffer.

\_\_\_\_\_ Note \_\_\_\_\_

Provided the write buffers (address or data) are not full, the SMC gives priority to read bursts.

To prevent system livelock or starvation issues, the SMC uses a balancing counter to track how many read bursts are granted while a write burst request is present but not granted. If this counter reaches a predefined value, then the SMC grants the write at the next arbitration point, regardless of the QoS values.

#### Poison

The AX15\_POISON\_EN configuration parameter controls whether the SMC supports data poisoning.

When data poisoning is enabled, the SMC provides 1 bit of poison information for each 64 bits of data. The SMC uses the MSB of the **memwen** write enable bus on the SRAM memory side to control the writes to the storage element that holds the poison information.

—— Note —

When narrow writes are written to the SRAM, the poison information always gets updated with the new value, regardless of the previously stored content.

The following table lists which signals contain the poison information for different DATA\_WIDTH configurations.

#### Table 5-1 Poison bit locations

| DATA_WIDTH | AXI poison bits               | Poison bits on the SRAM interface |

|------------|-------------------------------|-----------------------------------|

| 32         | wpoison[0] and rpoison[0]     | memd[32] and memq[32]             |

| 64         | wpoison[0] and rpoison[0]     | memd[64] and memq[64]             |

| 128        | wpoison[1:0] and rpoison[1:0] | memd[129:128] and memq[129:128]   |

| 256        | wpoison[3:0] and rpoison[3:0] | memd[259:256] and memq[259:256]   |

#### **Exclusive accesses**

The SMC can contain up to 16 *Exclusive Access Monitors* (EAMs), depending on the setting of the EXCLUSIVE\_MONITORS configuration parameter.

If EXCLUSIVE\_MONITORS > 0, then Exclusive Load transactions always return an EXOKAY response and the SMC stores the transaction details (address, ID) in an internal TAG buffer.

For Exclusive Store transactions, the SMC checks if the address and ID are present in the TAG buffer, and if so the SMC forwards the write to the SRAM and returns an EXOKAY write response. If the check fails, the SMC ignores the write data and it returns an OKAY response, which indicates an exclusive access failure.

If a non-exclusive write transaction accesses a location that is stored in a TAG buffer, then the SMC clears the TAG.

If all EAMs are occupied, and the SMC receives a new Exclusive Load transaction with an:

- ID that exists in the TAG table, then the new transaction replaces an old entry.

- ID that does not exist in the TAG table, then the SMC overwrites an entry in the TAG table that the round-robin algorithm selects, and returns an EXOKAY response.

If an SMC is configured to contain no EAMs (EXCLUSIVE\_MONITORS == 0), then exclusive writes always fail. The SMC ignores the write and returns an OKAY response.

# 5.2 SMC configuration options

The SMC has design options that configure the number of *Exclusive Access Monitors*, the FIFO depths, and whether the first cycle of an AXI read transaction can bypass an AXI channel buffer. There are also options to set the widths of some AXI signals, and the presence of synchronization logic on the Q-Channel inputs. You can also configure the SMC to support AXI data poisoning.

When implementing the SMC in an SoC, you can configure:

- The width of the AXI address bus, by using the ADDR\_WIDTH parameter. The parameter can be set to a value from 14-24 inclusive.

- The width of the AXI data bus, by using the DATA\_WIDTH parameter. The possible widths are 32, 64, 128, or 256 bits.

- The width of the ID signals on the AXI interfaces, by using the ID\_WIDTH parameter. The parameter can be set to a value from 2-32 inclusive.

- The number of exclusive access monitors, which observe and track AXI exclusive access transactions. The EXCLUSIVE\_MONITORS parameter can be set to a value from 0-16 inclusive. The number of exclusive monitors must be less than 2<sup>ID\_WIDTH</sup>, since any given ID is only stored in one of the monitors. If a new exclusive read occurs with the same ID, then the tracked address is updated.

- The FIFO depth on the AR channel. The AR\_BUF\_SIZE parameter can be set to a value from 1-16 inclusive.

- The FIFO depth on the AW channel. The AW\_BUF\_SIZE parameter can be set to a value from 1-16 inclusive.

- The FIFO depth on the W channel. The W\_BUF\_SIZE parameter can be set to a value from 1-16 inclusive.

- The SMC to bypass the AR channel buffer for the first cycle of an AXI read transaction.

- The SMC to bypass the R channel buffer for the first cycle of an AXI read transaction.

- The SMC to support AXI data poisoning, by using the AXI5\_POISON\_EN parameter. See *Poison* on page 5-37.

- The presence of a synchronizer on the Q-Channel **QREQn** inputs. See 5.3 SMC Q-Channels on page 5-40.

# 5.3 SMC Q-Channels

The SMC provides two Q-Channel interfaces for power and clock control. You can use one channel for clock control and the other channel for power control, which enables the SMC to indicate when it requires clock and power.

Both Q-Channels implement the low-power interfaces that the *AMBA*<sup>®</sup> *Low Power Interface Specification, Arm*<sup>®</sup> *Q*-*Channel and P-Channel Interfaces* describes.

The presence of a synchronizer on the **clk\_qreqn** and **pwr\_qreqn** inputs of the Q-Channels is configurable, by using the QCLK\_SYNC\_EN and QPWR\_SYNC\_EN parameters.

# 5.4 External gating of the SRAM interface

The SMC has a partial Q-Channel device interface. An external device can use the Q-Channel interface to gate transactions on the SRAM interface.

The external gating Q-Channel interface moves the SMC to a state that forcefully stops all activities towards the SRAM, when **ext\_gt\_qreqn** goes LOW. The SMC cannot deny an external gating request.

The SMC accepts an external gating request when there is no ongoing transfer and its internal buffers are empty. After the SMC sets **ext\_gt\_qacceptn** LOW, the system can apply the reset without the risk of data loss.

If the SMC receives a new AXI transaction while **ext\_gt\_qreqn** and **ext\_gt\_qacceptn** are LOW (Q\_STOPPED state), then the **cfg\_gate\_resp** signal controls whether the SMC:

- Responds with an AXI slave error (SLVERR).

- Stalls the transaction until the external gating request is released, that is, ext\_gt\_qreqn goes HIGH.

# 5.5 SMC AMBA bus properties

The AMBA protocols define multiple property types that indicate the capabilities of a device. The following table lists the AXI5 properties of the SMC.

## Table 5-2 SMC AXI5 properties

| AXI5 property             | Value                             | Comment                                                                      |

|---------------------------|-----------------------------------|------------------------------------------------------------------------------|

| Wakeup_Signals            | TRUE                              | Q-Channel activity is generated from the <b>awakeup</b> input signal.        |

| Check_Type                | FALSE                             | -                                                                            |

| Poison                    | TRUE when $AXI5_POISON_EN == 1$ . | Optional feature that depends on the AXI5_POISON_EN configuration parameter. |

| Trace_Signals             | FALSE                             | -                                                                            |

| QoS_Accept                | FALSE                             | -                                                                            |

| Loopback_Signals          | FALSE                             | -                                                                            |

| Untranslated_Transactions | FALSE                             | -                                                                            |

| NSAccess_Identifiers      | FALSE                             | -                                                                            |

| Atomic_Transactions       | FALSE                             | -                                                                            |

# Chapter 6 ACG, SDB, and SUB functional description

This chapter describes the functionality of the three bridge components, that is, the Access Control Gate, Sync-Down Bridge, and Sync-Up Bridge.

It contains the following sections:

- 6.1 About the bridge components on page 6-44.

- 6.2 Bridge configuration options on page 6-46.

- 6.3 Bridge upstream Q-Channels on page 6-47.

- 6.4 Bridge downstream Q-Channels on page 6-48.

- 6.5 Intra-bridge Q-Channels on page 6-49.

- 6.6 External gating of the AXI interface (upstream) on page 6-50.

- 6.7 External gating of the AXI interface (downstream) on page 6-51.

- 6.8 AMBA bus properties for bridge components on page 6-52.

# 6.1 About the bridge components

Bridge components provide low-power management and external gating on boundaries between clock and power domains along the AXI5 data bus. They also have configurable registering options to ease timing on long AXI5 paths.

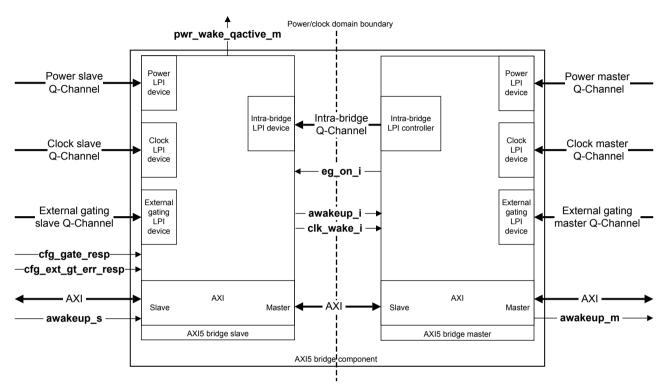

The following figure shows the interfaces of a bridge component.

#### Figure 6-1 Bridge component interfaces

The following table lists the SIE-300 bridge components.

## Table 6-1 Supported bridge components

| Bridge component          | Upstream to downstream clock ratio |

|---------------------------|------------------------------------|

| Access Control Gate (ACG) | One-to-one                         |

| Sync-Down Bridge (SDB)    | N-to-one                           |

| Sync-Up Bridge (SUB)      | One-to-N                           |

Each bridge component consists of an upstream side and a downstream side. To allow communication across clock and power domains, each side of the bridge has one intra-bridge Q-Channel interface and one intra-bridge AXI interface. The **eg\_on\_i** signal provides the upstream side with information about the state of external gating on the downstream side. The intra-bridge uses a standard Q-Channel LPI interface.

Each half of a bridge component supports the following features:

- A single clock and reset domain.

- An AXI5 slave interface.

- An AXI5 master interface.

- Two Q-Channels for clock and power control to support low-power quiescence.

- An external-gating interface that prevents the bridge component from issuing new transactions on the AXI interface. The external-gating interface is a Q-Channel implementation without the **QDENY** and **QACTIVE** signals.

#### **Configuration interface**

The **cfg\_gate\_resp** controls how the upstream side of the bridge component responds, when the bridge is closed by external gating or downstream power quiescence:

- Responds with an AXI slave error (SLVERR).

- The bridge component sets the relevant AXI **ready** signals LOW, which stalls any AXI transactions, until the bridge is able to forward the transfers to the downstream side.

The **cfg\_ext\_gt\_err\_resp** signal controls how the bridge component responds to AXI transactions, when the upstream external gating is in quiescence. However, if the **cfg\_gate\_resp** is set to error, then the bridge returns an error response. Therefore, when the upstream external gating is in quiescence, the bridge:

- Responds with an AXI slave error (SLVERR), when cfg\_gate\_resp or cfg\_ext\_gt\_err\_resp are HIGH.

- Stalls the transaction until the external gating request is released, that is, ext\_gt\_qreqn\_s goes HIGH. This response behavior requires that cfg\_gate\_resp and cfg\_ext\_gt\_err\_resp are LOW.

# 6.2 Bridge configuration options

The bridge components have design options that configure some AXI signal widths and the presence of synchronization logic on the Q-Channel inputs. You can also configure the presence of a register slice on each AXI channel.

When implementing the Access Control Gate, Sync-Down Bridge, or Sync-Up Bridge in an SoC, you can configure:

- The width of the AXI address bus, by using the ADDR\_WIDTH parameter. The parameter can be set to a value from 12-32 inclusive.

- The width of the AXI data bus, by using the DATA\_WIDTH parameter. The possible widths are 32, 64, 128, or 256 bits.

- The width of the ID signals on the AXI interfaces, by using the ID\_WIDTH parameter. The parameter can be set to a value from 2-32 inclusive.

- The width of the User signals on each AXI channel, by using the ARUSER\_WIDTH, AWUSER\_WIDTH, BUSER\_WIDTH, RUSER\_WIDTH, and WUSER\_WIDTH parameters. A parameter can be set to a value from 0-256 inclusive.

- The presence of a register slice on each AXI channel, and which direction the registering is applied.

- The presence of a synchronizer on the Q-Channel QREQn inputs. See:

- 6.3 Bridge upstream Q-Channels on page 6-47.

- 6.4 Bridge downstream Q-Channels on page 6-48.

# 6.3 Bridge upstream Q-Channels

The upstream side of each bridge component provides three Q-Channel interfaces for power, clock, and external gate control.

Each Q-Channel implements the low-power interfaces that the *AMBA*<sup>®</sup> *Low Power Interface Specification, Arm*<sup>®</sup> *Q*-*Channel and P-Channel Interfaces* describes.

The power Q-Channel and clock Q-Channel implement a full Q-Channel interface. These interfaces enable the upstream side of the bridge to indicate when it requires clock and power.

The external-gating interface implements a partial Q-Channel interface that omits the **QDENY** and **QACTIVE** signals.

The presence of a synchronizer on the **QREQn** input of a Q-Channel is configurable. See the *Arm*<sup>®</sup> *CoreLink*<sup>™</sup> *SIE-300 AXI5 System IP for Embedded Configuration and Integration Manual* for more information.

# 6.4 Bridge downstream Q-Channels

The downstream side of each bridge component provides three Q-Channel interfaces for power, clock, and external gate control.

Each Q-Channel implements the low-power interfaces that the *AMBA*<sup>®</sup> *Low Power Interface Specification, Arm*<sup>®</sup> *Q*-*Channel and P-Channel Interfaces* describes.

The power Q-Channel and clock Q-Channel implement a full Q-Channel interface. These interfaces enable the downstream side of the bridge to indicate when it requires clock and power.

The external-gating interface implements a partial Q-Channel interface that omits the **QDENY** and **QACTIVE** signals.

The presence of a synchronizer on the **QREQn** input of a Q-Channel is configurable. See the *Arm*<sup>®</sup> *CoreLink*<sup>™</sup> *SIE-300 AXI5 System IP for Embedded Configuration and Integration Manual* for more information.

# 6.5 Intra-bridge Q-Channels

The sides of each Bridge component communicate using a Q-Channel interface for power control.

The intra-bridge Q-Channel interface coordinates the powering down of the entire bridge by providing communication between the bridge sides. The power Q-Channel and external gating Q-Channel, on either side of the bridge, use the intra-bridge Q-Channel interface.

The intra-bridge Q-Channel interface also has an extra signal that indicates whether the quiescence request is from the power Q-Channel or the external gating Q-Channel. The bridge can deny a power Q-Channel quiescence request but it cannot deny an external gating Q-Channel quiescence request.

The Q-Channel implements the low-power interfaces that the AMBA<sup>®</sup> Low Power Interface Specification, Arm<sup>®</sup> Q-Channel and P-Channel Interfaces describes.

# 6.6 External gating of the AXI interface (upstream)

The upstream side of each bridge component has a Q-Channel device interface. An external device can use the Q-Channel interface to gate transactions on the AXI interface.

The external-gating interface is a Q-Channel implementation without the **QDENY** and **QACTIVE** signals.

If the upstream side of the bridge receives a gating request, that is **ext\_gt\_qreqn\_s** goes LOW, then the bridge component stalls any new incoming AXI transactions.

The bridge component accepts an external gating request when there is no ongoing transfer and its internal buffers are empty. After the bridge component sets **ext\_gt\_qacceptn\_s** LOW, the system can apply the reset to the upstream side of the bridge without the risk of data loss.

If the bridge component receives a new AXI transaction while **ext\_gt\_qreqn\_s** is LOW, then the **cfg\_ext\_gt\_err\_resp** and **cfg\_gate\_resp** signals control whether the bridge component:

- Responds with an AXI slave error (SLVERR).

- Stalls the transaction until the external gating request is released, that is, ext\_gt\_qreqn\_s goes HIGH.

# 6.7 External gating of the AXI interface (downstream)

The downstream side of each bridge component has a Q-Channel device interface. An external device can use the Q-Channel interface to gate transactions on the AXI interface.

The external-gating interface is a Q-Channel implementation without the **QDENY** and **QACTIVE** signals.

If the downstream side of the bridge receives a gating request, that is **ext\_gt\_qreqn\_m** goes LOW, then the bridge sets **eg\_on\_i** HIGH to notify the upstream side to stall any new incoming AXI transactions.

The bridge component accepts an external gating request when there is no ongoing transfer and its internal buffers are empty. After the bridge component sets **ext\_gt\_qacceptn\_m** LOW, the system can apply the reset to the downstream side of the bridge without the risk of data loss.

If the bridge component receives a new AXI transaction while **ext\_gt\_qreqn\_m** is LOW, then the **cfg gate resp** signal controls whether the bridge component:

- Responds with an AXI slave error (SLVERR).

- Stalls the transaction until the external gating request is released, that is, **ext\_gt\_qreqn\_m** goes HIGH.

# 6.8 AMBA bus properties for bridge components

The AMBA protocols define multiple property types that indicate the capabilities of a device.

The following table lists the AXI5 properties for all AXI interfaces of a bridge component.

## Table 6-2 Bridge component AXI5 properties

| AXI5 property             | Value | Comment                                                                                                          |

|---------------------------|-------|------------------------------------------------------------------------------------------------------------------|

| Wakeup_Signals            | TRUE  | Q-Channel activity is generated from the <b>awakeup</b> input signal.                                            |

| Check_Type                | FALSE | -                                                                                                                |

| Poison                    | TRUE  | The component forwards the poison data downstream, it does not use the information that the poison bits contain. |

| Trace_Signals             | FALSE | -                                                                                                                |

| QoS_Accept                | FALSE | -                                                                                                                |

| Loopback_Signals          | FALSE | -                                                                                                                |

| Untranslated_Transactions | FALSE | -                                                                                                                |

| NSAccess_Identifiers      | FALSE | -                                                                                                                |

| Atomic_Transactions       | FALSE | -                                                                                                                |

# Chapter 7 Programmers model

This chapter describes the memory regions and registers that the *Memory Protection Controller* (MPC) provides.

\_\_\_\_\_ Note \_\_\_\_\_

The MSC, PPC, ACG, SDB, SUB, and SMC components have no registers that software can program.

It contains the following sections:

- 7.1 About the programmers model on page 7-54.

- 7.2 Register summary on page 7-55.

- 7.3 Register descriptions on page 7-56.

- 7.4 Gating AXI transactions during register updates on page 7-70.

- 7.5 Programming the LUT on page 7-71.

- 7.6 Configuration lockdown on page 7-72.

# 7.1 About the programmers model

The following information applies to all registers:

- Do not attempt to access reserved or unused address locations. Attempting to access these locations can result in unpredictable behavior.

- Unless otherwise stated in the accompanying text:

- Do not modify undefined register bits.

- Ignore undefined register bits on reads.

- Unless otherwise specified, all register bits are reset to a logic 0 by a system or power up reset.

- The following describes the access type:

| d and | write. |

|-------|--------|

| U     | d and  |

**RO** Read-only.

WO Write-only.

# 7.2 Register summary

The Memory Protection Controller (MPC) registers occupy a 4KB region.

The following table shows the MPC registers in offset order from the base memory address.

# Table 7-1 MPC register summary

| Offset      | Name       | Туре | Width | Description                                                          |

|-------------|------------|------|-------|----------------------------------------------------------------------|

| 0x000       | CTRL       | RW   | 32    | 7.3.1 Control register, CTRL on page 7-56.                           |

| 0x004-0x00C |            | -    | -     | Reserved, RAZ/WI.                                                    |

| 0x010       | BLK_MAX    | RO   | 32    | 7.3.2 Block index maximum value register, BLK_MAX on page 7-57.      |

| 0x014       | BLK_CFG    | RO   | 32    | 7.3.3 Block LUT configuration status register, BLK_CFG on page 7-58. |

| 0x018       | BLK_IDX    | RW   | 32    | 7.3.4 Block LUT index register, BLK_IDX on page 7-58.                |

| 0x01C       | BLK_LUT[n] | RW   | 32    | 7.3.5 Block LUT register, BLK_LUT on page 7-59.                      |

| 0x020       | IRQ_STAT   | RO   | 32    | 7.3.6 Interrupt status register; IRQ_STAT on page 7-60.              |

| 0x024       | IRQ_CLEAR  | WO   | 32    | 7.3.7 Interrupt clear register, IRQ_CLEAR on page 7-61.              |

| 0x028       | IRQ_EN     | RW   | 32    | 7.3.8 Interrupt signal enable register; IRQ_EN on page 7-61.         |

| 0x02C       | IRQ_INFO1  | RO   | 32    | 7.3.9 Interrupt information register 1, IRQ_INFO1 on page 7-62.      |

| 0x030       | IRQ_INFO2  | RO   | 32    | 7.3.10 Interrupt information register 2, IRQ_INFO2 on page 7-62.     |

| 0x034       | IRQ_SET    | WO   | 32    | 7.3.11 Interrupt set register; IRQ_SET on page 7-64.                 |

| 0x038-0xFCC | -          | -    | -     | Reserved, RAZ/WI.                                                    |

| 0xFD0       | PIDR4      | RO   | 32    | Peripheral ID register 4, PIDR4 on page 7-64.                        |

| 0xFD4       | PIDR5      | RO   | 32    | Peripheral ID registers 5-7, PIDR5, PIDR6, PIDR7 on page 7-65.       |

| 0xFD8       | PIDR6      | RO   | 32    |                                                                      |

| ØxFDC       | PIDR7      | RO   | 32    |                                                                      |

| 0xFE0       | PIDR0      | RO   | 32    | Peripheral ID register 0, PIDR0 on page 7-65.                        |

| 0xFE4       | PIDR1      | RO   | 32    | Peripheral ID register 1, PIDR1 on page 7-66.                        |

| 0xFE8       | PIDR2      | RO   | 32    | Peripheral ID register 2, PIDR2 on page 7-66.                        |

| 0xFEC       | PIDR3      | RO   | 32    | Peripheral ID register 3, PIDR3 on page 7-67.                        |

| 0xFF0       | CIDR0      | RO   | 32    | Component ID register 0, CIDR0 on page 7-68.                         |

| 0xFF4       | CIDR1      | RO   | 32    | Component ID register 1, CIDR1 on page 7-68.                         |

| 0xFF8       | CIDR2      | RO   | 32    | Component ID register 2, CIDR2 on page 7-68.                         |

| 0xFFC       | CIDR3      | RO   | 32    | Component ID register 3, CIDR3 on page 7-69.                         |

# 7.3 Register descriptions

This section describes the MPC registers.

7.2 Register summary on page 7-55 provides cross references to individual registers.

This section contains the following subsections:

- 7.3.1 Control register, CTRL on page 7-56.

- 7.3.2 Block index maximum value register, BLK\_MAX on page 7-57.

- 7.3.3 Block LUT configuration status register, BLK\_CFG on page 7-58.

- 7.3.4 Block LUT index register, BLK\_IDX on page 7-58.

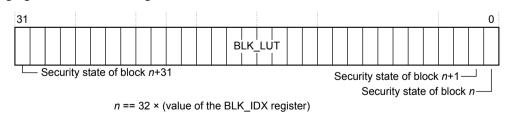

- 7.3.5 Block LUT register, BLK\_LUT on page 7-59.

- 7.3.6 Interrupt status register; IRQ\_STAT on page 7-60.

- 7.3.7 Interrupt clear register, IRQ\_CLEAR on page 7-61.

- 7.3.8 Interrupt signal enable register, IRQ\_EN on page 7-61.

- 7.3.9 Interrupt information register 1, IRQ\_INFO1 on page 7-62.

- 7.3.10 Interrupt information register 2, IRQ\_INFO2 on page 7-62.

- 7.3.11 Interrupt set register, IRQ SET on page 7-64.

- 7.3.12 Identification registers on page 7-64.

#### 7.3.1 Control register, CTRL

The CTRL register can lock down the programming configuration of the MPC. It also enables the BLK\_IDX autoincrement and controls the AXI response when software gates AXI transactions.

| Usage constraints | Accessible only from Secure state. If SEC_CFG_LOCK == 1, then the register is read-only, which also prevents software from gating AXI transactions. See <i>7.4 Gating AXI transactions during register updates</i> on page 7-70. |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configurations    | Available in all configurations.                                                                                                                                                                                                 |

| Attributes        | See 7.2 Register summary on page 7-55.                                                                                                                                                                                           |

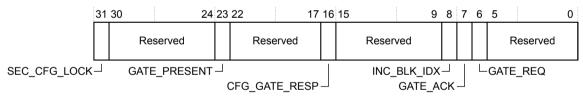

The following figure shows the bit assignments.

Figure 7-1 CTRL bit assignments

The following table shows the bit assignments.

## Table 7-2 CTRL bit assignments

| Bits    | Name         | Default | Description                                                                                                                                                                                                      |

|---------|--------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31]    | SEC_CFG_LOCK | 0       | Security configuration lockdown.<br>When set to 1, CTRL, BLK_LUT, IRQ_EN and IRQ_SET become read-only<br>registers. To set this bit to 0, the MPC must be reset. See 7.6 Configuration lockdown<br>on page 7-72. |

| [30:24] | -            | -       | Reserved, RAZ/WI.                                                                                                                                                                                                |

#### Table 7-2 CTRL bit assignments (continued)

| Bits    | Name          | Default      | Description                                                                                                                                                       |

|---------|---------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [23]    | GATE_PRESENT  | GATE_PRESENT | This read-only bit returns the state of the GATE_PRESENT parameter:                                                                                               |

|         |               |              | $0 =$ The GATE_PRESENT parameter is set to 0, so the MPC does not support external gating.                                                                        |

|         |               |              | 1 = The GATE_PRESENT parameter is set to 1, so the MPC supports external gating.                                                                                  |

| [22:17] | -             | -            | Reserved, RAZ/WI.                                                                                                                                                 |

| [16]    | CFG_GATE_RESP | 0            | When CTRL.GATE_PRESENT == 1, this bit enables software to control the AXI response type when the MPC is gating AXI transactions. The AXI response type is either: |

|         |               |              | 0 = The MPC sets the AXI <b>ready</b> signals LOW, which stalls any AXI transactions.                                                                             |

|         |               |              | 1 = The MPC returns an AXI ERROR response.                                                                                                                        |

|         |               |              | Note                                                                                                                                                              |

|         |               |              | If gating is active (CTRL.GATE_REQ == 1), then CTRL.CFG_GATE_RESP is read-<br>only.                                                                               |

|         |               |              | This bit is reserved when CTRL.GATE_PRESENT == 0.                                                                                                                 |

| [15:9]  | -             | -            | Reserved, RAZ/WI.                                                                                                                                                 |

| [8]     | INC_BLK_IDX   | 1            | BLK_IDX autoincrement enable.                                                                                                                                     |

|         |               |              | This bit is reserved when $ADDR\_WIDTH - BLK\_CFG.BLK\_SIZE < 11$ .                                                                                               |

| [7]     | GATE_ACK      | 0            | This read-only bit indicates if the MPC is gating incoming AXI transactions:                                                                                      |

|         |               |              | 0 = The MPC is not gating incoming AXI transactions.                                                                                                              |

|         |               |              | 1 = The MPC is gating incoming AXI transactions.                                                                                                                  |

|         |               |              | This bit is reserved when CTRL.GATE_PRESENT $== 0$ .                                                                                                              |

| [6]     | GATE_REQ      | 0            | Request to gate incoming AXI transactions.                                                                                                                        |

|         |               |              | Once the MPC enters configuration lockdown (CTRL.SEC_CFG_LOCK == 1), to avoid deadlock occurring the MPC sets GATE_REQ to 0.                                      |

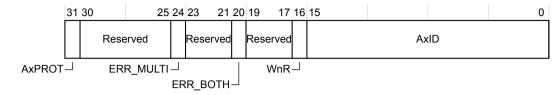

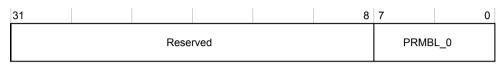

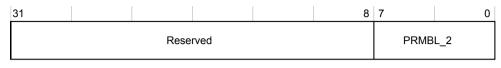

|         |               |              | This bit is reserved when CTRL.GATE_PRESENT $== 0$ .                                                                                                              |