## CoreSight Technology

System Design Guide

Copyright © 2004, 2007, 2010 ARM Limited. All rights reserved. ARM DGI 0012D (ID062610)

#### CoreSight Technology System Design Guide

Copyright © 2004, 2007, 2010 ARM Limited. All rights reserved.

#### **Release Information**

The table below shows the release state and change history of this document.

Change history

| Date              | Confidentiality  | Issue | Change                              |

|-------------------|------------------|-------|-------------------------------------|

| 29 September 2004 | Non-Confidential | А     | First release                       |

| 20 July 2007      | Non-Confidential | В     | Updated for r1p0                    |

| 29 April 2010     | Non-Confidential | С     | Updated for STM and TMC             |

| 25 June 2010      | Non-Confidential | D     | Update on Clock domain interactions |

#### **Proprietary Notice**

Words and logos marked with  $^{\circ}$  or  $^{\sim}$  are registered trademarks or trademarks of ARM $^{\circ}$  in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

## Contents CoreSight Technology System Design Guide

|           | Prefa | ace                                                       |      |

|-----------|-------|-----------------------------------------------------------|------|

|           |       | About this guide                                          | ix   |

|           |       | Feedback                                                  |      |

| Chapter 1 | Intro | duction                                                   |      |

| •         | 1.1   | About CoreSight systems                                   | 1-2  |

|           | 1.2   | CoreSight features                                        |      |

| Chapter 2 | Core  | Sight Components and Systems                              |      |

| •         | 2.1   | About CoreSight systems and components                    | 2-2  |

|           | 2.2   | CoreSight components                                      |      |

|           | 2.3   | CoreSight system examples                                 |      |

|           | 2.4   | Illegal structures                                        | 2-16 |

| Chapter 3 | Feat  | ures of CoreSight Technology and ETM Architectures        |      |

| •         | 3.1   | About CoreSight Technology and ETM architectures features |      |

|           | 3.2   | CoreSight component data                                  |      |

|           | 3.3   | Architectural features of ARM trace sources               |      |

| Chapter 4 | Debu  | ug Access                                                 |      |

| •         | 4.1   | About debug access                                        | 4-2  |

|           | 4.2   | Access to the system                                      |      |

|           | 4.3   | Access to debug components                                |      |

|           | 4.4   | Mixed legacy and DAP debug                                |      |

|           | 4.5   | Debug activity across the chip                            | 4-11 |

|           | 4.6   | Typical trigger signals                                   | 4-14 |

| Trace          | e Capture                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|----------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 5.1            | About trace capture                                                                                      | 5-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 5.2            |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 5.3            |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Implementation |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 6.1            | About implementation                                                                                     | 6-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 6.2            | -                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 6.3            | Power domains and system design                                                                          | 6-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 6.4            |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 6.5            | Debug and system power up                                                                                | 6-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 6.6            | Clock domains                                                                                            | 6-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 6.7            | Resets                                                                                                   | 6-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 6.8            |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 6.9            |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 6.10           |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Revis          | sions                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                | 5.1<br>5.2<br>5.3<br><b>Imple</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10 | 5.2       Designing your trace system         5.3       Using your system         5.3       Using your system <b>Implementation</b> 6.1       About implementation         6.2       Power control         6.3       Power domains and system design         6.4       Power control enabled components         6.5       Debug and system power up         6.6       Clock domains         6.7       Resets         6.8       Tools controlled debug reset         6.9       Interface timing |  |

Glossary

## List of Tables CoreSight Technology System Design Guide

|            | Change history                                                         | ii   |

|------------|------------------------------------------------------------------------|------|

| Table 3-1  | DAP component features for Debug Ports                                 |      |

| Table 3-2  | DAP component features for Access Ports                                | 3-4  |

| Table 3-3  | Trace source component features                                        | 3-6  |

| Table 3-4  | Trace source HTM and ITM features                                      | 3-7  |

| Table 3-5  | Link component features, part 1                                        | 3-8  |

| Table 3-6  | Link component features, part 2                                        | 3-9  |

| Table 3-7  | Sink component features, part 1                                        | 3-10 |

| Table 3-8  | Sink component features, part 2                                        | 3-11 |

| Table 3-9  | Debug component features, part 1                                       | 3-13 |

| Table 3-10 | Debug component features, part 2                                       | 3-14 |

| Table 3-11 | ARM trace source component features, part 1                            | 3-15 |

| Table 3-12 | ARM trace source component features, part 2                            | 3-16 |

| Table 4-1  | CPU connections                                                        | 4-14 |

| Table 4-2  | ETM connections                                                        | 4-14 |

| Table 4-3  | HTM, ITM, and STM connections                                          | 4-15 |

| Table 4-4  | TPIU, ETB, and TMC connections                                         | 4-15 |

| Table 5-1  | Effect of different tracing levels on ETM bandwidth requirements       | 5-7  |

| Table 6-1  | Power-up request and acknowledge signal connections                    | 6-12 |

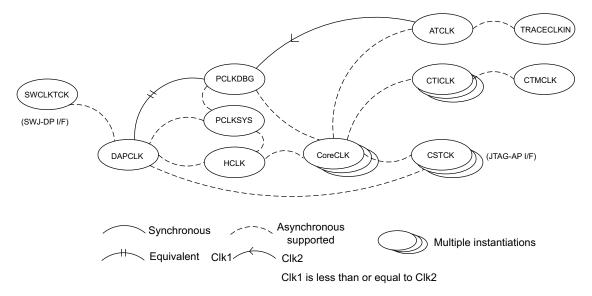

| Table 6-2  | CSDK clocks                                                            | 6-13 |

| Table 6-3  | CSDK reset signals                                                     | 6-15 |

| Table 6-4  | ATB master interface parameters, input to register, register to output | 6-20 |

| Table 6-5  | ATB slave interface parameters, input to register, register to output  | 6-21 |

| Table A-1  | Differences between issue B and issue C                                | A-1  |

| Table A-2  | Differences between issue C and issue D                                | A-2  |

# List of Figures CoreSight Technology System Design Guide

|             | Key to timing diagram conventions                                   | x    |

|-------------|---------------------------------------------------------------------|------|

| Figure 1-1  | DAP connections inside a SoC                                        | 1-4  |

| Figure 1-2  | Cross triggering                                                    | 1-5  |

| Figure 1-3  | Example system with trace components                                | 1-6  |

| Figure 2-1  | CoreSight system components                                         | 2-3  |

| Figure 2-2  | Structure of the CoreSight DAP component                            | 2-6  |

| Figure 2-3  | HTM connected to a multi-layer AHB system                           | 2-8  |

| Figure 2-4  | TPIU block diagram                                                  | 2-10 |

| Figure 2-5  | ETB block diagram                                                   | 2-11 |

| Figure 2-6  | Single CPU trace and Debug APB debug access                         | 2-13 |

| Figure 2-7  | Single source trace with the TPIU formatting bypass                 | 2-13 |

| Figure 2-8  | Full CoreSight trace with single core                               |      |

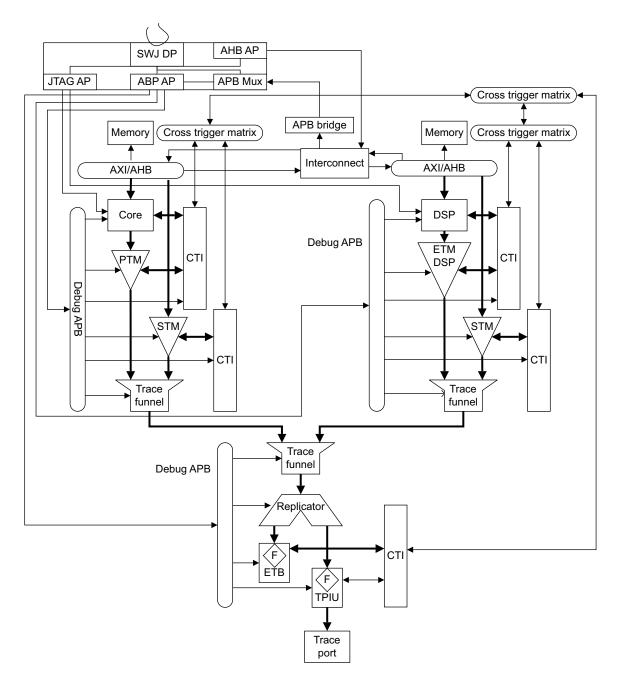

| Figure 2-9  | Full system trace with ARM core and CoreSight compliant DSP         | 2-15 |

| Figure 2-10 | Unsupported DAP connection                                          | 2-16 |

| Figure 2-11 | Unsupported replicator and funnel connection                        | 2-16 |

| Figure 2-12 | Unsupported feedback loop                                           | 2-16 |

| Figure 4-1  | JTAG connection                                                     | 4-3  |

| Figure 4-2  | Example memory system for access to debug components                | 4-7  |

| Figure 4-3  | Example memory map for access to debug components                   | 4-8  |

| Figure 4-4  | JTAG core connected in parallel with DAP                            | 4-9  |

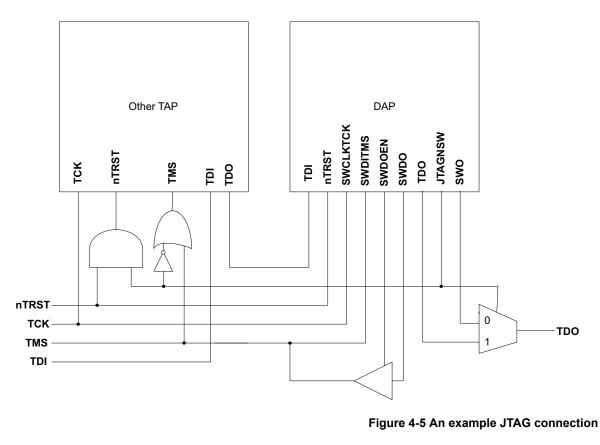

| Figure 4-5  | An example JTAG connection                                          | 4-10 |

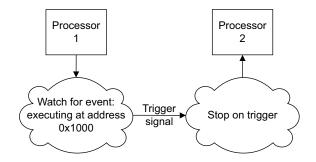

| Figure 4-6  | Processor interaction                                               | 4-11 |

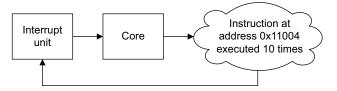

| Figure 4-7  | Signals of interest                                                 | 4-12 |

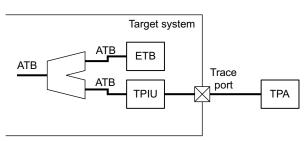

| Figure 5-1  | Example system with ETB and TPIU                                    | 5-2  |

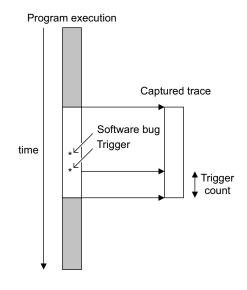

| Figure 5-2  | Use of the trigger to set a trace window                            | 5-3  |

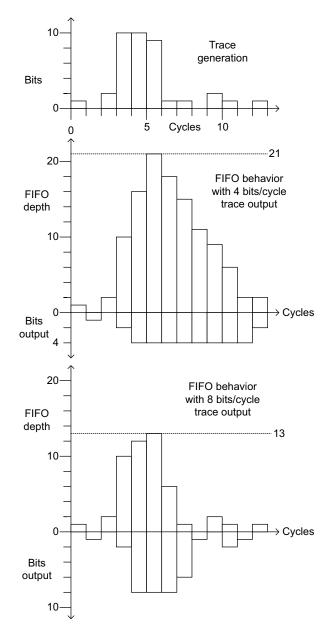

| Figure 5-3  | Effect of FIFO size on required trace bandwidth                     | 5-6  |

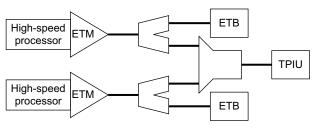

| Figure 5-4  | System with two ETBs                                                | 5-9  |

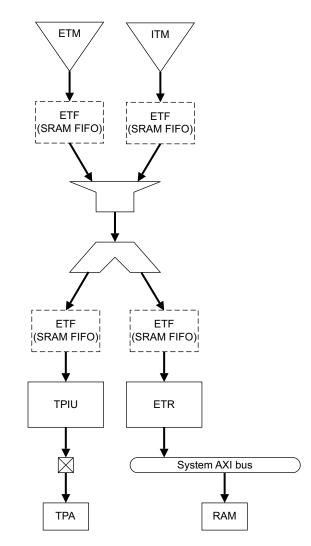

| Figure 5-5  | Using additional buffers for trace system                           |      |

| Figure 5-6  | Effect of frequency compared with infrequent synchronization points | 5-11 |

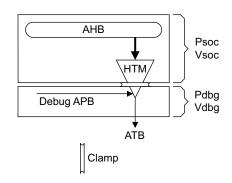

| Figure 6-1  | CoreSight system with no separate debug domains                     |      |

| Figure 6-2  | CoreSight system with a separate debug power domain |       |

|-------------|-----------------------------------------------------|-------|

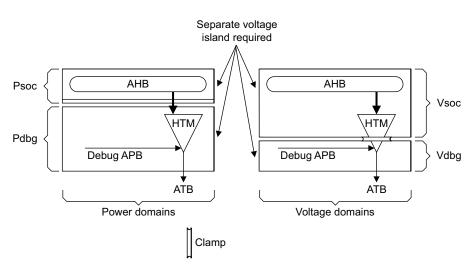

| Figure 6-3  | ETM power and voltage domains                       |       |

| Figure 6-4  | Unified power and voltage domains for ETM           |       |

| Figure 6-5  | HTM power and voltage domains                       | . 6-9 |

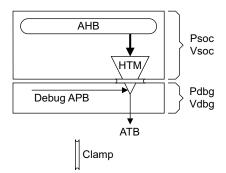

| Figure 6-6  | Unified power and voltage domains for HTM           | 6-10  |

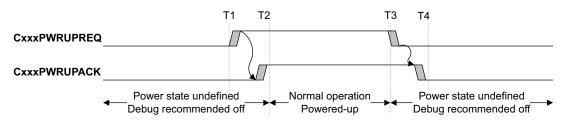

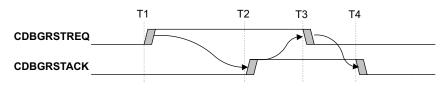

| Figure 6-7  | Power-up request and acknowledgement timing         | 6-12  |

| Figure 6-8  | Clock domain interactions                           | 6-14  |

| Figure 6-9  | Synchronous example clock configuration             | 6-17  |

| Figure 6-10 | Asynchronous example clock configuration            | 6-18  |

| Figure 6-11 | Reset handshaking mechanism                         | 6-19  |

| Figure 6-12 | ATB master interface timing                         | 6-20  |

| Figure 6-13 | ATB slave interface timing                          | 6-21  |

| Figure 6-14 | Balancing TRACECLK                                  | 6-23  |

| Figure 6-15 | Timing balance                                      | 6-24  |

### Preface

This preface introduces *CoreSight Technology System Design Guide*. It contains the following sections:

- *About this guide* on page ix

- *Feedback* on page xiii.

#### About this guide

This is the System Design Guide for CoreSight Technology.

| Product revision status |                                                                                                         |                                                                                                                                                                                      |  |

|-------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                         | The <i>rnpn</i> identifier indicates the revision status of the product described in this guide, where: |                                                                                                                                                                                      |  |

|                         | r <i>n</i>                                                                                              | Identifies the major revision of the product.                                                                                                                                        |  |

|                         | р <i>п</i>                                                                                              | Identifies the minor revision or modification status of the product.                                                                                                                 |  |

| Intended audience       |                                                                                                         |                                                                                                                                                                                      |  |

|                         | -                                                                                                       | written for system designers, and others who make design decisions about <i>hip</i> (SoC) designs that can use CoreSight Technology.                                                 |  |

| Using this guide        |                                                                                                         |                                                                                                                                                                                      |  |

|                         | This guide is                                                                                           | organized into the following chapters:                                                                                                                                               |  |

|                         | Chapter 1 In                                                                                            | ntroduction                                                                                                                                                                          |  |

|                         |                                                                                                         | Read this chapter for an introduction to CoreSight Technology.                                                                                                                       |  |

|                         | Chapter 2 C                                                                                             | oreSight Components and Systems                                                                                                                                                      |  |

|                         |                                                                                                         | Read this chapter for a description of the CoreSight components available and for information of how to combine components in typical systems for use in your CoreSight SoC designs. |  |

|                         | Chapter 3 F                                                                                             | eatures of CoreSight Technology and ETM Architectures                                                                                                                                |  |

|                         |                                                                                                         | Read this chapter for a description of the features of CoreSight components, ETM, and ETM architecture versions that you can use in your CoreSight SoC designs.                      |  |

|                         | Chapter 4 D                                                                                             | ebug Access                                                                                                                                                                          |  |

|                         |                                                                                                         | Read this chapter for a description of debug access in CoreSight systems.                                                                                                            |  |

|                         | Chapter 5 Th                                                                                            | race Capture                                                                                                                                                                         |  |

|                         |                                                                                                         | Read this chapter for a comparison of the performance of different trace methods and how to make choices about trace capture.                                                        |  |

|                         | Chapter 6 Implementation                                                                                |                                                                                                                                                                                      |  |

|                         |                                                                                                         | Read this chapter for a description of the implementation issues you must consider when designing a CoreSight system.                                                                |  |

|                         | Appendix A <i>Revisions</i>                                                                             |                                                                                                                                                                                      |  |

|                         |                                                                                                         | Read this for a description of the technical changes between released issues of this book.                                                                                           |  |

|                         | Glossary                                                                                                | Read the Glossary for definitions of terms used in this guide.                                                                                                                       |  |

| Conventions             |                                                                                                         |                                                                                                                                                                                      |  |

|                         |                                                                                                         | lescribes the conventions that this guide uses:<br>aphical on page x                                                                                                                 |  |

• *Timing diagrams* on page x

Signals on page xi

#### Typographical

The typographical conventions are:

| italic            | Highlights important notes, introduces special terminology, denotes internal cross-references, and citations.                                                                                                                                                          |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bold              | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.                                                                                                                                  |

| monospace         | Denotes text that you can enter at the keyboard, such as commands, file<br>and program names, and source code.                                                                                                                                                         |

| <u>mono</u> space | Denotes a permitted abbreviation for a command or option. You can enter<br>the underlined text instead of the full command or option name.                                                                                                                             |

| monospace italic  | Denotes arguments to monospace text where the argument is to be<br>replaced by a specific value.                                                                                                                                                                       |

| monospace bold    | Denotes language keywords when used outside example code.                                                                                                                                                                                                              |

| < and >           | <ul> <li>Angle brackets enclose replaceable terms for assembler syntax where they appear in code or code fragments. They appear in normal font in running text. For example:</li> <li>MRC p15, 0 <rd>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></rd></li> </ul> |

|                   | • The Opcode_2 value selects which register is accessed.                                                                                                                                                                                                               |

#### **Timing diagrams**

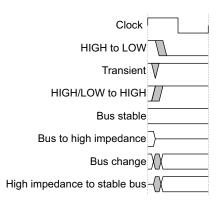

This guide contains one or more timing diagrams. The figure named *Key to timing diagram conventions* explains the components used in these diagrams. When variations occur they have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

#### Key to timing diagram conventions

#### Signals

The signal conventions are:

| Signal level | The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means HIGH for active-HIGH signals and LOW for active-LOW signals. |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lower-case n | Denotes an active-LOW signal.                                                                                                                                           |

| Prefix A     | Denotes global Advanced eXtensible Interface (AXI) signals:                                                                                                             |

| Prefix AR    | Denotes AXI read address channel signals.                                                                                                                               |

| Prefix AW    | Denotes AXI write address channel signals.                                                                                                                              |

| Prefix B     | Denotes AXI write response channel signals.                                                                                                                             |

| Prefix C     | Denotes AXI low-power interface signals.                                                                                                                                |

| Prefix H     | Denotes Advanced High-performance Bus (AHB) signals.                                                                                                                    |

| Prefix P     | Denotes Advanced Peripheral Bus (APB) signals.                                                                                                                          |

| Prefix R     | Denotes AXI read data channel signals.                                                                                                                                  |

| Prefix W     | Denotes AXI write data channel signals.                                                                                                                                 |

#### Additional reading

This section lists publications by ARM and by third parties.

ARM provides updates and corrections to its documentation. See http://www.arm.com for current errata sheets, addenda, and the Frequently Asked Questions list.

#### **ARM** publications

This guide contains information that is specific to CoreSight Technology systems. See to the following documents for other relevant information:

- $AMBA^{\text{TM}}$  Specification (Rev 2.0) (ARM IHI 0011)

- AMBA AXI Protocol Specification (ARM IHI 0022)

- AMBA 3 APB Protocol Specification (ARM IHI 0024)

- AMBA 3 ATB Protocol Specification (ARM IHI 0032A)

- CoreSight Architecture Specification (ARM IHI 0029)

- Embedded Trace Macrocell Architecture Specification (ARM IHI 0014)

- AHB Trace Macrocell Technical Reference Manual (ARM DDI 0328)

- CoreSight Components Implementation Guide (ARM DII 0143)

- CoreSight Components Technical Reference Manual (ARM DDI 0314)

- CoreSight DK9 Integration Manual (ARM DII 0131)

- CoreSight DK11 Integration Manual (ARM DII 0092)

- CoreSight DK-A8 Integration Manual (ARM DII 0135)

- CoreSight ETM11 Technical Reference Manual (ARM DDI 0318)

- CoreSight ETM11 Implementation Guide (ARM DII 0097)

- CoreSight ETM11 Integration Manual (ARM DII 0098)

- CoreSight ETM9 Technical Reference Manual (ARM DDI 0315)

- CoreSight ETM9 Implementation Guide (ARM DII 0093)

- CoreSight ETM9 Integration Manual (ARM DII 0094)

- Intelligent Energy Controller r0p0 Technical Overview (ARM DTO 0005)

- ARM Debug Interface v5 Architecture Specification (ARM IHI 0031A)

- AMBA Network Interconnect (NIC-301) Technical Reference Manual (ARM DDI 0397F)

- ARM Debug Interface v5.1 Supplement (DSA09-PRDC-008772)

- System Trace Macrocell Programmers' Model Architecture Specification Version 1.0 (ARM IHI 0054)

- CoreSight System Trace Macrocell Technical Reference Manual (ARM DDI 0444A)

- CoreSight System Trace Macrocell (STM) Integration and Implementation Manual (PR430-PRDC-011726)

- CoreSight Trace Memory Controller Technical Reference Manual (ARM DDI 0461A)

- CoreSight Trace Memory Controller (TMC) Integration and Implementation Manual (PR430-PRDC-011743).

#### Feedback

ARM welcomes feedback on this product and its documentation.

#### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

#### Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- the title

- the number, ARM DGI 0012D

- the page numbers to which your comments apply

- a concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

## Chapter 1 Introduction

This chapter describes CoreSight Technology. It contains the following sections:

- *About CoreSight systems* on page 1-2

- *CoreSight features* on page 1-4.

#### 1.1 About CoreSight systems

CoreSight systems provide all the infrastructure you require to debug, monitor, and optimize the performance of a complete *System on Chip* (SoC) design.

Historically, the following methods of debugging an ARM processor based SoC exist:

- Conventional JTAG debug. This is invasive debug with the core halted using:

- breakpoints and watchpoints to halt the core on specific activity

- a debug connection to examine and modify registers and memory and provide single-step execution.

- Conventional monitor debug. This is invasive debug with the core running using a debug monitor that resides in memory.

- Trace. This is non-invasive debug with the core running at full speed using:

- a collection of information on instruction execution and data transfers

- delivery off-chip in real-time

- tools to merge data with source code on a development workstation for future analysis.

CoreSight Technology addresses the requirement for a multi-core debug and trace solution with high bandwidth for whole systems beyond the core, including trace and monitor of the system bus.

CoreSight Technology provides:

- debug and trace visibility of whole systems

- cross triggering support between SoC subsystems

- higher data compression than previous solutions

- multi-source trace in a single stream

- standard Programmer's Models for standard tool support

- open interfaces for third party cores

- low pin count

- low silicon overhead.

CoreSight Technology addresses a number of trends in SoC design that increase the debug challenge:

#### Frequency increases and trace generation

Systems are tracing more information per second and must transfer this out of the SoC. Pin interface frequencies are not rising as fast as on-chip frequencies.

#### **Design Complexity**

The interactions between cores in SoCs are crucial to understanding system behavior. System logic is sufficiently decoupled from core execution to require direct visibility. For example, a system cannot determine from inside a processor with cache, the amount of time a peripheral takes to respond to a memory request.

Clock and power domain implementations are complicated. The clock frequencies can change and any part of the system can enter a low-power mode at any time. Conventional JTAG-based systems must disable all power saving features to provide debug, but in many situations this is not acceptable.

**Pin count** Pin count is crucial. Chip package restrictions do not permit a separate trace port for each core in a chip and static switching between trace ports prevents debug of complex interactions.

SoC designs must be flexible to provide the correct number of pins to achieve the required trace capture capabilities. It is not acceptable to double the number of pins because the frequency is 10% too high, or because the data bandwidth is 5% too high.

#### Performance optimization

Products must reach their performance targets. To make the most of high performance cores in SoC designs, it is essential to profile processor and bus activity to optimize performance.

#### 1.2 CoreSight features

This section describes some of the fundamental features of CoreSight Technology that enable you to address the issues and challenges of debugging complex SoCs. It contains the following sections:

- Debug access

- Cross Triggering on page 1-5

- *Trace* on page 1-6.

For more information on CoreSight components, see Chapter 2 CoreSight Components and Systems and the appropriate Technical Reference Manuals for the components.

#### 1.2.1 Debug access

You gain debug access in CoreSight systems using the Debug Access Port (DAP) that provides:

- real-time access to physical memory without halting the core, and without any target resident code

- debug control and access to all status registers.

The same mechanism provides fast access for downloading code at the start of the debug session. This is faster than the traditional JTAG mechanism that uses the ARM core to write data to memory. You can still use the ARM core to write data to virtual memory and to ease migration when the debugger does not support this approach.

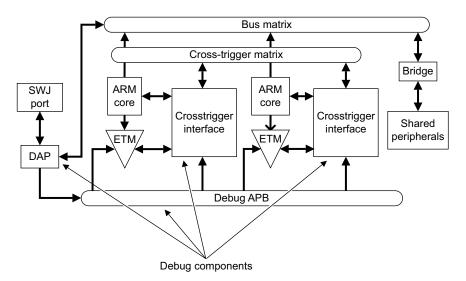

Figure 1-1 shows an example system with debug components and a DAP in a SoC design.

Figure 1-1 DAP connections inside a SoC

The DAP provides the following advantages for multi-core SoC designs:

- There is no requirement to run at the lowest common speed. A slow or powered-down component has no effect on access to other components. This means that power management has minimal impact on debug.

- The speed of access is not affected by the number of devices in the system. You have direct access to individual devices.

- You can add third party debug components using the *Advanced Microcontroller Bus Architecture* (AMBA) debug bus interface, AMBA 3 *Advanced Peripheral Bus* (APB), that provides internal and external access to the component.

- More than one core can control debug functionality, rather than restricting this to the core being debugged. One core can debug another. In particular, this enables a multi-core SoC when used as a single core platform to have complex on-chip debug and analysis features. You could use this, for example, during application development.

The DAP eases the physical implementation:

- You have a choice of physical debug interfaces. JTAG is no longer the single choice for a system, because other lower-cost interfaces are possible.

- The system does not have to support a fully asynchronous clock, **TCK**, because the DAP manages the clock. Debug clock synchronization is a problem for synthesized cores because the you must either keep the frequency of **TCK** well below the processor clock, or use a handshaking clock signal, **RTCK**.

- You do not require a return **TCK**, **RTCK**, off-chip because synchronization is performed inside the DAP.

- You can make significant savings in gate area by not having to implement a TAP controller and associated clock domain synchronization circuitry for each new debug element in the SoC.

The DAP supports increased security to prevent unwanted debug activity:

- you can add extra control over software access to the debug register file between the core and the debug bus

- you have a single access mechanism for hardware and software because the DAP arbitrates between accesses.

For 100% backward compatibility with existing tools, you can serially daisy-chain JTAG scan chains with the DAP to provide access to them.

If you do this, you lose some of the advantages of the CoreSight Technology.

For more information on the DAP, see Debug Access Port on page 2-5.

#### 1.2.2 Cross Triggering

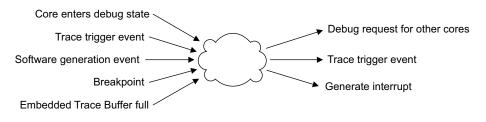

The *Embedded Cross Trigger* (ECT), comprising of the *Cross Trigger Interface* (CTI) and *Cross Trigger Matrix* (CTM), provides a standard interconnect mechanism to pass debug or profiling events around the SoC.

#### Figure 1-2 Cross triggering

The ECT provides you with a standard mechanism to connect different signal types. A set of standard triggers for cores and *Embedded Trace Macrocells* (ETMs) are predefined, and you can add triggers for third party cores.

The ECT enables tool developers to supply a standard control dialog so that software programmers can connect trigger events.

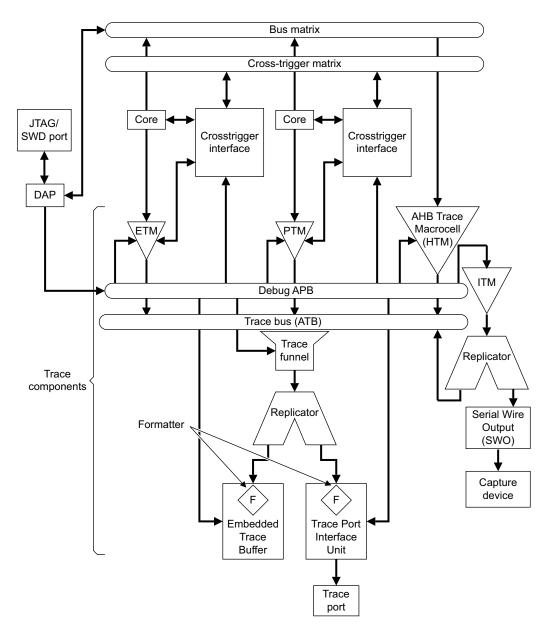

#### 1.2.3 Trace

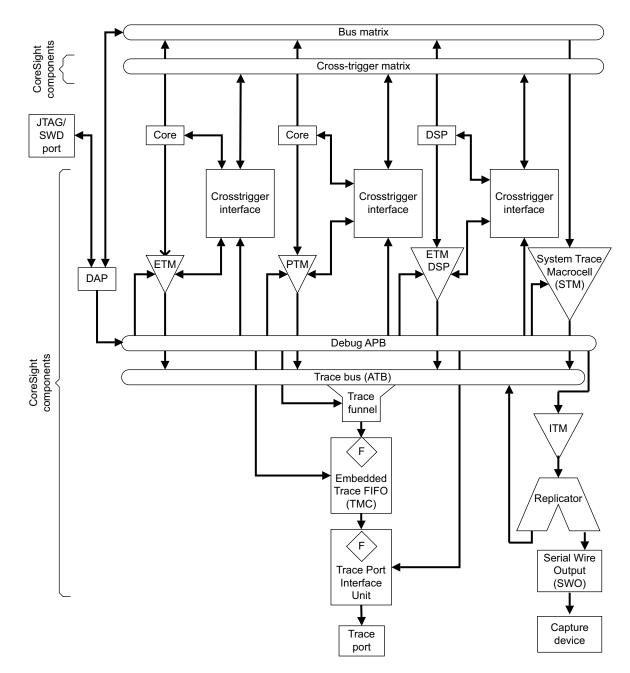

CoreSight Technology provides components that support a standard infrastructure for the capture and transmission of trace data, a combination of multiple data streams by funneling together, and then output of data to a trace port, or storage in an on-chip buffer. Figure 1-3 shows some CoreSight components.

#### Figure 1-3 Example system with trace components

CoreSight Technology enables:

- simultaneous trace of asynchronous cores, busses and intelligent peripherals

- debug and trace of an AMBA 2 AHB bus

- tracing of instrumented bus masters

output of trace data to:

.

•

- the Trace Port that can run at an independent frequency to on-chip busses

- an embedded trace buffer for on-chip storage of trace data in dedicated RAM or system RAM

- the DAP (*Debug Access Port*) for low-demand trace solutions in pin count limited targets.

- support for third party cores to enable debug control and trace capture through a standardized Programmer's Model and infrastructure.

For more information on trace components, see CoreSight components on page 2-4.

## Chapter 2 CoreSight Components and Systems

This chapter describes the CoreSight components available and how you can connect them to form complete systems. It contains the following sections:

- About CoreSight systems and components on page 2-2

- *CoreSight components* on page 2-4

- *CoreSight system examples* on page 2-13

- *Illegal structures* on page 2-16.

#### 2.1 About CoreSight systems and components

This chapter describes the individual components that make up CoreSight systems and provides some simple examples of CoreSight systems.

The following sections describe the main components of a CoreSight system:

- Buses on page 2-4

- Control and access components on page 2-5

- *Trace sources* on page 2-7

- Trace links on page 2-9

- *Trace sinks* on page 2-10

- *External debug hardware and software* on page 2-12.

Figure 2-1 on page 2-3 shows a system containing CoreSight components.

Figure 2-1 CoreSight system components

#### 2.2 CoreSight components

This section describes the CoreSight components. For more information on CoreSight Technology, see the *CoreSight Design Kit Technical Reference Manual*.

#### 2.2.1 Buses

The CoreSight systems use the following bus protocols to connect components together, and to enable integration in a SoC:

- AMBA Trace Bus (ATB)

- AMBA 3 Advanced Peripheral Bus (AMBA 3 APB)

- Advanced High-performance Bus (AHB)

- AMBA Advanced eXtensible Interface (AXI).

#### AMBA Trace Bus (ATB)

The ATB transfers trace data through the CoreSight infrastructure in a SoC. Trace sources are ATB masters, and sinks are ATB slaves. Link components provide both master and slave interfaces.

The ATB protocol supports:

- Stalling of trace sources to enable the CoreSight components to funnel and combine sources into a single trace stream.

- Association of trace data with the generating source using trace source IDs. A CoreSight system can trace up to 111 different items at any one time.

- Capture and transfer of multiple byte bus widths, currently to 32-bits.

- A flushing mechanism to force historic trace to drain from any sources, links, or sinks up to the point that the request was initiated.

For more information about ATB, see the AMBA ATB Protocol Specification.

#### AMBA 3 APB

CoreSight supports the AMBA 3 APB protocol to enable transfer extension using wait states.

The Debug APB bus uses the AMBA 3 APB protocol within a CoreSight system. The Debug APB is a bus dedicated to the connection of debug and trace components in a CoreSight-compliant SoC. All CoreSight components are configured and accessed over this bus through the APB-Mux in the DAP.

For more information about AMBA 3 APB, see the AMBA 3 APB Protocol Specification.

#### Advanced High-performance Bus (AHB)

CoreSight supports access to a system bus infrastructure using the *AHB Access Port* (AHB-AP) in the DAP. The AHB-AP provides an AHB master port for direct access to system memory.

CoreSight also supports AHB bus tracing using an *AHB Trace Macrocell* (HTM) that provides non-invasive debug visibility to any bus transactions on AHB connections.

For more information on AHB, see the AMBA Specification.

#### AMBA Advanced eXtensible Interface (AXI)

CoreSight supports the use of AXI in the system interconnect. Direct access to the AXI system can be provided through a Cortex core as an AXI bus master, or through the use of an AHB to AXI bridge on the AHB Access Port in the DAP.

CoreSight also supports trace generation from bus masters on the AXI through the use of the STM that converts stimulus writes to the device into a trace data stream.

For more information on AXI, see the AMBA Specification.

#### 2.2.2 Control and access components

Control and access components configure, provide access to, and control debug logic and the generation of trace. They do not generate trace, or process the trace data. The CoreSight control and access components are:

- the *Debug Access Port* (DAP)

- the *Embedded Cross Trigger* (ECT) that includes the *Cross Trigger Matrix* (CTM) and the *Cross Trigger Interface* (CTI).

#### **Debug Access Port**

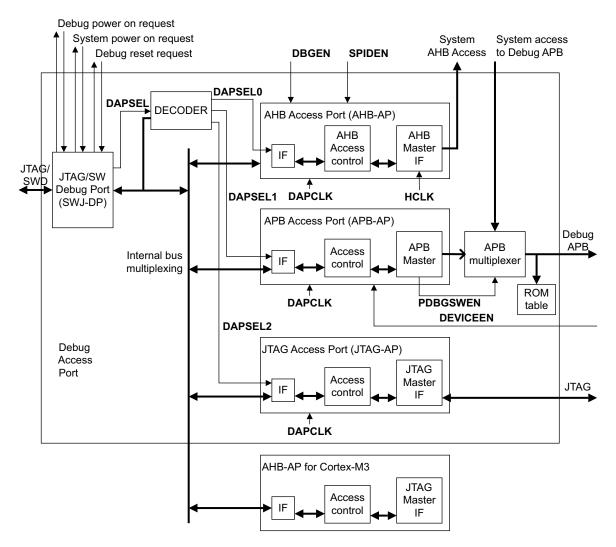

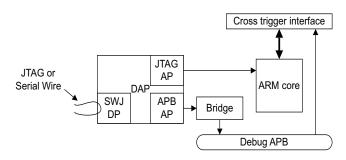

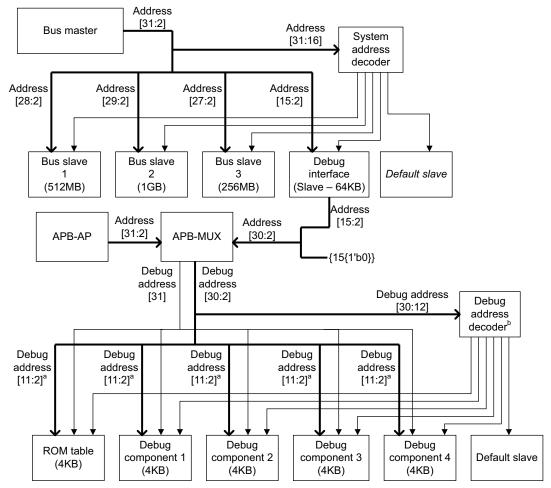

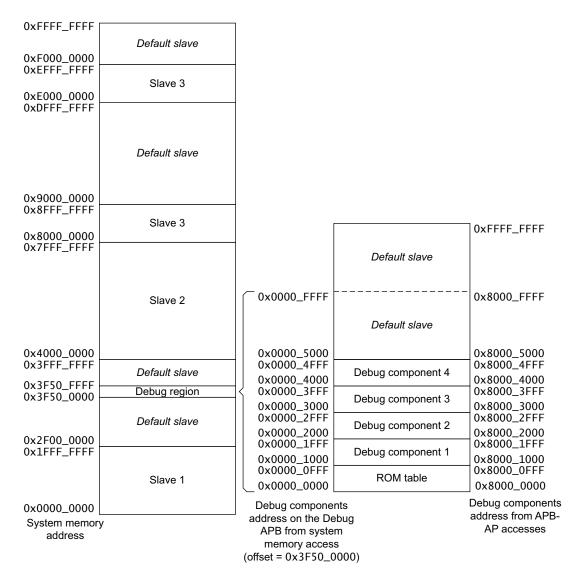

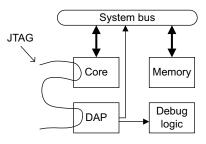

The DAP enables debug access to the complete SoC through system master ports. Figure 2-2 on page 2-6 shows the structure of the DAP.

#### Figure 2-2 Structure of the CoreSight DAP component

Access to the CoreSight Debug APB is enabled through the *APB Access Port* (APB-AP) and *APB Multiplexer* (APB-Mux), and system access is provided through the AHB-AP and *JTAG Access Port* (JTAG-AP). The DAP has the following interface blocks:

- External Serial Wire or JTAG access using the Serial Wire/JTAG Debug Port (SWJ-DP).

- Internal system access using:

- AHB-AP

- APB-AP

- JTAG-AP

- AHB-AP for Cortex-M3, if present.

- An APB-Mux enables system access to CoreSight components connected to the Debug APB.

- The ROM table provides a list of memory locations of CoreSight components connected to the Debug APB. This is visible from both tools and system access and you must configure it during system implementation.

External read/write access to the internal interface is provided by the SWJ-DP. The SWJ-DP provides both a standard interface and an ARM Serial Wire Debug interface for debug access to an SoC through the DAP. It interfaces to the DAP internal bus.

Internal access to on-chip busses and other interfaces is provided by the *Access Ports* (APs). The APs are as follows:

- the AHB-AP that provides an AHB-Lite master for access to a system AHB bus

- the APB-AP that provides an AMBA 3 APB master for access to the Debug APB that configures all CoreSight components

- the JTAG-AP that provides JTAG access to on-chip components and operates as a JTAG master port to drive JTAG chains throughout the SoC.

For more information, see the CoreSight Design Kit Technical Reference Manual.

#### **Embedded Cross Trigger**

The ECT is a modular component that supports the interaction and synchronization of multiple triggering events within a SoC.

The ECT consists of the following types of module:

- A CTI. The CTI provides the interface between a component or subsystem and the *Cross Trigger Matrix* (CTM). The system requires a CTI for each subsystem that supports cross triggering.

- A CTM. The CTM combines the trigger requests generated from CTIs and broadcasts them to all CTIs as channel triggers. This enables subsystems to interact, cross trigger, with one another. You can connect CTMs together to increase the number of CTIs.

For more information, see the CoreSight Design Kit Technical Reference Manual.

#### 2.2.3 Trace sources

Sources generate trace data and provide master ports to the AMBA Trace Bus. Depending on the licensed CoreSight components, the following trace sources can be provided:

- the AHB Trace Macrocell (HTM)

- CoreSight ETMs and PTMs for CPU trace:

- ETM9 for CoreSight (ETM9CS)

- *ETM11 for CoreSight* (ETM11CS)

- *ETM for Cortex-A8* (ETM-A8)

- *ETM for Cortex-R4* (ETM-R4)

- ETM for Cortex-M3 (ETM-M3)

- *ETM for Cortex-A5* (ETM-A5)

- PTM for Cortex-A9 (PTM-A9).

- the Instrumentation Trace Macrocell (ITM)

- the System Trace Macrocell (STM).

CoreSight Technology also enables you to add third party devices, for example a DSP trace component.

#### AHB Trace Macrocell (HTM)

The HTM makes bus information visible that you can not infer from core trace using an ETM:

- An understanding of multi-layer bus utilization.

- Software debug. For example, visibility of access to memory areas and data accesses.

- Bus event detection for trace trigger or filters, and for bus profiling.

Figure 2-3 on page 2-8 shows the HTM connected to an AHB bus. For more information on HTM see the *AMBA Trace Macrocell Technical Reference Manual*.

#### Figure 2-3 HTM connected to a multi-layer AHB system

#### Instrumentation Trace Macrocell and System Trace Macrocell

*The Instrumentation Trace Macrocell* (ITM) and *System Trace Macrocell* (STM) are application-driven trace sources that generate trace based on software written to the program interface. The ITM presents 32 APB registers, and the STM provides a set of 64K AXI registers that, on a write transaction, generate corresponding trace that indicates the register and value written.

#### Embedded Trace Macrocells (ETMs) and Program Trace Macrocells (PTMs)

The ETMs provide processor-driven trace through an ATB-compliant trace port. You can configure the ETM through the CoreSight APB programming interface. ETM9CS and ETM11CS both provide an asynchronous ATB master port that transfers trace data onto the CoreSight infrastructure.

ETM9CS implements the ETMv3.2 protocol. ETM11CS implements the ETMv3.2 protocol with TrustZone<sup>™</sup> and Thumb<sup>®</sup>-2 trace support.

ETM for Cortex-A8 and ETM for Cortex-R4 implement the ETMv3.3 protocol. However, the ETM for A8 is instruction and data address trace only.

ETM for Cortex-M3 implements the ETMv3.4 protocol. It only implements instruction trace.

PTM for Cortex-A9 implements the PTMv1 protocol to provide instruction flow trace.

For more information, see the following manuals:

- appropriate CoreSight ETM Technical Reference Manual

- Embedded Trace Macrocell Architecture Specification

- CoreSight PTM-A9 Technical Reference Manual

- Program Flow Trace Macrocell Architecture Specification.

#### 2.2.4 Trace links

Links provide connection, triggering, and flow of traced data. The following sections describe the links:

- Trace funnel

- Replicator

- Synchronous 1:1 ATB Bridge

- Embedded Trace FIFO (ETF).

#### Trace funnel

The Trace funnel combines up to eight trace sources on a single funnel. A static arbitration scheme selects the input trace stream to pass at any instant. The static arbitration permits reorganization of the slave port priorities between trace sessions. You can chain funnels together, with the ATB output from one funnel connected to an ATB input port of another. This enables you to both increase the number of inputs, and to connect independent systems together.

#### Replicator

The Replicator enables you to wire two trace sinks together and operate them on the same incoming trace stream. The input trace stream is output on two ATB ports that can then operate independently.

#### Synchronous 1:1 ATB Bridge

The Synchronous ATB Bridge provides a register slice that enables timing closure through the addition of a pipeline stage. It also provides a unidirectional link between two synchronous ATB domains. The bridge is 1:1 because both the input and output interfaces exist in the same clock domain. Because the bridge is a single register slice over the ATB interface, it temporarily holds one cycle of trace data within the register bank.

#### Embedded Trace FIFO (ETF)

The Embedded Trace FIFO is a trace buffer that uses a dedicated SRAM as either a circular capture buffer, or as a FIFO. The trace stream is captured by an ATB input that can then be output over an ATB output or the Debug APB interface.

The ETF is a configuration option of the Trace Memory Controller (TMC).

#### 2.2.5 Trace sinks

Sinks are the endpoints for trace data on the SoC. CoreSight provides sinks that the following sections describe:

- Trace Port Interface Unit (TPIU) for output of trace data off-chip

- Embedded Trace Buffer (ETB) on page 2-11 for on-chip storage of trace data in RAM

- Serial Wire Output on page 2-11 for output of trace data over a single pin

- Trace Port Interface Unit Lite on page 2-12

- *Embedded Trace Router (ETR)* on page 2-12 for on-chip storage of trace data across an AXI interconnect

- *Enhanced ETB* on page 2-12 for on-chip storage of trace as a configuration option of the TMC.

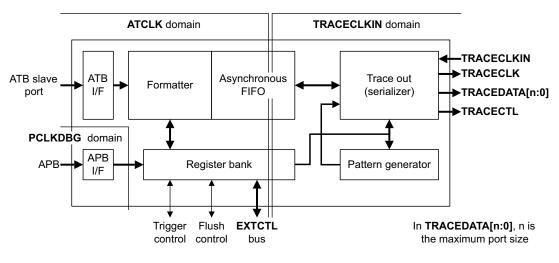

#### Trace Port Interface Unit (TPIU)

The TPIU is an ATB slave that drains trace data off the chip. It acts as a bridge between the on-chip trace data and a data stream that is captured by a *Trace Port Analyzer* (TPA). The formatter within the TPIU combines the source data and IDs into a single data stream, to enable serialization of data, inserting trigger packets on trigger detection. You can bypass formatting if your system only traces a single source, and in this situation, no IDs are embedded. The TPIU supports off-chip port sizes from 2 to 34 pins. The off-chip trace port can operate asynchronously to the incoming trace data. Figure 2-4 shows a block diagram of the TPIU.

#### Figure 2-4 TPIU block diagram

The TPIU has the following ports:

- a Debug APB programming interface

- an ATB slave port for receiving trace data from a source or link

- an asynchronous Trace Port (TP) at the pins of the device for connection to a TPA

- trigger ports for connection to a CTI.

For more information, see the CoreSight Technical Reference Manual.

#### **Embedded Trace Buffer (ETB)**

The *Embedded Trace Buffer* (ETB) is an ATB slave and provides on-chip storage of trace data using a configurable sized RAM. The ETB stores data as follows:

- The ATB bus receives Trace Data.

- The Formatter in the ETB combines the source data and IDs into a single data stream. The Formatter operates in an identical manner to the Formatter in the TPIU.

- The ETB stores the data in RAM.

You can bypass formatting if your system only traces a single source, and so reduce the amount of data stored in RAM. The ETB accesses RAM using read and write pointers to permit memory access through the APB interface. Figure 2-5 shows a block diagram of the ETB.

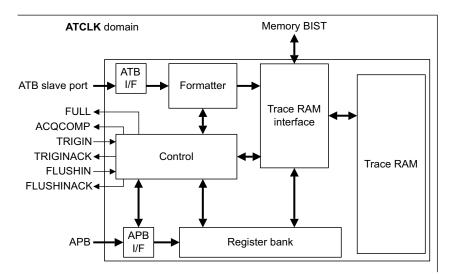

#### Figure 2-5 ETB block diagram

The ETB has the following ports:

- a Debug APB programming interface

- an ATB slave port for trace data for a source or link

- trigger ports for connection to a CTI

- a memory *Built In Self Test* (BIST) interface.

#### **Serial Wire Output**

*Serial Wire Output* (SWO) is a trace sink similar to the TPIU. It can only trace one source, the ITM. It outputs the data stream off-chip through a single-pin interface. You can select between the following operating modes for the single pin output:

- Manchester encoded stream

- NRZ-based UART byte structure, start bit, data bits, stop bit.

The SWO has an 8-bit ATB slave interface that you can connect to the CoreSight ITM. The SWO and the ATB interface are collectively called the *Serial Wire Viewer* (SWV).

#### **Trace Port Interface Unit Lite**

*The Trace Port Interface Unit Lite* (TPIU-Lite) is a reduced feature, low gate count version of the TPIU. The following differences apply:

- A synchronous trace port that operates at ATCLK speed.

- Single trace source only. There is no formatter.

- 2-bit, 4-bit, 8-bit, 16-bit, and 32-bit trace port widths.

- No pattern generator.

#### Embedded Trace Router (ETR)

The ETR is a trace sink that redirects the trace stream onto AXI. It can utilize a single contiguous region or a scattered allocation of blocks for a circular buffer. Reading of the AXI based trace buffer can either be done directly over AXI from a normal bus master, or through the ETR as if it were an ETB. You can also program it to stream trace data to a single address location for use with high-speed links.

The ETR is a configuration option of the TMC.

#### **Enhanced ETB**

An enhanced ETB is available as a configuration option of the TMC. This configuration is similar to the Classic ETB with extra features such as being able to FIFO trace data to the Debug APB interface and more memory size options.

#### 2.2.6 External debug hardware and software

Under the RealView and Keil brands are provides a range of development tools that support CoreSight debug and trace components. For more information on these tools, see, www.keil.com and, www.arm.com.

#### 2.3 CoreSight system examples

You can design a range of systems using CoreSight Technology. Some representative systems are described here and others are possible. The example systems are for:

- Single core debug

- Single source trace

- Multi source trace in an single CPU system on page 2-14

- Multi source trace in a multi-core system on page 2-14.

#### 2.3.1 Single core debug

Figure 2-6 shows CoreSight debug on a single core system. This configuration provides no trace capabilities. You can use either the AHB-AP, APB-AP, or the JTAG AP to access system components. In this configuration, the JTAG-AP accesses the core, and the APB-AP is bridged to configure the CTI. The CTI supports triggering of the core from a designated resource, and enables connection to additional triggering resources if this sample is integrated into a larger system.

Figure 2-6 Single CPU trace and Debug APB debug access

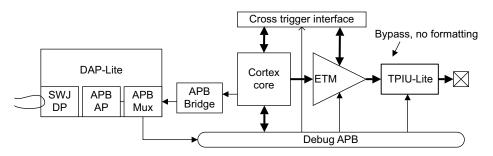

#### 2.3.2 Single source trace

Figure 2-7 shows single core trace using the CoreSight infrastructure. The CoreSight-compliant ETM outputs directly to a TPIU for direct output of core trace off-chip. The tracing of only a single trace source enables you to configure the TPIU in bypass mode because source IDs do not have to be embedded in the trace data. You can add a CoreSight ETB and replicator to provide on-chip storage of trace data.

Figure 2-7 Single source trace with the TPIU formatting bypass

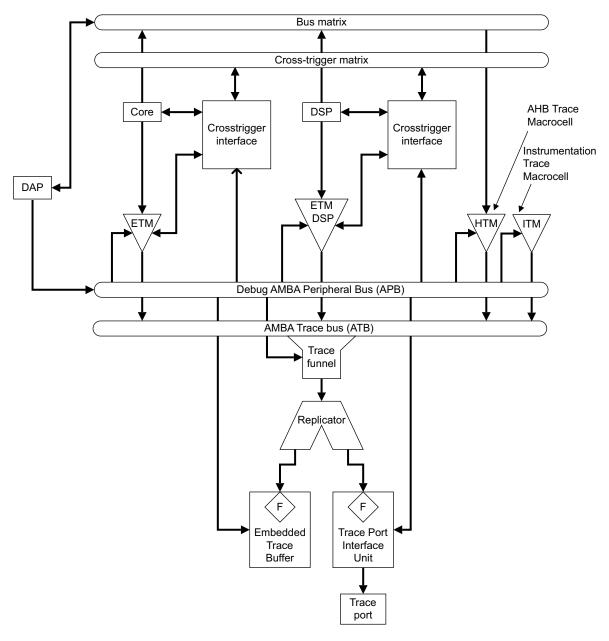

#### 2.3.3 Multi source trace in an single CPU system

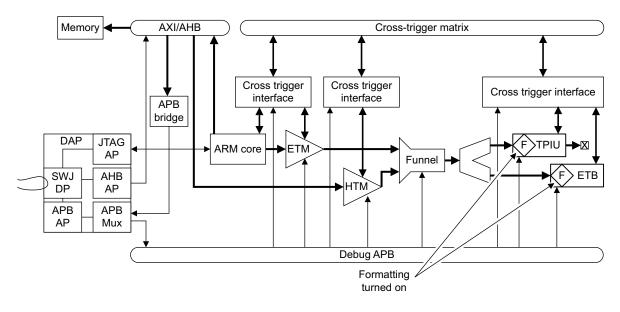

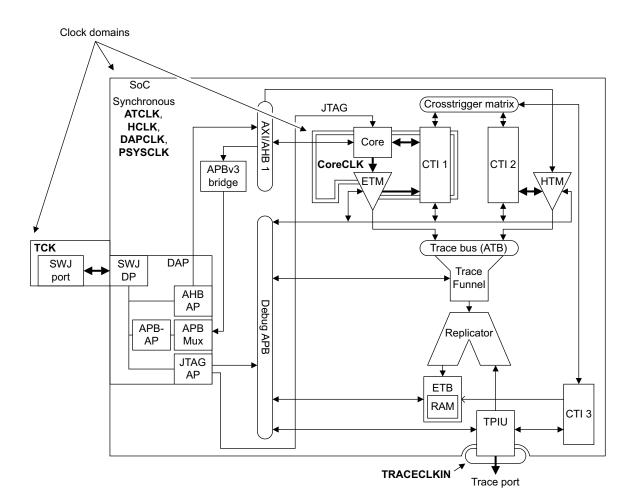

Figure 2-8 shows full trace capabilities in a single core system. The ETM provides core instruction and data tracing, and the HTM provides bus tracing. The trace funnel combines trace from all sources into a single trace stream, that is then replicated to provide on chip storage using the CoreSight ETB or output off chip using the TPIU. You can configure components using the DAP and operate cross triggering using the CTM and CTIs.

#### Figure 2-8 Full CoreSight trace with single core

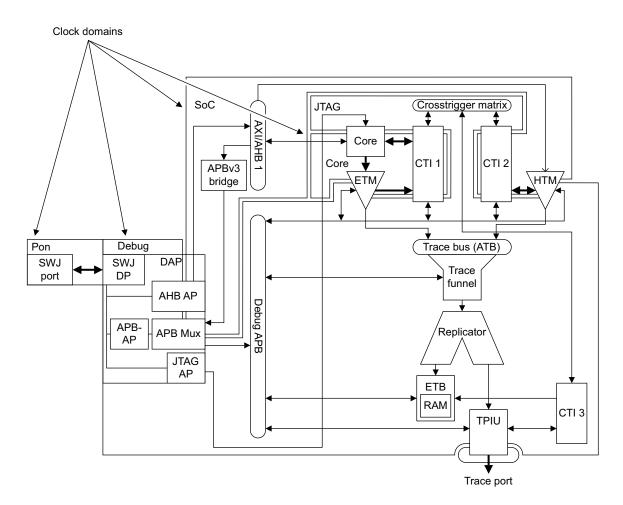

#### 2.3.4 Multi source trace in a multi-core system

Figure 2-9 on page 2-15 shows a system with a core and a third party DSP. A third smaller subsystem supports merging of multiple CoreSight ATB busses into a single trace stream. Figure 2-9 on page 2-15 also shows tracing of instrumented code using the STM.

#### Figure 2-9 Full system trace with ARM core and CoreSight compliant DSP

This system requires bridges to support access through the DAP to the separate core and DSP subsystems.

<sup>—</sup> Note -

There are many alternative configurations possible with this set of components. The configuration Figure 2-9 shows does not necessarily correspond with the best configuration to meet your specific requirements.

#### 2.4 Illegal structures

There are a number of structures that you must avoid even though it is possible to create them with the CoreSight Technology. The following sections describe these illegal structures:

- Stacked DAPs

- Duplicated IDs

- Feedback of source ID and data duplication.

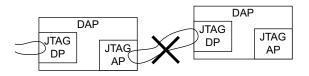

#### 2.4.1 Stacked DAPs

You must not connect a JTAG-AP to a JTAG-DP or SWJ-DP on another DAP. Figure 2-10 shows this illegal structure.

Figure 2-10 Unsupported DAP connection

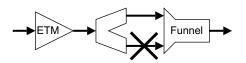

#### 2.4.2 Duplicated IDs

Two sources must never have the same source ID at any one time, and to the same component. You must not connect replicated source IDs at any point within a system. Figure 2-11shows this illegal structure.

Figure 2-11 Unsupported replicator and funnel connection

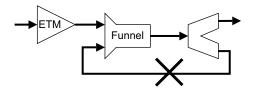

#### 2.4.3 Feedback of source ID and data duplication

You must not create feedback loops in the system that cause source ID duplication. Figure 2-12 shows this illegal structure.

Figure 2-12 Unsupported feedback loop

# Chapter 3 Features of CoreSight Technology and ETM Architectures

This chapter lists the features of CoreSight Technology components and ETM architectures. It contains the following sections:

- About CoreSight Technology and ETM architectures features on page 3-2

- CoreSight component data on page 3-3

- Architectural features of ARM trace sources on page 3-15.

## 3.1 About CoreSight Technology and ETM architectures features

CoreSight Technology provides a range of components with varying features that enable you to build trace and debug solutions to suit your SoC design. To aid comparison, this chapter lists the features of CoreSight Technology components:

- AHB-AP

- AHB-AP for Cortex-M3

- APB-AP

- APB-Mux

- ATB Bridge 1:1

- ATB Replicator

- CTI

- CTM

- DAP ROM

- ETB

- ETM9CS

- ETM11CS

- ETM-A8

- ETM-R4

- ETM-M3

- HTM

- ITM

- ITM-M3

- JTAG-AP

- JTAG-DP

- STM

- SW-DP

- SWJ-DP

- SWO

- TPIU

- TPIU-Lite

- Trace funnel.

It also describes the ETM, and PTM architecture versions, and lists the features of the trace macrocells:

- ETM9, medium plus

- ETM9CS

- ETM11RV

- ETM11CS

- ETM-A5

- ETM-A8

- ETM-R4

- ETM-M3

- PTM-A9.

## 3.2 CoreSight component data

The following sections list the component features:

- DAP features on page 3-4

- *Source features* on page 3-6

- *Link features* on page 3-8

- Sink features on page 3-10

- *Debug features* on page 3-13.

Table 3-1 on page 3-4 lists the DAP features:

- description

- type

- identification register

- input interface

- output interface

- authentication support

- power control support

- abort mechanism.

Table 3-3 on page 3-6 to Table 3-9 on page 3-13 list these features of the other components:

- description

- features

- primary non-programming inputs

- primary non-programming outputs

- programmer's model

- memory space

- part number

- device type identifier

- device ID.

#### 3.2.1 DAP features

The DAP is the bridge for access to the Debug APB and system busses. Table 3-1 shows the DAP component features for Debug Ports.

| Component name                                      | JTAG-DP                                                                      | SW-DP                                                                                               | SWJ-DP                                                                                                                                      |

|-----------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| ADIv5 Architecture<br>Compliance                    | JTAG-DP                                                                      | SW-DP                                                                                               | JTAG-DP and SW-DP                                                                                                                           |

| Description                                         | Externally visible TAP that<br>links to various on chip master<br>interfaces | Low pin count, clock plus<br>bidirectional data, alternative<br>to a conventional JTAG<br>interface | Combined TAP and Serial<br>Wire interface, effectively<br>JTAG-DP and SW-DP, with a<br>switching sequence to translate<br>between pin modes |

| Identification Register,<br>excludes revision value | 0xBA00477                                                                    | 0xBA01477                                                                                           | 0xBA02477 Serial Wire<br>0xBA00477 JTAG                                                                                                     |

| Manufacturer/designer                               | ARM (0x43B)                                                                  | ARM (0x43B)                                                                                         | ARM (0x43B)                                                                                                                                 |

| Part Number/AP<br>Identification                    | 0xBA00                                                                       | 0xBA01                                                                                              | 0xBA01 Serial Wire<br>0xBA02 Serial Wire with<br>Multidrop support<br>0xBA00 JTAG                                                           |

| Input interface                                     | JTAG                                                                         | Serial Wire                                                                                         | Shared JTAG and Serial Wire                                                                                                                 |

| Output interface                                    | DAP internal bus                                                             | DAP internal bus                                                                                    | DAP internal bus                                                                                                                            |

| Authentication support                              | No                                                                           | No                                                                                                  | No                                                                                                                                          |

| Power control support                               | Yes                                                                          | Yes                                                                                                 | Yes                                                                                                                                         |

| Abort mechanism                                     | Initiator                                                                    | Initiator                                                                                           | Initiator                                                                                                                                   |

#### Table 3-1 DAP component features for Debug Ports

Table 3-2 shows the CoreSight components for Access Ports.

#### Table 3-2 DAP component features for Access Ports

| Component name                                      | AHB-AP                         | APB-AP                            | JTAG-AP                                     | AHB-AP for CM3                                                        |

|-----------------------------------------------------|--------------------------------|-----------------------------------|---------------------------------------------|-----------------------------------------------------------------------|

| ADIv5 Architecture<br>Compliance                    | Mem-AP                         | Mem-AP                            | JTAG-AP                                     | Mem-AP                                                                |

| Description                                         | DAP interface to an AHB system | DAP interface to the<br>Debug APB | DAP interface to<br>on-chip TAP controllers | DAP Interface to<br>Cortex-M3 system<br>including debug<br>components |

| Identification Register,<br>excludes revision value | 0x4770001                      | 0x4770002                         | 0x4770010                                   | 0x4770011                                                             |

| Manufacturer/designer                               | ARM (0x43B)                    | ARM (0x43B)                       | ARM (0x43B)                                 | ARM (0x43B)                                                           |

| Part Number/AP<br>Identification                    | 0x01, AHB Bus                  | 0x02, APB Bus                     | 0x10, JTAG connection                       | 0x11, AHB Bus                                                         |

| Input interface                                     | DAP internal bus               | DAP internal bus                  | DAP internal bus                            | DAP internal bus                                                      |

|                                                     |                                |                                   |                                             |                                                                       |

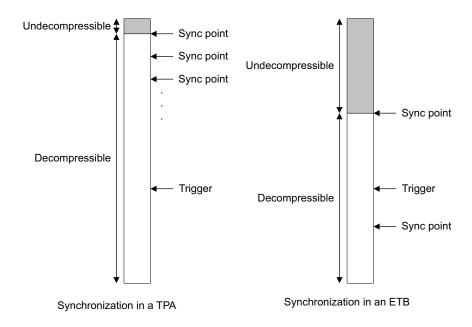

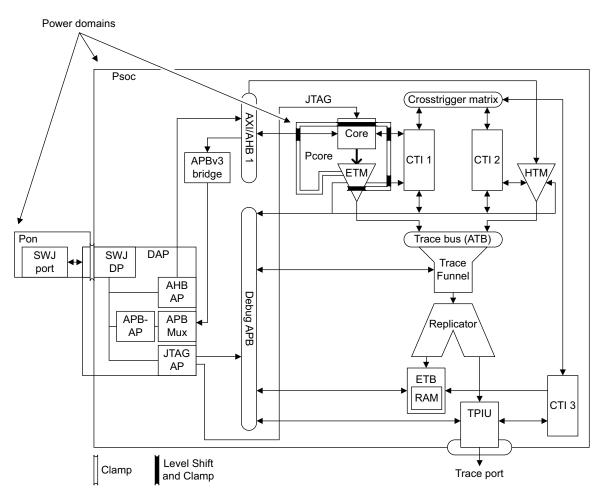

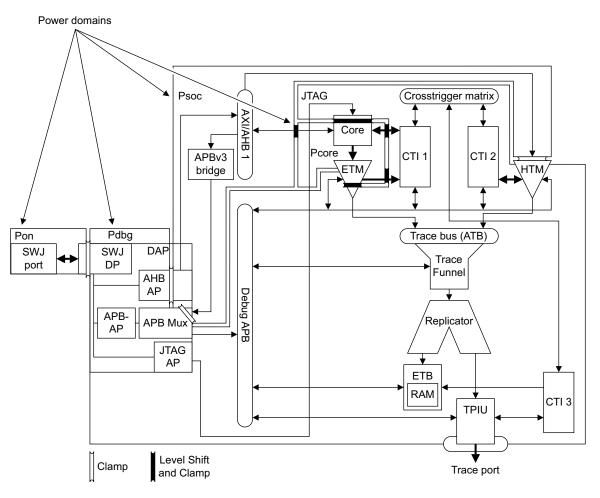

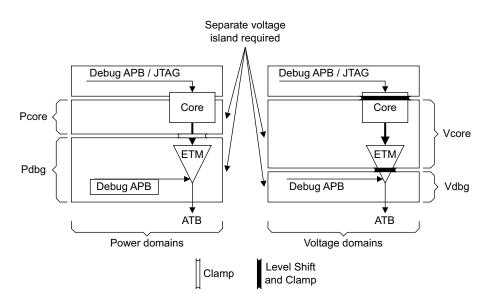

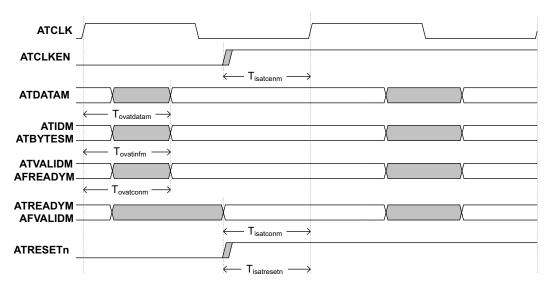

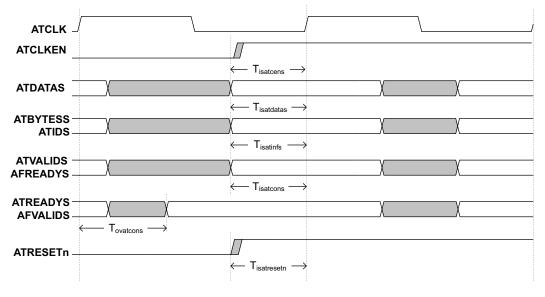

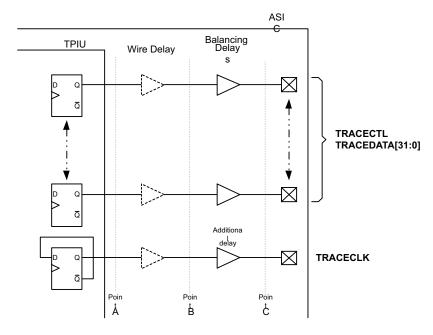

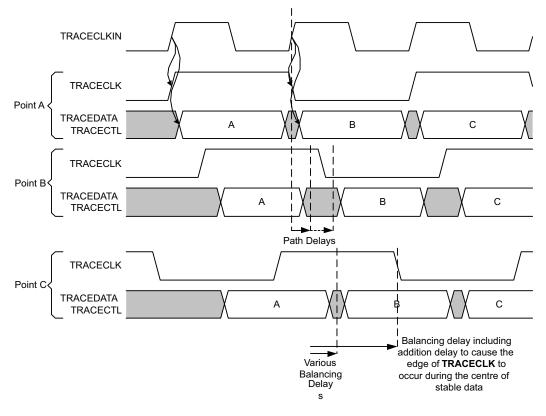

| Component name         | AHB-AP                                                       | APB-AP                                                       | JTAG-AP                                                                                                                                                                                                          | AHB-AP for CM3                                                                                                                       |