# ARM® CoreSight® STM-500 System Trace Macrocell

Revision: r0p1

**Technical Reference Manual**

## ARM CoreSight STM-500 System Trace Macrocell Technical Reference Manual

Copyright © 2013, 2014 ARM. All rights reserved.

#### **Release Information**

The following changes have been made to this book.

#### Change history

| Date            | Issue | Confidentiality  | Change                 |

|-----------------|-------|------------------|------------------------|

| 01 October 2013 | A     | Non-Confidential | First release for r0p0 |

| 11 March 2014   | В     | Non-Confidential | First release for r0p1 |

### **Proprietary Notice**

Words and logos marked with  $^*$  or  $^{\rm m}$  are registered trademarks or trademarks of ARM $^*$  in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

### **Product Status**

The information in this document is final, that is for a developed product.

### Web Address

http://www.arm.com

### Contents

## **ARM CoreSight STM-500 System Trace Macrocell Technical Reference Manual**

|           | Prefa | ace                                                  |      |  |  |  |

|-----------|-------|------------------------------------------------------|------|--|--|--|

|           |       | About this book                                      | vi   |  |  |  |

|           |       | Feedback                                             | ix   |  |  |  |

| Chapter 1 | Intro | duction                                              |      |  |  |  |

| •         | 1.1   | About the STM-500 System Trace Macrocell             | 1-2  |  |  |  |

|           | 1.2   | Compliance                                           |      |  |  |  |

|           | 1.3   | Features                                             | 1-5  |  |  |  |

|           | 1.4   | Interfaces                                           | 1-7  |  |  |  |

|           | 1.5   | Configurable options                                 | 1-8  |  |  |  |

|           | 1.6   | Test features                                        | 1-9  |  |  |  |

|           | 1.7   | Product documentation, design flow, and architecture | 1-10 |  |  |  |

|           | 1.8   | Product revisions                                    | 1-11 |  |  |  |

| Chapter 2 | Fund  | Functional Description                               |      |  |  |  |

|           | 2.1   | About the functions                                  | 2-2  |  |  |  |

|           | 2.2   | Interfaces                                           | 2-3  |  |  |  |

|           | 2.3   | Clocking and resets                                  | 2-5  |  |  |  |

|           | 2.4   | Trace protocol                                       | 2-6  |  |  |  |

|           | 2.5   | Timestamping                                         | 2-10 |  |  |  |

|           | 2.6   | Triggering                                           | 2-11 |  |  |  |

|           | 2.7   | Extended stimulus port interface                     | 2-12 |  |  |  |

|           | 2.8   | Hardware event tracing                               | 2-18 |  |  |  |

|           | 2.9   | DMA control                                          | 2-19 |  |  |  |

|           | 2.10  | Data compression                                     | 2-21 |  |  |  |

|           | 2.11  | Buffer flushing                                      | 2-22 |  |  |  |

|           | 2.12  | ATB data ordering                                    | 2-24 |  |  |  |

|            | 2.13 | Integration mode and topology detection      | 2-25 |  |  |  |

|------------|------|----------------------------------------------|------|--|--|--|

|            | 2.14 | Constraints and limitations of use           |      |  |  |  |

| Chapter 3  | Prog | Programmers Model                            |      |  |  |  |

| -          | 3.1  | About the programmers model                  | 3-2  |  |  |  |

|            | 3.2  | Register summary                             |      |  |  |  |

|            | 3.3  | Register descriptions                        |      |  |  |  |

| Appendix A | Sign | al Descriptions                              |      |  |  |  |

|            | A.1  | Clocks and resets                            | A-2  |  |  |  |

|            | A.2  | AXI slave interface signals                  | A-3  |  |  |  |

|            | A.3  | Debug APB interface signals                  | A-5  |  |  |  |

|            | A.4  | ATB master interface signals                 |      |  |  |  |

|            | A.5  | Hardware event observation interface signals | A-7  |  |  |  |

|            | A.6  | DMA peripheral request interface signals     |      |  |  |  |

|            | A.7  | Timestamp port signals                       |      |  |  |  |

|            | A.8  | Authentication interface signals             |      |  |  |  |

|            | A.9  | Non-secure guaranteed interface signals      | A-11 |  |  |  |

|            | A.10 | Cross-trigger interface signals              | A-12 |  |  |  |

|            | A.11 | Test interface signals                       |      |  |  |  |

|            | A.12 | AXI low-power interface signals              |      |  |  |  |

|            | A.13 | STM low-power interface signals              |      |  |  |  |

| Appendix B | Revi | sions                                        |      |  |  |  |

### **Preface**

This preface introduces the  $ARM^{\otimes}$   $CoreSight^{\bowtie}$  STM-500 System Trace Macrocell Technical Reference Manual. It contains the following sections:

- About this book on page vi.

- Feedback on page ix.

### About this book

This book is for the CoreSight STM-500 System Trace Macrocell.

### **Product revision status**

The rnpn identifier indicates the revision status of the product described in this book, where:

**rn** Identifies the major revision of the product.

**pn** Identifies the minor revision or modification status of the product.

### Intended audience

This book is written for:

- Designers of development tools providing support for STM functionality. Implementation-specific behavior is described in this document. You can find complementary information in the ARM® System Trace Macrocell Programmers' Model Architecture Specification.

- Hardware and software engineers integrating the STM into a *System on Chip* (SoC) design.

### Using this book

This book is organized into the following chapters:

### **Chapter 1 Introduction**

Read this for an introduction to the STM-500.

### **Chapter 2** Functional Description

Read this for a description of the interfaces, operation, and clocking and resets.

### Chapter 3 Programmers Model

Read this for a description of the programmers model and registers.

### **Appendix A Signal Descriptions**

Read this for a description of the signals.

### Appendix B Revisions

Read this for a description of the technical changes between released issues of this book.

### Glossary

The ARM® Glossary is a list of terms used in ARM documentation, together with definitions for those terms. The ARM® Glossary does not contain terms that are industry standard unless the ARM meaning differs from the generally accepted meaning.

See the ARM® Glossary

http://infocenter.arm.com/help/topic/com.arm.doc.aeg0014-/index.html.

### Conventions

Conventions that this book can use are described in:

- Typographical conventions on page vii.

- Timing diagrams on page vii.

• Signals on page viii.

### Typographical conventions

The following table describes the typographical conventions:

### Typographical conventions

| Style             | Purpose                                                                                                                                                                                                           |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| italic            | Introduces special terminology, denotes cross-references, and citations.                                                                                                                                          |  |

| bold              | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.                                                                             |  |

| monospace         | Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.                                                                                                       |  |

| <u>mono</u> space | Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.                                                                           |  |

| monospace italic  | Denotes arguments to monospace text where the argument is to be replaced by a specific value.                                                                                                                     |  |

| monospace bold    | Denotes language keywords when used outside example code.                                                                                                                                                         |  |

| <and></and>       | Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example: MRC p15, $\theta$ <rd>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></rd>                            |  |

| SMALL CAPITALS    | Used in body text for a few terms that have specific technical meanings, that are defined in the <i>ARM® Glossary</i> . For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE. |  |

### **Timing diagrams**

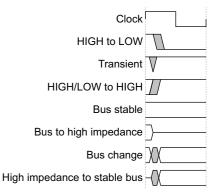

The figure named *Key to timing diagram conventions* explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are UNDEFINED, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

### Key to timing diagram conventions

Timing diagrams sometimes show single-bit signals as HIGH and LOW at the same time and they look similar to the bus change shown in *Key to timing diagram conventions*. If a timing diagram shows a single-bit signal in this way then its value does not affect the accompanying description.

### **Signals**

The signal conventions are:

### Signal level

The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

- HIGH for active-HIGH signals.

- LOW for active-LOW signals.

Lower-case n

At the start or end of a signal name denotes an active-LOW signal.

### **Additional reading**

This section lists publications by ARM.

See Infocenter http://infocenter.arm.com, for access to ARM documentation.

### **ARM** publications

This book contains information that is specific to this product. See the following documents for other relevant information:

- ARM® System Trace Macrocell Programmers' Model Architecture Specification (ARM IHI 0054).

- *ARM® ARMv7-M Architecture Reference Manual* (ARM DDI 0403).

- ARM® Architecture Reference Manual, ARMv7-A and ARMv7-R edition (ARM DDI 0406).

- ARM® Embedded Trace Macrocell Architecture Specification (ARM IHI 0014).

- *ARM® CoreSight™ Architecture Specification* (ARM IHI 0029).

- ARM® Debug Interface Architecture Specification (ARM IHI 0031).

- *ARM® AMBA® AXI and ACE Protocol Specification* (ARM IHI 0022).

- *ARM*<sup>®</sup> *AMBA*<sup>®</sup> *APB Protocol Specification* (ARM IHI 0024).

- ARM® AMBA® 4 ATB Protocol Specification ATBv1.0 and ATBv1.1 (ARM IHI 0032).

- *ARM® CoreLink™ DMA-330 DMA Controller Technical Reference Manual* (ARM DDI 0424).

- *ARM® CoreSight™ SoC-400 Technical Reference Manual* (ARM DDI 0480).

The following confidential books are only available to licensees:

- *ARM® CoreSight™ SoC-400 System Design Guide* (ARM DGI 0018).

- *ARM*<sup>®</sup> *CoreSight*<sup>™</sup> *STM-500 System Trace Macrocell Integration and Implementation Manual* (ARM-EPM-043442).

### Other publications

This section lists relevant documents published by third parties:

- MIPI System Trace Protocol version 2 (STPv2).

- JEDEC Solid State Technology Association, *Standard Manufacturer's Identification Code*, JEP106.

### **Feedback**

ARM welcomes feedback on this product and its documentation.

### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

### Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- The title.

- The number, ARM DDI 0528B.

- The page numbers to which your comments apply.

- A concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

Note

ARM tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader.

## Chapter 1 **Introduction**

This chapter introduces the CoreSight STM-500. It contains the following sections:

- About the STM-500 System Trace Macrocell on page 1-2.

- *Compliance* on page 1-4.

- *Features* on page 1-5.

- *Interfaces* on page 1-7.

- Configurable options on page 1-8.

- *Test features* on page 1-9.

- Product documentation, design flow, and architecture on page 1-10.

- *Product revisions* on page 1-11.

### 1.1 About the STM-500 System Trace Macrocell

| Note                         | •                          |

|------------------------------|----------------------------|

| In this document, the word S | STM refers to the STM-500. |

The STM-500 is a trace source that is integrated into a CoreSight system, and that is designed primarily for high-bandwidth trace of instrumentation embedded into software. This instrumentation is made up of memory-mapped writes to the STM *Advanced eXtensible Interface* (AXI) slave, which carry information about the behavior of the software.

The STM is a natural successor to the CoreSight *Instrumentation Trace Macrocell* (ITM) in mid- to high-performance applications. The STM provides the following advantages over the ITM for software instrumentation:

- It has a dedicated AXI slave interface for receiving the instrumentation information. The AXI slave interface is in addition to the *Advanced Peripheral Bus* (APB) interface that you can use for programming the STM registers. The AXI slave interface has significantly higher performance than the APB interface of the ITM.

- Multiple processors and processes can share and directly access the STM without being aware of each other, by being allocated different pages in the STM stimulus space. 128 masters, each supporting 65,536 stimulus ports. Each 4KB page of the STM stimulus space provides 16 stimulus ports. Stimulus ports are also known as channels.

- The STM can optionally stall the AXI when its FIFO becomes full, ensuring that no data is lost because of overflow, without having to poll the FIFO status in software. This behavior depends on the address written to, and can therefore be controlled by each stimulus port independently.

- An improved, configurable FIFO, supporting up to 32 transactions, reduces the likelihood of the FIFO becoming full.

- Timestamping can be requested for each write independently, based on the address written to. You can also optimize the bandwidth by requesting a timestamp for only one write transaction in a message made up of several writes.

- Timestamps are automatically correlated with other timestamping trace sources in the CoreSight system, enabling automatic correlation with, for example, processor execution trace.

In addition to the AXI slave, the STM provides a hardware event interface. The STM generates trace when signals are asserted on this interface. Alternatively, you can implement advanced custom system tracing features by generating AXI write accesses directly to the AXI slave.

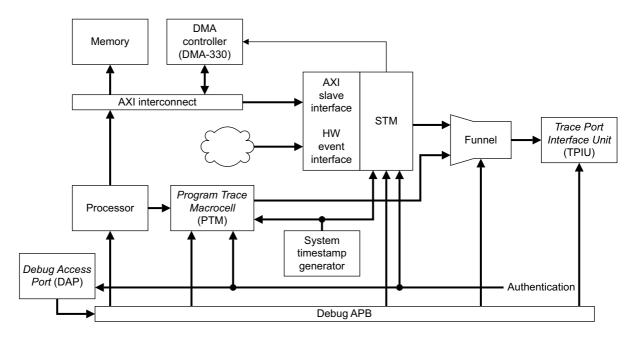

Figure 1-1 on page 1-3 shows the STM integrated into a typical system.

Figure 1-1 STM system integration

The STM AXI slave is connected to a system interconnect that enables all system masters, such as processors and *Direct Memory Access* (DMA) controllers, to generate trace by writing to the STM stimulus ports.

For interaction with DMA controllers, the STM provides a DMA request interface that is compatible with the AMBA DMA Controller DMA-330.

For configuration purposes, the STM is connected to a Debug APB interconnect. This enables off-chip and on-chip debug agents to access the STM.

The STM uses CoreSight authentication signals to control debug permissions.

The STM trace stream is output through the *Advanced Trace Bus* (ATB) interface and it is integrated with the rest of the CoreSight trace infrastructure.

### 1.2 Compliance

The STM complies with, or implements, the specifications described in:

- System Trace Protocol.

- System Trace Macrocell Programmers' Model Architecture.

- CoreSight Architecture.

- Advanced Microcontroller Bus Architecture.

This TRM complements architecture reference manuals, architecture specifications, protocol specifications, and relevant external standards. It does not duplicate information from these sources.

### 1.2.1 System Trace Protocol

The STM supports a trace stream that conforms to the MIPI System Trace Protocol version 2. See the MIPI System Trace Protocol version 2 (STPv2).

### 1.2.2 System Trace Macrocell Programmers' Model Architecture

The STM implements the STM architecture version 1.1. See the ARM® System Trace Macrocell Programmers' Model Architecture Specification.

### 1.2.3 CoreSight Architecture

The STM implements the CoreSight architecture version 2.0. See the  $ARM^{\circ}$  CoreSight  $^{\sim}$  Architecture Specification.

### 1.2.4 Advanced Microcontroller Bus Architecture

The STM complies with the AMBA 4 protocol. See the *ARM*<sup>®</sup> *AMBA*<sup>®</sup> *AXI and ACE Protocol Specification* and the *ARM*<sup>®</sup> *AMBA*<sup>®</sup> *APB Protocol Specification*.

### 1.3 Features

The STM has the following features:

- A fully synchronous design with one clock and two resets.

- One 64-bit AXI slave interface for extended stimulus port inputs.

- One hardware event observation interface for tracing 64 hardware events.

- One 32-bit debug APB slave interface for configuration and status.

- One 64-bit ATB master interface for trace output.

- One DMA peripheral request interface that is compatible with the AMBA DMA Controller DMA-330.

- Two depth-configurable FIFO buffers for usage-optimized configurability:

- Data FIFO.

- Channel information FIFO.

- A fully memory-mapped software stimulus supporting 65,536 stimulus ports and 128 masters.

- Leading zero data compression.

- Full support for guaranteed and invariant timing software stimulus writes.

- Support for single-shot and multi-shot triggers with a cross-trigger port, trigger packet insertion, and ATB trace triggers.

- An internal and an external source for STPv2 synchronization.

- Timestamping of trace events.

- Two low-power interfaces.

The STM architecture has many IMPLEMENTATION DEFINED options. Table 1-1 shows the configuration implemented by the STM-500.

Table 1-1 STM configuration

| Feature            | Configuration                 |

|--------------------|-------------------------------|

| Trace protocol     | STPv2                         |

| Timestamping       | Absolute                      |

| STMTSFREQR         | Read-write                    |

| STMTSSTIMR         | Implemented                   |

| STMSYNCR           | Implemented                   |

| Claim tags         | Four                          |

| TRACEID            | CoreSight ATB and ATB trigger |

| Trigger control    | Multi-shot and single-shot    |

| STMTCSR.TSPRESCALE | Not implemented               |

| STMTCSR.HWTEN      | Not implemented               |

| STMTCSR.SYNCEN     | Always reads as 0b1           |

**Table 1-1 STM configuration (continued)**

| Feature                                  | Configuration                   |

|------------------------------------------|---------------------------------|

| STMTCSR.SWOEN                            | Not implemented                 |

| Number of stimulus ports                 | 65536                           |

| Number of masters                        | Minimum of two                  |

| Stimulus port types                      | Extended only                   |

| Fundamental data size                    | 64                              |

| Transaction Types                        | Invariant timing and guaranteed |

| STMSPER                                  | Implemented                     |

| STMSPTER                                 | Implemented                     |

| STMPRIVMASKR                             | Not implemented                 |

| STMSPOVERRIDER and STMSPMOVERRIDER       | Implemented                     |

| STMSPSCR and STMSPMSCR                   | Implemented                     |

| Data compression on stimulus ports       | Programmable                    |

| Hardware event tracing                   | Implemented                     |

| Number of hardware events                | 64                              |

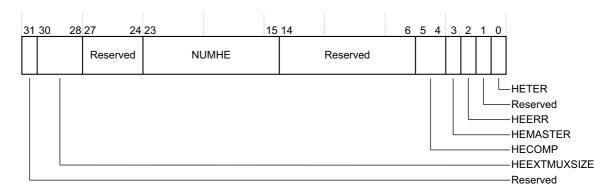

| STMHETER                                 | Implemented                     |

| Hardware error detection                 | Implemented                     |

| STMHEMASTR                               | Read only                       |

| Data compression on hardware event trace | Programmable                    |

| Hardware event multiplexing              | The STMHEEXTMUXR is 8-bits wide |

### 1.4 Interfaces

The STM-500 has the following external interfaces:

- AMBA AXI4 slave.

- Hardware event observation interface.

- DMA peripheral request interface.

- Debug APB slave interface.

- AMBA 4 ATB master interface.

- Timestamp port interface.

- Authentication interface.

- Non-secure guaranteed stimulus port access enable interface.

- Cross-trigger interface.

- Two low-power interfaces.

See *Interfaces* on page 2-3 for more information about these interfaces.

### 1.5 Configurable options

You can configure the depths of the STM FIFO buffers to match the instrumentation usage model. Deeper buffers improve STM performance but increase area and power consumption.

Each data FIFO entry can store up to 64 bits of data and up to 16 bits of timestamp information. Each channel FIFO entry can store one channel or master change message. It is not usually necessary to implement as many channel FIFO entries as data FIFO entries, because the channel or master does not usually change on every write to the AXI slave.

You can also specify the presence of the hardware event observation interface and the width of the AXI ID. Table 1-2 shows the configurable options.

Table 1-2 STM configurable options

| Configurable option | Valid values  | Description                                                                                                                                                                          |  |

|---------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DATA_FIFO_DEPTH     | 4, 8, 16, 32  | Depth of the data FIFO buffer.                                                                                                                                                       |  |

| CHN_FIFO_DEPTH      | 4, 8, 16, 32a | Depth of the channel FIFO buffer.                                                                                                                                                    |  |

| HWEVOBIF_PRESENT    | FALSE         | Hardware event observation interface is not present.                                                                                                                                 |  |

|                     | TRUE          | Hardware event observation interface is present.                                                                                                                                     |  |

| AXI_ID_WIDTH        | 2-24          | Width of the AXI IDs, including AWID, BID, ARID, and RID.                                                                                                                            |  |

| HWEVOBIF_CONFIG_n   | 0 or 1        | Specifies whether the hardware event input <i>n</i> is edge-sensitive or level-sensitive:  0                                                                                         |  |

|                     |               | The RTL groups these configuration options into the following 32-bit parameters:  HWEVOBIF_CONFIG_31_0  For hardware events 0-31.  HWEVOBIF_CONFIG_63_32  For hardware events 32-63. |  |

a. This value must not be more than the DATA\_FIFO\_DEPTH value.

If you are unsure about the instrumentation profile in your system, ARM recommends that you implement the STM in a configuration with CHN\_FIFO\_DEPTH set to eight and DATA\_FIFO\_DEPTH set to 16.

### 1.6 Test features

The STM includes clock gating circuitry to save power when the STM is disabled. It includes the following *Design-For-Test* (DFT) port to enable the clock during STM testing:

### **DFTCLKCGEN**

Forces the STM clock on during DFT shift.

### 1.7 Product documentation, design flow, and architecture

This section describes the STM documents, how they relate to the design flow, and the relevant architectural standards and protocols.

See *Additional reading* on page viii for more information about the documents described in this section.

### 1.7.1 Documentation

The STM documentation is as follows:

### **Technical Reference Manual**

The *Technical Reference Manual* (TRM) describes the functionality and the effects of functional options on the behavior of the STM. It is required at all stages of the design flow. The choices made in the design flow can mean that some behavior described in the TRM is not relevant.

### **Integration and Implementation Manual**

The Integration and Implementation Manual (IIM) describes:

- The available build configuration options and related issues in selecting them.

- How to configure the RTL with the build configuration options.

- How to integrate the STM into an SoC. This includes describing the pins that the integrator must tie off to configure the macrocell for the required integration.

- The processes to sign off the integration and implementation of the design.

The ARM product deliverables include reference scripts and information about using them to implement your design.

Reference methodology documentation from your EDA tools vendor complements the IIM.

The IIM is a confidential document that is only available to licensees.

### 1.7.2 Design flow

The STM is delivered as synthesizable RTL. Before using the STM in a product, you must integrate and implement the STM. Implementation and integration choices affect the behavior and features of the STM. The operation of the final device depends on:

### **Build configuration**

The implementer chooses the options that affect how the RTL source files are configured. These options usually include or exclude logic that affects one or more of the area, maximum frequency, and features of the resulting macrocell.

### **Configuration inputs**

The integrator configures some features of the STM by tying inputs to specific values. These configurations affect the start-up behavior before any software configuration is made. They can also limit the options available to the software.

### Software configuration

The programmer configures the STM by programming particular values into registers. This affects the behavior of the STM.

### 1.8 Product revisions

This section describes the differences in functionality between product revisions:

**r0p0** First release.

**r0p0-r0p1** Updated the revision field for the Peripheral ID 2 register. See *Peripheral ID2*

Register on page 3-25.

## Chapter 2 **Functional Description**

This chapter describes the interfaces, operation, and clocking and resets of the STM-500. It contains the following sections:

- *About the functions* on page 2-2.

- *Interfaces* on page 2-3.

- *Clocking and resets* on page 2-5.

- Trace protocol on page 2-6.

- *Timestamping* on page 2-10

- *Triggering* on page 2-11.

- Extended stimulus port interface on page 2-12.

- *Hardware event tracing* on page 2-18.

- *DMA control* on page 2-19.

- *Data compression* on page 2-21.

- Buffer flushing on page 2-22.

ATB data ordering on page 2-24.

- *Integration mode and topology detection* on page 2-25.

- Constraints and limitations of use on page 2-26.

### 2.1 About the functions

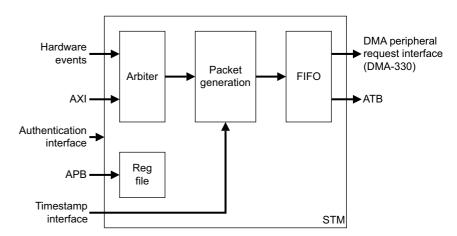

Figure 2-1 shows the main functional blocks of the STM.

Figure 2-1 STM block diagram

The STM implements tracing of software writes to its stimulus ports using the AXI interface and tracing of hardware events in the following manner:

- Selects stimulus ports and hardware events to be traced based on programmed controls and the state of the authentication interface.

- 2. Arbitrates, with higher priority assigned to AXI transactions, between traced transactions from the two interfaces, AXI and hardware events.

- 3. Presents the trace data to the packet generation logic, which timestamps and organizes the trace data according to the STPv2 protocol.

- 4. Packs the STPv2 data into the trace stream and outputs the stream on the ATB interface. In case of an overflow, that is, when the STM FIFO is full, the STM can either stall the AXI or drop the data indicating an overflow condition in the trace stream. There is no stall mechanism on the hardware interface. For hardware events, the STM either silently drops the event or indicates an overflow condition in the trace stream.

- 5. Periodically outputs a synchronization sequence to enable the trace receiver to align packet boundaries in the trace stream.

### 2.2 Interfaces

The STM interfaces are not configurable except for the AXI\_ID\_WIDTH. The STM has the following external interfaces:

### **AXI** slave interface

This interface connects the STM to the system bus. This design provides a 64-bit AMBA AXI4 slave. See the *ARM*<sup>®</sup> *AMBA*<sup>®</sup> *AXI and ACE Protocol Specification* for more information about the AXI signals.

This interface occupies writable space in the memory map that you can use to generate trace.

### Hardware event observation interface

This interface consists of 64 input signals, and connects to various signals from the system, such as interrupt lines, DMA request lines, and *Cross-Trigger Interface* (CTI) trigger outputs.

The STM captures hardware events on this interface and generates trace based on captured events. See *Hardware event tracing* on page 2-18.

### DMA peripheral request interface

This interface connects to a Corelink DMA Controller DMA-330. When you program the STM to initiate a DMA transfer, this interface requests the DMA controller to write to the STM AXI interface. See *DMA control* on page 2-19.

### Debug APB slave interface

This interface provides access to the STM configuration and status registers.

See the  $ARM^{\$}$   $AMBA^{\$}$  APB Protocol Specification and the  $ARM^{\$}$   $CoreSight^{\texttt{M}}$  Architecture Specification for more information about the debug APB signals.

### ATB master interface

The STM uses the AMBA 4 ATBv1.1 interface for trace output. It includes handshaking signals for making flush requests to the STM and the ability for external logic to request insertion of synchronization information into the trace stream. The interface width is 64 bits.

See the ARM® AMBA® 4 ATB Protocol Specification ATBv1.0 and ATBv1.1 for more information about the ATB signals.

### Timestamp port interface

This interface provides the timestamp that is used in timestamped trace packets. The timestamp is a 64-bit natural binary encoded number.

### **Authentication interface**

This interface provides connections for the CoreSight Authentication Interface.

The STM is a non-invasive debug component because it generates trace only in response to writes to its stimulus ports. See *Extended stimulus port interface* on page 2-12.

### Non-secure guaranteed stimulus port accesses enable interface

This interface provides control over behavior of Non-secure guaranteed accesses to the extended stimulus ports. See *Extended stimulus port interface* on page 2-12.

### Cross-trigger interface

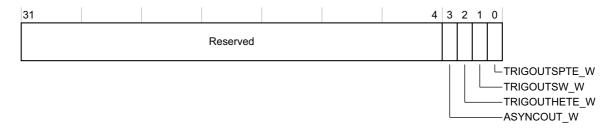

The STM implements three trigger output ports, **TRIGOUTSPTE**, **TRIGOUTSW**, and **TRIGOUTHETE**, to connect to a cross-trigger interface in a CoreSight system to indicate trigger events. The output ports correspond to the dedicated trigger outputs described in the *ARM® System Trace Macrocell Programmers' Model Architecture Specification*.

The **ASYNCOUT** output port indicates that alignment synchronization has occurred. You can use this port to generate other forms of periodic synchronization, for example by causing an interrupt on a processor. You must also connect this signal to a cross-trigger interface input.

### Low-power interfaces

The STM includes two low-power interfaces that are used by a clock controller to determine whether the clock to the STM can be stopped:

- The AXI low-power interface to determine if the AXI slave and DMA interfaces are idle.

- The STM low-power interface to determine if the rest of the STM is idle.

A clock controller must only stop the clock if both low power interfaces indicate that the STM is idle.

### 2.3 Clocking and resets

The following sections describe the STM clock and resets:

- Clock.

- Resets.

### 2.3.1 Clock

The STM has a single clock input, **CLK**, which is synchronous to the system bus clock. You must use asynchronous bridges when connecting the STM interfaces to differently-clocked buses.

To minimize power consumption when not enabled, the STM implements architectural clock gating. The STM gates the internal clock for all parts of the design except for the AXI slave, DMA peripheral request, and low-power interfaces. These interfaces must be able to respond to transactions from the system interconnect, the DMA controller, and the clock controller for the low-power interfaces.

The architectural clock gating is transparent to the programmer. The internal clock is enabled when you access the STM registers or enable tracing.

### 2.3.2 Resets

The STM has two asynchronous active LOW resets:

ARESETn The ARESETn reset domain resets the AXI slave, the DMA peripheral

request blocks, and the AXI low-power interface.

**STMRESETn** The **STMRESETn** reset domain resets the rest of the STM, including the

hardware event observation interface, the APB interface register file, the STM low-power interface, and the *Trace Generation Unit* (TGU).

The STM supports independent assertion of both resets, and can:

- Maintain the STM state through an AXI reset, ARESETn asserted, and STMRESETn not asserted.

- Reset debug logic without resetting the rest of the system, ARESETn not asserted, and STMRESETn asserted.

### 2.4 Trace protocol

Trace generated by the STM conforms to the MIPI System Trace Protocol version 2 (STPv2).

The STM provides 65,536 STPv2 channels for flexibility and for enabling additional definition of message boundaries. These channels directly map to the 65,536 extended stimulus ports.

The maximum size data packet generated is 64 bits.

The following sections describe trace protocol:

- Trace packets.

- *Alignment synchronization* on page 2-7.

- Error packets on page 2-8.

- *Trace output* on page 2-9.

### 2.4.1 Trace packets

Table 2-1 shows the valid trace packets that the STM generates.

Table 2-1 Generated trace packets

| Name                                    | Туре      | Description                                                                                                                                                                                                                                      |

|-----------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASYNC                                   | Alignment | Provides alignment synchronization for the trace stream. This packet is always followed by a VERSION packet.                                                                                                                                     |

| C8, C16                                 | Channel   | Channel indicator. The STM sends a C8 or C16 packet only when the software channel changes. C16 indicates a change in any of the upper 8 bits of the channel number. C8 indicates that the channel change is limited to any of the lower 8 bits. |

|                                         |           | The default channel is 0, which is set when the STM generates a VERSION packet.                                                                                                                                                                  |

| D4, D8, D16, D32, D64                   | Data      | Data only                                                                                                                                                                                                                                        |

| D4M, D8M, D16M, D32M, D64M              | Data      | Data with marker                                                                                                                                                                                                                                 |

| D4TS, D8TS, D16TS, D32TS, D64TS         | Data      | Data with timestamp                                                                                                                                                                                                                              |

| D4MTS, D8MTS, D16MTS,<br>D32MTS, D64MTS | Data      | Data with marker and timestamp                                                                                                                                                                                                                   |

| M8                                      | Master    | Master indicator. The STM sends this packet only when the source master for the trace changes.                                                                                                                                                   |

|                                         |           | The default master is 0, which is set when the STM generates a VERSION packet.                                                                                                                                                                   |

| MERR                                    | Error     | Master error. Generated when the STM drops stimulus because of a full buffer.                                                                                                                                                                    |

| GERR                                    | Error     | Global error. Generated when the STM drops stimulus from multiple masters because of a full buffer and the STM cannot send MERR for each master.                                                                                                 |

| FLAG                                    | Marker    | Flag, can indicate message boundaries                                                                                                                                                                                                            |

| FLAG_TS                                 | Marker    | Flag with timestamp                                                                                                                                                                                                                              |

| NULL                                    | Filler    | Filler packet. The STM can insert this to byte align the trace stream for the ATB output.                                                                                                                                                        |

| TRIG                                    | Trigger   | Trigger                                                                                                                                                                                                                                          |

Table 2-1 Generated trace packets (continued)

| Туре      | Description                                                                                                                                                                                                                 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Trigger   | Trigger with timestamp                                                                                                                                                                                                      |

| Version   | Indicates protocol version. Always sent immediately after ASYNC. Also resets the active master and channel values to 0.  The STM generates the following VERSION value only:  3 STPv2 with natural binary STPv2 timestamps. |

| Frequency | Indicates the frequency of the global system counter supplying timestamp information, in Hertz.  The STM always sends this packet immediately after an ASYNC-VERSION                                                        |

|           | Trigger<br>Version                                                                                                                                                                                                          |

\_\_\_\_ Note \_\_\_\_

See *Constraints and limitations of use* on page 2-26 for information about STPv2 trace packets that the STM does not generate.

### 2.4.2 Alignment synchronization

To comply with STPv2, STM performs alignment synchronization of the trace stream by generating an ASYNC packet followed by a VERSION packet. If you enable timestamping, a FREQ packet follows the VERSION packet.

The STM generates alignment synchronization packets as the first packets after the STM is enabled, and in response to synchronization requests.

In addition, the **ASYNCOUT** output signal uses a one-cycle pulse to indicate every alignment synchronization carried out by the STM.

### Synchronization request sources

The synchronization request sources can be internal or external:

### Internal synchronization requests

The STM generates an internal synchronization request when one of the following events occur:

- The STM is enabled.

- The STMTSFREQR is programmed.

- The STMSYNCR is programmed.

- The synchronization period ends, defined in terms of number of bytes of trace generated. The synchronization period is defined by the STMSYNCR.

### **External synchronization requests**

An external synchronization request comes from outside the STM through the **SYNCREQM** signal. This enables the system to indicate that the STM must perform alignment synchronization at the next opportunity.

Both internal and external synchronization requests are disabled when the STM is disabled, that is, the STMTCSR.EN bit is set to 0b0.

### Synchronization request combining

The STM combines internal and external synchronization requests to avoid excessive ATB bandwidth usage when requests occur near each other.

### Synchronization priority escalation

This feature addresses non-typical usage cases. In a typical trace scenario, you must not enable this feature, that is, leave the STMAUXCR at its reset value.

The STMAUXCR contains an override control to guarantee synchronization insertion when required. You can enable the override by programming the STMAUXCR.ASYNCPE bit. The behavior of override control is as follows:

- If the STM cannot insert the synchronization packets, the request remains pending.

- If the STM receives another synchronization request when there is a request pending and the STMAUXCR.ASYNCPE bit is set, the STM escalates the priority of the synchronization request.

- The STM stalls trace data if required when inserting a high priority synchronization request.

The STMAUXCR is implementation defined. Controls defined in this register are not defined in the *ARM® System Trace Macrocell Programmers' Model Architecture Specification*. There is no guarantee that other implementations of the architecture have the same controls in the STMAUXCR.

### 2.4.3 Error packets

The STM generates and inserts error packets in the trace stream when information is lost because of overflow.

### **MERR** packets

MERR packets are master-specific. A MERR packet referring to a currently inactive master is preceded by an M8 packet. The STM resets the active channel to zero after the MERR packet is generated.

MERR packets have an 8-bit payload that is always 0x00.

### **GERR** packets

The STM generates and inserts GERR packets in the trace stream when more than one master experiences an error condition and a MERR packet cannot be output for each master.

GERR packets have an 8-bit payload that is always 0x00.

### 2.4.4 Trace output

The STM always tries to perform 64-bit ATB transactions to maximize trace bandwidth efficiency. Therefore, it can hold trace packet nibbles until enough nibbles are generated to enable a 64-bit ATB transaction. The exceptions to this are when:

- An ATB flush is requested.

- The STM is disabled.

- Auto-flush is enabled.

- Authentication permissions are removed.

In these cases, the STM can perform smaller-size ATB transactions after byte aligning the data.

### 2.5 Timestamping

The STM supports timestamping of trace using values from a system global counter. The timestamp is a 64-bit natural binary encoded value.

### 2.6 Triggering

A trigger event indicates points of interest within the trace. The STM supports triggering functionality through:

- Assertion of the trigger outputs, TRIGOUTSPTE, TRIGOUTSW, and TRIGOUTHETE.

- Insertion of TRIG or TRIG\_TS packets into the trace stream.

- Use of the trigger ATID on the ATB interface.

See the ARM® System Trace Macrocell Programmers' Model Architecture Specification for more information about triggers.

### 2.6.1 TRIGOUT ports

The **TRIGOUTSPTE**, **TRIGOUTSW**, and **TRIGOUTHETE** ports are part of a cross-trigger interface. The STM asserts these ports to indicate to the system that trigger events have occurred. The corresponding port is asserted in every cycle in which a particular trigger event has occurred. Table 2-2 shows the function of the TRIGOUT ports.

**Table 2-2 TRIGOUT ports**

| TRIGOUT port | Trigger event               |

|--------------|-----------------------------|

| TRIGOUTSPTE  | Match using the STMSPTER.   |

| TRIGOUTSW    | Write to the TRIG location. |

| TRIGOUTHETE  | Match using the STMHETER.   |

### 2.7 Extended stimulus port interface

The STM implements an extended stimulus port interface using AXI. There are 65,536 channels implemented as a stimulus port per channel, occupying a total of 16MB in the AXI memory space. See the *ARM® System Trace Macrocell Programmers' Model Architecture Specification* for more information about the extended stimulus port interface.

The STM implements an AMBA AXI4 slave with the following attributes for extended stimulus port functionality:

- Write acceptance capability of three.

- Read acceptance capability of one.

- Read data reordering depth of one, that is, no reordering.

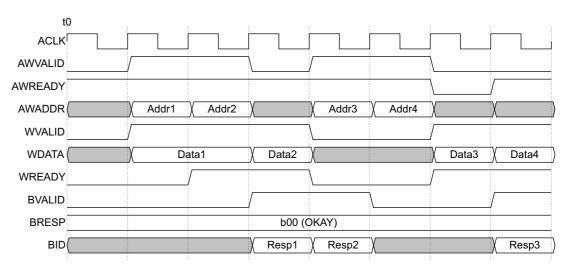

Figure 2-2 shows an example AXI write sequence.

Figure 2-2 Example AXI write sequence

The following sections describe the extended stimulus port interface:

- AXI responses.

- STM enabled.

- *STM disabled* on page 2-17.

- *AXI reads* on page 2-17.

- Stimulus port and trigger enables on page 2-17.

- *Invariant-timing packets and overflow* on page 2-17.

### 2.7.1 AXI responses

The STM gives an OKAY response for all transfers. The trace output indicates error conditions during STM operation, such as dropped requests.

### 2.7.2 STM enabled

The following sections describe the operation when the STM is enabled:

- Guaranteed and invariant timing transactions on page 2-13.

- *Multiple STPv2 master support* on page 2-13.

- *Timestamp requests* on page 2-14.

- *WSTRBS usage* on page 2-14.

- *AWSIZE usage* on page 2-15.

- Writes to disabled stimulus ports on page 2-15.

- Access control based on AWPROT on page 2-15.

- Non-secure guaranteed access control on page 2-16.

- *Overrides* on page 2-16.

### Guaranteed and invariant timing transactions

The STM supports both types of software stimulus transfers, that is, guaranteed and invariant timing. It considers transaction properties, such as master enable, stimulus port enable, override controls, and guaranteed or invariant timing, for each AXI burst beat.

### Behavior on guaranteed transactions

If you make a guaranteed transaction when the STM is unable to accept the transaction immediately, the STM stalls the AXI write data channel until the write can be accepted, inserting as many wait states as necessary by keeping the **WREADY** signal LOW.

Use only a guaranteed write for critical trace information because it guarantees that a trace packet is generated for the write transaction. The wait states can adversely affect system performance.

### Behavior on invariant timing transactions

If you make an invariant timing transaction when the STM is unable to trace the transaction immediately, the STM does not stall the AXI. After the address transfer, the STM drives the **WREADY** signal HIGH, enabling the data transfer. The STM discards write data if it cannot be traced.

There is no guarantee that an invariant timing write results in a trace packet appearing in the trace stream.

### Multiple STPv2 master support

The STM supports multiple STPv2 masters. For AXI transactions, the master identification is based on all of the following:

- Whether the access is Secure or Non-secure.

- The upper bits of the AXI address.

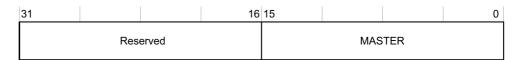

Software stimulus has 128 master IDs allocated, 0x00-0x7F. The lower half of the master ID space is for Secure accesses and the upper half for Non-secure accesses.

The STPv2 master ID from the AXI stimulus port is constructed as:

- [7] = 0b0.

- [6] = AWPROTS[1].

- [5:0] = AWADDRS[29:24].

In this ID, master IDs 0-63 are allocated to Secure transactions and master IDs 64-127 to Non-secure transactions.

ARM strongly recommends that the **AWADDRS[29:24]** signal is driven uniquely for each master in the system. For example, transactions that arrive at the STM drive the **AWADDRS[29:24]** signal with a unique value for each core in a processor cluster. Typically, this means that the system interconnect drives the **AWADDRS[29:24]** signal with a value derived from the original master of the transaction. However, it does not mean that the software instrumentation controls the **AWADDRS[29:24]** signal.

Instrumentation from each master is uniquely identified in the output trace stream.

### **Timestamp requests**

Transactions to extended stimulus ports can include a timestamp request. You can promote transactions to extended stimulus ports to include a timestamp request by writing 0b1 to the STMTSSTIMR.FORCETS bit. If a transaction already includes a timestamp request, the FORCETS bit value has no effect.

### Timestamping guaranteed writes

Timestamp requests from guaranteed writes are compulsory. This guarantees that a timestamp is included in the packet generated from the write. The AXI slave stalls all future writes if it cannot accommodate the timestamp request.

### Timestamping invariant timing writes

The STM treats timestamp requests in an invariant timing transaction as sticky. A sticky timestamp request means that if the STM cannot accommodate a timestamp in the STM FIFO, the request remains pending and timestamp insertion occurs at the next opportunity. Sticky timestamp requests do not stall the STM.

The STM clears the pending sticky timestamp state when the timestamp is output regardless of whether a new transaction has its own timestamp request or not. This guarantees that a timestamp is eventually inserted into the trace stream because of the transaction. However, the timestamp might be attached to a different packet, and the number of timestamps generated might be fewer than the number requested.

### **WSTRBS** usage

The STM uses the **WSTRBS** signal to determine the size of the transfer and the location of the data on the data bus, and ignores the value of the **AWADDRS[2:0]** signal. Table 2-3 shows the supported values of the **WSTRBS** signal, whether the encoding is permitted to be the first in a burst, which lanes of the **WDATAS** channel are used, and, by example, the packet that is produced when **AWADDR[6:3]** = 0x0.

**Table 2-3 Supported values of WSTRBS**

| WSTRBS     | Permitted to start a burst | Data          | Packet when AWADDR[6:3] = $0 \times 0$ |

|------------|----------------------------|---------------|----------------------------------------|

| 0b00000000 | Yes                        | -             | No data output.                        |

| 0b00000001 | Yes                        | WDATAS[7:0]   | D8MTS                                  |

| 0b00000010 | No                         | WDATAS[15:8]  | D8MTS                                  |

| 0b00000100 | No                         | WDATAS[23:16] | D8MTS                                  |

| 0b00001000 | No                         | WDATAS[31:24] | D8MTS                                  |

| 0b00010000 | No                         | WDATAS[39:32] | D8MTS                                  |

| 0b00100000 | No                         | WDATAS[47:40] | D8MTS                                  |

| 0b01000000 | No                         | WDATAS[55:48] | D8MTS                                  |

| 0b10000000 | No                         | WDATAS[63:56] | D8MTS                                  |

| 0b00000011 | Yes                        | WDATAS[15:0]  | D16MTS                                 |

| 0b00001100 | No                         | WDATAS[31:16] | D16MTS                                 |

| 0b00110000 | No                         | WDATAS[47:32] | D16MTS                                 |

|            |                            |               |                                        |

Table 2-3 Supported values of WSTRBS (continued)

| WSTRBS     | Permitted to start a burst | Data          | Packet when AWADDR[6:3] = 0x0 |

|------------|----------------------------|---------------|-------------------------------|

| 0b11000000 | No                         | WDATAS[63:48] | D16MTS                        |

| 0b00001111 | Yes                        | WDATAS[31:0]  | D32MTS                        |

| 0b11110000 | No                         | WDATAS[63:32] | D32MTS                        |

| 0b11111111 | Yes                        | WDATAS[63:0]  | D64MTS                        |

All other values of the **WSTRBS** signal result in UNPREDICTABLE behavior. Unaligned transfers are not supported.

You must align all write data bursts so that the **WDATAS[0]** signal is the LSB at the start of the burst. Writes to other alignments are architecturally UNPREDICTABLE.

### **AWSIZE** usage

| Jse the AWSIZE signal to control the address increment between beats of an incrementing |

|-----------------------------------------------------------------------------------------|

| purst.                                                                                  |

| Note                                                                                    |

|                                                                                         |

| The AWSIZE signal is not used when calculating the packet type                          |

### Writes to disabled stimulus ports

The STM responds to writes to disabled stimulus ports in the same way as for invariant timing transactions:

- The data is ignored and no trace is generated.

- Error packets are not generated when these writes are ignored.

### Access control based on AWPROT

On writes, the STM compares the value of the **AWPROT[1]** signal with the current authentication status of the STM. If the value corresponds to a Secure transaction when Secure accesses are disabled, the STM drops the access as if the stimulus port were disabled.

See the  $ARM^{\circledast}$   $CoreSight^{\bowtie}$  Architecture Specification for more information about Secure and Non-secure accesses to CoreSight components.

| Note                       |           |           |          |               |

|----------------------------|-----------|-----------|----------|---------------|

| The STM ignores the values | of the AW | PROT[2] a | nd AWPRO | Γ[0] signals. |

|                            |           |           |          |               |

Table 2-4 shows the authentication control with Non-secure access for the AWPROT[1] signal.

**Table 2-4 Authentication control with Non-secure access**

|               | Permitted level of debug |                     |                     |                            |                 |

|---------------|--------------------------|---------------------|---------------------|----------------------------|-----------------|

| AWPROT[1]     | Secure invasive          | Non-secure invasive | Secure non-invasive | Non-secure<br>non-invasive | Action on write |

| 1, Non-secure | -                        | -                   | -                   | 1                          | Capture         |

| 1             | -                        | -                   | -                   | 0                          | Drop            |

| 0, Secure     | -                        | -                   | 1                   | -                          | Capture         |

| 0             | -                        | -                   | 0                   | -                          | Drop            |

See the *ARM*<sup>®</sup> *CoreSight*<sup>™</sup> *Architecture Specification* for information about mapping authentication signals, **DBGEN**, **NIDEN**, **SPIDEN**, and **SPNIDEN**, to the permitted level of debug.

### Non-secure guaranteed access control

The top-level static configuration port, **NSGUAREN**, controls the behavior of the STM for Non-secure guaranteed AXI accesses:

- When the **NSGUAREN** signal is LOW, Non-secure guaranteed accesses behave like invariant timing accesses, that is, the AXI does not stall.

- When the **NSGUAREN** signal is HIGH, Non-secure guaranteed accesses are enabled, that is, the AXI can stall and the trace output is guaranteed.

### **Overrides**

The debugger can override the stimulus ports selected by using the STMSPOVERRIDER and STMSPMOVERRIDER to always treat transactions as guaranteed or as invariant timing transactions.

When overriding transactions to be guaranteed, the STM treats the overrides as invasive debug because the debugger might increase the level of intrusion defined by system software. The guaranteed override is possible only when invasive debug is permitted. When invasive debug is disabled, the override has no effect.

Table 2-5 shows the authentication control with guaranteed override.

Table 2-5 Authentication control with guaranteed override

| AWPROT[1]     | Secure invasive | Non-secure invasive | Secure<br>non-invasive | Non-secure non-invasive | Guaranteed  |

|---------------|-----------------|---------------------|------------------------|-------------------------|-------------|

| 1, Non-secure | -               | 1                   | -                      | -                       | Allowed     |

| 1             | -               | 0                   | -                      | -                       | Not allowed |

| 0, Secure     | 1               | -                   | -                      | -                       | Allowed     |

| 0             | 0               | -                   | -                      | -                       | Not allowed |

See the *ARM® CoreSight™ Architecture Specification* for information about mapping the authentication signals, **DBGEN**, **NIDEN**, **SPIDEN**, and **SPNIDEN**, to the permitted level of debug.

There are no requirements for debug permissions when overriding transactions to make them invariant timing transactions.

#### 2.7.3 STM disabled

When the STM is disabled, it accepts all writes immediately and ignores the write data. This behavior is identical to when all the STM stimulus ports are disabled.

#### 2.7.4 AXI reads

All STM memory-mapped registers presented on the AXI are write-only. Reads always return an AXI OKAY read response and the read data is zero regardless of the STM state.

### 2.7.5 Stimulus port and trigger enables

You can enable or disable stimulus ports and triggers using the STMSPER, STMSPTER, and STMSPSCR. See the *ARM® System Trace Macrocell Programmers' Model Architecture Specification* for more information about stimulus ports and triggers.

#### 2.7.6 Invariant-timing packets and overflow

If you perform a write access to an invariant-timing stimulus port location on the software stimulus interface, the STM immediately accepts the access, regardless of the state of the STM buffers. If there is not enough space for the generated packet in the STM buffer, the STM discards the data, and the data does not appear in the trace output.

If the data is discarded as a result of invariant timing writes made while the STM buffer is full, the STM adds a MERR packet to the STM buffer when space is available in the buffer. The STM generates only one MERR packet regardless of the number of discarded transactions, until:

- At least one of the other packet types is successfully generated and added to the buffer.

- The master ID is changed.

If the new data is discarded with a master ID different from the previously discarded transaction, and there is a MERR packet pending that has not been accepted by the STM FIFO, the STM generates a GERR packet instead.

# 2.8 Hardware event tracing

The STM hardware event observation interface enables monitoring and tracing of 64 hardware events, each of which is represented by a single bit. You can use this functionality to monitor interrupts, cross-triggers, and other signals in your system. The STM captures and traces, as a data packet, asserted and enabled hardware events.

Before you synthesize the STM-500, you can configure each hardware event to be rising-edge-sensitive or level-sensitive. When configured for level-sensitive observation, the STM treats each cycle on which you assert a hardware event input as a separate event.

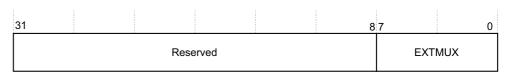

The STM-500 can observe more than 64 hardware events, by using external multiplexing logic. You can control the multiplexing logic by using the STMHEEXTMUXR. The value of the STMHEEXTMUXR is output on the output bus HEEXTMUX from the STM.

To enable the STM to monitor and trace cross-trigger events in the system, ARM recommends that you:

- 1. Connect at least two trigger outputs from a CTI to hardware event inputs on the STM.

- 2. Connect the inverse of these CTI trigger outputs to the hardware event inputs on the STM to enable falling edges of these signals to be traced.

- 3. Configure the hardware events to be rising-edge-sensitive.

- 4. Enable the CTI connections when the **HEEXTMUX**[7:0] signal output is zero if you use external multiplexing logic and control the logic by the **HEEXTMUX**[7:0] signal.

You can enable triggers for hardware events, in which case the assertion of the event, when captured, also causes a trigger event.

The STM can merge multiple different hardware events into a single traced event.

If you assert the same hardware event multiple times while the first captured assertion is pending and has not yet been traced, the STM traces only one assertion and drops the others. If you enable error detection, the STM generates a MERR packet to indicate that merging has occurred.

See the ARM® System Trace Macrocell Programmers' Model Architecture Specification for more information about hardware events.

#### 2.9 DMA control

The STM has a DMA peripheral request interface designed to function with a CoreLink DMA-330 DMA Controller. This interface enables the STM to request write accesses to its extended stimulus ports using the DMA controller. You must set up and program the DMA controller with the required transactions before enabling this functionality in the STM.

See the  $ARM^{\circ}$  CoreLink<sup>TM</sup> DMA-330 DMA Controller Technical Reference Manual for more information about the specification of this interface.

## 2.9.1 Starting and stopping requests

The registers for controlling the DMA peripheral request interface are in the STM APB memory space:

- Program the STM to create DMA requests by writing 0b1 to the STMDMASTART.START bit. When programmed to create requests, the interface can create DMA controller requests whenever the STM FIFO has enough free space and a DMA transaction is not in progress. The interface creates requests repeatedly until programmed to stop.

- Program the STM to stop DMA requests by writing 0b1 to the STMDMASTOP.STOP bit.

When programmed to stop, the STM does not create any more DMA controller requests.

Programming the interface to stop does not affect the progress of any existing active DMA transaction.

### 2.9.2 FIFO level monitoring

You can configure the DMA peripheral request interface to wait until a certain amount of free space is available in the STM FIFO before issuing the request.

FIFO level monitoring does not guarantee FIFO space for transactions from the DMA controller. However, this reduces the risk of a large number of invariant timing writes being dropped or guaranteed writes stalling the AXI interconnect for an extended period of time.

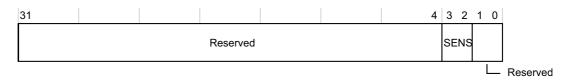

You can program the sensitivity of the DMA request to the current FIFO level using the STMDMACTLR.SENS bit. When FIFO conditions are met, the STM makes a DMA request. When the request is asserted, it remains asserted until accepted by the DMA controller, even if FIFO space is no longer available.

#### 2.9.3 DMA interface behavior

The DMA interface functions as follows:

- When you start a DMA request by writing 0b1 to the STMDMASTART.START bit, the STM initiates a burst transfer by setting the **DRTYPE[1:0]** signal to 0b01.

- When a burst is acknowledged by setting the **DATYPE[1:0]** signal to 0b01, the STM initiates a new burst transfer as soon as there is sufficient space in the FIFO as described in *FIFO level monitoring*. The STM ignores single transfer acknowledges.

- When a flush is requested by setting the **DATYPE[1:0]** signal to 0b10, the STM abandons a burst request and acknowledges the flush by setting the **DRTYPE[1:0]** signal to 0b10. If DMA transfers are still enabled, the STM initiates a new burst immediately.

- The **DRLAST** signal is always 0b0.

• The **DAVALID**, **DRVALID**, **DAREADY**, and **DRREADY** signals function with the preceding signals as described in the *ARM® CoreLink™ DMA-330 DMA Controller Technical Reference Manual*.

# 2.10 Data compression

The STM supports leading-zero trace data compression. You can enable support for this functionality for each of the extended stimulus port and hardware event observation front-end input interfaces:

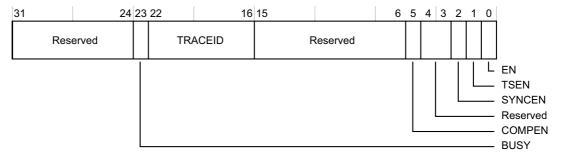

- Program the STMTCSR.COMPEN bit to control the compression functionality for the extended stimulus ports.

- Program the STMHEMCR.COMPEN bit to control the compression functionality for the hardware event observation interface.

This compression method chooses a smaller data packet size than that specified by the stimulus if the data contains enough leading zeros. For example, if you write a 32-bit value of 0x00000FFFF to the stimulus port and enable compression, the STM generates a D16 packet rather than a D32 packet. A value of 0x00000FFF generates a D16 packet because the highest nonzero bit (11) is beyond the range of a D8 packet.

You must only enable compression for extended stimulus ports if the size of every write to the STM is known, for example because every write is 32 bits. This is because the original size of each STM write is not indicated in the packet when compression is enabled.

You can enable compression for the hardware event observation interface without losing information.

# 2.11 Buffer flushing

The STM might be required to flush its buffers, that is, output all buffered trace as soon as possible, in the following situations:

- A flush request is made over ATB using the AFVALIDM signal. The STM continues to

accept new stimulus writes. The flush is complete when all trace generated before the

flush request is output.

- The STM is disabled by reprogramming the STMTCSR.EN bit with 0b0. The STM drops new stimulus until it is enabled again.

- Auto-flush is enabled in the STMAUXCR.

- Authentication is removed.

On a flush request, the STM continues outputting 64-bit ATB transactions as normal. However, if insufficient nibbles remain in the buffer for a 64-bit transaction, the STM does not wait. It chooses the most appropriate transaction size and pads the buffer contents with NULL nibbles for the ATB transaction.

#### \_\_\_\_\_Note \_\_\_\_\_

- These features in the STMAUXCR are present to address non-typical usage cases. Do not

enable these features in a typical trace scenario, that is leave the STMAUXCR at its reset

value.

- The STMAUXCR is IMPLEMENTATION DEFINED. Controls defined in this register are not defined in the *ARM® System Trace Macrocell Programmers' Model Architecture Specification*. There is no guarantee that other implementations of the architecture have the same controls as the STMAUXCR.

The following sections describe buffer flushing:

- Override using auto-flush.

- *ATB flush request and priority inversion.*

### 2.11.1 Override using auto-flush

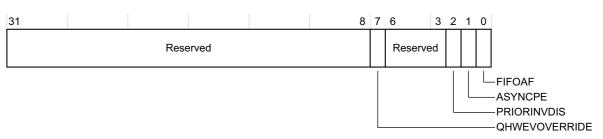

You can enable the STM to output ATB transactions that are smaller than 64 bits, without waiting for sufficient data to complete a 64-bit transaction. To override this behavior, program the STMAUXCR.FIFOAF bit with 0b1, which enables auto-flush of the STM FIFOs.

When auto-flush is enabled, if the FIFO contains insufficient data for a 64-bit ATB transfer and has all its other entries empty, the STM performs a smaller-sized ATB transaction rather than waiting for more data, padding the data with as many NULL packets as required for byte alignment. For example:

- If there are five nibbles to output (20 bits), the STM inserts a NULL packet to create a 24-bit transaction.

- If there are three nibbles to output (12 bits), the STM inserts a NULL packet to create a 16-bit transaction.

- If there are two nibbles to output, no NULL packets are required.

### 2.11.2 ATB flush request and priority inversion

The STM acknowledges ATB flush requests by asserting the **AFREADYM** output signal, after all data present in the STM before the ATB flush request has been output.

The default behavior on an ATB flush request is to flush AXI stimulus historical data first, and then flush historical data from hardware event tracing. When historical AXI data has been flushed, the STM temporarily inverts the priority and assigns a higher priority to hardware event tracing until it is flushed. This helps the flush to complete as soon as possible, but can cause loss of invariant transactions on the AXI.

You can use the override control in the STMAUXCR to disable priority inversion during flush. If you set the STMAUXCR.PRIORINVDIS bit, the AXI stimulus port trace remains higher priority than hardware events trace during flush. This can delay the STM flush acknowledgement because the STM can output new AXI trace before historical hardware event data.

# 2.12 ATB data ordering

When ATB transfers are generated, the STM modifies the order of the data from the original packet values. The STM splits the channel, data, and timestamp values into nibbles and writes them in reverse nibble order, most significant nibble first in the data stream, after the packet header (opcode) or timestamp size.

For example, a write requesting a D32TS at stimulus port 20 of value 0x12345678 with timestamp offset of value 0x1234 produces the following data values:

- Channel packet C8 = 0x3, 0x14 (opcode, channel number).

- Data packet D32TS = 0xF6, 0x12345678 (opcode, data value).

- Associated timestamp TS = 0x4, 0x1234 (size = 4 nibbles, timestamp value).

The generated ATB transactions are:

0x21487654\_3216F413 0xXXXXXXXXXXXXXXXX43

Xs are filled by the next packet.

Table 2-6 shows the structure of the ATB transactions.

**Table 2-6 ATB transactions**

| ATB 32-bit transaction | ATB data nibbles                                        | Source data nibbles                       |

|------------------------|---------------------------------------------------------|-------------------------------------------|

| First doubleword       | [63:60] = 0x2                                           | TS value[11:8]                            |

| 0x21487654_3216F413    | [59:56] = 0x1                                           | TS value[15:12]                           |

|                        | [55:52] = 0x4                                           | TS size[3:0]                              |

|                        | [51:48] = 0x8                                           | D32TS data[3:0]                           |

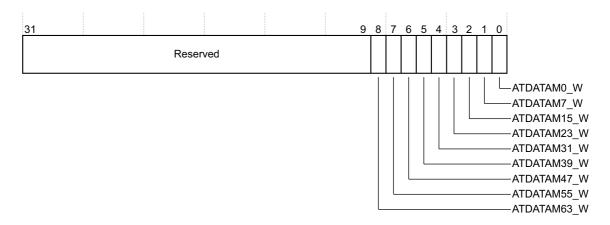

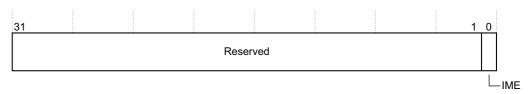

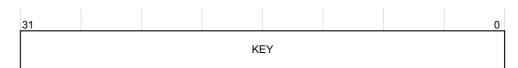

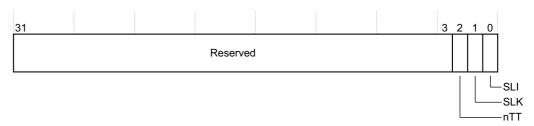

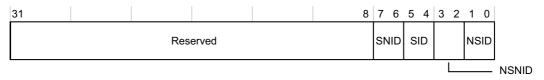

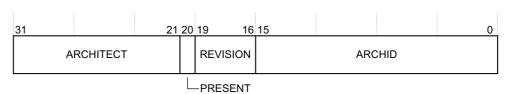

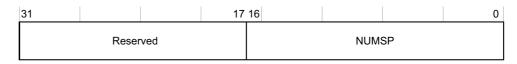

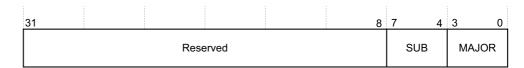

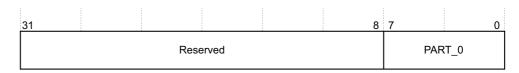

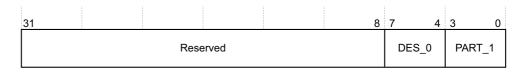

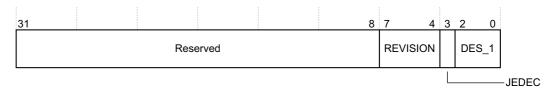

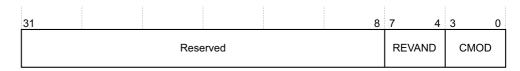

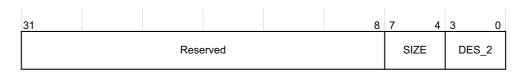

|                        | [47:44] = 0x7                                           | D32TS data[7:4]                           |