# DesignStart FPGA on Cloud: Cortex-M33 based platform

# **Technical Reference Manual**

**Non-Confidential**

# DesignStart FPGA on Cloud: Cortex-M33 based platform

Copyright © 2018 ARM. All rights reserved.

#### **Release Information**

The following changes have been made to this document.

|                 |         |                  |                | Change Histor |

|-----------------|---------|------------------|----------------|---------------|

| Date            | Issue   | Confidentiality  | Change         |               |

| 23 October 2018 | 0000-00 | Non-Confidential | First Release. |               |

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or <sup>™</sup> are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at <a href="http://www.arm.com/company/policies/trademarks">http://www.arm.com/company/policies/trademarks</a>.

Copyright © 2018 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England. 110 Fulbourn Road, Cambridge, England CB1 9NJ. LES-PRE-20349

# Contents

# DesignStart FPGA on Cloud: Cortex-M33 based platform

| 1   | Conventions and feedback1-3          |

|-----|--------------------------------------|

| 2   | Preface                              |

| 2.1 | Purpose of this application note2-1  |

| 2.2 | References2-1                        |

| 2.3 | Terms and abbreviations2-1           |

| 2.4 | Subsystem version details            |

| 3   | Overview                             |

| 3.1 | System block diagram                 |

| 3.2 | SIE200 components                    |

| 3.3 | Memory protection note 3-4           |

| 3.4 | Memory map overview                  |

| 4   | Programmers Model                    |

| 4.1 | CMSDK and SIE200 components4-12      |

| 4.2 | SRAMs                                |

| 4.3 | UART 4-13                            |

| 4.4 | FPGA system control and I/O 4-13     |

| 4.5 | Serial Communication Controller 4-13 |

| 5   | Clock and reset architecture         |

| 5.1 | Clocks 5-15                          |

| 5.2 | Resets 5-16                          |

| 6   | FPGA secure privilege control        |

| 7   | Interrupt map7-20                    |

| 7.1 | UARTS interrupts7-21                 |

| 8   | Configurations                       |

| 8.1 | IoT subsystem8-22                    |

| 8.2 | Cortex-M33 8-23                      |

| 9   | Host interfaces9-24                  |

| 9.1 | PCIe mapping9-24                     |

| 9.2 | vLED and vDIP mapping                |

# **1** Conventions and feedback

The following describes the typographical conventions and how to give feedback:

#### **Typographical conventions**

The following typographical conventions are used:

- monospace denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.

- monospace denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.

monospace italic

denotes arguments to commands and functions where the argument is to be replaced by a specific value.

| monospace | <b>bold</b> denotes language keywords when used outside example code.                                                                       |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------|

| italic    | highlights important notes, introduces special terminology, denotes internal cross-references, and citations.                               |

| bold      | highlights interface elements, such as menu names. Denotes signal names.<br>Also used for emphasis in descriptive lists, where appropriate. |

#### Feedback on this product

If you have any comments and suggestions about this product, contact your supplier and give:

- Your name and company.

- The serial number of the product.

- Details of the release you are using.

- Details of the platform you are using, such as the hardware platform, operating system type and version.

- A small standalone sample of code that reproduces the problem.

- A clear explanation of what you expected to happen, and what actually happened.

- The commands you used, including any command-line options.

- Sample output illustrating the problem.

- The version string of the tools, including the version number and build numbers.

#### Feedback on documentation

If you have comments on the documentation, e-mail errata@arm.com. Give:

- The title.

- The number, 101505\_0000\_00\_en.

- If viewing online, the topic names to which your comments apply.

- If viewing a PDF version of a document, the page numbers to which your comments apply.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

Arm periodically provides updates and corrections to its documentation on the Arm Information Center, together with knowledge articles and Frequently Asked Questions (FAQs).

#### Other information

- Arm Information Center, http://infocenter.arm.com/help/index.jsp

- Arm Technical Support Knowledge Articles, http://infocenter.arm.com/help/topic/com.arm.doc.faqs/index.html

- Arm Support and Maintenance, http://www.arm.com/support/services/supportmaintenance.php

- Arm Glossary, http://infocenter.arm.com/help/topic/com.arm.doc.aeg0014g/index.html

The Arm Glossary is a list of terms used in Arm documentation, together with definitions for those terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

# 2 Preface

# 2.1 Purpose of this application note

This application note discusses the operation of DesignStart FPGA on Cloud: Cortex-M33 based platform. DesignStart FPGA on Cloud: Cortex-M33 based platform is an FPGA implementation of an IoT Subsystem that uses SIE200 components together with CMSDK peripherals to provide an example design for the AWS F1 FPGA instances.

# 2.2 References

- Arm DDI 0218 PrimeCell<sup>®</sup> SingleMaster DMA Controller (PL081) Technical Reference Manual.

- Arm-ECM-0601256 Armv8-M IoT Kit User Guide.

# 2.3 Terms and abbreviations

| CMSDK | Cortex-M System Design Kit.             |

|-------|-----------------------------------------|

| DMA   | Direct Memory Access.                   |

| MCC   | Motherboard Configuration Controller.   |

| RAM   | Random Access Memory.                   |

| FPGA  | Field Programmable Gate Array.          |

| SCC   | Serial Configuration Controller.        |

| TRM   | Technical Reference Manual.             |

| APB   | Advanced Peripheral Bus.                |

| AHB   | Advanced High-performance Bus.          |

| RTL   | Register Transfer Level.                |

| SMM   | Soft Macrocell Model.                   |

| MSC   | Master Security Controller              |

| PPC   | Peripheral Protection Controller        |

| EAM   | Exclusive Access Controller             |

| MPC   | Memory Protection Controller            |

| IDAU  | Implementation Defined Attribution Unit |

| PCIe  | PCI-Express                             |

| BAR   | Base Address Register                   |

# 2.4 Subsystem version details

| Version                | Descriptions                                                                                                                                                                                   |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CG062<br>r1p0-00eac2   | Arm <sup>®</sup> Corelink <sup>™</sup> SSE-200 Subsystem for Embedded<br>Full version of the design kit supporting Cortex-M33 Also contains the AHB Bus Matrix and<br>advanced AHB components. |

| AT623/624<br>r0p2-rel0 | Arm <sup>®</sup> Cortex <sup>®</sup> -M33 and Arm <sup>®</sup> Cortex <sup>®</sup> -M33 FPU                                                                                                    |

| BP210<br>r1p0-01rel0   | Arm <sup>®</sup> Cortex <sup>®</sup> -M System Design Kit                                                                                                                                      |

| BP300<br>r3p1-00rel0   | Arm <sup>®</sup> CoreLink <sup>™</sup> SIE-200 System IP for Embedded                                                                                                                          |

| PL408<br>r0p0-00rel0   | Arm <sup>®</sup> CoreLink <sup>™</sup> LPD-500 Low Power Interface Distributor                                                                                                                 |

| TM100<br>r3p2-50rel0   | Arm <sup>®</sup> CoreSight <sup>™</sup> SoC-400                                                                                                                                                |

| TM976<br>r0p2-00rel0   | Arm <sup>®</sup> CoreSight <sup>™</sup> ETM-M33                                                                                                                                                |

| PL081<br>r1p2          | Arm <sup>®</sup> PrimeCell <sup>®</sup> Single Master DMA Controller                                                                                                                           |

|                        | Figure 2-1 Module version                                                                                                                                                                      |

This SMM is generated using various packages, which are detailed in the following figure.

# **3 Overview**

# 3.1 System block diagram

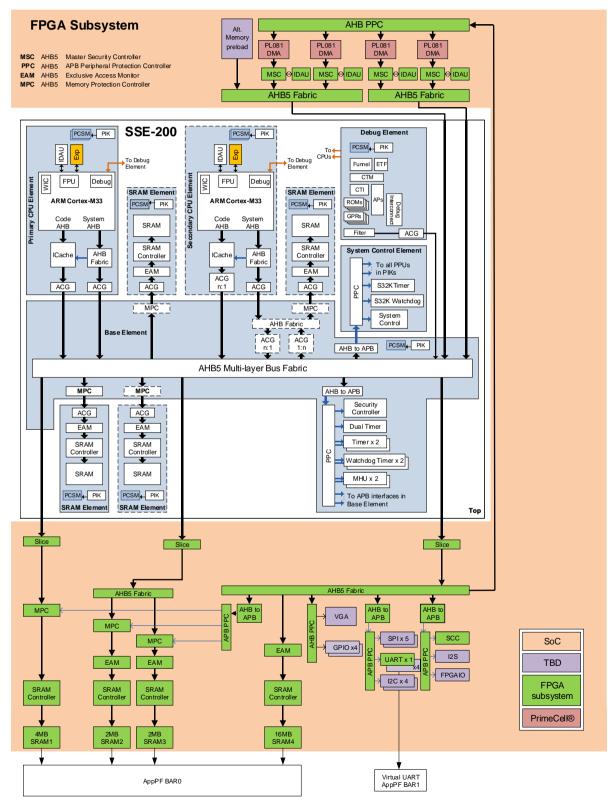

Figure 3-1 shows the high-level diagram of the full AWS F1 FPGA System.

Note how the FPGA Subsystem extends the *Armv8-M IoT Kit* by adding to its expansion interfaces.

A slice has been added before the IoT kit SRAM to maintain FPGA timing.

# 3.2 SIE200 components

The following SIE200 components are used in this system:

- TrustZone AHB5 peripheral protection controller.

- TrustZone AHB5 master security controller.

- AHB5 bus matrix.

- AHB5 to AHB5 synchronous bridge.

- AHB5 to APB synchronous bridge.

- TrustZone APB4 peripheral protection controller.

- TrustZone AHB5 memory protection controller.

- AHB5 exclusive access monitor.

- AHB5 default slave.

## 3.3 Memory protection note

The SIE200 MPC and PPC components can affect memory and IO security management and must be configured as required for your application. Please see *Armv8-M IoT Kit User Guide* (Arm-ECM-0601256).

# 3.4 Memory map overview

This memory map includes information regarding IDAU security information for memory regions. For more information on these, please refer to the SIE200 components documentation.

| ROW | Address     |             |       | Region             |                                                 | Alias          | IDAU Re    | gion Value | es     |

|-----|-------------|-------------|-------|--------------------|-------------------------------------------------|----------------|------------|------------|--------|

| ID  | From        | То          | Size  | Name               | Description                                     | With<br>Row ID | Security   | IDAUID     | NSC    |

| 1   | 0x0000_0000 | 0x0DFF_FFFF | 224MB | Code<br>Memory     | Maps to AHB5 Master<br>Expansion Code Interface | 3              | NS         | 0          | 0      |

| 2   | 0x0E00_0000 | 0x0FFF_FFFF | 32MB  | Reserved           | Reserved                                        |                |            |            |        |

| 3   | 0x1000_0000 | 0x1DFF_FFFF | 224MB | Code<br>Memory     | Maps to AHB5 Master<br>Expansion Code Interface | 1              | <u>_</u> S | 1          | CODE   |

| 4   | 0x1E00_0000 | 0x1FFF_FFFF | 32MB  | Reserved           | Reserved                                        |                |            |            | NSC2   |

| 5   | 0x2000_0000 | 0x20FF_FFFF | 16MB  | Internal<br>SRAM   | Internal SRAM Area.                             | 8              | _          |            |        |

| 6   | 0x2100_0000 | 0x27FF_FFFF | 112MB | Reserved           | Reserved                                        |                | NS         | 2          | 0      |

| 7   | 0x2800_0000 | 0x2FFF_FFFF | 128MB | Expansion 0        | Maps to AHB5 Master<br>Expansion 0 Interface    | 10             | -          |            |        |

| 8   | 0x3000_0000 | 0x30FF_FFFF | 16MB  | Internal<br>SRAM   | Internal SRAM Area.                             | 5              | _          |            |        |

| 9   | 0x3100_0000 | 0x37FF_FFFF | 112MB | Reserved           | Reserved                                        |                | S          | 3          | RAMNSC |

| 10  | 0x3800_0000 | 0x3FFF_FFFF | 128MB | Expansion 0        | Maps to AHB5 Master<br>Expansion 0 Interface    | 8              |            |            |        |

| 11  | 0x4000_0000 | 0x4000_FFFF | 64KB  | Base<br>Peripheral | Base Element Peripheral Region.                 | 18             | _          |            |        |

| 12  | 0x4001_0000 | 0x4001_FFFF | 64KB  | Private CPU        | CPU Element Peripheral<br>Region.               | 19             | _          |            |        |

| 13  | 0x4002_0000 | 0x4002_FFFF | 64KB  | System<br>Control  | System Control Element<br>Peripheral region.    | 20             | _          |            |        |

| 14  | 0x4003_0000 | 0x4003_FFFF |       | Reserved           | Reserved                                        |                | NS         | 4          | 0      |

| 15  | 0x4004_0000 | 0x4007_FFFF |       | Reserved           | Reserved                                        |                | -          |            |        |

| 16  | 0x4008_0000 | 0x400F_FFFF | 512KB | Base<br>Peripheral | Base Element Peripheral<br>Region.              | 23             | _          |            |        |

| 17  | 0x4010_0000 | 0x4FFF_FFFF | 255MB | Expansion 1        | Maps to AHB5 Master<br>Expansion 1 Interface    | 24             |            |            |        |

| 18  | 0x5000_0000 | 0x5000_FFFF | 64KB  | Base<br>Peripheral | Base Element Peripheral<br>Region.              | 11             | _          |            |        |

| 19  | 0x5001_0000 | 0x5001_FFFF | 64KB  | Private CPU        | CPU Element Peripheral<br>Region.               | 12             | _          |            |        |

| 20  | 0x5002_0000 | 0x5002_FFFF | 64KB  | System<br>Control  | System Control Element<br>Peripheral region.    | 13             | _S         | 5          | 0      |

| 21  | 0x5003_0000 | 0x5003_FFFF |       | Reserved           | Reserved                                        |                |            |            |        |

| 22  | 0x5004_0000 | 0x5007_FFFF |       | Reserved           | Reserved                                        |                | _          |            |        |

| 23  | 0x5008_0000 | 0x500F_FFFF | 512KB | Base<br>Peripheral | Base Element Peripheral<br>Region.              | 16             |            |            |        |

| ROW | Address     | lress       |       | c. Region D. I. I |                                              | Alias          | IDAU Region Values |        |     |   |

|-----|-------------|-------------|-------|-------------------|----------------------------------------------|----------------|--------------------|--------|-----|---|

| ID  | From        | То          | Size  | Name              | Description                                  | With<br>Row ID | Security           | IDAUID | NSC |   |

| 24  | 0x5010_0000 | 0x5FFF_FFFF | 255MB | Expansion 1       | Maps to AHB5 Master<br>Expansion 1 Interface | 17             |                    |        |     |   |

| 25  | 0x6000_0000 | 0x6FFF_FFFF | 256MB | Expansion 0       | Maps to AHB5 Master<br>Expansion 0 Interface | 26             | NS                 | 6      | 0   |   |

| 26  | 0x7000_0000 | 0x7FFF_FFFF | 256MB | Expansion 0       | Maps to AHB5 Master<br>Expansion 0 Interface | 25             | S                  | 7      | 0   |   |

| 27  | 0x8000_0000 | 0x8FFF_FFFF | 256MB | Expansion 1       | Maps to AHB5 Master<br>Expansion 1 Interface | 28             | NS                 | 8      | 0   |   |

| 28  | 0x9000_0000 | 0x9FFF_FFFF | 256MB | Expansion 1       | Maps to AHB5 Master<br>Expansion 1 Interface | 27             | S                  | 9      | 0   |   |

| 29  | 0xA000_0000 | 0xAFFF_FFFF | 256MB | Expansion 1       | Maps to AHB5 Master<br>Expansion 1 Interface | 30             | NS                 | А      | 0   |   |

| 30  | 0xB000_0000 | 0xBFFF_FFFF | 256MB | Expansion 1       | Maps to AHB5 Master<br>Expansion 1 Interface | 29             | S                  | В      | 0   |   |

| 31  | 0xC000_0000 | 0xCFFF_FFFF | 256MB | Expansion 1       | Maps to AHB5 Master<br>Expansion 1 Interface | 32             | NS                 | С      | 0   |   |

| 32  | 0xD000_0000 | 0xDFFF_FFFF | 256MB | Expansion 1       | Maps to AHB5 Master<br>Expansion 1 Interface | 31             | S                  | D      | 0   |   |

|     |             |             |       |                   |                                              |                |                    |        |     |   |

| 34  | 0xE010_0000 | 0xEFFF_FFFF | 255MB | Expansion 1       | Maps to AHB5 Master<br>Expansion 1 Interface | 36             | NS                 | E      |     | 0 |

| 35  | 0xF000_0000 | 0xF00F_FFFF | 1MB   | System<br>Debug   | System Debug.                                | 33             | Exempt             |        |     |   |

| 36  | 0xF010_0000 | 0xFFFF_FFFF | 255MB | Expansion 1       | Maps to AHB5 Master<br>Expansion 1 Interface | 34             | S                  | F      |     | 0 |

Table 1: Memory map overview

#### 3.4.1 Synchronous SRAM for code (SRAM1)

4MB of SRAM memory is available in the code region of the memory map. The memory is named SRAM1 and is mapped both to the non-secure and Secure code memory region as shown in Table 2. To provide security gating, an MPC is place before this memory. It is called SSRAM1MPC, its configuration interface is located at 0x5800\_7000 and its interrupt signal is connected to S\_MPCEXP\_STATUS[0]. All unused regions in the code memory space return bus error responses when accessed.

| ROW | Address     |             | 0:    | Region   | Region                                      |        | IDAU Region Values |        |      |

|-----|-------------|-------------|-------|----------|---------------------------------------------|--------|--------------------|--------|------|

| ID  | From        | То          | Size  | Name     | Description                                 | Row ID | Security           | IDAUID | NSC  |

| 1   | 0x0000_0000 | 0x003F_FFFF | 4MB   |          | SRAM (SRAM1)                                | 5      |                    |        |      |

| 2   | 0x0040_0000 | 0x007F_FFFF | 4MB   | Code     | SRAM1 alias                                 | 6      | NS                 | 0      |      |

| 3   | 0x0080_0000 | 0x0DFF_FFFF | 116MB | - Memory | Not used. Returns Bus Errors when accessed. | -      |                    |        | 0    |

| 4   | 0x0E00_0000 | 0x0FFF_FFFF | 32MB  | Reserved | Reserved                                    | -      |                    |        |      |

|     |             |             |       |          |                                             |        |                    |        |      |

| 5   | 0x1000_0000 | 0x103F_FFFF | 4MB   | _        | SRAM (SRAM1)                                | 1      | _                  |        |      |

| 6   | 0x1040_0000 | 0x107F_FFFF | 4MB   | Code     | SRAM1 alias                                 | 2      |                    |        | CODE |

| 7   | 0x1080_0000 | 0x1DFF_FFFF | 116MB | - Memory | Not used. Returns Bus Errors when accessed. | -      | S                  | 1      | NSC  |

| 8   | 0x1E00_0000 | 0x1FFF_FFFF | 32MB  | Reserved | Reserved                                    | -      |                    |        |      |

### Table 2: SRAM1 mapping to code memory

Because 4MB of memory exists in an 8MB window, the top 4MB of that window is aliased with the lower 4MB. As a result, both will share the same security setting. This ensures that there are no security holes that allow Secure and Non-secure access to the same physical location on the SRAM at the same time.

The SSRAM1MPC is configured as follows:

| DATA_WIDTH   | 32bits | Data Width: 32bits                                                                              |

|--------------|--------|-------------------------------------------------------------------------------------------------|

| ADDR_WIDTH   | 22     | Address Width. Set at 22bits to support 4 Mbyte of memory space.                                |

| MASTER_WIDTH | 5      | HMASTER signal width. 5 bit for 32 masters                                                      |

| USER_WIDTH   | 0      | User signal width parameter, default: 1, ports tied if 0                                        |

| BLK_SIZE     | 8      | Block size: (1 << BLK_SIZE) bytes, min. value: 5, max. value: 20. Set at 8 for 256 byte blocks. |

|              |        | Response on data AHB when accessed during programming lock:                                     |

| GATE_RESP    | 0      | 0 – Add wait states until lock is released (default)                                            |

|              |        | 1 – Drive bus error                                                                             |

#### Table 3: SSRAM1MPC configuration settings

#### 3.4.2 Synchronous SRAM (SRAM2 and SRAM3)

4MB of SRAM memory is available in the expansion 0 region of the memory map. The memory is formed by the combination of memories SRAM2 and SRAM3. All unused regions shown in the table return bus error responses when accessed.

| ROW | Address     |             |        | Pagian             |                                                | Alias<br>With | IDAU Region Values |        |     |  |

|-----|-------------|-------------|--------|--------------------|------------------------------------------------|---------------|--------------------|--------|-----|--|

| ID  | From        | То          | Size   | Region<br>Name     | Description                                    | Row<br>ID     | Security           | IDAUID | NSC |  |

| 1   | 0x2000_0000 | 0x2007_FFFF | 32KB   | SRAM               | FPGA Block Ram                                 | 6             |                    |        |     |  |

| 2   | 0x2080_0000 | 0x27FF_FFFF | ~128MB | Reserved           | Reserved                                       |               | _                  |        |     |  |

| 3   | 0x2800_0000 | 0x281F_FFFF | 2MB    |                    | SRAM (SRAM2)                                   | 8             | –<br>– NS          | 2      | 0   |  |

| 4   | 0x2820_0000 | 0x283F_FFFF | 2MB    | –<br>– Expansion 0 | SRAM (SRAM3)                                   | 9             | - 115              | 2      | 0   |  |

| 5   | 0x2840_0000 | 0x2FFF_FFFF | 124MB  |                    | Not used. Returns Bus<br>Errors when accessed. |               | _                  |        |     |  |

| 6   | 0x3000_0000 | 0x3007_FFFF | 32KB   | SRAM               | FPGA Block Ram                                 | 1             |                    |        |     |  |

| 7   | 0x3080_0000 | 0x37FF_FFFF | ~128MB | Reserved           | Reserved                                       |               | _                  |        |     |  |

| 8   | 0x3800_0000 | 0x381F_FFFF | 2MB    |                    | SRAM (SRAM2)                                   | 3             | _                  | 2      | RAM |  |

| 9   | 0x3820_0000 | 0x383F_FFFF | 2MB    | _ Expansion 0      | SRAM (SRAM3)                                   | 4             | – S                | 3      | NSC |  |

| 10  | 0x3840_0000 | 0x3FFF_FFFF | 124MB  |                    | Maps to AHB5 Master<br>Expansion 0 Interface   |               | _                  |        |     |  |

#### Table 4: SRAM2 and SRAM3 address mapping

An Exclusive Access Monitor and a Memory Protection Controller exist on the path of each SRAM. They support exclusive access and security gating, so that blocks of aliased memory can be assigned individually to Secure or Non-secure regions. The two MPCs are as follows:

- SSRAM2MPC is the MPC for SSRAM2. Its APB interface is mapped to address 0x5800\_8000 and its interrupt signal is connected to S\_MPCEXP\_STATUS[1].

- SSRAM3MPC is the MPC for SSRAM3. Its APB interface is mapped to address 0x5800\_9000 and its interrupt signal is connected to S\_MPCEXP\_STATUS[2].

Both SSRAM1MPC and SSRAM2MPC have the same configuration settings as listed in Table 5.

| Parameter     | Configuration | Description                                                                                                                                |  |  |  |

|---------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| DATA_WIDTH    | 32bits        | Data Width: 32bits                                                                                                                         |  |  |  |

| ADDR_WIDTH 22 |               | Address Width. Set at 22bits to support 4 Mbyte of memory space.                                                                           |  |  |  |

| MASTER_WIDTH  | 5             | HMASTER signal width. 5 bit for 32 masters                                                                                                 |  |  |  |

| USER_WIDTH    | 0             | User signal width parameter, default: 1, ports tied if 0                                                                                   |  |  |  |

| BLK_SIZE 8    |               | Block size: (1 << BLK_SIZE) bytes, min. value: 5, max. value: 20. Set at 8 for 256 byte blocks.                                            |  |  |  |

| GATE_RESP     | 0             | Response on data AHB when accessed during programming lock:<br>0 – Add wait states until lock is released (default)<br>1 – Drive bus error |  |  |  |

### Table 5: SSRAM2MPC and SSRAM3MPC configuration settings

### 3.4.3 Synchronous SRAM (SRAM4)

The memory map includes 16MB of SRAM memory in the expansion 1 region. All unused regions shown in the table return bus error responses when accessed. These memories are currently mapped only to Non-secure SRAM space as follows:

| ROW | Address     |             | Regi  | Region                                                                           | n                                              | Alias          | IDAU Region Values |        |     |

|-----|-------------|-------------|-------|----------------------------------------------------------------------------------|------------------------------------------------|----------------|--------------------|--------|-----|

| ID  | From        | То          | Size  | Name                                                                             | Description                                    | With<br>Row ID | Security           | IDAUID | NSC |

| 1   | 0x8000_0000 | 0x80FF_FFFF | 16MB  | AHB                                                                              | SRAM4                                          |                |                    |        |     |

| 2   | 0x8100_0001 | 0x8FFF_FFFF | 246MB | <ul> <li>Master</li> <li>Expansion</li> <li>1 Interface</li> <li>Area</li> </ul> | Not used. Returns Bus<br>Errors when accessed. |                | -<br>NS            | 8      | 0   |

# Table 6: SRAM4

### 3.4.4 Expansion system peripherals

Other than the SRAMs, all FPGA peripherals that are extensions to the IoT lot are mapped into two key areas of the memory map:

- 0x4010\_0000 to 0x4FFF\_FFFF Non-secure region, which maps to AHB Master Expansion 1 interface.

- 0x5010\_0000 to 0x5FFF\_FFFF Secure region, which maps to AHB Master Expansion 1 interface.

Table 7 shows how these peripherals are mapped.

To support TrustZone-Armv8M, and allow software to map these peripherals to Secure or Nonsecure address space, many peripherals are mapped twice, and either APB PPC or AHB PPC is then used to gate access to these peripherals. An FPGA Secure Privilege Control block and a Nonsecure Privilege Control block then provide controls to these PPC.

For expansion AHB Masters within the system, a Master Security Controller (MSC) is added to each master with an associated IDAU. Masters that have IDAU are:

• PL081 DMA Engine. All DMAs can be mapped as Secure or Non-secure Masters. The intention is to support the use case in which, for each pair of DMAs that shared a single AHB expansion interface, one is mapped as Secure and another is mapped as non-Secure.

| ROW                                                                                | Address                    |                            | Size      | Description                                             | Alias<br>With | IDAU Reg<br>Values | gion |

|------------------------------------------------------------------------------------|----------------------------|----------------------------|-----------|---------------------------------------------------------|---------------|--------------------|------|

| ID                                                                                 | From                       | То                         |           |                                                         | Row ID        | Security           | ID   |

| 1                                                                                  | 0x4010_0000                | 0x4010_0FFF                | 4K        | GPIO 0                                                  | 24            | _                  |      |

| 2                                                                                  | 0x4010_1000                | 0x4010_1FFF                | 4K        | GPIO 1                                                  | 25            | _                  |      |

| 3                                                                                  | 0x4010_2000                | 0x4010_2FFF                | 4K        | GPIO 2                                                  | 26            | _                  |      |

| 4                                                                                  | 0x4010_3000                | 0x4010_3FFF                | 4K        | GPIO 3                                                  | 27            |                    |      |

| 5                                                                                  | 0x4010_4000                | 0x4010_FFFF                |           | Not used. Returns Bus Errors when accessed.             |               | _                  |      |

| 6                                                                                  | 0x4011_0000                | 0x4011_0FFF                | 4K        | DMA 0                                                   | 29            |                    |      |

| 7                                                                                  | 0x4011_1000                | 0x4011_1FFF                | 4K        | DMA 1                                                   | 30            | _                  |      |

| 8                                                                                  | 0x4011_2000                | 0x4011_2FFF                | 4K        | DMA 2                                                   | 31            |                    |      |

| 9                                                                                  | 0x4011_3000                | 0x4011_3FFF                | 4K        | DMA 3                                                   | 32            | _                  |      |

| 10                                                                                 | 0x4011_4000                | 0x401F_FFFF                |           | Not used. Returns Bus Errors when accessed.             |               | _                  |      |

| 11                                                                                 | 0x4020_0000                | 0x4020_0FFF                | 4K        | UART 0 – Virtual UART                                   | 34            | _                  |      |

| 12                                                                                 | 0x4020_1000                | 0x4020_DFFF                | 52K       | Reserved                                                | 35            | NS                 | 4    |

| 13                                                                                 | 0x4020_E000                | 0x402F_FFFF                |           | Not used. Returns Bus Errors when accessed.             |               | _                  |      |

| 14                                                                                 | 0x4030_0000                | 0x4030_0FFF                | 4K        | FPGA - SCC registers                                    | 37            | _                  |      |

| 15                                                                                 | 0x4030_1000                | 0x4030_1FFF                | 4K        | Reserved                                                | 38            | _                  |      |

| 16                                                                                 | 0x4030_2000                | 0x4030_2FFF                | 4K        | FPGA - IO (System Ctrl + I/O)                           | 39            | _                  |      |

| 17                                                                                 | 0x4030_3000                | 0x40FF_FFFF                |           | Not used. Returns Bus Errors when accessed.             |               | _                  |      |

| 18                                                                                 | 0x4100_0000                | 0x4113_FFFF                | 320K      | Reserved                                                | 40            | _                  |      |

| 19                                                                                 | 0x4114_0000                | 0x41FF_FFFF                |           | Not used. Returns Bus Errors when accessed.             |               | _                  |      |

| 20                                                                                 | 0x4200_0000                | 0x420F_FFFF                | 1M        | Reserved                                                | 42            | _                  |      |

| 21                                                                                 | 0x4210_0000                | 0x4800_6FFF                |           | Not used. Returns Bus Errors when accessed.             |               | _                  |      |

| 22                                                                                 | 0x4800_7000                | 0x4800_7FFF                | 4K        | FPGA Non-Secure Privilege Control                       |               | _                  |      |

| 23                                                                                 | 0x4800_8000                | 0x4FFFF_FFFF               |           | Not used. Returns Bus Errors when accessed.             |               | _                  |      |

|                                                                                    |                            |                            |           |                                                         |               | _                  |      |

| 24                                                                                 | 0x5010_0000                | 0x5010_0FFF                | 4K        | GPIO 0                                                  | 1             |                    |      |

| 25                                                                                 | 0x5010_1000                | 0x5010_1FFF                | 4K        | GPIO 1                                                  | 2             | _                  |      |

| 26                                                                                 | 0x5010_2000                | 0x5010_2FFF                | 4K        | GPIO 2                                                  | 3             | _                  |      |

| 27                                                                                 | 0x5010_3000                | 0x5010_3FFF                | 4K        | GPIO 3                                                  | 4             | _                  |      |

| 28                                                                                 | 0x5010_4000                | 0x5010_FFFF                |           | Not used. Returns Bus Errors when accessed.             |               | _                  |      |

| 29                                                                                 | 0x5011_0000                | 0x5011_0FFF                | 4K        | DMA 0                                                   | 6             | _                  |      |

| 30                                                                                 | 0x5011_1000                | 0x5011_1FFF                | 4K        | DMA 1                                                   | 7             | _                  |      |

| 31                                                                                 | 0x5011_2000                | 0x5011_2FFF                | 4K        | DMA 2                                                   | 8             | _                  |      |

| 32                                                                                 | 0x5011_3000                | 0x5011_3FFF                | 4K        | DMA 3                                                   | 9             | - S                | 5    |

|                                                                                    | 0x5011_4000                | 0x501F_FFFF                |           | Not used. Returns Bus Errors when accessed.             |               | _                  |      |

| 33                                                                                 |                            |                            | 4K        | UART 0 – Virtual UART                                   | 11            | _                  |      |

|                                                                                    | 0x5020_0000                | 013020_0111                |           |                                                         |               | -                  |      |

| 34                                                                                 | 0x5020_0000<br>0x5020_1000 | 0x5020_DFFF                | 52K       | Reserved                                                | 12            |                    |      |

| 34<br>35                                                                           |                            |                            | 52K       | Reserved<br>Not used. Returns Bus Errors when accessed. | 12            | _                  |      |

| 34<br>35<br>36                                                                     | 0x5020_1000                | 0x5020_DFFF                | 52K<br>4K | Not used. Returns Bus Errors when accessed.             | 12            | _                  |      |

| <ul> <li>33</li> <li>34</li> <li>35</li> <li>36</li> <li>37</li> <li>38</li> </ul> | 0x5020_1000<br>0x5020_E000 | 0x5020_DFFF<br>0x502F_FFFF |           |                                                         |               | -                  |      |

| ROW | Address     |             | Size       | Description                                 | Alias<br>With | IDAU Region<br>Values |

|-----|-------------|-------------|------------|---------------------------------------------|---------------|-----------------------|

| ID  | From        | То          |            |                                             | Row ID        | Security ID           |

| 38  | 0x5030_3000 | 0x50FF_FFFF |            | Not used. Returns Bus Errors when accessed. |               | _                     |

| 39  | 0x5100_0000 | 0x5113_FFFF | 320K       | Reserved                                    | 18            | _                     |

| 40  | 0x5114_0000 | 0x51FF_FFFF |            | Not used. Returns Bus Errors when accessed. |               | _                     |

| 41  | 0x5200_0000 | 0x520F_FFFF | 1 <b>M</b> | Reserved                                    | 20            | _                     |

| 42  | 0x5210_0000 | 0x5800_6FFF |            | Not used. Returns Bus Errors when accessed. |               | _                     |

| 43  | 0x5800_7000 | 0x5800_7FFF | 4K         | SSRAM1 Memory Protection Controller (MPC)   |               | _                     |

| 44  | 0x5800_8000 | 0x5800_8FFF | 4K         | SSRAM2 Memory Protection Controller (MPC)   |               |                       |

| 45  | 0x5800_9000 | 0x5800_9FFF | 4K         | SSRAM3 Memory Protection Controller (MPC)   |               |                       |

| 46  | 0x5800_A000 | 0x5FFFF_FFF |            | Not used. Returns Bus Errors when accessed. |               |                       |

Table 7: FPGA expansion peripheral map

# **4** Programmers Model

# 4.1 CMSDK and SIE200 components

This programmer's model is supplemental to the CMSDK IoT kit and Armv8-M IoT kit documentation, which covers many of the included components in more detail. Figure 3-1 System overview shows the connectivity of the system.

# 4.2 SRAMs

#### 4.2.1 SRAM1

SRAM1 is in the CODE region. It forms a 64-bit SRAM. Although 8MB of memory space is allocated, only 4MB is used.

#### 4.2.2 SRAM2 & SRAM3

Although 8MB of memory space is allocated, only 4MB is used.

This memory is also accessible at 0x38000000.

Note: SRAM2 and SRAM3 are in the SRAM region. Running code from SRAM region is slower than from CODE region, because the internal bus structure is not optimized for running programs from this region.

#### 4.2.3 SRAM4

A 16MB SRAM4 area is available, and the memory map allocates the address-range 0x80000000 - 0x80FFFFFF. This enables large test programs, for example uClinux, to be used in the External RAM region of the Cortex-M memory space.

Note: SRAM4 is in the SRAM region. Running code from SRAM region is slower than from CODE region because the internal bus structure is not optimized for running programs from this region.

# 4.3 UART

The SMM implements one CMSDK UARTs:

• UART 0 – Virtual UART

# 4.4 FPGA system control and I/O

The SMM implements an FPGA system control block.

| Address    | Name             | Information                                                                                       |

|------------|------------------|---------------------------------------------------------------------------------------------------|

| 0x40028000 | FPGAIO->LED0     | LED connections                                                                                   |

| 0x50028000 |                  | [31:2] : Reserved                                                                                 |

|            |                  | [1:0] : vLED[1:0]                                                                                 |

| 0x40028004 | RESERVED         |                                                                                                   |

| 0x50028004 |                  |                                                                                                   |

| 0x40028008 | FPGAIO->BUTTON   | Buttons                                                                                           |

| 0x50028008 |                  | [31:2] : Reserved                                                                                 |

|            |                  | [1:0] : Buttons (vDIP[1:0])                                                                       |

| 0x4002800C | RESERVED         |                                                                                                   |

| 0x5002800C |                  |                                                                                                   |

| 0x40028010 | FPGAIO->CLK1HZ   | 1Hz up counter                                                                                    |

| 0x50028010 |                  |                                                                                                   |

| 0x40028014 | FPGAIO->CLK100HZ | 100Hz up counter                                                                                  |

| 0x50028014 |                  |                                                                                                   |

| 0x40028018 | FPGAIO->COUNTER  | Cycle Up Counter                                                                                  |

| 0x50028018 |                  | Increments when 32-bit prescale counter reach zero.                                               |

| 0x4002801C | FPGAIO->PRESCALE | Bit[31:0] – reload value for prescale counter.                                                    |

| 0x5002801C |                  |                                                                                                   |

| 0x40028020 | FPGAIO->PSCNTR   | 32-bit Prescale counter – current value of the pre-scaler                                         |

| 0x50028020 |                  | counter. The Cycle Up Counter increment when the                                                  |

|            |                  | prescale down counter reach 0. The pre-scaler counter is reloaded with PRESCALE after reaching 0. |

| 0x40028024 | RESERVED         |                                                                                                   |

| 0x40028024 |                  |                                                                                                   |

| 0x4002804C | FPGAIO->MISC     | Misc control                                                                                      |

| 0x5002804C |                  | [31:0] : Reserved                                                                                 |

### Table 8: System control and I/O memory map

# 4.5 Serial Communication Controller

The SMM implements communication between the host and the FPGA system through a *Serial Communication Controller* (SCC) interface. The interface is mapped to BAR0 (TODO ref).

| Address     | Name            | Information                                                    |

|-------------|-----------------|----------------------------------------------------------------|

| 0x000       | CFG_REG0        | Bits[31:0] Reserved                                            |

| 0x004       | CFG_REG1        | Bits [31:0] Reserved                                           |

| 0x008       | CFG_REG2        | Reserved                                                       |

| 0x00C       | CFG_REG3        | Bits [31:0] Reserved                                           |

| 0x010       | CFG_REG4        | Bits [31:0] Reserved                                           |

| 0x014       | RESERVED        | -                                                              |

| 0x018       | RESERVED        | -                                                              |

| 0x01C       | RESERVED        | -                                                              |

| 0x020-0x09C | RESERVED        | -                                                              |

| 0x0A0       | SYS_CFGDATA_RTN | 32bit DATA [r/w]                                               |

| 0x0A4       | SYS_CFGDATA_OUT | 32bit DATA [r/w]                                               |

| 0x0A8       | SYS_CFGCTRL     | Bit[31] : Start (generates interrupt on write to this bit)     |

|             |                 | Bit[30] : R/W access                                           |

|             |                 | Bits[29:26] : Reserved                                         |

|             |                 | Bits[25:20] : Function value                                   |

|             |                 | Bits[19:12] : Reserved                                         |

|             |                 | Bits[11:0] : Device (value of 0/1/2 for supported clocks)      |

| 0x0AC       | SYS_CFGSTAT     | Bit 0 : Complete                                               |

|             |                 | Bit 1 : Error                                                  |

| 0x0AD-0x0FC | RESERVED        | -                                                              |

| 0x100       | RESERVED        | -                                                              |

| 0x104-0xFF4 | RESERVED        | -                                                              |

| 0xFF8       | SCC_AID         | SCC AID register is read only                                  |

|             |                 | Bits[31:8] :Reserved                                           |

|             |                 | Bits[7:0] number of SCC configuration register                 |

| 0xFFC       | SCC_ID          | SCC ID register is read only                                   |

|             |                 | Bits[31:24] : Implementer ID: 0x41 = Arm                       |

|             |                 | Bits[23:20] : Reserved                                         |

|             |                 | Bits[19:16] : IP Architecture: 0x4 =AHB                        |

|             |                 | Bits[15:4] : Primary part number: 505 = <todo an???=""></todo> |

|             |                 | Bits[3:0] : Reserved                                           |

The read addresses and write addresses of the SCC interface do not use bits[1:0]. All address words are word-aligned.

# Table 9: SCC register memory map

# **5 Clock and reset architecture**

The following tables list clocks entering and generated by the SMM.

# 5.1 Clocks

# 5.1.1 Source clocks

The following clocks are inputs to the system.

| Clock | Input Pin | Frequency | Note |  |

|-------|-----------|-----------|------|--|

| OSC0  | OSCCLK[0] | 250MHz    |      |  |

Table 10: Source clocks

# 5.1.2 Internal clocks

The following clocks are generated internally from the source clocks.

| Clock     | Source | Frequency | Note |

|-----------|--------|-----------|------|

| MAINCLK   | OSC0   | 50MHz     |      |

| S32KCLK   | OSC0   | 32kHz     |      |

| clk_100hz | OSC0   | 100Hz     |      |

Table 11: Generated internal clocks

# 5.1.3 Clocks connecting to the IoT kit

The following clocks connect to the IoT kit. Both clocks are provided to the IoT kit and clocks generated by the kit

| MAINCLKOSC050MHzSYSCLKOutput50MHzS32KCLKS32KCLK32kHz |                                |

|------------------------------------------------------|--------------------------------|

|                                                      | Main Clock Input               |

| S32KCLK S32KCLK 32kHz                                | Main System Clock              |

|                                                      | Asynchronous 32KHz clock input |

| TRACECLK Output 50MHz                                | TPIU trace port clock          |

| SWCLKTCK OSCO 50MHz                                  | SW/JTAG DP clock               |

| TRACECLKIN OSCO 50MHz                                | TPIU trace port clock input    |

#### Table 12: IoT kit clocks

# 5.2 Resets

### 5.2.1 Source resets

The following resets are inputs to the system.

| Reset      | Input Pin  | Note                                            |

|------------|------------|-------------------------------------------------|

| CB_NPOR    | vDIP[0]    | Controls the SW preload interfaces and memories |

| CB_NRST    | vDIP[1]    | Controls the rest of the system                 |

| rst_main_n | rst_main_n | Master reset from AWS framework                 |

Table 13: Source resets

# 6 FPGA secure privilege control

The IoT kit subsystem's Secure Privilege Control Block and Non-secure Privilege Block are able to provides expansion security control signals to control the various security gating units within the subsystem. The following table lists the connectivity of the system security extension signal. More details are available in *Armv8-M IoT Kit User Guide* (Arm-ECM-0601256).

| Component name | Components signals | Security expansion signals |

|----------------|--------------------|----------------------------|

|                | msc_irq            | S_MSCEXP_STATUS[0]         |

| OMA 0 MSC      | msc_irq_clear      | S_MSCEXP_CLEAR[0]          |

|                | cfg_nonsec         | NS_MSCEXP[0]               |

|                | msc_irq            | S_MSCEXP_STATUS[1]         |

| DMA 1 MSC      | msc_irq_clear      | S_MSCEXP_CLEAR[1]          |

|                | cfg_nonsec         | NS_MSCEXP[1]               |

|                | msc_irq            | S_MSCEXP_STATUS[2]         |

| OMA 2 MSC      | msc_irq_clear      | S_MSCEXP_CLEAR[2]          |

|                | cfg_nonsec         | NS_MSCEXP[2]               |

|                | msc_irq            | S_MSCEXP_STATUS[3]         |

| OMA 3 MSC      | msc_irq_clear      | S_MSCEXP_CLEAR[3]          |

|                | cfg_nonsec         | NS_MSCEXP[3]               |

|                | apb_ppc_irq        | S_APBPPCEXP_STATUS[0]      |

|                | apb_ppc_clear      | S_APBPPCEXP_CLEAR[0]       |

| APB PPC EXP 0  | cfg_sec_resp       | SEC_RESP_CFG               |

|                | cfg_non_sec        | APB_NS_PPCEXP0[15:0]       |

|                | cfg_ap             | APB_P_PPCEXP0[15:0]        |

|                | apb_ppc_irq        | S_APBPPCEXP_STATUS[1]      |

|                | apb_ppc_clear      | S_APBPPCEXP_CLEAR[1]       |

| APB PPC EXP 1  | cfg_sec_resp       | SEC_RESP_CFG               |

|                | cfg_non_sec        | APB_NS_PPCEXP1[15:0]       |

|                | cfg_ap             | APB_P_PPCEXP1[15:0]        |

|                | apb_ppc_irq        | S_APBPPCEXP_STATUS[2]      |

|                | apb_ppc_clear      | S_APBPPCEXP_CLEAR[2]       |

| APB PPC EXP 2  | cfg_sec_resp       | SEC_RESP_CFG               |

|                | cfg_non_sec        | APB_NS_PPCEXP2[15:0]       |

|                | cfg_ap             | APB_P_PPCEXP2[15:0]        |

|                | ahb_ppc_irq        | S_AHBPPCEXP_STATUS[0]      |

|                | ahb_ppc_clear      | S_AHBPPCEXP_CLEAR[0]       |

| AHB PPC EXP 0  | cfg_sec_resp       | SEC_RESP_CFG               |

|                | cfg_non_sec        | AHB_NS_PPCEXP0[15:0]       |

|                | chg_ap             | AHB_P_PPCEXP0[15:0]        |

| AHB PPC EXP 1  | ahb_ppc_irq        | S_AHBPPCEXP_STATUS[1]      |

| Component name | Components signals | Security expansion signals |

|----------------|--------------------|----------------------------|

|                | ahb_ppc_clear      | S_AHBPPCEXP_CLEAR[1]       |

|                | cfg_sec_resp       | SEC_RESP_CFG               |

|                | cfg_non_sec        | AHB_NS_PPCEXP1[15:0]       |

|                | chg_ap             | AHB_P_PPCEXP1[15:0]        |

| MPC SSRAM0     | secure_error_irq   | S_MPCEXP_STATUS[0]         |

| MPC SSRAM1     | secure_error_irq   | S_MPCEXP_STATUS[1]         |

| MPC SSRAM2     | secure_error_irq   | S_MPCEXP_STATUS[2]         |

### Table 14: Security expansion signals connectivity

The following table lists the peripherals that are controlled by APB PPC EXP 0. Each APB <n> interface is controlled by APB\_NS\_PPCEXP0[n] and APB\_P\_PPCEXP0[n].

| APB PPC EXP 0 Interface Number <n></n> | Name                                      |

|----------------------------------------|-------------------------------------------|

| 0                                      | SSRAM1 Memory Protection Controller (MPC) |

| 1                                      | SSRAM2 Memory Protection Controller (MPC) |

| 2                                      | SSRAM3 Memory Protection Controller (MPC) |

| 15:3                                   | Reserved                                  |

### Table 15: Peripherals mapping of APB PPC EXP 0

The following table lists the peripherals that are controlled by APB PPC EXP 1. Each APB <n> interface is controlled by APB\_NS\_PPCEXP1[n] and APB\_P\_PPCEXP1[n].

| APB PPC EXP 1 Interface Number <n></n> | Name     |

|----------------------------------------|----------|

| 0                                      | Reserved |

| 1                                      | Reserved |

| 2                                      | Reserved |

| 3                                      | Reserved |

| 4                                      | Reserved |

| 5                                      | UART_0   |

| 6                                      | Reserved |

| 7                                      | Reserved |

| 8                                      | Reserved |

| 9                                      | Reserved |

| 10                                     | Reserved |

| 11                                     | Reserved |

| 12                                     | Reserved |

| 13                                     | Reserved |

| 15:14                                  | Reserved |

## Table 16: Peripherals mapping of APB PPC EXP 1

| APB PPC EXP 0 Interface Number <n></n> | Name     |

|----------------------------------------|----------|

| 0                                      | SCC      |

| 1                                      | Reserved |

| 2                                      | FPGAIO   |

| 15:3                                   | Reserved |

The following table lists the peripherals that are controlled by APB PPC EXP 2. Each APB <n> interface is controlled by APB\_NS\_PPCEXP2[n] and APB\_P\_PPCEXP2[n].

#### Table 17: Peripherals mapping of APB PPC EXP 2

The following table lists the peripherals that are controlled by AHB PPC EXP 0 . each APB <n> interface is controlled by AHB\_NS\_PPCEXP0[n] and AHB\_P\_PPCEXP0[n].

| Name     |

|----------|

| Reserved |

|          |

### Table 18: Peripherals mapping of AHB PPC EXP 0

The following table lists the peripherals that are controlled by AHB PPC EXP 1. Each APB  $\langle n \rangle$  interface is controlled by AHB\_NS\_PPCEXP1[n] and AHB\_P\_PPCEXP0[n].

| AHB PPC EXP 0 Interface Number <n></n> | Name     |

|----------------------------------------|----------|

| 0                                      | DMA_0    |

| 1                                      | DMA_1    |

| 2                                      | DMA_2    |

| 3                                      | DMA_3    |

| 15:4                                   | Reserved |

#### Table 19: Peripherals mapping of AHB PPC EXP1

The following table lists the *Master Security Controllers* (MSCs) that are controlled by NS\_MSCEXP signals. These control signals are used to map each peripheral connected to their associated MSCs as Secure or Non-secure Masters.

| NS_MSCEXP bits | Name                    |

|----------------|-------------------------|

| 0              | MSC cfg_nonsec for DMA0 |

| 1              | MSC cfg_nonsec for DMA1 |

| 2              | MSC cfg_nonsec for DMA2 |

| 3              | MSC cfg_nonsec for DMA3 |

| 15:4           | Reserved                |

#### Table 20: Peripherals mapping of AHB PPC EXP1

# 7 Interrupt map

The interrupts in the FPGA subsystem extend the *Armv8-M IoT Kit* interrupt map by adding to the expansion area as follows:

| NMICombined Secure Watchdog, S32K Watchdog and NMI_ExpansionIRQ[0]Non-Secure Watchdog Reset RequestIRQ[1]Non-Secure Watchdog InterruptIRQ[2]S32K TimerIRQ[3]Timer 0IRQ[4]Timer 1IRQ[5]Dual TimerIRQ[6]ReservedIRQ[9]MPC Combined (Secure)IRQ[10]PPC Combined (Secure)IRQ[11]MSC Combined (Secure)IRQ[12]Bridge Error Combined Interrupt (Secure)IRQ[33]UART 0 Receive InterruptIRQ[34]ReservedIRQ[35]ReservedIRQ[36]ReservedIRQ[37]ReservedIRQ[38]ReservedIRQ[39]ReservedIRQ[40]ReservedIRQ[41]ReservedIRQ[42]UART 0 Combined InterruptIRQ[43]ReservedIRQ[44]ReservedIRQ[45]ReservedIRQ[46]ReservedIRQ[47]UART 0 Combined InterruptIRQ[48]ReservedIRQ[44]ReservedIRQ[45]ReservedIRQ[46]ReservedIRQ[47]UART 0 OverflowIRQ[48]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[51]ReservedIRQ[52]ReservedIRQ[54]ReservedIRQ[54]Reserved                                                                          | Interrupt Input | Interrupt Source                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------------------------|

| IRQ[1]Non-Secure Watchdog InterruptIRQ[2]S32K TimerIRQ[3]Timer 0IRQ[4]Timer 1IRQ[5]Dual TimerIRQ[6]ReservedIRQ[9]MPC Combined (Secure)IRQ[10]PPC Combined (Secure)IRQ[11]MSC Combined (Secure)IRQ[12]Bridge Error Combined Interrupt (Secure)IRQ[32]UART 0 Receive InterruptIRQ[33]UART 0 Transmit InterruptIRQ[34]ReservedIRQ[35]ReservedIRQ[37]ReservedIRQ[38]ReservedIRQ[39]ReservedIRQ[40]ReservedIRQ[41]ReservedIRQ[42]UART 0 Combined InterruptIRQ[43]ReservedIRQ[44]ReservedIRQ[45]ReservedIRQ[44]ReservedIRQ[45]ReservedIRQ[44]ReservedIRQ[45]ReservedIRQ[46]ReservedIRQ[47]UART 0 OverflowIRQ[48]ReservedIRQ[44]ReservedIRQ[45]ReservedIRQ[46]ReservedIRQ[47]UART0 OverflowIRQ[48]ReservedIRQ[49]ReservedIRQ[44]ReservedIRQ[45]ReservedIRQ[46]ReservedIRQ[47]UART0 OverflowIRQ[48]ReservedIRQ[49]ReservedIRQ[44]ReservedIRQ[45]ReservedIRQ[46]Reserved </td <td>NMI</td> <td>Combined Secure Watchdog, S32K Watchdog and NMI_Expansion</td> | NMI             | Combined Secure Watchdog, S32K Watchdog and NMI_Expansion |

| IRQ[2]S32K TimerIRQ[3]Timer 0IRQ[4]Timer 1IRQ[5]Dual TimerIRQ[5]ReservedIRQ[9]MPC Combined (Secure)IRQ[10]PPC Combined (Secure)IRQ[11]MSC Combined (Secure)IRQ[12]Bridge Error Combined Interrupt (Secure)IRQ[31]ReservedIRQ[32]UART 0 Receive InterruptIRQ[33]UART 0 Transmit InterruptIRQ[34]ReservedIRQ[35]ReservedIRQ[36]ReservedIRQ[37]ReservedIRQ[38]ReservedIRQ[39]ReservedIRQ[40]ReservedIRQ[41]ReservedIRQ[42]UART 0 Combined InterruptIRQ[43]ReservedIRQ[44]ReservedIRQ[45]ReservedIRQ[46]ReservedIRQ[47]UART 0 Combined InterruptIRQ[48]ReservedIRQ[49]ReservedIRQ[44]ReservedIRQ[45]ReservedIRQ[46]ReservedIRQ[47]UART0 OverflowIRQ[48]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[41]ReservedIRQ[42]ReservedIRQ[43]ReservedIRQ[44]ReservedIRQ[45]ReservedIRQ[46]ReservedIRQ[47]UART0 OverflowIRQ[48]ReservedIRQ[51]Reserved <t< td=""><td>IRQ[0]</td><td>Non-Secure Watchdog Reset Request</td></t<>                       | IRQ[0]          | Non-Secure Watchdog Reset Request                         |

| IRQ13Timer 0IRQ14Timer 1IRQ15Dual TimerIRQ161ReservedIRQ191MPC Combined (Secure)IRQ101PPC Combined (Secure)IRQ111MSC Combined (Secure)IRQ112Bridge Error Combined Interrupt (Secure)IRQ131Bridge Error Combined Interrupt (Secure)IRQ132UART 0 Receive InterruptIRQ133UART 0 Transmit InterruptIRQ134ReservedIRQ135ReservedIRQ136ReservedIRQ137ReservedIRQ138ReservedIRQ139ReservedIRQ140ReservedIRQ141ReservedIRQ142UART 0 Combined InterruptIRQ143ReservedIRQ144ReservedIRQ145ReservedIRQ146ReservedIRQ147UART0 OverflowIRQ148ReservedIRQ149ReservedIRQ149ReservedIRQ141ReservedIRQ143ReservedIRQ144ReservedIRQ145ReservedIRQ146ReservedIRQ147UART0 OverflowIRQ148ReservedIRQ151ReservedIRQ151ReservedIRQ151ReservedIRQ152ReservedIRQ153ReservedIRQ153Reserved                                                                                                                                                                                     | IRQ[1]          | Non-Secure Watchdog Interrupt                             |

| IRQ[4]Timer 1IRQ[5]Dual TimerIRQ[9]MPC Combined (Secure)IRQ[10]PPC Combined (Secure)IRQ[11]MSC Combined (Secure)IRQ[12]Bridge Error Combined Interrupt (Secure)IRQ[31:13]ReservedIRQ[32]UART 0 Receive InterruptIRQ[33]UART 0 Transmit InterruptIRQ[34]ReservedIRQ[35]ReservedIRQ[36]ReservedIRQ[37]ReservedIRQ[38]ReservedIRQ[40]ReservedIRQ[41]ReservedIRQ[42]UART 0 Combined InterruptIRQ[43]ReservedIRQ[44]ReservedIRQ[45]ReservedIRQ[46]ReservedIRQ[47]UART0 Ormbined InterruptIRQ[46]ReservedIRQ[47]UART0 Ormbined InterruptIRQ[48]ReservedIRQ[49]ReservedIRQ[44]ReservedIRQ[45]ReservedIRQ[46]ReservedIRQ[47]UART0 OverflowIRQ[48]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[50]ReservedIRQ[51]ReservedIRQ[52]ReservedIRQ[53]Reserved                                                                                                                                                                                                          | IRQ[2]          | S32K Timer                                                |

| IRQ[5]Dual TimerIRQ[5]Dual TimerIRQ[9]MPC Combined (Secure)IRQ[10]PPC Combined (Secure)IRQ[11]MSC Combined (Secure)IRQ[12]Bridge Error Combined Interrupt (Secure)IRQ[31:13]ReservedIRQ[32]UART 0 Receive InterruptIRQ[33]UART 0 Transmit InterruptIRQ[34]ReservedIRQ[35]ReservedIRQ[36]ReservedIRQ[37]ReservedIRQ[38]ReservedIRQ[39]ReservedIRQ[40]ReservedIRQ[41]ReservedIRQ[42]UART 0 Combined InterruptIRQ[43]ReservedIRQ[44]ReservedIRQ[45]ReservedIRQ[46]ReservedIRQ[47]UART 0 Combined InterruptIRQ[48]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[51]ReservedIRQ[52]ReservedIRQ[53]ReservedIRQ[53]Reserved                                                                                                                                                                                                                                                                         | IRQ[3]          | Timer 0                                                   |

| IRQReservedIRQ[9]MPC Combined (Secure)IRQ[10]PPC Combined (Secure)IRQ[11]MSC Combined (Secure)IRQ[12]Bridge Error Combined Interrupt (Secure)IRQ[31:13]ReservedIRQ[32]UART 0 Receive InterruptIRQ[33]UART 0 Transmit InterruptIRQ[34]ReservedIRQ[35]ReservedIRQ[36]ReservedIRQ[37]ReservedIRQ[38]ReservedIRQ[39]ReservedIRQ[40]ReservedIRQ[41]ReservedIRQ[42]UART 0 Combined InterruptIRQ[43]ReservedIRQ[44]ReservedIRQ[45]ReservedIRQ[46]ReservedIRQ[47]UART 0 Combined InterruptIRQ[48]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[51]ReservedIRQ[52]ReservedIRQ[53]ReservedIRQ[53]Reserved                                                                                                                                                                                                                                                                                              | IRQ[4]          | Timer 1                                                   |

| IRQ[9]MPC Combined (Secure)IRQ[10]PPC Combined (Secure)IRQ[11]MSC Combined (Secure)IRQ[12]Bridge Error Combined Interrupt (Secure)IRQ[31:13]ReservedIRQ[32]UART 0 Receive InterruptIRQ[33]UART 0 Transmit InterruptIRQ[34]ReservedIRQ[35]ReservedIRQ[36]ReservedIRQ[37]ReservedIRQ[38]ReservedIRQ[39]ReservedIRQ[40]ReservedIRQ[41]ReservedIRQ[42]UART 0 Combined InterruptIRQ[43]ReservedIRQ[44]ReservedIRQ[45]ReservedIRQ[46]ReservedIRQ[47]UART0 OverflowIRQ[48]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[50]ReservedIRQ[51]ReservedIRQ[52]ReservedIRQ[53]ReservedIRQ[53]Reserved                                                                                                                                                                                                                                                                                                                                                  | IRQ[5]          | Dual Timer                                                |

| IRQ[10]PPC Combined (Secure)IRQ[11]MSC Combined (Secure)IRQ[12]Bridge Error Combined Interrupt (Secure)IRQ[31:13]ReservedIRQ[32]UART 0 Receive InterruptIRQ[33]UART 0 Transmit InterruptIRQ[34]ReservedIRQ[35]ReservedIRQ[36]ReservedIRQ[37]ReservedIRQ[38]ReservedIRQ[39]ReservedIRQ[40]ReservedIRQ[41]ReservedIRQ[42]UART 0 Combined InterruptIRQ[43]ReservedIRQ[44]ReservedIRQ[45]ReservedIRQ[46]ReservedIRQ[47]UART 0 OverflowIRQ[48]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[41]ReservedIRQ[42]ReservedIRQ[43]ReservedIRQ[44]ReservedIRQ[45]ReservedIRQ[46]ReservedIRQ[47]UART0 OverflowIRQ[48]ReservedIRQ[50]ReservedIRQ[51]ReservedIRQ[52]ReservedIRQ[53]ReservedIRQ[53]Reserved                                                                                                                                                                                                                                                             | IRQ[8:6]        | Reserved                                                  |

| IRQ[11]MSC Combined (Secure)IRQ[12]Bridge Error Combined Interrupt (Secure)IRQ[31:13]ReservedIRQ[32]UART 0 Receive InterruptIRQ[33]UART 0 Transmit InterruptIRQ[34]ReservedIRQ[35]ReservedIRQ[36]ReservedIRQ[37]ReservedIRQ[38]ReservedIRQ[39]ReservedIRQ[40]ReservedIRQ[41]ReservedIRQ[42]UART 0 Combined InterruptIRQ[43]ReservedIRQ[44]ReservedIRQ[45]ReservedIRQ[46]ReservedIRQ[47]UART0 OverflowIRQ[48]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[50]ReservedIRQ[51]ReservedIRQ[52]ReservedIRQ[53]ReservedIRQ[53]Reserved                                                                                                                                                                                                                                                                                                                                                                                                                        | IRQ[9]          | MPC Combined (Secure)                                     |

| IRQ[12]Bridge Error Combined Interrupt (Secure)IRQ[31:13]ReservedIRQ[32]UART 0 Receive InterruptIRQ[33]UART 0 Transmit InterruptIRQ[34]ReservedIRQ[35]ReservedIRQ[36]ReservedIRQ[37]ReservedIRQ[38]ReservedIRQ[40]ReservedIRQ[41]ReservedIRQ[42]UART 0 Combined InterruptIRQ[43]ReservedIRQ[44]ReservedIRQ[45]ReservedIRQ[46]ReservedIRQ[47]UART0 OverflowIRQ[48]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[50]ReservedIRQ[51]ReservedIRQ[52]ReservedIRQ[53]Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                     | IRQ[10]         | PPC Combined (Secure)                                     |

| IRQ[31:13]ReservedIRQ[32]UART 0 Receive InterruptIRQ[33]UART 0 Transmit InterruptIRQ[34]ReservedIRQ[35]ReservedIRQ[36]ReservedIRQ[37]ReservedIRQ[38]ReservedIRQ[39]ReservedIRQ[40]ReservedIRQ[41]ReservedIRQ[42]UART 0 Combined InterruptIRQ[43]ReservedIRQ[44]ReservedIRQ[45]ReservedIRQ[46]ReservedIRQ[47]UART0 OverflowIRQ[48]ReservedIRQ[49]ReservedIRQ[49]ReservedIRQ[50]ReservedIRQ[51]ReservedIRQ[52]ReservedIRQ[53]ReservedIRQ[53]Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | IRQ[11]         | MSC Combined (Secure)                                     |