# Cortex<sup>-</sup>-A7 Floating-Point Unit

Revision: r0p3

**Technical Reference Manual**

# Cortex-A7 Floating-Point Unit Technical Reference Manual

Copyright © 2011, 2012 ARM. All rights reserved.

#### **Release Information**

The following changes have been made to this book.

| _                 |       |                  | Change history         |

|-------------------|-------|------------------|------------------------|

| Date              | Issue | Confidentiality  | Change                 |

| 13 September 2011 | А     | Non-Confidential | First release for r0p0 |

| 08 November 2011  | В     | Non-Confidential | First release for r0p1 |

| 11 January 2012   | С     | Non-Confidential | First release for r0p2 |

| 03 May 2012       | D     | Non-Confidential | First release for r0p3 |

#### **Proprietary Notice**

Words and logos marked with \* or  $^{m}$  are registered trademarks or trademarks of ARM\* in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

# Contents Cortex-A7 Floating-Point Unit Technical Reference Manual

|            | Prefa | ace                            |      |

|------------|-------|--------------------------------|------|

|            |       | About this book                | v    |

|            |       | Feedback                       | viii |

| Chapter 1  | Intro | oduction                       |      |

| -          | 1.1   | About the Cortex-A7 FPU        | 1-2  |

|            | 1.2   | Applications Product revisions | 1-3  |

|            | 1.3   | Product revisions              | 1-4  |

| Chapter 2  | Prog  | grammers Model                 |      |

| •          | 2.1   | About the programmers model    |      |

|            | 2.2   | VFP register access            |      |

|            | 2.3   | Register summary               |      |

|            | 2.4   | Register descriptions          |      |

| Appendix A | Revi  | sions                          |      |

# Preface

This preface introduces the *Cortex-A7 Floating-Point Unit Technical Reference Manual*. It contains the following sections:

- About this book on page v

- *Feedback* on page viii.

# About this book

| This book is for the Cortex-A7 Floating-Point Unit (FPU) and describes the external |

|-------------------------------------------------------------------------------------|

| functionality of the FPU.                                                           |

| Product revision statu | IS                                 |                                                                                                                                                                                                                                       |  |

|------------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                        | The rnpn ide                       | entifier indicates the revision status of the product described in this book, where:                                                                                                                                                  |  |

|                        | r <i>n</i>                         | Identifies the major revision of the product.                                                                                                                                                                                         |  |

|                        | р <i>п</i>                         | Identifies the minor revision or modification status of the product.                                                                                                                                                                  |  |

| Intended audience      |                                    |                                                                                                                                                                                                                                       |  |

|                        |                                    | written for system designers, system integrators, and programmers who are <i>System-on-Chip</i> (SoC) device that uses the Cortex-A7 FPU.                                                                                             |  |

| Using this book        |                                    |                                                                                                                                                                                                                                       |  |

|                        | This book is                       | organized into the following chapters:                                                                                                                                                                                                |  |

|                        | Chapter 1 <i>I</i>                 | Introduction                                                                                                                                                                                                                          |  |

|                        |                                    | Read this for a high-level overview of the Cortex-A7 FPU and a description of its features.                                                                                                                                           |  |

|                        | Chapter 2 <i>I</i>                 | Programmers Model                                                                                                                                                                                                                     |  |

|                        |                                    | Read this for a description of the Cortex-A7 FPU system registers.                                                                                                                                                                    |  |

|                        | Appendix A                         | Revisions                                                                                                                                                                                                                             |  |

|                        |                                    | Read this for a description of technical changes in this document.                                                                                                                                                                    |  |

| Glossary               |                                    |                                                                                                                                                                                                                                       |  |

|                        | those terms.                       | <i>lossary</i> is a list of terms used in ARM documentation, together with definitions for<br>The <i>ARM Glossary</i> does not contain terms that are industry standard unless the<br>ng differs from the generally accepted meaning. |  |

|                        | See ARM Gl                         | ossary, http://infocenter.arm.com/help/topic/com.arm.doc.aeg0014-/index.html.                                                                                                                                                         |  |

| Conventions            |                                    |                                                                                                                                                                                                                                       |  |

|                        | Conventions                        | s that this book can use are described in:                                                                                                                                                                                            |  |

|                        |                                    | raphical                                                                                                                                                                                                                              |  |

|                        |                                    | s on page vi.                                                                                                                                                                                                                         |  |

|                        | Typograph                          | ical                                                                                                                                                                                                                                  |  |

|                        | The typographical conventions are: |                                                                                                                                                                                                                                       |  |

|                        | italic                             | Highlights important notes, introduces special terminology, denotes internal cross-references, and citations.                                                                                                                         |  |

|                        | bold                               | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.                                                                                                 |  |

|                        | monospace                          | Denotes text that you can enter at the keyboard, such as commands, file                                                                                                                                                               |  |

and program names, and source code.

|                    | <u>mono</u> space                                                           | Denotes a permitted abbreviation for a command or option. You can enter<br>the underlined text instead of the full command or option name.                                                                       |  |

|--------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                    | monospace italic                                                            | Denotes arguments to monospace text where the argument is to be replaced by a specific value.                                                                                                                    |  |

|                    | monospace bold                                                              | Denotes language keywords when used outside example code.                                                                                                                                                        |  |

|                    | < and >                                                                     | Enclose replaceable terms for assembler syntax where they appear in code or code fragments. For example:<br>MRC p15, 0 <rd>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></rd>                                |  |

|                    | SMALL CAPITALS                                                              | Used in body text for a few terms that have specific technical meanings, that are defined in the <i>ARM glossary</i> . For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE. |  |

|                    | Signals                                                                     |                                                                                                                                                                                                                  |  |

|                    | The signal conventi                                                         | ons are:                                                                                                                                                                                                         |  |

|                    | Signal level                                                                | <ul> <li>The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:</li> <li>HIGH for active-HIGH signals</li> <li>LOW for active-LOW signals.</li> </ul>       |  |

|                    | Lower-case n                                                                | At the start or end of a signal name denotes an active-LOW signal.                                                                                                                                               |  |

|                    |                                                                             |                                                                                                                                                                                                                  |  |

| Additional reading |                                                                             |                                                                                                                                                                                                                  |  |

|                    | This section lists publications by ARM and by third parties.                |                                                                                                                                                                                                                  |  |

|                    | See Infocenter, http://infocenter.arm.com, for access to ARM documentation. |                                                                                                                                                                                                                  |  |

|                    | ARM publications                                                            |                                                                                                                                                                                                                  |  |

|                    | This book contains other relevant inform                                    | information that is specific to this product. See the following documents for mation:                                                                                                                            |  |

|                    | • Cortex-A7 M                                                               | PCore Technical Reference Manual (ARM DDI 0464)                                                                                                                                                                  |  |

|                    | • Cortex-A7 NE<br>(ARM DDI 0                                                | EON Media Processing Engine Technical Reference Manual<br>462)                                                                                                                                                   |  |

|                    | • Cortex-A7 M                                                               | PCore Configuration and Sign-Off Guide (ARM DII 0256)                                                                                                                                                            |  |

|                    | • Cortex-A7 M                                                               | PCore Integration Manual (ARM DIT 0017)                                                                                                                                                                          |  |

|                    | • ARM Archited                                                              | cture Reference Manual, ARMv7-A and ARMv7-R edition (ARM DDI 0406)                                                                                                                                               |  |

|                    | • $CoreSight^{TM} E$                                                        | TM <sup>™</sup> Cortex-A7 Technical Reference Manual (ARM DDI 0468)                                                                                                                                              |  |

|                    | • CoreSight ET                                                              | M Cortex-A7 Configuration and Sign-Off Guide (ARM DII 0261)                                                                                                                                                      |  |

|                    | • CoreSight Em                                                              | bedded Trace Macrocell v3.5 Architecture Specification (ARM IHI 0014)                                                                                                                                            |  |

|                    | • AMBA® AXI I                                                               | Protocol v1.0 Specification (ARM IHI 0022)                                                                                                                                                                       |  |

|                    | • ARM Generic                                                               | Interrupt Controller Architecture Specification (ARM IHI 0048)                                                                                                                                                   |  |

|                    |                                                                             | E User Guide (ARM DUI 0155)                                                                                                                                                                                      |  |

|                    |                                                                             |                                                                                                                                                                                                                  |  |

- CoreSight Architecture Specification (ARM IHI 0029)

- CoreSight Technology System Design Guide (ARM DGI 0012).

# Other publications

This section lists relevant documents published by third parties:

• ANSI/IEEE Std 754-2008, IEEE Standard for Floating-Point Arithmetic.

# Feedback

ARM welcomes feedback on this product and its documentation.

# Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

# Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- the title

- the number, ARM DDI 0463D

- the page numbers to which your comments apply

- a concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

# Chapter 1 Introduction

This chapter introduces the Cortex-A7 FPU. It contains the following sections:

- *About the Cortex-A7 FPU* on page 1-2

- *Applications* on page 1-3

- *Product revisions* on page 1-4.

# 1.1 About the Cortex-A7 FPU

The Cortex-A7 FPU is a VFPv4-D16 implementation of the ARMv7 floating-point architecture. It provides low-cost high performance floating-point computation. The Cortex-A7 FPU supports all addressing modes and operations described in the *ARM Architecture Reference Manual*.

The Cortex-A7 FPU features are:

— Note —

- support for single-precision and double-precision floating-point formats

- support for conversion between half-precision and single-precision

- support for Fused Multiply ACcumulate (FMAC) operations

- normalized and denormalized data are all handled in hardware

- trapless operation enabling fast execution.

The Cortex-A7 FPU hardware supports single and double-precision add, subtract, multiply, divide, multiply and accumulate, fused multiply accumulate, and square root operations as described in the ARM VFPv4 architecture. It provides conversions between 16-bit, 32-bit, and 64-bit floating-point formats and ARM integer word formats, with special operations to perform conversions in round-towards-zero mode for high-level language support.

ARMv7 deprecates the use of VFP vector mode. The Cortex-A7 FPU hardware does not support VFP vector operations. The Cortex-A7 FPU provides high speed VFP operation without support code. However, if an application requires VFP vector operation, then it must use support code. See the *ARM Architecture Reference Manual* for information on VFP vector operation support.

This manual gives information specific to the Cortex-A7 FPU implementation of the ARM VFPv4 extension. See the *ARM Architecture Reference Manual* for full instruction set and usage details.

# 1.2 Applications

The Cortex-A7 FPU provides floating-point computation suitable for a wide spectrum of applications such as:

- personal digital assistants and smartphones for graphics, voice compression and decompression, user interfaces, Java interpretation, and *Just In Time* (JIT) compilation

- games machines for three-dimensional graphics and digital audio

- printers and *MultiFunction Peripheral* (MFP) controllers for high-definition color rendering

- set-top boxes for digital audio and digital video, and three-dimensional user interfaces

- automotive applications for engine management and power train computations.

# 1.3 **Product revisions**

This section describes the differences in functionality between product revisions:

- r0p0-r0p1 Functional changes are:

- ID register value changed to reflect product revision status:

- **FPSID Register** 0x41023071

\_\_\_\_\_Note \_\_\_\_\_

Product revision updated to maintain consistency with the main Cortex-A7 MPCore product.

# r0p1-r0p2 Functional changes are:

• ID register value changed to reflect product revision status:

FPSID Register 0x41023072

—— Note ———

Product revision updated to maintain consistency with the main Cortex-A7 MPCore product.

# r0p2-r0p3 Functional changes are:

• ID register value changed to reflect product revision status:

FPSID Register 0x41023073

—— Note ———

Product revision updated to maintain consistency with the main Cortex-A7 MPCore product.

# Chapter 2 Programmers Model

This chapter describes implementation-specific features of the Cortex-A7 FPU that are useful to programmers. It contains the following sections:

- *About the programmers model* on page 2-2

- *VFP register access* on page 2-4

- *Register summary* on page 2-5

- *Register descriptions* on page 2-6.

# 2.1 About the programmers model

This section introduces the Cortex-A7 FPU implementation of the VFPv4 floating-point architecture, VFPv4-D16, with version 2 of the Common VFP subarchitecture. In this implementation:

- All scalar operations are implemented entirely in hardware, with support for all combinations of rounding modes, flush-to-zero, and default NaN modes.

- Vector operations are not supported. Any attempt to execute a vector operation results in an Undefined Instruction exception with the FPEXC.DEX bit set to 1.

- The Cortex-A7 FPU never generates an asynchronous VFP exception.

In addition it provides information on initializing the Cortex-A7 FPU ready for application code execution.

# 2.1.1 VFP feature identification registers

The Cortex-A7 FPU implements the ARMv7 VFPv4 extension.

Software can identify this extension and the features it provides, using the feature identification registers. These registers are in extension is in the coprocessor space for coprocessors CP10 and CP11. You can access the registers using the VMRS and VMSR instructions, for example:

VMRS <Rd>, FPSID ; Read Floating-Point System ID Register VMRS <Rd>, MVFR1 ; Read Media and VFP Feature Register 1 VMSR FPSCR, <Rt> ; Write Floating-Point System Control Register

See VFP register access on page 2-4 for a description of the registers.

# 2.1.2 Enabling VFP support

From reset, the Cortex-A7 FPU is disabled. Any attempt to execute a VFP instruction results in an Undefined Instruction exception being taken. To enable software to access VFP features ensure that:

- Access to CP10 and CP11 is enabled for the appropriate privilege level. See *VFP register* access on page 2-4.

- If Non-secure access to the VFP features is required, the access flags for CP10 and CP11 in the NSACR must be set to 1. See *VFP register access* on page 2-4.

In addition, software must set the FPEXC.EN bit to 1 to enable most VFP operations. See *Floating-Point Exception Register* on page 2-10.

When VFP operation is disabled because FPEXC.EN is 0, all VFP instructions are treated as Undefined instructions except for execution of the following in privileged modes:

- a VMSR to the FPEXC or FPSID register

- a VMRS from the FPEXC, FPSID, MVFR0, or MVFR1 registers.

# To use the Cortex-A7 FPU in Secure state only

To use the Cortex-A7 FPU in Secure state only, define the CPACR and *Floating-Point Exception* (FPEXC) registers to enable the Cortex-A7 FPU:

1. Set the CPACR for access to CP10 and CP11:

LDR r0, =(0xF << 20) MCR p15, 0, r0, c1, c0, 2  Set the FPEXC EN bit to enable the Cortex-A7 FPU: MOV r3, #0x40000000 VMSR FPEXC, r3

At this point the Cortex-A7 processor can execute VFP instructions.

# To use the Cortex-A7 FPU in Secure state and Non-secure state

To use the Cortex-A7 FPU in Secure state and Non-secure state, first define the NSACR and then define the CPACR and FPEXC registers to enable the Cortex-A7 FPU.

1. Set bits [11:10] of the NSACR for access to CP10 and CP11 from both Secure and Non-secure states:

MRC p15, 0, r0, c1, c1, 2

ORR r0, r0, #2\_11<<10 ; enable fpu

MCR p15, 0, r0, c1, c1, 2</pre>

2. Set the CPACR for access to CP10 and CP11:

LDR r0, =(0xF << 20) MCR p15, 0, r0, c1, c0, 2

3. Set the FPEXC EN bit to enable the Cortex-A7 FPU:

MOV r3, #0x40000000 VMSR FPEXC, r3

At this point the Cortex-A7 processor can execute VFP instructions.

— Note —

Operation is UNPREDICTABLE if you configure the *Coprocessor Access Control Register* (CPACR) such that CP10 and CP11 do not have identical access permissions.

# 2.2 VFP register access

Table 2-1 shows the system control coprocessor registers, accessed through CP15, that determine access to VFP registers, where:

- CRn is the register number within CP15

- Op1 is the Opcode\_1 value for the register

- CRm is the operational register

- Op2 is the Opcode\_2 value for the register.

| CRn | Op1 | CRm | Op2 | Name  | Description                                         |

|-----|-----|-----|-----|-------|-----------------------------------------------------|

| c1  | 0   | c0  | 2   | CPACR | See the Cortex-A7 MPCore Technical Reference Manual |

| c1  | 0   | c1  | 2   | NSACR | See the Cortex-A7 MPCore Technical Reference Manual |

#### **Table 2-1 Coprocessor Access Control registers**

# 2.3 Register summary

Table 2-2 shows the Cortex-A7 FPU system registers. All Cortex-A7 FPU system registers are 32-bit wide. Reserved register addresses are UNPREDICTABLE.

| Name  | Type                                    | Reset      | Description                                            |

|-------|-----------------------------------------|------------|--------------------------------------------------------|

|       | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |            |                                                        |

| FPSID | RO                                      | 0x41023073 | Floating-Point System ID Register on page 2-6          |

| FPSCR | RW                                      | 0x00000000 | Floating-Point Status and Control Register on page 2-6 |

| MVFR0 | RO                                      | 0x10110221 | Media and VFP Feature Register 0 on page 2-8           |

| MVFR1 | RO                                      | 0x11000011 | Media and VFP Feature Register 1 on page 2-9           |

| FPEXC | RW                                      | 0x00000000 | Floating-Point Exception Register on page 2-10         |

### Table 2-2 Cortex-A7 FPU system registers

— Note —

The FPINST and FPINST2 registers are not implemented, and any attempt to access them is UNPREDICTABLE.

# 2.3.1 Processor modes for accessing the Cortex-A7 FPU system registers

Table 2-3 shows the processor modes for accessing the Cortex-A7 FPU system registers.

| Register     | Privileged access |            | User access   |               |

|--------------|-------------------|------------|---------------|---------------|

|              | FPEXC EN=0        | FPEXC EN=1 | FPEXC EN=0    | FPEXC EN=1    |

| FPSID        | Permitted         | Permitted  | Not permitted | Not permitted |

| FPSCR        | Not permitted     | Permitted  | Not permitted | Permitted     |

| MVFR0, MVFR1 | Permitted         | Permitted  | Not permitted | Not permitted |

| FPEXC        | Permitted         | Permitted  | Not permitted | Not permitted |

# Table 2-3 Accessing Cortex-A7 FPU system registers

# 2.4 Register descriptions

This section describes the Cortex-A7 FPU system registers. Table 2-2 on page 2-5 provides cross references to individual registers.

# 2.4.1 Floating-Point System ID Register

The FPSID characteristics are:

| Purpose           | Provides information about the VFP implementation.                                                                                                                                    |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Usage constraints | This register is:                                                                                                                                                                     |  |  |

|                   | • Only accessible in the Non-secure state if the CP10 and CP11 bits in the NSACR are set to 1, see <i>VFP register access</i> on page 2-4.                                            |  |  |

|                   | • Only accessible in privileged modes, and only if access to coprocessors CP10 and CP11 is enabled in the CPACR and FPEXC.EN is set to 1, see <i>VFP register access</i> on page 2-4. |  |  |

| Configurations    | Available in all configurations.                                                                                                                                                      |  |  |

| Attributes        | See the register summary in Table 2-2 on page 2-5.                                                                                                                                    |  |  |

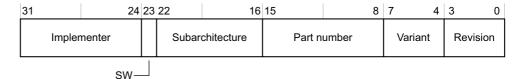

Figure 2-1 shows the FPSID bit assignments.

# Figure 2-1 FPSID bit assignments

Table 2-4 shows the FPSID bit assignments.

#### Table 2-4 FPSID bit assignments

| Bits    | Name            | Function                                                          |

|---------|-----------------|-------------------------------------------------------------------|

| [31:24] | Implementer     | Denotes ARM. Value is 0x41.                                       |

| [23]    | SW              | Hardware implementation with no software emulation. Value is 0x0. |

| [22:16] | Subarchitecture | VFPv3 or greater with v2 subarchitecture. Value is 0x2.           |

| [15:8]  | Part number     | Cortex-A. Value is 0x30.                                          |

| [7:4]   | Variant         | Cortex-A7. Value is 0x7.                                          |

| [3:0]   | Revision        | Revision. Value is 0x3.                                           |

You can access the FPSID with the following VMRS instruction:

VMRS <Rd>, FPSID ; Read Floating-Point System ID register

# 2.4.2 Floating-Point Status and Control Register

The FPSCR characteristics are:

Purpose Provides user-level control of the Cortex-A7 FPU.

Usage constraints This register is:

- Only accessible in the Non-secure state if the CP10 and CP11 bits in the NSACR are set to 1, see *VFP register access* on page 2-4.

- Accessible in all modes depending on the setting of bits [23:20] of the CPACR and FPEXC.EN, see *VFP register access* on page 2-4.

**Configurations** Available in all configurations.

Attributes See the register summary in Table 2-2 on page 2-5.

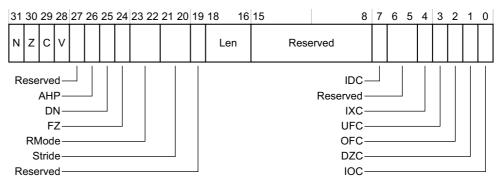

Figure 2-2 shows the FPSCR bit assignments.

# Figure 2-2 FPSCR bit assignments

Table 2-5 shows the FPSCR bit assignments.

### Table 2-5 FPSCR bit assignments

| Bits | Name     | Function                                                                                                            |  |  |

|------|----------|---------------------------------------------------------------------------------------------------------------------|--|--|

| [31] | Ν        | Set to 1 if a comparison operation produces a less than result.                                                     |  |  |

| [30] | Ζ        | Set to 1 if a comparison operation produces an equal result.                                                        |  |  |

| [29] | С        | Set to 1 if a comparison operation produces an equal, greater than, or unordered result.                            |  |  |

| [28] | V        | Set to 1 if a comparison operation produces an unordered result.                                                    |  |  |

| [27] | Reserved | UNK/SBZP.                                                                                                           |  |  |

| [26] | AHP      | Alternative Half-Precision control bit:                                                                             |  |  |

|      |          | 0 IEEE half-precision format selected.                                                                              |  |  |

|      |          | 1 Alternative half-precision.                                                                                       |  |  |

| [25] | DN       | Default NaN mode control bit:                                                                                       |  |  |

|      |          | <b>0</b> NaN operands propagate through to the output of a floating-point operation.                                |  |  |

|      |          | 1 Any operation involving one or more NaNs returns the Default NaN.                                                 |  |  |

| [24] | FZ       | Flush-to-zero mode control bit:                                                                                     |  |  |

|      |          | • Flush-to-zero mode disabled. Behavior of the floating-point system is fully compliant with the IEEE 754 standard. |  |  |

|      |          | 1 Flush-to-zero mode enabled.                                                                                       |  |  |

# Table 2-5 FPSCR bit assignments (continued)

| Bits    | Name     | Function                                                                  |  |

|---------|----------|---------------------------------------------------------------------------|--|

| [23:22] | RMode    | Rounding Mode control field:                                              |  |

|         |          | b00 Round to Nearest (RN) mode.                                           |  |

|         |          | b01 Round towards Plus infinity (RP) mode.                                |  |

|         |          | b10 Round towards Minus infinity (RM) mode.                               |  |

|         |          | b11 Round towards Zero (RZ) mode.                                         |  |

| [21:20] | Stride   | Stride control used for backwards compatibility with short vector values. |  |

|         |          | See the ARM Architecture Reference Manual.                                |  |

| [19]    | Reserved | UNK/SBZP.                                                                 |  |

| [18:16] | Len      | Vector length, used for backwards compatibility with short vector values. |  |

|         |          | See the ARM Architecture Reference Manual.                                |  |

| [15:8]  | Reserved | UNK/SBZP.                                                                 |  |

| [7]     | IDC      | Input Denormal cumulative exception flag.                                 |  |

| [6:5]   | Reserved | UNK/SBZP.                                                                 |  |

| [4]     | IXC      | Inexact cumulative exception flag.                                        |  |

| [3]     | UFC      | Underflow cumulative exception flag.                                      |  |

| [2]     | OFC      | Overflow cumulative exception flag.                                       |  |

| [1]     | DZC      | Division by Zero cumulative exception flag.                               |  |

| [0]     | IOC      | Invalid Operation cumulative exception flag.                              |  |

You can access the FPSCR with the following VMSR instructions:

VMRS <Rd>, FPSCR ; Read Floating-Point Status and Control Register VMSR FPSCR, <Rt> ; Write Floating-Point Status and Control Register

# 2.4.3 Media and VFP Feature Register 0

The MVFR0 characteristics are:

| Purpose              | Together with MVFR1, describes the features that the Cortex-A7 FPU provides.                                                                                                          |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Usage constraints    | This register is:                                                                                                                                                                     |  |  |

|                      | • Only accessible in the Non-secure state if the CP10 and CP11 bits in the NSACR are set to 1, see <i>VFP register access</i> on page 2-4.                                            |  |  |

|                      | • Only accessible in privileged modes, and only if access to coprocessors CP10 and CP11 is enabled in the CPACR and FPEXC.EN is set to 1, see <i>VFP register access</i> on page 2-4. |  |  |

| Configurations       | Available in all configurations.                                                                                                                                                      |  |  |

| Attributes           | See the register summary in Table 2-2 on page 2-5.                                                                                                                                    |  |  |

| Figure 2-3 on page 2 | 2-9 shows the MVFR0 bit assignments.                                                                                                                                                  |  |  |

| 31 28                    | 27 24            | 23 20          | 19 16  | 15 12                        | 11 8                 | 7 4                  | 3 0                 |

|--------------------------|------------------|----------------|--------|------------------------------|----------------------|----------------------|---------------------|

| VFP<br>rounding<br>modes | Short<br>vectors | Square<br>root | Divide | VFP<br>exception<br>trapping | Double-<br>precision | Single-<br>precision | A_SIMD<br>registers |

# Figure 2-3 MVFR0 bit assignments

Table 2-6 shows the MVFR0 bit assignments.

#### Table 2-6 MVFR0 bit assignments

| Bits    | Name                   | Function                                             |

|---------|------------------------|------------------------------------------------------|

| [31:28] | VFP rounding modes     | All VFP rounding modes supported. Value is 0x1.      |

| [27:24] | Short vectors          | VFP short vectors not supported. Value is 0x0.       |

| [23:20] | Square root            | VFP square root operation supported. Value is 0x1.   |

| [19:16] | Divide                 | VFP divide operation supported. Value is 0x1.        |

| [15:12] | VFP exception trapping | VFP exception trapping not supported. Value is 0x0.  |

| [11:8]  | Double-precision       | Double-precision operations supported. Value is 0x2. |

| [7:4]   | Single-precision       | Single-precision operations supported. Value is 0x2. |

| [3:0]   | A_SIMD registers       | Sixteen 64-bit registers supported. Value is 0x1.    |

You can access the MVFR0 with the following VMSR instruction:

VMRS <Rd>, MVFR0 ; Read Media and VFP Feature Register 0

# 2.4.4 Media and VFP Feature Register 1

The MVFR1 characteristics are:

| Purpose           | gether with MVFR0, describes the features that the Cortex-A7 FPU vides.                                                                    |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Usage constraints | This register is:                                                                                                                          |  |  |  |

|                   | • Only accessible in the Non-secure state if the CP10 and CP11 bits in the NSACR are set to 1, see <i>VFP register access</i> on page 2-4. |  |  |  |

|                   | • Only accessible in privileged modes, and only if access to                                                                               |  |  |  |

coprocessors CP10 and CP11 is enabled in the CPACR and FPEXC.EN is set to 1, see *VFP register access* on page 2-4.

Attributes See the register summary in Table 2-2 on page 2-5.

Figure 2-4 shows the MVFR1 bit assignments.

| 31 28  | 27 24 | 23 20  | 19 16  | 15 12   | 11 8       | 7 4   | 3 0  |

|--------|-------|--------|--------|---------|------------|-------|------|

| A_SIMD | VFP   | A_SIMD | A_SIMD | A_SIMD  | A_SIMD     | D_NaN | FtZ  |

| FMAC   | HPFP  | HPFP   | SPFP   | integer | load/store | mode  | mode |

### Figure 2-4 MVFR1 bit assignments

Programmers Model

Table 2-7 shows the MVFR1 bit assignments.

# Table 2-7 MVFR1 bit assignments

| Bits    | Name              | Function                                                               |

|---------|-------------------|------------------------------------------------------------------------|

| [31:28] | A_SIMD FMAC       | Fused Multiply Accumulate supported. Value is 0x1.                     |

| [27:24] | VFP HPFP          | VFP half-precision operations supported. Value is 0x1.                 |

| [23:20] | A_SIMD HPFP       | Advanced SIMD half-precision operations not supported. Value is 0x0.   |

| [19:16] | A_SIMD SPFP       | Advanced SIMD single-precision operations not supported. Value is 0x0. |

| [15:12] | A_SIMD integer    | Advanced SIMD integer operations not supported. Value is 0x0.          |

| [11:8]  | A_SIMD load/store | Advanced SIMD load/store instructions not supported. Value is 0x0.     |

| [7:4]   | D_NaN mode        | Propagation of NaN values supported for VFP. Value is 0x1.             |

| [3:0]   | FtZ mode          | Full denormal arithmetic operations supported for VFP. Value is 0x1.   |

You can access the MVFR1 with the following VMSR instruction:

## 2.4.5 Floating-Point Exception Register

The FPEXC characteristics are:

| Purpose           | Provides global enable control of the VFP extension.                                                                                                         |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Usage constraints | This register is:                                                                                                                                            |  |  |

|                   | • Only accessible in the Non-secure state if the CP10 and CP11 bits in the NSACR are set to 1, see <i>VFP register access</i> on page 2-4.                   |  |  |

|                   | • Only accessible in privileged modes, and only if access to coprocessors CP10 and CP11 is enabled in the CPACR, see <i>VFP</i> register access on page 2-4. |  |  |

| Configurations    | Available in all configurations.                                                                                                                             |  |  |

Attributes See the register summary in Table 2-2 on page 2-5.

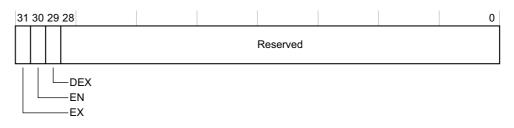

Figure 2-5 shows the FPEXC bit assignments.

Figure 2-5 FPEXC bit assignments

# Table 2-8 FPEXC bit assignments

| Bits   | Name     | Function                                                                                                                                                                                                                                       |

|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31]   | EX       | The Cortex-A7 FPU does not generate asynchronous VFP exceptions, therefore this bit is RAZ/WI.                                                                                                                                                 |

| [30]   | EN       | Cortex-A7 FPU enable bit:                                                                                                                                                                                                                      |

|        |          | 0 FPU disabled.                                                                                                                                                                                                                                |

|        |          | 1 FPU enabled.                                                                                                                                                                                                                                 |

|        |          | The EN bit is cleared to 0 at reset.                                                                                                                                                                                                           |

| [29]   | DEX      | Defined synchronous instruction exceptional flag. The Cortex-A7 FPU sets this bit when generating a synchronous bounce because of an attempt to execute a vector operation. All other Undefined Instruction exceptions clear this bit to zero. |

|        |          | See the ARM Architecture Reference Manual for more information.                                                                                                                                                                                |

| [28:0] | Reserved | RAZ/WI.                                                                                                                                                                                                                                        |

You can access the FPEXC with the following VMSR instructions:

VMRS <Rd>, FPEXC ; Read Floating-Point Exception Register VMSR FPEXC, <Rt> ; Write Floating-Point Exception Register

# Appendix A **Revisions**

This appendix describes the technical changes between released issues of this book.

#### Table A-1 Issue A

| Change                    | Location | Affects |  |

|---------------------------|----------|---------|--|

| No changes, first release | -        | -       |  |

# Table A-2 Differences between issue A and issue B

| Change                                              | Location              | Affects |

|-----------------------------------------------------|-----------------------|---------|

| Updated reset value of the FPSID Register           | Table 2-2 on page 2-5 | r0p1    |

| Updated bits[3:0] of the FPSID Register             | Table 2-4 on page 2-6 | r0p1    |

| Clarified the value for MVFR0.A_SIMD register field | Table 2-6 on page 2-9 | All     |

# Table A-3 Differences between issue B and issue C

| Change                                    | Location              | Affects |

|-------------------------------------------|-----------------------|---------|

| Updated reset value of the FPSID Register | Table 2-2 on page 2-5 | r0p2    |

| Updated bits[3:0] of the FPSID Register   | Table 2-4 on page 2-6 | r0p2    |

Table A-4 Differences between issue C and issue D

| Change                                    | Location              | Affects |

|-------------------------------------------|-----------------------|---------|

| Updated reset value of the FPSID Register | Table 2-2 on page 2-5 | r0p3    |

| Updated bits[3:0] of the FPSID Register   | Table 2-4 on page 2-6 | r0p3    |